### 8 Port 10/100 Ethernet Integrated Switch

#### **Features**

- Support 1k MAC address

- 512k bits packet buffer memory

- Support auto-polarity for 10 Mbps

- Support filter/ forward special DA option

- Support broadcast storm protection

- Auto MDI-MDIX option

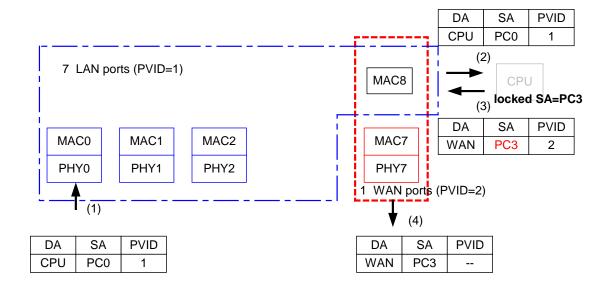

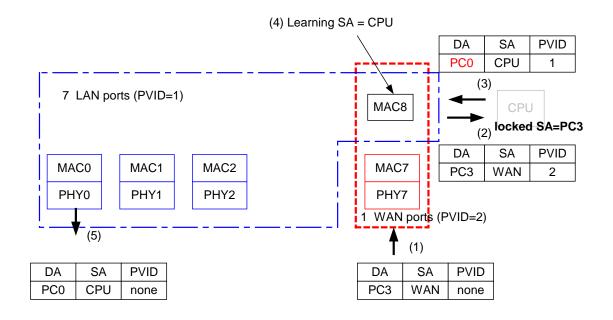

- Support port security option to lock the first MAC address

- Support one MII/RMII port, which works at 100 Mbps full duplex for router application

- Support port base VLAN & tag VLAN

- Support CoS

- Support SMART MAC function

- Support spanning tree protocol

- Support max forwarding packet length 1552/ 1536 bytes option

- Support 8-level bandwidth control

- Support SCA

- Support two fiber ports with far end fault function for IP178CH only

- Built in linear regulator control circuit

- Support Lead Free package (Please refer to the Order Information)

Note – some features need CPU support, please refer to the detail description inside this data sheet

#### **General Description**

**IP178C/IP178CH** integrates a 9-port switch controller, SSRAM, and 8 10/100 Ethernet transceivers. Each of the transceivers complies with the IEEE802.3, IEEE802.3u, and IEEE802.3x specifications. The transceivers are designed in DSP approach in 0.18um technology; they have high noise immunity and robust performance.

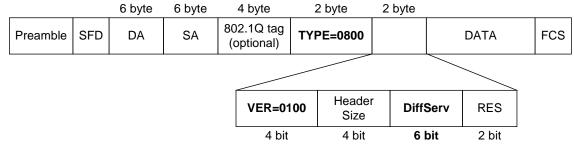

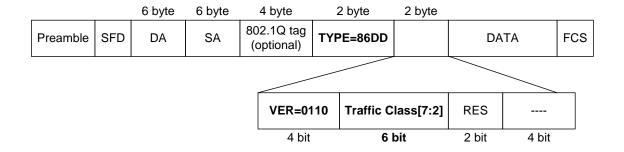

**IP178C/IP178CH** operates in store and forward mode. It supports flow control, auto MDI/MDI-X, CoS, port base VLAN, bandwidth control, DiffServ, SMART MAC and LED functions, etc. Each port can be configured as auto-negotiation or forced 10 Mbps/100 Mbps, full/half duplex mode. Using an EEPROM or pull up/down resistors on specific pins can configure the desired options.

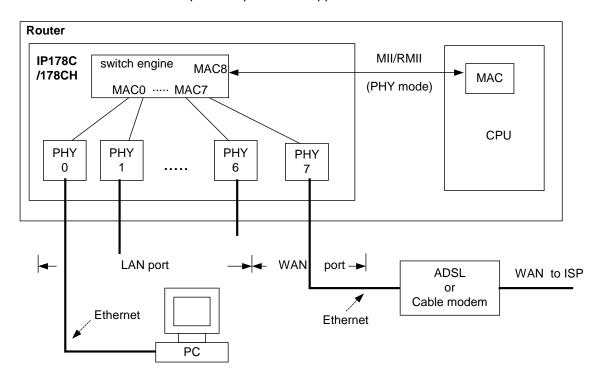

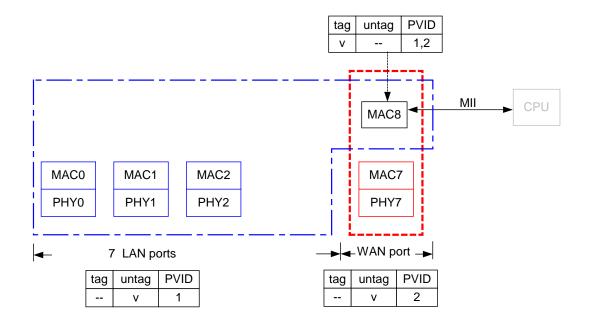

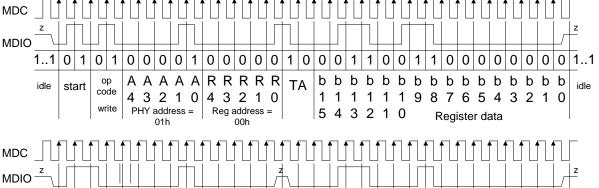

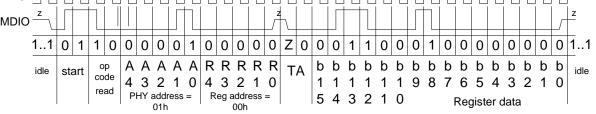

Besides an 8-port switch application, IP178C/IP178CH supports one MII/RMII ports for router application, which supports 7 LAN ports and one WAN port. The external MAC can monitor or configure IP178C/IP178CH by accessing MII registers through SMI.

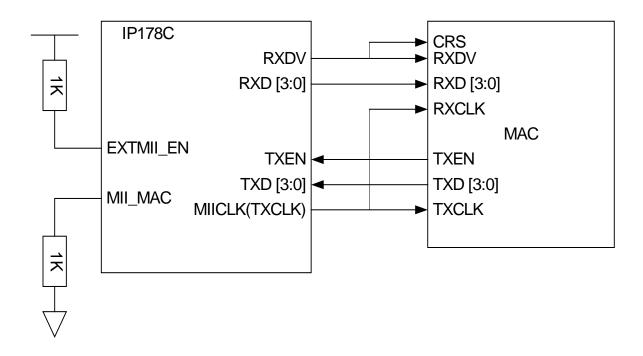

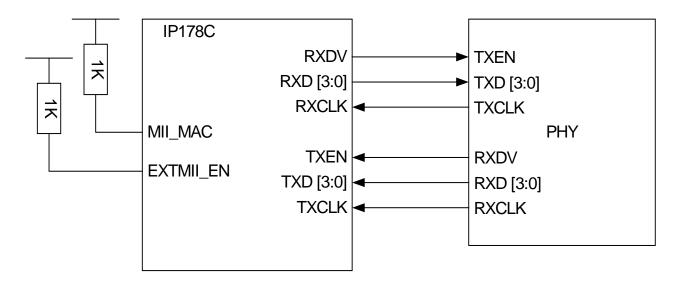

MII/RMII port also can be configured to be MAC mode. It is used to interface an external PHY to work as an 8+1 switch.

**IP178CH** supports two fiber ports with far end fault function.

### **Table Of Contents**

| Features                              |    |

|---------------------------------------|----|

| General Description                   | 1  |

| Table Of Contents                     |    |

| Revision History                      | 3  |

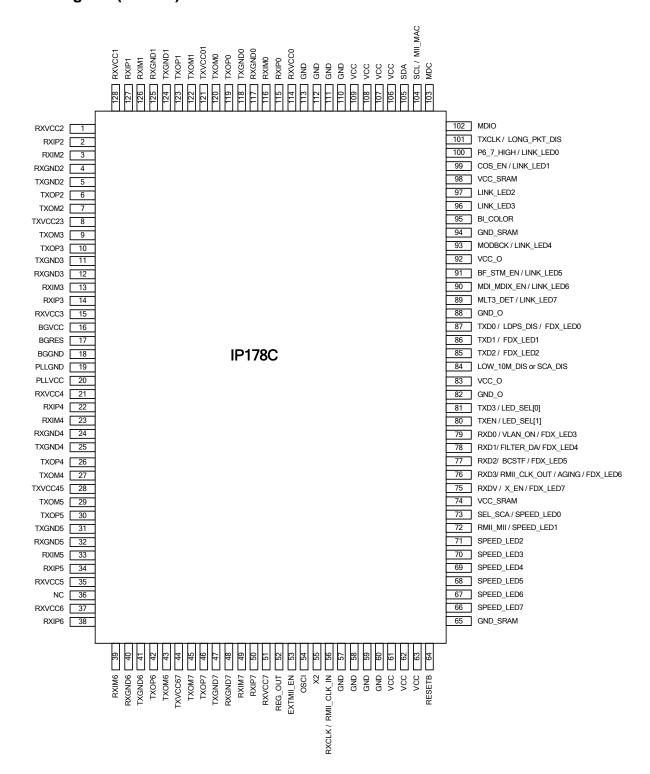

| Pin diagram (IP178C)                  | 10 |

| 1 Pin description                     | 15 |

| Pin description (continued)           | 16 |

| Pin description (continued)           | 18 |

| Pin description (continued)           | 19 |

| Pin description (continued)           | 20 |

| Pin description (continued)           | 21 |

| Pin description (continued)           | 22 |

| Pin description (continued)           | 24 |

| Pin description (continued)           | 25 |

| Pin description (continued)           | 26 |

| Pin description (continued)           | 27 |

| Pin description (continued)           |    |

| 2 Functional Description              |    |

| 2.1 Flow control                      |    |

| 2.2 Broadcast storm protection        | 33 |

| 2.3 Port locking                      |    |

| 2.4 Port base VLAN                    |    |

| 2.5 Tag VLAN/ Tag and un-tag function |    |

| 2.6 Tag VLAN                          |    |

| 2.7 Tag VLAN in router application    |    |

| 2.8 Smart MAC                         |    |

| 2.9 CoS                               |    |

| 2.9.1 Port base priority              |    |

| 2.9.2 Frame base priority             |    |

| 2.10 Spanning tree                    |    |

| 2.11 Static MAC address table         |    |

| 2.12 Serial management interface      |    |

| 2.13 SCA                              |    |

| 2.14 Bandwidth control                |    |

| 2.15 Register descriptions            |    |

| 3 Electrical Characteristics          |    |

| 3.1 Absolute Maximum Rating           |    |

| 3.2 DC Characteristic                 |    |

| 3.3 AC Timing                         |    |

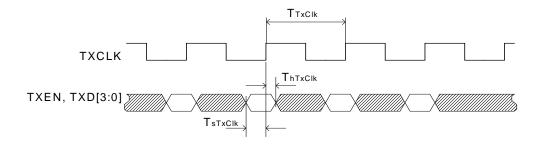

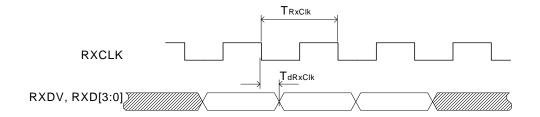

| 3.3.1 PHY Mode MII Timing             |    |

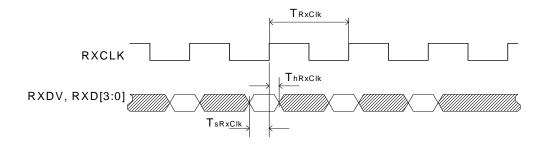

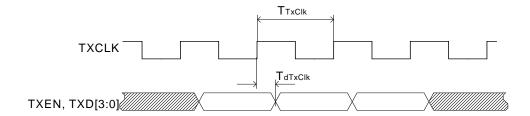

| 3.3.2 MAC Mode MII Timing             |    |

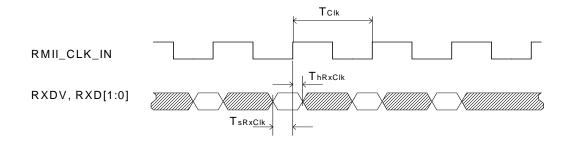

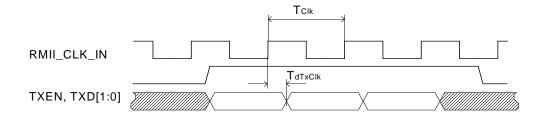

| 3.3.3 RMII Timing                     |    |

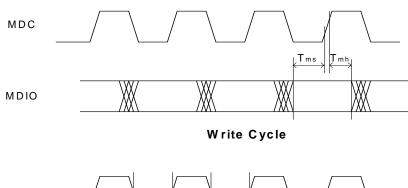

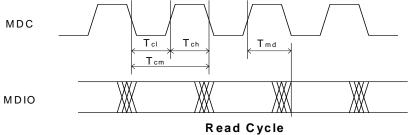

| 3.3.4 SMI Timing                      |    |

| 3.3.5 EEPROM Timing                   |    |

| 3.4 Thermal Data                      |    |

| 4 Order information                   |    |

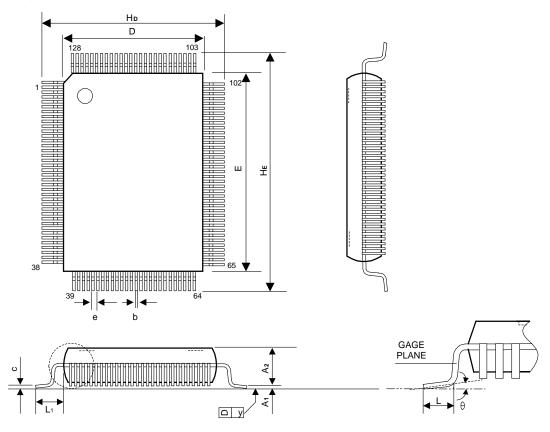

| 5 Package Detail                      | 93 |

### **Revision History**

| Revision #    | Change Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IP178C-DS-R01 | Initial release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| IP178C-DS-R02 | <ol> <li>Modify Pin diagram in page 9, pin_89 from HASH_MODE[1]/LINK_LED7 to MLT3_DET/LINK_LED7,pin 84 from LOW_10M_DIS to SCA_DIS, pin_36 from SCA to NC, VCTRL to REG_OUT</li> <li>Replace VCTRL with REG_OUT</li> <li>Modify HASH_MODE [1] to MLT3_DET in page 17, 54 &amp; 55</li> <li>Modify pin 84 from LOW_10M_DIS to SCA_DIS, pin_36 from SCA to NC</li> <li>Change BF_STM_THR_SEL [1:0] from 01: 128 frames to 126 frames in page 74</li> <li>Modify EXT MII Pin description in page 21, 22, 23</li> <li>"100M" change to "100 Mbps" and "10M" change to "10 Mbps".</li> <li>Modify PHY mode for only support one MIICLK on page 25</li> <li>Add in Thermal Data on page 85</li> <li>Add in power consumption on page 80</li> <li>P.54 PHY30.1[12] Default value=0, P.56 PHY30.2[7] Default value=0, P.56 PHY30.2[0] 爲 FORCE_MODE -&gt; BI_COLOR</li> <li>1.8V change 1.95V</li> </ol> |

| IP178C-DS-R03 | <ol> <li>Modify FILTER_DA, 01-80-c2-00-00-00 to 01-80-c2-00-00-02 on page 19</li> <li>Modify VLAN_ON function when Pin 53EXTMII_EN=1 on page 18</li> <li>Modify long packet enable function description on page 55</li> <li>Modify Backpressure type selection on page 54</li> <li>Modify RESETB CKT on page 14</li> <li>Modify HASH_MODE [0] to LDPS_DIS on page 17, 54</li> <li>Modify Pin type description on page 13</li> <li>Modify Pin 84 from SCA_DIS to LOW_10M_DIS or SCA_DIS on page 14</li> <li>Modify Pin 73 from LINK_Q to SEL_SCA on page 18</li> <li>Modify Pin diagram on page 9, pin_87 from HASH_MODE [0] to LDPS_DIS,pin 84 from SCA_DIS to LOW_10M_DIS or SCA_DIS, pin_73 from LINK_Q to SEL_SCA</li> </ol>                                                                                                                                                                 |

| IP178C-DS-R04 | <ol> <li>Modify broadcast storm protection function on page 18, page 30, page 75</li> <li>Add BW control value setting on page 81</li> <li>Add BW control description on page 45</li> <li>Rearrange Index</li> <li>Add special_add_forward description on page 81</li> <li>Add "The function is valid only if pin 53 EXTMII_EN is pulled low." To pin 75, 76, 77, 78, 85, 86, 87</li> <li>Add Note on page 1 for CPU support</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| IP178C-DS-R05 | Add the order information for lead free package                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| IP178C-DS-R06 | 1. Add IP178C.RX_DV connect to MAC.RX_DV and MAC.CRS on page 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| IP178C-DS-R07 | <ol> <li>All ports unlink on page 84 for VCC</li> <li>Modify VCC min form 1.85V to 1.80V on page 84</li> <li>Modify regulator description on page 1 &amp; 13</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| IP178C-DS-R08 | <ol> <li>Revise the pin description.</li> <li>Modify Pin diagram of pin 85, 86, 96 and 97.</li> <li>Modify application diagram on page 10.</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

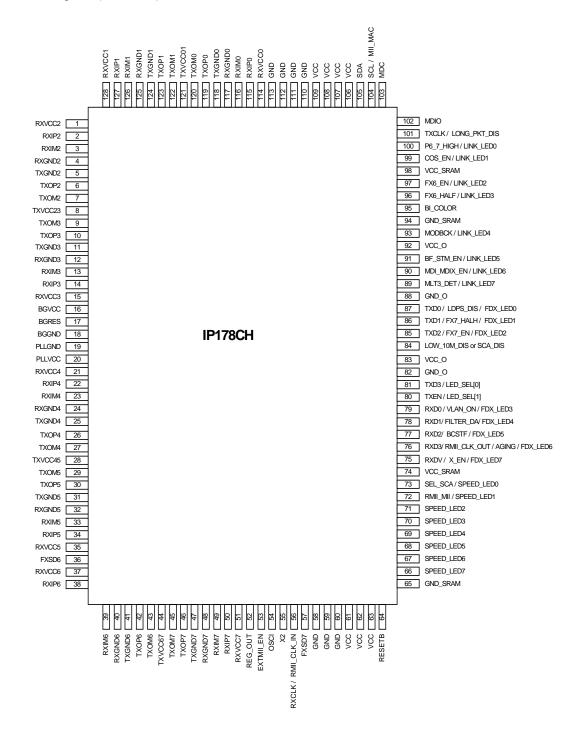

| IP178C-DS-R09 | <ol> <li>Add FXSD7 on page 26 FXSD6 on page 15</li> <li>Add fiber application for order information on page 90</li> <li>Add IP178CH Pin diagram on page 10</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| IP178C-DS-R10 | 1. Modify Pin diagram of pin 85, 86, 96 and 97 (IP178CH)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

### **Revision History**

| Revision #     | Change Description                                                                                            |

|----------------|---------------------------------------------------------------------------------------------------------------|

|                | 2. Modify Pin description on page 21 for (IP178CH)                                                            |

|                | 3. Modify initial setting on page 5 for (IP178CH)                                                             |

| IP178Cx-DS-R11 | 1. Modify SCA Table on page 48                                                                                |

|                | Replace with new SCA register table                                                                           |

|                | 3. Replace IP178C with IP178C/IP178CH                                                                         |

|                | 4. Modify the difference of the definition in pin 36 and 57 between IP178B and IP178C/IP178CH on page 5 and 6 |

|                | 5. Modify application blocks on page 12, 13 and 14                                                            |

|                | 6. Add "IP178CH support two fiber " to feature list and general description on page 1                         |

| IP178Cx-DS-R12 | 1. Modify from "register 0" to "register 5" on page 74                                                        |

|                | 2. Modify flow control description on page 32                                                                 |

|                | 3. Modify IPL/IPH description on page 15                                                                      |

|                | 4. Add 2.5V VCC_O DC description on page 86                                                                   |

|                | 5. Modify Bi-color LED definition on page 19                                                                  |

|                | 6. Replace PHY0 register 1.1 IP113A to IP178C/IP178CH & add RO/LH on page 51                                  |

|                | 7. Modify OP0 OP1 to FX enable/half on page 60                                                                |

|                | 8. Add FXSDx DC on page 86                                                                                    |

|                | 9. Modify LED Flash behavior on page 31                                                                       |

|                | 10. Add X1 VIL & X1 VIH on page 86                                                                            |

|                | 11. Add 512k bits packet buffer memory on page 1                                                              |

### The difference in pin definition between IP178B and IP178C/IP178CH (MII port disabled: EXTMII\_EN=0)

| Pin |            | IP178B        |      | IP178C/IP178CH                |                                |      |

|-----|------------|---------------|------|-------------------------------|--------------------------------|------|

|     | Function   | Configure     | Туре | Function                      | Configure                      | Type |

| 36  | NC         |               | 1    | NC(IP178C)<br>FXSD6(IP178CH)  |                                | IPL  |

| 52  | REG_OUT    |               | I    | REG_OUT                       |                                | 0    |

| 53  | OSCGND     |               |      |                               | EXTMII_EN=0                    | IPL  |

| 56  | OSCVCC     |               |      | RXCLK                         |                                | IPH  |

| 57  | GND        |               |      | GND(IP178C)<br>FXSD7(IP178CH) |                                |      |

| 72  | SPEED_LED1 | DIRECT_LED    | IPL  | SPEED_LED1                    |                                | IPL  |

| 73  | SPEED_LED0 |               |      | SPEED_LED0                    | SEL_SCA                        | IPL  |

| 75  | FDX_LED7   |               |      | FDX_LED7                      | X_EN                           | IPH  |

| 76  | FDX_LED6   |               |      | FDX_LED6                      | AGING                          | IPH  |

| 77  | FDX_LED5   |               |      | FDX_LED5                      | BCSTF                          | IPL  |

| 78  | FDX_LED4   |               |      | FDX_LED4                      | FILTER_DA                      | IPL  |

| 79  | FDX_LED3   | VLAN_ON       | IPL  | FDX_LED3                      | VLAN_ON                        | IPL  |

| 80  |            | LED_SEL [1]   | IPH  |                               | LED_SEL [1]                    | IPH  |

| 81  |            | LED_SEL [0]   | IPH  |                               | LED_SEL [0]                    | IPH  |

| 84  |            | AGING         | IPH  | LOW_10M_DIS/<br>SCA_DIS       |                                | IPH  |

| 85  | FDX_LED2   | OP1 [1]       | IPL  | FDX_LED2                      | FX7_EN<br>(for IP178CH only)   | IPL  |

| 86  | FDX_LED1   | OP1 [0]       | IPL  | FDX_LED1                      | FX7_HALF<br>(for IP178CH only) | IPL  |

| 87  | FDX_LED0   | HASH_MODE [0] | IPL  | FDX_LED0                      | LDPS_DIS                       | IPL  |

| 90  |            | MID_MDIX_EN   | IPL  |                               | MID_MDIX_EN                    | IPH  |

| 95  |            | FORCE_MODE    | IPL  |                               | BI_COLOR                       | IPL  |

| 96  | LINK_LED3  | OP0 [0]       | IPL  | LINK_LED3                     | FX6_EN<br>(for IP178CH only)   | IPL  |

| 97  | LINK_LED2  | OP0 [1]       | IPL  | LINK_LED2                     | FX6_HALF<br>(for IP178CH only) | IPL  |

| 101 |            | UPDATE_R4_EN  | IPH  | TXCLK                         | LONG_PKT_DIS                   | IPH  |

| 102 | EEDI       |               | IPL  | MDIO                          |                                | IPH  |

| 103 | EEDO       |               | IPL  | MDC                           |                                | IPL  |

| 104 | EECS       |               | IPL  | SCL                           |                                | IPL  |

| 105 | EESK       |               | IPL  | SDA                           |                                | IPH  |

The difference in pin definition between IP178B and IP178C/IP178CH (MII port enabled: EXTMII\_EN=1)

| Pin |            | IP178B        |      | IP178C/IP178CH                |                                |      |

|-----|------------|---------------|------|-------------------------------|--------------------------------|------|

|     | Function   | Configure     | Туре | Function                      | Configure                      | Туре |

| 36  | NC         |               | I    | NC(IP178C)<br>FXSD6(IP178CH)  |                                | IPL  |

| 52  | REG_OUT    |               | I    | REG_OUT                       |                                | 0    |

| 53  | OSCGND     |               |      |                               | EXTMII_EN=1                    | IPL  |

| 56  | OSCVCC     |               |      | RMII_CLK_IN                   |                                | IPH  |

| 57  | GND        |               |      | GND(IP178C)<br>FXSD7(IP178CH) |                                |      |

| 72  | SPEED_LED1 | DIRECT_LED    | IPL  | SPEED_LED1                    | RMII_ MII                      | IPL  |

| 73  | SPEED_LED0 |               |      | SPEED_LED0                    | SEL_SCA                        | IPL  |

| 75  | FDX_LED7   |               |      | RXDV                          | X_EN                           | IPH  |

| 76  | FDX_LED6   |               |      | RMII_CLK_OUT                  | AGING                          | IPH  |

| 77  | FDX_LED5   |               |      | RXD2                          | BCSTF                          | IPL  |

| 78  | FDX_LED4   |               |      | RXD1                          | FILTER_DA                      | IPL  |

| 79  | FDX_LED3   | VLAN_ON       | IPL  | RXD0                          | VLAN_ON                        | IPL  |

| 80  |            | LED_SEL [1]   | IPH  | TXEN                          | LED_SEL [1]                    | IPH  |

| 81  |            | LED_SEL [0]   | IPH  | TXD3                          | LED_SEL [0]                    | IPH  |

| 84  |            | AGING         | IPH  |                               | LOW_10M_DIS/<br>SCA_DIS        | IPH  |

| 85  | FDX_LED2   | OP1 [1]       | IPL  | TXD2                          | (note1)<br>(for IP178CH only)  | IPL  |

| 86  | FDX_LED1   | OP1 [0]       | IPL  | TXD1                          | (note1)<br>(for IP178CH only)  | IPL  |

| 87  | FDX_LED0   | HASH_MODE [0] | IPL  | TXD0                          | LDPS_DIS                       | IPL  |

| 90  |            | MID_MDIX_EN   | IPL  |                               | MID_MDIX_EN                    | IPH  |

| 95  |            | FORCE_MODE    | IPL  |                               | BI_COLOR                       | IPL  |

| 96  | LINK_LED3  | OP0 [0]       | IPL  | LINK_LED3                     | FX6_EN<br>(for IP178CH only)   | IPL  |

| 97  | LINK_LED2  | OP0 [1]       | IPL  | LINK_LED2                     | FX6_HALF<br>(for IP178CH only) | IPL  |

| 101 |            | UPDATE_R4_EN  | IPH  | TXCLK                         | LONG_PKT_DIS                   | IPH  |

| 102 | EEDI       |               | IPL  | MDIO                          |                                | IPH  |

| 103 | EEDO       |               | IPL  | MDC                           |                                | IPL  |

| 104 | EECS       |               | IPL  | SCL                           | MII_MAC                        | IPL  |

| 105 | EESK       |               | IPL  | SDA                           |                                | IPH  |

Note1: FX7\_EN & FX7\_HALH only can be updated by EEPORM or MDC/MDIO when EXTMII\_EN = 1

#### Features comparison between IP178B and IP178C/IP178CH

| Function                       | IP178B                 | IP178C/I                                 | P178CH                                  |

|--------------------------------|------------------------|------------------------------------------|-----------------------------------------|

| EEPROM                         | 93C46                  | 24C01A                                   |                                         |

| SCA (Smart Cable Analysis)     | X                      | C                                        | )                                       |

| UPDATE_R4_EN                   | 0                      | Х                                        |                                         |

| 8 TP + 1* MII (9 port switch)  | 8 TP                   | 8 TP + 1* MII (                          | 9 port switch)                          |

|                                |                        | Disable MII port<br>(pin 53 EXTMII_EN=0) | Enable MII port<br>(pin 53 EXTMII_EN=1) |

| LED pins                       | Link, Speed,<br>Duplex | Link, Speed, Duplex                      | Link, Speed                             |

| Link quality LED               | X                      | Pin 73                                   | Default on (note1)                      |

| VLAN_ON                        | Pin 79                 | Pin 79                                   | Default off (note1)                     |

| Filter reserved address option | Fixed on               | Pin 78                                   | Default off (note1)                     |

| Broadcast frame option         | X                      | Pin 77                                   | Default off (note1)                     |

| Aging option                   | Pin 84                 | Pin 76                                   | Default on (note1)                      |

| Flow control option            | Fixed on               | Pin 75                                   | Default on (note1)                      |

| Max packet length option       | X                      | Pin 101                                  | Default off (note1)                     |

| MII port speed/ duplex         | X                      | X                                        | Fixed 100 Mbps full                     |

| RMII/MII option                | X                      | X                                        | Pin 72                                  |

| MII MAC mode/ PHY mode         | X                      | X                                        | Pin 104                                 |

| MII register, MDC/MDIO         | X                      | X                                        | 0                                       |

| Built in regulator             | X                      | 2.5v → 1.95V                             | 3.3V → 1.95V                            |

**Note1**: The default value can be updated by EEPORM or MDC/MDIO.

Note2: It is UPDATE\_R4\_EN in IP178B.

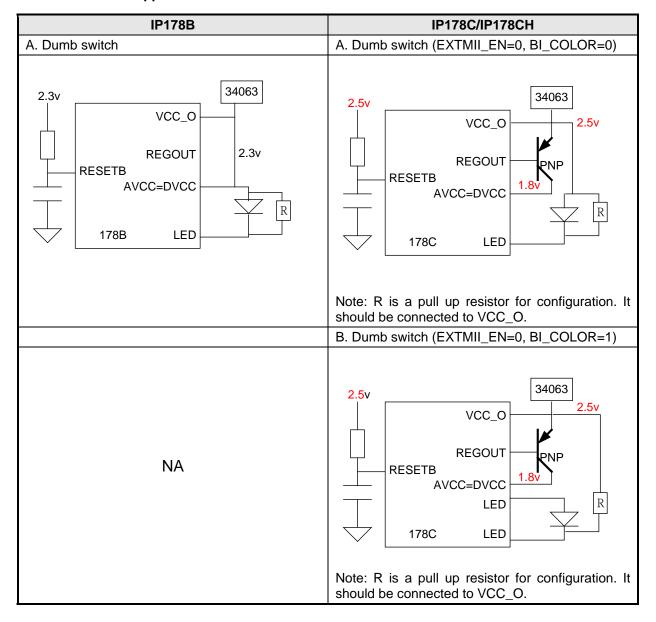

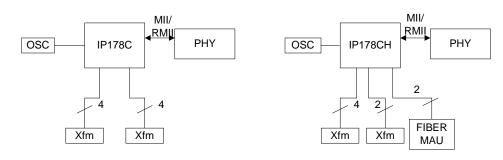

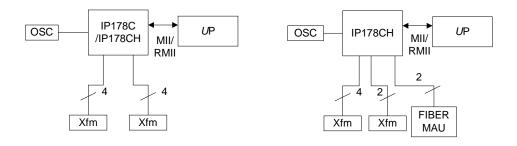

#### The differences in application circuit between IP178B and IP178C/IP178CH

### The differences in application circuit between IP178B and IP178C/IP178CH (continued)

| IP178B | IP178C/IP178CH                                                                                                         |

|--------|------------------------------------------------------------------------------------------------------------------------|

|        | C. Router (EXTMII_EN=1, BI_COLOR=0)                                                                                    |

| NA     | 3.3v<br>VCC_O<br>REGOUT<br>RESETB<br>AVCC=DVCC<br>178C LED                                                             |

|        | Note: R is a pull up resistor for configuration. It should be connected to VCC_O.  D. Router (EXTMII_EN=1, BI_COLOR=1) |

| NA     | 3.3v  VCC_O  REGOUT  RESETB  AVCC=DVCC  LED  178C  LED  R  R                                                           |

|        | Note: R is a pull up resistor for configuration. It should be connected to VCC_O.                                      |

#### Pin diagram (IP178C)

Pin diagram (IP178CH)

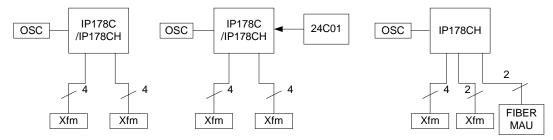

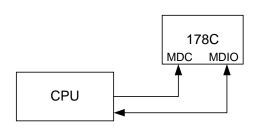

#### An 8-port switch

#### A 9-port switch

#### An 8-port router

IP178C/IP178CH applications: (continued)

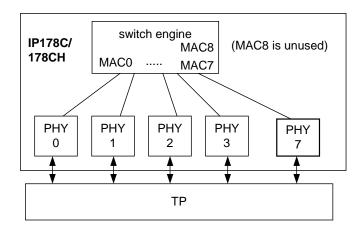

#### An 8-port switch application

If pin 53 EXTMII\_EN is pulled low, then MII/ RMII interface is disabled. **IP178C/IP178CH** is not connected to a CPU and works as an 8-port switch. The ninth switch port MAC8 is unused in this application.

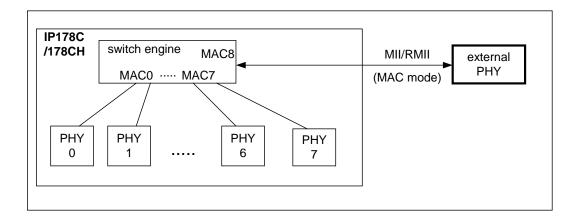

#### A 9-port switch application

If pin 53 EXTMII\_EN is pulled high, then MII/ RMII interface is enabled. The ninth switch port MAC8 is connected to a PHY through the MII/RMII interface. **IP178C/IP178CH** works as a 9-port switch. Because **IP178C/IP178CH** doesn't access the MII register of the external PHY through SMI, MII/RMII interface should be MAC mode and full duplex in this application.

#### IP178C/IP178CH applications: (continued)

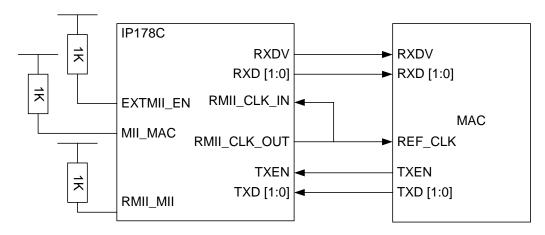

#### An 8-port router application

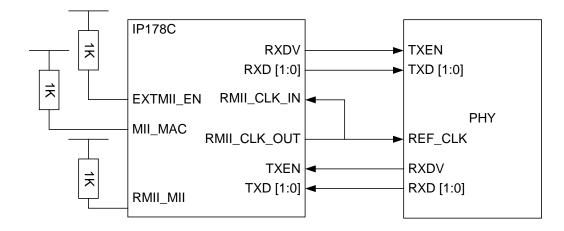

IF pin 53 EXTMII\_EN is pulled high, then MII/RMII interface is enabled. **IP178C/IP178CH** is connected to a CPU through MII/ RMII interface. **IP178C/IP178CH** works as an 8-port router. MII/RMII interface is set to be PHY mode and 100 Mbps full duplex in this application.

### 1 Pin description

| Туре | Description                               |

|------|-------------------------------------------|

| I    | Input pin                                 |

| 0    | Output pin                                |

| IPL  | Input pin with internal pull low 50M ohm  |

| IPH  | Input pin with internal pull high 50M ohm |

| Туре | Description                                  |

|------|----------------------------------------------|

| IPL1 | Input pin with internal pull low 22.8k ohm   |

| IPH1 | Input pin with internal pull high 22.8k ohm  |

| IPL2 | Input pin with internal pull low 92.6k ohm   |

| IPH2 | Input pin with internal pull high 113.8k ohm |

| Pin No.                                                                               | Label              | Туре | Description                                                                                                                                                                                 |

|---------------------------------------------------------------------------------------|--------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Analog                                                                                |                    |      |                                                                                                                                                                                             |

| 52                                                                                    | REG_OUT            | 0    | Regulator output voltage                                                                                                                                                                    |

|                                                                                       |                    |      | The internal regulator uses pin83/pin92 VCC_O as reference voltage to control external transistor to generate a voltage source between 1.80v ~ 2.05v                                        |

|                                                                                       |                    |      | If pin 53 EXTMII_EN is pulled high, then pin83/pin92 VCC_O should be connected to 3.3v to generate 1.80v ~ 2.05v voltage source.  If pin 53 EXTMII_EN is pulled low, then pin83/pin92 VCC_O |

|                                                                                       |                    |      | should be connected to 2.5v to generate 1.80v ~ 2.05v voltage source.                                                                                                                       |

| 17                                                                                    | BGRES              | I    | Band gap resister                                                                                                                                                                           |

|                                                                                       |                    |      | It is connected to GND through a 6.19k (1%) resistor in application circuit.                                                                                                                |

| 115, 116,<br>127, 126,<br>2, 3, 14,<br>13, 22,<br>23, 34,<br>33, 38,<br>39, 50,<br>49 | RXIP0~7<br>RXIM0~7 | _    | TP receive                                                                                                                                                                                  |

| 119, 120,<br>123, 122,<br>6, 7, 10,<br>9, 26, 27,<br>30, 29,<br>42, 43,<br>46, 45     | TXOP0~7<br>TXOM0~7 | 0    | TP transmit                                                                                                                                                                                 |

| Pin No. | Label         | Туре       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|---------|---------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Misc.   |               | 71.5       | The state of the s |

| 36      | NC            |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|         | (FXSD6)       |            | (for IP178CH only)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 54      | OSCI          | I          | 25Mhz system clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|         |               |            | It is recommended to connect OSCI and X2 to a 25M crystal. If the clock source is from another chip or oscillator, the clock should be active at least for 1ms before pin 64 RESETB de-asserted.  Pin 55 X2 should be left open in this application.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 55      | X2            | 0          | Crystal pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|         |               |            | A 25Mhz crystal can be connected to OSCI and X2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 64      | RESETB        | ı          | Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|         |               | ·          | It is low active. It must be hold for more than 1ms. It is Schmitt trigger input. If a R/C reset circuit is used, the capacitor should be connected to VCC_O as shown in the figure.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|         |               |            | VCC_O R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|         |               |            | C GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 84      | LOW_10M_DIS   | IPH2       | LOW_10M_DIS or SCA_DIS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|         | Or<br>SCA_DIS |            | If pin 73 SEL_SCA is pull low, then pin 84 is LOW_10M_DIS. If pin 73 SEL_SCA is pull high, then pin 84 is SCA_DIS.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|         |               |            | For LOW_10M_DIS  1: disable power saving mode, the 10M transmit amplitude is depressed in this mode. (default)  0: enable power saving mode For SCA_DIS  1: Disable smart cable analysis function (default).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|         |               |            | 0: Enable smart cable analysis function.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| EEPROM  |               |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

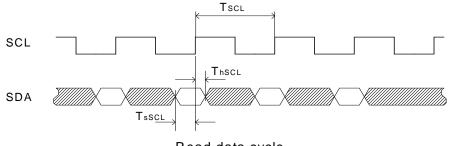

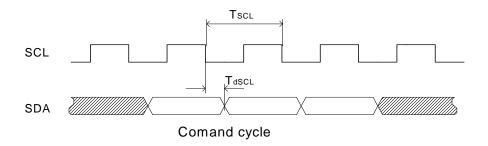

| 104     | SCL           | IPL2<br>/O | Clock of EEPROM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|         |               |            | After reset, it is used as clock pin SCL of EEPROM. After reading EEPROM, this pin becomes an input pin. Its period is longer than 10us.  IP178C/IP178CH stops reading the rest data in EEPROM if the first two bytes in EEPROM aren't 55AA.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 105 | SDA | IPH2 | Data of EEPROM                                                                                          |

|-----|-----|------|---------------------------------------------------------------------------------------------------------|

|     |     | /0   | After reset, it is used as data pin SDA of EEPROM. After reading EEPROM, this pin becomes an input pin. |

| Pin no.                                  |           | Label       | Туре                                                  |                                                               | Description                                                                                                                             |                                                         |

|------------------------------------------|-----------|-------------|-------------------------------------------------------|---------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|

| LED.                                     |           |             |                                                       |                                                               |                                                                                                                                         |                                                         |

| 89, 90,<br>91, 93,<br>96, 97,<br>99, 100 | LINK      | _LED [7:0]  | 0                                                     |                                                               | ctions are illustrated in<br>nected to VCC_O through                                                                                    |                                                         |

| 66, 67,                                  | SPE       | D_LED [7:0] | 0                                                     | SPEED LED                                                     |                                                                                                                                         |                                                         |

| 68, 69,<br>70, 71,<br>72, 73             |           |             |                                                       |                                                               | ctions are illustrated in nected to VCC_O through                                                                                       |                                                         |

| 75, 76,                                  | FDX_      | LED [7:0]   | 0                                                     | FDX LED                                                       |                                                                                                                                         |                                                         |

| 77, 78,<br>79, 85,<br>86, 87             |           |             |                                                       |                                                               | ctions are illustrated in<br>nected to VCC_O through                                                                                    |                                                         |

|                                          |           |             |                                                       | The function is valid only if pin 53 EXTMII_EN is pulled low. |                                                                                                                                         |                                                         |

| 80, 81                                   | LED_      | SEL [1:0]   | IPH2                                                  | select LED mo<br>functions are ill<br>After reset, the        | election  hese pins are latched a  odes. The default value  lustrated in the following  ese two pins becomes M  EXTMII_EN is pulled hig | is mode 3. The detail table.  III interface TXEN and    |