## gapDRIVE™: galvanically isolated single gate driver

Datasheet - production data

#### **Features**

- Qualified for automotive applications according to AEC-Q100

- High voltage rail up to 1500 V

- Driver current capability: 5 A sink/source current at 25 °C

- dV/dt transient immunity ± 50 V/ns in full temperature range

- · Overall input/output propagation delay: 100 ns

- Separate sink and source for easy gate driving configuration

- · Negative gate drive ability

- Active Miller clamp

- · Desaturation detection

- SENSE input

- V<sub>CE</sub> active clamping

- Output 2-level turn-off

- · Diagnostic status output

- UVLO and OVLO functions

- · Programmable input deglitch filter

- Asynchronous stop command

- Programmable deadtime, with violation error

- SPI interface for parameters programming

- Temperature warning and shutdown protection

- Self-diagnostic routines for protection features

- Full effective fault protection

#### **Applications**

- 600/1200 V inverters

- Inverters for EV\HEV

- EV charging stations

- Industrial drives

- UPS equipment

- DC/DC converters

- Solar inverters

#### **Description**

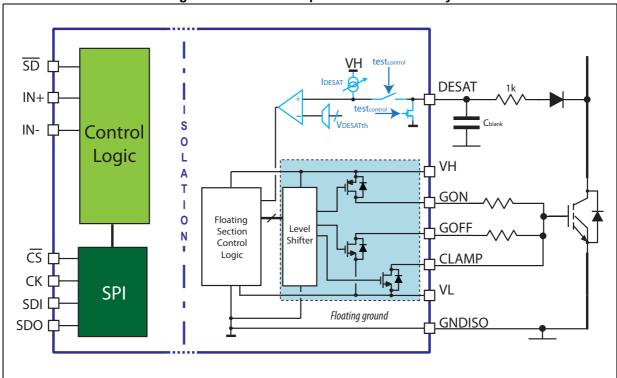

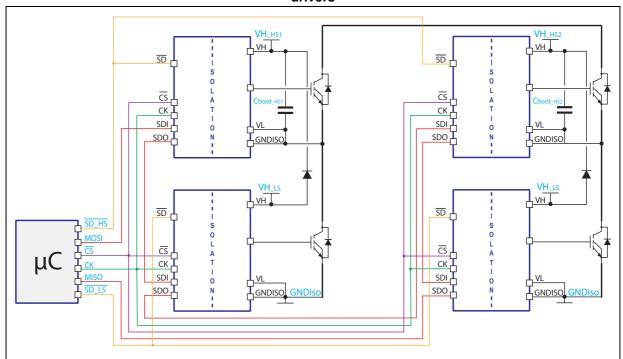

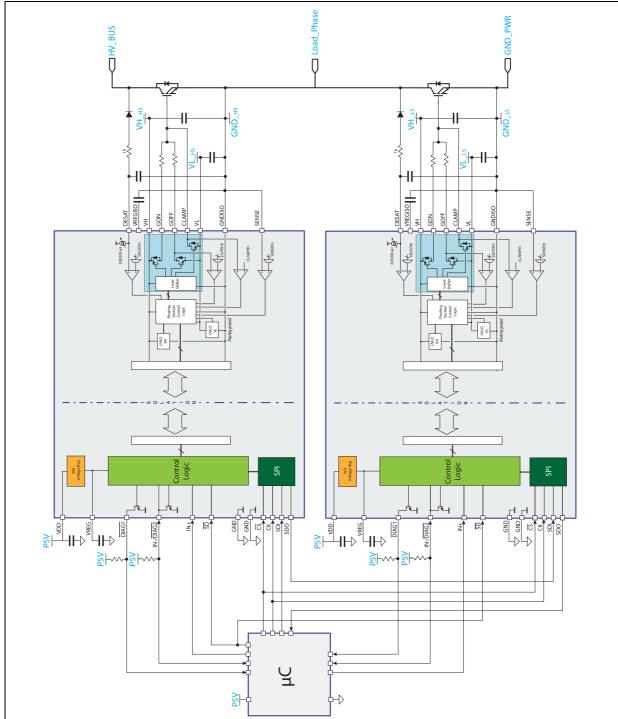

The STGAP1S gapDRIVE™ is a galvanically isolated single gate driver for N-channel MOSFETs and IGBTs with advanced protection, configuration and diagnostic features. The architecture of the STGAP1S isolates the channel from the control and the low voltage interface circuitry through true galvanic isolation.

The gate driver is characterized by 5 A capability, making the device also suitable for high power inverter applications such as motor drivers in hybrid and electric vehicles and in industrial drives. The output driver section provides a rail-to-rail output with the possibility to use a negative gate driver supply.

The input to output propagation delay results contained within 100 ns, providing high PWM control accuracy.

Protection functions such as the Miller clamp, desaturation detection, dedicated sense pin for overcurrent detection, output 2-level turn-off, VCE overvoltage protection, UVLO and OVLO are included to easily design high reliability systems. Open drain diagnostic outputs are present and detailed device conditions can be monitored through the SPI. Each function's parameter can be programmed via the SPI, making the device very flexible and allowing it to fit in a wide range of applications. Separate sink and source outputs provide high flexibility and bill of material reduction for external components.

Contents STGAP1S

# **Contents**

| 1 | Bloo  | k diagram 8                                |  |  |  |

|---|-------|--------------------------------------------|--|--|--|

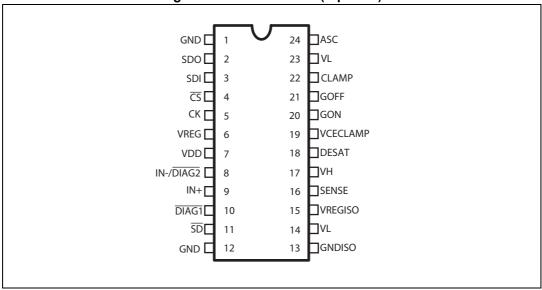

| 2 | Pin   | Pin connection                             |  |  |  |

| 3 | Elec  | trical data11                              |  |  |  |

|   | 3.1   | Absolute maximum ratings                   |  |  |  |

|   | 3.2   | Thermal data                               |  |  |  |

|   | 3.3   | Recommended operating conditions           |  |  |  |

| 4 | Elec  | trical characteristics13                   |  |  |  |

|   | 4.1   | AC operation                               |  |  |  |

|   | 4.2   | DC operation                               |  |  |  |

| 5 | Isola | ation                                      |  |  |  |

| 6 | Logi  | ic supply management                       |  |  |  |

|   | 6.1   | Low voltage section voltage regulator      |  |  |  |

|   | 6.2   | High voltage section voltage regulator     |  |  |  |

|   | 6.3   | Power-up, power-down and "safe state"      |  |  |  |

|   | 6.4   | Standby function                           |  |  |  |

| 7 | Fun   | ctional description                        |  |  |  |

|   | 7.1   | Inputs and outputs                         |  |  |  |

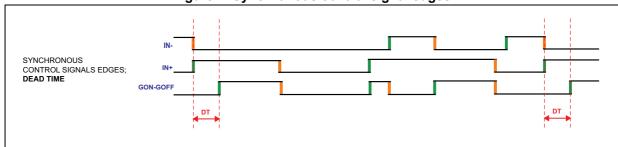

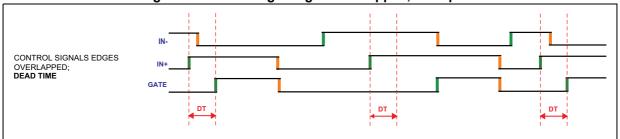

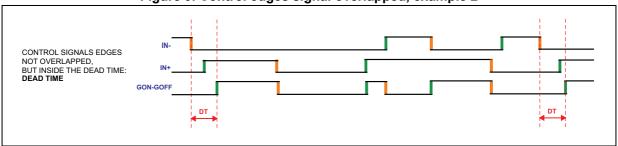

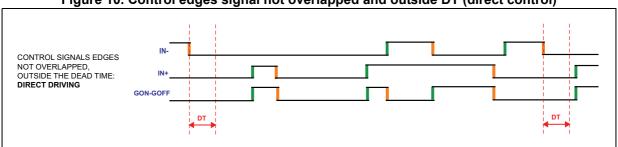

|   | 7.2   | Deadtime and interlocking                  |  |  |  |

|   | 7.3   | Hardware RESET                             |  |  |  |

|   | 7.4   | Power supply UVLO and OVLO                 |  |  |  |

|   | 7.5   | Thermal warning and shutdown protection    |  |  |  |

|   | 7.6   | Desaturation protection                    |  |  |  |

|   | 7.7   | V <sub>CE</sub> active clamping protection |  |  |  |

|   | 7.8   | SENSE overcurrent protection               |  |  |  |

|        | 7.9              | Miller cl                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | amp function                                                                                                                                                                                                                                                                                                                                                                                                                                          | 33                                                                               |

|--------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

|        | 7.10             | 2-level t                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | turn-off function                                                                                                                                                                                                                                                                                                                                                                                                                                     | 33                                                                               |

|        |                  | 7.10.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Always                                                                                                                                                                                                                                                                                                                                                                                                                                                | . 34                                                                             |

|        |                  | 7.10.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Fault                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 34                                                                             |

|        |                  | 7.10.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Never                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 35                                                                             |

|        | 7.11             | Failure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | management                                                                                                                                                                                                                                                                                                                                                                                                                                            | 35                                                                               |

|        | 7.12             | Asynchi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ronous stop command                                                                                                                                                                                                                                                                                                                                                                                                                                   | 36                                                                               |

|        | 7.13             | Watchd                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | og                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 36                                                                               |

|        | 7.14             | Security                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | / check functions                                                                                                                                                                                                                                                                                                                                                                                                                                     | 36                                                                               |

|        |                  | 7.14.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | GON to gate path check                                                                                                                                                                                                                                                                                                                                                                                                                                | . 37                                                                             |

|        |                  | 7.14.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | GOFF to gate path check                                                                                                                                                                                                                                                                                                                                                                                                                               | . 37                                                                             |

|        |                  | 7.14.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | SENSE comparator check                                                                                                                                                                                                                                                                                                                                                                                                                                | . 39                                                                             |

|        |                  | 7.14.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | SENSE resistor check                                                                                                                                                                                                                                                                                                                                                                                                                                  | . 40                                                                             |

|        |                  | 7.14.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | DESAT comparator check                                                                                                                                                                                                                                                                                                                                                                                                                                | . 41                                                                             |

|        | 7.15             | Registe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | r corruption protection                                                                                                                                                                                                                                                                                                                                                                                                                               | 42                                                                               |

|        |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                  |

| 0      | eni i            | storfooo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 12                                                                               |

| 8      |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                  |

| 8      |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                  |

| 8<br>9 | CRC <sub>I</sub> | orotection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 45                                                                               |

|        | CRC <sub>I</sub> | orotection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 45<br><b>47</b>                                                                  |

|        | CRC              | orotection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | g manual                                                                                                                                                                                                                                                                                                                                                                                                                                              | 45<br><b>47</b><br>47                                                            |

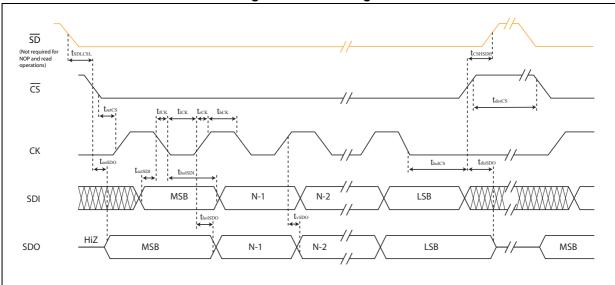

|        | CRC              | orotection<br>rammine<br>SPI con                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | g manual                                                                                                                                                                                                                                                                                                                                                                                                                                              | 45<br><b>47</b><br>47<br>. 47                                                    |

|        | CRC              | rammine<br>SPI con<br>9.1.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | g manual                                                                                                                                                                                                                                                                                                                                                                                                                                              | 45<br>47<br>47<br>. 47                                                           |

|        | CRC              | ramming<br>SPI con<br>9.1.1<br>9.1.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | g manual nmands StartConfig and StopConfig commands WriteReg command                                                                                                                                                                                                                                                                                                                                                                                  | 45<br>47<br>47<br>. 47<br>. 48                                                   |

|        | CRC              | ramming<br>SPI con<br>9.1.1<br>9.1.2<br>9.1.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | manual                                                                                                                                                                                                                                                                                                                                                                                                                                                | 45<br>47<br>47<br>48<br>48<br>48                                                 |

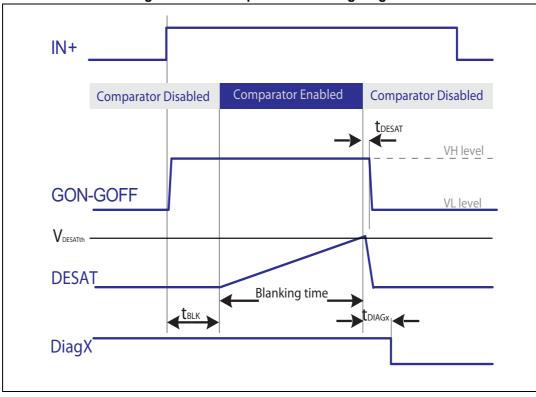

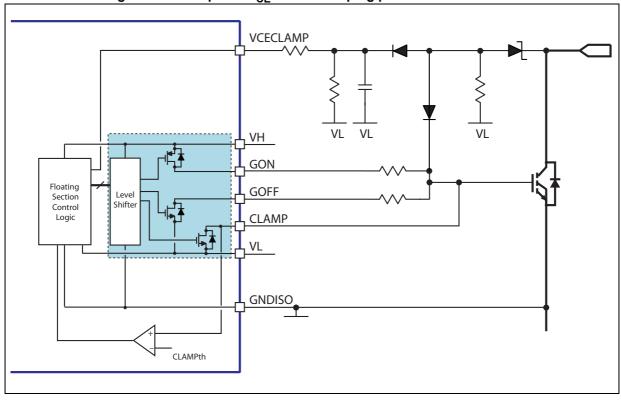

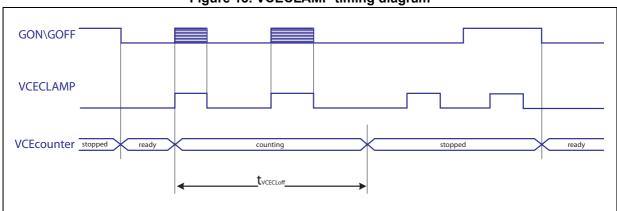

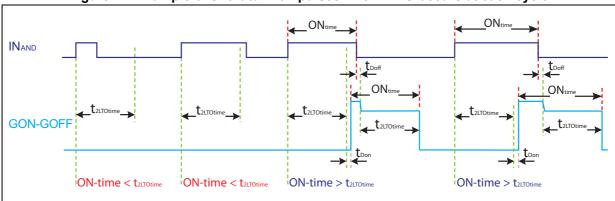

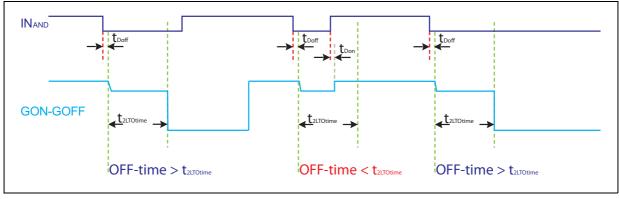

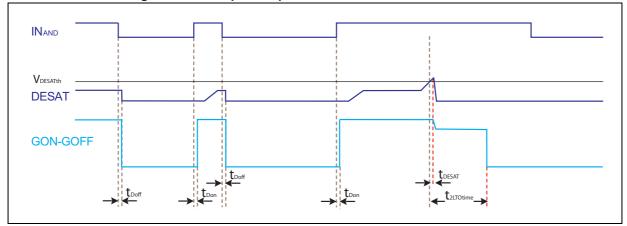

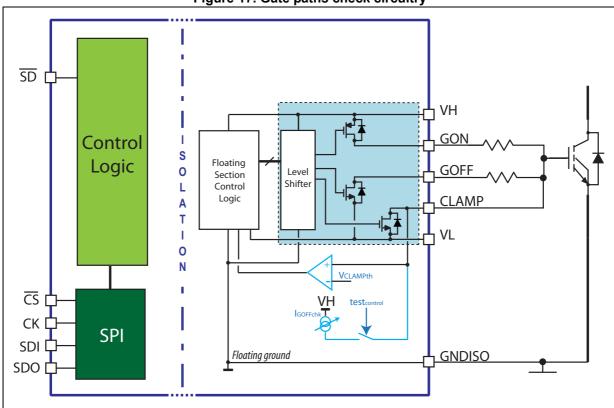

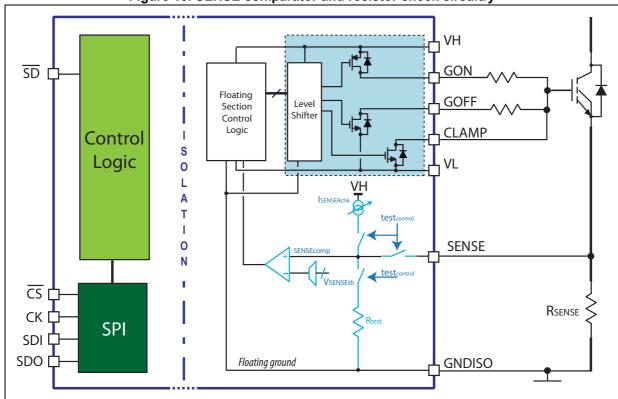

|        | CRC              | SPI con<br>9.1.1<br>9.1.2<br>9.1.3<br>9.1.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | manual                                                                                                                                                                                                                                                                                                                                                                                                                                                | 45<br>47<br>47<br>. 47<br>. 48<br>. 48<br>. 49                                   |