## 54LS283/DM54LS283/DM74LS283 4-Bit Binary Adders with Fast Carry

### General Description

These full adders perform the addition of two 4-bit binary numbers. The sum ( $\Sigma$ ) outputs are provided for each bit and the resultant carry (C4) is obtained from the fourth bit. These adders feature full internal look ahead across all four bits. This provides the system designer with partial look-ahead performance at the economy and reduced package count of a ripple-carry implementation.

The adder logic, including the carry, is implemented in its true form meaning that the end-around carry can be accomplished without the need for logic or level inversion.

### Features

- Full-carry look-ahead across the four bits

- Systems achieve partial look-ahead performance with the economy of ripple carry

- Typical add times

- Two 8-bit words 25 ns

- Two 16-bit words 45 ns

- Typical power dissipation per 4-bit adder 95 mW

- Alternate Military/Aerospace device (54LS283) is available. Contact a National Semiconductor Sales Office/Distributor for specifications.

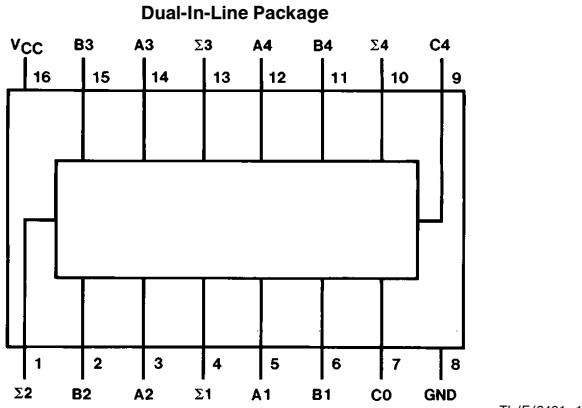

### Connection Diagram

TL/F/6421-1

Order Number 54LS283DMQB, 54LS283FMQB, 54LS283LMQB,

DM54LS283J, DM54LS283W, DM74LS283M or DM74LS283N

See NS Package Number E20A, J16A, M16A, N16E or W16A

## Absolute Maximum Ratings (Note)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

|                                      |                 |

|--------------------------------------|-----------------|

| Supply Voltage                       | 7V              |

| Input Voltage                        | 7V              |

| Operating Free Air Temperature Range |                 |

| DM54LS and 54LS                      | −55°C to +125°C |

| DM74LS                               | 0°C to +70°C    |

| Storage Temperature Range            | −65°C to +150°C |

Note: The "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. The device should not be operated at these limits. The parametric values defined in the "Electrical Characteristics" table are not guaranteed at the absolute maximum ratings. The "Recommended Operating Conditions" table will define the conditions for actual device operation.

## Recommended Operating Conditions

| Symbol   | Parameter                      | DM54LS283 |     |      | DM74LS283 |     |      | Units |

|----------|--------------------------------|-----------|-----|------|-----------|-----|------|-------|

|          |                                | Min       | Nom | Max  | Min       | Nom | Max  |       |

| $V_{CC}$ | Supply Voltage                 | 4.5       | 5   | 5.5  | 4.75      | 5   | 5.25 | V     |

| $V_{IH}$ | High Level Input Voltage       | 2         |     |      | 2         |     |      | V     |

| $V_{IL}$ | Low Level Input Voltage        |           |     | 0.7  |           |     | 0.8  | V     |

| $I_{OH}$ | High Level Output Current      |           |     | −0.4 |           |     | −0.4 | mA    |

| $I_{OL}$ | Low Level Output Current       |           |     | 4    |           |     | 8    | mA    |

| $T_A$    | Free Air Operating Temperature | −55       |     | 125  | 0         |     | 70   | °C    |

## Electrical Characteristics

over recommended operating free air temperature range (unless otherwise noted)

| Symbol    | Parameter                                       | Conditions                                     | Min  | Typ (Note 1) | Max  | Units         |

|-----------|-------------------------------------------------|------------------------------------------------|------|--------------|------|---------------|

| $V_I$     | Input Clamp Voltage                             | $V_{CC} = \text{Min}$ , $I_I = -18 \text{ mA}$ |      |              | −1.5 | V             |

| $V_{OH}$  | High Level Output Voltage                       | $V_{CC} = \text{Min}$ , $I_{OH} = \text{Max}$  | DM54 | 2.5          | 3.4  | V             |

|           |                                                 | $V_{IL} = \text{Max}$ , $V_{IH} = \text{Min}$  | DM74 | 2.7          | 3.4  |               |

| $V_{OL}$  | Low Level Output Voltage                        | $V_{CC} = \text{Min}$ , $I_{OL} = \text{Max}$  | DM54 |              | 0.25 | V             |

|           |                                                 | $V_{IL} = \text{Max}$ , $V_{IH} = \text{Min}$  | DM74 |              | 0.35 |               |

|           | $I_{OL} = 4 \text{ mA}$ , $V_{CC} = \text{Min}$ | DM74                                           |      | 0.25         | 0.4  |               |

| $I_I$     | Input Current @ Max Input Voltage               | $V_{CC} = \text{Max}$                          | A, B |              | 0.2  | mA            |

|           |                                                 | $V_I = 7V$                                     | C0   |              | 0.1  |               |

| $I_{IH}$  | High Level Input Current                        | $V_{CC} = \text{Max}$                          | A, B |              | 40   | $\mu\text{A}$ |

|           |                                                 | $V_I = 2.7V$                                   | C0   |              | 20   |               |

| $I_{IL}$  | Low Level Input Current                         | $V_{CC} = \text{Max}$                          | A, B |              | −0.8 | mA            |

|           |                                                 | $V_I = 0.4V$                                   | C0   |              | −0.4 |               |

| $I_{OS}$  | Short Circuit Output Current                    | $V_{CC} = \text{Max}$<br>(Note 2)              | DM54 | −20          | −100 | mA            |

|           |                                                 |                                                | DM74 | −20          | −100 |               |

| $I_{CC1}$ | Supply Current                                  | $V_{CC} = \text{Max}$ (Note 3)                 |      | 19           | 34   | mA            |

| $I_{CC2}$ | Supply Current                                  | $V_{CC} = \text{Max}$ (Note 4)                 |      | 22           | 39   | mA            |

Note 1: All typicals are at  $V_{CC} = 5V$ ,  $T_A = 25^\circ\text{C}$ .

Note 2: Not more than one output should be shorted at a time, and the duration should not exceed one second.

Note 3:  $I_{CC1}$  is measured with all outputs open, all B inputs low and all other inputs at 4.5V, or all inputs at 4.5V.

Note 4:  $I_{CC2}$  is measured with all outputs open and all inputs grounded.

**Switching Characteristics** at  $V_{CC} = 5V$  and  $T_A = 25^\circ C$  (See Section 1 for Test Waveforms and Output Load)

| Symbol    | Parameter                                          | From (Input)<br>To (Output)      | $R_L = 2\text{ k}\Omega$ |     |                      |     | Units |  |

|-----------|----------------------------------------------------|----------------------------------|--------------------------|-----|----------------------|-----|-------|--|

|           |                                                    |                                  | $C_L = 15\text{ pF}$     |     | $C_L = 50\text{ pF}$ |     |       |  |

|           |                                                    |                                  | Min                      | Max | Min                  | Max |       |  |

| $t_{PLH}$ | Propagation Delay Time<br>Low to High Level Output | $C_0$ to<br>$\Sigma_1, \Sigma_2$ |                          | 24  |                      | 28  | ns    |  |

| $t_{PHL}$ | Propagation Delay Time<br>High to Low Level Output | $C_0$ to<br>$\Sigma_1, \Sigma_2$ |                          | 24  |                      | 30  | ns    |  |

| $t_{PLH}$ | Propagation Delay Time<br>Low to High Level Output | $C_0$ to<br>$\Sigma_3$           |                          | 24  |                      | 28  | ns    |  |

| $t_{PHL}$ | Propagation Delay Time<br>High to Low Level Output | $C_0$ to<br>$\Sigma_3$           |                          | 24  |                      | 30  | ns    |  |

| $t_{PLH}$ | Propagation Delay Time<br>Low to High Level Output | $C_0$ to<br>$\Sigma_4$           |                          | 24  |                      | 28  | ns    |  |

| $t_{PHL}$ | Propagation Delay Time<br>High to Low Level Output | $C_0$ to<br>$\Sigma_4$           |                          | 24  |                      | 30  | ns    |  |

| $t_{PLH}$ | Propagation Delay Time<br>Low to High Level Output | $A_i$ or $B_i$<br>to $\Sigma_i$  |                          | 24  |                      | 28  | ns    |  |

| $t_{PHL}$ | Propagation Delay Time<br>High to Low Level Output | $A_i$ or $B_i$<br>to $\Sigma_i$  |                          | 24  |                      | 30  | ns    |  |

| $t_{PLH}$ | Propagation Delay Time<br>Low to High Level Output | $C_0$ to<br>$C_4$                |                          | 17  |                      | 24  | ns    |  |

| $t_{PHL}$ | Propagation Delay Time<br>High to Low Level Output | $C_0$ to<br>$C_4$                |                          | 17  |                      | 25  | ns    |  |

| $t_{PLH}$ | Propagation Delay Time<br>Low to High Level Output | $A_i$ or $B_i$<br>to $C_4$       |                          | 17  |                      | 24  | ns    |  |

| $t_{PHL}$ | Propagation Delay Time<br>High to Low Level Output | $A_i$ or $B_i$<br>to $C_4$       |                          | 17  |                      | 26  | ns    |  |

**Function Table**

| Input          |          |                |          |                          | Outputs                  |                |                          |                          |                |                          |                          |          |  |

|----------------|----------|----------------|----------|--------------------------|--------------------------|----------------|--------------------------|--------------------------|----------------|--------------------------|--------------------------|----------|--|

|                |          |                |          |                          | When $C_0 = L$           |                |                          |                          | When $C_0 = H$ |                          |                          |          |  |

| When $C_2 = L$ |          | When $C_2 = H$ |          | When $C_2 = L$           |                          | When $C_2 = H$ |                          |                          |                |                          |                          |          |  |

| A1<br>A3       | B1<br>B3 | A2<br>A4       | B2<br>B4 | $\Sigma_1$<br>$\Sigma_3$ | $\Sigma_2$<br>$\Sigma_4$ | C2<br>C4       | $\Sigma_1$<br>$\Sigma_3$ | $\Sigma_2$<br>$\Sigma_4$ | C2<br>C4       | $\Sigma_1$<br>$\Sigma_3$ | $\Sigma_2$<br>$\Sigma_4$ | C2<br>C4 |  |

| L              | L        | L              | L        | L                        | L                        | L              | H                        | L                        | L              | L                        | L                        | L        |  |

| H              | L        | L              | L        | H                        | L                        | L              | L                        | L                        | L              | H                        | H                        | L        |  |

| L              | H        | L              | L        | H                        | L                        | L              | L                        | L                        | L              | H                        | H                        | L        |  |

| H              | H        | L              | L        | L                        | H                        | L              | H                        | L                        | L              | H                        | H                        | L        |  |

| L              | L        | H              | L        | L                        | H                        | L              | H                        | L                        | L              | H                        | H                        | L        |  |

| H              | L        | H              | L        | H                        | H                        | L              | L                        | H                        | L              | L                        | H                        | H        |  |

| L              | H        | H              | L        | H                        | L                        | H              | L                        | H                        | L              | L                        | H                        | H        |  |

| H              | H        | H              | L        | L                        | H                        | L              | H                        | L                        | L              | L                        | H                        | H        |  |

| L              | L        | L              | H        | H                        | L                        | H              | L                        | H                        | L              | H                        | L                        | L        |  |

| H              | L        | H              | H        | H                        | H                        | L              | L                        | H                        | L              | L                        | H                        | H        |  |

| L              | H        | H              | H        | H                        | L                        | H              | L                        | H                        | L              | H                        | H                        | H        |  |

| H              | H        | H              | H        | L                        | H                        | L              | H                        | L                        | H              | H                        | H                        | H        |  |

H = High Level, L = Low Level

**Note:** Input conditions at A1, B1, A2, B2, and C0 are used to determine outputs  $\Sigma_1$  and  $\Sigma_2$  and the value of the internal carry C2. The values at C2, A3, B3, A4, and B4 are then used to determine outputs  $\Sigma_3$ ,  $\Sigma_4$ , and C4.

TL/F/6421-3

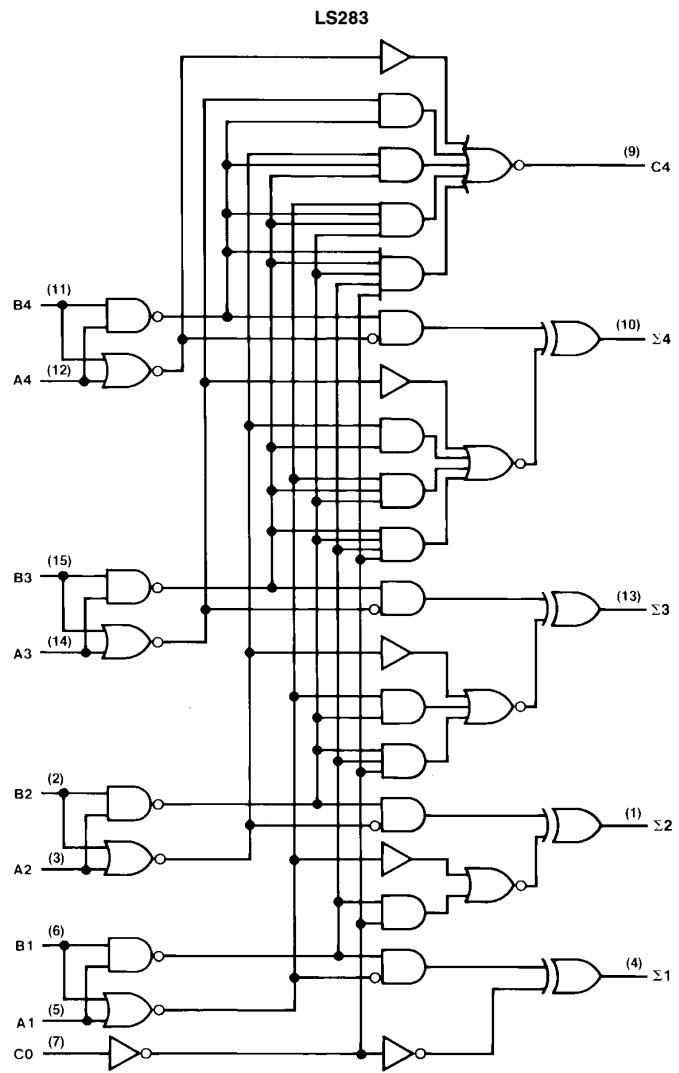

## Logic Diagram

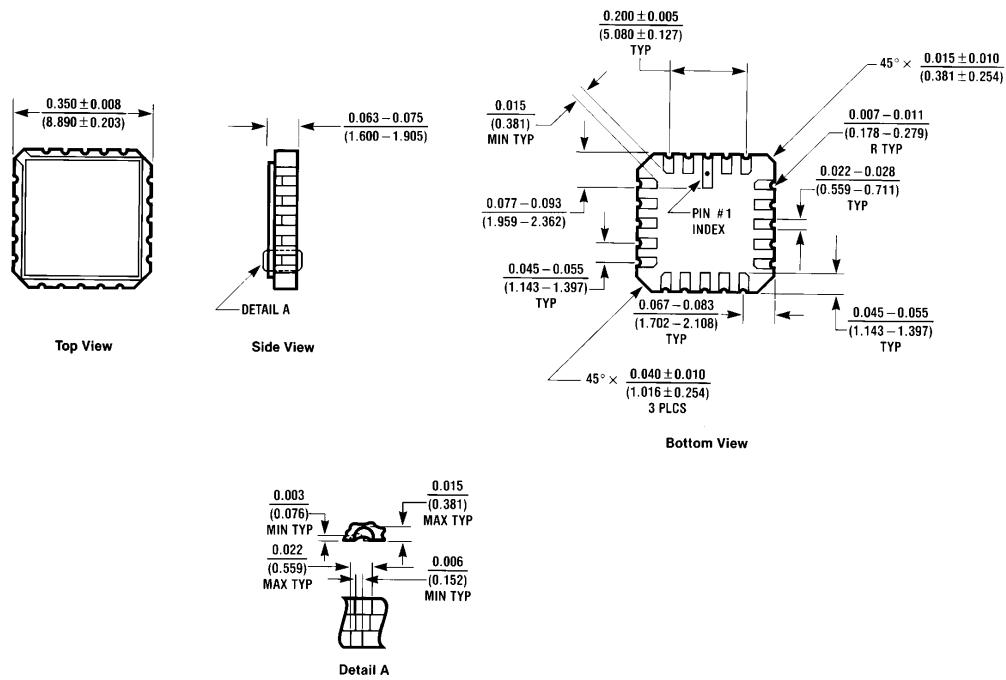

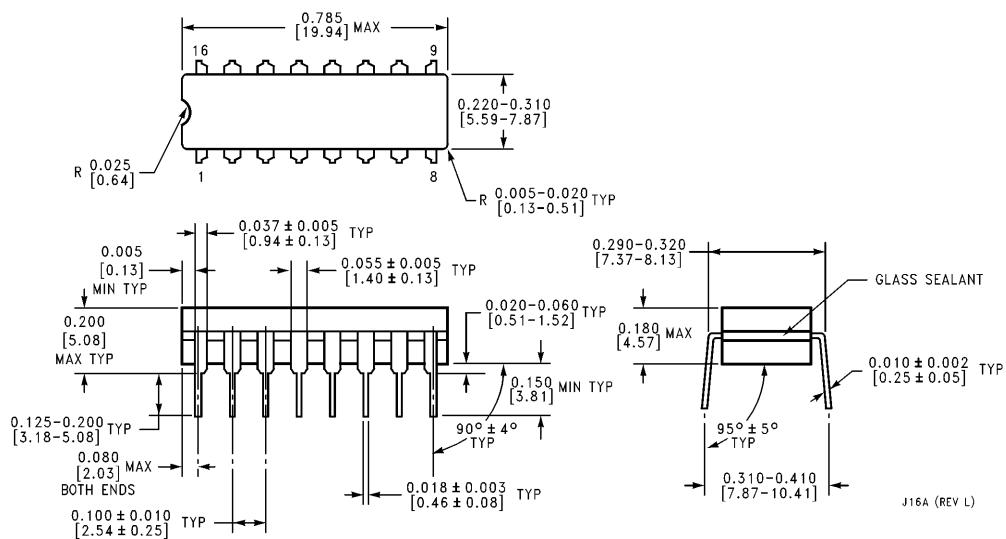

## Physical Dimensions

**Ceramic Leadless Chip Carrier Package (E)

Order Number 54LS283LMQB

NS Package Number E20A**

E20A (REV D)

**16-Lead Ceramic Dual-In-Line Package (J)

Order Number 54LS283DMQB or DM54LS283J

NS Package Number J16A**

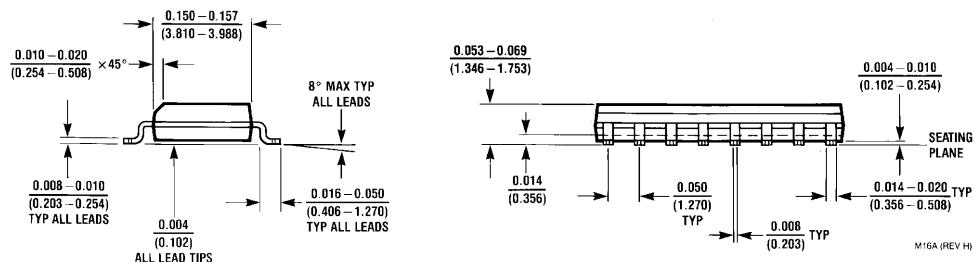

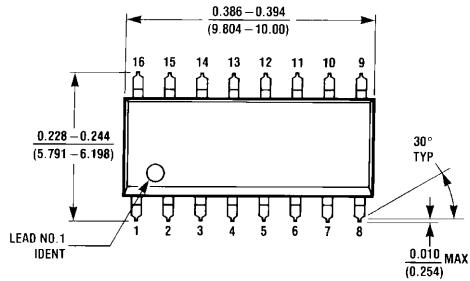

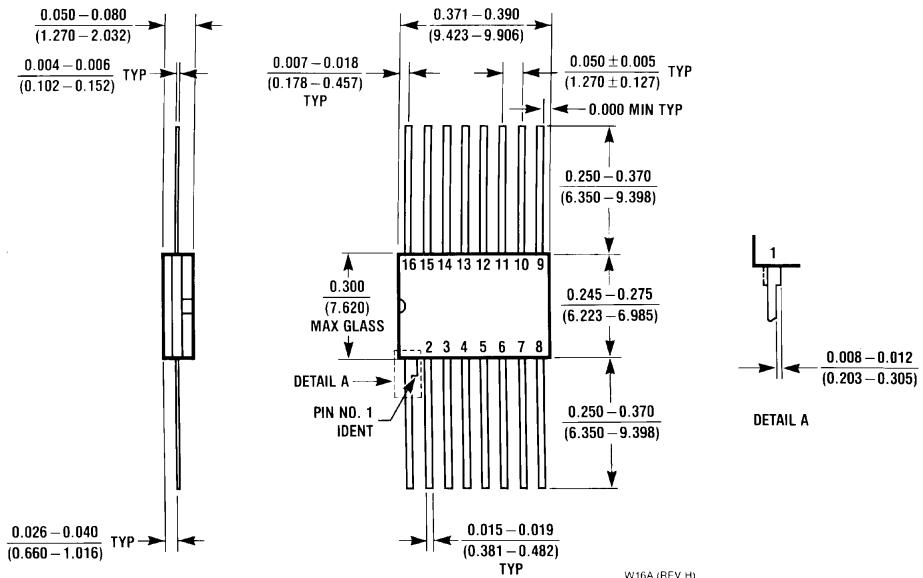

## **Physical Dimensions** inches (millimeters) (Continued)

**16-Lead Small Outline Molded Package (M)

Order Number DM74LS283M

NS Package Number M16A**

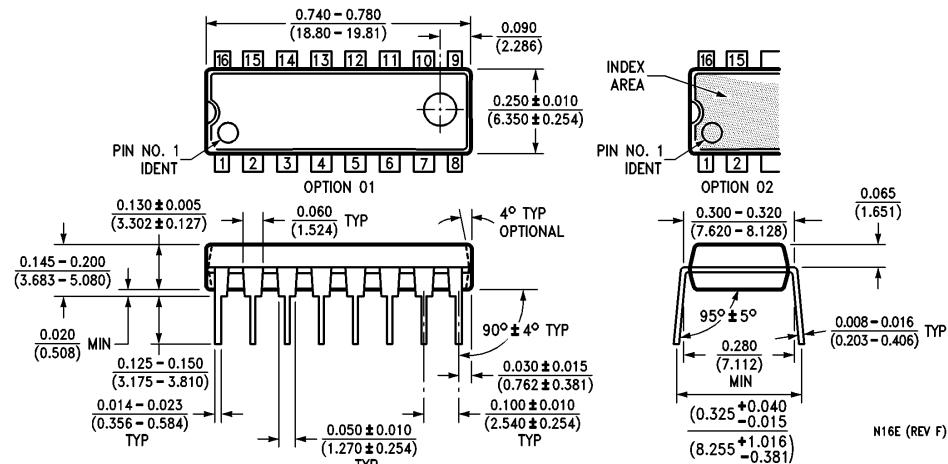

16-Lead Molded Dual-In-Line Package (N)

Order Number DM74LS283N

NS Package Number N16E

**Physical Dimensions** inches (millimeters) (Continued)

16-Lead Ceramic Flat Package (W)

Order Number 54LS283FMQB or DM54LS283W

NS Package Number W16A

**LIFE SUPPORT POLICY**

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

National Semiconductor

Corporation

1111 West Bardin Road

Arlington, TX 76017

Tel: (800) 272-9959

Fax: (800) 737-7018

National Semiconductor

Europe

Fax: (+49) 0-180-530 85 86

Email: cnjwge@tevm2.nsc.com

Deutsch Tel: (+49) 0-180-530 85 85

English Tel: (+49) 0-180-532 78 32

Français Tel: (+49) 0-180-532 93 58

Italiano Tel: (+49) 0-180-534 16 80

National Semiconductor

Hong Kong Ltd.

13th Floor, Straight Block,

Ocean Centre, 5 Canton Rd.

Tsimshatsui, Kowloon

Hong Kong

Tel: (852) 2737-1600

Fax: (852) 2736-9960

National Semiconductor

Japan Ltd.

Tel: 81-043-299-2309

Fax: 81-043-299-2406