# HIGH-SPEED DIFFERENTIAL 8-BIT REGISTERED TRANSCEIVER

#### **FEATURES**

- 8-Bit Bidirectional Data Storage Register With Full Parallel Access

- Parallel Transfer Rates

- (1) Parallel data transfer through all channels simultaneously as defined by TIA/EIA-644 with t<sub>r</sub> of t<sub>f</sub> less than 30% of the unit interval.

- Buffer Mode: Up to 475 Megatransfers

- Flip-Flop Mode: Up to 300 Megatransfers

- Latch Mode: Up to 300 Megatransfers

- Operates With a Single 3.3-V Supply

- Low-Voltage Differential Signaling With Typical Output Voltage of 350 mV Across a 50- $\Omega$  Load

- Bus and Logic Loopback Capability

- Very Low Radiation Emission

- Low Skew Performance

- Pulse Skew Less Than 100 ps

- Output Skew Less Than 320 ps

- Part-to-Part Skew Less Than 1 ns

- Open-Circuit Differential Receiver Fail Safe Assures a Low-Level Output

- Reset at Power Up

- 12-kV Bus-Pin ESD Protection

- Bus Pins Remain High-Impedance When Disabled or With V<sub>CC</sub> Below 1.5 V for Power-Up/Down Glitch-Free Performance and Hot Plugging

- 5-V Tolerant LVCMOS Inputs

## **APPLICATIONS**

- Telecom Switching

- Printers and Copiers

- Audio Mixing Consoles

- Automated Test Equipment

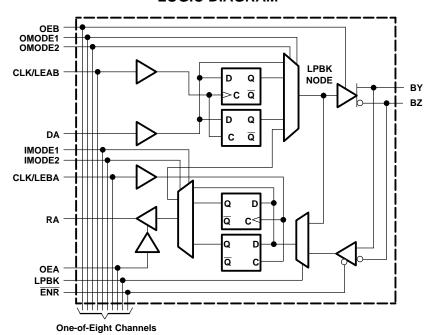

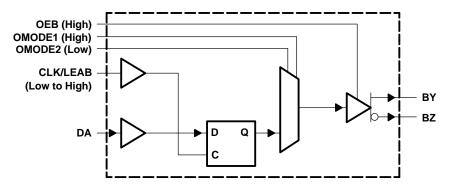

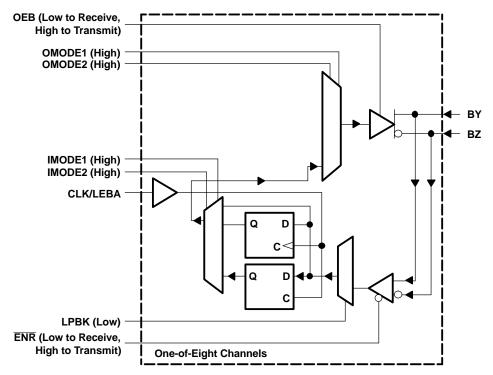

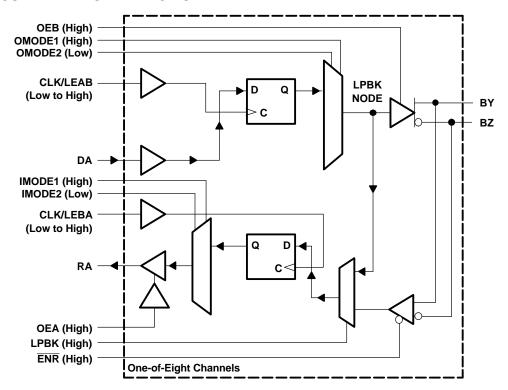

#### LOGIC DIAGRAM

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

## **DESCRIPTION**

The SN65LVDM320 is an 8-bit data storage register with differential line drivers and receivers that are electrically compatible with ANSI EIA/TIA-644 for multipoint architectures with standard-compliant parallel transfer rates of 475 Mbps. The SN65LVDM320 includes transmitter and receiver data registers that remain active regardless of the state of their associated outputs.

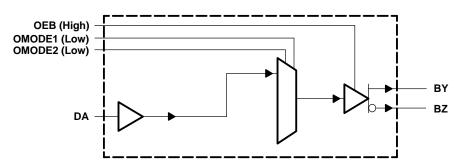

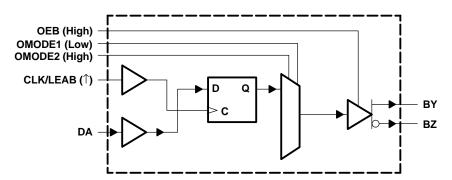

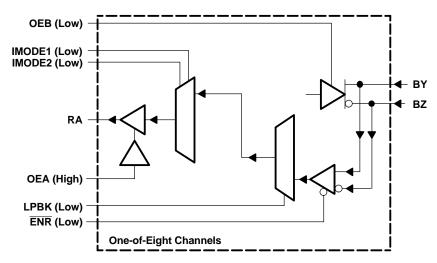

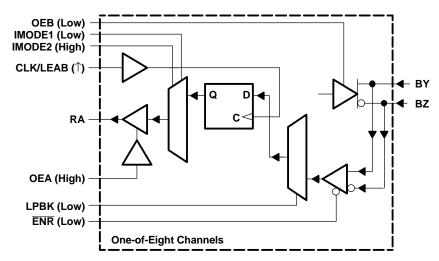

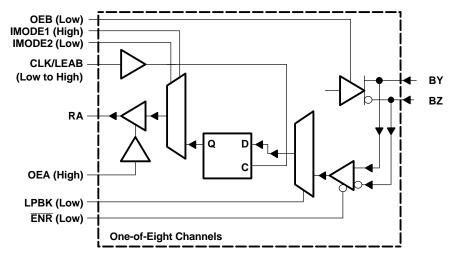

The logic element for data flow in each direction is configured by mode-control inputs. IMODE1 and IMODE2 control data flow in the B-to-A (bus side to digital side) direction when configured as a buffer, a D-type flip-flop, or a D-type latch. OMODE1 and OMODE2 control data flow in each of the operating modes for the A-to-B (digital side to bus side) direction. When configured in buffer mode, input data appears at the output port. In the flip-flop mode, data is stored on the rising edge of the appropriate clock input, CLKAB/LEAB or CLKBA/LEBA. In the latch mode, this clock pin also serves as an active-high transparent latch enable.

Data flow is further controlled by the A-side loopback (LPBK) input. When LPBK is high, DA input data is looped back to the RA output. B-side bus data is looped back to the bus in latch mode by means of the IMODE and OMODE logic states.

The A-side output enable/disable control is provided by OEA. When OEA is low or  $V_{CC}$  is less than 2 V, the A side is in the high-impedance state. When OEA is high, the A side is active (high or low logic levels). The B-side output enable/disable control is provided by OEB. When OEB is low or  $V_{CC}$  is less than 2 V, the B side is in the high impedance state. When OEB is high, the B side is active (high or low logic levels).

The A-to-B and B-to-A logic elements are active regardless of the state of their associated outputs. New data can be entered (in latch and flip-flop modes) or previously stored data can be retained while the associated outputs are in the high-impedance or inactive states. The SN65LVDM320 also includes internally isolated analog (B-side) and digital (A-side) grounds for enhanced operation.

The SN65LVDM320 is characterized for operation from -40°C to 85°C.

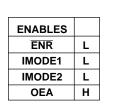

**INPUTS** MODE **CLK/LEAB** CLK/LEBA ENR OMODE1 OMODE2 IMODE1 IMODE2 OEA OEB **LPBK** Χ Χ Х Χ Χ Χ Χ Isolation A-to-B buffer mode L Χ Χ Χ Н Χ L Χ Χ Χ (see Figure 1) A-to-B flip-flop mode Χ Χ Н Χ L Н Χ Χ Χ (see Figure 2) H(B follows A) A-to-B latch mode Χ Χ Н Χ Н L Χ Χ Χ (see Figure 3) L(B latched) B-to-A buffer mode Х Χ Н L L Χ Χ ı L (see Figure 4) B-to-A flip-flop mode(see 1 Χ Н L L Χ Χ 1 Н 1 Figure 5) H(A follows B) B-to-A latch mode Χ Н L L Χ Χ Н L L (see Figure 6) L(A latched) Bus loopback latch mode(see Χ Х L L Н Н Н Н Н L Figure 7) DA to RA loopback mode (see Χ Χ L Н Χ Χ Χ Χ Н Figures 8 through 10)

Table 1. Mode Functions (1)

<sup>(1)</sup>  $H = high level, L = low level, X = don't care, \uparrow = low-to-high$

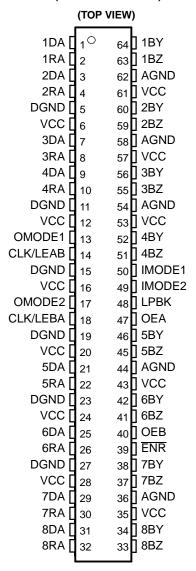

# **PIN DESCRIPTIONS**

| PII                  | N                                                                               | Decembria                                                                                        |

|----------------------|---------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|

| NAME                 | NO.                                                                             | Description                                                                                      |

| AGND                 | 36, 44, 54, 58, 62                                                              | Analog (B-side) ground                                                                           |

| 1BY-8BY &<br>1BZ-8BZ | 64 & 63, 60 & 59,<br>56 & 55, 52 & 51,<br>46 & 45, 42 & 41,<br>38 & 37, 34 & 33 | Differential I/O pair                                                                            |

| CLK/LEBA             | 18                                                                              | B-side to A-side clock input or latch enable                                                     |

| CLK/LEAB             | 14                                                                              | A-side to B-side clock input or latch enable                                                     |

| 1DA-8DA              | 1, 3, 7, 9, 21, 25,<br>29, 31                                                   | Single-ended input                                                                               |

| DGND                 | 5, 11, 15, 19, 23,<br>27                                                        | Digital (A-side) ground                                                                          |

| ENR                  | 39                                                                              | Receiver differential data enable                                                                |

| IMODE1IMODE2         | 50,49                                                                           | B-side to A-side buffer, flip-flop, or latch mode control and bus loopback control (see Table 2) |

| LPBK                 | 48                                                                              | A-side loopback enable                                                                           |

| OEA                  | 47                                                                              | A-side output enable                                                                             |

| OEB                  | 40                                                                              | B-side output enable                                                                             |

| OMODE1,OMODE2        | 13,17                                                                           | A-side to B-side buffer, flip-flop, or latch mode control and bus loopback control (see Table 3) |

| RA                   | 2, 4, 8, 10, 22, 26,<br>30, 32                                                  | Single-ended output                                                                              |

| VCC                  | 6, 12, 16, 20, 24,<br>28, 35, 43, 53, 57,<br>61                                 | Supply voltage                                                                                   |

## **PIN DESCRIPTIONS**

SN65LVDM320DGG (Marked as LVDM320)

**Table 2. IMODE Logic**

| IMODE1 | IMODE2     | MODE FUNCTION<br>(B SIDE TO A SIDE) |

|--------|------------|-------------------------------------|

| 0      | 0 0 Buffer |                                     |

| 0      | 1          | Flip-Flop                           |

| 1      | 0          | Latch                               |

| 1      | 1          | Bus loopback <sup>(1)</sup>         |

All IMODE and OMODE pins must be high for the differential bus loopback latch mode.

Table 3. OMODE Logic

| IMODE1 | IMODE2 | MODE FUNCTION (A SIDE TO B SIDE) |

|--------|--------|----------------------------------|

| 0      | 0      | Buffer                           |

| 0      | 1      | Flip-Flop                        |

| 1      | 0      | Latch                            |

| 1      | 1      | Bus loopback <sup>(1)</sup>      |

All IMODE and OMODE pins must be high for the differential bus loopback latch mode.

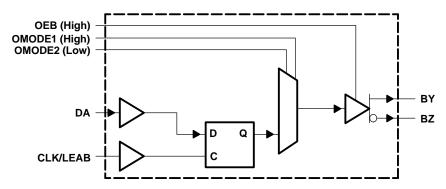

# **MODE FUNCTION DIAGRAMS**

Figure 1. A-to-B Buffer Mode

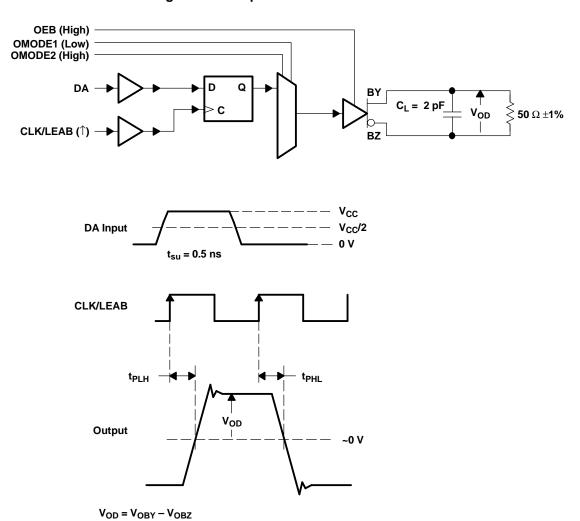

Figure 2. A-to-B Flip-Flop Mode

Figure 3. A-to-B Latch Mode

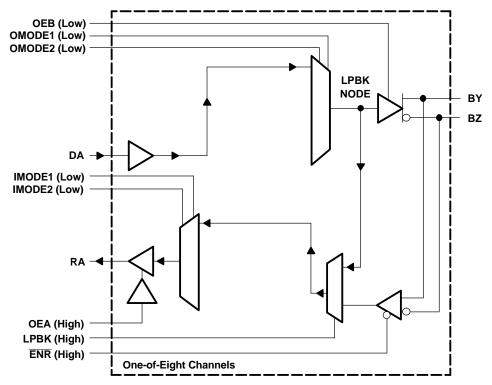

# **MODE FUNCTION DIAGRAMS (continued)**

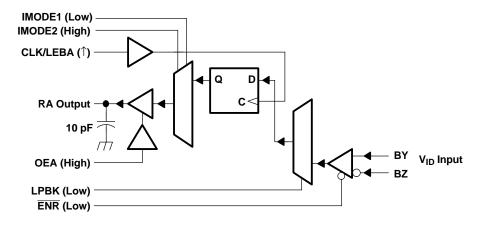

Figure 4. B-to-A Buffer Mode

Figure 5. B-to-A Flip-Flop Mode

Figure 6. B-to-A Latch Mode

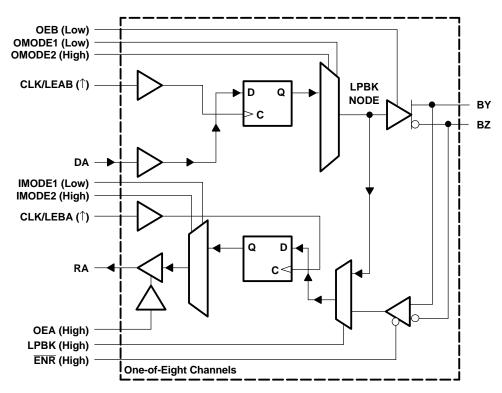

# **MODE FUNCTION DIAGRAMS (continued)**

Figure 7. Bus Loopback Latch Mode

Figure 8. DA to RA Buffer Mode

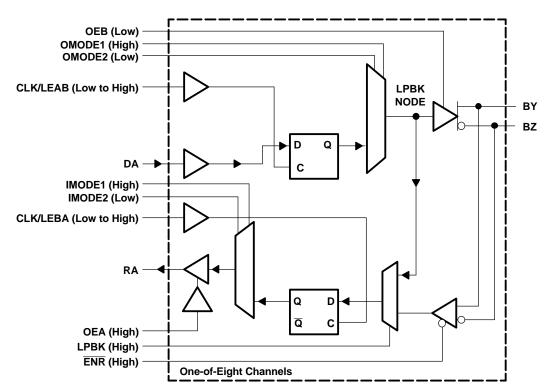

# **MODE FUNCTION DIAGRAMS (continued)**

Figure 9. DA to RA Flip-Flop Mode

Figure 10. DA to RA Latch Mode

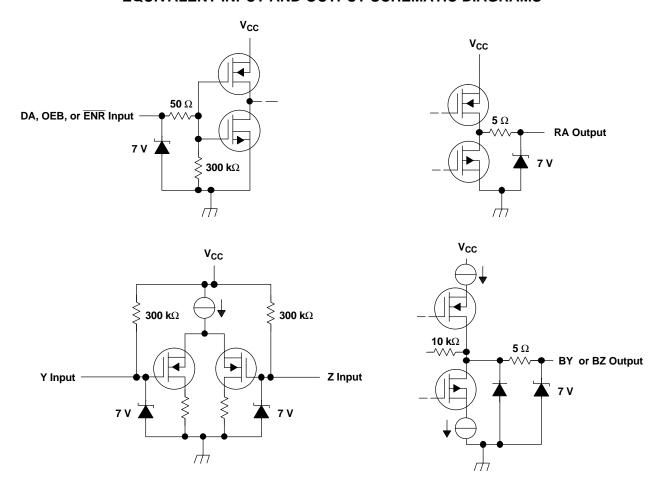

# **EQUIVALENT INPUT AND OUTPUT SCHEMATIC DIAGRAMS**

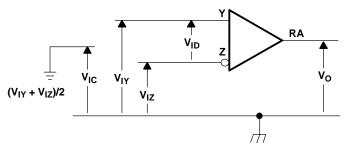

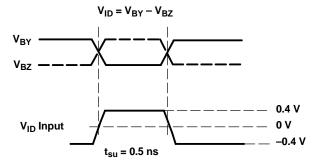

**Table 4. LVDM Receiver Function Table**

| BUS INPUTS                         | OUTPUT <sup>(1)</sup> |

|------------------------------------|-----------------------|

| $V_{ID} = V_Y - V_Z$               |                       |

| V <sub>ID</sub> ≥ 100 mV           | Н                     |

| -100 mV < V <sub>ID</sub> < 100 mV | ?                     |

| V <sub>ID</sub> ≤ −100 mV          | L                     |

| Open                               | L                     |

(1) H = high-level, L = low-level, ? = indeterminate

## **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range (unless otherwise noted)(1)

|                                                              |                   | UNIT                           |

|--------------------------------------------------------------|-------------------|--------------------------------|

| Supply voltage range, V <sub>CC</sub>                        | (2)               | –0.5 V to 4 V                  |

| Voltage range (TTL pins)                                     |                   | -0.5 V to 6 V                  |

| Voltage range BY and BZ                                      |                   | -0.5 V to 4 V                  |

| Electrostatic discharge                                      | Y, Z, and GND (3) | Class 3, A: 12 kV, B: 600 V    |

|                                                              | All pins          | Class 3, A: 7 kV, B: 500 V     |

| Continuous power dissipati                                   | on                | (see Dissipation Rating Table) |

| Storage temperature range                                    |                   | -65°C to 150°C                 |

| Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds |                   | 260°C                          |

<sup>(1)</sup> Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### **DISSIPATION RATING TABLE**

| PACKAGE            | $ \textbf{PACKAGE} \hspace{1cm} \textbf{T_A} \leq \textbf{25}^{\circ}\textbf{C} $ |            | T <sub>A</sub> = 70°C<br>POWER RATING | T <sub>A</sub> = 85°C<br>POWER RATING |

|--------------------|-----------------------------------------------------------------------------------|------------|---------------------------------------|---------------------------------------|

| DGG <sup>(2)</sup> | 2094 mW                                                                           | 16.7 mW/°C | 1340 mW                               | 1089 mW                               |

| DGG <sup>(3)</sup> | 3765 mW                                                                           | 30.1 mW/°C | 2410 mW                               | 1958 mW                               |

<sup>(1)</sup> This is the inverse of the junction-to-ambient thermal resistance when board-mounted and with no air flow.

#### RECOMMENDED OPERATING CONDITIONS

|                 |                                         | MIN                  | NOM | MAX                                      | UNIT |

|-----------------|-----------------------------------------|----------------------|-----|------------------------------------------|------|

| V <sub>CC</sub> | Supply voltage                          | 3                    | 3.3 | 3.6                                      | V    |

| V <sub>IH</sub> | High-level input voltage                | 2                    |     |                                          | V    |

| V <sub>IL</sub> | Low-level input voltage,                |                      |     | 0.8                                      | V    |

| $ V_{ID} $      | Magnitude of differential input voltage | 0.1                  |     | 0.6                                      | V    |

| $V_{IC}$        | Common-mode input voltage               | $\frac{ V_{ID} }{2}$ |     | $2.4 - \frac{ V_{ D} }{2}$ $V_{CC}$ -0.8 | ٧    |

| T <sub>A</sub>  | Operating free-air temperature          | -40                  |     | 85                                       | °C   |

# **SUPPLY CURRENT**

|     | PARAMETER          | TEST CONDITIONS                                                                                          | MIN | NOM | MAX | UNIT |

|-----|--------------------|----------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| Icc |                    | Driver enabled, receiver enabled, $R_L = 50 \Omega$ (DA, OEA, OEB to $V_{CC}$ , $\overline{ENR}$ to GND) |     | 75  | 130 | mA   |

|     | Complex government | Driver disabled, receiver disabled (DA, OEA, OEB to GND, ENR to V <sub>CC</sub> )                        |     | 1   | 3   | mA   |

|     | Supply current     | Driver enabled, receiver disabled, $R_L = 50 \Omega$ (DA, OEB, ENR to $V_{CC}$ , OEA to GND)             |     | 60  | 100 | mA   |

|     |                    | Driver disabled, receiver enabled (DA, OEB, ENR to GND, OEA to V <sub>CC</sub> )                         |     | 20  | 40  | mA   |

<sup>(2)</sup> All voltage values, except differential I/O bus voltages, are with respect to network ground terminal.

<sup>(3)</sup> Tested in accordance with MIL-STD-883E Method 3015.7.

<sup>2)</sup> Tested in accordance with the Low-K thermal metric definitions of EIA/JESD51-3.

<sup>(3)</sup> Tested in accordance with the High-K thermal metric definitions of EIA/JESD51-7.

# **ELECTRICAL CHARACTERISTICS**

over recommended operating conditions (unless otherwise noted)

|                     | PARAMETER                                                                     | TEST CONDITIONS                                                              | MIN                | TYP <sup>(1)</sup> | MAX   | UNIT |

|---------------------|-------------------------------------------------------------------------------|------------------------------------------------------------------------------|--------------------|--------------------|-------|------|

| V <sub>OD</sub>     | Differential output voltage magnitude                                         | $R_L = 50 \Omega$ ,                                                          | 247                | 330                | 454   |      |

| $\Delta  V_{OD} $   | Change in differential output voltage magnitude between logic states          | See Figure 11 and Figure 12                                                  | -50 <sup>(2)</sup> |                    | 50    | mV   |

| V <sub>OC(SS)</sub> | Steady-state common-mode B-port output voltage                                |                                                                              | 1.125              |                    | 1.375 | V    |

| $\Delta V_{OC(SS)}$ | Change in steady-state common-mode B-port output voltage between logic states | See Figure 13                                                                | -50                |                    | 50    | mV   |

| V <sub>OC(PP)</sub> | Peak-to-peak common-mode B-port output voltage                                |                                                                              |                    | 50                 | 150   |      |

| I <sub>OZ</sub>     | RA-port high-impedance output current                                         | V <sub>O</sub> = 0 V or 3.6 V                                                | -10                |                    | 10    | μΑ   |

| I <sub>IH</sub>     | DA port high-level input current                                              | V <sub>IH</sub> = 2 V                                                        |                    |                    | 20    | μΑ   |

| I <sub>IL</sub>     | DA port low-level input current                                               | V <sub>IL</sub> = 0.8 V                                                      |                    |                    | 10    | μΑ   |

|                     | Differential about aircrit autout auront                                      | $V_{OY}$ or $V_{OZ} = 0$                                                     | -10                |                    | 10    | mA   |

| I <sub>OS</sub>     | Differential short-circuit output current                                     | V <sub>OD</sub> = 0                                                          | -10                |                    | 10    | mA   |

| I <sub>O(OFF)</sub> | Power-off differential output current                                         | V <sub>OD</sub> = 2.4 V, V <sub>CC</sub> = 1.5 V                             | -10                |                    | 10    | μΑ   |

| V <sub>IT+</sub>    | Positive-going differential input voltage threshold                           | Con Figure 46 and Table F                                                    |                    |                    | 100   | mV   |

| V <sub>IT-</sub>    | Negative-going differential input voltage threshold                           | See Figure 16 and Table 5                                                    | -100               |                    |       | mv   |

| V <sub>OH</sub>     | High-level RA port output voltage                                             | $I_{OH} = -8 \text{ mA}$                                                     | 2.4                |                    |       | V    |

| V <sub>OL</sub>     | Low-level RA port output voltage                                              | I <sub>OL</sub> = 8 mA                                                       |                    |                    | 0.4   | V    |

|                     | land comet (V or 7 incuts)                                                    | V <sub>I</sub> = 0 V                                                         | -35                |                    |       | μΑ   |

| l <sub>l</sub>      | Input current (Y or Z inputs)                                                 | V <sub>I</sub> = 2.4 V                                                       | -10                |                    |       | μΑ   |

| I <sub>ID</sub>     | Differential input current M I <sub>IY</sub> - I <sub>IZ</sub> M              | $V_{IY} = 0$ and $V_{IZ} = 100$ mV,<br>$V_{IY} = 2.4$ V and $V_{IZ} = 2.3$ V | -10                |                    | 10    | μΑ   |

| I <sub>I(OFF)</sub> | Power-off input current (Y or Z inputs)                                       | V <sub>CC</sub> 0 V, V <sub>I</sub> = 2.4 V                                  | -20                |                    | 20    | μA   |

| C <sub>(INA)</sub>  | DA port Input capacitance                                                     | $V_1 = 0.4 \sin (4E6\pi t) + 0.5 V$                                          |                    | 5                  |       | pF   |

| C <sub>(INB)</sub>  | B-port Input capacitance                                                      | $V_1 = 0.4 \sin (4E6\pi t) + 0.5 V$                                          |                    | 6                  |       | pF   |

| V <sub>O(0PX)</sub> | B-port crosstalk output voltage (zero-to-peak)                                | See Figure 20                                                                |                    | 0.1                |       | mV   |

# **DEVICE SWITCHING CHARACTERISTICS**

over recommended operating conditions (unless otherwise noted)

|                  | PARAMETER                                        | FROM<br>(INPUT)                | TO<br>(OUTPUT) | MIN | TYP | MAX  | UNIT |

|------------------|--------------------------------------------------|--------------------------------|----------------|-----|-----|------|------|

| t <sub>PLH</sub> | Propagation delay time, low-to-high-level output | DA (buffer mode), See          | BY, BZ         | 1.4 | 3.3 | 5.2  | ns   |

| t <sub>PHL</sub> | Propagation delay time, high-to-low-level output | Figure 1 and Figure 14         | DI, DZ         | 1.4 | 3.3 | 5.3  | 115  |

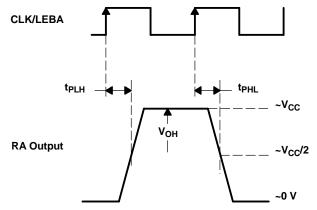

| t <sub>PLH</sub> | Propagation delay time, low-to-high-level output | BY, BZ (buffer mode),          |                | 2.5 | 4.3 | 6.2  |      |

| t <sub>PHL</sub> | Propagation delay time, high-to-low-level output | See See Figure 4 and Figure 17 | RA             | 2.5 | 4.3 | 6.5  | ns   |

| t <sub>PLH</sub> | Propagation delay time, low-to-high-level output | DA (latch mode), See           | DV D7          | 3   | 5.5 | 8.5  | 5    |

| t <sub>PHL</sub> | Propagation delay time, high-to-low-level output | Figure 3 and Figure 14  BY, BZ |                | 3   | 5.5 | 8.7  | ns   |

| t <sub>PLH</sub> | Propagation delay time, low-to-high-level output | BY, BZ (latch mode), See       | RA             | 4   | 6.5 | 9.3  |      |

| t <sub>PHL</sub> | Propagation delay time, high-to-low-level output | Figure 6                       | KA             | 4   | 6.5 | 9.8  | ns   |

| t <sub>PLH</sub> | Propagation delay time, low-to-high-level output | CLKAB, See Figure 2            | DV D7          | 3.5 | 6.5 | 9.5  | 20   |

| t <sub>PHL</sub> | Propagation delay time, high-to-low-level output | and Figure 22                  |                | 3.5 | 6.5 | 9.5  | ns   |

| t <sub>PLH</sub> | Propagation delay time, low-to-high-level output | CLKBA, See Figure 5            | RA             | 3.8 | 6.5 | 10.5 |      |

| t <sub>PHL</sub> | Propagation delay time, high-to-low-level output | and Figure 23                  | KA             | 3.8 | 6.5 | 10.5 | ns   |

| t <sub>PLH</sub> | Propagation delay time, low-to-high-level output | DA, See Figure 8 and           | RA             | 1.8 | 3.2 | 7    | no   |

| t <sub>PHL</sub> | Propagation delay time, high-to-low-level output | Figure 19                      | KA             | 1.8 | 3.2 | 7    | ns   |

All typical values are at 25°C and with a 3.3-V supply voltage. The algebraic convention, in which the least positive (most negative) limit is designated as minimum is used in this data sheet.

# **DEVICE SWITCHING CHARACTERISTICS (continued)**

over recommended operating conditions (unless otherwise noted)

|                         | PARAMETER                                                    | FROM<br>(INPUT)    | TO<br>(OUTPUT) | MIN    | TYP    | MAX    | UNIT   |        |    |    |    |  |  |  |  |  |    |    |    |

|-------------------------|--------------------------------------------------------------|--------------------|----------------|--------|--------|--------|--------|--------|----|----|----|--|--|--|--|--|----|----|----|

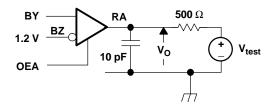

| t <sub>PHZ</sub>        | Propagation delay time, high-level-to-high-impedance output  |                    |                |        | 15     | 26     | 20     |        |    |    |    |  |  |  |  |  |    |    |    |

| t <sub>PLZ</sub>        | Propagation delay time, low-level-to-high-impedance output   | OEA, See Figure 20 | RA             |        | 15     | 23     | ns     |        |    |    |    |  |  |  |  |  |    |    |    |

| t <sub>PZH</sub>        | Propagation delay time, high-impedance-to-high-level output  | OEA, See Figure 20 | KA             |        | 15     | 26     |        |        |    |    |    |  |  |  |  |  |    |    |    |

| t <sub>PZL</sub>        | Propagation delay time, high-impedance-to-low-level output   |                    |                |        | 15     | 23     | ns     |        |    |    |    |  |  |  |  |  |    |    |    |

| t <sub>PHZ</sub>        | Propagation delay time, high-level-to-high-impedance output  |                    | BY, BZ         |        |        |        |        |        |    |    |    |  |  |  |  |  | 10 | 15 | 20 |

| t <sub>PLZ</sub>        | Propagation delay time, low-level-to-high-impedance output   | OFR Con Figure 45  |                |        | 10     | 17     | ns     |        |    |    |    |  |  |  |  |  |    |    |    |

| t <sub>PZH</sub>        | Propagation delay time, high-impedance-to-high-level output  | OEB, See Figure 15 |                | BY, BZ | DT, DZ | D1, DZ | D1, DZ | B1, B2 |    | 10 | 15 |  |  |  |  |  |    |    |    |

| t <sub>PZL</sub>        | Propagation delay time, high-impedance-to-low-level output   |                    |                |        |        |        | 10     | 17     | ns |    |    |  |  |  |  |  |    |    |    |

| t <sub>r(B)</sub>       | Output signal rise time B port                               | Coo Figure 4       | ·              |        | 470    |        | 20     |        |    |    |    |  |  |  |  |  |    |    |    |

| t <sub>f(B)</sub>       | Output signal fall time B port                               | See Figure 14      | •              |        | 450    |        | ps     |        |    |    |    |  |  |  |  |  |    |    |    |

| t <sub>r(A)</sub>       | Output signal rise time A port                               | Coo Figure 47      | ,              |        | 580    |        | 20     |        |    |    |    |  |  |  |  |  |    |    |    |

| t <sub>f(A)</sub>       | Output signal fall time A port                               | See Figure 17      |                |        | 630    |        | ps     |        |    |    |    |  |  |  |  |  |    |    |    |

| t <sub>sk(o)</sub> (1)  | Output skew channel-to-channel                               | _                  |                |        | 0.3    |        | ns     |        |    |    |    |  |  |  |  |  |    |    |    |

| t <sub>sk(p)</sub>      | Pulse skew ( t <sub>PHL</sub> - t <sub>PLH</sub>  ) (A-port) |                    |                |        | 0.7    |        | ns     |        |    |    |    |  |  |  |  |  |    |    |    |

| t <sub>sk(p)</sub>      | Pulse skew ( t <sub>PHL</sub> - t <sub>PLH</sub>  ) (B-port) |                    |                |        | 0.7    |        | ns     |        |    |    |    |  |  |  |  |  |    |    |    |

| t <sub>sk(pp)</sub> (2) | Part-to-part skew                                            |                    |                |        | 0.6    |        | ns     |        |    |    |    |  |  |  |  |  |    |    |    |

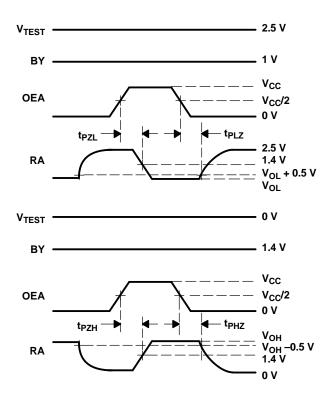

## **TIMING REQUIREMENTS**

over recommended operating conditions (see Figure 21) (unless otherwise noted)

|                          |                         |                                        | MIN | TYP | MAX | UNIT |

|--------------------------|-------------------------|----------------------------------------|-----|-----|-----|------|

| $f_{\text{max}}$         |                         | CLK/LEAB or CLK/LEBA in flip-flop mode |     |     | 300 | MHz  |

| t Cotum time             | Setup for flip-flop     | 0.2                                    |     |     | ns  |      |

| t <sub>SU</sub>          | Setup time              | Setup for latch                        | 1.0 |     |     | ns   |

| t <sub>h</sub> Hold time | Hold time for flip-flop | 1.9                                    |     |     | ns  |      |

|                          |                         | Hold time for latch                    | 1.0 |     |     | ns   |

$t_{sk(o)}$  is the skew between specified outputs of a single device with all driving inputs connected together and the outputs switching in the same direction while driving identical specified loads.  $t_{sk(pp)}$  is the magnitude of the difference delay times between any specified terminals of two devices when both devices operate with the same supply voltages, at the same temperature, and have identical packages and test circuits.

# PARAMETER MEASUREMENT INFORMATION

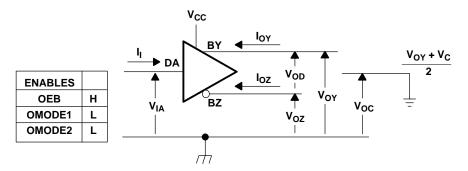

Figure 11. Driver Voltage and Current Definitions

Figure 12. VOD Test Circuit

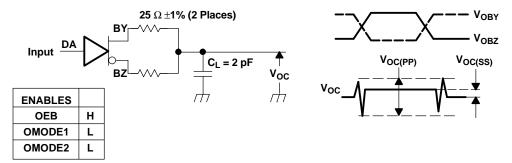

NOTE: All input pulses are supplied by a generator having the following characteristics:  $t_r$  or  $t_f \le 1$  ns, pulse repetition rate (PRR) = 0.5 Mpps, pulse width =  $500 \pm 10$  ns.  $C_L$  includes instrumentation and fixture capacitance within 0,06 m of the device under test. The measurement of  $V_{OC(PP)}$  is made on test equipment with a -3-dB bandwidth of at least 300 MHz.

Figure 13. Test Circuit and Definitions for the Differential Common-Mode Output Voltage

# PARAMETER MEASUREMENT INFORMATION (continued)

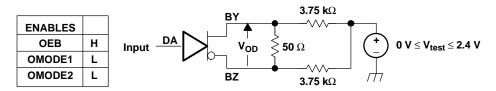

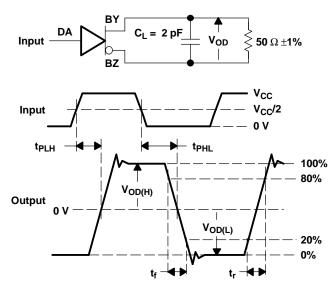

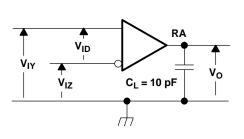

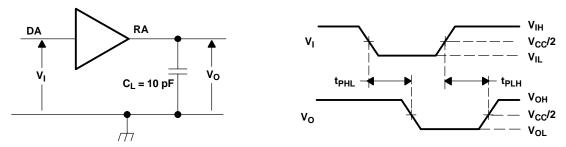

NOTE: All input pulses are supplied by a generator having the following characteristics:  $t_r$  or  $t_f \le 1$  ns, pulse repetition rate (PRR) = 50 Mpps, pulse width = 10 ± 0.2 ns .  $C_L$  includes instrumentation and fixture capacitance within 0,06 m of the device under test

Figure 14. Test Circuit, Timing, and Voltage Definitions for the Dlfferential Output Signal

# PARAMETER MEASUREMENT INFORMATION (continued)

Figure 15. A-to-B Enable/Disable Time Test Circuit and Definitions

Figure 16. Voltage Definitions

Table 5. Receiver Minimum and Maximum Fail-Safe Input Threshold Test Voltages

| APPLIED VOLTAGES |                 | RESULTING DIFFERENTIAL INPUT VOLTAGE | RESULTING COMMON-MODE INPUT VOLTAGE |  |  |

|------------------|-----------------|--------------------------------------|-------------------------------------|--|--|

| V <sub>IY</sub>  | V <sub>IZ</sub> | V <sub>ID</sub>                      | V <sub>IC</sub>                     |  |  |

| 1.25 V           | 1.15 V          | 100 mV                               | 1.2 V                               |  |  |

| 1.15 V           | 1.25 V          | –100 mV                              | 1.2 V                               |  |  |

| 2.4 V            | 2.3 V           | 100 mV                               | 2.35 V                              |  |  |

| 2.3 V            | 2.4 V           | –100 mV                              | 2.35 V                              |  |  |

| 0.1 V            | 0 V             | 100 mV                               | 0.05 V                              |  |  |

| 0 V              | 0.1 V           | –100 mV                              | 0.05 V                              |  |  |

| 1.5 V            | 0.9 V           | 600 mV                               | 1.2 V                               |  |  |

| 0.9 V            | 1.5 V           | –600 mV                              | 1.2 V                               |  |  |

| 2.4 V            | 1.8 V           | 600 mV                               | 2.1 V                               |  |  |

| 1.8 V            | 2.4 V           | –600 mV                              | 2.1 V                               |  |  |

| 0.6 V            | 0 V             | 600 mV                               | 0.3 V                               |  |  |

| 0 V              | 0.6 V           | –600 mV                              | 0 .3V                               |  |  |

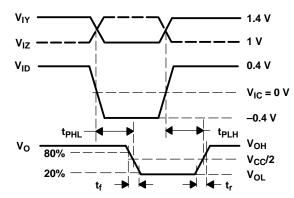

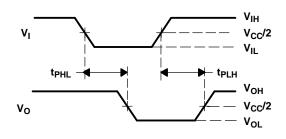

NOTE: All input pulses are supplied by a generator having the following characteristics:  $t_r$  or  $t_f \le 1$  ns, pulse repetition rate (PRR) = 50 Mpps, pulse width = 10  $\pm$  0.2 ns.  $C_L$  includes instrumentation and fixture capacitance within 0,06 m of the device under test.

Figure 17. Timing Test Circuit and Waveforms

NOTE: All input pulses are supplied by a generator having the following characteristics:  $t_r$  or  $t_f \le 1$  ns, pulse repetition rate (PRR) = 50 Mpps, pulse width = 10  $\pm$  0.2 ns.  $C_L$  includes instrumentation and fixture capacitance within 0,06 m of the device under test.

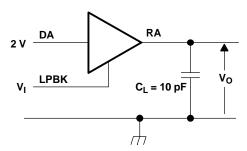

Figure 18. LPBK Timing Test Circuit and Waveforms

NOTE: All input pulses are supplied by a generator having the following characteristics:  $t_r$  or  $t_f \le 1$  ns, pulse repetition rate (PRR) = 50 Mpps, pulse width = 10  $\pm$  0.2 ns.  $C_L$  includes instrumentation and fixture capacitance within 0,06 m of the device under test.

Figure 19. DA to RA Timing Test Circuit and Waveforms

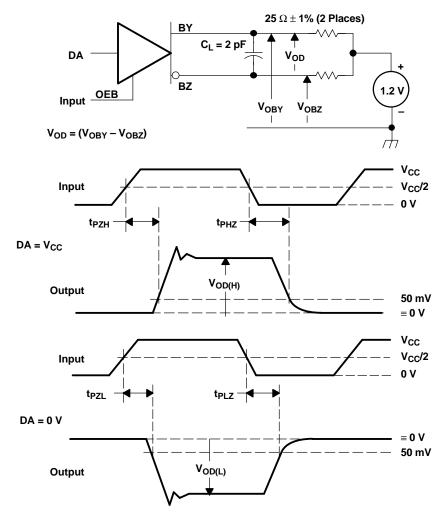

NOTE: All input pulses are supplied by a generator having the following characteristics:  $t_f$  or  $t_f \le 1$  ns, pulse repetition rate (PRR) = 0.5 Mpps, pulse width =  $500 \pm 10$  ns .  $C_1$  includes instrumentation and fixture capacitance within 0,06 m of the device under test.

Figure 20. B-to-A Enable/Disable Time Test Circuit and Definitions

Figure 21. Setup and Hold Time Definition

Figure 22. A-to-B Flip-Flop Mode Timing Circuit

Figure 23. B-to-A Flip-Flop Mode Timing Circuit

#### **APPLICATION INFORMATION**

#### **ABSTRACT**

This section discusses electrical and operational topics not previously covered in this document, such as error detection and the device's ability to synchronize clock signals or manage data transfer between systems with different clock speeds. Basic applications of the analog and digital system diagnostic loopback functions and timing considerations are also analyzed. The SN65LVDM320 is resistant, although not immune, to the effect of setup and hold-time violations; therefore, the penalties of a violation are also examined.

#### INTRODUCTION

The SN65LVDM320 is a versatile, multifunctional device with many applications. Low EMI, low crosstalk, and high differential-current output makes the SN65LVDM320 ideally suited for sensitive multipoint applications and low-impedance loads. Balanced differential signaling reduces noise coupling and allows high signaling rates. Balanced means that the current flowing in each signal line is equal but opposite in direction, resulting in a field canceling effect. This is one of the keys to the low-noise performance of an LVDS differential bus.

Balanced differential input signals eliminate induced noise with efficient common mode rejection (CMR). Internal chip design techniques reduce noise generated by inductive and capacitive mutual coupling, thereby increasing signal integrity. One of the techniques employed to reduce internal noise is the design of separate, dedicated grounds for the single-ended and differential circuitry incorporated within the device.

#### **APPLICATIONS**

The SN65LVDM320 may be used to connect major system blocks, including parallel processors, DRAMs, fast-cache SRAMs, and complex ASIC gate arrays. It effectively transceives the addresses, data, and control signals of these integrated-circuit elements to and from system blocks and backplanes.

The SN65LVDM320 not only facilitates extremely-high parallel burst-transfer rates, but in buffer mode, can move a constant stream of data at 475 Mbps through all of the eight channels simultaneously for a total data throughput exceeding 5 Gbps (transfer rate).

Deskewing clock signals is a requirement in many complex high-speed circuits, and the SN65LVDM320 performs this function at synchronous parallel transfers of 300 megatransfers per second (Mxferps) with very-low channel-to-channel output skew.

The SN65LVDM320 is also ideally suited for connecting system blocks operating at different clock speeds. When OEA and OEB are low, the system on the A-side of the device may be operated independently of the system on the B-side.

#### DIAGNOSTICS AND ERROR DETECTION

Figure 24. Loopback Error Detection

It is not a requirement that the driver be disabled (OEB low) during loopback. The driver may be enabled (OEB high) while loopback is engaged at any time without damaging the circuit. The loopback configuration in Figure 24 with the differential driver enabled provides error assessment in which transmitted data is looped back and compared to the original data by the microprocessor/microcontroller host. This may be implemented in buffer, flip-flop, or in the latch mode shown in Figure 24, and in accordance with the logic of Table 2 and Table 3.

The SN65LVDM320 has been designed to improve a circuit's fault detection capabilities. 100% of the circuitry of the SN65LVDM320 may be functionally checked by activating the A-side and B-side loopback modes. With this functionality, a problem rack, card, circuit block, and even a chip can be located without the burden of boundary-scan protocols.

Traditionally, testability functions such as read-back, pattern insertion, and functional hardware test control require additional part count, connector pins, board space, power, and cost. However, the SN65LVDM320 provides full circuit observability and controllability within the package of an 8-bit LVDM transceiver.

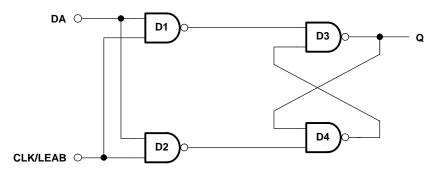

#### METASTABILITY IN LATCHES AND FLIP-FLOPS

Interfacing the asynchronous world to synchronous logic systems can cause problems. Latches and flip-flops, or basically, registers which are normally considered to have only two stable states (low and high) actually have a third state, the metastable state. Metastability can occur when the setup or the hold time is violated and the latch remains balanced in its threshold region. While in this metastable state, system noise can trigger either a high or low state.

Figure 25. The A-Side to B-Side Signal Path

Figure 26. SN65LVDM320 D-Type latch

The SN65LVDM320 D-type latch circuitry of Figure 26 is shown in Figure 25. When data at pin DA is applied to D1, data is internally applied to D2. Therefore, when the CLK/LEAB pin is low, the outputs of D1 and D2 are high and the D3/D4 R-S latch is latched and stable. When CLK/LEAB transitions to high, the latch is transparent to the data input to DA and Q equals DA.

If data changes during the setup to hold time period, it is possible for the D1 and D2 outputs to be in the threshold region of D3 and D4. Under these conditions, D3 and D4 could be perfectly balanced in a metastable condition, allowing system noise to force the latch into a high or low state. This metastable condition can theoretically last as long as 25 ns and cause a system to crash if care is not taken with the asynchronous/synchronous interface. Although the SN65LVDM320 is metastable resistant by design, it is not entirely immune, and the setup and hold times must adhere to those listed in the timing requirements section.

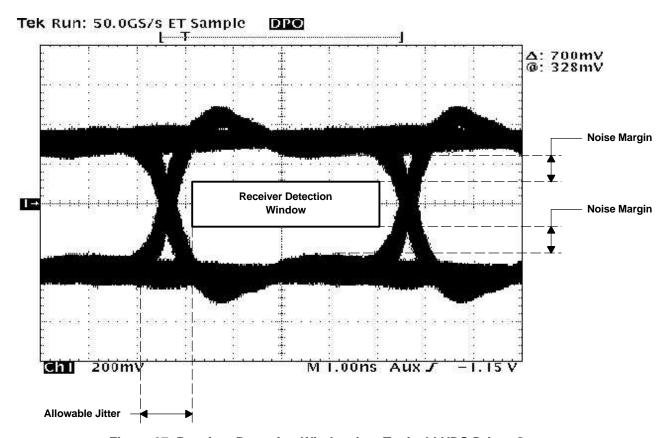

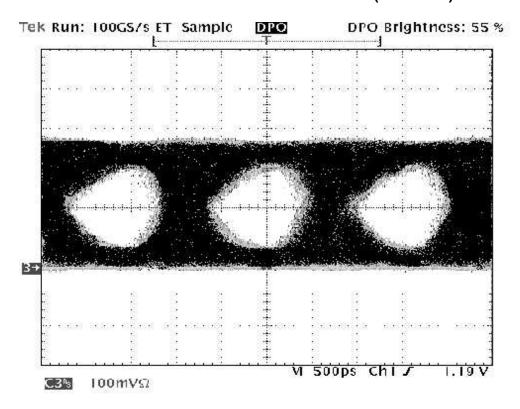

## TYPICAL SN65LVDM320 OUTPUT WAVEFORM (THE EYE PATTERN)

Figure 27 displays a receiver's detection window in a typical LVDS output signal. When a receiver's differential-input voltage level drops, the system noise margin is reduced. Lowering the height enters the input voltage threshold of a receiver, eventually closing the eye and corrupting the data. Jitter content decreases the available time for accurate reception, and depending upon the application, may exceed 50% of the bit width without any problems. To read more about the terms and sources of jitter, see the *Jitter Analysis* application report (SLLA075).

Figure 27. Receiver Detection Window in a Typical LVDS Driver Output

Figure 28. A Receiver Output With All Eight Channels at 630 Megatransfers per Second

The highest signaling rate measurable is 630 Mbps due to the limitations of the test circuit and equipment used to capture this oscillograph. It was captured while all eight channels were transmitting data in B-to-A buffer mode from the differential bus to the receiver. The measurement is taken from a receiver output test point across a 1.75-in, 50- $\Omega$  characteristic impedance trace of a TI bench evaluation board.

#### **TEST EQUIPMENT**

HP 6236B dc power supply provides the required supply voltage of 3.3 V for the LVDM320. A Tektronix HFS9009 signal generator is employed as a nonreturn-to-zero (NRZ), pseudo-random binary sequence (PRBS) signal source for the LVDM320 and is adjusted as follows:

- Pattern: NRZ, PRBS

- Differential input high level: 1.6 V

Differential input low level: 0.8 V

- Transition time: 800 ps

At high signaling rates, the influence of the equipment used to measure a signal of concern must be minimized. A Tektronix 794D oscilloscope and Tektronix P6247 differential probes are used in this test. Each probe has a bandwidth of 1 GHz and the probe capacitance is less than 1 pF.

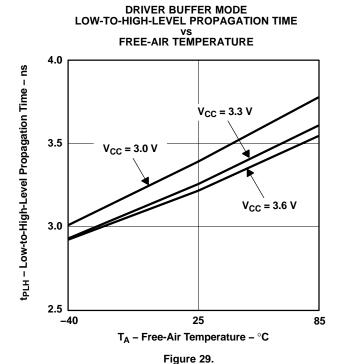

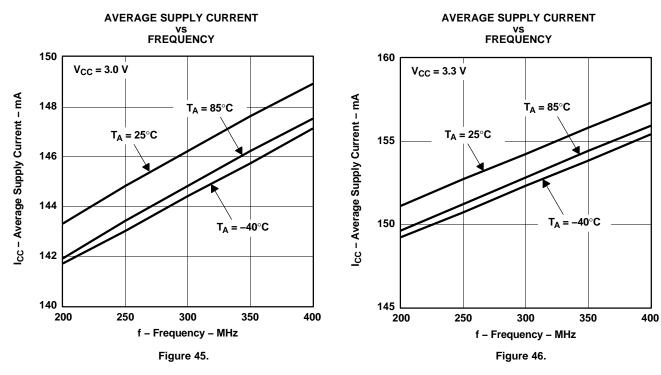

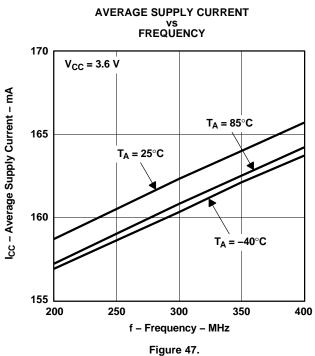

# TYPICAL CHARACTERISTICS

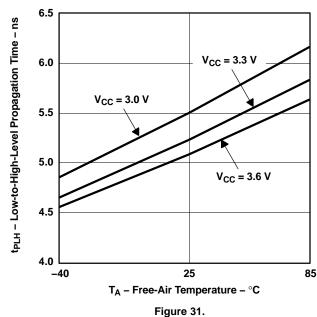

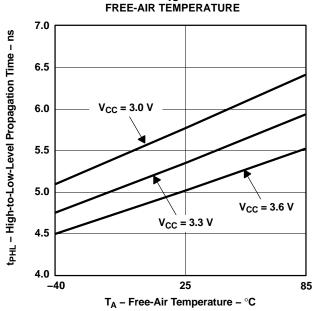

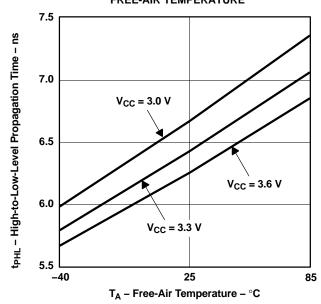

#### DRIVER LATCH MODE LOW-TO-HIGH-LEVEL PROPAGATION TIME vs FREE-AIR TEMPERATURE

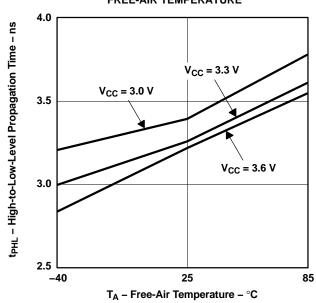

#### DRIVER BUFFER MODE HIGH-TO-LOW-LEVEL PROPAGATION TIME VS FREE-AIR TEMPERATURE

Figure 30.

#### DRIVER LATCH MODE HIGH-TO-LOW-LEVEL PROPAGATION TIME VS

Figure 32.

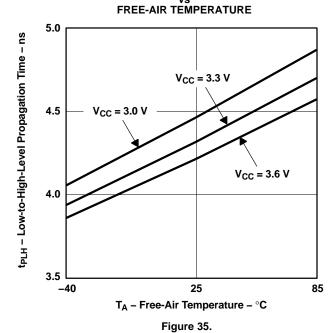

#### DRIVER FLIP-FLOP MODE LOW-TO-HIGH-LEVEL PROPAGATION TIME VS FREE-AIR TEMPERATURE

Figure 33.

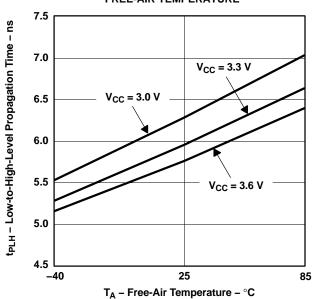

# RECEIVER BUFFER MODE LOW-TO-HIGH-LEVEL PROPAGATION TIME

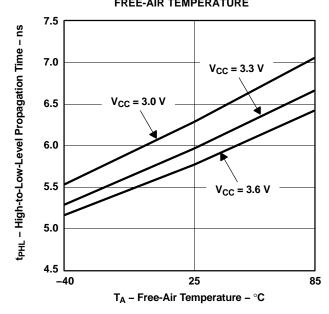

# DRIVER FLIP-FLOP MODE HIGH-TO-LOW-LEVEL PROPAGATION TIME vs FREE-AIR TEMPERATURE

Figure 34.

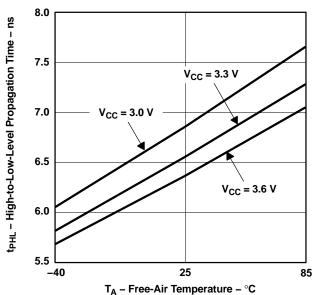

# RECEIVER BUFFER MODE HIGH-TO-LOW-LEVEL PROPAGATION TIME

#### FREE-AIR TEMPERATURE

Figure 36.

Figure 37.

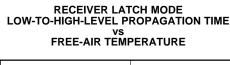

#### RECEIVER FLIP-FLOP MODE LOW-TO-HIGH-LEVEL PROPAGATION TIME vs

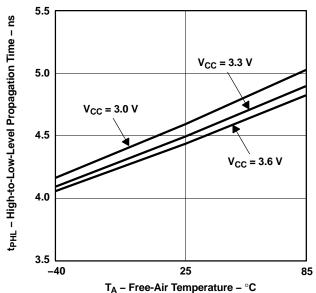

RECEIVER LATCH MODE

HIGH-TO-LOW-LEVEL PROPAGATION TIME

VS

FREE-AIR TEMPERATURE

Figure 38.

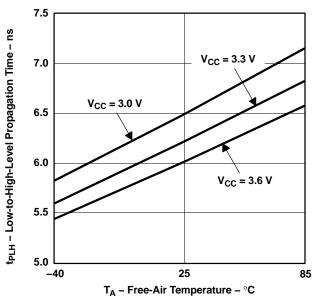

# RECEIVER FLIP-FLOP MODE HIGH-TO-LOW-LEVEL PROPAGATION TIME

#### FREE-AIR TEMPERATURE

Figure 40.

Figure 41.

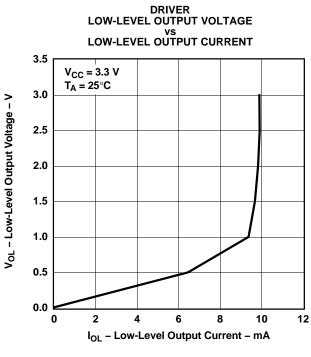

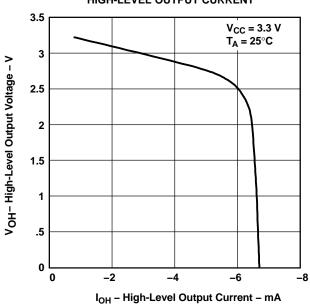

DRIVER

HIGH-LEVEL OUTPUT VOLTAGE

VS

HIGH-LEVEL OUTPUT CURRENT

Figure 42.

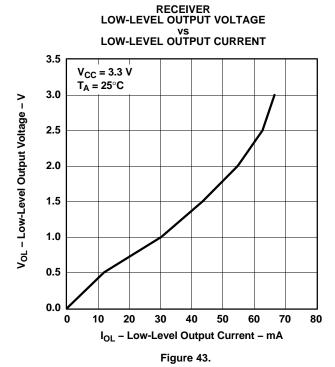

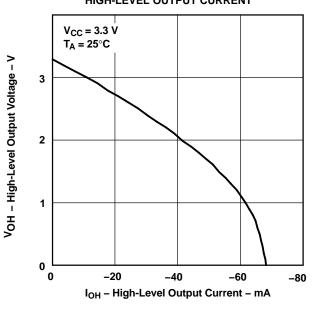

# RECEIVER HIGH-LEVEL OUTPUT VOLTAGE VS HIGH-LEVEL OUTPUT CURRENT

Figure 44.

#### PACKAGE OPTION ADDENDUM

www.ti.com 30-Jul-2009

#### **PACKAGING INFORMATION**

| Orderable Device  | Status <sup>(1)</sup> | Package<br>Type | Package<br>Drawing | Pins | Package<br>Qty | e Eco Plan <sup>(2)</sup> | Lead/Ball Finish | MSL Peak Temp <sup>(3)</sup> |

|-------------------|-----------------------|-----------------|--------------------|------|----------------|---------------------------|------------------|------------------------------|

| SN65LVDM320DGG    | ACTIVE                | TSSOP           | DGG                | 64   | 25             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR          |

| SN65LVDM320DGGG4  | ACTIVE                | TSSOP           | DGG                | 64   | 25             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR          |

| SN65LVDM320DGGR   | ACTIVE                | TSSOP           | DGG                | 64   |                | TBD                       | Call TI          | Call TI                      |

| SN65LVDM320DGGRG4 | ACTIVE                | TSSOP           | DGG                | 64   |                | TBD                       | Call TI          | Call TI                      |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

**NRND:** Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

TBD: The Pb-Free/Green conversion plan has not been defined.

**Pb-Free** (RoHS): TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

**Pb-Free (RoHS Exempt):** This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

**Green (RoHS & no Sb/Br):** TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

(3) MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

**Applications Products Amplifiers** amplifier.ti.com Audio www.ti.com/audio Data Converters Automotive www.ti.com/automotive dataconverter.ti.com DLP® Products Broadband www.dlp.com www.ti.com/broadband DSP Digital Control dsp.ti.com www.ti.com/digitalcontrol Clocks and Timers www.ti.com/clocks Medical www.ti.com/medical Military Interface www.ti.com/military interface.ti.com Optical Networking Logic logic.ti.com www.ti.com/opticalnetwork Power Mgmt power.ti.com Security www.ti.com/security Telephony Microcontrollers microcontroller.ti.com www.ti.com/telephony Video & Imaging www.ti-rfid.com www.ti.com/video RF/IF and ZigBee® Solutions www.ti.com/lprf Wireless www.ti.com/wireless

> Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2009, Texas Instruments Incorporated