# Micropower Single-Supply Rail-to-Rail Input/Output Op Amps

# OP191/0P291/0P491

#### **FEATURES**

Single-Supply Operation: 2.7 V to 12 V

Wide Input Voltage Range Rail-to-Rail Output Swing

Low Supply Current: 300 μA/Amp

Wide Bandwidth: 3 MHz Slew Rate: 0.5 V/ $\mu$ s

Low Offset Voltage: 700  $\mu$ V

No Phase Reversal

#### **APPLICATIONS**

Industrial Process Control

Battery-Powered Instrumentation

Power Supply Control and Protection

Telecom

Remote Sensors

Low-Voltage Strain Gage Amplifiers

DAC Output Amplifier

#### **GENERAL DESCRIPTION**

The OP191, OP291, and OP491 are single, dual and quad micropower, single-supply, 3 MHz bandwidth amplifiers featuring rail-to-rail inputs and outputs. All are guaranteed to operate from a 3 V single supply as well as  $\pm 5$  V dual supplies.

Fabricated on Analog Devices' CBCMOS process, the OP191 family has a unique input stage that allows the input voltage to safely extend 10 V beyond either supply without any phase inversion or latch-up. The output voltage swings to within millivolts of the supplies and continues to sink or source current all the way to the supplies.

Applications for these amplifiers include portable telecom equipment, power supply control and protection, and interface for transducers with wide output ranges. Sensors requiring a rail-to-rail input amplifier include Hall effect, piezo electric, and resistive transducers.

The ability to swing rail-to-rail at both the input and output enables designers to build multistage filters in single-supply systems and maintain high signal-to-noise ratios.

The OP191/OP291/OP491 are specified over the extended industrial (-40°C to +125°C) temperature range. The OP191 single and OP291 dual amplifiers are available in 8-lead plastic SO surface mount packages\*. The OP491 quad is available in 14-lead DIPs and narrow 14-lead SO packages. Consult factory for OP491 TSSOP availability.

\*The OP291 dual is also available in 8-lead Plastic Dip.

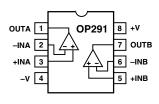

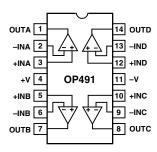

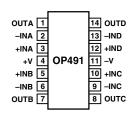

#### PIN CONFIGURATIONS

8-Lead Narrow-Body SO

8-Lead Narrow-Body SO

8-Lead Plastic DIP

14-Lead Plastic DIP

14-Lead SO

14-Lead TSSOP

#### REV. A

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

# OP191/OP291/OP491-SPECIFICATIONS

# **ELECTRICAL SPECIFICATIONS** (@ $V_S = +3.0 \text{ V}$ , $V_{CM} = 0.1 \text{ V}$ , $V_0 = 1.4 \text{ V}$ , $T_A = 25^{\circ}\text{C}$ unless otherwise noted.)

| Parameter                                                                                                                                                                                              | Symbol                                                                                                           | Conditions                                                                                                                                                                                                                                                                                                                                                                                                         | Min                         | Тур                                       | Max                                                  | Unit                                                                                             |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-------------------------------------------|------------------------------------------------------|--------------------------------------------------------------------------------------------------|

| INPUT CHARACTERISTICS Offset Voltage OP191G  OP291/OP491G  Input Bias Current  Input Offset Current  Input Voltage Range Common-Mode Rejection Ratio                                                   | V <sub>os</sub>                                                                                                  | $-40^{\circ}\text{C} \le \text{T}_{\text{A}} \le +125^{\circ}\text{C}$ $V_{\text{CM}} = 0 \text{ V to } 2.9 \text{ V}$ $-40^{\circ}\text{C} \le \text{T}_{\text{A}} \le +125^{\circ}\text{C}$ | 0<br>70<br>65               | 80<br>80<br>30<br>0.1                     | 500<br>1<br>700<br>1.25<br>65<br>95<br>11<br>22<br>3 | μV<br>mV<br>μV<br>mV<br>nA<br>nA<br>nA<br>v<br>dB<br>dB                                          |

| Large Signal Voltage Gain  Offset Voltage Drift Bias Current Drift Offset Current Drift                                                                                                                | $\begin{array}{c} A_{VO} \\ \Delta V_{OS}/\Delta T \\ \Delta I_B/\Delta T \\ \Delta I_{OS}/\Delta T \end{array}$ | $R_{L} = 10 \text{ k}\Omega$ , $V_{O} = 0.3 \text{ V to } 2.7 \text{ V}$<br>$-40^{\circ}\text{C} \le T_{A} \le +125^{\circ}\text{C}$                                                                                                                                                                                                                                                                               | 25                          | 70<br>50<br>1.1<br>100<br>20              |                                                      | V/mV<br>V/mV<br>µV/°C<br>pA/°C<br>pA/°C                                                          |

| OUTPUT CHARACTERISTICS Output Voltage High Output Voltage Low Short Circuit Limit                                                                                                                      | $ m V_{OH}$ $ m V_{OL}$ $ m I_{SC}$                                                                              | $R_{L} = 100 \text{ k}\Omega \text{ to GND}$ $-40^{\circ}\text{C to } +125^{\circ}\text{C}$ $R_{L} = 2 \text{ k}\Omega \text{ to GND}$ $-40^{\circ}\text{C to } +125^{\circ}\text{C}$ $R_{L} = 100 \text{ k}\Omega \text{ to V+}$ $-40^{\circ}\text{C to } +125^{\circ}\text{C}$ $R_{L} = 2 \text{ k}\Omega \text{ to V+}$ $-40^{\circ}\text{C to } +125^{\circ}\text{C}$ Sink/Source                              | 2.95<br>2.90<br>2.8<br>2.70 | 2.99<br>2.98<br>2.9<br>2.8<br>4.5<br>40   | 10<br>35<br>75<br>130                                | V<br>V<br>V<br>V<br>mV<br>mV<br>mV<br>mV                                                         |

| Open-Loop Impedance                                                                                                                                                                                    | Z <sub>OUT</sub>                                                                                                 | -40°C to +125°C<br>f = 1 MHz, A <sub>V</sub> = 1                                                                                                                                                                                                                                                                                                                                                                   | ±6.0                        | ±10.5<br>200                              |                                                      | mA<br>Ω                                                                                          |

| POWER SUPPLY Power Supply Rejection Ratio Supply Current/Amplifier                                                                                                                                     | PSRR<br>I <sub>SY</sub>                                                                                          | $V_S = 2.7 \text{ V to } 12 \text{ V}$<br>$-40^{\circ}\text{C} \le T_A \le +125^{\circ}\text{C}$<br>$V_O = 0 \text{ V}$<br>$-40^{\circ}\text{C} \le T_A \le +125^{\circ}\text{C}$                                                                                                                                                                                                                                  | 80<br>75                    | 110<br>110<br>200<br>330                  | 350<br>480                                           | dB<br>dB<br>μA<br>μA                                                                             |

| DYNAMIC PERFORMANCE Slew Rate Slew Rate Full-Power Bandwidth Settling Time Gain Bandwidth Product Phase Margin Channel Separation  NOISE PERFORMANCE Voltage Noise Voltage Noise Current Noise Density | $+SR$ $-SR$ $BW_{P}$ $t_{S}$ $GBP$ $\theta_{O}$ $CS$ $e_{n} p-p$ $e_{n}$ $i_{n}$                                 | $R_{L} = 10 \text{ k}\Omega$ $R_{L} = 10 \text{ k}\Omega$ $1\% \text{ Distortion}$ $To 0.01\%$ $f = 1 \text{ kHz}, R_{L} = 10 \text{ k}\Omega$ $0.1 \text{ Hz to } 10 \text{ Hz}$ $f = 1 \text{ kHz}$                                                                                                                                                                                                              |                             | 0.4<br>0.4<br>1.2<br>22<br>3<br>45<br>145 |                                                      | $V/\mu s$ $V/\mu s$ $kHz$ $\mu s$ $MHz$ $Degrees$ $dB$ $\mu V p-p$ $nV/\sqrt{Hz}$ $pA/\sqrt{Hz}$ |

Specifications subject to change without notice.

-2- REV. A

# $\textbf{ELECTRICAL SPECIFICATIONS} \ (@V_S = +5.0 \ V, V_{CM} = 0.1 \ V, V_0 = 1.4 \ V, T_A = 25^{\circ}\text{C unless otherwise noted.} )$

| Parameter                         | Symbol                   | Conditions                                                             | Min       | Typ          | Max     | Unit           |

|-----------------------------------|--------------------------|------------------------------------------------------------------------|-----------|--------------|---------|----------------|

| INPUT CHARACTERISTICS             |                          |                                                                        |           |              |         |                |

| Offset Voltage OP191              | $V_{OS}$                 |                                                                        |           | 80           | 500     | μV             |

|                                   |                          | $-40^{\circ}\text{C} \le \text{T}_{\text{A}} \le +125^{\circ}\text{C}$ |           |              | 1.0     | mV             |

| OP291/OP491                       | $V_{OS}$                 |                                                                        |           | 80           | 700     | μV             |

|                                   | _                        | $-40^{\circ}\text{C} \le \text{T}_{\text{A}} \le +125^{\circ}\text{C}$ |           |              | 1.25    | mV             |

| Input Bias Current                | $I_{\mathrm{B}}$         | 4000 45 4 44500                                                        |           | 30           | 65      | nA             |

| I 000 00                          |                          | $-40^{\circ}\text{C} \le \text{T}_{\text{A}} \le +125^{\circ}\text{C}$ |           | 0.1          | 95      | nA             |

| Input Offset Current              | $I_{OS}$                 | 400C < T < 11050C                                                      |           | 0.1          | 11      | nA             |

| Input Voltage Range               |                          | $-40$ °C $\leq$ T <sub>A</sub> $\leq$ +125°C                           | 0         |              | 22<br>5 | nA<br>V        |

| Common-Mode Rejection Ratio       | CMRR                     | $V_{CM} = 0 \text{ V to } 4.9 \text{ V}$                               | 70        | 93           | 5       | dB             |

| Common-wode Rejection Ratio       | CMIKK                    | $V_{CM} = 0$ V to 4.9 V<br>-40°C $\leq T_A \leq +125$ °C               | 65        | 90           |         | dB             |

| Large Signal Voltage Gain         | $A_{ m VO}$              | $R_L = 10 \text{ k}\Omega$ , $V_O = 0.3 \text{ V to } 4.7 \text{ V}$   | 25        | 70           |         | V/mV           |

| Daige Signar Voltage Sum          | 1100                     | $-40^{\circ}$ C $\leq$ T <sub>A</sub> $\leq$ +125 $^{\circ}$ C         | 23        | 50           |         | V/mV           |

| Offset Voltage Drift              | $\Delta V_{OS}/\Delta T$ | $-40^{\circ}\text{C} \le \text{T}_{\text{A}} \le +125^{\circ}\text{C}$ |           | 1.1          |         | μV/°C          |

| Bias Current Drift                | $\Delta I_B/\Delta T$    | a - 123 C                                                              |           | 100          |         | pA/°C          |

| Offset Current Drift              | $\Delta I_{OS}/\Delta T$ |                                                                        |           | 20           |         | pA/°C          |

| OUTPUT CHARACTERISTICS            |                          |                                                                        |           |              |         |                |

| Output Voltage High               | $V_{OH}$                 | $R_{L} = 100 \text{ k}\Omega \text{ to GND}$                           | 4.95      | 4.99         |         | V              |

| Output voltage High               | v OH                     | -40°C to +125°C                                                        | 4.90      | 4.99         |         | V              |

|                                   |                          | $R_L = 2 k\Omega$ to GND                                               | 4.8       | 4.85         |         | V              |

|                                   |                          | -40°C to +125°C                                                        | 4.65      | 4.75         |         | V              |

| Output Voltage Low                | $V_{OL}$                 | $R_{\rm I} = 100 \text{ k}\Omega \text{ to V} +$                       | 1.05      | 4.5          | 10      | mV             |

| output voltage 20 w               | · OL                     | -40°C to +125°C                                                        |           | 1.5          | 35      | mV             |

|                                   |                          | $R_L = 2 k\Omega \text{ to V}+$                                        |           | 40           | 75      | mV             |

|                                   |                          | -40°C to +125°C                                                        |           |              | 155     | mV             |

| Short Circuit Limit               | $I_{SC}$                 | Sink/Source                                                            | ±8.75     | ±13.5        |         | mA             |

|                                   |                          | −40°C to +125°C                                                        | $\pm 6.0$ | $\pm 10.5$   |         | mA             |

| Open-Loop Impedance               | $Z_{OUT}$                | $f = 1 \text{ MHz}, A_V = 1$                                           |           | 200          |         | Ω              |

| POWER SUPPLY                      |                          |                                                                        |           |              |         |                |

| Power Supply Rejection Ratio      | PSRR                     | $V_S = 2.7 \text{ V to } 12 \text{ V}$                                 | 80        | 110          |         | dB             |

| 1 ower supply rejection ratio     | 10141                    | $-40^{\circ}\text{C} \le \text{T}_{\text{A}} \le +125^{\circ}\text{C}$ | 75        | 110          |         | dB             |

| Supply Current/Amplifier          | $I_{SY}$                 | $V_{O} = 0 \text{ V}$                                                  | 13        | 220          | 400     | μA             |

|                                   | -31                      | $-40$ °C $\leq T_A \leq +125$ °C                                       |           | 350          | 500     | μΑ             |

| DYNAMIC PERFORMANCE               |                          |                                                                        |           |              |         |                |

| Slew Rate                         | +SR                      | $R_{L} = 10 \text{ k}\Omega$                                           |           | 0.4          |         | V/µs           |

|                                   | –SR                      | 2                                                                      |           |              |         |                |

| Slew Rate<br>Full-Power Bandwidth | -SK<br>BW <sub>P</sub>   | $R_{L} = 10 \text{ k}\Omega$<br>1% Distortion                          |           | $0.4 \\ 1.2$ |         | V/µs<br>kHz    |

| Settling Time                     |                          | To 0.01%                                                               |           | 22           |         | μs             |

| Gain Bandwidth Product            | t <sub>s</sub><br>GBP    | 10 0.01/0                                                              |           | 3            |         | μs<br>MHz      |

| Phase Margin                      | $\theta_{\rm O}$         |                                                                        |           | 45           |         | Degrees        |

| Channel Separation                | CS                       | $f = 1 \text{ kHz}, R_L = 10 \text{ k}\Omega$                          |           | 145          |         | dB             |

|                                   |                          |                                                                        |           |              |         |                |

| NOISE PERFORMANCE                 |                          | 0.1 II- 6- 10 II                                                       |           | 2            |         |                |

| Voltage Noise                     | e <sub>n</sub> p-p       | 0.1 Hz to 10 Hz                                                        |           | 2            |         | μV p-p         |

| Voltage Noise Density             | e <sub>n</sub>           | f = 1 kHz                                                              |           | 35           |         | $nV/\sqrt{Hz}$ |

| Current Noise Density             | i <sub>n</sub>           |                                                                        |           | 0.8          |         | pA/√Hz         |

NOTE

REV. A \_3\_

<sup>+5</sup> V specifications are guaranteed by +3 V and  $\pm 5$  V testing.

Specifications subject to change without notice.

# $\textbf{ELECTRICAL SPECIFICATIONS} \ (@\ V_0 = \pm 5.0\ V, -4.9\ V \leq V_{\text{CM}} \leq +4.9\ V, \, T_A = 25^{\circ}\text{C unless otherwise noted.})$

| Parameter                                                                                            | Symbol                                                                                                 | Conditions                                                                                                                                       | Min                              | Typ                                         | Max            | Unit                                           |

|------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|---------------------------------------------|----------------|------------------------------------------------|

| INPUT CHARACTERISTICS<br>Offset Voltage OP191                                                        | V <sub>OS</sub>                                                                                        | $-40^{\circ}\text{C} \le \text{T}_{\text{A}} \le +125^{\circ}\text{C}$                                                                           |                                  | 80                                          | 500<br>1       | μV<br>mV                                       |

| OP291/OP491                                                                                          | Vos                                                                                                    | $-40^{\circ}\text{C} \le \text{T}_{\text{A}} \le +125^{\circ}\text{C}$                                                                           |                                  | 80                                          | 700<br>1.25    | μV<br>mV                                       |

| Input Bias Current                                                                                   | $I_B$                                                                                                  |                                                                                                                                                  |                                  | 30                                          | 65             | nA                                             |

| Input Offset Current                                                                                 | $I_{OS}$                                                                                               | $-40^{\circ}\text{C} \le \text{T}_{\text{A}} \le +125^{\circ}\text{C}$<br>$-40^{\circ}\text{C} \le \text{T}_{\text{A}} \le +125^{\circ}\text{C}$ |                                  | 0.1                                         | 95<br>11<br>22 | nA<br>nA<br>nA                                 |

| Input Voltage Range<br>Common-Mode Rejection                                                         | CMR                                                                                                    | $V_{CM} = \pm 5 V$<br>-40°C \le T <sub>A</sub> \le +125°C                                                                                        | -5<br>75<br>67                   | 100<br>97                                   | +5             | V<br>dB<br>dB                                  |

| Large Signal Voltage Gain                                                                            | A <sub>VO</sub>                                                                                        | $R_L = 10 \text{ k}\Omega, V_O = \pm 4.7 \text{ V}, \\ -40^{\circ}\text{C} \le T_A \le +125^{\circ}\text{C}$                                     | 25                               | 70<br>50                                    |                | V/mV                                           |

| Offset Voltage Drift<br>Bias Current Drift<br>Offset Current Drift                                   | $\begin{array}{c} \Delta V_{OS}/\Delta T \\ \Delta I_B/\Delta T \\ \Delta I_{OS}/\Delta T \end{array}$ | 10 G = 1 <sub>A</sub> = 125 G                                                                                                                    |                                  | 1.1<br>100<br>20                            |                | μV/°C<br>pA/°C<br>pA/°C                        |

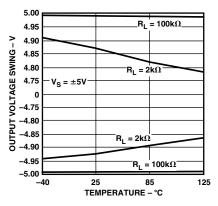

| OUTPUT CHARACTERISTICS Output Voltage Swing                                                          | Vo                                                                                                     | $R_{L} = 100 \text{ k}\Omega \text{ to GND}$<br>-40°C to +125°C<br>$R_{L} = 2 \text{ k}\Omega \text{ to GND}$<br>-40°C $\leq T_{A} \leq$ +125°C  | ±4.93<br>±4.90<br>±4.80<br>±4.65 | $\pm 4.99$ $\pm 4.98$ $\pm 4.95$ $\pm 4.75$ |                | V<br>V<br>V                                    |

| Short Circuit Limit                                                                                  | $I_{SC}$                                                                                               | Sink/Source<br>-40°C to +125°C                                                                                                                   | ±8.75<br>±6                      | ±16<br>±13                                  |                | mA<br>mA                                       |

| Open-Loop Impedance                                                                                  | Z <sub>OUT</sub>                                                                                       | $f = 1 \text{ MHz}, A_V = 1$                                                                                                                     |                                  | 200                                         |                | Ω                                              |

| POWER SUPPLY                                                                                         |                                                                                                        |                                                                                                                                                  |                                  |                                             |                |                                                |

| Power Supply Rejection Ratio Supply Current/Amplifier                                                | PSRR I <sub>SY</sub>                                                                                   | $V_S = \pm 5 \text{ V}$<br>$-40^{\circ}\text{C} \le T_A \le +125^{\circ}\text{C}$<br>$V_O = 0 \text{ V}$                                         | 80<br>70                         | 110<br>100<br>260<br>390                    | 420            | dB<br>dB<br>μA                                 |

| DVNAMIC DEDECORMANICE                                                                                |                                                                                                        | $-40 \le T_A \le +125^{\circ}C$                                                                                                                  |                                  | 390                                         | 550            | μА                                             |

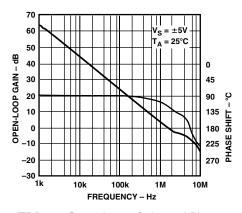

| DYNAMIC PERFORMANCE Slew Rate Full-Power Bandwidth Settling Time Gain Bandwidth Product Phase Margin | $\pm$ SR<br>$BW_P$<br>$t_S$<br>GBP<br>$\theta_O$<br>CS                                                 | $R_L = 10 \text{ k}\Omega$ 1% Distortion To 0.01% $f = 1 \text{ kHz}$                                                                            |                                  | 0.5<br>1.2<br>22<br>3<br>45                 |                | V/µs kHz µs MHz Degrees                        |

| Channel Separation  NOISE PERFORMANCE  Voltage Noise  Voltage Noise Density  Current Noise Density   | e <sub>n</sub> p-p<br>e <sub>n</sub><br>i <sub>n</sub>                                                 | 0.1 Hz to 10 Hz<br>f = 1 kHz                                                                                                                     |                                  | 2<br>35<br>0.8                              |                | dB $\mu V p-p \\ nV/\sqrt{Hz} \\ pA/\sqrt{Hz}$ |

Specifications subject to change without notice.

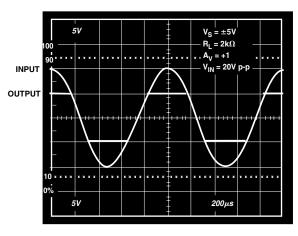

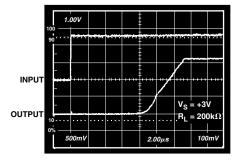

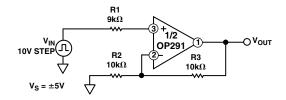

Figure 1. Input and Output with Inputs Overdriven by 5 V

#### ABSOLUTE MAXIMUM RATINGS1

| Supply Voltage                                   |

|--------------------------------------------------|

| Input Voltage GND to $V_S$ 10 V                  |

| Differential Input Voltage7 V                    |

| Output Short-Circuit Duration to GND Indefinite  |

| Storage Temperature Range                        |

| P, S, RU Packages65°C to +150°C                  |

| Operating Temperature Range                      |

| OP191/OP291/OP491G40°C to +125°C                 |

| Junction Temperature Range                       |

| P, S, RU Packages65°C to +150°C                  |

| Lead Temperature Range (Soldering 60 sec) +300°C |

|                                                  |

| Package Type            | $\theta_{\mathrm{JA}}^{2}$ | $\theta_{ m JC}$ | Units |

|-------------------------|----------------------------|------------------|-------|

| 8-Lead Plastic DIP (P)  | 103                        | 43               | °C/W  |

| 8-Lead SOIC (S)         | 158                        | 43               | °C/W  |

| 14-Lead Plastic DIP (P) | 76                         | 33               | °C/W  |

| 14-Lead SOIC (S)        | 120                        | 36               | °C/W  |

| 14-Lead TSSOP (RU)      | 180                        | 35               | °C/W  |

#### NOTES

#### **ORDERING GUIDE**

| Model    | Temperature<br>Range | Package<br>Description | Package<br>Option |

|----------|----------------------|------------------------|-------------------|

| OP191GS  | -40°C to +125°C      | 8-Lead SOIC            | SO-8              |

| OP291GP* | -40°C to +125°C      | 8-Lead Plastic DIP     | N-8               |

| OP291GS  | -40°C to +125°C      | 8-Lead SOIC            | SO-8              |

| OP491GP  | -40°C to +125°C      | 14-Lead Plastic DIP    | N-14              |

| OP491GS  | -40°C to +125°C      | 14-Lead SOIC           | SO-14             |

| OP491GRU | -40°C to +125°C      | 14-Lead TSSOP          | RU-14             |

<sup>\*</sup>Not for new design; obsolete April 2002.

#### **CAUTION**

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the OP191/OP291/OP491 feature proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high-energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

REV. A -5-

<sup>&</sup>lt;sup>1</sup>Absolute maximum ratings apply to both DICE and packaged parts, unless otherwise noted.

$<sup>^2\</sup>theta_{JA}$  is specified for the worst case conditions; i.e.,  $\theta_{JA}$  is specified for device in socket for P-DIP packages;  $\theta_{JA}$  is specified for device soldered in circuit board for TSSOP and SOIC packages.

# **OP191/OP291/OP491—Typical Performance Characteristics**

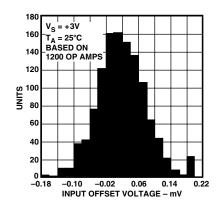

TPC 1. OP291 Input Offset Voltage Distribution,  $V_S = +3 \text{ V}$

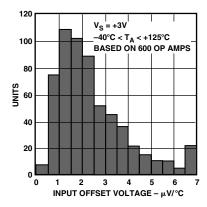

TPC 2. OP291 Input Offset Voltage Drift Distribution,  $V_S = +3 \text{ V}$

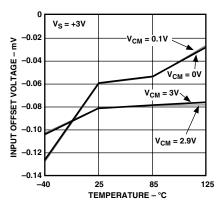

TPC 3. Input Offset Voltage vs. Temperature,  $V_S = +3 V$

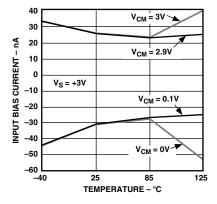

TPC 4. Input Bias Current vs. Temperature,  $V_S = +3 V$

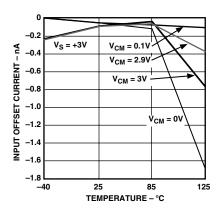

TPC 5. Input Offset Current vs. Temperature,  $V_S = +3 V$

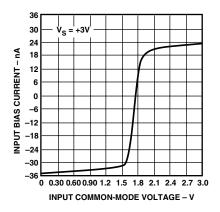

TPC 6. Input Bias Current vs. Common-Mode Voltage,  $V_S = +3 \text{ V}$

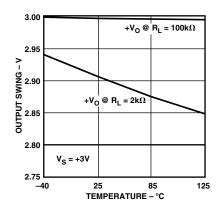

TPC 7. Output Voltage Swing vs. Temperature,  $V_S = +3 \text{ V}$

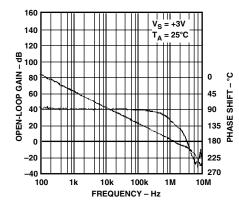

TPC 8. Open-Loop Gain and Phase vs. Frequency,  $V_S = +3 \text{ V}$

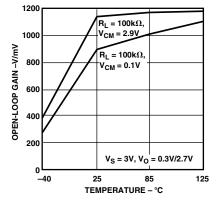

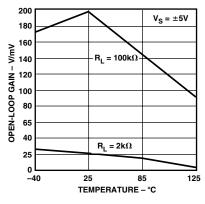

TPC 9. Open-Loop Gain vs. Temperature,  $V_S = +3 \text{ V}$

-6- REV. A

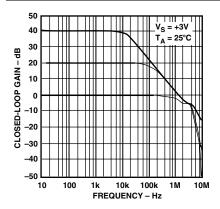

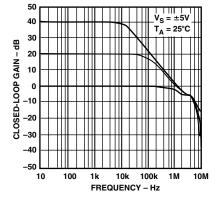

TPC 10. Closed-Loop Gain vs. Frequency,  $V_S = +3 \text{ V}$

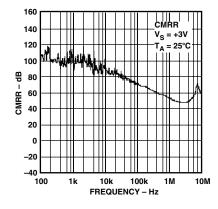

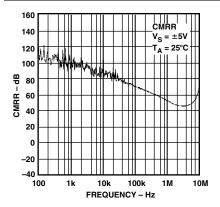

TPC 11. CMRR vs. Frequency,  $V_S = +3 V$

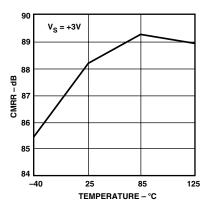

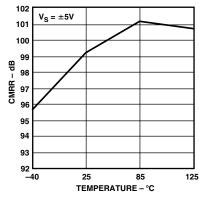

TPC 12. CMRR vs. Temperature,  $V_S = +3 V$

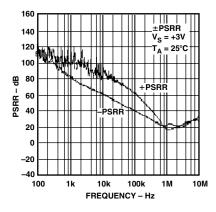

TPC 13. PSRR vs. Frequency,  $V_S = +3 V$

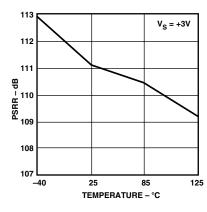

TPC 14. PSRR vs. Temperature,  $V_S = +3 V$

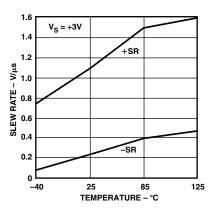

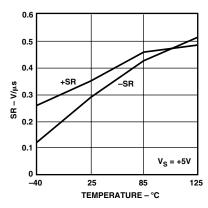

TPC 15. Slew Rate vs. Temperature,  $V_S = +3 V$

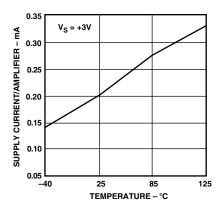

TPC 16. Supply Current vs. Temperature,  $V_S = +3 V$ , +5 V,  $\pm 5 V$

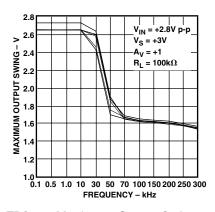

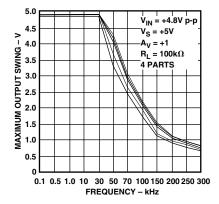

TPC 17. Maximum Output Swing vs. Frequency,  $V_S = +3 \text{ V}$

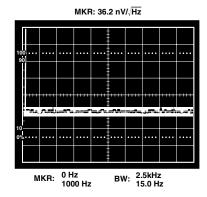

TPC 18. Voltage Noise Density,  $V_S = +3 \text{ V to } \pm 5 \text{ V}$ ,  $A_{VO} = 1000$

REV. A -7-

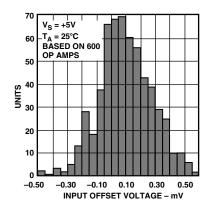

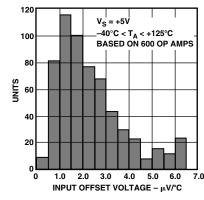

TPC 19. OP291 Input Offset Voltage Distribution,  $V_S = +5 \text{ V}$

TPC 20. OP291 Input Offset Voltage Drift Distribution,  $V_S = +5 \text{ V}$

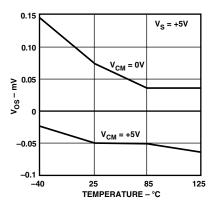

TPC 21. Input Offset Voltage vs. Temperature,  $V_S = +5 \text{ V}$

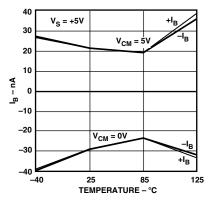

TPC 22. Input Bias Current vs. Temperature,  $V_S = +5 V$

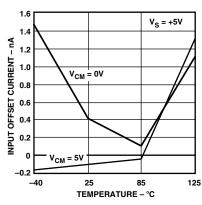

TPC 23. Input Offset Current vs. Temperature,  $V_S = +5 \text{ V}$

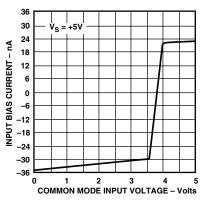

TPC 24. Input Bias Current vs. Common-Mode Voltage,  $V_S = +5 \text{ V}$

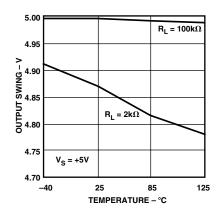

TPC 25. Output Voltage Swing vs. Temperature,  $V_S = +5 \text{ V}$

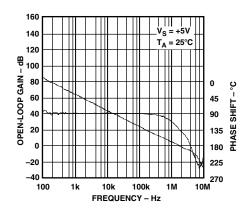

TPC 26. Open-Loop Gain and Phase vs. Frequency,  $V_S = +5 \text{ V}$

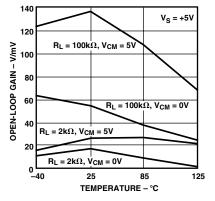

TPC 27. Open-Loop Gain vs. Temperature,  $V_S = +5 \text{ V}$

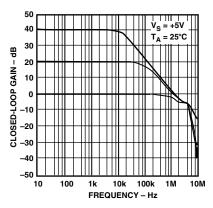

TPC 28. Closed-Loop Gain vs. Frequency,  $V_S = +5 \text{ V}$

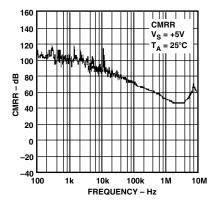

TPC 29. CMRR vs. Frequency,  $V_S = +5 \text{ V}$

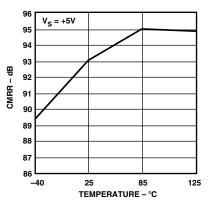

TPC 30. CMRR vs. Temperature,  $V_S = +5 \text{ V}$

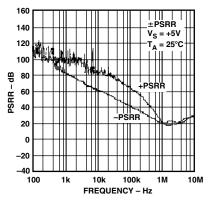

TPC 31. PSRR vs. Frequency,  $V_S = +5 V$

TPC 32. OP291 Slew Rate vs. Temperature,  $V_S = +5 \text{ V}$

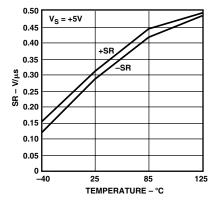

TPC 33. OP491 Slew Rate vs. Temperature,  $V_S = +5 \text{ V}$

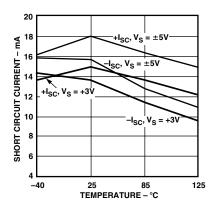

TPC 34. Short Circuit Current vs. Temperature,  $V_S = +3 V$ , +5 V,  $\pm 5 V$

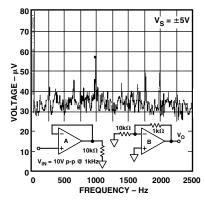

TPC 35. Channel Separation,  $V_S = \pm 5 V$

TPC 36. Maximum Output Swing vs. Frequency,  $V_S = +5 \text{ V}$

REV. A \_9\_

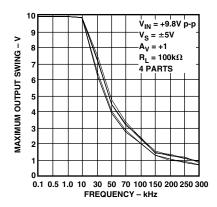

TPC 37. Maximum Output Swing vs. Frequency,  $V_S = \pm 5 V$

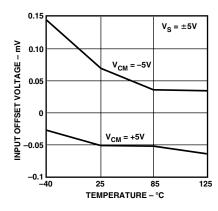

TPC 38. Input Offset Voltage vs. Temperature,  $V_S = \pm 5 V$

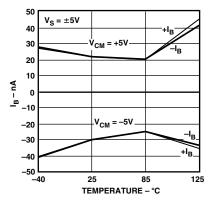

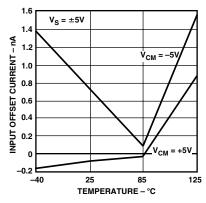

TPC 39. Input Bias Current vs. Temperature,  $V_S = \pm 5 \ V$

TPC 40. Input Offset Current vs. Temperature,  $V_S = \pm 5 V$

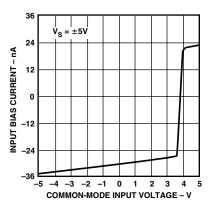

TPC 41. Input Bias Current vs. Common-Mode Voltage,  $V_S = \pm 5 V$

TPC 42. Output Voltage Swing vs. Temperature,  $V_S = \pm 5 V$

TPC 43. Open-Loop Gain and Phase vs. Frequency,  $V_S = \pm 5 \ V$

TPC 44. Open-Loop Gain vs. Temperature,  $V_S = \pm 5 V$

TPC 45. Closed-Loop Gain vs. Frequency,  $V_S = \pm 5 V$

-10- REV. A

TPC 46. CMRR vs. Frequency,  $V_S = \pm 5 V$

TPC 47. CMRR vs. Temperature,  $V_S = \pm 5 V$

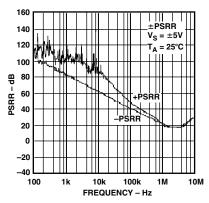

TPC 48. PSRR vs. Frequency,  $V_S = \pm 5 V$

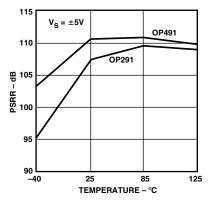

TPC 49. OP291/OP491 PSRR vs. Temperature,  $V_S = \pm 5 V$

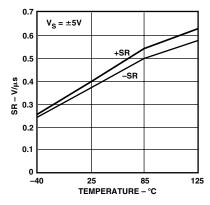

TPC 50. Slew Rate vs. Temperature,  $V_S = \pm 5 V$

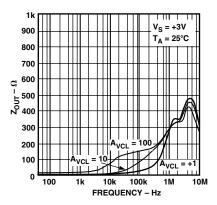

TPC 51. Output Impedance vs. Frequency

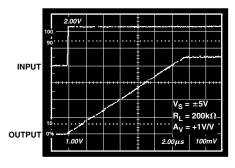

TPC 52. Large Signal Transient Response,  $V_S = +3 V$

TPC 53. Large Signal Transient Response,  $V_S = \pm 5 V$

REV. A -11-

#### **FUNCTIONAL DESCRIPTION**

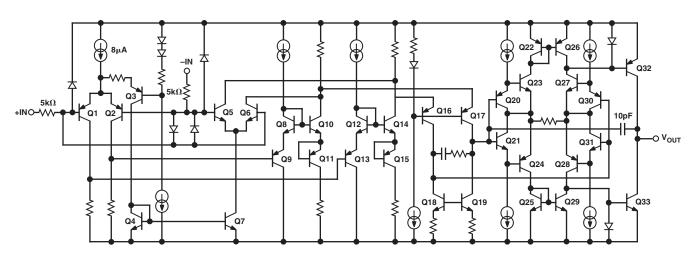

The OP191/OP291/OP491 are single-supply, micropower amplifiers featuring rail-to-rail inputs and outputs. In order to achieve wide input and output ranges, these amplifiers employ unique input and output stages. As the simplified schematic shows (Figure 2), the input stage is actually comprised of two differential pairs, a PNP pair and an NPN pair. These two stages do not actually work in parallel. Instead, only one or the other stage is on for any given input signal level. The PNP stage (transistors Q1 and Q2) is required to ensure that the amplifier remains in the linear region when the input voltage approaches and reaches the negative rail. On the other hand, the NPN stage (transistors Q5 and Q6) is needed for input voltages up to and including the positive rail.

For the majority of the input common-mode range, the PNP stage is active, as is evidenced by examining the graph of Input Bias Current vs. Common-Mode Voltage. Notice that the bias current switches direction at approximately 1.2 V to 1.3 V below the positive rail. At voltages below this, the bias current flows out of the OP291, indicating a PNP input stage. Above this voltage, however, the bias current enters the device, revealing the NPN stage. The actual mechanism within the amplifier for switching between the input stages is comprised of the transistors Q3, Q4, and Q7. As the input common-mode voltage increases, the emitters of Q1 and Q2 follow that voltage plus a diode drop. Eventually the emitters of Q1 and Q2 are high enough to turn Q3 on. This diverts the 8  $\mu A$  of tail current away from the PNP input stage, turning it off. Instead, the current is mirrored through Q4 and Q7 to activate the NPN input stage.

Notice that the input stage includes 5  $k\Omega$  series resistors and differential diodes, a common practice in bipolar amplifiers to protect the input transistors from large differential voltages. These diodes will turn on whenever the differential voltage

exceeds approximately 0.6 V. In this condition, current will flow between the input pins, limited only by the two 5 k $\Omega$  resistors. Being aware of this characteristic is important in circuits where the amplifier may be operated open-loop, such as a comparator. Evaluate each circuit carefully to make sure that the increase in current does not affect the performance.

The output stage of the OP191 family uses a PNP and an NPN transistor as do most output stages; however, the output transistors, Q32 and Q33, are actually connected with their collectors to the output pin to achieve the rail-to-rail output swing. As the output voltage approaches either the positive or negative rail, these transistors begin to saturate. Thus, the final limit on output voltage is the saturation voltage of these transistors, which is about 50 mV. The output stage does have inherent gain arising from the collectors and any external load impedance. Because of this, the open-loop gain of the amplifier is dependent on the load resistance.

#### **Input Overvoltage Protection**

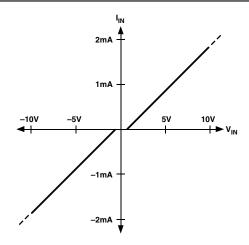

As with any semiconductor device, whenever the condition exists for the input to exceed either supply voltage, attention needs to be paid to the input overvoltage characteristic. When an overvoltage occurs, the amplifier could be damaged depending on the voltage level and the magnitude of the fault current. Figure 3 shows the characteristic for the OP191 family. This graph was generated with the power supplies at ground and a curve tracer connected to the input. As can be seen, when the input voltage exceeds either supply by more than 0.6 V, internal pn-junctions energize, allowing current to flow from the input to the supplies. As described above, the OP291/OP491 does have 5 k $\Omega$  resistors in series with each input, which helps limit the current. Calculating the slope of the current versus voltage in the graph confirms the 5 k $\Omega$  resistor.

Figure 2. Simplified Schematic

-12- REV. A

Figure 3. Input Overvoltage Characteristics

This input current is not inherently damaging to the device as long as it is limited to 5 mA or less. In the case shown, for an input of 10 V over the supply, the current is limited to 1.8 mA. If the voltage is large enough to cause more than 5 mA of current to flow, then an external series resistor should be added. The size of this resistor is calculated by dividing the maximum overvoltage by 5mA and subtracting the internal 5 k $\Omega$  resister. For example, if the input voltage could reach 100 V, the external resistor should be (100 V/5 mA) –5 k = 15 k $\Omega$ . This resistance should be placed in series with either or both inputs if they are subjected to the overvoltages. For more information on general overvoltage characteristics of amplifiers refer to the 1993 System Applications Guide, available from the Analog Devices Literature Center.

#### **Output Voltage Phase Reversal**

Some operational amplifiers designed for single-supply operation exhibit an output voltage phase reversal when their inputs are driven beyond their useful common-mode range. Typically for single-supply bipolar op amps, the negative supply determines the lower limit of their common-mode range. With these devices, external clamping diodes, with the anode connected to

ground and the cathode to the inputs, prevent input signal excursions from exceeding the device's negative supply (i.e., GND), preventing a condition which could cause the output voltage to change phase. JFET-input amplifiers may also exhibit phase reversal, and, if so, a series input resistor is usually required to prevent it.

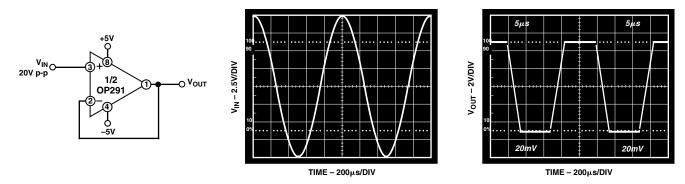

The OP191 family is free from reasonable input voltage range restrictions due to its novel input structure. In fact, the input signal can exceed the supply voltage by a significant amount without causing damage to the device. As illustrated in Figure 4, the OP191 family can safely handle a 20 V p-p input signal on  $\pm 5$  V supplies without exhibiting any sign of output voltage phase reversal or other anomalous behavior. Thus no external clamping diodes are required.

#### Overdrive Recovery

The overdrive recovery time of an operational amplifier is the time required for the output voltage to recover to its linear region from a saturated condition. This recovery time is important in applications where the amplifier must recover quickly after a large transient event, such as a comparator. The circuit shown in Figure 5 was used to evaluate the OP191 family's overload recovery time. The OP191 family takes approximately 8  $\mu s$  to recover from positive saturation and approximately 6.5  $\mu s$  to recover from negative saturation.

Figure 5. Overdrive Recovery Time Test Circuit

Figure 4. Output Voltage Phase Reversal Behavior

REV. A -13-

#### **APPLICATIONS**

#### Single +3 V Supply, Instrumentation Amplifier

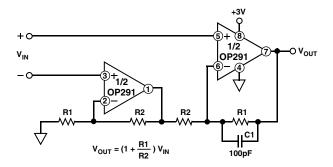

The OP291's low supply current and low voltage operation make it ideal for battery-powered applications such as the instrumentation amplifier shown in Figure 6. The circuit utilizes the classic two op amp instrumentation amplifier topology, with four resistors to set the gain. The equation is simply that of a noninverting amplifier as shown in the figure. The two resistors labeled R1 should be closely matched to each other as well as both resistors labeled R2 to ensure good common-mode rejection performance. Resistor networks ensure the closest matching as well as matched drifts for good temperature stability. Capacitor C1 is included to limit the bandwidth and, therefore, the noise in sensitive applications. The value of this capacitor should be adjusted depending on the desired closed-loop bandwidth of the instrumentation amplifier. The RC combination creates a pole at a frequency equal to  $1/(2 \pi \times R1C1)$ . If AC-CMRR is critical, than a matched capacitor to C1 should be included across the second resistor labeled R1.

Figure 6. Single +3 V Supply Instrumentation Amplifier

Because the OP291 accepts rail-to-rail inputs, the input common-mode range includes both ground and the positive supply of 3 V. Furthermore, the rail-to-rail output range ensures the widest signal range possible and maximizes the dynamic range of the system. Also, with its low supply current of 300  $\mu$ A/device, this circuit consumes a quiescent current of only 600  $\mu$ A, yet still exhibits a gain bandwidth of 3 MHz.

A question may arise about other instrumentation amplifier topologies for single-supply applications. For example, a variation on this topology adds a fifth resistor between the two inverting inputs of the op amps for gain setting. While that topology works well in dual-supply applications, it is inherently not appropriate for single-supply circuits. The same could be said for the traditional three op amp instrumentation amplifier. In both cases, the circuits simply will not work in single-supply situations unless a false ground between the supplies is created.

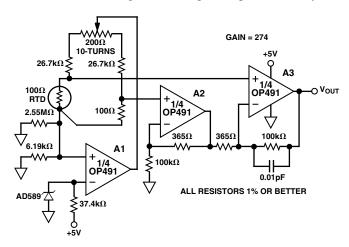

#### Single-Supply RTD Amplifier

The circuit in Figure 7 uses three op amps of the OP491 to develop a bridge configuration for an RTD amplifier that operates from a single +5 V supply. The circuit takes advantage of the OP491's wide output swing range to generate a high bridge excitation voltage of 3.9 V. In fact, because of the rail-to-rail output swing, this circuit will work with supplies as low as 4.0 V. Amplifier A1 servos the bridge to create a constant excitation current in conjunction with the AD589, a 1.235 V precision reference. The op amp maintains the reference voltage across the parallel combination of the 6.19 k $\Omega$  and 2.55  $M\Omega$  resistor, which generates a 200  $\mu$ A current source. This current splits evenly and flows through both halves of the bridge. Thus, 100  $\mu$ A flows through the RTD to generate an output voltage based on its resistance. A 3-wire RTD is used to balance the line resistance in both 100  $\Omega$  legs of the bridge to improve accuracy.

Figure 7. Single-Supply RTD Amplifier

Amplifiers A2 and A3 are configured in the two op amp IA discussed above. Their resistors are chosen to produce a gain of 274, such that each 1°C increase in temperature results in a 10 mV change in the output voltage, for ease of measurement. A 0.01  $\mu F$  capacitor is included in parallel with the 100  $k\Omega$  resistor on amplifier A3 to filter out any unwanted noise from this high gain circuit. This particular RC combination creates a pole at 1.6 kHz.

–14– REV. A

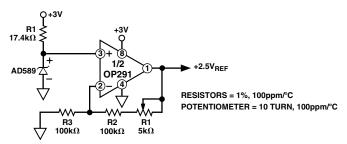

#### A +2.5 V Reference from a +3 V Supply

In many single-supply applications, the need for a 2.5 V reference often arises. Many commercially available monolithic 2.5 V references require at least a minimum operating supply voltage of 4 V. The problem is exacerbated when the minimum operating system supply voltage is +3 V. The circuit illustrated in Figure 8 is an example of a +2.5 V that operates from a single +3 V supply. The circuit takes advantage of the OP291's rail-to-rail input and output voltage ranges to amplify an AD589's 1.235 V output to +2.5 V. The OP291's low TCV $_{\rm OS}$  of 1  $\mu \text{V/}^{\circ}\text{C}$  helps maintain an output voltage temperature coefficient of less than 200 ppm/ $^{\circ}\text{C}$ . The circuit's overall temperature coefficient is dominated by R2 and R3's temperature coefficient. Lower tempco resistors are recommended. The entire circuit draws less than 420  $\mu \text{A}$  from a +3 V supply at 25°C.

Figure 8. A +2.5 V Reference that Operates on a Single +3 V Supply

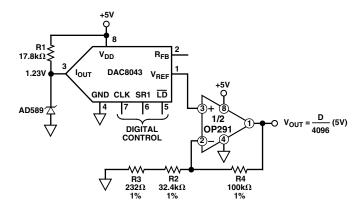

#### +5 V Only, 12-Bit DAC Swings Rail-to-Rail

The OP191 family is ideal for use with a CMOS DAC to generate a digitally controlled voltage with a wide output range. Figure 9 shows the DAC8043 used in conjunction with the AD589 to generate a voltage output from 0 V to 1.23 V. The DAC is actually operated in "voltage switching" mode where the reference is connected to the current output,  $I_{\rm OUT}$ , and the output voltage is taken from the  $V_{\rm REF}$  pin. This topology is inherently noninverting as opposed to the classic current output mode, which is inverting and, therefore, unsuitable for single supply.

Figure 9. +5 V Only, 12-Bit DAC Swings Rail-to-Rail

The OP291 serves two functions. First, it is required to buffer the high output impedance of the DAC's  $V_{REF}$  pin, which is on the order of  $10~k\Omega$ . The op amp provides a low impedance output to drive any following circuitry. Secondly, the op amp amplifies the output signal to provide a rail-to-rail output swing. In this particular case, the gain is set to 4.1 to generate a 5.0 V output when the DAC is at full scale. If other output voltage ranges are needed, such as 0 to 4.095, the gain can easily be adjusted by altering the value of the resistors.

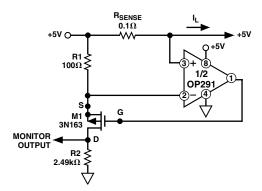

#### A High-Side Current Monitor

In the design of power supply control circuits, a great deal of design effort is focused on ensuring a pass transistor's long-term reliability over a wide range of load current conditions. As a result, monitoring and limiting device power dissipation is of prime importance in these designs. The circuit illustrated in Figure 10 is an example of a +5 V, single-supply high-side current monitor that can be incorporated into the design of a voltage regulator with fold-back current limiting or a high current power supply with crowbar protection. This design uses an OP291's rail-to-rail input voltage range to sense the voltage drop across a 0.1  $\Omega$  current shunt. A p-channel MOSFET used as the feedback element in the circuit converts the op amp's differential input voltage into a current. This current is then applied to R2 to generate a voltage that is a linear representation of the load current. The transfer equation for the current monitor is given by:

Monitor Output =

$$R2 \times \left(\frac{R_{SENSE}}{R1}\right) \times I_L$$

For the element values shown, the Monitor Output's transfer characteristic is 2.5 V/A.

Figure 10. A High-Side Load Current Monitor

REV. A –15–

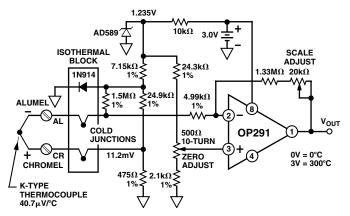

# A +3 V, Cold Junction Compensated Thermocouple Amplifier The OP291's low supply operation makes it ideal for +3 V battery-powered applications such as the thermocouple amplifier shown in Figure 11. The K-type thermocouple terminates in an isothermal block where the junctions' ambient temperature is continuously monitored using a simple 1N914 diode. The diode corrects the thermal EMF generated in the junctions by feeding a small voltage, scaled by the 1.5 M $\Omega$ and 475 $\Omega$ resistors, to the op amp.

To calibrate this circuit, immerse the thermocouple measuring junction in a 0°C ice bath, and adjust the 500  $\Omega$  pot to zero volts out. Next, immerse the thermocouple in a 250°C temperature bath or oven and adjust the Scale Adjust pot for an output voltage of 2.50 V. Within this temperature range, the K-type thermocouple is accurate to within  $\pm 3$ °C without linearization.

Figure 11. A 3 V, Cold Junction Compensated Thermocouple Amplifier

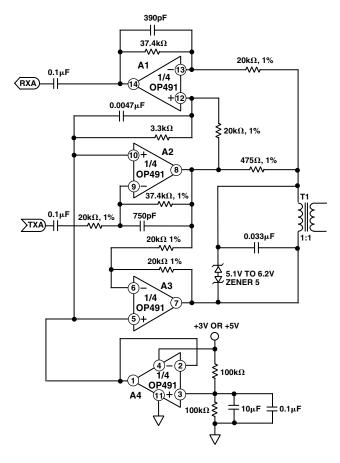

#### Single-Supply, Direct Access Arrangement for Modems

An important building block in modems is the telephone line interface. In the circuit shown in Figure 12, a direct access arrangement is utilized for transmitting and receiving data from the telephone line. Amplifier A1 is the receiving amplifier, and amplifiers A2 and A3 are the transmitters. The forth amplifier, A4, generates a pseudo ground half-way between the supply voltage and ground. This pseudo ground is needed for the ac coupled bipolar input signals.

The transmit signal, TXA, is inverted by A2 and then reinverted by A3 to provide a differential drive to the transformer, where each amplifier supplies half the drive signal. This is needed because of the smaller swings associated with a single supply as opposed to a dual supply. Amplifier A1 provides some gain for the received signal, and it also removes the transmit signal present at the transformer from the receive signal. To do this, the drive signal from A2 is also fed to the noninverting input of A1 to cancel the transmit signal from the transformer.

Figure 12. Single-Supply Direct Access Arrangement for Modems

The OP491's bandwidth of 3 MHz and rail-to-rail output swings ensures that it can provide the largest possible drive to the transformer at the frequency of transmission.

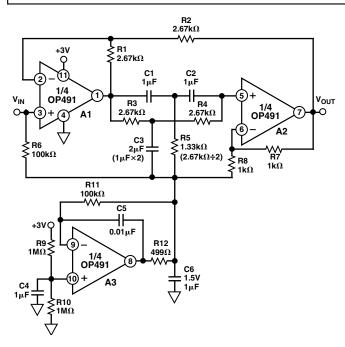

#### A +3 V, 50 Hz/60 Hz Active Notch Filter with False Ground

To process ac signals in a single-supply system, it is often best to use a false-ground biasing scheme. A circuit that uses this approach is illustrated in Figure 13. In this circuit, a false-ground circuit biases an active notch filter used to reject 50 Hz/60 Hz power line interference in portable patient monitoring equipment. Notch filters are quite commonly used to reject power line frequency interference which often obscures low frequency physiological signals, such as heart rates, blood pressure readings, EEGs, and EKGs. This notch filter effectively squelches 60 Hz pickup at a filter Q of 0.75. Substituting 3.16 k $\Omega$  resistors for the 2.67 k $\Omega$  resistors in the twin-T section (R1 through R5) configures the active filter to reject 50 Hz interference.

–16– REV. A

Figure 13. A +3 V Single-Supply, 50 Hz/60 Hz Active Notch Filter with False Ground

Amplifier A3 is the heart of the false-ground bias circuit. It simply buffers the voltage developed by R9 and R10 and is the reference for the active notch filter. Since the OP491 exhibits a rail-to-rail input common-mode range, R9 and R10 are chosen to split the +3 V supply symmetrically. An in-the-loop compensation scheme is used around the OP491 that allows the op amp to drive C6, a 1  $\mu F$  capacitor, without oscillation. C6 maintains a low impedance ac ground over the operating frequency range of the filter.

The filter section uses a pair of OP491s in a twin-T configuration whose frequency selectivity is very sensitive to the relative matching of the capacitors and resistors in the twin-T section. Mylar is the material of choice for the capacitors, and the relative matching of the capacitors and resistors determines the filter's passband symmetry. Using 1% resistors and 5% capacitors produces satisfactory results.

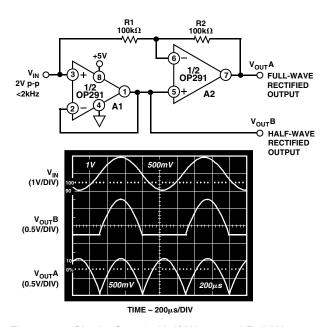

#### Single-Supply Half-Wave and Full-Wave Rectifiers

An OP191 family configured as a voltage follower operating on a single supply can be used as a simple half-wave rectifier in low-frequency (<2 kHz) applications. A full-wave rectifier can be configured with a pair of OP291s as illustrated in Figure 14. The circuit works in the following way: When the input signal is above 0 V, the output of amplifier A1 follows the input signal. Since the noninverting input of amplifier A2 is connected to Al's output, op amp loop control forces the A2's inverting input to the same potential. The result is that both terminals of R1 are equipotential; i.e., no current flows. Since there is no current flow in R1, the same condition exists upon R2; thus, the output of the circuit tracks the input signal. When the input signal is below 0 V, the output voltage of A1 is forced to 0 V. This condition now forces A2 to operate as an inverting voltage follower because the noninverting terminal of A2 is at 0 V as well. The output voltage at V<sub>OUT</sub>A is then a full-wave rectified version of the input signal. If needed, a buffered, half-wave rectified version of the input signal is available at V<sub>OUT</sub>B.

Figure 14. Single-Supply Half-Wave and Full-Wave Rectifiers Using an OP291

REV. A –17–

R10 16

98

10

```

* OP491 SPICE Macro-model

Rev. A, 5/94

* POLE AT 2.5 MHz

ARG/ADI

*

Copyright 1994 by Analog Devices, Inc.

G3

(12,39) 1E-6

98

18

R11

18

98

1E6

* Refer to "README.DOC" file for License Statement. Use of

C4

18

98

63.662E-15

* this model indicates your acceptance of the terms and pro-

* BIAS CURRENT-VS-COMMON-MODE VOLTAGE

* visions in the License Statement.

* Node assignments

EP

97

0

(99,0)1

VB

99

17

1.3

noninverting input

inverting input

RB

17

50

1E9

positive supply

E3

19

0

(15,17) 16

D13

19

20

DX

negative supply

output

R12

20

0

1E6

G4

98

21

(20,0) 1E-3

.SUBCKT OP491

99

R13

21

98

1

2

50

45

5E3

21

D14

22

DY

* INPUT STAGE

E4

97

22

(POLY(1) (99,98) -0.765 1

I1

99

7

8.06E-6

* POLE AT 100 MHz

Q1

6

4

7

QP

Q2

5

3

7

QP

G6

98

40

(18,39) 1E-6

3

99

R20

40

D1

DX

98

1E6

99

D2

4

DX

C10

40

98

1.592E-15

D3

3

4

DX

4

* OUTPUT STAGE

D4

3

DX

R1

3

8

5E3

109.375E3

R2

4

2

5E3

RS1

99

39

5

50

6.4654E3

39

50

109.375E3

R3

RS2

R4

6

50

6.4654E3

RO1

99

45

41.667

EOS

8

POLY(1) (16,39) -0.08E-3 1

RO2

45

50

41.667

1

99

(99,40) 24E-3

IOS

3

4

50E-12

G7

45

98

(21,98) 50E-9

G8

50

45

(40,50) 24E-3

GB1 3

GB2 4

98

(21,98) 50E-9

G9

98

60

(45,40) 24E-3

2

1E-12

D9

60

61

DX

CIN 1

D10 62

60

DX

* 1ST GAIN STAGE

V7

61

98

DC 0

DC 0

V8

98

62

EREF 98

0

(39,0)

FSY 99

50

POLY(2) V7 V8 0.207E-3 1 1

1

G1

98

9

(6,5)

31.667E-6

D11 41

45

9

R7

98

1E6

D12 45

42

D7

EC1 99

10

POLY(1) (99,39)

-0.52

V5

40

41

0.131

EC2

11

50

POLY(1) (39,50)

V6

42

40

0.131

-0.52

.MODEL DX D()

D5

10

DX

D6

9

DX

.MODEL DY D(IS=1E-9)

11

.MODEL DZ D(IS=1E-6)

* 2ND GAIN STAGE AND DOMINANT POLE AT 1.25 Hz

.MODEL QP PNP(BF=66.667)

.ENDS

G2

98

12

(9,39)

8E-6

R8

12

98

276.311E6

C2

12

98

16E-12

D7

12

13

DX

DX

D8

14

12

V1

99

13

0.58

V2

50

0.58

14

* COMMON-MODE STAGE

ECM 15

98

POLY(2) (1,39) (2,39) 0 0.5 0.5

15

16

1E6

```

–18– REV. A

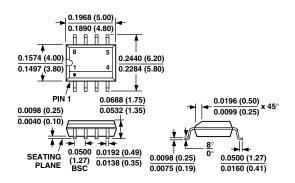

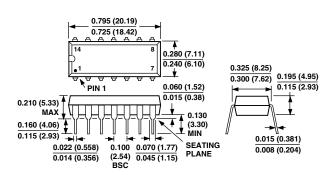

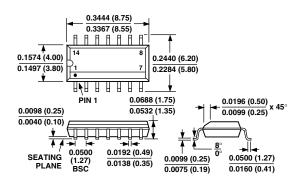

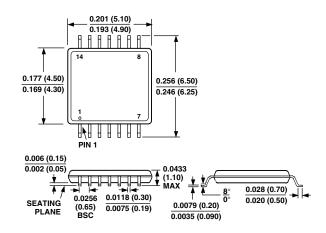

#### **OUTLINE DIMENSIONS**

Dimensions shown in inches and (mm).

#### 8-Lead Plastic DIP (N-8)0.430 (10.92) 0.348 (8.84) 0.280 (7.11) 0.240 (6.10) 0.325 (8.25) <u>\*</u> PIN 1 0.300 (7.62) 0.060 (1.52) 0.015 (0.38) <u>A</u> 0.195 (4.95) 0.210 (5.33) 0.115 (2.93) MAX. 0.160 (4.06) 0.015 (0.381) 0.022 (0.558) 0.100 0.070 (1.77) 0.014 (0.356) (2.54) BSC 0.045 (1.15) SEATING 0.008 (0.204)

8-Lead Narrow-Body SO (SO-8)

14-Lead Plastic DIP (N-14)

14-Lead Narrow-Body SO (R-14)

14-Lead TSSOP (RU-14)

REV. A -19-

# **Revision History**

| Location                                  |   |  |

|-------------------------------------------|---|--|

| Data Sheet changed from REV. 0 to REV. A. |   |  |

| Edits to GENERAL DESCRIPTION              | 1 |  |

| Edits to PIN CONFIGURATION                | 1 |  |

| Edits to ODERING GUIDE                    | 5 |  |

| Edits to DICE CHARACTERISTICS             |   |  |