## **LXT1000**

#### Gigabit Ethernet Transceiver

#### **Datasheet**

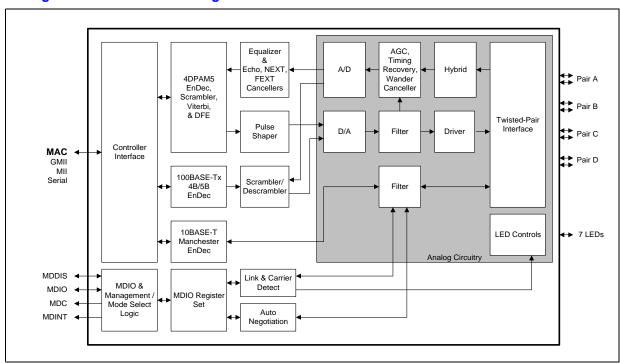

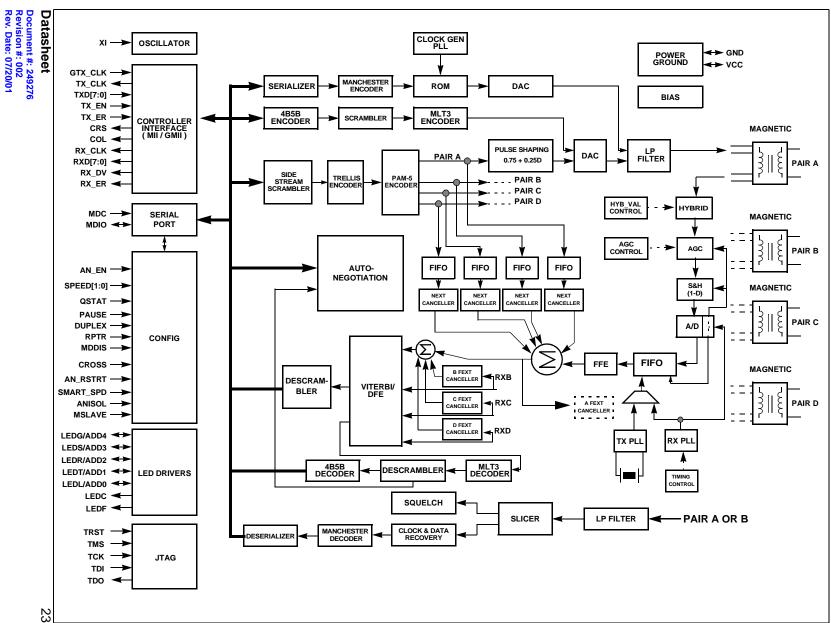

The LXT1000 transceiver supports Gigabit Ethernet over copper twisted-pair connections and supplies all of the physical layer (PHY) functions needed to interface a Gigabit Ethernet controller to a 100-meter CAT5 twisted-pair connection. The device incorporates Intel's high-efficiency Optimal Signal Processing (OSP<sup>™</sup>) technology, combining the best properties of digital and analog signal processing to produce a truly optimal device.

Featuring a GMII interface, 4DPAM5 encoder, scrambler, and 8B/10B encoder, Viterbi Decision Feedback Equalizer (DFE), DSP filtering for echo cancellation, equalization, and near- and farend crosstalk elimination, as well as gain control and timing recovery, the LXT1000 also includes an internal hybrid circuit combining the transmit and receive paths on each pair, allowing simple 1:1 turns ratio magnetics. LXT1000 complies with applicable portions of 802.3.

#### **Product Features**

- IEEE 802.3ab compliant.

- GMII and Ten-Bit Interface (TBI) MAC interface configurations.

- Integrated 10/100 transceiver with fallback support.

- Provides 802.3ab auto-negotiation for resolution of Master/Slave and flow-control (802.3x).

- MII management, QuickStatus, 7 LEDs, Interrupt.

- Supports 10 KB Jumbo Frames (full duplex).

- Supports carrier extension and packet bursting (half duplex).

- JTAG support.

- 3.3V power supply.

- Packaging: 492-Lead PBGA.

- Commercial Temperature Range, 0-55° C.

Order Number: 249276-002

July 2001

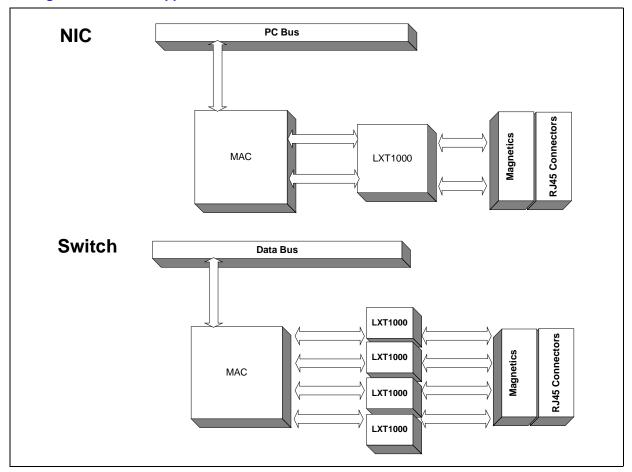

#### **Applications**

NICs

Switches

#### **Related Documents**

■ LXT1000 Gigabit Ethernet Transceiver Design and Layout Guide

Information in this document is provided in connection with Intel<sup>®</sup> products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The LXT1000 may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling 1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

Copyright © Intel Corporation, 2001

\*Third-party brands and names are the property of their respective owners.

2 Datasheet

| 1.0 | Ball | Assigni   | ments and Signal Descriptions                        | 12 |

|-----|------|-----------|------------------------------------------------------|----|

| 2.0 | Fund | ctional [ | Description                                          | 20 |

|     | 2.1  |           | ction                                                |    |

|     | 2.1  | 2.1.1     | Network Interface                                    |    |

|     |      | 2.1.1     | MAC Interface                                        |    |

|     |      | 2.1.2     | MDIO/MDC Interface (Management)                      |    |

|     |      | 2.1.3     |                                                      |    |

|     |      |           | Hardware Control Interface                           |    |

|     |      | 2.1.5     |                                                      |    |

|     |      | 2.1.6     | Initialization                                       |    |

|     |      | 2.1.7     | Link                                                 |    |

|     |      | 2.1.8     | Auto Negotiation                                     |    |

|     | 2.2  |           | 00 Applications                                      |    |

|     | 2.3  |           | ce Descriptions                                      |    |

|     |      | 2.3.1     | Network Interface                                    |    |

|     |      |           | 2.3.1.1 MDI/MDIX Configuration                       |    |

|     |      | 2.3.2     | MAC Data Interface                                   |    |

|     |      |           | 2.3.2.1 Modes of Operation                           |    |

|     |      |           | 2.3.2.2 GMII Mode (1000 BASE-T)                      |    |

|     |      |           | 2.3.2.3 MII Mode (10/100BASE-T)                      | 27 |

|     |      |           | 2.3.2.4 Serial Mode (10BASE-T)                       |    |

|     |      |           | 2.3.2.5 Test Loopback                                | 28 |

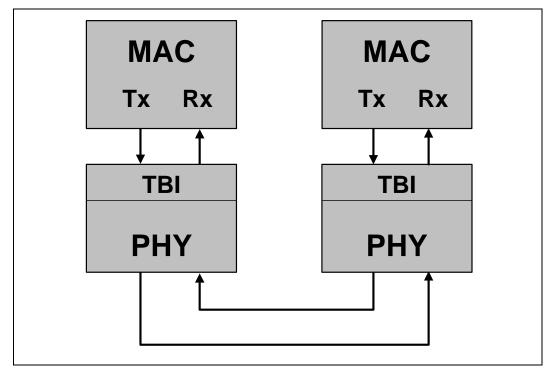

|     |      | 2.3.3     | TBI Configuration (1000BASE-T Only)                  |    |

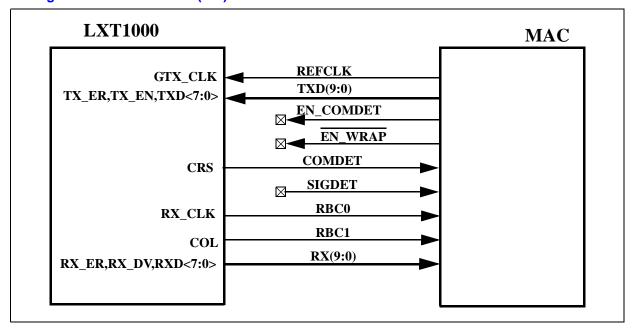

|     |      | 2.3.4     | TBI Communication Between MAC and PHY                |    |

|     |      |           | 2.3.4.1 Transmit Mode – Data Traffic from MAC to PHY |    |

|     |      |           | 2.3.4.2 Receive Mode – Data Traffic from PHY to MAC  |    |

|     |      | 2.3.5     | MAC Data Interface Control                           |    |

|     |      | 2.3.6     | MDIO/MDC Management Interface                        | 31 |

|     |      |           | 2.3.6.1 Interrupts                                   |    |

|     |      | 2.3.7     | Hardware Control Interface                           | 33 |

|     |      | 2.3.8     | Quick Status Interface                               | 34 |

|     |      | 2.3.9     | LED Functions                                        | 35 |

|     |      |           | 2.3.9.1 Link Up                                      | 35 |

|     |      |           | 2.3.9.2 Link Down                                    |    |

|     |      |           | 2.3.9.3 LED Options                                  |    |

|     |      |           | 2.3.9.4 PHY Address Determination                    |    |

|     |      | 2.3.10    | JTAG Boundary Scan Interface                         | 37 |

|     |      |           | 2.3.10.1State Machine                                |    |

|     |      |           | 2.3.10.2Instruction Register                         | 37 |

|     |      |           | 2.3.10.3Boundary Scan Register                       |    |

|     | 2.4  | Initializ | ation                                                |    |

|     |      | 2.4.1     | Power-Up                                             |    |

|     |      | 2.4.2     | Hardware Reset                                       |    |

|     |      | 2.4.3     | Software Reset                                       |    |

|     |      | 2.4.4     | Hardware Power-Down                                  |    |

|     |      | 2.4.5     | Software Power-Down                                  |    |

|     |      | 2.4.6     | Determining Link State                               |    |

|     |      | ∠.4.∪     | DOLO                                                 |    |

|     |        | 2.4.6.1 False Link                                                |       |

|-----|--------|-------------------------------------------------------------------|-------|

|     |        | 2.4.6.2 Auto-Negotiation                                          |       |

|     |        | 2.4.6.3 Parallel Detection                                        |       |

|     |        | 2.4.6.4 Forced Operation                                          |       |

|     | 2.4.7  | Establishing and Maintaining the Link                             |       |

|     |        | 2.4.7.1 1000BASE-T                                                |       |

|     |        | 2.4.7.2 100BASE-TX                                                |       |

|     |        | 2.4.7.3 10BASE-T                                                  |       |

|     | 2.4.8  | Taking Down the Link                                              |       |

|     | 2.4.9  | Link Enhancements                                                 |       |

|     |        | 2.4.9.1 SmartSpeed                                                |       |

|     |        | 2.4.9.2 Auto-Negotiate Isolation                                  |       |

|     |        | 2.4.9.3 Flow Control                                              |       |

|     | 2.4.10 | Link Speed Changes                                                |       |

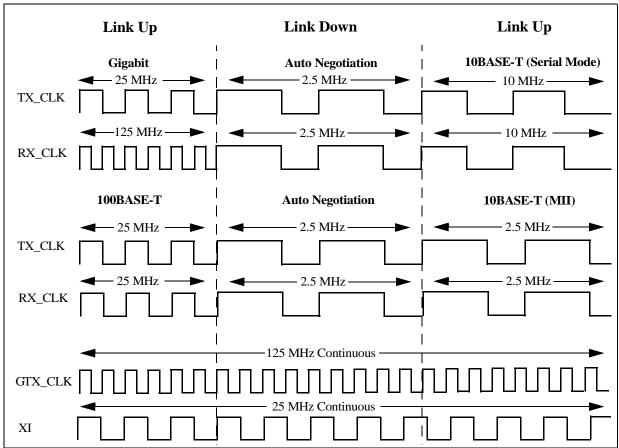

|     |        | 2.4.10.1How Link Speed Changes Affect MAC Interface Clock Signals |       |

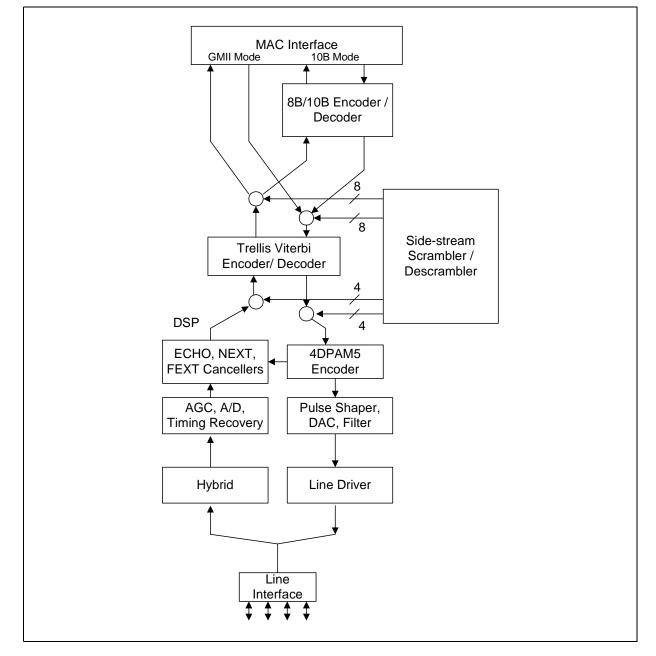

| 2.5 | 1000 M | lbps Operation                                                    |       |

|     | 2.5.1  | Introduction                                                      |       |

|     | 2.5.2  | Transmit Functions                                                |       |

|     |        | 2.5.2.1 8B/10B Decoder                                            | . 48  |

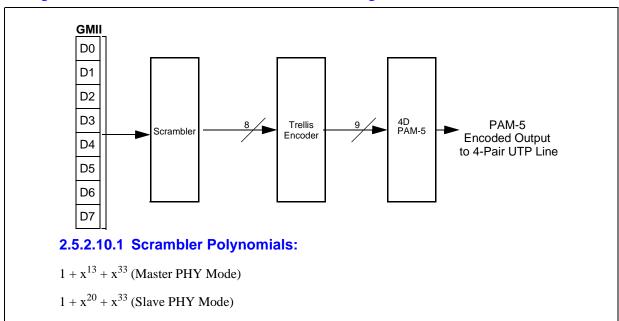

|     |        | 2.5.2.2 Scrambler                                                 |       |

|     |        | 2.5.2.3 Transmit FIFO                                             |       |

|     |        | 2.5.2.4 Transmit Phase-Locked Loop PLL                            |       |

|     |        | 2.5.2.5 Trellis Encoder                                           |       |

|     |        | 2.5.2.6 4DPAM5 Encoder                                            |       |

|     |        | 2.5.2.7 Spectral Shaper                                           | .49   |

|     |        | 2.5.2.8 Low-Pass Filter                                           |       |

|     |        | 2.5.2.9 Line Driver                                               |       |

|     |        | 2.5.2.10Transmit/Receive Flow                                     |       |

|     | 2.5.3  | Receive Functions                                                 |       |

|     |        | 2.5.3.1 Hybrid                                                    |       |

|     |        | 2.5.3.2 Automatic Gain Control                                    |       |

|     |        | 2.5.3.3 Timing Recovery                                           | .50   |

|     |        | 2.5.3.4 Analog-to-Digital Converter                               | .50   |

|     |        | 2.5.3.5 Digital Signal Processor                                  |       |

|     |        | 2.5.3.6 Descrambler                                               | . D I |

|     |        | 2.5.3.8 4DPAM5 Decoder                                            |       |

|     |        | 2.5.3.9 8B/10B Encoder                                            |       |

|     | 2.5.4  | Supported Operations                                              |       |

|     | 2.5.4  | 2.5.4.1 Operation Details                                         | .01   |

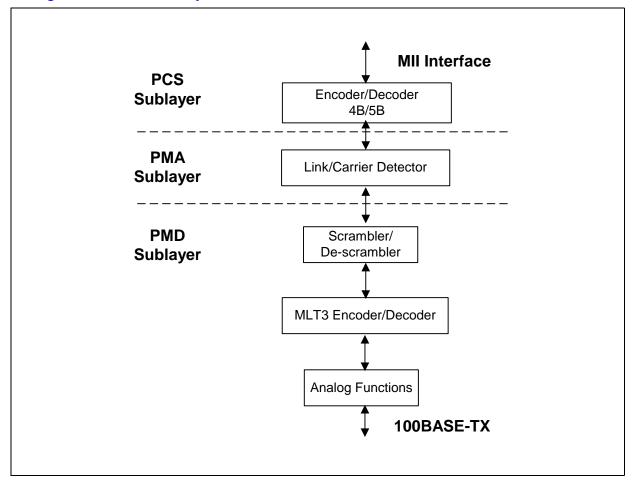

| 2.6 | 100 M  | pps Operation                                                     |       |

| 2.6 |        | • •                                                               |       |

|     | 2.6.1  | Protocol Support                                                  |       |

|     | 2.6.2  | Digital Functions                                                 |       |

|     |        | 2.6.2.1 4B/5B Encoder                                             |       |

|     |        | 2.6.2.2 Scrambler                                                 |       |

|     |        | 2.6.2.3 MLT3 Encoder                                              |       |

|     |        | 2.6.2.4 Link and Carrier Detector                                 |       |

|     | 262    |                                                                   |       |

|     | 2.6.3  | Analog Functions                                                  |       |

|     |        | 2.6.3.1 Transmitting/Receiving                                    |       |

|     |        | 2.6.3.2 Collision Detection                                       |       |

|     |        | 2.6.3.4 Error Handling                                            |       |

|     |        | 2.0.0.7 LITOI Handing                                             | . 00  |

|     | 2.7  | 10 Mbps Operation                                   | 62 |

|-----|------|-----------------------------------------------------|----|

|     |      | 2.7.1 Transmitting/Receiving                        | 63 |

|     |      | 2.7.2 Polarity Correction                           | 63 |

|     |      | 2.7.3 Link Test                                     | 63 |

|     |      | 2.7.4 Link Failure                                  | 63 |

|     |      | 2.7.5 SQE (Heartbeat)                               | 63 |

|     |      | 2.7.6 Jabber                                        | 64 |

|     |      | 2.7.7 Preamble Generation Mode                      |    |

|     | 2.8  | LXT1000 Operating Requirements                      | 64 |

|     |      | 2.8.1 Power                                         |    |

|     |      | 2.8.2 Clock                                         |    |

|     |      | 2.8.3 RBIAS                                         |    |

|     |      | 2.8.4 GBIAS                                         | 65 |

| 3.0 | App  | olication Information                               | 66 |

|     | 3.1  | Design Recommendations                              | 66 |

|     |      | 3.1.1 Device Placement                              |    |

|     |      | 3.1.2 Ground Plane Layout                           | 66 |

|     |      | 3.1.3 Power Plane Layout and Filtering              |    |

|     |      | 3.1.3.1 Decoupling Capacitors                       |    |

|     |      | 3.1.4 RBIAS and GBIAS Requirements                  |    |

|     |      | 3.1.5 Twisted-Pair Layout                           | 67 |

|     |      | 3.1.6 MAC Interface Layout                          | 67 |

|     |      | 3.1.7 5V Tolerance Considerations                   | 67 |

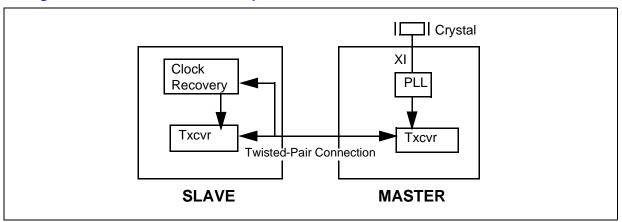

|     |      | 3.1.8 Master/Slave Relationship Details             | 68 |

|     |      | 3.1.8.1 Configuring Master/Slave in Software        |    |

|     |      | 3.1.8.2 Configuring Master/Slave in Hardware        |    |

|     |      | 3.1.8.3 Resolution of the Master/Slave Relationship |    |

|     | 3.2  | Test Information                                    |    |

|     |      | 3.2.1 Forced Gig Operation                          |    |

|     |      | 3.2.2 Gigabit Transmit Test Clock                   |    |

|     |      | 3.2.3 Scrambler/Encoder Disable (100M)              |    |

|     | 3.3  | Magnetics Information                               |    |

|     | 3.4  | Component Manufacturers                             |    |

|     | 3.5  | Typical Application Circuitry                       |    |

|     |      | 3.5.1 Typical NIC Application                       | /2 |

| 4.0 | Test | t Specifications                                    | 75 |

|     | 4.1  | 1000BASE-T Timing Parameters                        | 78 |

|     | 4.2  | 100BASE-TX Timing Parameters                        |    |

|     | 4.3  | 10BASE-T Timing Parameters                          |    |

|     | 4.4  | Auto-Negotiation Timing Parameters                  | 87 |

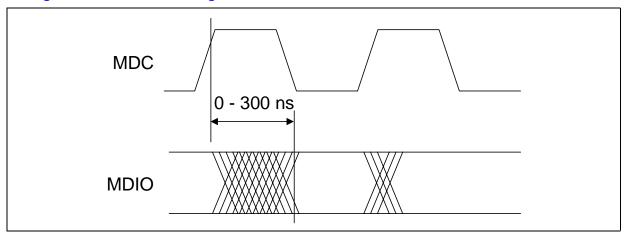

|     | 4.5  | MDIO Timing Parameters                              |    |

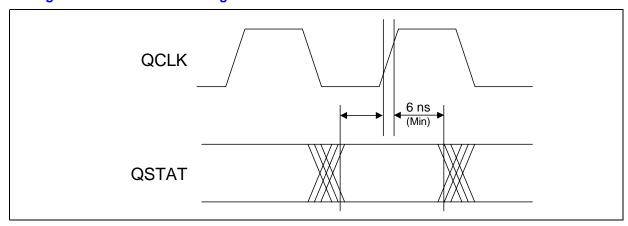

|     | 4.6  | OSTAT Timing Parameters                             | 89 |

| 5.0     | Regi | ister Set                                                                              | 90    |

|---------|------|----------------------------------------------------------------------------------------|-------|

| 6.0     | Mec  | hanical Specification                                                                  | 105   |

| Α       | Orde | ering Information                                                                      | . 106 |

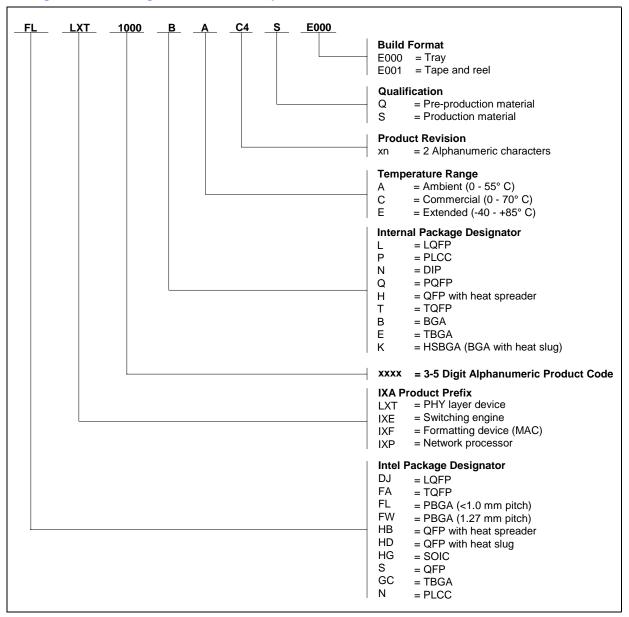

| Figures |      |                                                                                        |       |

| •       | 1    | LXT1000 Block Diagram                                                                  | 11    |

|         | 2    | LXT1000 PBGA Assignments                                                               |       |

|         | 3    | LXT1000 Applications                                                                   |       |

|         | 4    | LXT1000 Block Diagram                                                                  |       |

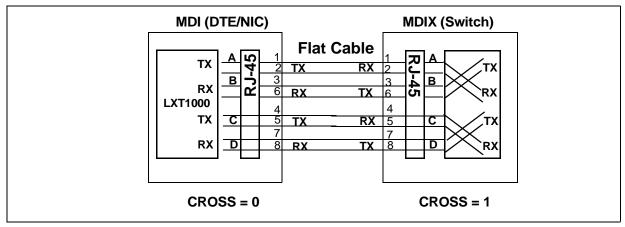

|         | 5    | Crossover Function                                                                     |       |

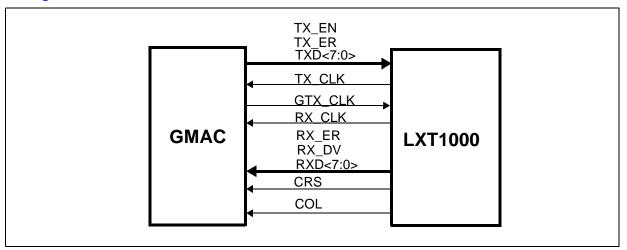

|         | 6    | GMII Data Interface                                                                    | 27    |

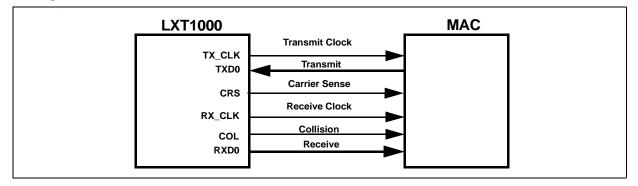

|         | 7    | Serial Interface                                                                       | 28    |

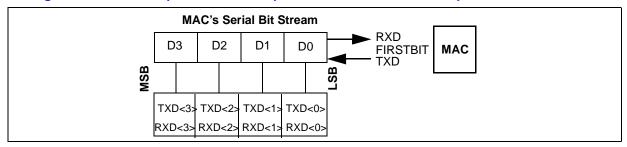

|         | 8    | Relationship between 10 Mbps Serial Interface and 10 Mbps MII Interface                |       |

|         | 9    | 10-Bit Interface (TBI)                                                                 |       |

|         | 10   | Data Flow Between PHY and Mac                                                          |       |

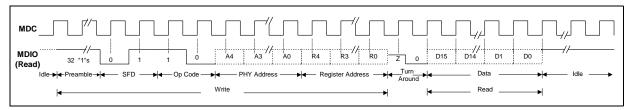

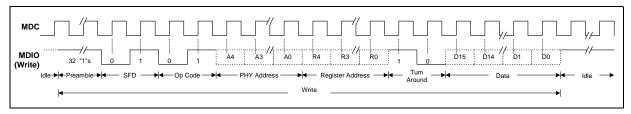

|         | 11   | MDIO Read Frame Format                                                                 | 32    |

|         | 12   | MDIO Write Frame Format                                                                | 32    |

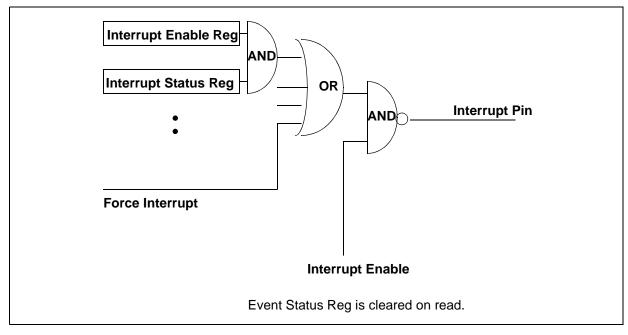

|         | 13   | Interrupt Handling                                                                     | 33    |

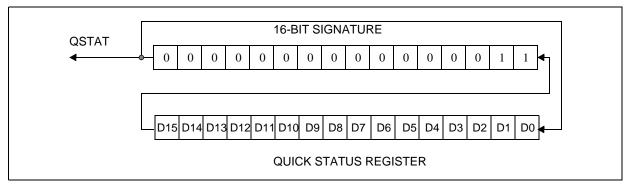

|         | 14   | Quick Status Register                                                                  |       |

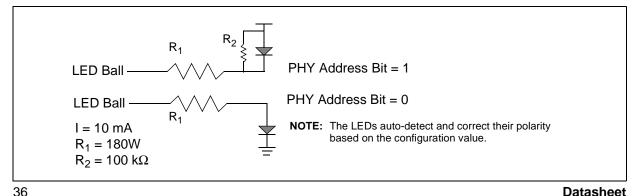

|         | 15   | PHY Address Determination via LED balls                                                | 36    |

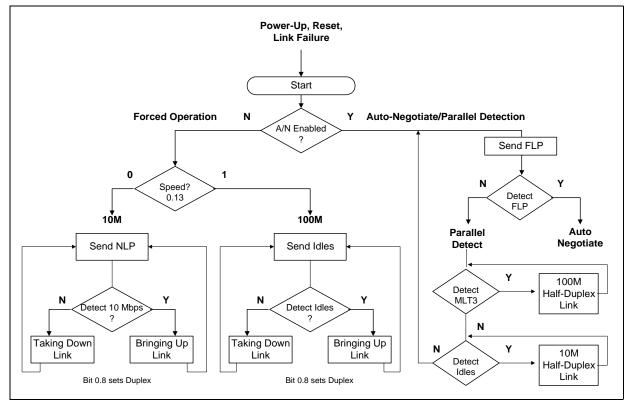

|         | 16   | Overview of Link Establishment                                                         | 40    |

|         | 17   | Link Speed and Corresponding Clock Frequency Changes                                   | 46    |

|         | 18   | 1000BASE-T Functions Overview                                                          | 47    |

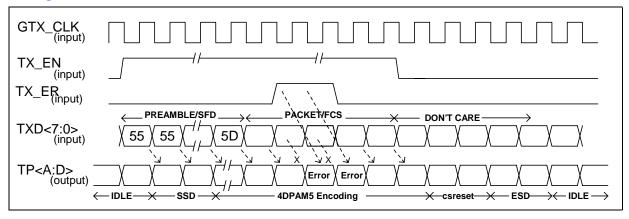

|         | 19   | 1000BASE-T Transmit Flow and Line Coding Scheme                                        | 49    |

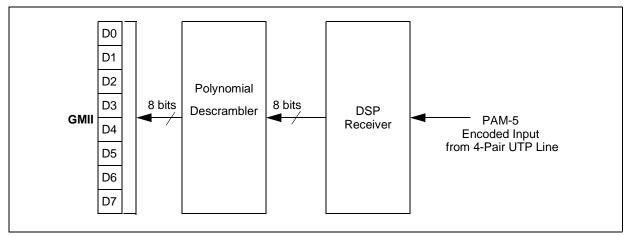

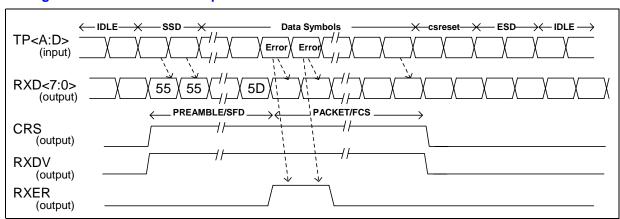

|         | 20   | 1000BASE-T Receive Flow                                                                | 50    |

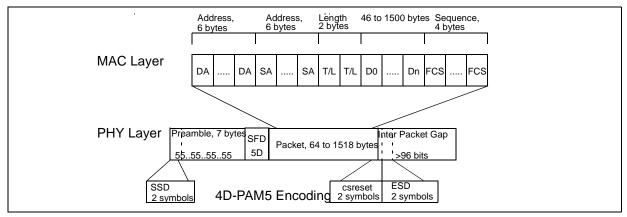

|         | 21   | 1000BASE-T Frame Structure                                                             | 52    |

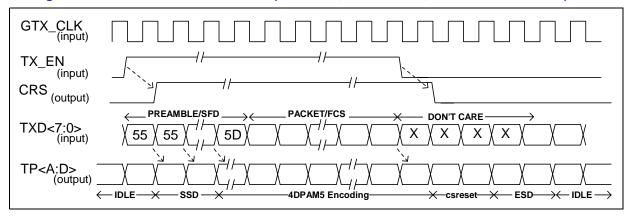

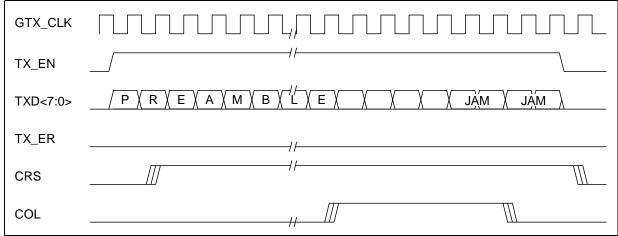

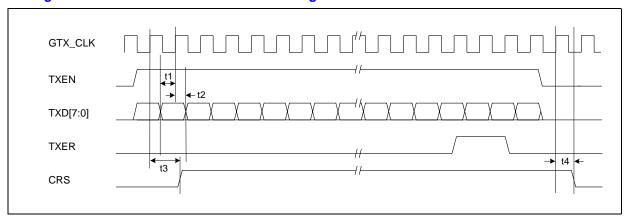

|         | 22   | 1000BASE-T Transmission (No Errors, No Collision, No Carrier Extension)                | 53    |

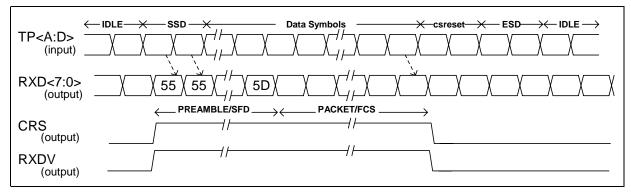

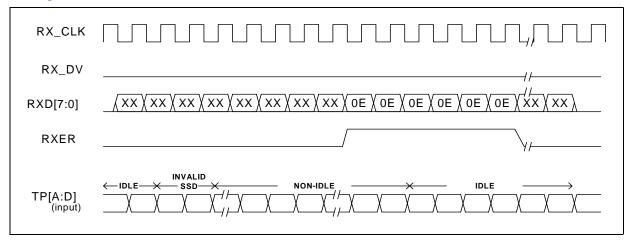

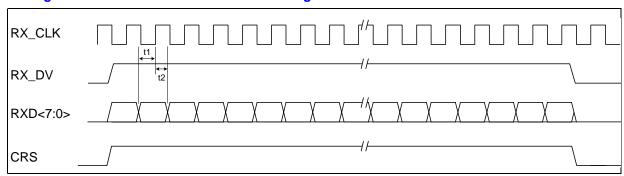

|         | 23   | 1000BASE-T Reception (No Errors, No Collision, No Carrier Extension)                   | 53    |

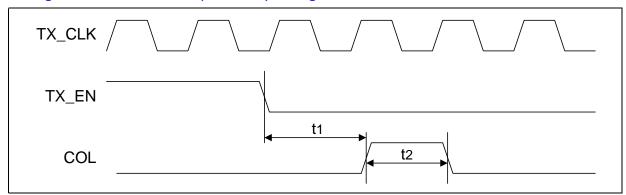

|         | 24   | 1000BASE-T Transmission with Collision                                                 | 53    |

|         | 25   | 1000BASE-T False Carrier Detection                                                     | 54    |

|         | 26   | 1000BASE-T Transmission with Error                                                     | 54    |

|         | 27   | 1000BASE-T Reception with Error                                                        | 55    |

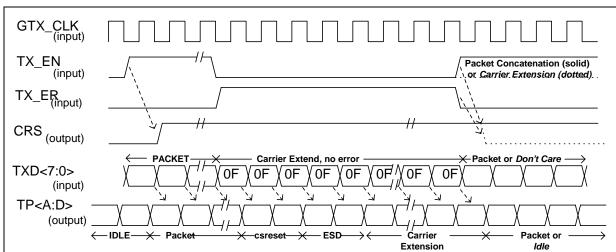

|         | 28   | 1000BASE-T Transmission, Carrier Extend and Packet Concatenation                       |       |

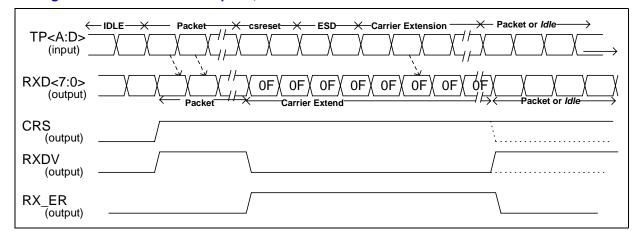

|         | 29   | 1000BASE-T Reception, Carrier Extension and Packet Concatenation                       | 56    |

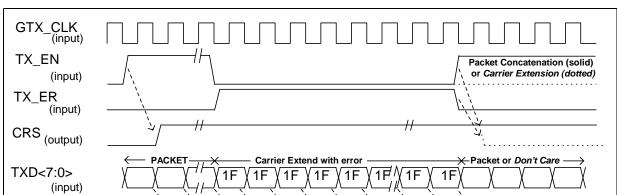

|         | 30   | 1000BASE-T Transmission Extend - Packet Concatenation and Carrier Extens with Errors57 |       |

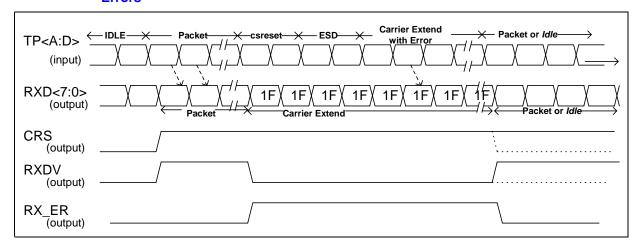

|         | 31   | 1000BASE-T Reception Extend - Packet Concatenation and Carrier Extension with Errors57 |       |

|         | 32   | Protocol Sublayers and Associated Functions                                            | 58    |

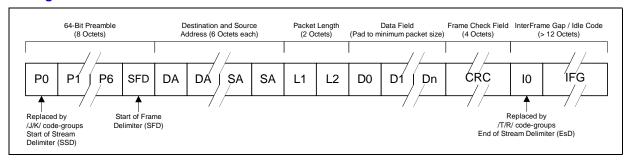

|         | 33   | 100BASE-TX Frame Structure                                                             | 60    |

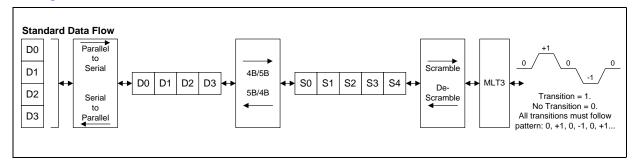

|         | 34   | 100BASE-TX Data Flow                                                                   |       |

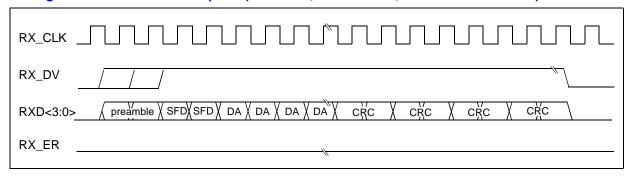

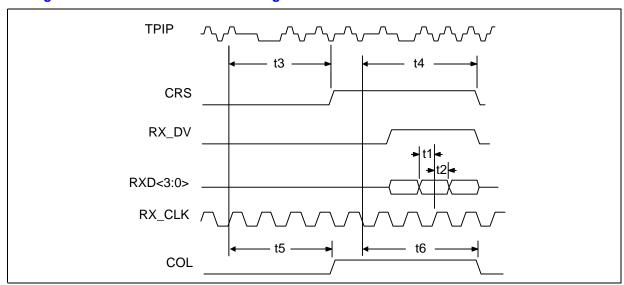

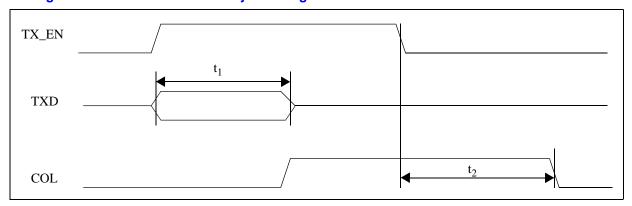

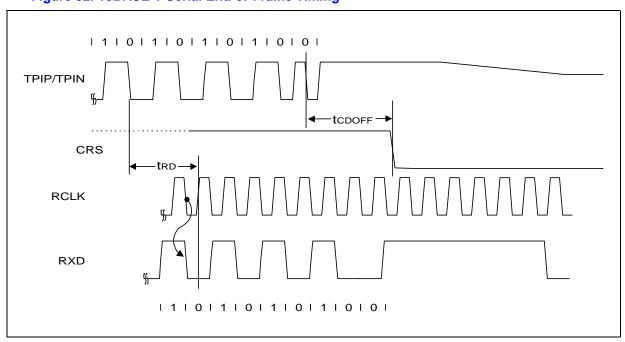

|         | 36   | 100BASE-T Reception (No Errors, No Collision, No Carrier Extension)                    | 62    |

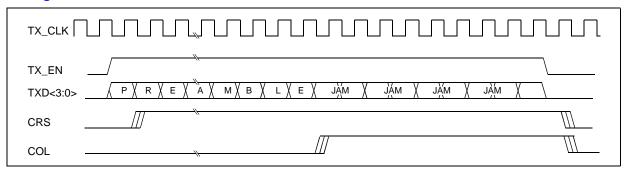

|         | 37   | 100BASE-TX Transmission with Collision                                                 |       |

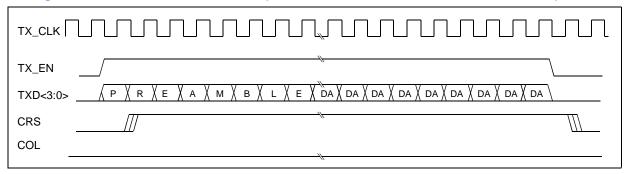

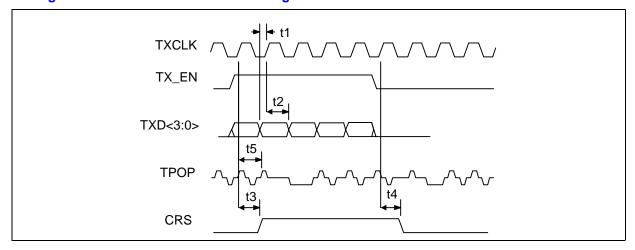

|         | 35   | 100BASE-T Transmission (No Errors, No Collision, No Carrier Extension)                 | 62    |

|         | 38   | Master/Slave Relationship                                                              | 68    |

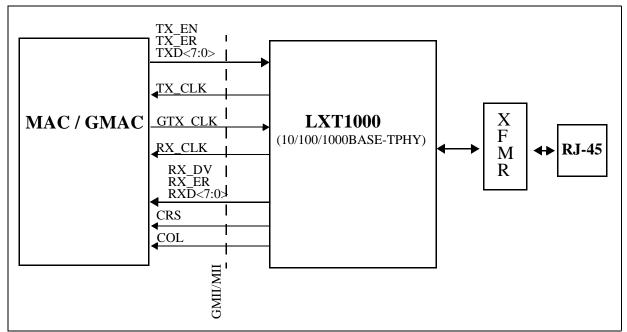

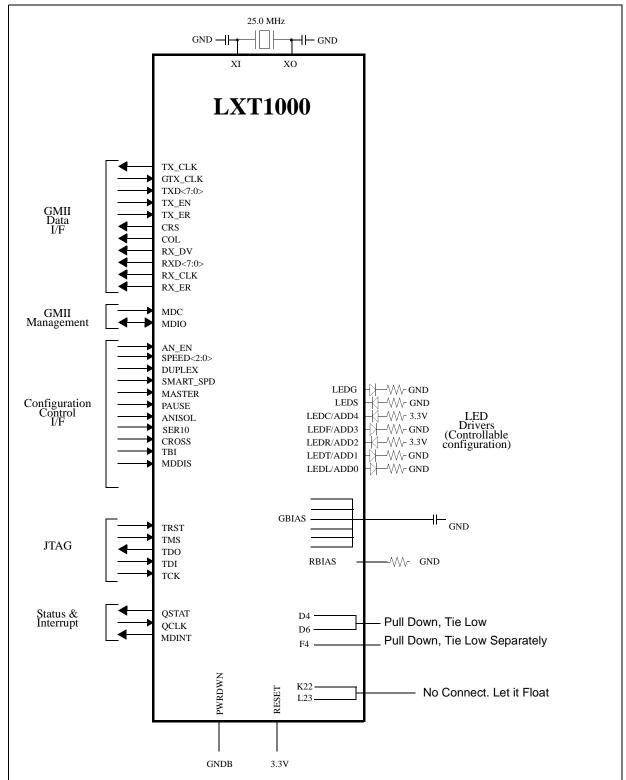

|         | 39   | Typical MII/GMII Interface                                                             | 72    |

|         | 40   | Typical Configuration - GMII Interface                                                 | 73    |

**Tables**

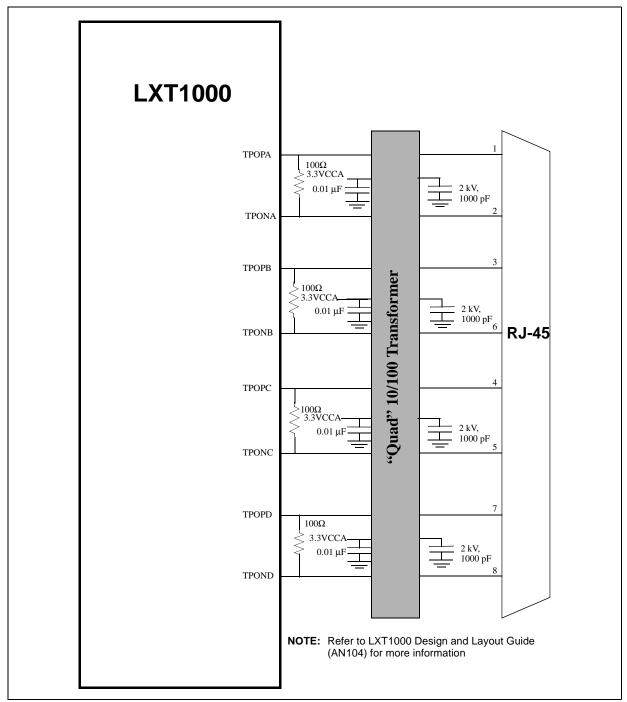

| 41       | NIC Application - Twisted-Pair Interface                                            | 74 |

|----------|-------------------------------------------------------------------------------------|----|

| 42       | 1000BASE-T GMII Transmit Timing                                                     | 78 |

| 43       | 1000BASE-T GMII Receive Timing                                                      | 79 |

| 44       | 100BASE-TX Transmit Timing                                                          |    |

| 45       | 100BASE-TX Receive Timing                                                           | 81 |

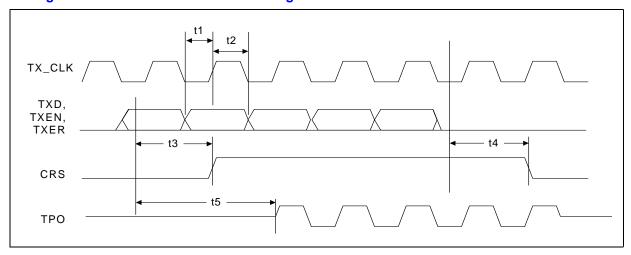

| 46       | 10BASE-T MII Transmit Timing                                                        | 82 |

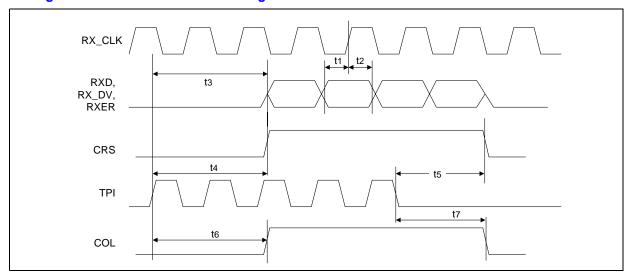

| 47       | 10BASE-T Receive Timing                                                             |    |

| 48       | 10BASE-T SQE (Heartbeat) Timing                                                     |    |

| 49       | 10BASE-T Jab and Unjab Timing                                                       |    |

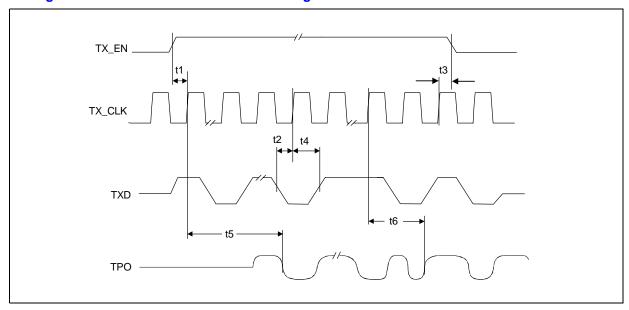

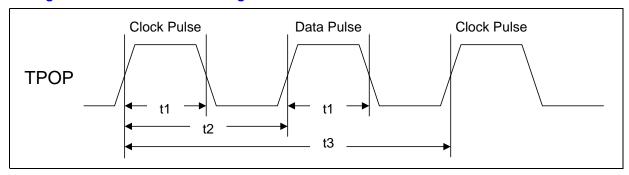

| 50       | 10BASE-T Serial Transmit Timing                                                     |    |

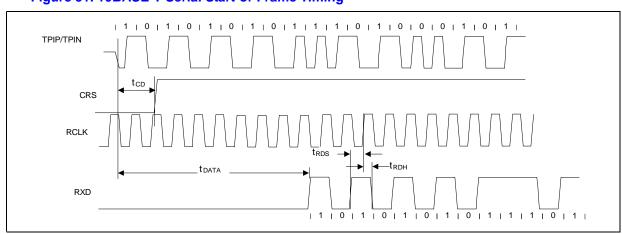

| 51       | 10BASE-T Serial Start-of-Frame Timing                                               |    |

| 52       | 10BASE-T Serial End-of-Frame Timing                                                 |    |

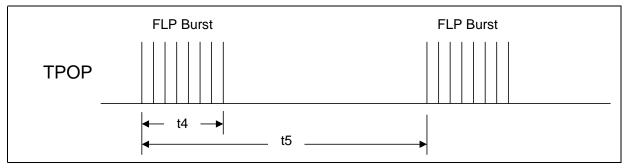

| 53       | Fast Link Pulse Timing                                                              |    |

| 54       | FLP Burst Timing                                                                    |    |

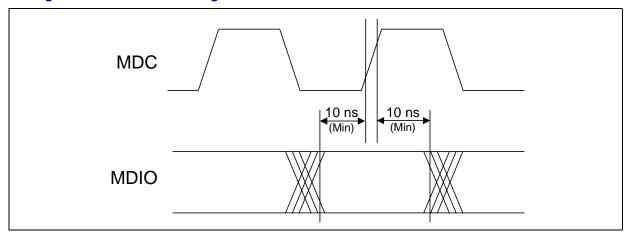

| 55       | MDIO Write Timing                                                                   |    |

| 56       | MDIO Read Timing                                                                    |    |

| 57<br>50 | QSTAT Write Timing                                                                  |    |

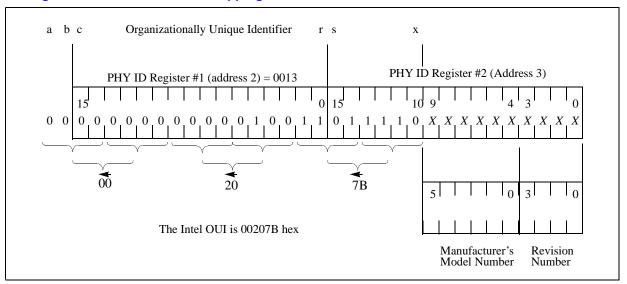

| 58       | PHY Identifier Bit Mapping                                                          |    |

| 59<br>60 | Preliminary PBGA Package Specification  Ordering Information - Sample               |    |

|          |                                                                                     |    |

| 1 2      | Signal Type AbbreviationsLXT1000 GMII Signal Descriptions                           |    |

| 3        | LXT1000 Givin Signal DescriptionsLXT1000 Twisted-Pair Interface Signal Descriptions |    |

| 4        | LXT1000 Configuration Signal Descriptions                                           |    |

| 5        | LXT1000 LED Indicator Configuration Signal Descriptions                             |    |

| 6        | LXT1000 Miscellaneous Signal Descriptions                                           |    |

| 8        | LXT1000 Power Supply Signal Descriptions                                            |    |

| 7        | LXT1000 Boundary Scan Signal Descriptions                                           |    |

| 9        | Mapping of Twisted-Pair Outputs to RJ-45s                                           |    |

| 10       | Crossover Control and Automatic Detection                                           |    |

| 11       | MAC Interface Modes of Operation                                                    | 25 |

| 12       | MAC Interface Transmit Signal Mapping                                               | 26 |

| 13       | MAC Interface Receive Signal Mapping                                                |    |

| 14       | Test Loopback Operation                                                             | 28 |

| 15       | Configuring the LXT1000 via Hardware Control Interface                              |    |

| 16       | LED Status Indication / PHY Addressing                                              |    |

| 17       | Boundary Scan Supported Instructions                                                |    |

| 18       | BSR Mode of Operation                                                               |    |

| 19       | JTAG ID Register                                                                    |    |

| 20       | Initialization Modes                                                                |    |

| 21       | Determining Duplex State via Parallel Detection                                     |    |

| 22       | Transmission Pattern If Link Is Down                                                |    |

| 23       | Pause and Asymmetric Pause Settings                                                 |    |

| 24<br>25 | 4B/5B Coding                                                                        | 60 |

|          | Configuring Moster/Clave Relationship                                               | 00 |

| 25<br>26 | Configuring Master/Slave Relationship                                               |    |

| 28 | Component Manufacturers                                                    |        |

|----|----------------------------------------------------------------------------|--------|

| 29 | Absolute Maximum Ratings                                                   | 75     |

| 30 | Operating Conditions                                                       | 75     |

| 31 | GMII DC Specifications                                                     | 75     |

| 32 | GMII General AC Specifications                                             | 76     |

| 33 | Other Digital I/O Characteristics1                                         | 76     |

| 34 | Required Clock Characteristics                                             | 77     |

| 35 | 1000BASE-T Transceiver Characteristics                                     | 77     |

| 36 | 100BASE-TX Transceiver Characteristics                                     | 77     |

| 37 | 10BASE-T Transceiver Characteristics                                       | 78     |

| 38 | 10BASE-T Link Integrity Timing Characteristics                             | 78     |

| 39 | 1000BASE-T GMII Transmit Timing Parameters                                 | 79     |

| 40 | 1000BASE-T GMII Receive Timing Parameters                                  | 79     |

| 41 | GMII - 100BASE-TX Transmit Timing Parameters / 4B Mode                     | 80     |

| 42 | GMII - 100BASE-TX Receive Timing Parameters / 4B Mode                      | 81     |

| 43 | GMII - 10BASE-T Transmit Timing Parameters                                 | 82     |

| 44 | GMII - 10BASE-T Receive Timing Parameters                                  | 83     |

| 45 | 10BASE-T SQE (Heartbeat) Timing Parameters                                 | 84     |

| 46 | 10BASE-T Jab and Unjab Timing Parameters                                   |        |

| 47 | 10BASE-T Serial Transmit Timing                                            |        |

| 48 | 10BASE-T Serial Start-of-Frame Timing                                      | 86     |

| 49 | 10BASE-T Serial End-of-Frame Timing                                        | 86     |

| 50 | Fast Link Pulse Timing Parameters                                          |        |

| 51 | MDIO Timing Parameters                                                     | 8      |

| 52 | QSTAT Timing Parameters                                                    | 89     |

| 53 | Register Set                                                               | 90     |

| 54 | Control Register (Address 0)                                               | 91     |

| 55 | Status Register (Address 1)                                                | 92     |

| 56 | PHY Identification Register 1 (Address 2)                                  | 92     |

| 57 | PHY Identification Register 2 (Address 3)                                  | 93     |

| 58 | Auto-Negotiation Advertisement Register (Address 4)1                       | 93     |

| 59 | Auto-Negotiation Link-Partner Base Page Ability Register (Address 5)       | 94     |

| 60 | Auto-Negotiation Expansion Register (Address 6)                            | 95     |

| 61 | Auto-Negotiation Next Page Transmit Register (Address 7)                   | 96     |

| 62 | Auto-Negotiation Link Partner Received Next Page Ability Register (Addi 96 | ess 8) |

| 63 | 1000BASE-T/100BASE-T2 Control Register (Address 9 )1                       | 97     |

| 64 | 1000BASE-T/100BASE-T2 Status Register (Address 10)                         |        |

| 65 | Extended Status Register (Address 15)                                      | 98     |

| 66 | Port Configuration Register (Address 16)                                   |        |

| 67 | Quick Status Register (Address 17)                                         |        |

| 68 | Interrupt Enable Register (Address 18)                                     |        |

| 69 | Interrupt Status Register (Address 19)                                     |        |

| 70 | LED Configuration Register (Address 20)                                    |        |

| 71 | Port Control Register (Address 21)                                         |        |

| 72 | Product Information                                                        |        |

# Revision History

| Revision | Date      | Page # | Description                                                                                                                                                                         |  |  |  |  |  |  |  |

|----------|-----------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

|          |           | 28     | Add "Test Loopback" to the Functional Description section.                                                                                                                          |  |  |  |  |  |  |  |

|          |           | 71     | Add footnote to Table 27 in the Applications Information section referring to return loss test conditions.                                                                          |  |  |  |  |  |  |  |

| 002      | July 2001 | 75     | Add a footnote to Table 29 and Table 30 in the Test Specifications section referring to LXT1000 Application Note Thermal Design Considerations Application Note for further detail. |  |  |  |  |  |  |  |

|          |           | 76     | Changed Output Set-up Time and Output Hold Time values from Maximums to Minimums in Table 32.                                                                                       |  |  |  |  |  |  |  |

|          |           | 93     | Add a footnote to Table 58 and Table 68 in the Register Set section referring to Auto-Negotiation and Registers 4 and 9.                                                            |  |  |  |  |  |  |  |

|          |           | 106    | Add Appendix A, "Ordering Information".                                                                                                                                             |  |  |  |  |  |  |  |

Figure 1. LXT1000 Block Diagram

## 1.0 Ball Assignments and Signal Descriptions

Figure 2. LXT1000 PBGA Assignments

|    | 1   | 2            | 3          | 4          | 5          | 6    | 7    | 8    | 9     | 10   | 11    | 12    | 13    | 14    | 15     | 16   | 17          | 18    | 19   | 20   | 21         | 22                  | 23            | 24     | 25  | 26  |    |

|----|-----|--------------|------------|------------|------------|------|------|------|-------|------|-------|-------|-------|-------|--------|------|-------------|-------|------|------|------------|---------------------|---------------|--------|-----|-----|----|

| Α  | gnd | gnd          | gnd        | gnd        | gnd        | gnd  | gnd  | gnd  | gnd   | gnd  | gnd   | gnd   | gnd   | gnd   | gnd    | gnd  | gnd         | gnd   | gnd  | gnd  | gnd        | gnd                 | gnd           | gnd    | gnd | gnd | Α  |

| В  | gnd | gnd          | gnd        | gnd        | gnd        | gnd  | gnd  | gnd  | rxd5  | vccd | rxd7  | vccd  | gbias | gnd   | rx_clk | gnd  | gtx_cl<br>k | gnd   | p/d  | gnd  | maste<br>r | gnd                 | gnd           | gnd    | gnd | gnd | В  |

| С  | gnd | gnd          | gnd        | gnd        | gnd        | gnd  | gnd  | rxd3 | gnd   | rxd6 | gnd   | rx_dv | gnd   | gbias | gnd    | vccd | gnd         | tx_er | gnd  | txd7 | gnd        | qstat               | gnd           | gnd    | gnd | gnd | С  |

| D  | gnd | gnd          | gnd        | p/d        | gnd        | p/d  | rxd1 | gnd  | gbias | gnd  | gbias | gbias | gnd   | gnd   | gnd    | gnd  | tx_clk      | gnd   | qclk | gnd  | txd5       | gnd                 | gnd           | gnd    | gnd | gnd | D  |

| E  | gnd | gnd          | gnd        | gnd        | gnd        | rxd0 | vccd | rxd2 | gnd   | rxd4 | gnd   | gbias | rx_er | gnd   | col    | crs  | gnd         | tx_en | gnd  | txd6 | gnd        | gnd                 | gnd           | gnd    | gnd | gnd | Е  |

| F  | gnd | gnd          | gnd        | p/d        | gnd        | vccd | vccd | vccd | vccd  | vccd |       |       |       |       |        |      | vccd        | vccd  | vccd | vccd | vccd       | gnd                 | txd3          | gnd    | gnd | gnd | F  |

| G  | gnd | mdc          | gnd        | speed<br>0 | gnd        | vccd |      |      |       |      |       |       |       |       |        |      |             |       |      |      | vccd       | txd4                | gnd           | gnd    | gnd | gnd | G  |

| н  | gnd | gnd          | speed<br>2 | gnd        | speed<br>1 | vccd |      |      |       |      |       |       |       |       |        |      |             |       |      |      | vccd       | gnd                 | txd2          | gnd    | gnd | gnd | н  |

| J  | gnd | p/d          | gnd        | gnd        | mdio       | vccd |      |      |       |      |       |       |       |       |        |      |             |       |      |      | vccd       | txd1                | gnd           | txd0   | gnd | gnd | J  |

| к  | gnd | gnd          | mdint      | gnd        | an_en      | vccd |      |      |       |      |       |       |       |       |        |      |             |       |      |      | vccd       | gnd                 | nc2           | gnd    | gnd | gnd | к  |

| L  | gnd | an_rst<br>rt | gnd        | gnd        | mddis      |      |      |      |       |      | gnd   | gnd   | gnd   | gnd   | gnd    | gnd  |             |       |      |      |            | gnd                 | nc1           | gnd    | gnd | gnd | L  |

| М  | gnd | gnd          | gnd        | tms        | gnd        |      |      |      |       |      | gnd   | gnd   | gnd   | gnd   | gnd    | gnd  |             |       |      |      |            | ser10               | gnd           | anisol | gnd | gnd | М  |

| N  | gnd | gnd          | tdi        | gnd        | tck        |      |      |      |       |      | gnd   | gnd   | gnd   | gnd   | gnd    | gnd  |             |       |      |      |            | gnd                 | reset         | gnd    | gnd | gnd | N  |

| Р  | gnd | trst         | gnd        | tdo        | gnd        |      |      |      |       |      | gnd   | gnd   | gnd   | gnd   | gnd    | gnd  |             |       |      |      |            | vcca                | gnd           | gnd    | gnd | gnd | Р  |

| R  | gnd | gnd          | gnd        | gnd        | gnd        |      |      |      |       |      | gnd   | gnd   | gnd   | gnd   | gnd    | gnd  |             |       |      |      |            | gnd                 | smart<br>_spd | gnd    | gnd | gnd | R  |

| т  | gnd | gnd          | gnd        | gnd        | gnd        |      |      |      |       |      | gnd   | gnd   | gnd   | gnd   | gnd    | gnd  |             |       |      |      |            | cross               | vcca          | gnd    | gnd | gnd | т  |

| U  | gnd | gnd          | gnd        | ledl       | ledt       | vcca |      |      |       |      |       |       |       |       |        |      |             |       |      |      | vcca       | pwrdw<br>n          | gnd           | tbi    | gnd | gnd | U  |

| v  | gnd | gnd          | gnd        | vcca       | gnd        | gnd  |      |      |       |      |       |       |       |       |        |      |             |       |      |      | gnd        | vcca                | gnd           | gnd    | gnd | gnd | ٧  |

| w  | gnd | gnd          | gnd        | ledr       | gnd        | ledf |      |      |       |      |       |       |       |       |        |      |             |       |      |      | vcca       | gnd                 | gnd           | gnd    | gnd | gnd | w  |

| Y  | gnd | gnd          | gnd        | gnd        | vcca       | leds |      |      |       |      |       |       |       |       |        |      |             |       |      |      | gnd        | duplex/tx<br>_tclkn | gnd           | gnd    | gnd | gnd | Υ  |

| AA | gnd | gnd          | gnd        | ledc       | ledg       | vcca | gnd  | gnd  | gnd   | vcca |       |       |       |       |        |      | gnd         | gnd   | gnd  | gnd  | vcca       | pause/tx_<br>tclkp  | gnd           | хо     | gnd | gnd | AA |

| АВ | gnd | gnd          | gnd        | gnd        | vcca       | gnd  | gnd  | gnd  | gnd   | gnd  | gnd   | vcca  | gnd   | rbias | gnd    | gnd  | vcca        | gnd   | gnd  | gnd  | vcca       | gnd                 | gnd           | gnd    | gnd | gnd | АВ |

| AC | gnd | gnd          | gnd        | gnd        | gnd        | gnd  | gnd  | gnd  | gnd   | gnd  | gnd   | gnd   | vcca  | gnd   | gnd    | gnd  | gnd         | gnd   | gnd  | gnd  | gnd        | gnd                 | xi            | gnd    | gnd | gnd | AC |

| AD | gnd | gnd          | gnd        | gnd        | gnd        | gnd  | gnd  | gnd  | gnd   | gnd  | gnd   | gnd   | vcca  | vcca  | gnd    | gnd  | gnd         | gnd   | gnd  | gnd  | gnd        | gnd                 | gnd           | gnd    | gnd | gnd | AD |

| AE | gnd | gnd          | gnd        | gnd        | gnd        | gnd  | gnd  | gnd  | gnd   | gnd  | gnd   | gnd   | vcca  | gnd   | gnd    | gnd  | gnd         | gnd   | gnd  | gnd  | gnd        | gnd                 | gnd           | gnd    | gnd | gnd | AE |

| AF | gnd | gnd          | gnd        | vcca       | tpap       | tpan | vcca | vcca | tpbn  | tpbp | vcca  | gnd   | gnd   | gnd   | vcca   | tpcp | tpcn        | vcca  | vcca | tpdn | tpdp       | vcca                | gnd           | gnd    | gnd | gnd | AF |

|    | 1   | 2            | 3          | 4          | 5          | 6    | 7    | 8    | 9     | 10   | 11    | 12    | 13    | 14    | 15     | 16   | 17          | 18    | 19   | 20   | 21         | 22                  | 23            | 24     | 25  | 26  |    |

| -  |     |              | l.         | l.         |            |      |      |      |       |      |       |       |       |       |        |      | 1           |       |      | ı    |            |                     |               |        |     |     |    |

**Table 1. Signal Type Abbreviations**

| Symbol | Signal Type                 | Definition                                                                                     |

|--------|-----------------------------|------------------------------------------------------------------------------------------------|

| I      | Input                       | Standard input-only signal.                                                                    |

| LHR    | Input<br>Latched, L-H Reset | Latched on Low-to-High edge of RESET; ignored thereafter.                                      |

| MD     | Input,<br>Latched, MDDIS    | Latched on Low-to-High edge of RESET; used thereafter only if Manual Control mode (MDDIS) = 1. |

| 0      | Output                      | Standard output-only signal.                                                                   |

| I/O    | Bidirectional               | Input and output signal.                                                                       |

| Α      | Analog                      | Current source signal.                                                                         |

| PD     | Pull Down                   | Pull down signal. Tie Low.                                                                     |

| PU     | Pull Up                     | Pull up signal.                                                                                |

| N/C    | No Connect                  | Do not connect.                                                                                |

Table 2. LXT1000 GMII Signal Descriptions

| Ball #                                               | Symbol                                                  | Type <sup>1</sup> Description |                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |

|------------------------------------------------------|---------------------------------------------------------|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

|                                                      | MAC Data Interface <sup>2</sup> - 1000/100/10 Operation |                               |                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |

| C20<br>E20<br>D21<br>G22<br>F23<br>H23<br>J22<br>J24 | TXD7 TXD6 TXD5 TXD4 TXD3 TXD2 TXD1 TXD0                 | ı                             | Transmit Data Bus. The width of this synchronous input bus varies with the speed/mode:  1000: All 8 bits are used.  100 or 10 MII: TXD<3:0> are used; TXD<7:4> are ignored.  10 Serial: TXD<0> is monitored; TXD<7:1> are ignored.                                                            |  |  |  |  |  |  |  |

| E18                                                  | TX_EN                                                   | 1                             | <b>Transmit Enable.</b> This synchronous input indicates that valid data is being driven on the TXD bus.                                                                                                                                                                                      |  |  |  |  |  |  |  |

| D17                                                  | TX_CLK                                                  | 0                             | Transmit Clock. All transmit inputs must be synchronized to this output clock during 10/100 operation. It is provided as a utility clock during 1000 operation. Its frequency depends on the link speed/mode:  100/1000 Mbps: 25 MHz  10 MII and Auto-negotiation: 2.5 MHz  10 Serial: 10 MHz |  |  |  |  |  |  |  |

| B17                                                  | GTX_CLK                                                 | I                             | Gigabit Transmit Clock. 125 MHz input clock; all transmit inputs must be synchronized to this clock during 1000 operation.                                                                                                                                                                    |  |  |  |  |  |  |  |

| C18                                                  | TX_ER                                                   | I                             | <b>Transmit Coding Error.</b> This synchronous input causes the transmission of error symbols in 1000/100 links. For half-duplex 1000 links, it will cause the generation of carrier-extension symbols when properly synchronized with TX_EN (refer to 1000 Mbps operation section).          |  |  |  |  |  |  |  |

<sup>1.</sup> I/O Column Coding: I = Input, O = Output 2. Complies with IEEE 802.3, Clauses 35.(GMII) and 22 (MII); Modes 1000 (GMII), 100 (MII), 10 (MII or Serial), Autonegotiation.

3. Complies with IEEE 802.3, Clause 36. NOTE: This section is an alternate listing of previously described pins.

Table 2. LXT1000 GMII Signal Descriptions (Continued)

| Ball #                                                       | Symbol                                                       | Type <sup>1</sup> | Description                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

|--------------------------------------------------------------|--------------------------------------------------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| B11<br>C10<br>B9<br>E10<br>C8<br>E8<br>D7<br>E6              | RXD7<br>RXD6<br>RXD5<br>RXD4<br>RXD3<br>RXD2<br>RXD1<br>RXD0 | 0                 | Receive Data Bus. The width of this synchronous output bus varies with speed/mode: 1000: All 8 bits are driven. 100 and 10 MII mode: RXD<3:0> are driven; RXD<7:4> are held Low. 10 Serial: RXD<0> is driven; RXD<7:1> are held Low.                                          |  |  |  |  |  |  |

| C12                                                          | RX_DV                                                        | 0                 | Receive Data Valid. This synchronous output is asserted when valid data is driven on RXD.                                                                                                                                                                                     |  |  |  |  |  |  |

| E13                                                          | RX_ER                                                        | 0                 | <b>Receive Error</b> . For 1000 operation, this output is asserted when error symbols or carrier-extension symbols are received. For 100 operation, it is asserted when error symbols are received. For 10 operation, it is not asserted. It is always synchronous to RX_CLK. |  |  |  |  |  |  |

| B15                                                          | RX_CLK                                                       | 0                 | Receive Clock. This output clock is used to synchronize the receive output signals. I frequency depends upon the link speed:  1000: 125 MHz  100: 25 MHz (35/65 duty cycle)  10 MII or Auto-negotiation: 2.5 MHz  10 Serial: 10 MHz                                           |  |  |  |  |  |  |

| E15                                                          | COL                                                          | 0                 | <b>Collision.</b> This asynchronous output is asserted when a collision is detected (applies to half-duplex links only). In full-duplex mode, this output is forced Low.                                                                                                      |  |  |  |  |  |  |

| E16                                                          | CRS                                                          | 0                 | Carrier Sense. This asynchronous output is asserted when data is detected at the twisted-pair interface.                                                                                                                                                                      |  |  |  |  |  |  |

|                                                              | •                                                            | MAC Data          | a Interface - TBI Configuration <sup>3</sup> - 1000-Only Operation                                                                                                                                                                                                            |  |  |  |  |  |  |

| C20, E20,<br>D21, G22,<br>F23, H23,<br>J22, J24,<br>E18, C18 | TXD<9:0>                                                     | I                 | Transmit Data Bus. This input bus must be synchronized to GTX_CLK.                                                                                                                                                                                                            |  |  |  |  |  |  |

| D17                                                          | TX_CLK                                                       | 0                 | Transmit Clock. 25 MHz output. Not used; provided as a utility.                                                                                                                                                                                                               |  |  |  |  |  |  |

| B17                                                          | GTX_CLK                                                      | 1                 | Gigabit Transmit Clock. 125 MHz input clock                                                                                                                                                                                                                                   |  |  |  |  |  |  |

| B11, C10,<br>B9, E10,<br>C8, E8, D7,<br>E6, C12,<br>E13      | RXD<9:0>                                                     | 0                 | Receive Data Bus. This output data bus is synchronized to RBC0/RBC1.                                                                                                                                                                                                          |  |  |  |  |  |  |

| B15, E15                                                     | RBC0, RBC1                                                   | 0                 | <b>Receive Clocks</b> . Two 62.5 MHz output clocks are provided at these outputs. RBC0 is 180 degrees (8 ns = 1/2 period delay) with respect to RBC1.                                                                                                                         |  |  |  |  |  |  |

| E16                                                          | COMDET                                                       | 0                 | Comma Detect. Toggles when comma sequence is detected in the receive data stream.                                                                                                                                                                                             |  |  |  |  |  |  |

<sup>1.</sup> I/O Column Coding: I = Input, O = Output

2. Complies with IEEE 802.3, Clauses 35.(GMII) and 22 (MII); Modes 1000 (GMII), 100 (MII), 10 (MII or Serial), Autonegotiation.

3. Complies with IEEE 802.3, Clause 36. NOTE: This section is an alternate listing of previously described pins.

Table 2. LXT1000 GMII Signal Descriptions (Continued)

| Ball # | Symbol                 | Type <sup>1</sup> | Description                                                                                                                    |  |  |  |

|--------|------------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|        | GMII Control Interface |                   |                                                                                                                                |  |  |  |

| G2     | MDC                    | I                 | Management Data Clock. Clock for the MDIO serial data channel. Maximum frequency is 2.5 MHz.                                   |  |  |  |

| J5     | MDIO                   | I/O               | Management Data Input/Output. Bidirectional serial data channel for communication between the PHY and the management function. |  |  |  |

- 1. I/O Column Coding: I = Input, O = Output 2. Complies with IEEE 802.3, Clauses 35.(GMII) and 22 (MII); Modes 1000 (GMII), 100 (MII), 10 (MII or Serial), Autonegotiation.

- 3. Complies with IEEE 802.3, Clause 36. NOTE: This section is an alternate listing of previously described pins.

Table 3. LXT1000 Twisted-Pair Interface Signal Descriptions

| Ball #                                            | Symbol                                               | Type <sup>1</sup>        | Description                                                                                                                                                                                                                                                                     |  |  |

|---------------------------------------------------|------------------------------------------------------|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| AF5, AF6,<br>AF10,AF9<br>AF16,AF17,<br>AF21, AF20 | TPAP, TPAN<br>TPBP, TPBN<br>TPCP, TPCN<br>TPDP, TPDN | I/O<br>I/O<br>I/O<br>I/O | <b>Twisted-Pair A - D, Positive and Negative.</b> For 1000BASE-T operation, all four pair are both input and output at the same time. For 100BASE-TX and 10BASE-T operation, only TPAP/TPAN and TPBP/TPBN are used. The device automatically configures input and output pairs. |  |  |

| 1. I/O Column                                     | 1. I/O Column Coding: I = Input, O = Output          |                          |                                                                                                                                                                                                                                                                                 |  |  |

Table 4. LXT1000 Configuration Signal Descriptions

| Ball #   | Symbol                     | Type <sup>1</sup> | Description <sup>2</sup>                                                                                                                                                                                                                                                           |

|----------|----------------------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | SPEED2<br>SPEED1<br>SPEED0 |                   | <b>Speed Select.</b> These inputs determine the LXT1000's operating speed. When the MAC Interface is used in a TBI configuration, they must be set as follows: High, Low, Low (advertise 1000BASE-T only).                                                                         |

| H3<br>H5 |                            | I, MD             | When the MAC Interface is used in a GMII configuration, their function varies depending on whether auto-negotiation is enabled. When auto-negotiation is enabled, each signal, when High, enables advertising of a specific speed via the corresponding bits in the MII Registers: |

| G4       |                            |                   | SPEED<2> = 1000 (9.9, 9.8)<br>SPEED<1> = 100 (4.7, 4.8)<br>SPEED<0> = 10 (4.5, 4.6)                                                                                                                                                                                                |

|          |                            |                   | When auto-negotiation is disabled by tying AN_EN Low, SPEED<0> forces the speed via MII Bit 0.13 to either 10 (= 0) or 100 (=1). SPEED<2:1> should be tied Low.                                                                                                                    |

|          | AN_EN                      | LHR               | <b>Auto Negotiation Enable.</b> This input sets the power-on state of MII Register Bit 0.12, which controls Auto-Negotiation. Normally, this input should be tied High.                                                                                                            |

| K5       |                            |                   | When High, auto-negotiation is enabled. When Low, auto-negotiation is disabled.                                                                                                                                                                                                    |

<sup>1.</sup> I/O Column Coding: LHR = Input, Latched on Low-to-High edge of RESET (ignored thereafter); I, MD = Input, Latched on Low-to-High edge of RESET, used thereafter only if Manual Control mode (MDDIS = 1).

**Datasheet** 15

<sup>2.</sup> MAC Interface Operating modes: GMII (1000 Mbps), MII (10 or 100 Mbps), Serial (10 Mbps).

Table 4. LXT1000 Configuration Signal Descriptions (Continued)

| Ball # | Symbol            | Type <sup>1</sup> | Description <sup>2</sup>                                                                                                                                                                                                               |

|--------|-------------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        |                   |                   | <b>Duplex Mode.</b> When 21.15 = 0 (default), this input controls the duplex state of the link. Its exact function varies depending on the state of AN_EN. For TBI configurations, this input should be tied High.                     |

| Y22    | DUPLEX/           | I, MD             | When AN_EN is High, this bit enables advertising of full-duplex capabilities. (Bits 9.9, 4.8, and 4.6 are set High if the corresponding SPEED is also High).                                                                           |

|        | TX_TCLKN          |                   | When AN_EN is Low, this bit directly forces duplex state through MII bit 0.8; Low = half duplex; High = full duplex.                                                                                                                   |

|        |                   | 0                 | TX_TCLKN (Transmit Jitter Test Clock). The internal 125 MHz clock used to transmit data is output as a differential signal on Y22 and AA22 when 21.15 = 1.                                                                             |

| L2     | AN_RSTRT          | I, MD             | Restart Auto Negotiation. A positive edge on AN_RSTRT restarts the Autonegotiation process. This signal controls the MII Control Register bit 0.9. AN_RSTRT is relevant only when AN_EN is High.                                       |

| R23    | SMART_SPD         | LHR               | Smart Speed Select. When High, this input enables SmartSpeed control. SMART_SPD drives bit 16.7 (see "SmartSpeed" on page 43).                                                                                                         |

| AA22   | PAUSE/            | I, MD             | Pause Configuration. When 21.15 = 0 (default), this input determines the settings of Pause (4.10) and ASM_DIR (4.11) during auto-negotiation. If this input is High, both bits are set High; if Low, both are disabled.                |

|        | TX_TCLKP          | 0                 | <b>TX_TCLKP (Transmit Jitter Test Clock)</b> . The internal 125 MHz clock used to transmit data is output as a differential signal on Y22 and AA22 when 21.15 = 1.                                                                     |

|        |                   | I, MD             | Master/Slave Configuration. This configuration sets Port Type bit 9.10, which indicates the Gigabit Master/Slave configuration. The default configuration, bit 9.12, interprets this setting as the preferred, but not required, mode. |

| B21    | MASTER            |                   | High = Master (multi-port) configuration (Transmitter driven from local clock source).                                                                                                                                                 |

|        |                   |                   | Low = Slave (single-port) configuration. (Transmitter driven from recovered clock).                                                                                                                                                    |

|        |                   | 0 1 MD            | <b>Crossover Selection.</b> Determines TPAP/N and TPBP/N operation during autonegotiation and 10/100 operation. Crossover Selection is not used during 1000 operation.                                                                 |

| T22    | CROSS             |                   | When High, TPAP/N is an input; TPBP/N is an output (Switch configuration).                                                                                                                                                             |

| 122    | CROSS             | I, MD             | When Low, TPAP/N is an output; TPBP/N is an input (NIC/DTE configuration).                                                                                                                                                             |

|        |                   |                   | When set to mid-level voltage or left open, the device automatically determines correct operation. Changing the state of this input generates an internal reset, resulting in a new auto-negotiation cycle.                            |

| M24    | ANISOL            | LHR               | Auto Negotiate Isolate. When ANISOL is High, the auto-negotiation isolate feature is enabled (refer to "Auto-Negotiate Isolation" on page 44). ANISOL drives 16.2.                                                                     |

|        |                   |                   | <b>Serial Mode.</b> Applies when the MAC interface is used in the GMII configuration. Determines how 10 Mbps links are handled and setting of bit 16.3:                                                                                |

|        |                   |                   | GMII Configuration:                                                                                                                                                                                                                    |

| M22    | SER10             | LHR               | High = Serial mode (1 bit x 10 MHz)                                                                                                                                                                                                    |

|        |                   |                   | Low = MII mode (4 bits x 2.5 MHz).                                                                                                                                                                                                     |

|        |                   |                   | TBI Configuration:                                                                                                                                                                                                                     |

|        |                   |                   | For TBI configuration, pull Low.                                                                                                                                                                                                       |

|        | ТВІ               | LUD               | <b>Ten-Bit Interface (TBI) Mode.</b> Determines MAC interface configuration and setting of bit 16.1.                                                                                                                                   |

| U24    | CONFIGURATI<br>ON | LHR               | High = TBI Configuration                                                                                                                                                                                                               |

|        | 011               | 1                 | Low = GMII configurations.                                                                                                                                                                                                             |

<sup>1.</sup> I/O Column Coding: LHR = Input, Latched on Low-to-High edge of RESET (ignored thereafter); I, MD = Input, Latched on Low-to-High edge of RESET, used thereafter only if Manual Control mode (MDDIS = 1).

16

<sup>2.</sup> MAC Interface Operating modes: GMII (1000 Mbps), MII (10 or 100 Mbps), Serial (10 Mbps).

Table 5. LXT1000 LED Indicator Configuration Signal Descriptions

| Ball # | Symbol    | Type <sup>1</sup> | Description                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

|--------|-----------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| AA5    | LEDG      | I/O               | Gigabit LED. This active High output is asserted when a Gigabit link is established. Pull Low through a resistor/LED. (Refer to "PHY Address Determination" on page 36.)                                                                                                                                                                                                                                    |  |  |  |

| Y6     | LEDS      | I/O               | Speed LED. This active high output is asserted when a 100 Mbps link is established. Pull Low through a resistor/LED. (Refer to "PHY Address Determination" on page 36.)                                                                                                                                                                                                                                     |  |  |  |

| AA4    | LEDC/ADD4 | I/O <sup>3</sup>  | Collision LED <sup>2</sup> . After reset, this is a LED output indicating collision. The LXT1000 automatically determines whether this output is active High or active Low. In full-duplex Gigabit mode, the LEDC output goes active whenever pack are simultaneously transmitted and received.  MDIO Address 4. During power-up or reset, this ball is read to determine bit 4 the LXT1000's MDIO Address. |  |  |  |

| W6     | LEDF/ADD3 | I/O <sup>3</sup>  | Duplex LED <sup>2</sup> . After reset, this ball is a LED output indicating duplex state. The LXT1000 automatically determines whether this output is active High or active Low.  MDIO Address 3. During power-up or reset, this ball is read to determine bit 3 of the LXT1000's MDIO Address.                                                                                                             |  |  |  |

| W4     | LEDR/ADD2 | I/O               | Receive LED <sup>2</sup> . After reset, this LED output indicates receive activity at the twisted-pair (not indicated in Loopback operation). The LXT1000 automaticall determines whether this output is active High or active Low.  MDIO Address 2. During power-up or reset, this ball is read to determine bit 2 the LXT1000's MDIO Address.                                                             |  |  |  |

| U5     | LEDT/ADD1 | I/O               | Transmit LED <sup>2</sup> . After reset, this ball is an LED output indicating transmit activity at the twisted-pair (not indicated in Loopback operation). The LXT1000 automatically determines whether this output is active High or active Low.  MDIO Address 1. During power-up or reset, this ball is read to determine bit 1 of the LXT1000's MDIO Address.                                           |  |  |  |

| U4     | LEDL/ADD0 | I/O               | Link LED <sup>2</sup> . After reset, this ball is an LED output indicating link establishment any speed. The LXT1000 automatically determines whether this output is acti High or active Low.  MDIO Address 0. During power-up or reset, this ball is read to determine bit 0 the LXT1000's MDIO Address.                                                                                                   |  |  |  |

I/O Column Coding: I = Input, O = Output.

Polarity of LEDs is automatically set during the initial configuration.

The Input function, however, is not used.

Table 6. LXT1000 Miscellaneous Signal Descriptions

| Ball #                            | Symbol                  | Type <sup>1</sup> | Description                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

|-----------------------------------|-------------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| C22                               | QSTAT                   | O, PU             | <b>Quick Chip Status.</b> Link-state monitoring. See Section 2.3.8, "Quick Status Interface" on page 34.                                                                                                                                                                                                                                                                                        |  |  |  |

| D19                               | QCLK                    | 1                 | Quick Clock. Clock input used for QSTAT feature. Maximum frequency is 25 MHz. (There is no minimum.)                                                                                                                                                                                                                                                                                            |  |  |  |

| L5                                | MDDIS                   | I                 | Management Disable. When MDDIS is High, read and write operations on the MDIO are disabled and most hardware control balls have continuous control over their respective functions (some balls are read only at reset or power-up). When MDDIS is Low, the MDIO supports read and write operations, and hardware control balls establish only the initial values of their respective functions. |  |  |  |

| K3                                | MDINT                   | 0                 | <b>Management Data Interrupt</b> . When bit 18.1 = 1, an Active Low output indicates status change. Interrupt is cleared by reading Register 19.                                                                                                                                                                                                                                                |  |  |  |

| AC23<br>AA24,                     | XI<br>XO                | I<br>0            | Crystal Input and Output. A 25 MHz clock must be supplied at this input, either by placing a 25 MHz crystal across XI and XO, or by driving a 25 MHz signal directly into XI. Refer to Functional Description on page 20 for detailed requirements.                                                                                                                                             |  |  |  |

| AB14                              | RBIAS                   | Al                | <b>Bias Control.</b> A 10.7 k $\Omega$ , 1% resistor must be tied from this ball to ground.                                                                                                                                                                                                                                                                                                     |  |  |  |

| D9, D11,<br>D12, E12,<br>C14, B13 | GBIAS                   | AI                | <b>GMII Bias.</b> Tie these balls together, and then to the anode of a 0.1 $\mu$ f capacitor. Tie the cathode of the capacitor to ground.                                                                                                                                                                                                                                                       |  |  |  |

| N23                               | RESET                   | I                 | Reset. This active Low input is OR'ed with the control register Reset bit (0.15). The LXT1000 reset cycle is extended 258 μs (nominal) after Reset is de-asserted. The transmitter is held disabled until the transmit clock frequency is within specification.                                                                                                                                 |  |  |  |

| U22                               | PWRDWN                  | I                 | <b>Power Down.</b> When High, PWRDWN forces the LXT1000 into hardware power down mode, de-activating all functions and interfaces. This ball is OR'ed with the Power Down bit 0.11.                                                                                                                                                                                                             |  |  |  |

|                                   |                         | •                 | Pull Down (P/D)                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |