- Integrated, Single-Chip, Ethernet™ Physical-Layer (PHY) Interface for Full-Duplex or Half-Duplex Connection to 10BASE-T, 100BASE-TX, and 100BASE-FX Networks

- Low-Power 3.3-V CMOS Design With Power-Down Capability for CardBus and Other Applications Requiring Low Power

- **Integrated Transmit Filtering and Receive Equalization Provide for Minimal External** Component Count to Reduce System Cost

- 10BASE-T/100BASE-TX Connection **Supported With Magnetics Package and RJ-45 Connector**

- **Electrostatic Discharge (ESD) Human Body** Model (HBM) Protection 1.5 kV Per JEDEC JESD 22-A114-A

- Digital Signal Processor (DSP)-Based Digital Phase-Locked Loop (PLL) **Technology Allows Data Recovery at** 10 Mbit/s and 100 Mbit/s, Requiring One 20-MHz Clock Reference Source

- 10BASE-T

- Fully Compliant With IEEE Std 802.3

- Smart Squelch for Improved Noise **Immunity**

- Integrated Transmit Wave Shaping

- Autopolarity (Reverse-Polarity Correction)

- Transmit Jabber Detection

#### 100BASE-TX

- Fully Compliant With ANSI Twisted-Pair Physical-Media-Dependent (TP-PMD) Standard and IEEE Std 802.3

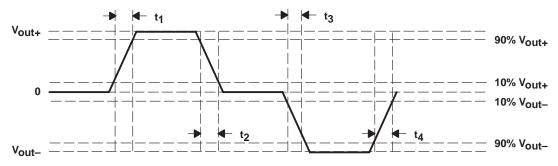

- Synthesized Rise-Time Control

- Integrated Receiver With Adaptive Line Equalization (EQ) and Baseline Wander (BLW) Correction (DC Restoration)

- **IEEE Std 802.3-Compliant** Media-Independent Interface (MII) That **Includes Management Interface**

- **IEEE Std 802.3-Compliant Autonegotiation** (N-Way) With Next-Page Support

- IEEE Std 1149.1 (JTAG) Test Access Port (TAP)

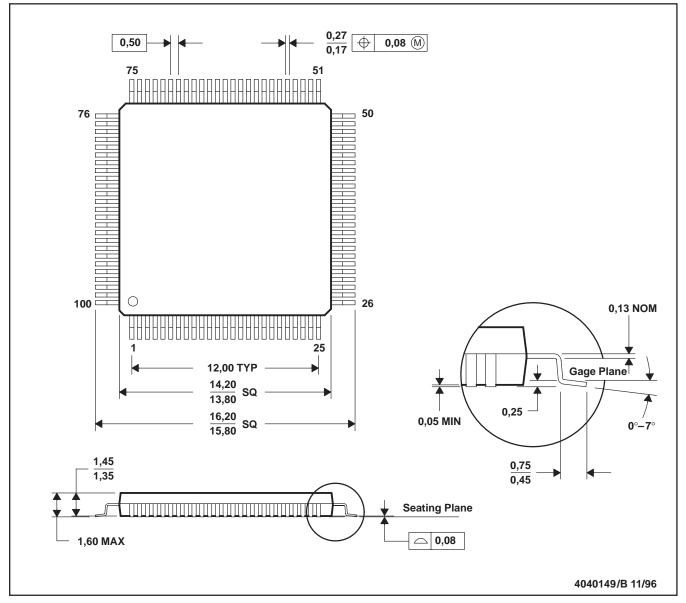

- Packaged in 100-Terminal Plastic Quad **Flatpack**

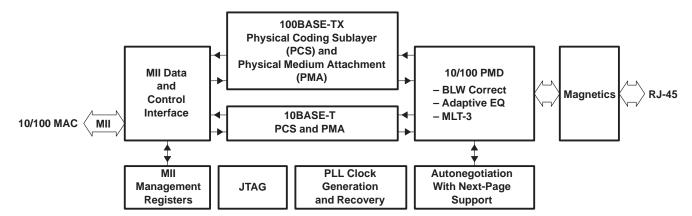

Figure 1. 10BASE-T/100BASE-TX PHY

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

TI is a trademark of Texas Instruments Incorporated. Ethernet is a registered trademark of Xerox Corporation.

### description

The TNETE2101 physical-layer (PHY) device from Texas Instruments (TI™) is a single-chip, high-performance solution for a range of 10BASE-T, 100BASE-TX, and 100BASE-FX networking systems (see Figure 1). The highly integrated TNETE2101 includes an on-board media-independent interface (MII) for simple connection to IEEE Std 802.3-compliant media-access controls (MACs). The device integrates all filtering and rise-time control functions for a cost-effective and space-saving PHY solution. Built-in autonegotiation allows automatic selection of half-/full-duplex 10BASE-T or 100BASE-TX, with an autopolarity-correction feature for immunity to receive-pair reversal.

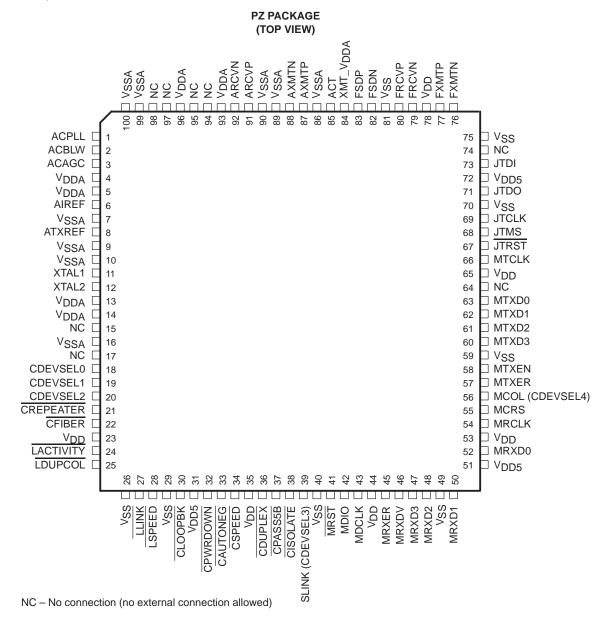

# **Terminal Functions**

# analog function

| TERMIN | IAL | t     | 1/0 | DESCRIPTION                                                                                                                        |

|--------|-----|-------|-----|------------------------------------------------------------------------------------------------------------------------------------|

| NAME   | NO. | TYPET | 1/0 | DESCRIPTION                                                                                                                        |

| ACAGC  | 3   | Α     | I   | Automatic gain control (AGC) capacitor for the AGC loop                                                                            |

| ACBLW  | 2   | Α     | I   | Baseline wander (BLW) capacitor for the BLW correction loop                                                                        |

| ACPLL  | 1   | Α     | I   | PLL capacitor required for an internal PLL                                                                                         |

| AIREF  | 6   | А     | _   | Analog current reference. An external resistor between AIREF and analog ground sets the bias current for internal analog circuits. |

| ATXREF | 8   | А     | I   | 100BASE-TX transmit reference. An external resistor between ATXREF and analog ground sets the 100BASE-TX transmit amplitude.       |

<sup>†</sup> A = analog

# configuration

| TERMINAL                         |                |      |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------------------------------|----------------|------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                             | NO.            | TYPE | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| CAUTONEG                         | 33             | TTL  | 1   | Autonegotiation enable. CAUTONEG enables (active high) or disables autonegotiation within the PHY. When CAUTONEG is low, the current values of CSPEED and CDUPLEX determine the speed and duplex of the PHY. On the rising edge of CAUTONEG, the values of CSPEED and CDUPLEX set the advertised capabilities of the PHY for autonegotiate. This also occurs on power up or on the rising edge of MRST if CAUTONEG is high. When CAUTONEG is high, the autonegotiation process also can be controlled with the PHY register bit AUTOENB (register 0, bit 12). See 10BASE-T/100BASE-TX PHY operation for details. |

| CDEVSEL2<br>CDEVSEL1<br>CDEVSEL0 | 20<br>19<br>18 | TTL  | I   | MII device-select address. The values of CDEVSEL2–CDEVSEL0, SLINK (CDEVSEL3), and MCOL (CDEVSEL4) are latched into the MII on the rising edge of MRST. This allows a unique address to be assigned to the PHY in applications in which multiple PHYs are in use.                                                                                                                                                                                                                                                                                                                                                 |

| CDUPLEX                          | 36             | TTL  | I/O | Duplex configuration. When CAUTONEG is low, CDUPLEX sets the PHY duplex to either half-duplex (low) or full-duplex (high). When CAUTONEG is high and autonegotiation is complete, CDUPLEX is driven low if half-duplex mode was selected, or set to the high-impedance state if full-duplex mode was selected. The PHY duplex also can be controlled and read at PHY register 0, bit 8, DUPLEX.                                                                                                                                                                                                                  |

| CFIBER                           | 22             | TTL  | I   | 100BASE-FX fiber-mode enable. In 100BASE-FX fiber mode, the fiber interface is enabled, and unshielded twisted pair (UTP) interface and autonegotiation are disabled. Selecting 10BASE-T mode with this mode enabled causes the PHY to power down. This function can be controlled by PHY register 0x11 bit 10, FIBER, if CFIBER is high.                                                                                                                                                                                                                                                                        |

| CISOLATE                         | 38             | TTL  | ı   | MII-isolate enable. CISOLATE causes the PHY to raise all its MII outputs to a high-impedance state and ignore the MII inputs. In normal mode (CREPEATER is high), the PHY raises MTCLK, MRCLK, MRXD0–MRXD3, MRXDV, MRXER, MCRS, and MCOL to a high-impedance state and does not respond to MTXEN. In repeater mode, only MRCLK, MRXD0–MRXD3, MRXDV, and MRXER are raised to high impedance and, consequently, CISOLATE performs an active-high receive-enable function. This function can be controlled by PHY register 0, bit 10, ISOLATE, if CISOLATE is low.                                                  |

| CLOOPBK                          | 30             | TTL  | 1   | Loopback enable. When CLOOPBK is low, transmit is looped back to receive. This function can be controlled by PHY register 0, bit 14, LOOPBK, if CLOOPBK is high.                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| CPASS5B                          | 37             | TTL  | ı   | Pass-through mode enable. CPASS5B when set low, configures the PHY to bypass the internal 5B4B encoder and decoder. The 5B-encoded data is transmitted on MTXD0–MTXD3 and MTXER with the most significant data bit on MTXER. The 5B-encoded data is received on MRXD0–MRXD3 and MRXER, with the most significant bit on MRXER. This function can be controlled by PHY register 0x11, bit 8, NOENDEC, if CPASS5B is high.                                                                                                                                                                                         |

# **Terminal Functions (Continued)**

# configuration (continued)

| TERMINA   | TERMINAL |      |     | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                    |

|-----------|----------|------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME      | NO.      | TYPE | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                    |

| CPWRDOWN  | 32       | TTL  | I   | Power-down enable. When CPWRDOWN is low, the PHY is placed in a low power-consumption state. This function can be controlled by PHY register 0, bit 11, PDOWN, if CPWRDOWN is high.                                                                                                                                                                                            |

| CREPEATER | 21       | TTL  | ı   | Repeater-mode enable. When CREPEATER is low, the repeater mode is enabled and the PHY does not assert MCRS in response to transmit activity. This function can be controlled by PHY register 0x11, bit 5, REPEATER, if CREPEATER is high.                                                                                                                                      |

| CSPEED    | 34       | TTL  | I/O | Speed configuration. When CAUTONEG is low, CSPEED sets the PHY speed to either 10BASE-T (low) or 100BASE-TX (high). When CAUTONEG is high and autonegotiation is complete, CSPEED is driven low if 10BASE-T mode was selected, or set at high-impedance state if 100BASE-TX mode was selected. The PHY speed also can be controlled and read at PHY register 0, bit 13, SPEED. |

## fiber interface

| TERMI          | NAL      | TVD=+ |     | DESCRIPTION                                                                                                                             |  |  |  |

|----------------|----------|-------|-----|-----------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME           | NO.      | TYPE† | 1/0 | DESCRIPTION                                                                                                                             |  |  |  |

| FRCVN<br>FRCVP | 79<br>80 | PECL  | _   | 100BASE-FX serial data input pair. Differential 3.3-V pseudo-emitter-coupled logic (PECL) 125-Mbit/s receive-data input for fiber mode. |  |  |  |

| FSDN<br>FSDP   | 82<br>83 | PECL  | _   | 100BASE-FX serial data detect pair. Differential 3.3-V PECL 125-Mbit/s signal-detect input.                                             |  |  |  |

| FXMTN<br>FXMTP | 76<br>77 | PECL  | 0   | 100BASE-FX serial data output pair. Differential 3.3-V PECL 125-Mbit/s serialized transmit-data output for fiber mode.                  |  |  |  |

<sup>†</sup> PECL = pseudo-emitter-coupled-logic

## IEEE Std 1149.1 JTAG interface

| TERMII | NAL | TYPE‡   | 1/0 | DESCRIPTION                                                                                                                           |

|--------|-----|---------|-----|---------------------------------------------------------------------------------------------------------------------------------------|

| NAME   | NO. | TYPE+   | 1/0 | DESCRIPTION                                                                                                                           |

| JTCLK  | 69  | 5-V TTL | _   | Test clock. JTCLK is used to clock state information and test data into and out of the device during operation of the test port.      |

| JTDI   | 73  | 5-V TTL | I   | Test data input. JTDI is used to serially shift test data and test instructions into the device during operation of the test port.    |

| JTDO   | 71  | 5-V TTL | 0   | Test data output. JTDO is used to serially shift test data and test instructions out of the device during operation of the test port. |

| JTMS   | 68  | 5-V TTL | I   | Test-mode select. JTMS is used to control the state of the test-port controller within the PHY.                                       |

| JTRST  | 67  | 5-V TTL | I   | TAP reset. JTRST is used to reset the TAP controller (optional).                                                                      |

$<sup>\</sup>ddagger$  5-V TTL terminals are 5-V tolerant if  $V_{\mbox{\scriptsize DD5}}$  is connected to 5 V.

# **Terminal Functions (Continued)**

# **LED** status

| TERMINA<br>NAME | AL<br>NO. | TYPE | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----------------|-----------|------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LACTIVITY       | 24        | LED  | 0   | Activity indicator. LACTIVITY lights an attached LED in response to receive and transmit activity within the PHY.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| LDUPCOL         | 25        | LED  | 0   | Duplex/collision indicator. LDUPCOL lights an attached LED in response to a network collision when the PHY is in half-duplex mode of operation. The LED is illuminated continuously when the PHY is in full-duplex mode.                                                                                                                                                                                                                                                                                                                                                                                                                               |

| LLINK           | 27        | LED  | 0   | Link status indicator. LLINK lights an attached LED when the PHY has established a valid link with its partner. If autonegotiation is enabled, the driver flashes the LED during negotiation to indicate that it is attempting to establish a link. This is useful because a negotiation takes a minimum of 3 seconds (considerably longer if next-page information also is being exchanged), and the user may be tempted to remove the cable if the link light does not illuminate immediately. The user also is alerted to a network misconfiguration (where no common ability exists between the two link partners) by a continuously flashing LED. |

| LSPEED          | 28        | LED  | 0   | Link speed indicator.  LSPEED lights an attached LED when the PHY has established a valid 100BASE-TX link with its partner.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

## **MII** interface

| TERMINA                          | L                    |         |     | DESCRIPTION                                                                                                                                                                                                                                                        |

|----------------------------------|----------------------|---------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                             | NO.                  | TYPET   | I/O | DESCRIPTION                                                                                                                                                                                                                                                        |

| MCOL<br>(CDEVSEL4)               | 56                   | 5-V TTL | I/O | Collision detect. MCOL indicates that the PHY is receiving data while simultaneously transmitting. MCOL does not assert in full-duplex mode. The value of MCOL is latched on the rising edge of MRST for use as CDEVSEL4, bit 4, of the MII device-select address. |

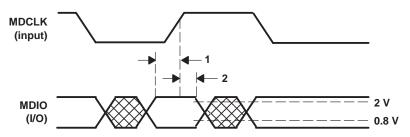

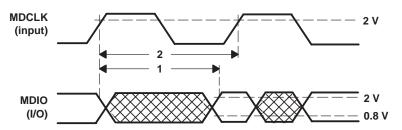

| MDCLK                            | 43                   | 5-V TTL | _   | Management data clock. MDCLK clocks serial management interface to the physical-media-dependent (PMD) chip.                                                                                                                                                        |

| MDIO                             | 42                   | 5-V TTL | I/O | Management data I/O. MDIO is serial management interface to the PMD chip. MDIO is synchronous to MDCLK.                                                                                                                                                            |

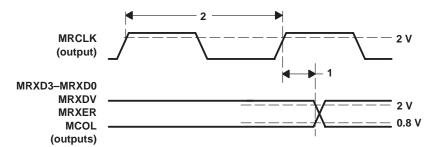

| MRCLK                            | 54                   | 5-V TTL | 0   | Receive clock. Receive clock source from the PHY. MRCLK is 2.5 MHz in 10BASE-T mode and 25 MHz in 100BASE-TX mode.                                                                                                                                                 |

| MCRS                             | 55                   | 5-V TTL | 0   | Carrier sense. MCRS asserts when the PHY initiates a frame reception.                                                                                                                                                                                              |

| MRST                             | 41                   | 5-V TTL | I   | MII reset. MRST is the reset signal to the PMD front end (active low).                                                                                                                                                                                             |

| MRXD3<br>MRXD2<br>MRXD1<br>MRXD0 | 47<br>48<br>50<br>52 | 5-V TTL | 0   | Receive data. MRXD3-MRXD0 are nibble receive data bits 3-0 from the PHY. Data is synchronous to MRCLK.                                                                                                                                                             |

| MRXDV                            | 46                   | 5-V TTL | 0   | Receive data valid. MRXDV indicates that data on MRXD0-MRXD3 is valid. MRXDV is synchronous to MRCLK.                                                                                                                                                              |

| MRXER                            | 45                   | 5-V TTL | 0   | Receive error. MRXER indicates reception of a coding error on received data. MRXER is synchronous to MRCLK.                                                                                                                                                        |

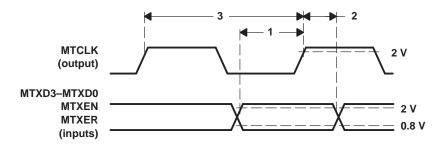

| MTCLK                            | 66                   | 5-V TTL | 0   | Transmit clock. MTCLK is the transmit clock source from the PHY. This clock is 2.5 MHz in 10BASE-T mode and 25 MHz in 100BASE-TX mode.                                                                                                                             |

| MTXD3<br>MTXD2<br>MTXD1<br>MTXD0 | 60<br>61<br>62<br>63 | 5-V TTL | I   | Transmit data. MTXD3-MTXD0 are nibble transmit data bits 3-0 from the MAC. Data is synchronous to MTCLK.                                                                                                                                                           |

<sup>† 5-</sup>V TTL terminals are 5-V tolerant if V<sub>DD5</sub> is connected to 5 V.

# **Terminal Functions (Continued)**

# MII interface (continued)

| TERMINAL |     | TVDET   | 1/0 | DESCRIPTION                                                                                                |

|----------|-----|---------|-----|------------------------------------------------------------------------------------------------------------|

| NAME     | NO. | TYPET   | I/O | DESCRIPTION                                                                                                |

| MTXEN    | 58  | 5-V TTL | I   | Transmit enable. MTXEN indicates valid transmit data on MTXD0-MTXD3. MTXEN is synchronous to MTCLK.        |

| MTXER    | 57  | 5-V TTL | ı   | Transmit error. MTXER allows coding errors to be propagated across the MII. MTXER is synchronous to MTCLK. |

<sup>†5-</sup>V TTL terminals are 5-V tolerant if V<sub>DD5</sub> is connected to 5 V.

# miscellaneous

| TERMINA             | TERMINAL |       | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                           |

|---------------------|----------|-------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                | NO.      | TYPE‡ | 1/0 | DESCRIFTION                                                                                                                                                                                                                                                                                                                                                                                           |

| SLINK<br>(CDEVSEL3) | 39       | TTL   | I/O | Link status. When asserted high, SLINK indicates that a good link has been established with the link partner. When autonegotiation is enabled, SLINK also indicates that the CSPEED and CDUPLEX terminals are being driven with the negotiated speed and duplex configuration. The value of SLINK is latched on the rising edge of MRST for use as CDEVSEL3, bit 3, of the MII device-select address. |

| XTAL1               | 11       | А     | I   | Clock input. XTAL1 is the main 20-MHz reference clock input for the TNETE2101. A 20-MHz clock oscillator can be connected to XTAL1, or a crystal with a capacitor network can be connected across XTAL1 and XTAL2.                                                                                                                                                                                    |

| XTAL2               | 12       | Α     | 0   | Output for external crystal circuit. See XTAL1.                                                                                                                                                                                                                                                                                                                                                       |

<sup>‡</sup> A = analog

## network interface

| TERMIN         | NAL      | TYPE <sup>‡</sup> |     | DESCRIPTION                                                                                                                     |

|----------------|----------|-------------------|-----|---------------------------------------------------------------------------------------------------------------------------------|

| NAME           | NO.      |                   | 1/0 | DESCRIPTION                                                                                                                     |

| ACT            | 85       | А                 | 0   | Center tap. ACT is the connection to the primary center tap of the transmit transformer.                                        |

| ARCVP<br>ARCVN | 91<br>92 | А                 | _   | Receive pair. ARCVP and ARCVN are the differential line inputs to the device from the transformer and termination components.   |

| AXMTP<br>AXMTN | 87<br>88 | А                 | 0   | Transmit pair. AXMTN and AXMTP are the differential line outputs from the device to the transformer and termination components. |

<sup>‡</sup> A = analog

### no connection

| NAME | TERMINAL<br>NO.                | DESCRIPTION                                     |

|------|--------------------------------|-------------------------------------------------|

| NC   | 15, 17, 64, 74, 94, 95, 97, 98 | No connection (no external connection allowed). |

# **Terminal Functions (Continued)**

# power

| TERI             | MINAL                                   | POWER                                  | DESCRIPTION                                                                                                                                             |  |

|------------------|-----------------------------------------|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME             | NO.                                     | DOMAINT                                | DESCRIPTION                                                                                                                                             |  |

| V <sub>DDA</sub> | 5, 13, 14, 96                           | $V_{DDA}$                              | Power. Analog 3.3-V supply connection.                                                                                                                  |  |

| $XMT_V_{DDA}$    | 84                                      | XMT_AV <sub>DD</sub>                   | Power. Analog 3.3-V supply connection for transmit.                                                                                                     |  |

| V <sub>DDA</sub> | 4, 93                                   | $V_{DDA}$                              | Power. Analog 3.3-V supply connection for receive.                                                                                                      |  |

| V <sub>DD5</sub> | 31, 51, 72                              | V <sub>DD</sub> or<br>V <sub>DD5</sub> | Power. Power for digital I/O that connects to 3.3 V for 3.3-V I/O operations and to 5 V for 5-V I/O operations. Used for I/O on MII and JTAG interface. |  |

| V <sub>DD</sub>  | 23, 35, 44, 53,<br>65, 78               | V <sub>DDD</sub>                       | Power. Digital 3.3-V supply connection for core logic and I/O.                                                                                          |  |

| VSSA             | 7, 9, 10, 16,<br>86, 89, 90, 99,<br>100 | GND                                    | Ground. Analog ground connection.                                                                                                                       |  |

| V <sub>SS</sub>  | 26, 29, 40, 49,<br>59, 70, 75, 81       | GND                                    | Ground. Digital ground connection.                                                                                                                      |  |

<sup>†</sup> Denotes suggested power-plane connection for layout

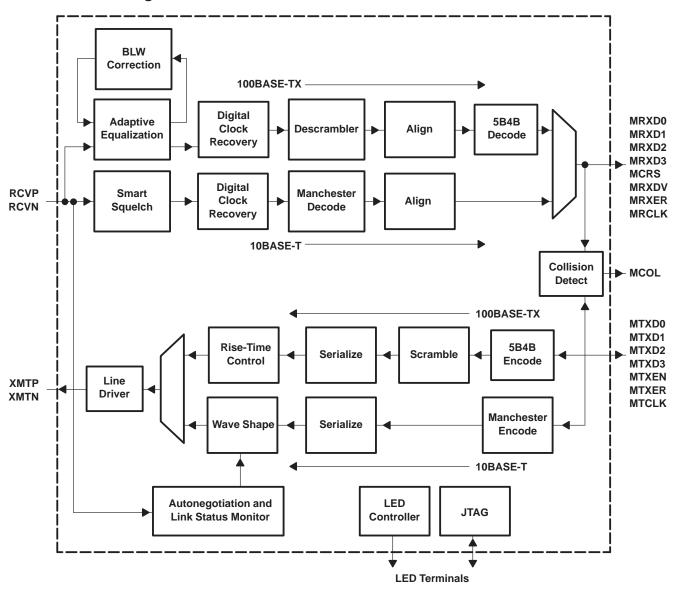

# functional block diagram for UTP interface

### functional description

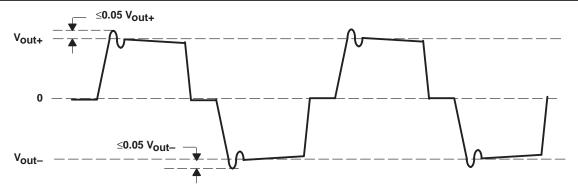

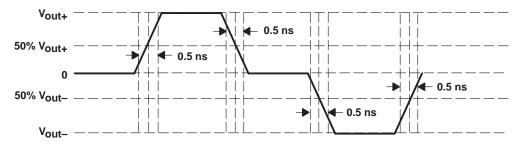

#### 10BASE-T/100BASE-TX differential line transmitter function

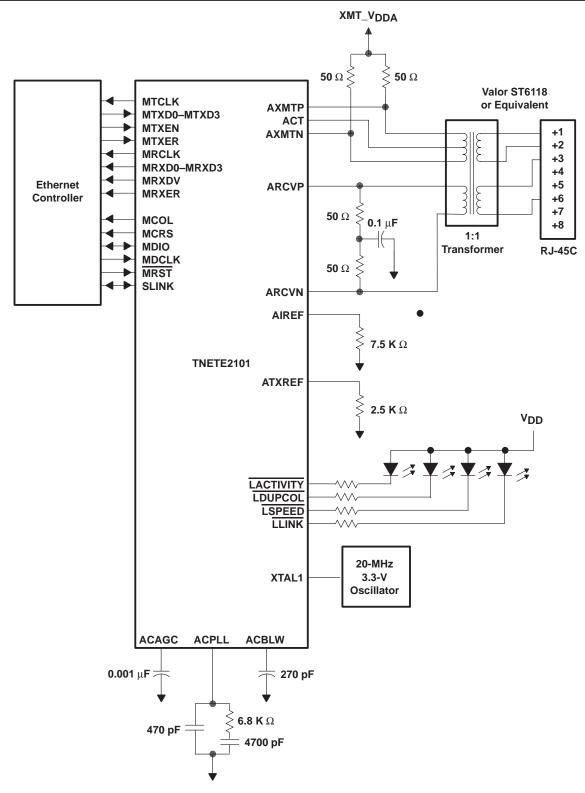

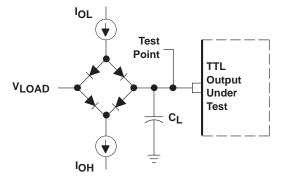

The TNETE2101 differential line drivers are designed to drive at least 100 m of CAT5 cable in 100BASE-TX mode and in excess of 100 m of CAT3 (or CAT5) cable in 10BASE-T mode. Three transmitter-output terminals (including a center-tap connection) interface to a single transformer for both operating modes. This simplifies the external connection to a single RJ-45 socket connected directly to the transformer secondary winding (see Figure 2).

The TNETE2101 incorporates on-chip wave shaping for 10BASE-T transmission and rise-time control for 100BASE-TX transmission, which enables the device to interface directly to the magnetics without using external components, other than two termination resistors. The functional block diagram illustrates the TNETE2101 transmitter function for a single 10BASE-T/100BASE-TX PHY channel.

#### 10BASE-T/100BASE-TX differential line receiver function

The two receiver-input terminals of the TNETE2101 must be connected to the physical-media interface (PMI) through an external isolation transformer. The receiver circuitry establishes its own common-mode input bias voltage, therefore, no external resistor divider-biasing network is required. A simple termination network consisting of two resistors and one capacitor is recommended (see Figure 2). Data received from the network is output on the MRXD data nibble of the MII and synchronized to the rising edge of the corresponding MRCLK signal. The MRCLK frequency automatically adjusts to 2.5 MHz in 10BASE-T mode or 25 MHz in 100BASE-TX mode.

A single receiver-input pair supports both speed modes, with all multiplexing functions performed internally to the device.

The 10BASE-T receiver smart-squelch function allows incoming data to pass only if the input amplitude is greater than a minimum signal threshold and a specific pulse sequence is received. This prevents input data being affected by impulse line noise that is mistaken for signal or link activity. The squelch circuits quickly deactivate if received pulses exceed the specifications; therefore, long pulses are not mistaken as link pulses.

The 100BASE-TX receiver decodes the MLT-3 waveform and provides a data nibble on MRXD0–MRXD3. After MLT-3 signal is received, the signal is immediately amplified and equalized. This allows reception over a minimum of 100 m of CAT5 cable. The low-frequency component of the MLT-3 signal, often referred to as BLW, is removed. BLW can be a consequence of long periods without data transitions in transformer-coupled circuits. The ideal MLT-3 then is internally converted to non-return-to-zero information (NRZI), then resynchronized to its own recovered clock using a digital phase-locked-loop (PLL) technique. The reclocked data then is deserialized into 5-bit code groups, descrambled, and 5B4B decoded. When a start-of-stream delimiter is detected in the 5B data stream, the next frame is output on the MII. The functional block diagram illustrates the TNETE2101 receiver function for a single 10BASE-T/100BASE-TX PHY channel.

Figure 2. External Components for the TNETE2101

#### link-integrity test and reverse-polarity and correction

When autonegotiation is disabled and the TNETE2101 is configured for 10BASE-T only, the transmitter sends a normal link pulse through the data-out (DO) circuit every 16 ms.

The receiver looks for valid link pulses on the input pair. If a link pulse is not received within a given time interval, the device enters a link-fail state. In this state, link pulses continue to be generated, and the receiver continuously looks for the link pulse pattern. The device remains in this state until a valid receive packet or multiple legal-link test pulses are received.

Link pulses of the opposite polarity (received and qualified in the same manner as normal link pulses) are an indication that the receive-pair connections are reversed and that an automatic internal reconfiguration has occurred to correct this problem. Reverse-polarity correction is not required in 100BASE-TX mode, where the data is MLT-3-encoded.

#### autonegotiation

The TNETE2101 fully supports IEEE Std 802.3 autonegotiation, including next-page transfer. When enabled, this feature allows the TNETE2101 to negotiate with any other autonegotiation-capable PHYs on its link segment to establish their highest common protocol. Until a PHY has completed its negotiation, it cannot assert LINK.

More information on the link partner abilities can be obtained by reading the TNETE2101 registers.

#### loopback test mode

By asserting the CLOOPBK terminal on the device or by setting the LOOPBK bit in the GEN\_ctl register, the transmit circuit of the PHY is looped back to the corresponding receive circuit located closest to the twisted-pair I/O terminals.

In 10BASE-T mode and loopback mode, all receive activities (other than link test pulses) are ignored. However, squelch information is still processed, allowing the link status to be maintained under momentary loopback self-test.

#### LED status indication

The TNETE2101 has four terminals that drive LEDs, indicating activity, duplex/collision, link, and speed. The circuitry contains an open-drain N-channel MOS (NMOS) device for the LED driver, and the LEDs should be connected to digital 3.3 V through a current-limiting resistor. The value of the resistor depends on the LED type.

In 10BASE-T mode, the link LED illuminates when the PHY has established a valid link. In 100BASE-TX mode, the link LED indicates that the descrambler has locked onto the data and the TNETE2101 is in a state to transmit and receive data. The link LED flashes during the autonegotiation process to indicate link activity to the user, since autonegotiation can take several seconds. During loopback test, the LED is not illuminated.

The activity LED illuminates when the PHY is transmitting or receiving data; it remains illuminated for a minimum of 20 ms for each activity. Its operation is the same in both speed modes. The activity LED illuminates on any attempt to transmit data, including those made in loopback mode and in link-fail state.

The duplex/collision LED illuminates continuously when the PHY is in full-duplex mode and for a minimum of 20 ms when collisions occur in half-duplex mode. If continuous or frequent collisions occur, it flashes at 10 Hz.

### test access port (TAP)

To be compliant with IEEE Std 1149.1 and for boundary-scan testing, the TAP includes five terminals that are used to interface serially with the device and the board on which it is installed.

# TNETE2101 10BASE-T/100BASE-TX/100BASE-FX LOW-POWER PHYSICAL-LAYER INTERFACE

SPWS032D - JANUARY 1997 - REVISED MARCH 1999

#### 100BASE-FX differential PECL interface

The PHY provides three pairs of differential PECL terminals for connection to external fiber-optic transceivers. The data streams are 125-Mbit/s NRZI encoded, with the receive data stream routed to the digital PLL for data recovery. To maintain a reliable lock on the digital PLL, the receive data stream must be jitter free.

The FSDP/FSDN serial data-detect pair must be differentially positive to enable data recovery. While this pair is differentially negative, MRCLK is inactive, and no attempt is made to process any receive data appearing on FRCVP/FRCVN.

Differential PECL signals should be terminated with a standard emitter-coupled logic (ECL) load of 50  $\Omega$  to a voltage source of V<sub>DD</sub> – 2 V (that is, 1.3 V) or to an equivalent circuit.

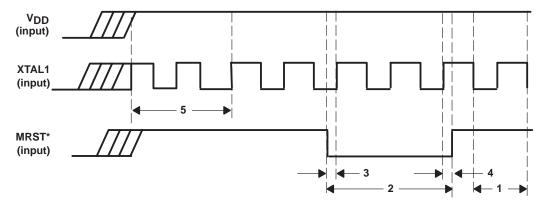

### reset and power up timing

At initial power up, the PHY performs an internal reset. No external reset circuitry is required; however, operation of the TNETE2101 is not specified for 50 ms after power up (V<sub>DD</sub> stable).

During operation, a full reset of the device can be performed by taking MRST low for not less than 50 μs. Correct operation of the device is not certain until 50 ms after MRST is deasserted high.

### 10BASE-T/100BASE-TX PHY operation

#### PHY link establishment

The PHY implements the full autonegotiation standard, including next-page capability, CAUTONEG, CSPEED, and CDUPLEX are used to directly configure the link speed or to set and report autonegotiated speeds.

When CAUTONEG is deasserted low, CSPEED and CDUPLEX determine the link configuration. CSPEED and CDUPLEX have weak pullups, giving a default configuration of full-duplex 100BASE-TX when not connected.

The rising edge of CAUTONEG latches the values of CSPEED and CDUPLEX into the autonegotiation advertisement (AN\_adv) register as shown in Table 1. This advertises to the link partner during negotiation of the capabilities of PHY and the highest common link is determined. CSPEED and CDUPLEX then are driven with the negotiated speed and duplex.

| CSPEED | CDUPLEX | AN_adv | ADVERTISED TECHNOLOGIES                                    |

|--------|---------|--------|------------------------------------------------------------|

| 0      | 0       | 0x0021 | Half-duplex 10BASE-T                                       |

| 0      | 1       | 0x0061 | Half-/full-duplex 10BASE-T                                 |

| 1      | 0       | 0x00A1 | Half-duplex 10BASE-T<br>Half-duplex 100BASE-TX             |

| 1      | 1       | 0x00E1 | Half-/full-duplex 10BASE-T<br>Half-/full-duplex 100BASE-TX |

**Table 1. External-Link Configuration Speeds**

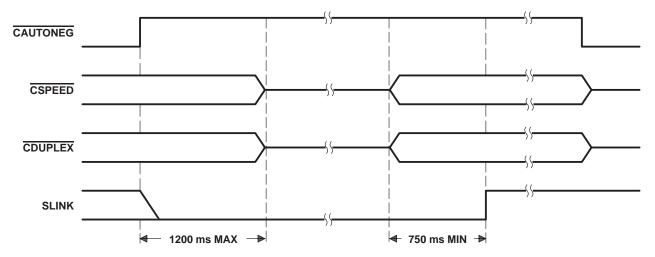

For external controlling and reading of CAUTONEG, CSPEED, and CDUPLEX, timing to be considered is shown in Figure 3. CSPEED and CDUPLEX must not be driven externally for 1200 ms (maximum) after CAUTONEG is asserted high. The PHY begins negotiation when CAUTONEG is asserted. In the final 750 ms (minimum) of autonegotiation, the PHY drives CSPEED and CDUPLEX to indicate the link configuration. The values of these two terminals can be latched on the rising edge of SLINK.

### PHY link establishment (continued)

Figure 3. External Autonegotiation Configuration and Status

Autonegotiation, duplex, and speed also can be controlled through the PHY register <u>0</u>, <u>GEN\_ctl. These bits</u>, AUTOENB (bit 12), SPEED (bit 13), and DUPLEX (bit 8), are similar to and work with <u>CAUTONEG</u>, <u>CSPEED</u>, and <u>CDUPLEX</u>, respectively. These bits can be written and read.

When CAUTONEG is low, the AUTOENB bit remains set to a 0 and cannot be set to a 1; therefore, autonegotiation cannot be enabled. In this case, the values read from SPEED and DUPLEX reflect the values driven on the terminals CSPEED and CDUPLEX, respectively.

When CAUTONEG is high, AUTOENB can be set to a 1 (enabled) or a 0 (disabled). When AUTOENB is enabled, autonegotiation is started and the SPEED and DUPLEX bits are updated to reflect the negotiated values. When AUTOENB is disabled, autonegotiation is disabled and speed and duplex are forced to the values written in the SPEED and DUPLEX bits.

### **PHY** configuration

The TNETE2101 can be configured externally through the terminals or internally through the PHY registers much like the autonegotiation terminals and register bits. Each external terminal has an equivalent PHY register bit. Table 2 correlates the terminal with the register bit.

| TERMINAL  | PIN NO. | BIT                                         | REGISTER | BIT NO. | NO. FUNCTION                               |  |  |  |

|-----------|---------|---------------------------------------------|----------|---------|--------------------------------------------|--|--|--|

| CISOLATE  | 38      | ISOLATE                                     | 0x0      | 10      | Sets MII interface to high-impedance state |  |  |  |

| CPWRDOWN  | 32      | PDOWN 0x0 11 Places PHY in power-down state |          |         |                                            |  |  |  |

| CLOOPBK   | 30      | LOOPBK                                      | 0x0      | 14      | Enables loopback                           |  |  |  |

| CREPEATER | 21      | REPEATER                                    | 0x11     | 5       | Enables repeater mode                      |  |  |  |

| CPASS5B   | 37      | NOENDEC                                     | 0x11     | 8       | Disables 5B4B encoder/decoder              |  |  |  |

| CFIBER    | 22      | FIBER                                       | 0x11     | 10      | Enables fiber interface                    |  |  |  |

Table 2. External Configuration Terminal/Register Bit Correlation

All of the terminals are active low and the register bits are active when set to a 1. All the register bits can be written and read. The value read from the register bit reflects the internal configuration setting of the PHY and is derived from the external terminal setting and the internal register bit value.

# TNETE2101 10BASE-T/100BASE-TX/100BASE-FX LOW-POWER PHYSICAL-LAYER INTERFACE

SPWS032D - JANUARY 1997 - REVISED MARCH 1999

## PHY configuration (continued)

Table 3 shows the external configuration terminal, register value, and the result, except for the isolate function.

**Table 3. Terminal and Register Values**

| TERMINAL<br>VALUE<br>(LOW = ACTIVE) | REGISTER<br>VALUE<br>WRITTEN | REGISTER<br>VALUE<br>READ | RESULT   |

|-------------------------------------|------------------------------|---------------------------|----------|

| Low                                 | Х                            | 1                         | Enabled  |

| High                                | 0                            | 0                         | Disabled |

| High                                | 1                            | 1                         | Enabled  |

Table 4 shows the operation for the isolate function and the resulting control of the isolate function.

**Table 4. Isolate-Function Operation**

| TERMINAL VALUE (LOW = ACTIVE) | REGISTER<br>VALUE<br>WRITTEN | REGISTER<br>VALUE<br>READ | RESULT   |

|-------------------------------|------------------------------|---------------------------|----------|

| Low                           | 0                            | 0                         | Disabled |

| Low                           | 1                            | 1                         | Enabled  |

| High                          | Х                            | 0                         | Disabled |

The terminal can be set to a value that disables control of the function through the internal PHY registers.

### 10BASE-T/100BASE-TX PHY registers

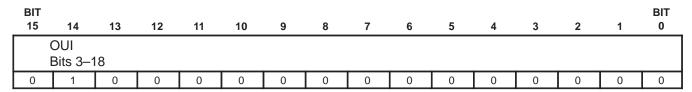

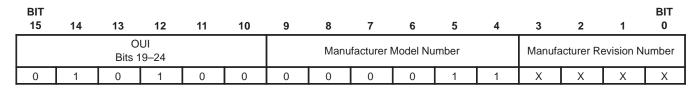

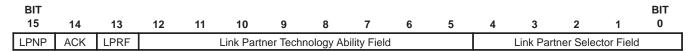

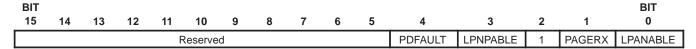

The IEEE Std 802.3 MII serial protocol allows for up to 32 different PMD devices, with up to 32 (16-bit-wide) internal registers in each device. The 10BASE-T/100BASE-TX PHY implements 11 internal registers, three of which are hardwired. Figure 4 shows the device register map. Most of the registers are the generic registers mandated by the MII specification. The three registers (TXPHY\_X) in Figure 4 are TI-specific registers. All other registers are read as 0s.

| REGISTER  | ADDRESS | DESCRIPTION                                                      |

|-----------|---------|------------------------------------------------------------------|

| GEN_ctl   | 0x00h   | Generic control (see Figure 7 and Table 6)                       |

| GEN_sts   | 0x01h   | Generic status (see Figure 8 and Table 7)                        |

| GEN_id_hi | 0x02h   | Generic identifier (high) hardwired (see Figure 9)               |

| GEN_id_lo | 0x03h   | Generic identifier (low) hardwired (see Figure 10)               |

| AN_adv    | 0x04h   | Autonegotiation advertisement (see Figure 11 and Table 8)        |

| AN_lpa    | 0x05h   | Autonegotiation link partner ability (see Figure 12 and Table 9) |

| AN_exp    | 0x06h   | Autonegotiation expansion (see Figure 15 and Table 13)           |

| AN_np     | 0x07h   | Autonegotiation next-page transmit (see Figure 16 and Table 14)  |

| Reserved  | 0x08h   |                                                                  |

| Reserved  |         | Reserved by IEEE Std 802.3                                       |

| Reserved  | 0x0Fh   |                                                                  |

| TXPHY_id  | 0x10h   | PHY identifier <sup>†</sup>                                      |

| TXPHY_ctl | 0x11h   | PHY control (see Figure 17 and Table 15)                         |

| TXPHY_sts | 0x12h   | PHY status (see Figure 18 and Table 16)                          |

<sup>†</sup>TI-specific register

Figure 4. Register Map

#### **MII** frame format

The default or IDLE state of the MII is a logic 1. All 3-state drivers are disabled and the PHY pullup resistor pulls the management data input/output (MDIO) line to a logic 1. Before initiating any other transaction, the station management entity sends a preamble sequence of contiguous logic-1 bits on MDIO with 32 corresponding cycles on MDCLK. This sequence provides the PHY a pattern to use to establish synchronization. A PHY observes the sequence of 32 contiguous 1 bits on MDIO with 32 corresponding cycles on MDCLK before responding to any other transactions. See Figures 5 and 6 for MII frame formats.

| Start Delimiter | Operation Code PHY Address |       | Register Address | Turnaround | Data                |  |  |

|-----------------|----------------------------|-------|------------------|------------|---------------------|--|--|

| 01              | 10                         | AAAAA | RRRRR            | 10         | DDDD.DDDD.DDDD.DDDD |  |  |

Figure 5. MII Read Frame Format

| Start Delimiter | Operation Code | PHY Address | Register Address | Turnaround | Data                |

|-----------------|----------------|-------------|------------------|------------|---------------------|

| 01              | 01             | AAAAA       | RRRRR            | 10         | DDDD.DDDD.DDDD.DDDD |

Figure 6. MII Write Frame Format

#### start delimiter

The start of a frame is indicated by a 01 pattern. This pattern specifies transitions from the default logic-1 line state to 0 and then back to 1.

#### operation code

The operation code for a read is 10, and the code for a write is 01.

#### PHY address

The PHY address is five bits, providing 32 unique PHY addresses. The first PHY address bit transmitted and received is the most significant bit of the address. The TNETE2101 address is set using CDEVSEL0–CDEVSEL2, CDEVSEL 3 (SLINK), and CDEVSEL4 (MCOL).

#### register address

The register address is 5 bits, providing 32 individual registers to be addressed within each PHY. See Figure 4 for the addresses of individual registers.

#### turnaround

An idle-bit time, during which no device actively drives the MDIO signal, is inserted between the register address field and the data field of a read frame to avoid contention. During a read frame, the PHY drives a 0 bit onto MDIO for the bit time that follows the idle bit and precedes the data field. During a write frame, this field consists of a 1 bit followed by a 0 bit.

#### data

The data field is 16 bits. The first data bit transmitted and received is the most significant bit of the data payload.

### MII interrupt operation

The TNETE2101 can provide an interrupt based on certain PHY events through the MII MDIO signal. This allows software to receive an interrupt on events, such as a change in link, without periodically polling the device. Interrupt is indicated by driving the MDIO terminal low after the quiescent cycle and while MDCLK is high. The quiescent cycle is the cycle following the data transfer, during which neither the MACs nor the PHYs drive the MDIO.

The interrupt feature is controlled by register bits, MINT, INTEN, and TINT. MINT is the MII-interrupt bit (register 0x12, bit 15) and is set to a 1 when one or more interrupt events have occurred. INTEN is the interrupt-enable bit (register 0x11, bit 1) which allows MINT to generate an interrupt on the MDIO terminal. Additionally, to test interrupt operation (TINT), test interrupt (register 0x11, bit 0) can be set to a 1 which generates an interrupt, regardless of the value of MINT and INTEN.

Once an interrupt has occurred, MINT can be set to a 0 again by reading the register that contains the event status. Table 5 shows all the events that can cause MINT to be set and the register location.

| EVENT     | CAUSE                                                                                    | REGISTER | BIT |

|-----------|------------------------------------------------------------------------------------------|----------|-----|

| JABBER    | When set to a 1                                                                          | 0x01     | 1   |

| LINK      | Change in state or is different from either the last read value of current state of LINK | 0x01     | 2   |

| RFAULT    | When set to a 1                                                                          | 0x01     | 4   |

| AUTOCMPLT | When set to a 1                                                                          | 0x01     | 5   |

| PAGERX    | When set to a 1                                                                          | 0x06     | 1   |

| FEFI      | When set to a 1                                                                          | 0x12     | 10  |

| SYNCLOSS  | When set to a 1                                                                          | 0x12     | 11  |

| TPENERGY  | When set to a 1 and MANCONF is enabled                                                   | 0x12     | 12  |

| PLOK      | Change in state and MANCONF is enabled                                                   | 0x12     | 13  |

| PHOK      | When set to a 1                                                                          | 0x12     | 14  |

**Table 5. Interrupt Causes and Register Location**

### details of an interrupt on MDIO

- The first MII frame exchanged after power up on MDCLK/MDIO synchronizes the internal MII-state machine. (After the first MII frame, the TNETE2101 does not require the 32 contiguous 1s before the start of frame for synchronization.)

- A complete clock cycle (high and low) must occur after the last data bit. This clock cycle, or quiescent cycle, allows the device driving MDIO to set its output to a high-impedance state. After reaching the high-impedance state, MDIO goes high due to the required external pullup on the MDIO signal.

- Clock brought high again enables the interrupt to be driven on the MDIO line (MDIO = low). For as long as

the clock is held high, if an interrupt occurs, MDIO is driven low. The interrupt occurring is not contingent

on seeing another rising edge on the MDCLK, instead, it is clocked through, based on the internal PHY

clock.

- On every rising edge thereafter, PHY samples the MDIO line to see if the management entity is outputing

a low, signifying the start of frame. If the MDIO line is high, there is no start of frame and the PHY again drives

the MDIO line low, if there is an interrupt. If start of frame is recognized, the PHY inhibits driving the interrupt

onto the MDIO line until after the MII frame has completed.

| PHY generic control register - | - GEN | ctl at | 0x00 |

|--------------------------------|-------|--------|------|

|--------------------------------|-------|--------|------|

| BIT<br>15             | 14                         | 13        | 12            | 11                    | 10                              | 9               | 8                          | 7       | 6 | 5 | 4 | 3        | 2 | 1 | BIT<br>0 |

|-----------------------|----------------------------|-----------|---------------|-----------------------|---------------------------------|-----------------|----------------------------|---------|---|---|---|----------|---|---|----------|

| R<br>E<br>S<br>E<br>T | L<br>O<br>O<br>P<br>B<br>K | S P E E D | A U T O E N B | P<br>D<br>O<br>W<br>N | I<br>S<br>O<br>L<br>A<br>T<br>E | A U T O R S R T | D<br>U<br>P<br>L<br>E<br>X | COLTEST |   |   |   | Reserved | d |   |          |

Figure 7. PHY Generic Control Register

# Table 6. PHY Generic Control Register Bit Functions

| BIT      |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|----------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME     | NO. | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| RESET    | 15  | PHY reset. Writing a 1 to RESET causes the PHY to be reset and all registers (except GEN_ctl) to be reset to their default values. RESET is self-clearing—it returns a value of 1 when read, until the internal reset is complete (which takes no longer than 500 ms). Writing a 0 to RESET (default) has no effect. This operation can interrupt data communications.                                                                                                                                                                                                                                                                                                                                                                                     |

| LOOPBK   | 14  | Loopback. LOOPBK enables or disables internal loopback within the PHY device. When LOOPBK is set to 1, data is wrapped internally within the PHY and does not appear on the network. When LOOPBK is cleared to 0 (default), data is transmitted to and received from the network. While the PHY is in loopback, all network lines are placed in a noncontentious state. If CLOOPBK is asserted low, loopback is enabled and this bit cannot be set to 0 but is read as 1.                                                                                                                                                                                                                                                                                  |

| SPEED    | 13  | Speed select. Link speed is determined by way of either autonegotiation or manual setting. There are three methods by which the PHY speed can be determined:  - Autonegotiation enabled. Speed determined by negotiation.  - Autonegotiation disabled by CAUTONEG being low. Speed determined by CSPEED setting.  - Autonegotiation disabled by register bit AUTOENB set to a 0. Speed determined by register bit SPEED setting.                                                                                                                                                                                                                                                                                                                           |

|          |     | When SPEED is set to a 1 (default) the PHY speed is 100 Mbit/s and when set to a 0 the PHY speed is 10 Mbit/s. The value read from the SPEED bit always reflects the current PHY speed, regardless of which method is used to select the speed (as described previously).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| AUTOEND  | 40  | Autonegotiate enable. AUTOENB enables or disables the autonegotiation process if CAUTONEG is high. When AUTOENB is 0, the link is configured by way of the DUPLEX and SPEED bits, and the PHY implements the appropriate link-integrity test.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| AUTOENB  | 12  | When AUTOENB is set to 1 (default), autonegotiation is enabled and the PHY engages in the autonegotiation process when a LINK FAIL condition is detected or the AUTORSRT bit is set. The link must not be treated as valid until the AUTOCMPLT bit and LINK bit are set to 1. If CAUTONEG terminal is low, autonegotiation is disabled, and AUTOENB cannot be set to 1 but is read as 0.                                                                                                                                                                                                                                                                                                                                                                   |

| PDOWN    | 11  | Power down. When PDOWN is set to 1, the PHY is placed in a low power-consumption state. The time required for the PHY to power up after PDOWN is cleared can vary considerably. It is good practice to set RESET after this time to make certain that the PHY is in a valid state. If CPWRDOWN is asserted low, the PHY is powered down, and this bit cannot be set to 0 but is read as 1.                                                                                                                                                                                                                                                                                                                                                                 |

| ISOLATE  | 10  | Isolate. The function of ISOLATE depends on whether the PHY is in repeater mode or node mode (determined by the REPEATER bit in TXPHY_ctl). In node mode, when ISOLATE is set to 1 (default), the PHY electrically isolates its data paths from the MII. In this state, it does not respond to MTXD0–MTXD3, MTXEN, and MTXER inputs, but presents a high impedance on its MTCLK, MRCLK, MRXDV, MRXER, MRXD0–MRXD3, and MCOL outputs. It still responds to management frames on MDIO and MDCLK. In repeater mode, when ISOLATE is set to 1, the PHY presents a high impedance on its MRCLK, MRXDV, MRXER, and MRXD0–MRXD3 outputs only. If CISOLATE is deasserted high, the ISOLATE function is disabled, and this bit cannot be set to 1 but is read as 0. |

| AUTORSRT | 9   | Restart autonegotiation. If autonegotiation has been enabled by setting AUTOENB to 1, the autonegotiation process can be restarted by setting AUTORSRT to 1. AUTORSRT is self clearing, and the PHY returns a value of 1 in this bit until autonegotiation fast-link pulse (FLP) data-burst transmission has been initiated. When AUTOENB is cleared to 0, AUTORSRT is read as 0. The default value of AUTORSRT is 0.                                                                                                                                                                                                                                                                                                                                      |

|          |     | Duplex mode. Duplex mode is determined by way of either autonegotiation or normal setting. There are three ways the PHY speed can be determined:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| DUPLEX   | 8   | <ul> <li>Autonegotiation enabled. Duplex determined by negotiation.</li> <li>Autonegotiation disabled by CAUTONEG being low. Duplex determined by CDUPLEX setting.</li> <li>Autonegotiation disabled by register bit AUTOENB set to a 0. Duplex determined by register bit DUPLEX setting.</li> <li>When DUPLEX is set to 1 (default), the PHY is in full duplex. When DUPLEX is set to 0, the PHY is in half duplex.</li> </ul>                                                                                                                                                                                                                                                                                                                           |

|          |     | The value read from the DUPLEX bit always reflects the current PHY duplex, regardless of which is used to select the duplex, (as described previously).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| COLTEST  | 7   | Collision test mode. When COLTEST is set to 1 and LOOPBK is set to 1, the PHY asserts the collision-detect signal MCOL when transmit enable MTXEN is asserted. The default value of COLTEST is 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Reserved | 6–0 | Reserved. Read and write as 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

# TNETE2101 10BASE-T/100BASE-TX/100BASE-FX LOW-POWER PHYSICAL-LAYER INTERFACE

SPWS032D - JANUARY 1997 - REVISED MARCH 1999

# PHY generic status register – GEN\_sts at 0x01

| BIT |    |    |    |    |    |          |   |   |           |        |   |      |        |   | BIT |

|-----|----|----|----|----|----|----------|---|---|-----------|--------|---|------|--------|---|-----|

| 15  | 14 | 13 | 12 | 11 | 10 | 9        | 8 | 7 | 6         | 5      | 4 | 3    | 2      | 1 | 0   |

| 0   | 1  | 1  | 1  | 1  |    | Reserved |   | 1 | AUTOCMPLT | RFAULT | 1 | LINK | JABBER | 1 |     |

Figure 8. PHY Generic Status Register

# **Table 7. PHY Generic Status Register Bit Functions**

| BIT       |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME      | NO.  | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 0         | 15   | 100BASE-T4 ability. Not supported.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 1         | 14   | 100BASE-TX full-duplex ability. Supported by this PHY.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 1         | 13   | 100BASE-TX half-duplex ability. Supported by this PHY.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 1         | 12   | 10BASE-T full-duplex ability. Supported by this PHY.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 1         | 11   | 10BASE-T half-duplex ability. Supported by this PHY.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Reserved  | 10–7 | Reserved. Read and write as 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 1         | 6    | Management frame preamble suppression. This PHY accepts management frames with the preamble suppressed. Management frames sent over MDIO do not need to be preceded by the preamble pattern of 32 1s.                                                                                                                                                                                                                                                                                                                                     |

| AUTOCMPLT | 5    | Autoconfiguration complete. When AUTOCMPLT is read as 1, it indicates that the autonegotiation process has completed and the values of registers AN_adv, AN_lpa, AN_exp, and AN_np are valid. If autonegotiation is in progress, or has been restarted and AUTORSRT is still set to 1, or has been disabled by clearing AUTOENB to 0, the AUTOCMPLT bit reads as 0.                                                                                                                                                                       |

| RFAULT    | 4    | Remote fault. The RFAULT bit is set to 1 during autonegotiation if an error in the protocol is detected and negotiation is restarted. If the negotiation involved the exchange of multiple next pages, this bit indicates that the first of those pages needs to be reloaded into AN_np due to the restart. RFAULT is latched as 1 until the register is read. The default value of RFAULT is 0.                                                                                                                                          |

| 1         | 3    | Autonegotiation ability. Supported by this PHY.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|           |      | Link status. In general, when LINK is set to 1, the PHY is reporting that a good link is available to the link partner for exchange of data. The value of LINK is latched until the register is read. The default value of LINK is 1.                                                                                                                                                                                                                                                                                                     |