# Intel® Server Board S1200KP

## *Technical Product Specification*

*Intel order number G38894-002*

**Revision 1.1**

**April, 2012**

**Enterprise Platforms and Services Division – Marketing**

## Revision History

| Date       | Revision Number | Modifications                             |

|------------|-----------------|-------------------------------------------|

| July 2011  | 1.0             | Initial release.                          |

| April 2012 | 1.1             | Added info for DBS1200KPR and BBS1200KPR. |

## Disclaimers

Information in this document is provided in connection with Intel® products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel®'s Terms and Conditions of Sale for such products, Intel® assumes no liability whatsoever, and Intel® disclaims any express or implied warranty, relating to sale and/or use of Intel® products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel® products are not intended for use in medical, life-saving, or life sustaining applications. Intel® may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined". Intel® reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

This document contains information on products in the design phase of development. Do not finalize a design with this information. Revised information will be published when the product is available. Verify with your local sales office that you have the latest datasheet before finalizing a design.

The server boards/chassis referenced in this document may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Intel, Pentium, Itanium, and Xeon are trademarks or registered trademarks of Intel Corporation.

\*Other brands and names may be claimed as the property of others.

Copyright © Intel Corporation 2012. All rights reserved.

## Table of Contents

|                                                        |           |

|--------------------------------------------------------|-----------|

| <b>1. Introduction.....</b>                            | <b>1</b>  |

| 1.1 Intended Audience .....                            | 1         |

| 1.2 What This Document Contains.....                   | 1         |

| 1.3 Typographical Conventions .....                    | 1         |

| <b>2. Product Description .....</b>                    | <b>3</b>  |

| 2.1 Overview .....                                     | 3         |

| 2.1.1 Feature Summary .....                            | 3         |

| 2.1.2 Board Layout.....                                | 5         |

| 2.1.3 Block Diagram.....                               | 7         |

| 2.2 Online Support .....                               | 7         |

| 2.3 Processor.....                                     | 8         |

| 2.3.1 PCI Express* x16 Graphics.....                   | 8         |

| 2.4 System Memory .....                                | 10        |

| 2.4.1 Memory Configurations .....                      | 11        |

| 2.5 Intel® C206 Chipset .....                          | 13        |

| 2.6 Graphics Subsystem .....                           | 13        |

| 2.6.1 Integrated Graphics .....                        | 13        |

| 2.6.2 USB .....                                        | 13        |

| 2.7 SATA Interfaces .....                              | 14        |

| 2.8 Real-Time Clock Subsystem .....                    | 15        |

| 2.9 Legacy I/O Controller .....                        | 15        |

| 2.10 LAN Subsystem.....                                | 16        |

| 2.10.1 Intel® 82574L Gigabit Ethernet Controller.....  | 16        |

| 2.10.2 Intel® 82579LM Gigabit Ethernet Controller..... | 16        |

| 2.10.3 LAN Subsystem Software .....                    | 17        |

| 2.10.4 RJ-45 LAN Connector with Integrated LEDs .....  | 17        |

| 2.11 Hardware Management Subsystem.....                | 18        |

| 2.11.1 Hardware Monitoring .....                       | 18        |

| 2.11.2 Fan Monitoring .....                            | 18        |

| 2.11.3 Chassis Intrusion and Detection.....            | 18        |

| 2.11.4 Thermal Monitoring .....                        | 19        |

| 2.12 Power Management .....                            | 20        |

| 2.12.1 ACPI .....                                      | 20        |

| 2.12.2 Hardware Support .....                          | 22        |

| <b>3. Technical Reference.....</b>                     | <b>27</b> |

| 3.1 Memory Resources .....                             | 27        |

| 3.1.1 Addressable Memory .....                         | 27        |

| 3.1.2 Memory Map .....                                 | 29        |

| 3.2 Connectors and Headers.....                        | 29        |

| 3.2.1 Back Panel Connectors.....                       | 29        |

| 3.2.2 Component-side Connectors and Headers .....      | 30        |

| 3.3 Jumper Block .....                                 | 38        |

| 3.4 Mechanical Considerations.....                     | 39        |

|           |                                                    |           |

|-----------|----------------------------------------------------|-----------|

| 3.4.1     | Form Factor .....                                  | 39        |

| 3.5       | Electrical Considerations .....                    | 40        |

| 3.5.1     | Power Supply Considerations .....                  | 40        |

| 3.5.2     | Fan Header Current Capability .....                | 41        |

| 3.5.3     | Add-in Board Considerations .....                  | 41        |

| 3.6       | Thermal Considerations .....                       | 41        |

| 3.7       | Reliability .....                                  | 44        |

| 3.8       | Environmental .....                                | 44        |

| <b>4.</b> | <b>Overview of BIOS Features .....</b>             | <b>45</b> |

| 4.1       | Introduction .....                                 | 45        |

| 4.2       | BIOS Flash Memory Organization .....               | 46        |

| 4.3       | System Management BIOS (SMBIOS) .....              | 46        |

| 4.4       | Legacy USB Support .....                           | 46        |

| 4.5       | BIOS Updates .....                                 | 47        |

| 4.5.1     | Language Support .....                             | 47        |

| 4.5.2     | Custom Splash Screen .....                         | 47        |

| 4.6       | BIOS Recovery .....                                | 48        |

| 4.6.1     | Recovery with USB Thumb Drive or CD-ROM .....      | 48        |

| 4.7       | Boot Options .....                                 | 48        |

| 4.7.1     | Optical Drive Boot .....                           | 49        |

| 4.7.2     | Network Boot .....                                 | 49        |

| 4.7.3     | Booting Without Attached Devices .....             | 49        |

| 4.7.4     | Changing the Default Boot Device During POST ..... | 49        |

| 4.8       | Adjusting Boot Speed .....                         | 49        |

| 4.8.1     | Peripheral Selection and Configuration .....       | 49        |

| 4.8.2     | BIOS Boot Optimizations .....                      | 50        |

| 4.9       | BIOS Security Features .....                       | 50        |

| <b>5.</b> | <b>Error Messages and Beep Codes .....</b>         | <b>52</b> |

| 5.1       | Speaker .....                                      | 52        |

| 5.2       | BIOS Beep Codes .....                              | 52        |

| 5.3       | Front-panel Power LED Blink Codes .....            | 53        |

| 5.4       | BIOS Error Messages .....                          | 53        |

| 5.5       | Port 80h POST Codes .....                          | 53        |

## ***List of Figures***

|                                                                     |    |

|---------------------------------------------------------------------|----|

| Figure 1. Major Board Components .....                              | 5  |

| Figure 2. Block Diagram .....                                       | 7  |

| Figure 3. Memory Channel and DIMM Configuration .....               | 12 |

| Figure 4. LAN Connector LED Locations .....                         | 17 |

| Figure 5. Thermal Sensors and Fan Headers .....                     | 19 |

| Figure 6. Location of the Standby Power LED .....                   | 25 |

| Figure 7. Detailed System Memory Address Map .....                  | 28 |

| Figure 8. Back Panel Connectors .....                               | 30 |

| Figure 9. Component-side Connectors and Headers .....               | 31 |

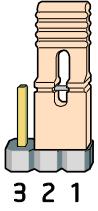

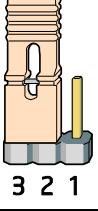

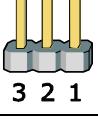

| Figure 10. Connection Diagram for Front Panel Header .....          | 35 |

| Figure 11. Connection Diagram for Front Panel USB 2.0 Headers ..... | 36 |

| Figure 12. Location of the Jumper Block .....                       | 38 |

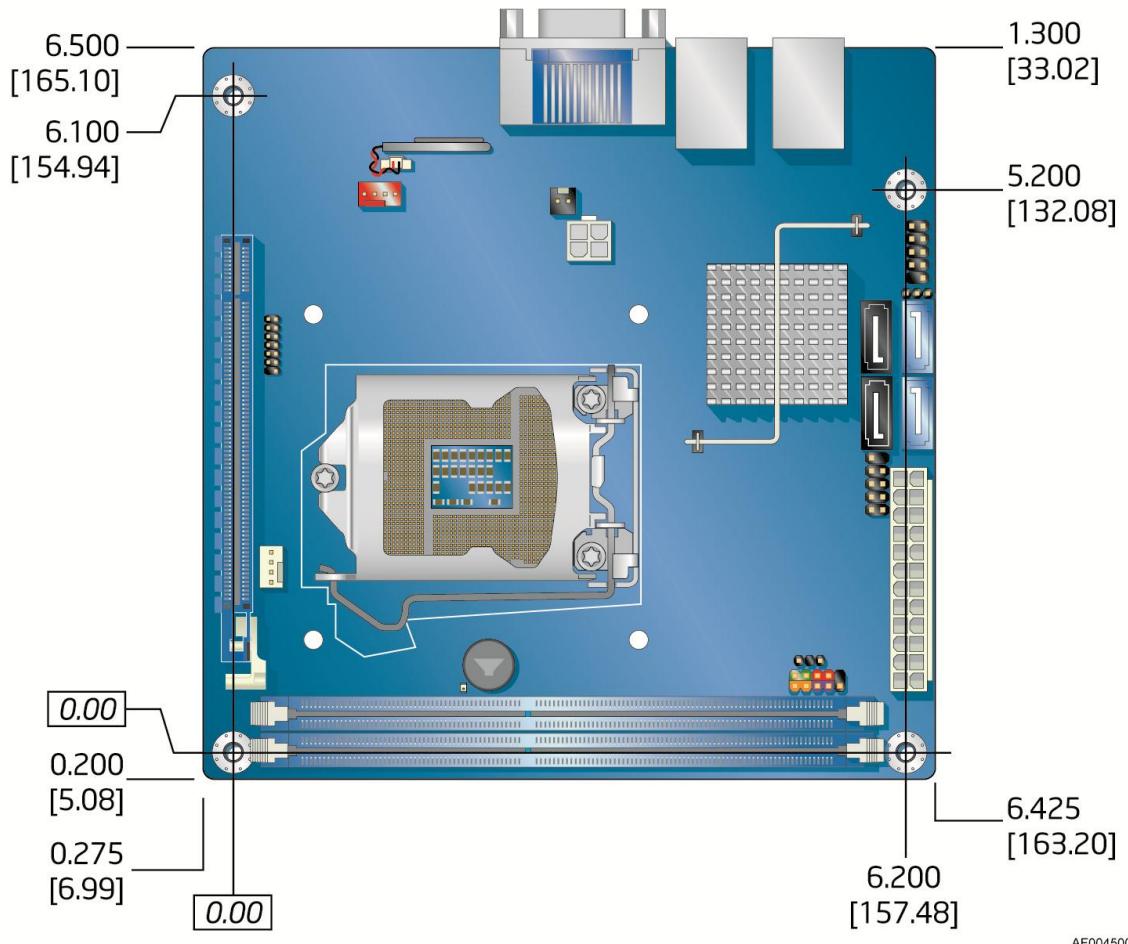

| Figure 13. Board Dimensions.....                                    | 40 |

| Figure 14. Localized High Temperature Zones .....                   | 43 |

## ***List of Tables***

|                                                                         |    |

|-------------------------------------------------------------------------|----|

| Table 1. Feature Summary .....                                          | 3  |

| Table 2. Components Shown in Figure 1 .....                             | 6  |

| Table 3. Reference URLs for Online Suppot .....                         | 7  |

| Table 4. Information on Supported Processors .....                      | 8  |

| Table 5. Information on PCI Express* Technology .....                   | 9  |

| Table 6. Supported Memory Configurations .....                          | 10 |

| Table 7. Information on System Memory .....                             | 10 |

| Table 8. Information on Resouces Used by the Chipset .....              | 13 |

| Table 9. DVI Port Status Conditions .....                               | 13 |

| Table 10. Information on USB Connectors .....                           | 14 |

| Table 11. Information on SATA Connector Locations .....                 | 14 |

| Table 12. Information on LAN Software and Drivers .....                 | 16 |

| Table 13. Information on Obtaining LAN Software and Drivers .....       | 17 |

| Table 14. LAN Connector LED States .....                                | 18 |

| Table 15. Information on the Function of the Fan Headers .....          | 18 |

| Table 16. Information on the Chassis Intrusion Headers .....            | 18 |

| Table 17. Effects of Pressing the Power Switch .....                    | 20 |

| Table 18. Power States and Targeted System Power .....                  | 21 |

| Table 19. Wake-up Devices and Events .....                              | 21 |

| Table 20. Information on Power Connector Locations .....                | 22 |

| Table 21. Information of the Fan Headers' Locations .....               | 23 |

| Table 22. System Memory Map .....                                       | 29 |

| Table 23. Component-side Connectors and Headers Shown in Figure 9 ..... | 32 |

| Table 24. Front Panel USB 2.0 Headers .....                             | 32 |

| Table 25. SATA Connectors .....                                         | 32 |

| Table 26. Chassis Intrusion Header .....                                | 33 |

| Table 27. Processor and System (4-Pin) Fan Headers .....                | 33 |

| Table 28. Processor Core Power Connector .....                          | 33 |

| Table 29. Main Power Connector .....                                    | 33 |

| Table 30. Front Panel Header .....                                      | 34 |

| Table 31. States for a One-Color Power LED .....                        | 35 |

| Table 32. States for a Two-Color Power LED .....                        | 35 |

| Table 33. Alternate Front Panel Power/Sleep LED Header .....            | 36 |

| Table 34. LPC Debug Header .....                                        | 37 |

| Table 35. BIOS Setup Configuration Jumper Settings .....                | 39 |

| Table 36. Recommended Power Supply Current Values .....                 | 41 |

| Table 37. Fan Header Current Capability .....                           | 41 |

| Table 38. Thermal Considerations for Components .....                   | 43 |

| Table 39. Tcontrol Values for Components .....                          | 43 |

| Table 40. Environmental Specifications .....                            | 44 |

| Table 41. BIOS Setup Program Menu Bar .....                             | 45 |

| Table 42. BIOS Setup Program Function Keys .....                        | 45 |

| Table 43. Information on Integrator Toolkit and Software Tools .....    | 47 |

| Table 44. Acceptable Drives/Media Types for BIOS Recovery .....         | 48 |

| Table 45. Boot Device Menu Options .....                                | 49 |

| Table 46. Supervisor and User Password Functions .....                  | 51 |

|                                                   |    |

|---------------------------------------------------|----|

| Table 47. Information about Onboard Speaker ..... | 52 |

| Table 48. BIOS Beep Codes .....                   | 52 |

| Table 49. Front-panel Power LED Blink Codes ..... | 53 |

| Table 50. BIOS Error Messages .....               | 53 |

| Table 51. Port 80h POST Code Ranges .....         | 54 |

| Table 52. Port 80h POST Codes .....               | 54 |

| Table 53. Typical Port 80h POST Sequence .....    | 57 |

**<This page is intentionally left blank.>**

# 1. Introduction

---

This Technical Product Specification (TPS) specifies the board layout, components, connectors, power and environmental requirements, and the BIOS for Intel® Server Board S1200KP.

## 1.1 Intended Audience

The TPS is intended to provide detailed, technical information about Intel® Server Board S1200KP and its components to the vendors, system integrators, and other engineers and technicians who need this level of information. It is specifically not intended for general audiences.

## 1.2 What This Document Contains

| Chapter | Description                                                          |

|---------|----------------------------------------------------------------------|

| 1       | A description of the hardware used on Intel® Server Board S1200KP.   |

| 2       | A map of the resources of the Intel® Server Board.                   |

| 3       | The features supported by the BIOS Setup program.                    |

| 4       | Descriptions of the BIOS error messages, beep codes, and POST codes. |

## 1.3 Typographical Conventions

This section contains information about the conventions used in this specification. Not all of these symbols and abbreviations appear in all specifications of this type.

### Notes, Cautions, and Warnings

**Note:** Notes call attention to important information.

### CAUTION

*Cautions are included to help you avoid damaging hardware or losing data.*

### Other Common Notation

|         |                                                                             |

|---------|-----------------------------------------------------------------------------|

| #       | Used after a signal name to identify an active-low signal (such as USBP0#). |

| GB      | Gigabyte (1,073,741,824 bytes).                                             |

| GB/s    | Gigabytes per second.                                                       |

| Gb/s    | Gigabits per second.                                                        |

| KB      | Kilobyte (1024 bytes).                                                      |

| Kbit    | Kilobit (1024 bits).                                                        |

| kbits/s | 1000 bits per second.                                                       |

| MB      | Megabyte (1,048,576 bytes).                                                 |

| MB/s    | Megabytes per second.                                                       |

| Mbit    | Megabit (1,048,576 bits).                                                   |

|         |                                                                                                                |

|---------|----------------------------------------------------------------------------------------------------------------|

| Mbits/s | Megabits per second.                                                                                           |

| xxh     | An address or data value ending with a lowercase h indicates a hexadecimal value.                              |

| x.x V   | Volts. Voltages are DC unless otherwise specified.                                                             |

| *       | This symbol is used to indicate third-party brands and names that are the property of their respective owners. |

## 2. Product Description

---

### 2.1 Overview

#### 2.1.1 Feature Summary

Table 1 summarizes the major features of the board.

**Table 1. Feature Summary**

| Feature                | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Form Factor</b>     | Mini-ITX (6.7 inches by 6.7 inches [170.18 millimeters by 170.18 millimeters])                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Processor              | <ul style="list-style-type: none"> <li>▪ Intel® Xeon® E3-1200 Processors, the 2<sup>nd</sup> Generation Intel® Core™ i3 Processors, Intel® Xeon® E3-1200 V2 Processors or the 3<sup>rd</sup> Generation Intel® Core™ i3 Processors with up to 95W TDP in an LGA1155 socket <sup>1,2</sup> <ul style="list-style-type: none"> <li>○ One PCI Express* 2.0 x16 (with Intel® Xeon® E3-1200 Processors or the 2<sup>nd</sup> Generation Intel® Core™ i3 Processors) or PCI Express* 3.0 x 16 (with Intel® Xeon® E3-1200 V2 Processors or the 3<sup>rd</sup> Generation Intel® Core™ i3 Processors) graphics interface</li> <li>○ Integrated memory controller with dual channel DDR3 memory support</li> <li>○ Integrated graphics processing (processors with Intel® Graphics Technology)</li> </ul> </li> </ul> |

| Memory                 | <ul style="list-style-type: none"> <li>▪ Two 240-pin DDR3 DRAM Dual Inline Memory Module (DIMM) sockets</li> <li>▪ Support for DDR3 1066/1333 MHz (with Intel® Xeon® E3-1200 Processors or the 2<sup>nd</sup> Generation Intel® Core™ i3 Processors) or DDR3 1333/1600 MHz (with Intel® Xeon® E3-1200 V2 Processors or the 3<sup>rd</sup> Generation Intel® Core™ i3 Processors) DIMMs</li> <li>▪ Support for 1Gb, 2Gb, and 4Gb memory technology</li> <li>▪ Support for up to 16 GB of system memory with two DIMMs using 4 Gb memory technology</li> <li>▪ Support for ECC and non-ECC memory <sup>3</sup></li> </ul>                                                                                                                                                                                      |

| Chipset                | Intel® C206 Platform Controller Hub (PCH) Chipset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Graphics               | <ul style="list-style-type: none"> <li>▪ Integrated graphics support for processors with Intel® Graphics Technology: <ul style="list-style-type: none"> <li>○ DVI-I</li> </ul> </li> <li>▪ Discrete graphics support for PCI Express* 2.0 x16 (with Intel® Xeon® E3-1200 Processors or the 2<sup>nd</sup> Generation Intel® Core™ i3 Processors) or PCI Express* 3.0 x 16 (with Intel® Xeon® E3-1200 V2 Processors or the 3<sup>rd</sup> Generation Intel® Core™ i3 Processors) add-in graphics card</li> </ul>                                                                                                                                                                                                                                                                                              |

| Peripheral Interfaces  | <ul style="list-style-type: none"> <li>▪ Eight USB 2.0 ports: <ul style="list-style-type: none"> <li>○ Four ports are implemented with stacked back panel connectors (black)</li> <li>○ Four front panel ports implemented through three internal headers</li> </ul> </li> <li>▪ Two SATA 6.0Gb/s interfaces through Intel® C206 Chipset with Intel® Rapid Storage Technology RAID support (blue)</li> <li>▪ Two SATA 3.0Gb/s interfaces through Intel® C206 Chipset with Intel® Rapid Storage Technology RAID support (black)</li> </ul>                                                                                                                                                                                                                                                                    |

| Expansion Capabilities | <ul style="list-style-type: none"> <li>▪ One PCI Express* 2.0 x16 (with Intel® Xeon® E3-1200 Processors or the 2<sup>nd</sup> Generation Intel® Core™ i3 Processors) or PCI Express* 3.0 x 16 (with Intel® Xeon® E3-1200 V2 Processors or the 3<sup>rd</sup> Generation Intel® Core™ i3 Processors) add-in card connector</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Feature                           | Description                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BIOS                              | <ul style="list-style-type: none"> <li>▪ Intel® BIOS resident in the Serial Peripheral Interface (SPI) Flash device</li> <li>▪ Support for Advanced Configuration and Power Interface (ACPI), Plug and Play, and System Management BIOS (SMBIOS)</li> </ul>                                                                                                                                                                        |

| Instantly Available PC Technology | <ul style="list-style-type: none"> <li>▪ Support for PCI Express* Revision 2.0 (with Intel® Xeon® E3-1200 Processors or the 2<sup>nd</sup> Generation Intel® Core™ i3 Processors) or PCI Express* Revision 3.0 (with Intel® Xeon® E3-1200 V2 Processors or the 3<sup>rd</sup> Generation Intel® Core™ i3 Processors)</li> <li>▪ Suspend to RAM support</li> <li>▪ Wake on PCI Express*, LAN, front panel, and USB ports</li> </ul> |

| LAN Support                       | <ul style="list-style-type: none"> <li>▪ Gigabit (10/100/1000Mbits/s) LAN subsystem using the Intel® 82574 and 82579 Gigabit Ethernet Controller</li> </ul>                                                                                                                                                                                                                                                                        |

| Legacy I/O Control                | <ul style="list-style-type: none"> <li>▪ Nuvoton* W83677HG-i I/O controller for hardware management support</li> </ul>                                                                                                                                                                                                                                                                                                             |

| Hardware Monitor Subsystem        | <ul style="list-style-type: none"> <li>▪ Hardware monitoring through the Nuvoton I/O controller</li> <li>▪ Voltage sense to detect out of range power supply voltages</li> <li>▪ Thermal sense to detect out of range thermal values</li> <li>▪ Two fan headers</li> <li>▪ Two fan sense inputs used to monitor fan activity</li> <li>▪ Fan speed control</li> </ul>                                                               |

**Notes:**

1. Pairing a mini-ITX chassis and more than 65W TDP processor with the supplied standard Intel® thermal solution may not meet Intel®'s thermal requirement standard. Please verify that your thermal solution and chassis will meet the necessary thermal requirements. Failing to do so may cause the processor to throttle, significantly decreasing system performance.

2. The product codes of DBS1200KP and BBS1200KP can only support Intel® Xeon® E3-1200 Processors or the 2<sup>nd</sup> Generation Intel® Core™ i3 Processors. The product codes of DBS1200KPR and BBS1200KPR can support Intel® Xeon® E3-1200 Processors, the 2<sup>nd</sup> Generation Intel® Core™ i3 Processors, Intel® Xeon® E3-1200 V2 Processors or the 3<sup>rd</sup> Generation Intel® Core™ i3 Processors.

3. ECC DIMMS are recommended to use for server system.

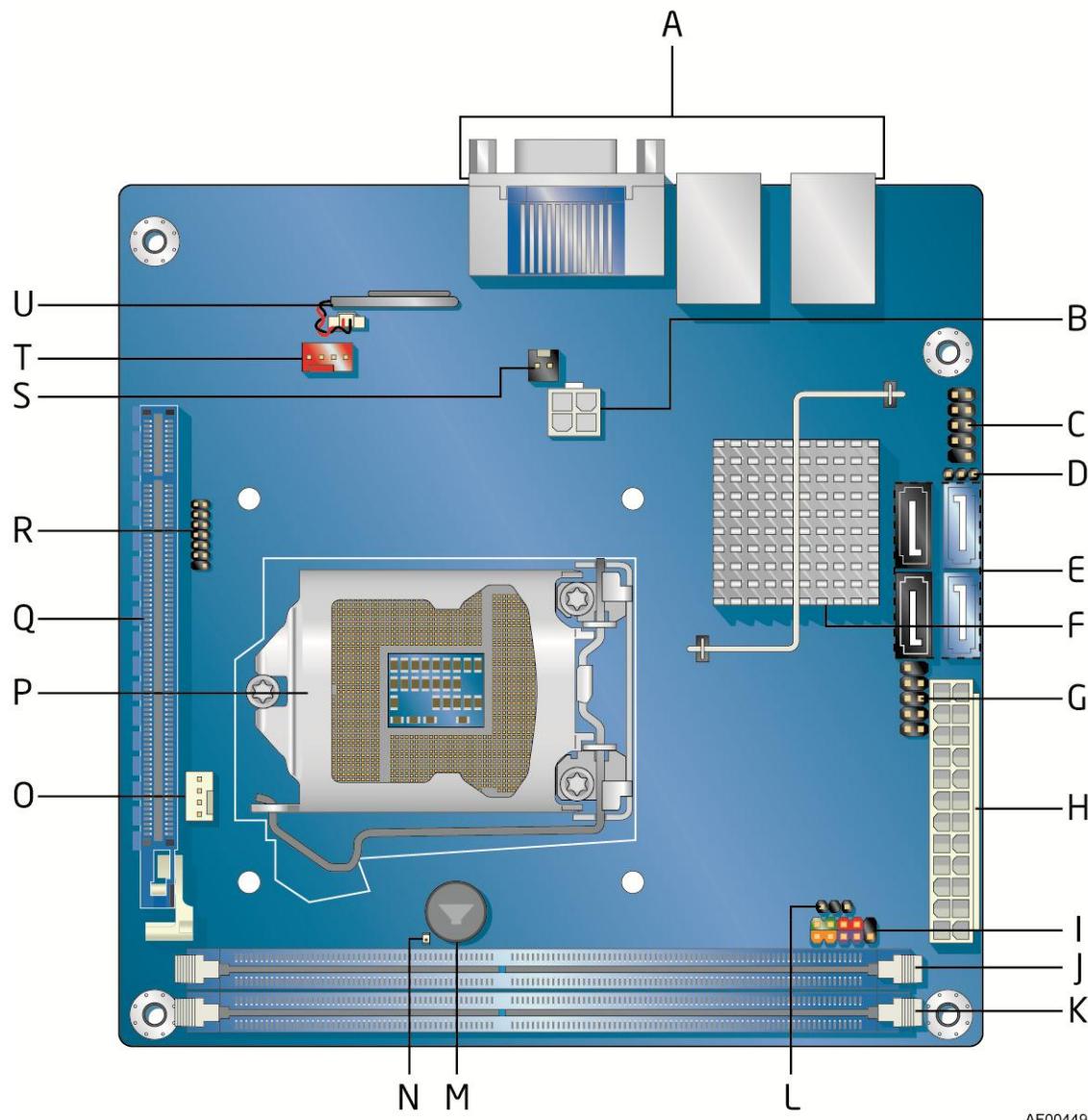

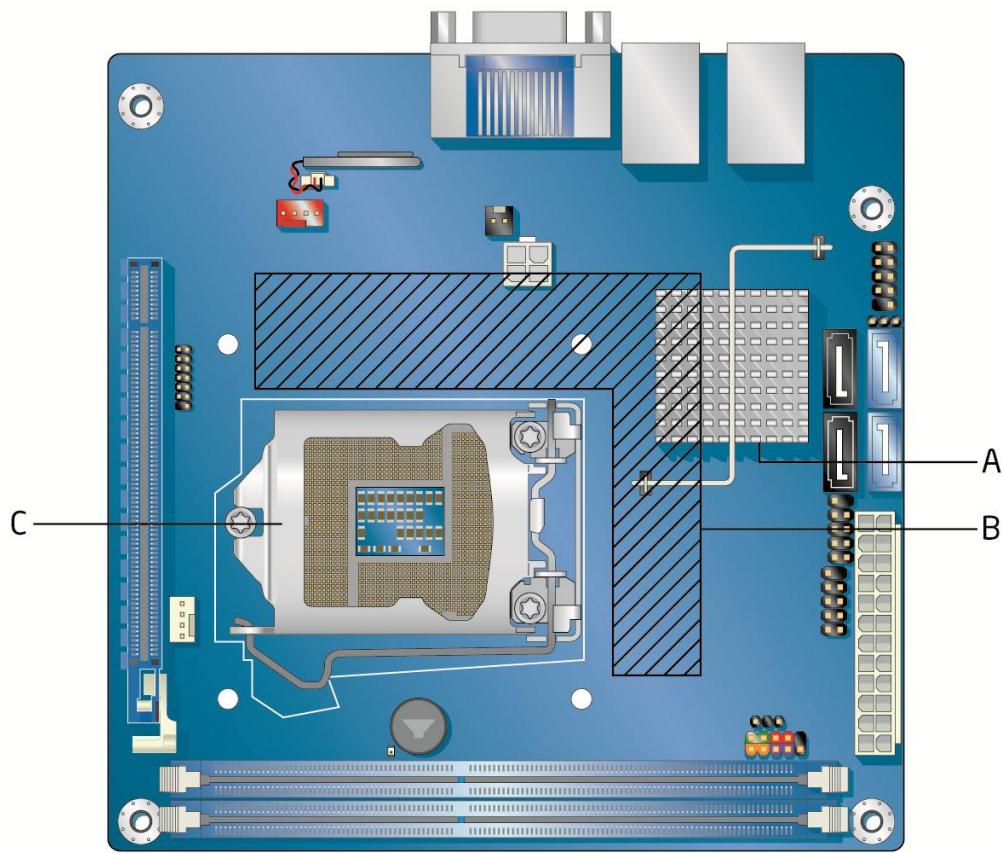

## 2.1.2 Board Layout

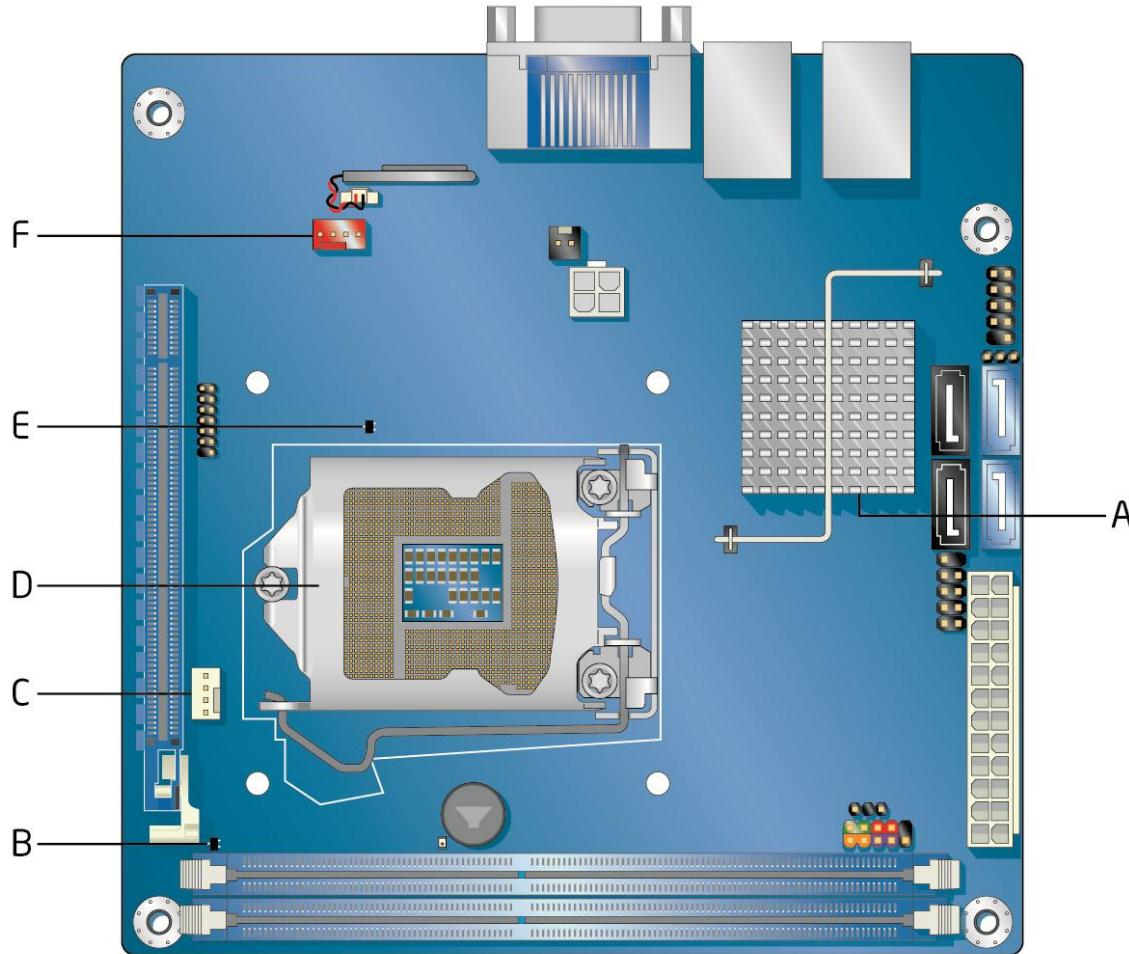

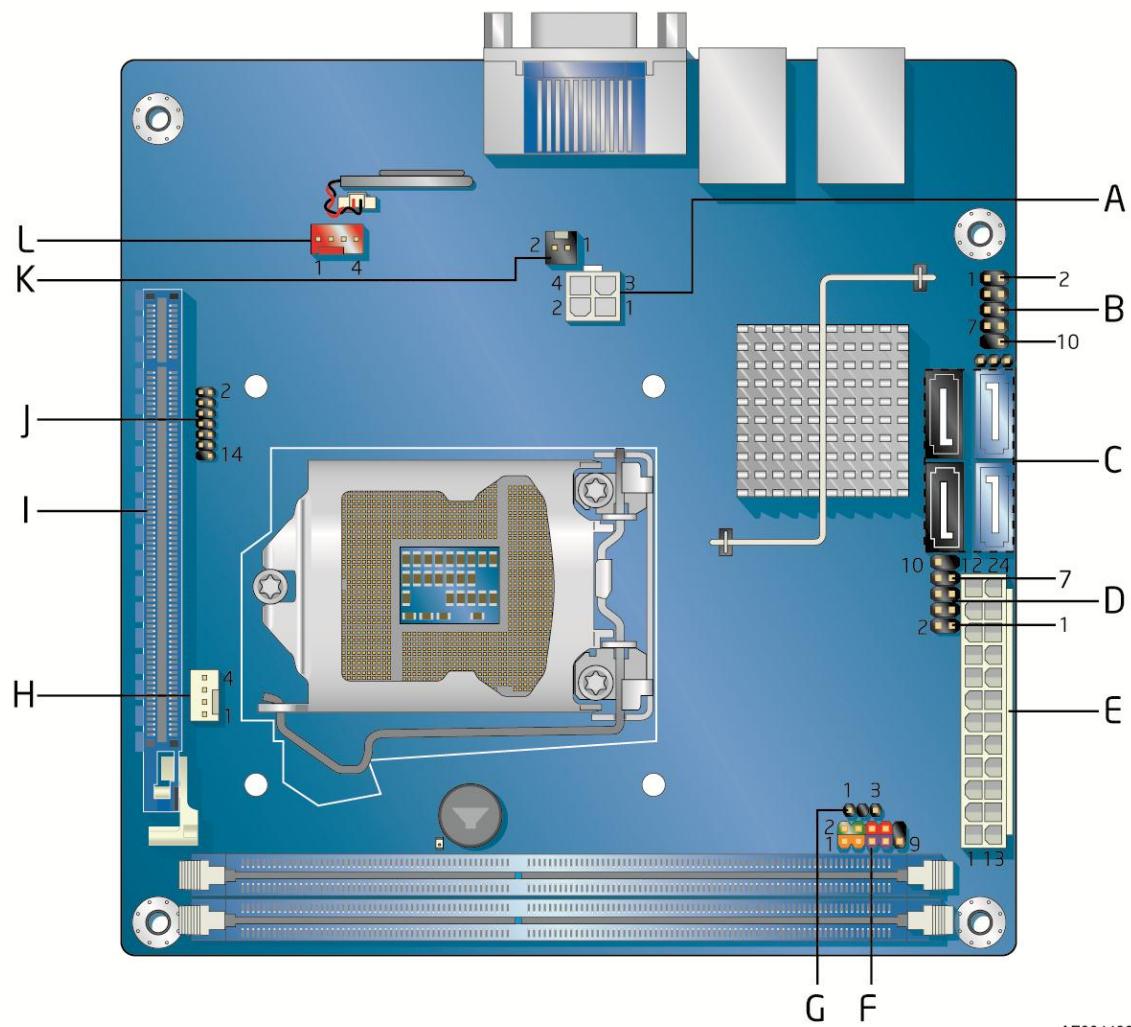

Following figure shows the location of the major components on Intel® Server Board S1200KP:

**Figure 1. Major Board Components**

Table 2 lists the components identified in Figure 1.

**Table 2. Components Shown in Figure 1**

| Item/callout | Description                                |

|--------------|--------------------------------------------|

| A            | Back panel connectors                      |

| B            | Processor core power connector (2 x 2)     |

| C            | Front panel USB 2.0 header                 |

| D            | BIOS Setup configuration jumper block      |

| E            | SATA connectors                            |

| F            | Intel® C206 Chipset                        |

| G            | Front panel USB 2.0 header                 |

| H            | Main power connector (2 x 12)              |

| I            | Front panel header                         |

| J            | DIMM 1 (Channel A DIMM 1)                  |

| K            | DIMM 2 (Channel B DIMM 1)                  |

| L            | Alternate front panel power LED header     |

| M            | Piezoelectric speaker                      |

| N            | Standby power LED                          |

| O            | Processor fan header                       |

| P            | LGA1155 processor socket                   |

| Q            | PCI Express* x16 bus add-in card connector |

| R            | Low Pin Count (LPC) Debug header           |

| S            | Chassis intrusion header                   |

| T            | System fan header                          |

| U            | Battery                                    |

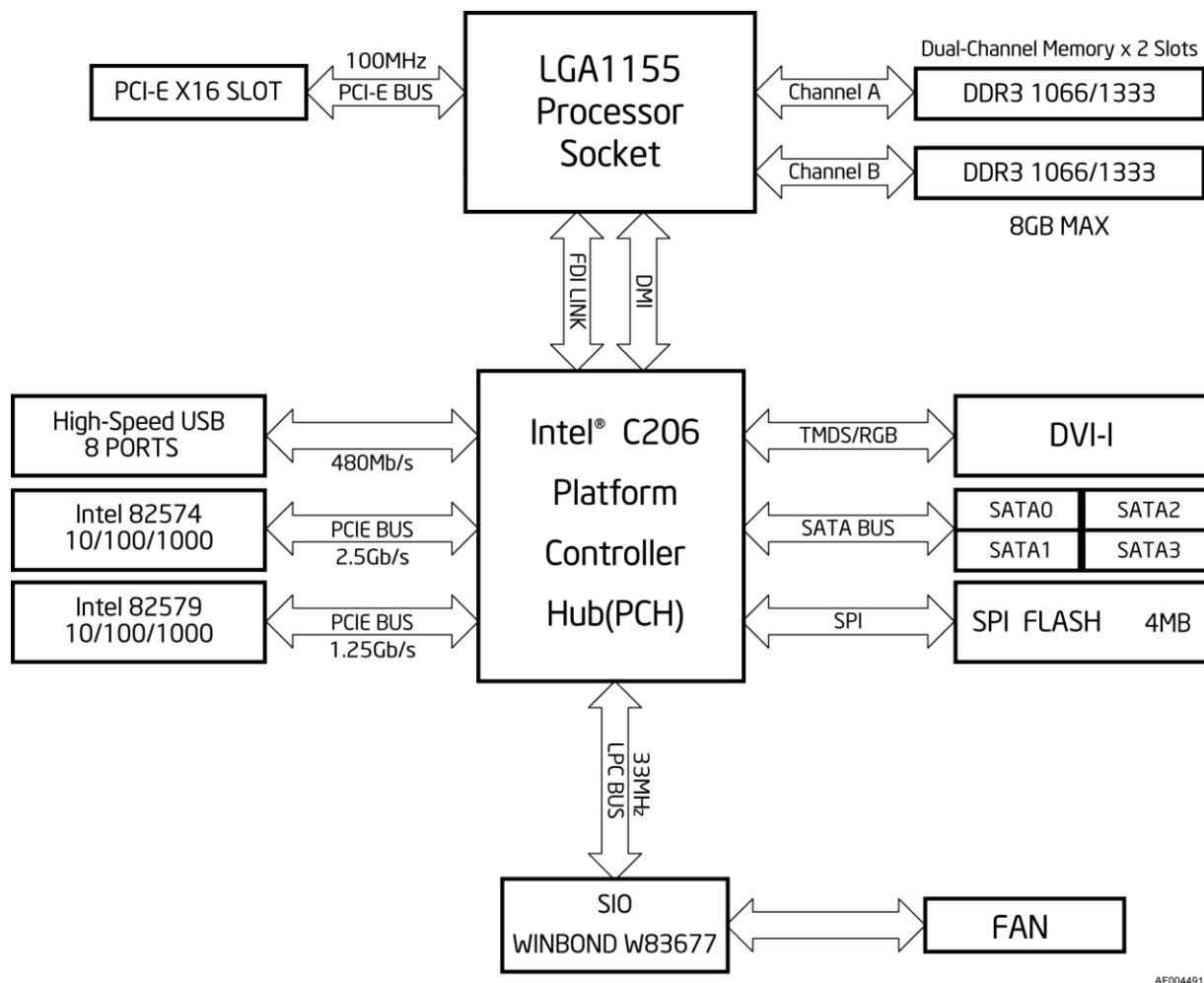

### 2.1.3 Block Diagram

Figure 2 is a block diagram of the major functional areas of the board.

**Figure 2. Block Diagram**

## 2.2 Online Support

**Table 3. Reference URLs for Online Suppot**

| To find information about              | Visit this World Wide Web site:                                                         |

|----------------------------------------|-----------------------------------------------------------------------------------------|

| Intel® Server Board S1200KP            | <a href="http://www.intel.com/products/server">http://www.intel.com/products/server</a> |

| Supported processors and tested memory | <a href="http://serverconfigurator.intel.com">http://serverconfigurator.intel.com</a>   |

| BIOS and driver updates                | <a href="http://downloadcenter.intel.com">http://downloadcenter.intel.com</a>           |

## 2.3 Processor

The board is designed to support the Intel® Xeon® E3-1200 Processors, the 2<sup>nd</sup> Generation Intel® Core™ i3 Processors, Intel® Xeon® E3-1200 V2 Processors or the 3<sup>rd</sup> Generation Intel® Core™ i3 Processors in an LGA1155 socket.

Other processors may be supported in the future. This board is designed to support processors with a maximum wattage of 95 W Thermal Design Power (TDP). The processors listed above are only supported when falling within the wattage requirements of Intel® Server Board S1200KP. See the Intel® web site listed below for the most up-to-date list of supported processors.

**Table 4. Information on Supported Processors**

| For information about | Refer to:                                                                             |

|-----------------------|---------------------------------------------------------------------------------------|

| Supported processors  | <a href="http://serverconfigurator.intel.com">http://serverconfigurator.intel.com</a> |

### **CAUTION**

*Use only the processors listed on the web site above. Use of unsupported processors can damage the board, the processor, and the power supply.*

#### **Notes:**

1. The product codes of DBS1200KP and BBS1200KP can only support Intel® Xeon® E3-1200 Processors or the 2<sup>nd</sup> Generation Intel® Core™ i3 Processors. The product codes of DBS1200KPR and BBS1200KPR can support Intel® Xeon® E3-1200 Processors, the 2<sup>nd</sup> Generation Intel® Core™ i3 Processors, Intel® Xeon® E3-1200 V2 Processors or the 3<sup>rd</sup> Generation Intel® Core™ i3 Processors.

2. This board has specific requirements for providing power to the processor. Refer to Section 3.5.1 on page 40 for information on power supply requirements for this board.

3. Pairing a mini-ITX chassis and more than 65W TDP processor with the supplied standard Intel® thermal solution may not meet Intel®'s thermal requirement standard. Please verify that your thermal solution and chassis will meet the necessary thermal requirements. Failing to do so may cause the processor to throttle, significantly decreasing system performance.

### **2.3.1 PCI Express® x16 Graphics**

The Intel® Xeon® E3-1200 Processors or the 2<sup>nd</sup> Generation Intel® Core™ i3 Processors in an LGA1155 socket support discrete add in graphics cards through the PCI Express® 2.0 x16 graphics connector. And the Intel® Xeon® E3-1200 V2 Processors or the 3<sup>rd</sup> Generation Intel® Core™ i3 Processors in an LGA1155 socket support discrete add in graphics cards through the PCI Express® 3.0 x16 graphics connector:

- Supports PCI Express® GEN3 frequency of 8 GHz resulting in 8.0 Gb/s each direction (1 GB/s) per lane. The maximum theoretical bandwidth on the interface is 16 GB/s in each direction, simultaneously, for an aggregate of 32 GB/s when operating in x16 GEN3 mode.

- Supports PCI Express\* GEN2 frequency of 5 GHz resulting in 5.0 Gb/s each direction (500 MB/s) per lane. The maximum theoretical bandwidth on the interface is 8 GB/s in each direction, simultaneously, for an aggregate of 16 GB/s when operating in x16 GEN2 mode.

- Supports PCI Express\* GEN1 frequency of 2.5 GHz resulting in 2.5 Gb/s each direction (250 MB/s) per lane. The maximum theoretical bandwidth on the interface is 4 GB/s in each direction, simultaneously, for an aggregate of 8 GB/s when operating in x16 GEN1 mode.

**Table 5. Information on PCI Express\* Technology**

| For information about   | Refer to                                                  |

|-------------------------|-----------------------------------------------------------|

| PCI Express* technology | <a href="http://www.pcisig.com">http://www.pcisig.com</a> |

## 2.4 System Memory

The board has two DIMM sockets and supports the following memory features:

- 1.5 V DDR3 DRAM DIMMs with gold plated contacts.

- Two independent memory channels with interleaved mode support

- Unbuffered, single-sided or double-sided DIMMs with the following restriction:

Double-sided DIMMs with x16 organization are not supported.

- 16 GB maximum total system memory (with 4 Gb memory technology). Refer to Section 3.1.1 on page 27 for information on the total amount of addressable memory.

- Minimum recommended total system memory: 512 MB

- ECC and Non-ECC DIMMs

- Serial Presence Detect

- Support for DDR3 1066/1333 MHz (with Intel® Xeon® E3-1200 Processors or the 2<sup>nd</sup> Generation Intel® Core™ i3 Processors) or DDR3 1333/1600 MHz (with Intel® Xeon® E3-1200 V2 Processors or the 3<sup>rd</sup> Generation Intel® Core™ i3 Processors) DIMMs

**Notes:**

1. To be fully compliant with all applicable DDR DRAM memory specifications, the board should be populated with DIMMs that support the Serial Presence Detect (SPD) data structure. This allows the BIOS to read the SPD data and program the chipset to accurately configure memory settings for optimum performance. If non-SPD memory is installed, the BIOS will attempt to correctly configure the memory settings, but performance and reliability may be impacted or the DIMMs may not function under the determined frequency.

2. ECC DIMMS are recommended to use for server system.

Table 6 lists the supported DIMM configurations.

**Table 6. Supported Memory Configurations**

| DIMM Capacity | Configuration (Note) | DRAM Density | DRAM Organization Front-side/Back-side | Number of DRAM Devices Non-ECC/ECC |

|---------------|----------------------|--------------|----------------------------------------|------------------------------------|

| 512 MB        | SS                   | 1 Gbit       | 1 Gb x16/empty                         | 4/NA                               |

| 1024 MB       | SS                   | 1 Gbit       | 1 Gb x8/empty                          | 8/9                                |

| 2048 MB       | DS                   | 1 Gbit       | 1 Gb x8/1 Gb x8                        | 16/18                              |

| 2048 MB       | SS                   | 2 Gbit       | 2 Gb x8/empty                          | 8/9                                |

| 4096 MB       | DS                   | 2 Gbit       | 2 Gb x8/2 Gb x8                        | 16/18                              |

| 8192 MB       | DS                   | 4 Gbit       | 4 Gb x8/4Gb x8                         | 16/18                              |

**Note:** “DS” refers to double-sided memory modules (containing two rows of DRAM) and “SS” refers to single-sided memory modules (containing one row of DRAM).

**Table 7. Information on System Memory**

|                       |                                                                                       |

|-----------------------|---------------------------------------------------------------------------------------|

| For information about | Refer to:                                                                             |

| Tested Memory         | <a href="http://serverconfigurator.intel.com">http://serverconfigurator.intel.com</a> |

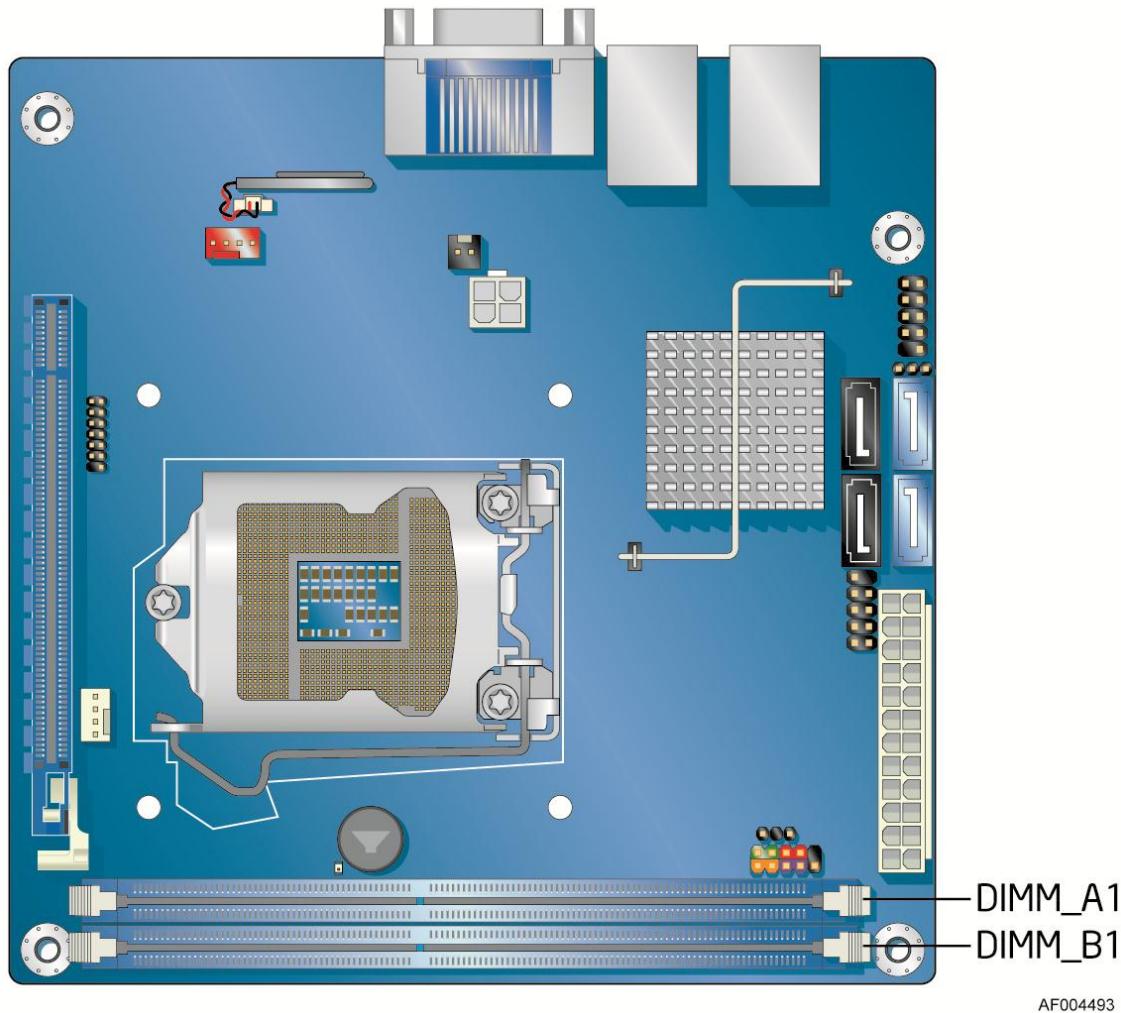

## 2.4.1 Memory Configurations

The Intel® Xeon® E3-1200 Processors, the 2<sup>nd</sup> Generation Intel® Core™ i3 Processors, Intel® Xeon® E3-1200 V2 Processors or the 3<sup>rd</sup> Generation Intel® Core™ i3 Processors in the LGA1155 socket support the following types of memory organization:

- **Dual channel (Interleaved) mode.** This mode offers the highest throughput for real world applications. Dual channel mode is enabled when the installed memory capacities of both DIMM channels are equal. Technology and device width can vary from one channel to the other but the installed memory capacity for each channel must be equal. If different speed DIMMs are used between channels, the slowest memory timing will be used.

- **Single channel (Asymmetric) mode.** This mode is equivalent to single channel bandwidth operation for real world applications. This mode is used when only a single DIMM is installed or the memory capacities are unequal. Technology and device width can vary from one channel to the other. If different speed DIMMs are used between channels, the slowest memory timing will be used.

- **Flex mode.** This mode provides the most flexible performance characteristics. The bottommost DRAM memory (the memory that is lowest within the system memory map) is mapped to dual channel operation; the topmost DRAM memory (the memory that is nearest to the 8 GB address space limit), if any, is mapped to single channel operation. Flex mode results in multiple zones of dual and single channel operation across the whole of DRAM memory. To use flex mode, it is necessary to populate both channels.

Figure 3 illustrates the memory channel and DIMM configuration.

**Figure 3. Memory Channel and DIMM Configuration**

**Note:** The Intel® Xeon® E3-1200 Processors, the 2<sup>nd</sup> Generation Intel® Core™ i3 Processors, Intel® Xeon® E3-1200 V2 Processors or the 3<sup>rd</sup> Generation Intel® Core™ i3 Processors require memory to be populated in the DIMM\_A1 (Channel A, DIMM 1) socket.

## 2.5 Intel® C206 Chipset

Intel® C206 Chipset with Direct Media Interface (DMI) interconnect provides interfaces to the processor and the USB, SATA, LPC, LAN and PCI Express\* interfaces. The Intel® C206 Chipset is a centralized controller for the board's I/O paths.

**Table 8. Information on Resources Used by the Chipset**

| For information about         | Refer to                  |

|-------------------------------|---------------------------|

| Resources used by the chipset | <a href="#">Chapter 2</a> |

## 2.6 Graphics Subsystem

The board supports graphics through either Intel® Graphics Technology or a PCI Express\* 2.0 x16 (with Intel® Xeon® E3-1200 Processors or the 2<sup>nd</sup> Generation Intel® Core™ i3 Processors) or PCI Express\* 3.0 x 16 (with Intel® Xeon® E3-1200 V2 Processors or the 3<sup>rd</sup> Generation Intel® Core™ i3 Processors) add-in graphics card.

### 2.6.1 Integrated Graphics

The board supports integrated graphics through the Intel® Flexible Display Interface (Intel® FDI) for processors with Intel® Graphics Technology.

#### 2.6.1.1 Digital Visual Interface (DVI-I)

The DVI-I port supports both digital and analog DVI displays. The maximum supported resolution is 1900 x 1200 (WUXGA). The DVI port is compliant with the DVI 1.0 specification. DVI analog output can also be converted to VGA using a DVI-VGA converter.

Depending on the type of add-in card installed in the PCI Express\* x16 connector, the DVI port will behave as described in Table 9.

**Table 9. DVI Port Status Conditions**

| PCI Express* x16 Connector Status               | DVI Digital (DVI-D) Port Status | DVI Analog (DVI-A) Port Status <sup>(Note 1)</sup> |

|-------------------------------------------------|---------------------------------|----------------------------------------------------|

| No add-in card installed                        | Enabled                         | Enabled                                            |

| Non-video PCI Express* x1 add-in card installed | Enabled                         | Enabled                                            |

| PCI Express* x16 add-in card installed          | Enabled                         | Enabled <sup>(Note 2)</sup>                        |

**Notes:**

1. DVI analog output can also be converted to VGA with a DVI-VGA converter.

2. May require BIOS setup menu changes.

### 2.6.2 USB

The board supports up to eight USB 2.0 ports.

The Intel® C206 Chipset provides the USB controller for the 2.0 ports. The port arrangement is as follows:

- Four USB 2.0 ports are implemented with stacked back panel connectors (black)

- Four USB 2.0 front panel ports implemented through three internal headers

All eight USB ports are high-speed, full-speed, and low-speed capable.

**Note:** Computer systems that have an unshielded cable attached to a USB port may not meet FCC Class B requirements, even if no device is attached to the cable. Use a shielded cable that meets the requirements for full-speed devices.

**Table 10. Information on USB Connectors**

| For information about                                | Refer to          |

|------------------------------------------------------|-------------------|

| The location of the USB connectors on the back panel | Figure 8, page 30 |

| The location of the front panel USB headers          | Figure 9, page 31 |

## 2.7 SATA Interfaces

The board provides five SATA connectors through the PCH, which support one device per connector:

- Two internal SATA 6.0 Gb/s connectors (blue)

- Two internal SATA 3.0 Gb/s connectors (black)

The PCH provides independent SATA ports with a theoretical maximum transfer rate of 6 Gb/s for two ports and 3 Gb/s for the other two ports. A point-to-point interface is used for host to device connections.

The underlying SATA functionality is transparent to the operating system. The SATA controller can operate in both legacy and native modes. In legacy mode, standard IDE I/O and IRQ resources are assigned (IRQ 14 and 15). In Native mode, standard PCI Conventional bus resource steering is used. Native mode is the preferred mode for configurations using the Windows 7\* operating systems.

**Note:** Many SATA drives use new low-voltage power connectors and require adapters or power supplies equipped with low-voltage power connectors.

For more information, see: <http://www.serialata.org/>.

**Table 11. Information on SATA Connector Locations**

| For information about               | Refer to          |

|-------------------------------------|-------------------|

| The location of the SATA connectors | Figure 9, page 31 |

### 2.7.1.1 SATA RAID

The board supports Intel® Rapid Storage Technology which provides the following RAID (Redundant Array of Independent Drives) levels through the Intel® C206 Chipset:

- RAID 0 - data striping

- RAID 1 - data mirroring

- RAID 0+1 (or RAID 10) - data striping and mirroring

- RAID 5 - distributed parity

## 2.8 Real-Time Clock Subsystem

A coin-cell battery (CR2032) powers the real-time clock and CMOS memory. When the computer is not plugged into a wall socket, the battery has an estimated life of three years. When the computer is plugged in, the standby current from the power supply extends the life of the battery. The clock is accurate to  $\pm$  13 minutes/year at 25 °C with 3.3 VSB applied through the power supply 5V STBY rail.

**Note:** If the battery and AC power fail, date and time values will be reset and the user will be notified during the POST.

When the voltage drops below a certain level, the BIOS Setup program settings stored in CMOS RAM (for example, the date and time) might not be accurate. Replace the battery with an equivalent one. Figure 1 on page 5 shows the location of the battery.

## 2.9 Legacy I/O Controller

The I/O controller provides the following features:

- Serial IRQ interface compatible with serialized IRQ support for PCI systems

- Intelligent power management, including a programmable wake-up event interface

- PCI power management support

The BIOS Setup program provides configuration options for the I/O controller.

## 2.10 LAN Subsystem

The LAN subsystem consists of the following:

- Intel® 82574L and 82579LM Gigabit Ethernet Controllers (10/100/1000 Mbits/s)

- Intel® C206 Chipset

- RJ-45 LAN connector with integrated status LEDs

Additional features of the LAN subsystem include:

- CSMA/CD protocol engine

- LAN connect interface between the PCH and the LAN controller

- PCI Conventional bus power management

- ACPI technology support

- LAN wake capabilities

- LAN subsystem software

**Table 12. Information on LAN Software and Drivers**

| For information about    | Refer to                                                                      |

|--------------------------|-------------------------------------------------------------------------------|

| LAN software and drivers | <a href="http://downloadcenter.intel.com">http://downloadcenter.intel.com</a> |

### 2.10.1 Intel® 82574L Gigabit Ethernet Controller

The Intel® 82574L Gigabit Ethernet Controller supports the following features:

- 10/100/1000 BASE-T IEEE 802.3 compliant

- Dual interconnect between the Integrated LAN Controller and the Physical Layer (PHY):

- PCI Express\*-based interface for active state operation (S0) state

- SMBUS\* for host and management traffic (Sx low power state)

- Compliant to IEEE 802.3x flow control support

- 802.1p and 802.1q

- TCP, IP, and UDP checksum offload (for IPv4 and IPv6)

- Full device driver compatibility

### 2.10.2 Intel® 82579LM Gigabit Ethernet Controller

The Intel® 82579LM Gigabit Ethernet Controller supports the following features:

- 10/100/1000 BASE-T IEEE 802.3 compliant

- Energy Efficient Ethernet (EEE) IEEE802.3az support [Low Power Idle (LPI) mode]

- Dual interconnect between the Integrated LAN Controller and the Physical Layer (PHY):

- PCI Express\*-based interface for active state operation (S0) state

- SMBUS\* for host and management traffic (Sx low power state)

- Compliant to IEEE 802.3x flow control support

- 802.1p and 802.1q

- TCP, IP, and UDP checksum offload (for IPv4 and IPv6)

- Full device driver compatibility

### 2.10.3 LAN Subsystem Software

LAN software and drivers are available from Intel®'s World Wide Web site.

**Table 13. Information on Obtaining LAN Software and Drivers**

| For information about              | Refer to                                                                      |

|------------------------------------|-------------------------------------------------------------------------------|

| Obtaining LAN software and drivers | <a href="http://downloadcenter.intel.com">http://downloadcenter.intel.com</a> |

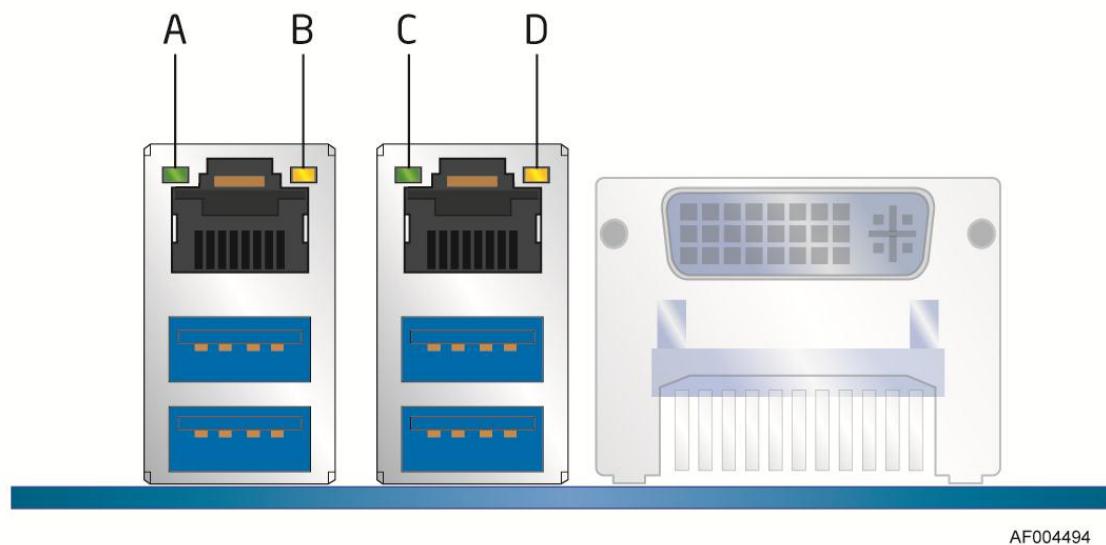

### 2.10.4 RJ-45 LAN Connector with Integrated LEDs

Two LEDs are built into the RJ-45 LAN connector (shown in Figure 4).

AF004494

| Item | Description                  |

|------|------------------------------|

| A    | Link LED (Green)             |

| B    | Data Rate LED (Green/Yellow) |

| C    | Link LED (Green)             |

| D    | Data Rate LED (Green/Yellow) |

**Figure 4. LAN Connector LED Locations**

Table 14 describes the LED states when the board is powered up and the LAN subsystem is operating.

**Table 14. LAN Connector LED States**

| LED       | LED Color    | LED State | Condition                           |

|-----------|--------------|-----------|-------------------------------------|

| Link      | Green        | Off       | LAN link is not established.        |

|           |              | On        | LAN link is established.            |

|           |              | Blinking  | LAN activity is occurring.          |

| Data Rate | Green/Yellow | Off       | 10 Mbits/s data rate is selected.   |

|           |              | Green     | 100 Mbits/s data rate is selected.  |

|           |              | Yellow    | 1000 Mbits/s data rate is selected. |

## 2.11 Hardware Management Subsystem

The hardware management features enable the board to be compatible with the Wired for Management (WfM) specification. The board has several hardware management features, including the following:

- Thermal and voltage monitoring

- Chassis intrusion detection

### 2.11.1 Hardware Monitoring

The hardware monitoring and fan control subsystem is based on the Nuvoton W83677HG-i device, which supports the following:

- Processor and system ambient temperature monitoring

- Chassis fan speed monitoring

- Power monitoring of +12 V, +5 V, V\_SM, +3.3 V, and +VCCP

- SMBus\* interface

### 2.11.2 Fan Monitoring

Fan monitoring can be implemented using third-party software.

**Table 15. Information on the Function of the Fan Headers**

| For information about            | Refer to                  |

|----------------------------------|---------------------------|

| The functions of the fan headers | Section 2.12.2.2, page 22 |

### 2.11.3 Chassis Intrusion and Detection

The board supports a chassis security feature that detects if the chassis cover is removed. The security feature uses a mechanical switch on the chassis that attaches to the chassis intrusion header. When the chassis cover is removed, the mechanical switch is in the closed position.

**Table 16. Information on the Chassis Intrusion Headers**

| For information about                        | Refer to          |

|----------------------------------------------|-------------------|

| The location of the chassis intrusion header | Figure 9, page 31 |

## 2.11.4 Thermal Monitoring

Figure 5 shows the locations of the thermal sensors and fan headers.

AF004495

| Item | Description                                   |

|------|-----------------------------------------------|

| A    | Thermal diode, located on the Intel® C206 PCH |

| B    | Remote thermal diode 1                        |

| C    | Processor fan header                          |

| D    | Thermal diode, located on the processor die   |

| E    | Remote thermal diode 2                        |

| F    | System fan header                             |

Figure 5. Thermal Sensors and Fan Headers

## 2.12 Power Management

Power management is implemented at several levels, including:

- Software support through Advanced Configuration and Power Interface (ACPI)

- Hardware support:

- Power connector

- Fan headers

- LAN wake capabilities

- Instantly Available PC technology

- Wake from USB

- PCI Express\* WAKE# signal support

### 2.12.1 ACPI

ACPI gives the operating system direct control over the power management and Plug and Play functions of a computer. The use of ACPI with this board requires an operating system that provides full ACPI support. ACPI features include:

- Plug and Play (including bus and device enumeration)

- Power management control of individual devices, add-in boards (some add-in boards may require an ACPI-aware driver), video displays, and hard disk drives

- Methods for achieving less than 15-watt system operation in the power-on/standby sleeping state

- A Soft-off feature that enables the operating system to power-off the computer

- Support for multiple wake-up events (see Table 19 on page 21)

- Support for a front panel power and sleep mode switch

Table 17 lists the system states based on how long the power switch is pressed, depending on how ACPI is configured with an ACPI-aware operating system.

**Table 17. Effects of Pressing the Power Switch**

| System Status                       | Power Switch Press Time | State of the System                            |

|-------------------------------------|-------------------------|------------------------------------------------|

| Off<br>(ACPI G2/G5 – Soft off)      | Less than four seconds  | Power-on<br>(ACPI G0 – working state)          |

| On<br>(ACPI G0 – working state)     | Less than four seconds  | Soft-off/Standby<br>(ACPI G1 – sleeping state) |

| On<br>(ACPI G0 – working state)     | More than six seconds   | Fail safe power-off<br>(ACPI G2/G5 – Soft off) |

| Sleep<br>(ACPI G1 – sleeping state) | Less than four seconds  | Wake-up<br>(ACPI G0 – working state)           |

| Sleep<br>(ACPI G1 – sleeping state) | More than six seconds   | Power-off<br>(ACPI G2/G5 – Soft off)           |

#### 2.12.1.1 System States and Power States

Under ACPI, the operating system directs all system and device power state transitions. The operating system puts devices in and out of low-power states based on user preferences and knowledge of how devices are being used by applications. Devices that are not being used can

be turned off. The operating system uses information from applications and user settings to put the system as a whole into a low-power state.

Table 18 lists the power states supported by the board along with the associated system power targets. See the ACPI specification for a complete description of the various system and power states.

**Table 18. Power States and Targeted System Power**

| Global States                                                      | Sleeping States                                          | Processor States | Device States                                                                        | Targeted System Power <sup>(Note 1)</sup>                |

|--------------------------------------------------------------------|----------------------------------------------------------|------------------|--------------------------------------------------------------------------------------|----------------------------------------------------------|

| G0 – working state                                                 | S0 – working                                             | C0 – working     | D0 – working state.                                                                  | Full power > 30 W                                        |

| G1 – sleeping state                                                | S3 – Suspend to RAM. Context saved to RAM.               | No power         | D3 – no power except for wake-up logic.                                              | Power < 5 W <sup>(Note 2)</sup>                          |

| G1 – sleeping state                                                | S4 – Suspend to disk. Context saved to disk.             | No power         | D3 – no power except for wake-up logic.                                              | Power < 5 W <sup>(Note 2)</sup>                          |

| G2/S5                                                              | S5 – Soft off. Context not saved. Cold boot is required. | No power         | D3 – no power except for wake-up logic.                                              | Power < 5 W <sup>(Note 2)</sup>                          |

| G3 – mechanical off<br>AC power is disconnected from the computer. | No power to the system.                                  | No power         | D3 – no power for wake-up logic, except when provided by battery or external source. | No power to the system. Service can be performed safely. |

**Notes:**

1. Total system power is dependent on the system configuration, including add-in boards and peripherals powered by the system chassis' power supply.

2. Dependent on the standby power consumption of wake-up devices used in the system.

### 2.12.1.2 Wake-up Devices and Events

Table 19 lists the devices or specific events that can wake the computer from specific states.

**Table 19. Wake-up Devices and Events**

| These devices/events can wake up the computer... | ...from this state             |

|--------------------------------------------------|--------------------------------|

| Power switch                                     | S3, S4, S5 <sup>(Note 1)</sup> |

| RTC alarm                                        | S3, S4, S5 <sup>(Note 1)</sup> |

| LAN                                              | S3, S4, S5 <sup>(Note 1)</sup> |

| USB                                              | S3                             |

| WAKE#                                            | S3, S4, S5 <sup>(Note 1)</sup> |

**Notes:**

1. S4 implies operating system support only.

2. Wake from S4 and S5 is recommended by Microsoft.

**Note:** The use of these wake-up events from an ACPI state requires an operating system that provides full ACPI support. In addition, software, drivers, and peripherals must fully support ACPI wake events.

## 2.12.2 Hardware Support

### CAUTION

*Ensure that the power supply provides adequate +5 V standby current if LAN wake capabilities and Instantly Available PC technology features are used. Failure to do so can damage the power supply. The total amount of standby current required depends on the wake devices supported and manufacturing options.*

The board provides several power management hardware features, including:

- Power connector

- Fan headers

- LAN wake capabilities

- Instantly Available PC technology

- Wake from USB

- WAKE# signal wake-up support

- +5 V Standby Power Indicator LED

LAN wake capabilities and Instantly Available PC technology require power from the +5 V standby line.

**Note:** The use of Wake from USB from an ACPI state requires an operating system that provides full ACPI support.

### 2.12.2.1 Power Connector

ATX12V-compliant power supplies can turn off the system power through system control. When an ACPI-enabled system receives the correct command, the power supply removes all non-standby voltages.

When resuming from an AC power failure, the computer returns to the power state it was in before power was interrupted (on or off). The computer's response can be set using the Last Power State feature in the BIOS Setup program's Boot menu.

**Table 20. Information on Power Connector Locations**

| For information about                        | Refer to          |

|----------------------------------------------|-------------------|

| The location of the main power connector     | Figure 9, page 31 |

| The signal names of the main power connector | Table 29, page 33 |

### 2.12.2.2 Fan Headers

The function/operation of the fan headers is as follows:

- The fans are on when the board is in the S0 state

- The fans are off when the board is off or in the S3, S4, or S5 state

- Each fan header is wired to a fan tachometer input of the hardware monitoring and fan control ASIC

- All fan headers support closed-loop fan control that can adjust the fan speed or switch the fan on or off as needed

- All fan headers have a +12 V DC connection

- 4-pin fan headers are controlled by Pulse Width Modulation

**Table 21. Information of the Fan Headers' Locations**

| For information about                                              | Refer to          |

|--------------------------------------------------------------------|-------------------|

| The location of the fan headers                                    | Figure 9, page 31 |

| The location of the fan headers and sensors for thermal monitoring | Figure 5, page 19 |

### 2.12.2.3 LAN Wake Capabilities

#### **CAUTION**

*For LAN wake capabilities, the +5 V standby line for the power supply must be capable of providing adequate +5 V standby current. Failure to provide adequate standby current when implementing LAN wake capabilities can damage the power supply.*

LAN wake capabilities enable remote wake-up of the computer through a network. The LAN subsystem PCI bus network adapter monitors network traffic at the Media Independent Interface. Upon detecting a Magic Packet\* frame, the LAN subsystem asserts a wake-up signal that powers up the computer. Depending on the LAN implementation, the board supports LAN wake capabilities with ACPI in the following ways:

- The PCI Express\* WAKE# signal

- The onboard LAN subsystem

### 2.12.2.4 Instantly Available PC Technology

#### **CAUTION**

*For Instantly Available PC technology, the +5 V standby line for the power supply must be capable of providing adequate +5 V standby current. Failure to provide adequate standby current when implementing Instantly Available PC technology can damage the power supply.*

Instantly Available PC technology enables the board to enter the ACPI S3 (Suspend-to-RAM) sleep-state. While in the S3 sleep-state, the computer will appear to be off (the power supply is off, and the front panel LED is amber if dual colored, or off if single colored.) When signaled by a wake-up device or event, the system quickly returns to its last known wake state. Table 19 on page 21 lists the devices and events that can wake the computer from the S3 state.

The use of Instantly Available PC technology requires operating system support and PCI Express\* add-in cards and drivers.

### 2.12.2.5 Wake from USB

USB bus activity wakes the computer from an ACPI S3 state.

**Note:** Wake from USB requires the use of a USB peripheral that supports Wake from USB.

#### 2.12.2.6 WAKE# Signal Wake-up Support

When the WAKE# signal on the PCI Express\* bus is asserted, the computer wakes from an ACPI S3, S4, or S5 state.

#### 2.12.2.7 Wake from S5

When the RTC Date and Time is set in the BIOS, the computer will automatically wake from an ACPI S5 state.

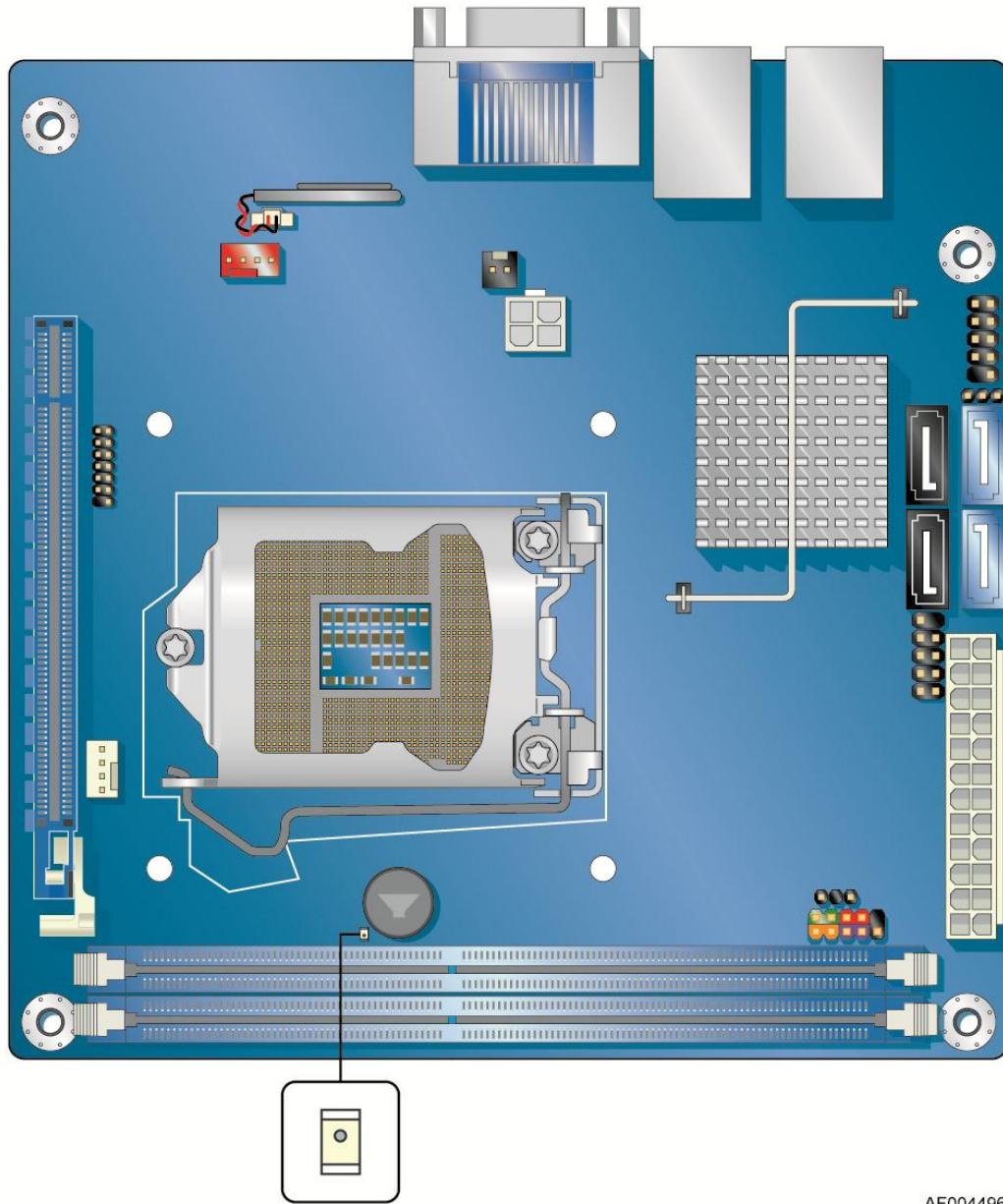

#### 2.12.2.8 +5 V Standby Power Indicator LED

The +5 V standby power indicator LED shows that power is still present even when the computer appears to be off. Figure 6 shows the location of the standby power LED.

#### CAUTION

*If AC power has been switched off and the standby power indicator is still lit, disconnect the power cord before installing or removing any devices connected to the board. Failure to do so could damage the board and any attached devices.*

**Figure 6. Location of the Standby Power LED**

## 3. Technical Reference

---

### 3.1 Memory Resources

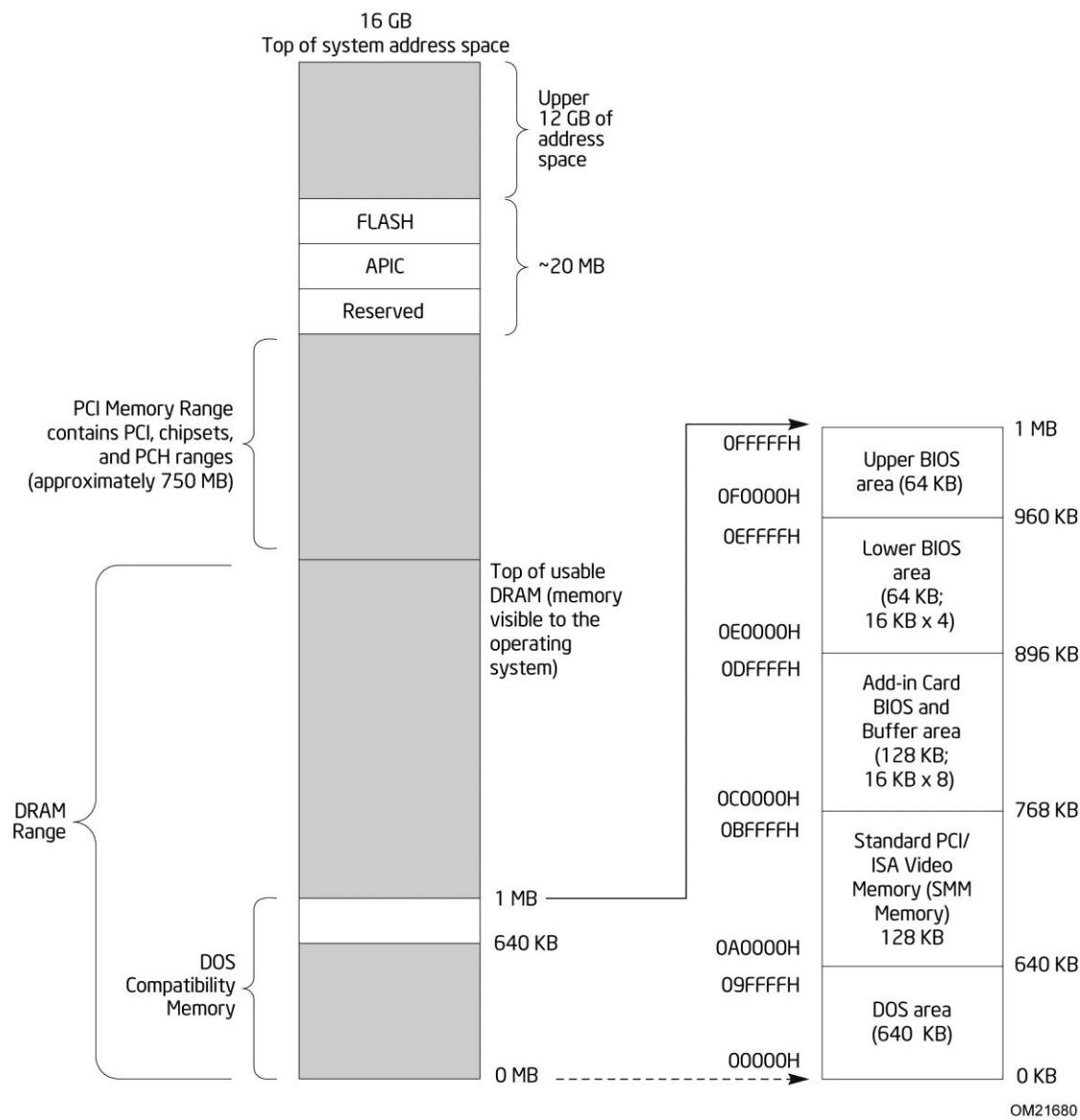

#### 3.1.1 Addressable Memory

The board utilizes 16 GB of addressable system memory. Typically the address space that is allocated for PCI Conventional bus add-in cards, PCI Express\* configuration space, BIOS (SPI Flash device), and chipset overhead resides above the top of DRAM (total system memory). On a system that has 16 GB of system memory installed, it is not possible to use all of the installed memory due to system address space being allocated for other system critical functions. These functions include the following:

- BIOS/SPI Flash device (16 Mbit)

- Local APIC (19 MB)

- Direct Media Interface (40 MB)

- Front side bus interrupts (17 MB)

- PCI Express\* configuration space (256 MB)

- PCH base address registers PCI Express\* ports (up to 256 MB)

- Memory-mapped I/O that is dynamically allocated for PCI Express\* add-in cards (256 MB)

The board provides the capability to reclaim the physical memory overlapped by the memory mapped I/O logical address space. The board remaps physical memory from the top of usable DRAM boundary to the 4 GB boundary to an equivalent sized logical address range located just above the 4 GB boundary. Figure 7 shows a schematic of the system memory map. All installed system memory can be used when there is no overlap of system addresses.

**Figure 7. Detailed System Memory Address Map**

### 3.1.2 Memory Map

Table 22 lists the system memory map.

**Table 22. System Memory Map**

| Address Range (decimal) | Address Range (hex) | Size     | Description                                                                                              |

|-------------------------|---------------------|----------|----------------------------------------------------------------------------------------------------------|

| 1024 K - 16777216 K K   | 100000 – 400000000  | 16382 MB | Extended memory                                                                                          |

| 960 K - 1024 K          | F0000 - FFFFF       | 64 KB    | Runtime BIOS                                                                                             |

| 896 K - 960 K           | E0000 - EFFFF       | 64 KB    | Reserved                                                                                                 |

| 800 K - 896 K           | C8000 - DFFFF       | 96 KB    | Potential available high DOS memory (open to the PCI Conventional bus). Dependent on video adapter used. |

| 640 K - 800 K           | A0000 - C7FFF       | 160 KB   | Video memory and BIOS                                                                                    |

| 639 K - 640 K           | 9FC00 - 9FFFF       | 1 KB     | Extended BIOS data (movable by memory manager software)                                                  |

| 512 K - 639 K           | 80000 - 9FBFF       | 127 KB   | Extended conventional memory                                                                             |

| 0 K - 512 K             | 00000 - 7FFFF       | 512 KB   | Conventional memory                                                                                      |

## 3.2 Connectors and Headers

### CAUTION

*Only the following connectors and headers have over-current protection: back panel and front panel USB.*

*The other internal connectors and headers are not over-current protected and should connect only to devices inside the computer's chassis, such as fans and internal peripherals. Do not use these connectors or headers to power devices external to the computer's chassis. A fault in the load presented by the external devices could cause damage to the computer, the power cable, and the external devices themselves.*

*Furthermore, improper connection of USB header single wire connectors may eventually overload the over-current protection and cause damage to the board.*

This section describes the board's connectors. The connectors can be divided into these groups:

- Back panel I/O connectors

- Component-side I/O connectors and headers (see page 30)

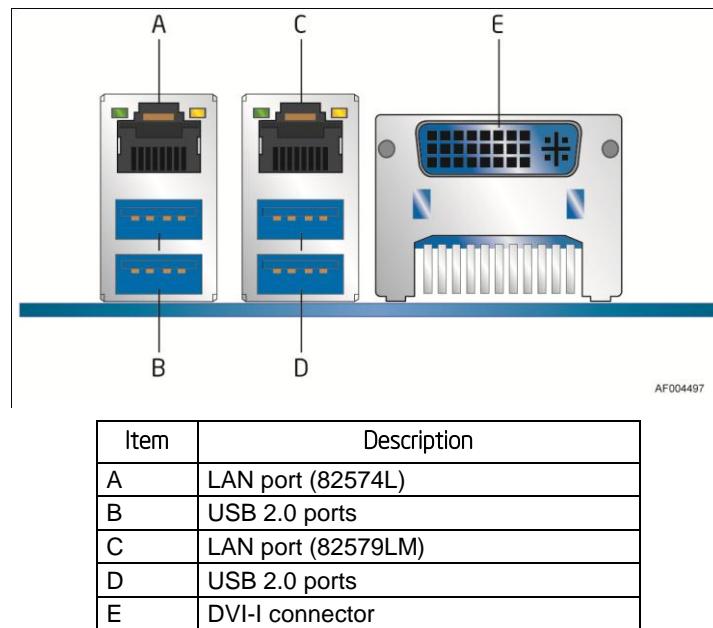

### 3.2.1 Back Panel Connectors

Figure 8 shows the location of the back panel connectors for the board.

**Figure 8. Back Panel Connectors**

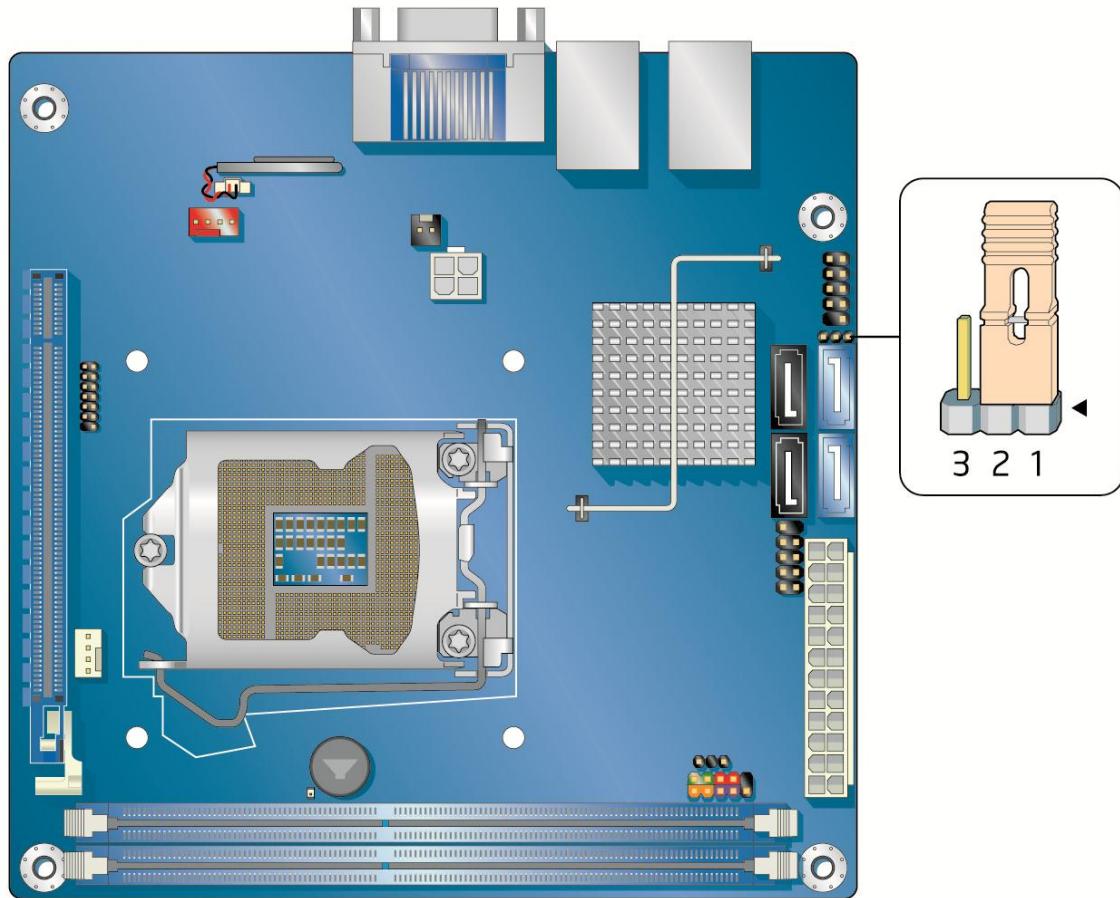

### 3.2.2 Component-side Connectors and Headers

Figure 9 shows the locations of the component-side connectors and headers.

**Figure 9. Component-side Connectors and Headers**

Table 23 lists the component-side connectors and headers identified in Figure 9.

**Table 23. Component-side Connectors and Headers Shown in Figure 9**

| Item/callout | Description                                |

|--------------|--------------------------------------------|

| A            | Processor core power connector (2 x 2)     |

| B            | Front panel USB header                     |

| C            | SATA connectors                            |

| D            | Front panel USB header                     |

| E            | Main power connector (2 X 12)              |

| F            | Front panel header                         |

| G            | Alternate front panel power LED header     |

| H            | Processor fan header                       |

| I            | PCI Express* x16 bus add-in card connector |

| J            | LPC Debug header                           |

| K            | Chassis intrusion header                   |

| L            | System fan header                          |

### 3.2.2.1 Signal Tables for the Connectors and Headers

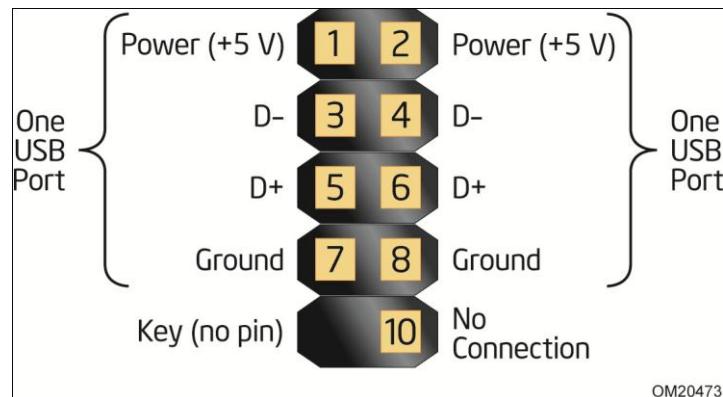

**Table 24. Front Panel USB 2.0 Headers**

| Pin | Signal Name  | Pin | Signal Name |

|-----|--------------|-----|-------------|

| 1   | +5 V DC      | 2   | +5 V DC     |

| 3   | D-           | 4   | D-          |

| 5   | D+           | 6   | D+          |

| 7   | Ground       | 8   | Ground      |

| 9   | KEY (no pin) | 10  | No Connect  |

**Table 25. SATA Connectors**

| Pin | Signal Name |

|-----|-------------|

| 1   | Ground      |

| 2   | TXP         |

| 3   | TXN         |

| 4   | Ground      |

| 5   | RXN         |

| 6   | RXP         |

| 7   | Ground      |

**Table 26. Chassis Intrusion Header**

| Pin | Signal Name |

|-----|-------------|

| 1   | Intruder#   |

| 2   | Ground      |

**Table 27. Processor and System (4-Pin) Fan Headers**

| Pin | Signal Name   |

|-----|---------------|

| 1   | Ground (Note) |

| 2   | +12 V         |

| 3   | FAN_TACH      |

| 4   | FAN_CONTROL   |

| 5   | Jack detect 2 |

**Note:** These fan headers use Pulse Width Modulation control for fan speed.

### 3.2.2.2 Add-in Card Connector

The board has one PCI Express® 2.0 x16 (with Intel® Xeon® E3-1200 Processors or the 2<sup>nd</sup> Generation Intel® Core™ i3 Processors) or PCI Express® 3.0 x 16 (with Intel® Xeon® E3-1200 V2 Processors or the 3<sup>rd</sup> Generation Intel® Core™ i3 Processors) connector supporting simultaneous transfer speeds up to 16 GB/s of peak bandwidth per direction and up to 32 GB/s concurrent bandwidth.

### 3.2.2.3 Power Supply Connectors

The board has the following power supply connectors:

- **Main power** – a 2 x 12 connector. The board supports the use of ATX12V power supplies with either 2 x 10 or 2 x 12 main power cables. When using a power supply with a 2 x 10 main power cable, attach that cable on the leftmost pins of the main power connector, leaving pins 11, 12, 23, and 24 unconnected.

- **Processor core power** – a 2 x 2 connector. This connector provides power directly to the processor voltage regulator and must always be used. Failure to do so will prevent the board from booting.

**Table 28. Processor Core Power Connector**

| Pin | Signal Name | Pin | Signal Name |

|-----|-------------|-----|-------------|

| 1   | Ground      | 2   | Ground      |

| 3   | +12 V       | 4   | +12 V       |

**Table 29. Main Power Connector**

| Pin | Signal Name | Pin | Signal Name |

|-----|-------------|-----|-------------|

| 1   | +3.3 V      | 13  | +3.3 V      |

| 2   | +3.3 V      | 14  | -12 V       |

| Pin | Signal Name                    | Pin | Signal Name                         |

|-----|--------------------------------|-----|-------------------------------------|

| 3   | Ground                         | 15  | Ground                              |

| 4   | +5 V                           | 16  | PS-ON# (power supply remote on/off) |

| 5   | Ground                         | 17  | Ground                              |

| 6   | +5 V                           | 18  | Ground                              |

| 7   | Ground                         | 19  | Ground                              |

| 8   | PWRGD (Power Good)             | 20  | No connect                          |

| 9   | +5 V (Standby)                 | 21  | +5 V                                |

| 10  | +12 V                          | 22  | +5 V                                |

| 11  | +12 V (Note)                   | 23  | +5 V (Note)                         |

| 12  | 2 x 12 connector detect (Note) | 24  | Ground (Note)                       |

**Note:** When using a 2 x 10 power supply cable, this pin will be unconnected.

| For information about       | Refer to                 |

|-----------------------------|--------------------------|

| Power supply considerations | Section 3.5.1 on page 40 |

### 3.2.2.4 Front Panel Header

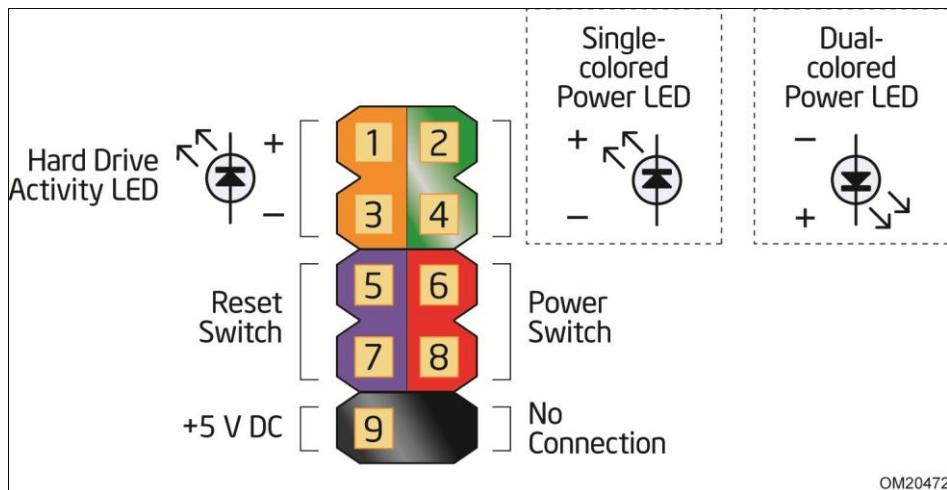

This section describes the functions of the front panel header. Table 30 lists the signal names of the front panel header. Figure 10 is a connection diagram for the front panel header.

**Table 30. Front Panel Header**

| Pin | Signal Name   | Description                     | Pin | Signal Name    | Description                        |

|-----|---------------|---------------------------------|-----|----------------|------------------------------------|

| 1   | HDD_POWER_LED | Pull-up resistor (750 Ω) to +5V | 2   | POWER_LED_MAIN | [Out] Front panel LED (main color) |

| 3   | HDD_LED#      | [Out] Hard disk activity LED    | 4   | POWER_LED_ALT  | [Out] Front panel LED (alt color)  |

| 5   | GROUND        | Ground                          | 6   | POWER_SWITCH#  | [In] Power switch                  |

| 7   | RESET_SWITCH# | [In] Reset switch               | 8   | GROUND         | Ground                             |

| 9   | +5V_DC        | Power                           | 10  | Key            | No pin                             |

OM20472

**Figure 10. Connection Diagram for Front Panel Header**

### 3.2.2.4.1 Hard Drive Activity LED Header

Pins 1 and 3 can be connected to an LED to provide a visual indicator that data is being read from or written to a hard drive. Proper LED function requires a SATA hard drive or optical drive connected to an onboard SATA connector.

### 3.2.2.4.2 Reset Switch Header

Pins 5 and 7 can be connected to a momentary single pole, single throw (SPST) type switch that is normally open. When the switch is closed, the board resets and runs the POST.

### 3.2.2.4.3 Power/Sleep LED Header

Pins 2 and 4 can be connected to a one- or two-color LED. Table 31 shows the possible states for a one-color LED. Table 32 shows the possible states for a two-color LED.

**Table 31. States for a One-Color Power LED**

| LED State    | Description        |

|--------------|--------------------|

| Off          | Power off/sleeping |

| Steady Green | Running            |

**Table 32. States for a Two-Color Power LED**

| LED State     | Description |

|---------------|-------------|

| Off           | Power off   |

| Steady Green  | Running     |

| Steady Yellow | Sleeping    |

**Note:** The colors listed in Table 31 and Table 32 are suggested colors only. Actual LED colors are chassis-specific.

### 3.2.2.4.4 Power Switch Header