## 9-Line Low Capacitance SCSI Active Terminator

#### **FEATURES**

- Complies with SCSI, SCSI-2 and SPI-2 Standards

- 3pF Channel Capacitance during Disconnect

- 100μA Supply Current in Disconnect Mode

- Meets SCSI Hot Plugging Capability

- –400mA Sourcing Current for Termination

- +400mA Sinking Current for Active Negation

- Logic Command Disconnects all Termination Lines

- Trimmed Termination Current to 5%

- Trimmed Impedance to 5%

- Current Limit and Thermal Shutdown Protection

#### **DESCRIPTION**

The UC5613 provides 9 lines of active termination for a SCSI (Small Computer Systems Interface) parallel bus. The SCSI standard recommends active termination at both ends of the cable segment.

The UC5613 provides a disconnect feature which, when opened or driven high, disconnects all terminating resistors and disables the regulator greatly reducing standby power. The output channels remain high impedance even without Termpwr applied. A low channel capacitance of 3pF allows units at interim points of the bus to have little or no effect on the signal integrity.

The UC5613 is pin-for-pin compatible with its predecessor, the UC5603 - 9 line Active Terminator. The only functional difference between the UC5613 and UC5603 is the absence of the negative clamps. Parametrically, the UC5613 has a 5% tolerance on impedance and current compared to a 3% tolerance on the UC5603. Custom power packages are utilized to allow normal operation at full power (1.2 watts).

Internal circuit trimming is utilized, first to trim the impedance to a 5% tolerance; then, the output current is trimmed to a 5% tolerance. The output current trim is set as close as possible to the maximum value of the SCSI specification which maximizes the noise margin for fast SCSI operation.

Other features include thermal shutdown and current limit.

This device is offered in low thermal resistance versions of the industry standard 16 pin narrow body SOIC, 16 pin ZIP (zig-zag in line package), and 24 pin TSSOP.

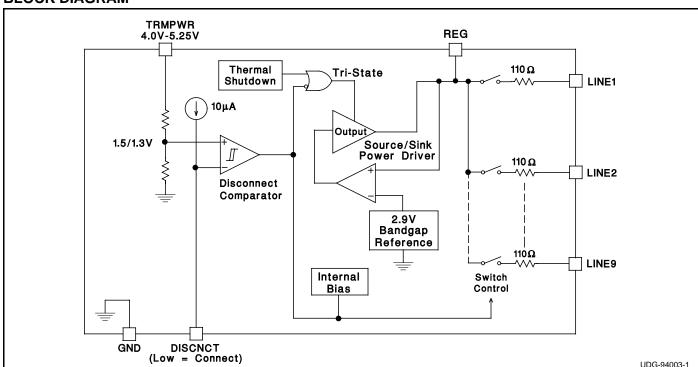

#### **BLOCK DIAGRAM**

**Circuit Design Patented**

#### **ABSOLUTE MAXIMUM RATINGS**

| Termpwr Voltage +7V                                                                        |

|--------------------------------------------------------------------------------------------|

| Signal Line Voltage 0V to +7V                                                              |

| Regulator Output Current                                                                   |

| Storage Temperature                                                                        |

| Operating Temperature                                                                      |

| Lead Temperature (Soldering, 10 Sec.) +300°C                                               |

| I lalace of a major and officed all violations are with manner to Crowned Comments are not |

Unless otherwise specified all voltages are with respect to Ground. Currents are positive into, negative out of the specified terminal.

Consult Packaging Section of Unitrode Integrated Circuits databook for thermal limitations and considerations of packages.

#### RECOMMENDED OPERATING CONDITIONS

| Termpwr Voltage          | 3.8V to 5.25V |

|--------------------------|---------------|

| Signal Line Voltage      | 0V to +5V     |

| Disconnect Input Voltage | 0V to Termpwr |

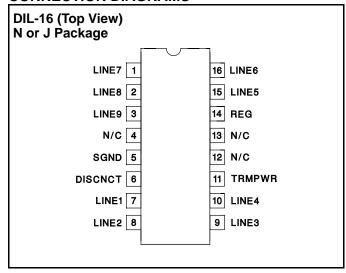

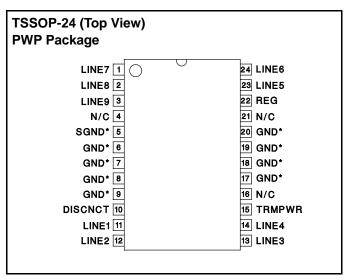

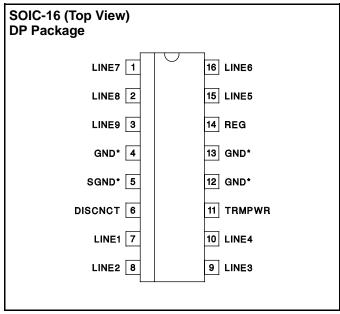

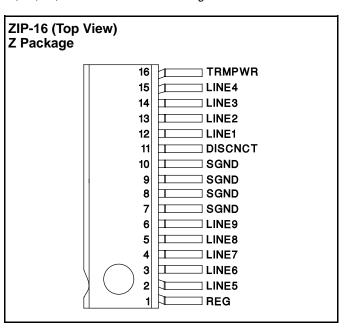

#### **CONNECTION DIAGRAMS**

\* PWP package pin 5 serves as signal ground; pins 6, 7, 8, 9, 17, 18, 19, and 20 serve as heatsink/ground.

<sup>\*</sup> DP package pin 5 serves as signal ground; pins 4, 12, 13 serve as heatsink/ground.

Note: Drawings are not to scale.

# **ELECTRICAL CHARACTERISTICS** Unless otherwise stated, these specifications apply for TA = 0°C to 70°C. TRMPWR = 4.75V, DISCNCT = 0V. TA = TJ.

| PARAMETER                                                               | TEST CONDITIONS                                                                       |                                  |                 | MIN   | TYP   | MAX   | UNITS |

|-------------------------------------------------------------------------|---------------------------------------------------------------------------------------|----------------------------------|-----------------|-------|-------|-------|-------|

| Supply Current Section                                                  |                                                                                       |                                  |                 |       |       |       |       |

| Termpwr Supply Current                                                  | All termination lines = Open                                                          |                                  |                 |       | 17    | 23    | mA    |

|                                                                         | All termination lines = 0.5V                                                          |                                  |                 |       | 200   | 225   | mA    |

| Power Down Mode                                                         | DISCNCT = Open                                                                        |                                  |                 |       | 100   | 150   | μΑ    |

| <b>Output Section (Terminator Lines</b>                                 | )                                                                                     |                                  |                 |       |       |       |       |

| Terminator Impedance                                                    | $\Delta$ ILINE = -5mA to -15mA                                                        |                                  |                 | 104.5 | 110   | 115.5 | Ohms  |

| Output High Voltage                                                     | TRMPWR = 4V (Note 1)                                                                  |                                  |                 | 2.7   | 2.9   |       | V     |

| Max Output Current                                                      | VLINE = $0.5V$ $T_J = 25^{\circ}C$ $0^{\circ}C < T_J < 70^{\circ}C$                   |                                  | TJ = 25°C       | -20.3 | -21.5 | -22.4 | mA    |

|                                                                         |                                                                                       |                                  | -19.8           | -21.5 | -22.4 | mA    |       |

| Max Output Current                                                      | VLINE = 0.5V, TRMPWR = 4V (Note 1) $TJ = 25^{\circ}C$ $0^{\circ}C < TJ < 70^{\circ}C$ |                                  | TJ = 25°C       | -19.5 | -21.5 | -22.4 | mA    |

|                                                                         |                                                                                       |                                  | -19.0           | -21.5 | -22.4 | mA    |       |

|                                                                         | VLINE = 0.2V, TR                                                                      | MPWR = 4V to 5.25V               | 0°C < TJ < 70°C | -21.6 | -24.0 | -25.4 | mA    |

| Output Leakage                                                          | DISCNCT = 4V                                                                          | TRMPWR = 0V to 5.25V<br>REG = 0V | VLINE = 0 to 4V |       | 10    | 400   | nA    |

|                                                                         |                                                                                       |                                  | VLINE = 5.25V   |       |       | 100   | μΑ    |

|                                                                         |                                                                                       | TRMPWR = $0V$ to $5.25V$ ,       | REG = Open      |       | 10    | 400   | nA    |

| 2                                                                       | VLINE = 0V to 5.25V                                                                   |                                  |                 |       | •     | 4.5   | _     |

| Output Capacitance   DISCNCT = Open, DP Package (Note 2)   3   4.5   pF |                                                                                       |                                  |                 |       |       |       |       |

| Regulator Section                                                       |                                                                                       |                                  |                 | 2.8   | 0.0   |       |       |

| Regulator Output Voltage                                                | AUT : C I EV                                                                          |                                  |                 |       | 2.9   | 3     | V     |

| Regulator Output Voltage                                                | All Termination Lines = 5V                                                            |                                  |                 | 2.8   | 2.9   | 3     | •     |

| Line Regulation                                                         | TRMPWR = 4V to 6V                                                                     |                                  |                 |       | 10    | 20    | mV    |

| Load Regulation                                                         | IREG = +100mA to -100mA                                                               |                                  |                 |       | 20    | 50    | mV    |

| Drop Out Voltage                                                        | All Termination Lines = 0.5V                                                          |                                  |                 |       | 0.7   | 1     | V     |

| Short Circuit Current                                                   | VREG = 0V                                                                             |                                  |                 | -200  | -400  | -600  | mA    |

| Sinking Current Capability                                              | VREG = 3.5V                                                                           |                                  |                 | 200   | 400   | 600   | mA    |

| Thermal Shutdown                                                        |                                                                                       |                                  |                 |       | 170   |       | °C    |

| Thermal Shutdown Hysteresis                                             |                                                                                       |                                  |                 |       | 10    |       | °C    |

| Disconnect Section                                                      | Γ                                                                                     |                                  |                 |       |       | ı     | 1     |

| Disconnect Threshold                                                    |                                                                                       |                                  |                 | 1.3   | 1.5   | 1.7   | V     |

| Threshold Hysteresis                                                    |                                                                                       |                                  |                 | 100   | 160   | 250   | mV    |

| Input Current                                                           | DISCNCT = 0V                                                                          |                                  |                 |       | 10    | 15    | μΑ    |

Note 1: Measuring each termination line while other 8 are low (0.5V).

Note 2: Guaranteed by design. Not 100% tested in production.

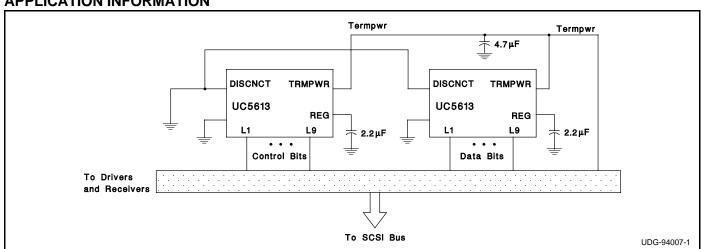

#### **APPLICATION INFORMATION**

Figure 1: Typical SCSI Bus Configurations Utilizing 2 UC5613 Devices

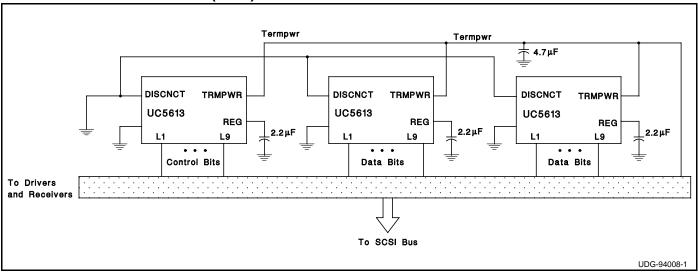

### **APPLICATION INFORMATION (cont.)**

Figure 2: Typical Wide SCSI Bus Configurations Utilizing 3 UC5613 Devices.

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 1999, Texas Instruments Incorporated