DLOGY 100kHz, 5A, 2.5A and 1.25A High Efficiency Switching Regulators

### **FEATURES**

- Wide Input Voltage Range: 3V to 60V

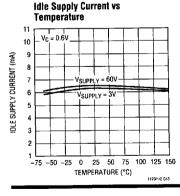

- Low Quiescent Current: 6mA

- Internal 5A Switch (2.5A for LT1171, 1.25A for LT1172)

- Very Few External Parts Required

- Self-Protected Against Overloads

- Operates in Nearly All Switching Topologies

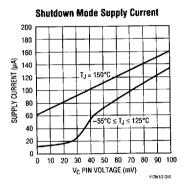

- Shutdown Mode Draws Only 50µA Supply Current

- Flyback-Regulated Mode Has Fully Floating Outputs

- Comes in Standard 5-Pin Packages

- LT1172 Available in 8-Pin MiniDIP and Surface Mount Packages

- Can Be Externally Synchronized

### **APPLICATIONS**

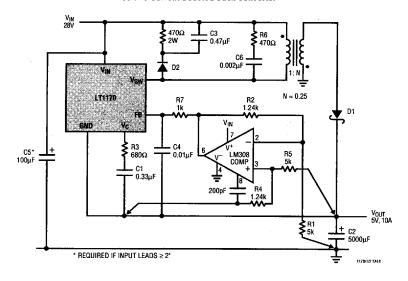

- Logic Supply 5V at 10A

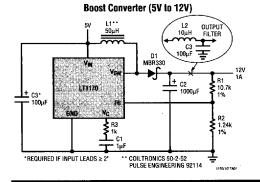

- 5V Logic to ±15V Op Amp Supply

- Battery Upconverter

- Power Inverter (+ to -) or (- to +)

- Fully Floating Multiple Outputs

#### USER NOTE:

This data sheet is only intended to provide specifications, graphs, and a general functional description of the LT1170/LT117/LT1172. Application circuits are included to show the capability of the LT1170/LT117/LT1172. A complete design amoual (ANII) should be obtained to assist in developing new designs. This manual contains a comprehensive discussion of both the LT1070 and the external components used with it, as well as complete formulas for calculating the values of these components. The manual can also be used for the LT1170/LT1172 by factoring in the higher frequency. A CAD design program called SwitcherCAD is also available.

### DESCRIPTION

The LT1170/LT1171/LT1172 are monolithic high power switching regulators. They can be operated in all standard switching configurations including buck, boost, flyback, forward, inverting and "Cuk." A high current, high efficiency switch is included on the die along with all oscillator, control, and protection circuitry. Integration of all functions allows the LT1170/LT1171/LT1172 to be built in a standard 5-pin TO-3 or TO-220 power package as well as the 8-pin packages (LT1172). This makes them extremely easy to use and provides "bust proof" operation similar to that obtained with 3-pin linear regulators.

The LT1170/LT1171/LT1172 operate with supply voltages from 3V to 60V, and draw only 6mA quiescent current. They can deliver load power up to 100W with no external power devices. By utilizing current-mode switching techniques, they provide excellent AC and DC load and line regulation.

The LT1170/LT1171/LT1172 have many unique features not found even on the vastly more difficult to use low power control chips presently available. They use adaptive anti-sat switch drive to allow very wide ranging load currents with no loss in efficiency. An externally activated shutdown mode reduces total supply current to  $50\mu A$  typically for standby operation.

Maximum Output Power\*

50

### TYPICAL APPLICATION

###

20 30

INPUT VOLTAGE (V)

\* ROUGH GUIDE ONLY. BUCK MODE POUT = 5A × VOUT. SPECIAL TOPOLOGIES DELIVER MORE POWER \*\* DIVIDE VERTICAL POWER SCALE

BY TWO FOR LT1171, BY FOUR FOR LT1172.

L11170/5/2 TA02

TECHNOLOGY TECHNOLOGY

4-433

5518468 0010440 94T **=**

### ABSOLUTE MAXIMUM RATINGS

| Supply Voltage                             |

|--------------------------------------------|

| LT1170/71/72HV 60V                         |

| LT1170/71/72 (See Note 1) 40V              |

| Switch Output Voltage                      |

| LT1170/71/72HV 75V                         |

| LT1170/71/72 65V                           |

| LT1172S8 60V                               |

| Feedback Pin Voltage (Transient, 1ms) ±15V |

| Storage Temperature Range65°C to 150°C     |

| Lead Temperature (Soldering, 10 sec) 300°C |

| Operating Junction Temperature Range       |

| LT1170/71/72M55°C to 150°C                 |

| LT1170/71/72HVC,                           |

| LT1170/71/72C (Oper.) 0°C to 100°C         |

| LT1170/71/72HVC,                           |

| LT1170/71/72C (Sh. Ckt.) 0°C to 125°C      |

| LT1170/71/72I (Oper.)40°C to 100°C         |

| LT1170/71/72I (Sh. Ckt.)40°C to 125°C      |

| ,                                          |

Note 1: Minimum effective switch "on" time for the LT1170/71/72 (in current limit only) is  $\sim$  0.6 $\mu$ s. This limits the maximum safe input voltage during an output shorted condition. Buck mode and inverting mode input voltage during an output shorted condition is limited to:

$V_{IN}$  (max, output shorted) = 15V +  $\frac{R \cdot I_L + Vf}{t \cdot f}$

R = Inductor DC resistance

I<sub>1</sub> = 10A for LT1170, 5A for LT1171, and 2.5A for LT1172

Vf = Output catch diode forward voltage at IL

t = 0.6µs, f = 100kHz switching frequency

Maximum input voltage can be increased by increasing R or Vf. External current limiting such as that shown in AN19, Figure 39, will provide protection up to the full supply voltage rating. C1 in Figure 39 should be reduced to 200pF.

Transformer designs will tolerate much higher input voltages because leakage inductance limits rate of rise of current in the switch. These designs must be evaluated individually to assure that current limit is well controlled up to maximum input voltage.

Boost mode designs are never protected against output shorts because the external catch diode and inductor connect input to output.

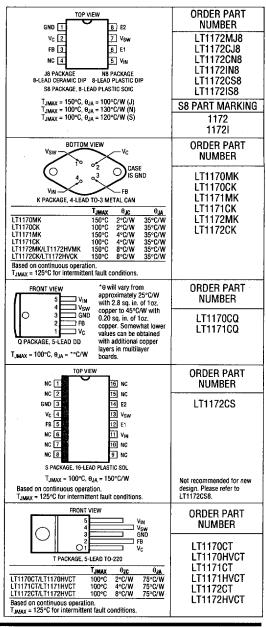

### PACKAGE/ORDER INFORMATION

# **ELECTRICAL CHARACTERISTICS** $v_{IN} = 15V$ , $v_{C} = 0.5V$ , $v_{FB} = v_{REF}$ , output pin open, unless otherwise noted.

| SYMBOL           | PARAMETER CONDITIONS                                    |          |                                                                    |                                        |                                               |   | MIN                  | TYP                  | MAX                  | UNITS        |

|------------------|---------------------------------------------------------|----------|--------------------------------------------------------------------|----------------------------------------|-----------------------------------------------|---|----------------------|----------------------|----------------------|--------------|

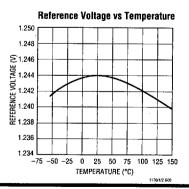

| $V_{REF}$        | Reference Voltage                                       |          | Measured at Feedback Pin<br>V <sub>C</sub> = 0.8V                  |                                        |                                               |   | 1.224<br>1.214       | 1.244<br>1.244       | 1.264<br>1.274       | V            |

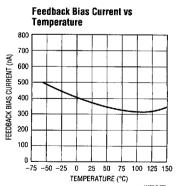

| l <sub>B</sub>   | Feedback Input Current                                  |          | V <sub>FB</sub> = V <sub>REF</sub>                                 |                                        |                                               |   |                      | 350                  | 750<br>1100          | nА<br>пА     |

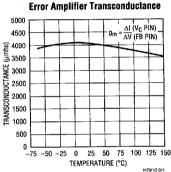

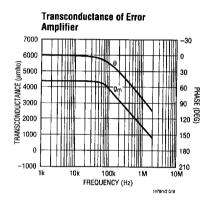

| 9m               | Error Amplifier<br>Transconductance                     |          | $\Delta I_C = \pm 25 \mu A$                                        |                                        |                                               | • | 3000<br>2400         | 4400                 | 6000<br>7000         | μmho<br>μmho |

|                  | Error Amplifier Source or<br>Sink Current               |          | V <sub>C</sub> = 1.5V                                              |                                        |                                               | • | 150<br>120           | 200                  | 350<br>400           | μA<br>μA     |

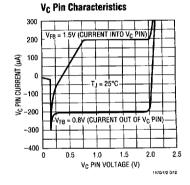

|                  | Error Amplifier Clamp<br>Voltage                        |          | Hi Clamp, V <sub>FB</sub> = 1V<br>Lo Clamp, V <sub>FB</sub> = 1.5V |                                        |                                               |   | 1.80<br>0.25         | 0.38                 | 2.30<br>0.52         | V            |

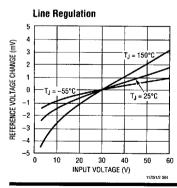

|                  | Reference Voltage Line<br>Regulation                    |          | $3V \le V_{IN} \le V_{MAX}$ $V_C = 0.8V$                           |                                        |                                               | • |                      |                      | 0.03                 | %/V          |

| Av               | Error Amplifier Voltage Gain                            |          | 0.9V ≤ V <sub>C</sub> ≤ 1.4V                                       |                                        |                                               |   | 500                  | 800                  |                      | V/V          |

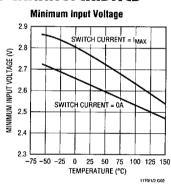

|                  | Minimum Input Voltage (Note 3)                          |          |                                                                    |                                        |                                               | • |                      | 2.6                  | 3.0                  | ٧            |

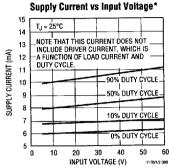

| Ia               | Supply Current                                          |          | $3V \le V_{IN} \le V_{MAX}$ , V                                    | <sub>C</sub> = 0.6V                    |                                               |   |                      | 6                    | 9                    | mA           |

|                  | Control Pin Threshold                                   |          | Duty Cycle = 0                                                     |                                        |                                               | • | 0.8<br>0.6           | 0.9                  | 1.08<br>1.25         | V            |

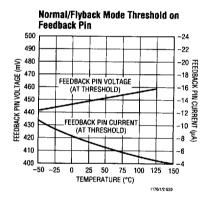

|                  | Normal/Flyback Thresh<br>on Feedback Pin                | old      |                                                                    |                                        |                                               |   | 0.4                  | 0.45                 | 0.54                 | V            |

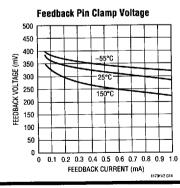

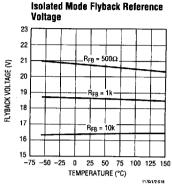

| V <sub>FB</sub>  | Flyback Reference Volt<br>(Note 3)                      | age      | I <sub>FB</sub> = 50μA                                             |                                        |                                               | • | 15.0<br>14.0         | 16.3                 | 17.6<br>18.0         | V            |

|                  | Change in Flyback Reference<br>Voltage                  |          | 0.05 ≤ I <sub>FB</sub> ≤ 1mA                                       |                                        |                                               |   | 4.5                  | 6.8                  | 9                    | ٧            |

|                  | Flyback Reference Volt                                  |          | $I_{FB} = 50\mu A$<br>$7V \le V_{IN} \le V_{MAX}$                  |                                        |                                               |   |                      | 0.01                 | 0.03                 | %/V          |

|                  | Flyback Amplifier<br>Transconductance (g <sub>m</sub> ) |          | $\Delta I_C = \pm 10 \mu A$                                        |                                        |                                               |   | 150                  | 300                  | 500                  | μmho         |

|                  | Flyback Amplifier Sour<br>and Sink Current              | ce       | V <sub>C</sub> = 0.6V<br>I <sub>FB</sub> = 50μA                    | Source<br>Sink                         | -                                             | • | 15<br>25             | 32<br>40             | 70<br>70             | μA<br>μA     |

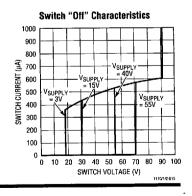

| BV               | Output Switch Breakdown<br>Voltage                      |          | $3V \le V_{IN} \le V_{MAX}$ , $I_{SW} = 1.5 \text{mA}$             | LT1170/LT11<br>LT1170HV/LT<br>LT1172S8 | 71/LT1172<br>1171HV/LT1172HV                  | • | 65<br>75<br>60       | 90<br>90<br>80       |                      | V            |

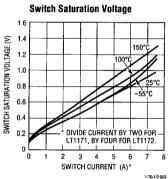

| V <sub>SAT</sub> | Output Switch "On" Resistance (Note 1)                  |          | LT1170<br>LT1171<br>LT1172                                         |                                        |                                               | • |                      | 0.15<br>0.30<br>0.60 | 0.24<br>0.50<br>1.00 | Ω<br>Ω<br>Ω  |

|                  | Control Voltage to Switch<br>Current Transconductance   |          | LT1170<br>LT1171<br>LT1172                                         |                                        |                                               |   |                      | 8<br>4<br>2          |                      | A/V<br>A/V   |

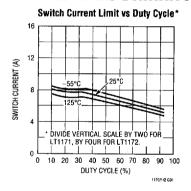

| LIM              | Switch Current Limit                                    | (LT1170) | Duty Cycle = 50%<br>Duty Cycle = 50%<br>Duty Cycle = 80%           | (Note 2)                               | T <sub>J</sub> ≥ 25°0<br>T <sub>J</sub> < 25° |   | 5<br>5<br>4          |                      | 10<br>11<br>10       | <i>I</i>     |

|                  |                                                         | (LT1171) | Duty Cycle = 50%<br>Duty Cycle = 50%<br>Duty Cycle = 80%           | (Note 2)                               | T <sub>J</sub> ≥ 25°0<br>T <sub>J</sub> < 25° |   | 2.5<br>2.5<br>2.0    |                      | 5.0<br>5.5<br>5.0    | ,            |

|                  |                                                         | (LT1172) | Duty Cycle = 50%<br>Duty Cycle = 50%<br>Duty Cycle = 80%           | (Note 2)                               | $T_{J} \ge 25^{\circ}$ $T_{J} < 25^{\circ}$   |   | 1.25<br>1.25<br>1.00 |                      | 3.0<br>3.5<br>2.5    |              |

4-435

**■** 5518468 0010442 712 **■**

# **ELECTRICAL CHARACTERISTICS** $V_{IN} = 15V$ , $V_C = 0.5V$ , $V_{FB} = V_{REF}$ , output pin open, unless otherwise noted.

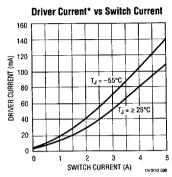

| SYMBOL                                              | PARAMETER                                        | CONDITIONS                                |   | MIN       | <b>TYP</b> 25 | <b>MAX</b><br>35 | mA/A       |

|-----------------------------------------------------|--------------------------------------------------|-------------------------------------------|---|-----------|---------------|------------------|------------|

| $\frac{\Delta l_{\text{IN}}}{\Delta l_{\text{SW}}}$ | Supply Current Increase<br>During Switch On-Time |                                           |   |           |               |                  |            |

| f                                                   | Switching Frequency                              |                                           | • | 88<br>85  | 100           | 112<br>115       | kHz<br>kHz |

| DC <sub>MAX</sub>                                   | Maximum Switch Duty Cycle                        |                                           | • | 80        | 90            | 95               | %          |

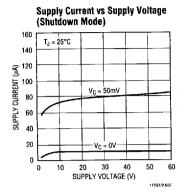

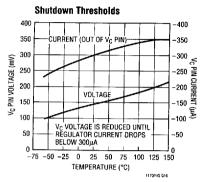

|                                                     | Shutdown Mode<br>Supply Current                  | $3V \le V_{IN} \le V_{MAX}$ $V_C = 0.05V$ |   |           | 100           | 250              | μА         |

|                                                     | Shutdown Mode<br>Threshold Voltage               | $3V \leq V_{IN} \leq V_{MAX}$             | • | 100<br>50 | 150           | 250<br>300       | mV<br>mV   |

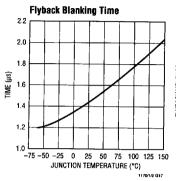

|                                                     | Flyback Sense Delay Time (Note 3)                |                                           |   |           | 1.5           |                  | μs         |

The ● denotes the specifications which apply over the full operating temperature range.

$V_{MAX} = 40V$  for LT1170/71/72 and 60V for LT1170/71/72HV.

Note 1: Measured with  $V_C$  in hi clamp,  $V_{FB}$  = 0.8V.  $I_{SW}$  = 4A for LT1170, 2A for LT1171, and 1A for LT1172.

Note 2: For duty cycles (DC) between 50% and 80%, minimum

guaranteed switch current is given by  $I_{LIM}$  = 3.33 (2 – DC) for the LT1170,  $I_{LIM}$  = 1.67 (2 – DC) for the LT1171, and  $I_{LIM}$  = 0.833 (2 – DC) for the LT1172.

Note 3: Minimum input voltage for isolated flyback mode is 7V. V<sub>MAX</sub> = 55V for HV grade in fully isolated mode to avoid switch breakdown.

### TYPICAL PERFORMANCE CHARACTERISTICS

4-436

LT LINEAR

**■** 5518468 0010443 659 **■**

# TYPICAL PERFORMANCE CHARACTERISTICS

\* UNDER VERY LOW OUTPUT CURRENT CONDITIONS, DUTY CYCLE FOR MOST CIRCUITS WILL APPROACH 10% OR LESS.

TECHNOLOGY

4-437

**■** 5518468 0010444 595 **■**

# TYPICAL PERFORMANCE CHARACTERISTICS

4-438

**■ 5518468 0010445 421 ■**

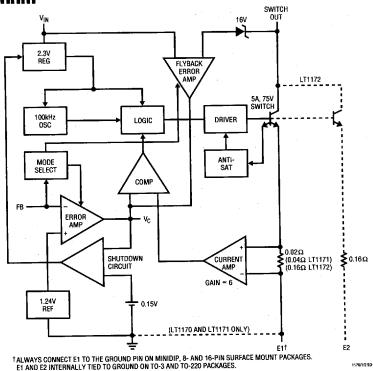

### **BLOCK DIAGRAM**

# OPERATION

The LT1170/LT1171/LT1172 are current mode switchers. This means that switch duty cycle is directly controlled by switch current rather than by output voltage. Referring to the block diagram, the switch is turned "on" at the start of each oscillator cycle. It is turned "off" when switch current reaches a predetermined level. Control of output voltage is obtained by using the output of a voltage sensing error amplifier to set current trip level. This technique has several advantages. First, it has immediate response to input voltage variations, unlike ordinary switchers which have notoriously poor line transient response. Second, it reduces the 90° phase shift at mid-frequencies in the energy storage inductor. This greatly simplifies closedloop frequency compensation under widely varying input voltage or output load conditions. Finally, it allows simple pulse-by-pulse current limiting to provide maximum switch

protection under output overload or short conditions. A low dropout internal regulator provides a 2.3V supply for all internal circuitry on the LT1170/LT1171/LT1172. This low dropout design allows input voltage to vary from 3V to 60V with virtually no change in device performance. A 100kHz oscillator is the basic clock for all internal timing. It turns "on" the output switch via the logic and driver circuitry. Special adaptive anti-sat circuitry detects onset of saturation in the power switch and adjusts driver current instantaneously to limit switch saturation. This minimizes driver dissipation and provides very rapid turnoff of the switch.

A 1.2V bandgap reference biases the positive input of the error amplifier. The negative input is brought out for output voltage sensing. This feedback pin has a second

4-439

5518468 0010446 368 📟

### **OPERATION**

function; when pulled low with an external resistor, it programs the LT1170/LT1171/LT1172 to disconnect the main error amplifier output and connects the output of the flyback amplifier to the comparator input. The LT1170/ LT1171/LT1172 will then regulate the value of the flyback pulse with respect to the supply voltage.\* This flyback pulse is directly proportional to output voltage in the traditional transformer coupled flyback topology regulator. By regulating the amplitude of the flyback pulse, the output voltage can be regulated with no direct connection between input and output. The output is fully floating up to the breakdown voltage of the transformer windings. Multiple floating outputs are easily obtained with additional windings. A special delay network inside the LT1170/ LT1171/LT1172 ignores the leakage inductance spike at the leading edge of the flyback pulse to improve output regulation.

The error signal developed at the comparator input is brought out externally. This pin ( $V_C$ ) has four different functions. It is used for frequency compensation, current limit adjustment, soft starting, and total regulator shutdown. During normal regulator operation this pin sits at a voltage between 0.9V (low output current) and 2.0V (high output current). The error amplifiers are current output ( $g_m$ ) types, so this voltage can be externally clamped for adjusting current limit. Likewise, a capacitor coupled external clamp will provide soft start. Switch duty cycle goes to zero if the  $V_C$  pin is pulled to ground through a diode, placing the LT1170/LT1171/LT1172 in an idle mode. Pulling the  $V_C$  pin below 0.15V causes total regulator shutdown, with only 50 $\mu$ A supply current for shutdown circuitry biasing. See AN19 for full application details.

### Extra Pins on the MiniDIP and Surface Mount Packages

The 8- and 16-pin versions of the LT1172 have the emitters of the power transistor brought out separately from the ground pin. This eliminates errors due to ground pin voltage drops and allows the user to reduce switch current limit 2:1 by leaving the second emitter (E2) disconnected. The first emitter (E1) should always be connected to the ground pin. Note that switch "on" resistance doubles when E2 is left open, so efficiency will suffer somewhat

when switch currents exceed 300mA. Also, note that chip dissipation will actually *increase* with E2 open during normal load operation, even though dissipation in current limit mode will *decrease*. See "Thermal Considerations" next.

# Thermal Considerations When Using the MiniDIP and SOL Packages

The low supply current and high switch efficiency of the LT1172 allow it to be used without a heat sink in most applications when the TO-220 or TO-3 package is selected. These packages are rated at 50°C/W and 35°C/W respectively. The miniDIPs, however, are rated at 100°C/W in ceramic (J) and 130°C/W in plastic (N).

Care should be taken for miniDIP applications to ensure that the worst case input voltage and load current conditions do not cause excessive die temperatures. The following formulas can be used as a rough guide to calculate LT1172 power dissipation. For more details, the reader is referred to Application Note 19 (AN19), "Efficiency Calculations" section.

Average supply current (including driver current) is:

$$I_{IN} \approx 6\text{mA} + I_{SW}(0.004 + DC/40)$$

Isw = switch current

DC = switch duty cycle

Switch power dissipation is given by:

$$P_{SW} = (I_{SW})^2 \cdot R_{SW} \cdot DC$$

$R_{SW} = LT1172$  switch "on" resistance (1 $\Omega$  maximum)

Total power dissipation is the sum of supply current times input voltage plus switch power:

$$P_{D(TOT)} = (I_{IN})(V_{IN}) + P_{SW}$$

In a typical example, using a boost converter to generate 12V at 0.12A from a 5V input, duty cycle is approximately 60%, and switch current is about 0.65A, yielding:

$$I_{IN} = 6mA + 0.65(0.004 + DC/40) = 18mA$$

$$P_{SW} = (0.65)^2 \cdot 1\Omega \cdot (0.6) = 0.25W$$

$$P_{D(TOT)} = (5V)(0.018A) + 0.25 = 0.34W$$

<sup>\*</sup>See note under block diagram.

### OPERATION

Temperature rise in a plastic miniDIP would be 130°C/W times 0.34W, or approximately 44°C. The maximum ambient temperature would be limited to 100°C (commercial temperature limit) minus 44°C. or 56°C.

in most applications, full load current is used to calculate die temperature. However, if overload conditions must also be accounted for, four approaches are possible. First, if loss of regulated output is acceptable under overload conditions, the internal thermal limit of the LT1172 will protect the die in most applications by shutting off switch current. Thermal limit is not a tested parameter, however, and should be considered only for noncritical applications with temporary overloads. A second approach is to use the larger TO-220 (T) or TO-3 (K) package which, even without a heat sink, may limit die temperatures to safe levels under overload conditions. In critical situations, heat sinking of these packages is required; especially if overload conditions must be tolerated for extended periods of time.

The third approach for lower current applications is to leave the second switch emitter (miniDIP only) open. This increases switch "on" resistance by 2:1, but reduces switch current limit by 2:1 also, resulting in a net 2:1 reduction in I<sup>2</sup>R switch dissipation under current limit conditions.

The fourth approach is to clamp the V<sub>C</sub> pin to a voltage less than its internal clamp level of 2V. The LT1172 switch current limit is zero at approximately 1V on the V<sub>C</sub> pin and 2A at 2V on the V<sub>C</sub> pin. Peak switch current can be externally clamped between these two levels with a diode. See AN19 for details.

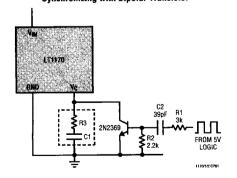

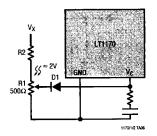

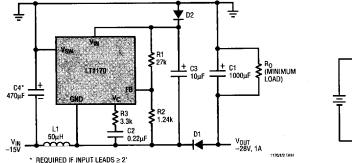

### Synchronizing with Bipolar Transistor

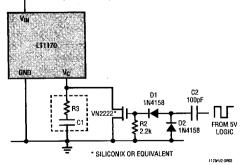

### LT1170/LT1171/LT1172 Synchronizing

The LT1170/LT1171/LT1172 can be externally synchronized in the frequency range of 120kHz to 160kHz. This is accomplished as shown in the accompanying figures. Synchronizing occurs when the V<sub>C</sub> pin is pulled to ground with an external transistor. To avoid disturbing the DC characteristics of the internal error amplifier, the width of the synchronizing pulse should be under 0.3µs. C2 sets the pulse width at  $\approx 0.2 \mu s$ . The effect of a synchronizing pulse on the LT1170/LT1171/LT1172 amplifier offset can be calculated from:

$$\Delta V_{OS} = \frac{\left(\frac{KT}{q}\right)\!\!\left(t_S\right)\!\!\left(f_S\!\right)\!\!\left(I_C + \frac{V_C}{R3}\right)}{I_C}$$

$\frac{KT}{q}$  = 26mV at 25°C

ts = pulse width

fs = pulse frequency

$I_C = V_C$  source current ( $\approx 200 \mu A$ )

V<sub>C</sub> = operating V<sub>C</sub> voltage (1V to 2V)

R3 = resistor used to set mid-frequency "zero" in frequency compensation network.

With  $t_S = 0.2 \mu s$ ,  $t_S = 150 kHz$ ,  $V_C = 1.5 V$ , and R3 = 2 k, offset voltage shift is ≈3.8mV. This is not particularly bothersome, but note that high offsets could result if R3 were reduced to a much lower value. Also, the synchronizing transistor must sink higher currents with low values of R3, so larger drives may have to be used. The transistor must be capable of pulling the V<sub>C</sub> pin to within 200mV of ground to ensure synchronizing.

#### Synchronizing with MOS Transistor

4-441

5518468 0010448 130 🚥

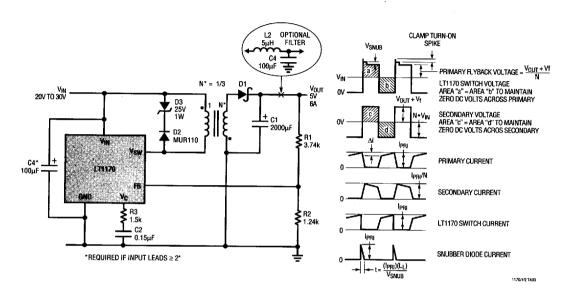

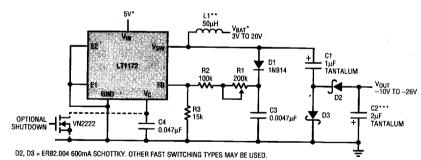

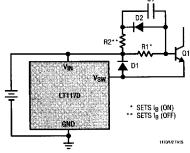

#### Flyback Converter

#### **LCD Contrast Supply**

- V<sub>IN</sub> AND BATTERY MAY BE TIED TOGETHER. MAXIMUM VALUE FOR V<sub>BAT</sub> IS EQUAL TO THE | NEGATIVE OUTPUT | + 1V. WITH HIGHER BATTERY VOLTAGES, HIGHEST EFFICIENCY IS OBTAINED BY RUNNING THE LT1172 V<sub>IN</sub> PIN FROM 5V. SHUTTING OFF THE 5V SUPPLY WILL AUTOMATICALLY TURN OFF THE LT1172. EFFICIENCY IS ABOUT 80% AT I<sub>OUT</sub> = 25mA.

- R1, R2, R3 ARE MADE LARGE TO MINIMIZE BATTERY DRAIN IN SHUTDOWN, WHICH IS APPROXIMATELY VBAT /(R1 + R2 + R3).

- •• FOR HIGH EFFICIENCY, L1 SHOULD BE MADE ON A FERRITE OR MOLYPERMALLDY CORE. PEAK INDUCTOR CURRENTS ARE ABOUT 500mA AT P<sub>OUT</sub> = 0.7Ω. INDUCTOR SERIES RESISTANCE SHOULD BE LESS THAN 0.4Ω FOR HIGH EFFICIENCY.

- \*\*\* OUTPUT RIPPLE IS ABOUT 200mV<sub>P-P</sub> TO 400mV<sub>P-P</sub> WITH C2 = 2μF TANTALUM. IF LOWER RIPPLE IS DESIRED, INCREASE C2, OR ADD A 10Ω, 1μF TANTALUM OUTPUT FILTER.

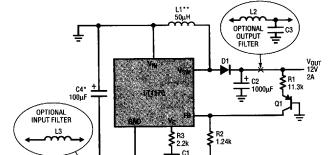

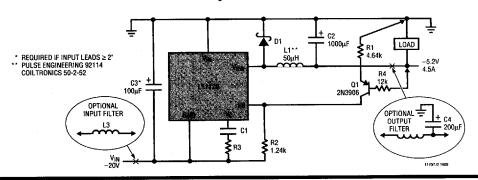

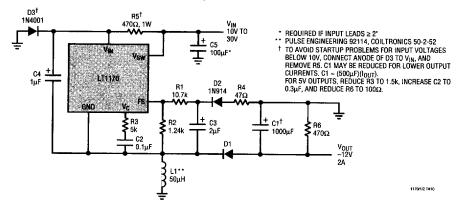

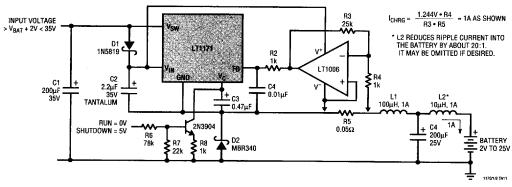

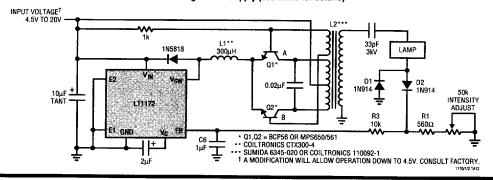

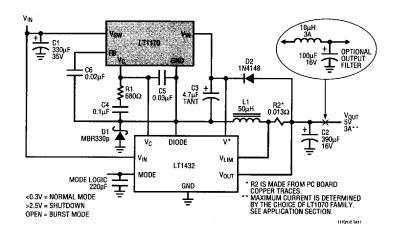

# TYPICAL APPLICATIONS (Note that maximum output currents are divided by 2 for LT1171, by 4 for LT1172.)

1170/1/2 TA05

# **Driving High Voltage FET** (for Off-Line Applications, See AN25) 10V TO 20V

### **External Current Limit**

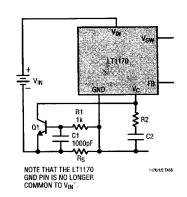

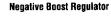

Negative-to-Positive Buck-Boost Converter<sup>†</sup>

0.22µF

V<sub>IN</sub> -20V

- \* REQUIRED IF INPUT LEADS ≥ 2\*

\*\* PULSE ENGINEERING 92114, COILTRONICS 50-2-52

† THIS CIRCUIT IS OFTEN USED TO CONVERT –48V TO 5V. TO GUARANTEE FULL SHORT-CIRCUIT PROTECTION, THE CURRENT LIMIT CIRCUIT SHOWN IN AN19, FIGURE 39, SHOULD BE ADDED WITH C1 REDUCED TO 200pF.

**External Current Limit**

#### **Negative Buck Converter**

4-443

# 5518468 0010450 899

#### Positive-to-Negative Buck-Boost Converter

#### **High Efficiency Constant Current Charger**

### Backlight CCFL Supply (see AN45 for details)

### 4-444

### **■** 5518468 0010451 725 **■**

#### **Positive Buck Converter** $V_{IN}$ REQUIRED IF INPUT LEADS ≥ 2" D3 PULSE ENGINEERING 92114 COILTRONICS 50-2-52 L2 OPTIONAL OUTPUT C5 2.2µF 200μ LT1170 FILTER D2 1**N**914 R1 3.74k <u>|+</u> C5\* 100μF ≹ R3 470 **≸**R2 1.24k ≸<sub>10Ω</sub> $470\Omega$ L1\*\* 5V, 4.5A 100mA 201 1000µF MINIMUM

Driving High Voltage NPN

TECHNOLOGY

4-445

**■ 5518468 0010452 661 ■**

#### High Efficiency 5V Buck Converter

#### **Positive Current Boosted Buck Converter**