TOSHIBA CMOS Digital Integrated Circuit Silicon Monolithic

# TC9268F,TC9268P

#### Σ-Δ Modulation System DA Converter with Built-In 8 Times Over Sampling Digital Filter

TC9268F, TC9268P are 2'nd order  $\Sigma$ - $\Delta$  modulation system 1 bit DA converter incorporating an 8-times over sampling digital filter developed for digital audio equipment.

Because the IC is small package (SOP20, DIP20) and includes the de-emphasis filter, it is possible to constitute reducing the size and cost of the DA converter.

#### **Features**

- Built-in 8-times over sampling digital filter.

- Low voltage operate (3.3 V).

- Built-in digital de-emphasis filter.

- Over sampling ratio (OSR) is 192 fs.

- Sampling frequency (fs): 44.1 kHz

- Support double speed operation.

- Characteristics of the digital filter and DA converter are as follows:

Weight SOP20-P-300-1.27: 0.48 g (typ.) DIP20-P-300-2.54A: 1.4 g (typ.)

#### **Digital Filter**

|                        | DIGITAL<br>FILTER | PASS-BAND<br>RIPPLE | TRANSIENT<br>BAND WIDTH | STOP-BAND<br>SUPPRESSION |

|------------------------|-------------------|---------------------|-------------------------|--------------------------|

| Standard operation     | 8 fs              | ±0.11 dB            | 20 k~24.1 kHz           | – 26 dB                  |

| Double speed operation | 8 fs              | ±0.11 dB            | 20 k~24.1 kHz           | – 26 dB                  |

1

#### DA Converter $(V_{DD} = 5 V)$

|                        | OSR    | NOISE<br>DISTORTION | S/N RATIO    |

|------------------------|--------|---------------------|--------------|

| Standard operation     | 192 fs | – 90 dB (Typ.)      | 98 dB (Typ.) |

| Double speed operation | 96 fs  | -85 dB (Typ.)       | 95 dB (Typ.) |

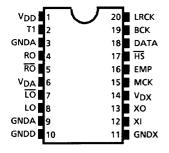

#### Pin Assignment (top view)

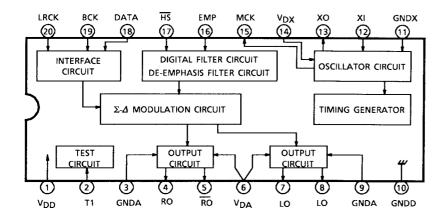

# **Block Diagram**

#### **Pin Function**

| Pin No. | Symbol   | I/O | Function&Operation                                                         | Remarks |

|---------|----------|-----|----------------------------------------------------------------------------|---------|

| 1       | $V_{DD}$ | _   | Digital power supply pin                                                   |         |

| 2       | T1       | I   | Test pin. Normally, use at "L".                                            |         |

| 3       | GNDA     | _   | Analog GND pin                                                             |         |

| 4       | RO       | 0   | Right channel data forward output pin.                                     |         |

| 5       | RO       | 0   | Right channel data reversed output pin.                                    |         |

| 6       | $V_{DA}$ | _   | Analog power supply pin                                                    |         |

| 7       | ΙŌ       | 0   | Left channel data reverse output pin.                                      |         |

| 8       | LO       | 0   | Left channel data forward output pin.                                      |         |

| 9       | GNDA     | _   | Analog GND pin                                                             |         |

| 10      | GNDD     | _   | Digital GND pin.                                                           |         |

| 11      | GNDX     | _   | Crystal oscillator GND pin.                                                |         |

| 12      | XI       | ı   | Crystal oscillator connection pin.                                         |         |

| 13      | хо       | 0   | Connect to a crystal oscillator, generates needed for the system. (384 fs) | xı xo   |

| 14      | $V_{DX}$ | _   | Oscillator power supply pin.                                               |         |

| 15      | MCK      | 0   | System clock output pin. (384 fs)                                          |         |

| 16      | EMP      |     | De-emphasis filter ON/OFF switching pin.                                   |         |

| 10      | EIVIF    | '   | ON at "H" and OFF at "L".                                                  |         |

| 17      | HS       |     | Standard/double speed operation mode switching pin.                        |         |

| 17      | 113      |     | Standard operation at "H", double speed operation at "L".                  |         |

| 18      | DATA     | 1   | Audio data input pin.                                                      |         |

| 19      | BCK      | I   | Bit clock input pin.                                                       |         |

| 20      | LRCK     | I   | LR clock input pin.                                                        |         |

#### **Description of Block Operation**

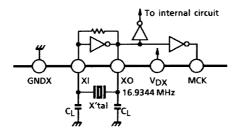

#### 1. Crystal Oscillation Circuit and Timing Generator

The clock required for internal operations is generated by connecting a crystal and condensers as shown in the diagram below.

The IC will also operate when a system clock is input from an external source through the XI pin (pin 12). However, in this situation, due consideration must be given to the fact that waveform characteristics, such as jitter and rising/falling characteristics of the system clock, significantly affect the DA converter's noise distortion and the S/N ratio.

$C_L = 10~33 pF$

Use a crystal with a low CI value and favorable start-up characteristics.

Figure 1 Configuration of Crystal Oscillation Circuit

The timing generator generates the clocks and process timing signals required for such functions as digital filtering and de-emphasis filtering.

#### 2. Data Input Circuit

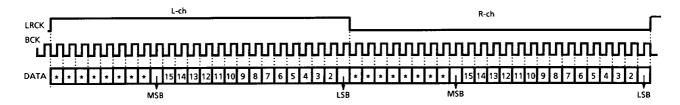

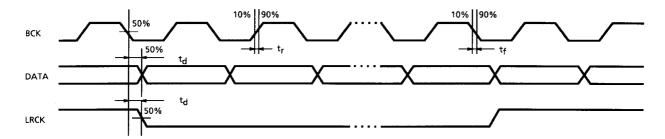

DATA and the LRCK are loaded to the LSI internal shift registers on the BCK signal rising edge. It is consequently necessary for the DATA and LRCK signals to be synchronized and input on the BCK signal falling edge as indicated in the timing example below. BCK is available only 48 fs.

Also, as DATA has been designed so that the 16 bits before the change point of LRCK are regarded as valid data, the data must be input with Right-justified mode.

\*: Not effective

Figure 2 Example of Input Timing Chart

3

#### 3. Digital Filter

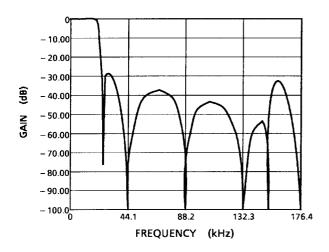

The 8-times oversampling IIR digital filter eliminates the noise returned from outside the bandwidth during standard and double speed operations.

Table 1 Characteristics of the Digital Filter

|                        | Pass-Band Ripple | Transient Bandwidth | Attenuation   |

|------------------------|------------------|---------------------|---------------|

| Standard operation     | ±0.11dB          | 20.0 k~24.1 kHz     | -26dB or less |

| Double speed operation | ±0.11dB          | 20.0 k~24.1 kHz     | -26dB or less |

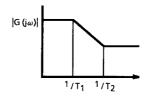

The characteristics of the digital filter frequencies are shown below. (double speed operation is same)

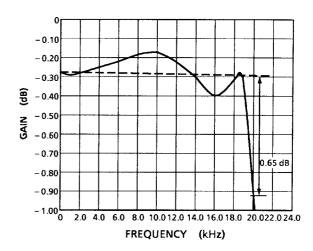

#### 4. De-Emphasis Filter

The built-in IIR type digital de-emphasis filter circuit is available for  $fs=44.1\ kHz$ . ON/OFF is controlled with the EMP pin.

Table 2 De-Emphasis Filter Setting

| EMP PIN            | Н  | L   |

|--------------------|----|-----|

| De-emphasis Filter | ON | OFF |

The digitalization of the de-emphasis filter eliminates the need for such external components as resistors, condensers and analog switches. In addition to this, the coefficients are aligned to reduce error in the de-emphasis filter characteristics.

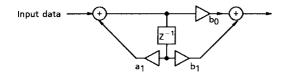

The filter structure and characteristics are shown below.

Transfer function: H (Z) =  $\frac{(b_0 + b_1 Z^{-1})}{(1 - a_1 Z^{-1})}$

$T_1 = 50~\mu s, \, T_2 = 15~\mu s$

Figure 4 IIR Digital De-Emphasis Filter

Figure 5 Filter Characteristics

#### 5. DA Conversion Circuit

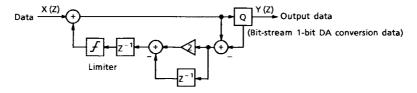

The IC incorporates a 2'nd order  $\Sigma$ - $\Delta$  modulation DA converter for two channels (simultaneous output type). The internal structure of this is shown in Figure 6.

2'nd order  $\sum -\Delta$  converter: Y (Z) = X (Z) +  $(1 - Z^{-1})^2$ Q (Z)

Figure 6  $\Sigma$ - $\Delta$  Modulation DA Converter

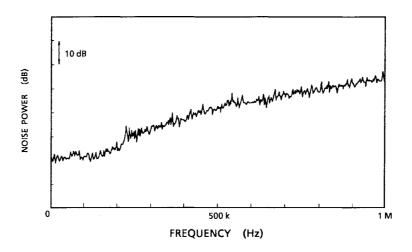

The  $\Sigma$ - $\Delta$  modulation clock has been designed to operate at 192 fs (when 384 fs). The noise shaping characteristics are shown in Figure 7.

Figure 7 Noise Shaping Characteristic

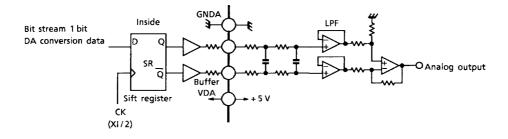

#### 6. Data Output Circuit

In this circuits, output data waveform is shaped and forward and reverse signals of bit stream data are output to the outside through a buffer.

By differentiating these forward signal and the reverse signal in the external analog circuit, DA conversion output of low distortion and high S/N ratio can be obtained.

Figure 8 Construction of Data Output Circuit

# Maximum Ratings (Ta = 25°C)

| Characteristics       |         | Symbol           | Rating                     | Unit  |  |

|-----------------------|---------|------------------|----------------------------|-------|--|

|                       |         | $V_{DD}$         | -0.3~6.0                   |       |  |

| Supply voltage        |         | $V_{DA}$         | -0.3~6.0                   | V     |  |

|                       |         | $V_{DX}$         | -0.3~6.0                   |       |  |

| Input voltage         |         | V <sub>in</sub>  | -0.3~V <sub>DD</sub> + 0.3 | V     |  |

| Power dissipation     | TC9268F |                  | 200                        | mW    |  |

| Fower dissipation     | TC9268P | P <sub>D</sub>   | 300                        | 11100 |  |

| Operating temperature |         | T <sub>opr</sub> | -35~85                     | °C    |  |

| Storage temperature   |         | T <sub>stg</sub> | -55~150                    | °C    |  |

# Electrical Characteristics (unless otherwise specified, Ta = 25°C, $V_{DD} = V_{DX} = V_{DA} = 5$ V) DC Characteristics

| Chara             | acteristics | Symbol          | Test<br>Circuit | Test Condition              | Min                   | Тур. | Max                   | Unit |

|-------------------|-------------|-----------------|-----------------|-----------------------------|-----------------------|------|-----------------------|------|

|                   |             |                 |                 |                             | 4.5                   | 5.0  | 5.5                   |      |

| Operating supply  | voltage (1) | $V_{DX}$        | _               | Ta = −35~85°C               | 4.5                   | 5.0  | 5.5                   | V    |

|                   |             | $V_{DA}$        |                 |                             | 4.5                   | 5.0  | 5.5                   |      |

|                   |             | $V_{DD}$        |                 | Ta = −15~55°C               | 3.3                   | 3.5  | 5.5                   |      |

| Operating supply  | voltage (2) | $V_{DX}$        | T —             | Operation frequency         | 3.3                   | 3.5  | 5.5                   | V    |

|                   |             | $V_{DA}$        |                 | f <sub>opr</sub> = 16.9 MHz | 3.3                   | 3.5  | 5.5                   |      |

| Power dissipation | า           | I <sub>DD</sub> | _               | XI = 16.9 MHz               | _                     | 12   | 20                    | mA   |

| Input voltage     | "H" level   | V <sub>IH</sub> |                 |                             | V <sub>DD</sub> × 0.7 |      | V <sub>DD</sub>       | V    |

| input voitage     | "L" level   | V <sub>IL</sub> |                 | _                           | 0                     |      | V <sub>DD</sub> × 0.3 | ٧    |

| Input current     | "H" level   | I <sub>IH</sub> |                 |                             | -10                   |      | 10                    | μА   |

| input current     | "L" level   | I <sub>IL</sub> |                 | _                           | -10                   |      | 10                    | μΛ   |

### AC Characteristics (over sampling ratio = 192 fs)

| Characteristics                     | Symbol           | Test<br>Circuit | Test Condition                               | Min | Тур.    | Max | Unit |

|-------------------------------------|------------------|-----------------|----------------------------------------------|-----|---------|-----|------|

| Table harmonic distortion + noise 1 | THD + N1         | 1               | 1 kHz Sine wave, full-scale input            | _   | -90     | -80 | dB   |

|                                     |                  |                 | $V_{DD} = V_{DX} = V_{DA} = 5 V$             |     |         |     |      |

| Table harmonic distortion + noise 2 | THD + N2         | 1               | 1 kHz Sine wave, full-scale input            | _   | -86     | -78 | dB   |

|                                     |                  |                 | $V_{DD} = V_{DX} = V_{DA} = 3.5 \text{ V}$   |     |         |     |      |

| S/N ratio                           | S/N              | 1               | _                                            | 90  | 98      | _   | dB   |

| Dynamic range                       | DR               | 1               | 1 kHz Sine wave,<br>-60dB input conversion   | 90  | 95      | _   | dB   |

| Cross-talk                          | СТ               | 1               | 1 kHz Sine wave, full-scale input            | _   | -95     | -90 | dB   |

| Operating frequency                 | f <sub>opr</sub> | _               | $V_{DD} = V_{DA} = V_{DX} \ge 4.5 \text{ V}$ | _   | 16.9344 | _   | MHz  |

| Input fraguency                     | f <sub>LR</sub>  |                 | LRCK duty cycle = 50%                        |     | 44.1    |     | kHz  |

| Input frequency                     | f <sub>BCK</sub> |                 | BCK duty cycle = 50%                         |     | 2.1168  |     | MHz  |

| Rise time                           | t <sub>r</sub>   |                 | L DOK DOK (40, 00%)                          | _   | _       | 15  | ns   |

| Fall time                           | t <sub>f</sub>   |                 | LRCK, BCK (10~90%)                           | _   | _       | 15  | ns   |

| Delay time                          | t <sub>d</sub>   | _               | BCK <b>V</b> _Edge → LRCK, DATA              |     | _       | 40  | ns   |

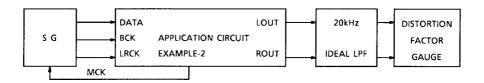

## Test Circuit-1: With the Use of Application Circuit Example-2

SG: ANRITSU MG-22A or equivalent LPF: SHIBASOKU 725C internal filter

Distortion factor gauge: SHIBASOKU 725C or equivalent

| Measuring Item | Distortion Factor Gauge Filter Setting<br>A Weight |

|----------------|----------------------------------------------------|

| THD + N, CT    | OFF                                                |

| S/N, DR        | ON                                                 |

7

A weight: IEC-A or equivalent

2003-06-27

#### AC Characteristics Stipulated Point (input signal stipulation: LRCK, BCK, DATA)

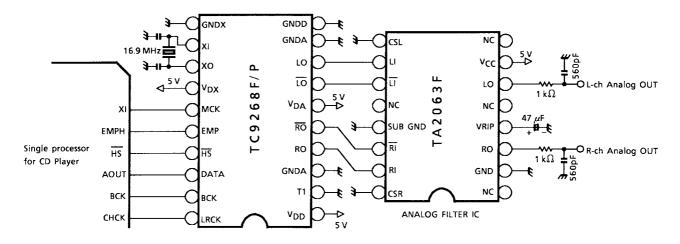

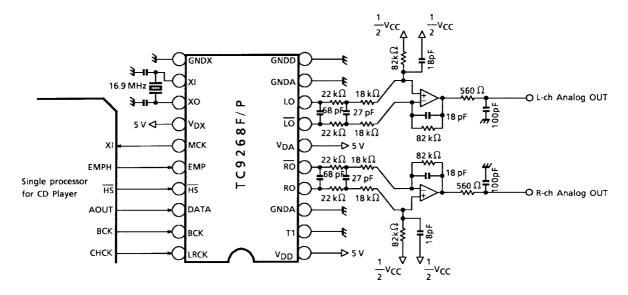

#### **Application Circuit Example-1** (+5 V single power supply used)

#### Application Circuit Example-2 (+5 V two power supply used)

8

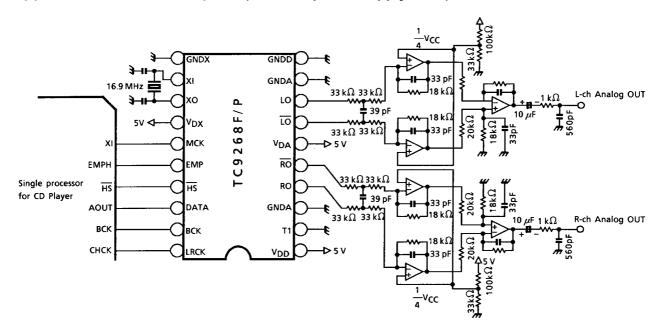

#### Application Circuit Example-3 (+5 V single power supply used)

#### **Cautions**

- Quality of crystal oscillation waveform largely affect S/N ratio and noise distortion. Further, this is also true then system clock is input externally through the XI pin of Pin 12.

- Suppress glitch of input signals (LRCK, BCK, DATA) as could as possible.

- The wiring between the TC9268F/P output and the analog filter amplifier input must be made the shortest.

- The capacitor between VDA and GNDA, VDD and GNDD, VDX and GNDX shall be connected as close to the pin as possible.

9 2003-06-27

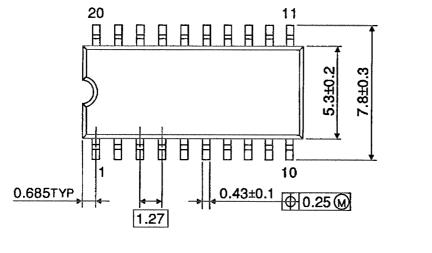

# **Package Dimensions**

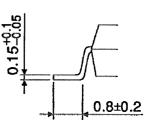

SOP20-P-300-1.27 Unit: mm

Weight: 0.48 g (typ.)

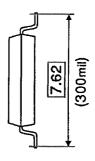

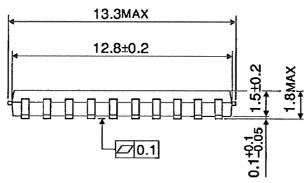

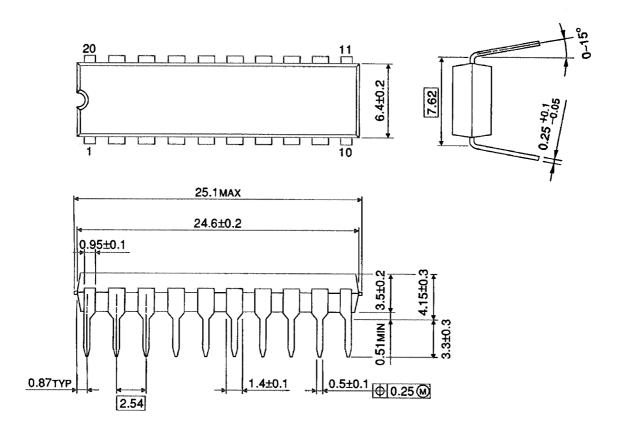

# **Package Dimensions**

DIP20-P-300-2.54A Unit: mm

Weight: 1.4 g (typ.)

#### **RESTRICTIONS ON PRODUCT USE**

Handbook" etc..

030619EBA

- The information contained herein is subject to change without notice.

- The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA for any infringements of patents or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of TOSHIBA or others.

- TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to comply with the standards of safety in making a safe design for the entire system, and to avoid situations in which a malfunction or failure of such TOSHIBA products could cause loss of human life, bodily injury or damage to property.

In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent TOSHIBA products specifications. Also, please keep in mind the precautions and conditions set forth in the "Handling Guide for Semiconductor Devices," or "TOSHIBA Semiconductor Reliability

- The TOSHIBA products listed in this document are intended for usage in general electronics applications (computer, personal equipment, office equipment, measuring equipment, industrial robotics, domestic appliances, etc.). These TOSHIBA products are neither intended nor warranted for usage in equipment that requires extraordinarily high quality and/or reliability or a malfunction or failure of which may cause loss of human life or bodily injury ("Unintended Usage"). Unintended Usage include atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, medical instruments, all types of safety devices, etc.. Unintended Usage of TOSHIBA products listed in this document shall be made at the customer's own risk.

- The products described in this document are subject to the foreign exchange and foreign trade laws.

- TOSHIBA products should not be embedded to the downstream products which are prohibited to be produced and sold, under any law and regulations.