### SANYO Semiconductors

# DATA SHEET

**CMOS LSI**

### Controller for The LC Dot Matrix LC7981 **Graphic Display**

#### Summary

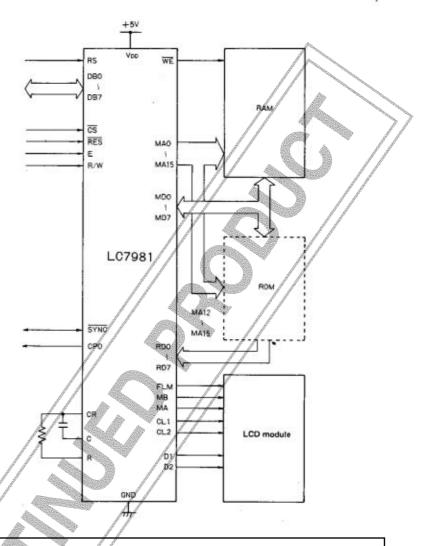

The LC7981 is a controller LSI for the liquid crystal dot matrix graphic display. It stores display data sent from the 8-bit microcomputer in the display RAM attached externally and generates dot matrix LC drive signals.

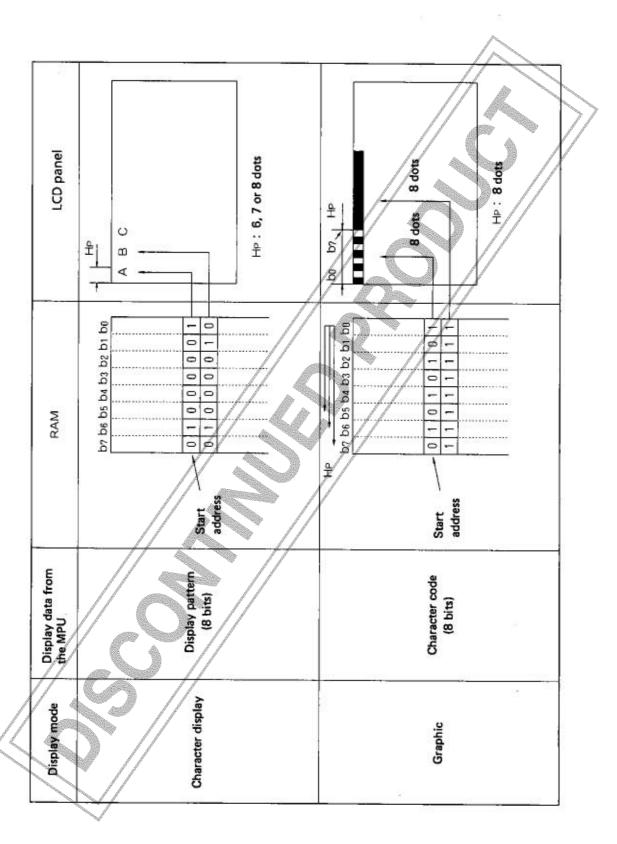

The LC7981 has two modes - the graphic mode, in which each bit of data from the external RAM either lights or does not light a dot in the LCD, and the character mode, in which character codes stored in the external RAM generate dot patterns through the built-in character-generator ROM. These two ways enable the LC7981 to cover a wide variety of applications.

As the LC7981 is fabricated using CMOS process technology, combining it with a CMOS microcomputer produces an LCD device of low power demand.

#### **Features**

- 1. Liquid crystal dot matrix graphic display controller

- 2. Display control capacity.

Graphic mode ---- 512K dots (216 bytes)

Character mode ---- 4096 characters (212 characters)

3. Character generator ROM ---- 7360 bits

Character font 5 x 7 dots

Character font 5 x 11 dots

Character font 5 x 11 dots

32 types

Total 192 types

(Extendable to 4K bytes with an external ROM)

- 4. Interfacing allowed with 8-bit MPU

- 5. Display duty (selectable by program) From static to 1/256 duty

6. A variety of instruction functions

Scroll, cursor on/off/blink, character blink, bit manipulation

- 7. Display system ---- A system or B system selectable

- 8. Built-in oscillator (resistor, capacitor attached externally)

- 9. Low power demand

- 10. Single +5V power supply

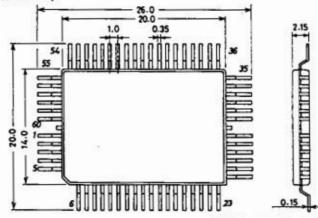

### Package Dimensions 3055A-Q60CIC (unit: mm)

SANYO: QIP60C

|                               |                         |                                 |                            |         |                         | 0.50                 | unit  |

|-------------------------------|-------------------------|---------------------------------|----------------------------|---------|-------------------------|----------------------|-------|

| Maximum Supply Voltage        | Vpo max                 |                                 |                            | -0.     | 3to +7.                 | 0                    | V     |

| Input Voltage                 | Vi                      |                                 |                            | -0.3to\ | /oo+0.                  | 3                    | V     |

| Output Voltage                | Vo                      |                                 |                            | -0.3to  | )<br>)<br>)<br>()<br>() | 3                    | V     |

| Allowable Power Dissipation   | Pd max                  | Ta=75℃                          |                            |         | 20                      | Q                    | mW    |

| Operating Temperature         | Topr                    |                                 |                            | -//=    | 20 <b>to</b> +7         | 5                    | to    |

| Storage Temperature           | Tstg                    | 4-1                             |                            | // -5   | 5 <b>to</b> +12         | 5                    | C     |

| lowable Operating Conditions  | /T <sub>a</sub> =–20 to | +75°C, GND=0V                   |                            |         |                         |                      |       |

|                               |                         |                                 |                            | mio     | typ                     | max                  | unit  |

| Supply Voltage                | Voo                     |                                 |                            | 4.75    | 1                       | 8.25                 | V     |

| Input "H"-Level Voltage       | VIH1                    |                                 | Is except for SYNC, CF     | 2.2     |                         | Voo                  | V     |

| Input "L"-Level Voltage       | VILI                    |                                 |                            | 0       |                         | 0.8                  | V     |

| Input "H"-Level Voltage       | VIH2                    | SYNC, CR                        |                            | ©.7Vpp  |                         | Voo                  | V     |

| Input "L"-Level Voltage       | VIL2                    | SYNC, CR                        |                            | 0/      |                         | 0.3Vpp               | V     |

| Output "H"-Level Voltage      | VoHI                    | IOH=-0.6mA<br>DB0to7, WE, MA0to | 5, MD0to?                  | 2.A     |                         | VDD                  | V     |

| Output "L"-Level Voltage      | VOL1                    | IOL=1.6mA<br>DB0to7, WE, MADto  |                            | // 0    |                         | 0.4                  | ٧     |

| Output "H"-Level Voltage      | VOH2                    | SYNC, CPO, FI                   |                            | VDD-0   | . 4                     | VDD                  | V     |

| Output "L"-Level Voltage      | VOL2                    | SYNC, CPO, FL                   | M. CL1/GC2.                | 0       |                         | 0.4                  | ٧     |

| ternal Clock Operation        | A.                      |                                 |                            |         |                         |                      |       |

| Clock OSC Frequency           | fosc //                 | Cf=15pF± 5 %, Rf=               | 39kΩ ± 2 %, Note 1         | 500     | 600                     | 700                  | kHz   |

| ternal Clock Operation        |                         |                                 |                            |         |                         | 0.75                 |       |

| Clock Frequency               | fcp                     | Note 2                          | **                         |         |                         | 2.5                  | MHz   |

| Clock Duty                    | Duty                    | Note 3                          |                            | 47.5    | 50                      | 52.5                 | %     |

| Clock Rise Time               | trop                    | Note 3                          |                            |         |                         | 50                   | ns    |

| Clock Fall Time               | tfcp                    | Note 3                          |                            |         |                         | 50                   | ns    |

|                               |                         | S //                            |                            |         |                         | 32700                | 100   |

| ctrical Characteristics/Ta=-2 | 0 to +75°C              | GND=0V, VDD=5V±                 | 5%                         | min     | typ                     | max                  | unit  |

| Input Leak Current            | -lini                   | VIN-Oto VDD, CS, E              |                            | - 5     | 1,70                    | 5                    | μА    |

| Current Dissipation           | loci                    | CR oscillation, fosc=           | 이 얼마를 다 하는 그의 아이라 가게 되었다.  | ×       | 2                       | 4                    | mΑ    |

| Current Dissipation           | CC2                     | External clock, fcp=            |                            |         | 3                       | 5                    | mA    |

| Pull-up Current               | TPL /                   | VIN=GND, DB0to7,                |                            |         | 10                      | 20                   | μΑ    |

| (Note 1)                      |                         | (Note 2)                        |                            | (Note   | 3)                      |                      |       |

|                               |                         |                                 | - 1                        | Th - -  | т                       |                      |       |

| R                             |                         | OpenR                           |                            | -       |                         |                      | _     |

| PH ≥ CH =                     | r                       | Open — C                        | 0.7Vcc<br>0.5Vcc<br>0.3Vcc | ¥       |                         | 7                    | -     |

| CR                            | _ L                     | Oscillator                      |                            |         |                         |                      | 10.00 |

|                               |                         | 9.74                            | trep                       | -       |                         | $ty = -\frac{T}{Th}$ | n     |

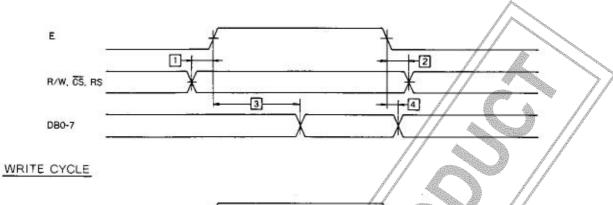

### **Timing Characteristics**

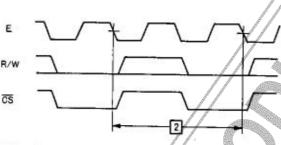

### Bus read/write operation 1

### READ CYCLE

Ta=-20to+75°C. VDD=5 V±5%. GND=0 V

| Na | Item                     | Symbol | min typ | max | unit | Conditions |

|----|--------------------------|--------|---------|-----|------|------------|

| 1  | Address set-up time      | taš    | 90      |     | ns   |            |

| 2  | Address hold time        | ĮAH.   | 10      |     | ns   |            |

| 3  | Data delay time (read)   | tDDR   |         | 140 | ns   | CL=50pF    |

| 4  | Data hold time (read)    | tDHR   | 10      |     | ns   |            |

| 5  | Data set-up time (write) | tośw   | 220     |     | ns   |            |

| 6  | Data hold time (wirte)   | *DHW   | 20      |     | ns   |            |

Note: Definition of the test waveform

The input terminals are driven at 2.4V and 0.45V. Timing is measured at 1.5V.

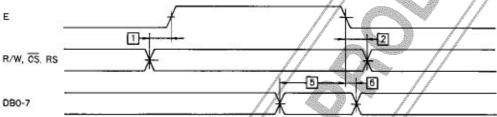

### Bus read/write operation 2

### DATA WRITE CYCLE

Ta = -20to +75°C, VDD = 5  $V \pm 5$  %, GND = 0 V

| No | Item             | Symbol | min | typ |                     | nit/ | Instruction register<br>value                     |

|----|------------------|--------|-----|-----|---------------------|------|---------------------------------------------------|

| 1  | Read cycle time  | tRCY   |     |     | (Ap+ 2 )×10° +200   | ns   | 0 DH                                              |

| 2  | Write cycle time | twcy1  |     |     | (2 Hp+2)×10³ +200 r | ns   | 0 EH. 0 FH                                        |

| 2  | Write cycle time | twcy2  |     |     | Fosc +200 r         | ns   | 0 CH                                              |

| 2  | Write cycle time | twcy3  | 1   |     | 2000<br>Fosc +200   | ns   | 00H, 01H, 02H, 03H<br>04H, 08H, 09H<br>0 AH, 0 BH |

Notes: (1) In the character mode, Hp is the number of horizontal dots per character in a character display. In the graphic mode, Hp indicates how many bits from RAM appear in a 1-byte display.

- (2) FOSC is the oscillating frequency, expressed in MHz.

- (3) All measurement points are at 1.5V.

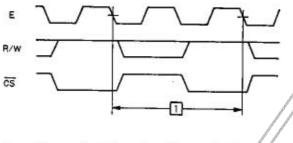

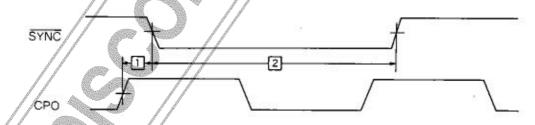

### Parallel operation (at master mode)

Ta = -20 to +75%.  $VDD = 5 V \pm 5\%$ . GND = 0 V

| No. | Item             | Symbol | min | typ | max | unit | Conditions |

|-----|------------------|--------|-----|-----|-----|------|------------|

| 1   | SYNC delay time  | tosy   |     |     | 100 | ns   |            |

| 2   | SYNC pulse width | twsy   | 350 |     |     | ns   |            |

Notes: (1) All output terminals are under no load.

(2) All measurement points are at 0.5VDD.

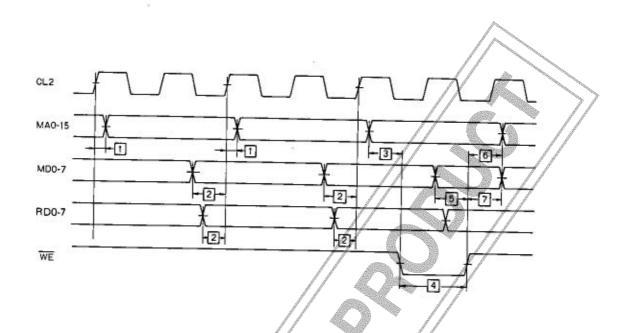

## Interface with external RAM and ROM

READ CYCLE

Ta=-20to+75°C, VDD-5V±5%, GND-0V

| No. | Item                              | Symbol min typ | max | unit | Conditions |

|-----|-----------------------------------|----------------|-----|------|------------|

| 1   | MA0-15<br>read address delay time | TOMAR          | 95  | ns   |            |

| 2   | MD0-7 · RD0-7<br>set-up time      | tsMOR 105      |     | ns   |            |

WRITE CYCLE

Ta

$$-20$$

**to**  $+75$ °C. VDD = 5  $V \pm 5$  %. GND = 0  $V$

| Na | Item                       | Symbol | min | typ | max | unit | Conditions |

|----|----------------------------|--------|-----|-----|-----|------|------------|

| 3  | Memory address set-up time | tswaw  | 50  |     |     | ns   |            |

| 4  | WE pulse width             | twwe   | 350 |     |     | ns   |            |

| 5  | Memory data set-up time    | tsmow  | 250 |     |     | ns   |            |

| 6  | Memory address hold time   | tHMAW  | 50  |     |     | ns   |            |

| 7  | Memory data hold time      | tHMDW  | 50  |     |     | ns   |            |

- Notes: (1) All output terminals are under no load.

- (2) All measurement points are at 1.5V.

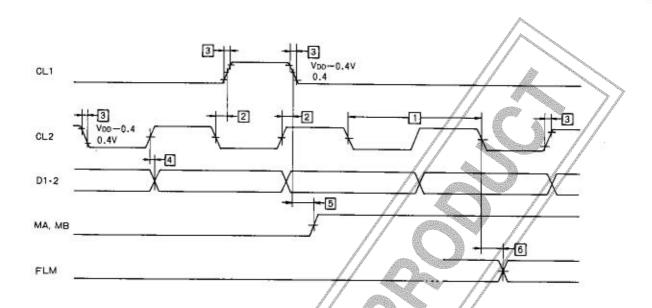

### Interface with the driver LSI

Ta=-20to+75℃, Voo=5V±5%, GND=0V

| No | Item                    | Symbol | min typ | max | unit | Conditions |

|----|-------------------------|--------|---------|-----|------|------------|

|    | Clock cycle time        | teve 4 | 400     |     | ns   |            |

| 2  | Clock phase difference  | tocu   |         | 100 | ns   |            |

| 3  | Clock rise/fall time    | ICRE   |         | 30  | ns   |            |

| 4  | D1-2 phase difference   | top    |         | 100 | ns   | 2562       |

| 5  | MA, MB phase difference | toma   |         | 200 | ns   |            |

| 6  | FLM phase difference    | torm   |         | 200 | ns   |            |

Notes: (1) All output terminals are under no load.

(2) All measurement points other than those specified are at 0.5VDD.

#### Pin Assignment MB MA1 MA2 MA3 MA5 MA5 MA7 MA8 888888 W & W W -54 MA10 53 MA11 C 6 52 MA12 R 7 CR 51 MA13 8 CPO 50 **MA14** 9 49 MA15 FLM 10 48 D2 CLI 11 47 D1 SYNC 12 WE 46 CL2 13 LC7981 RES 45 RD0 44 RO1 CS 15 43 RO2 E R/W 42 RO3 17 41 RO4 RS 18 40 RD5 MA 19 39 806 GND 20 38 RD7 DB7 21 37 MD0 DB6 22 36 MD1 DB5 23 8 2 8 2 2 2 2 2 2 2 2 MD5 DB4 DB3 DB2 V<sub>00</sub> V<sub>00</sub> (Top view) **Block Diagram** SYNC CLT MB WE Refresh address 16 counter (1) Dot counte Multiplexer 16 Refresh address RAM counter (2) I/O interface circuit input DB0toDB7 16 Cursor address register counter CS Dot register MD0toMD7 E RS R/W 4 Extended Row address RES ROM Data 6 counter 8 output Character register generator Cursor ROM signal Mode generator RD0toRD7 control Control register Instruc Multiplexer signal tion register Control Busy signal Serial-parallel conversion D1 flag Oscillating circuit Serial-parallel conversion - D2 CLZ CPO

When the ROM is extended, MA0 to MA11 are used for RAM addresses and MA12 to MA15 are used for the extended ROM.

#### Function of each block

#### Register

The LC7981 has 5 types of registers — the instruction register, data input register, data output register, dot register, and mode control register.

The instruction register stores such instruction codes as the start address, cursor address specification, etc. It consists of 4 bits, and the lower 4 bits of the data bus, DBO to DB3, are written into it.

The data input register temporarily stores data to be written into the external RAM, dot register, and mode control register. It consists of 8 bits.

The data output register temporarily stores data to be read from external RAM, and consists of 8 bits. When the cursor address is written into the cursor address counter via the data input register and the memory read instruction is set in the instruction register, data in external RAM is read into the data output register by internal operation. With the next instruction, the MPU reads the data output register, and completes data transfer to the MPU.

The dot register stores dot information such as the character pitch, the number of vertical dots, etc. Data sent from the MPU is written into the dot register via the data input register.

The mode control register stores LCD status information such as display on/off and cursor on/off/blink. It consists of 6 bits. Data sent from the MPU is written into this register via the data input register.

### Busy flag

When the busy flag is "1", the LC7981 is operating internally. At this time, the next instruction cannot be accepted. The busy flag is output to DB7 when RS=1, RW=1. The next instruction must be written after ensuring that the busy flag is "0". When the maximum value of the read cycle time or write cycle time has been passed after the execution of the preceding data read instruction or data write instruction, the next instruction can be executed without checking the busy flag.

#### Dot counter

The dot counter generates LC display timing according to the contents of the dot register.

#### Refresh address counter

The refresh address counter controls addresses of the external RAM, character generator ROM, extended ROM and is available in two types — refresh address counter (1) and refresh address counter (2). The former is for the upper screen, and the latter for the lower screen. In the graphic mode, 16-bit data is output and used as the address signal for the external RAM. In the character mode, the high-order 4 bits are ignored and 4 bits of the row address counter are output instead. The 4 bits are used as the address of the extended ROM.

#### Character generator ROM

The character generator ROM has a total of 7360 bits and stores data on 192 kinds of characters. Character codes from the external RAM and row codes from the row address counter are added to address signals, and ROM outputs 5-bit dot data.

There are 192 kinds of character fonts, of which 160 are 5 x 7 and 32 are 5 x 11. With extended ROM, character fonts can be increased to 256 kinds sized 8 x 16.

### Cursor address counter

The cursor address counter is a 16-bit counter which can be preset by instruction. When data is read from or written into external RAM (i.e., read/write of display dot data or character codes), the counter retains the addresses. The value indicated on the cursor address counter is automatically incremented by 1 when instructions to read/write display data and to perform bit set/clear are issued.

#### Cursor signal generator

In the character mode, the cursor can be displayed by means of instructions. The cursor is generated automatically when the cursor address counter and the row address counter reach the specified value.

### Parallel-serial conversion

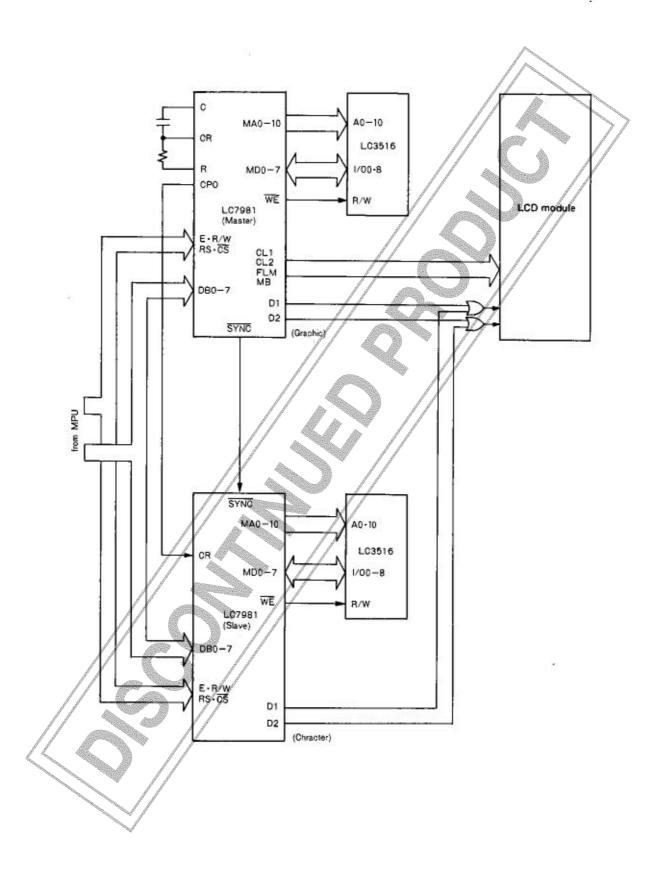

The two parallel-serial conversion circuits simultaneously transfer parallel data from the external RAM, character generator, and extended ROM to the upper and lower LC screen drive circuits as serial data.

### Pin Function

| Description | Pin No.            | Function                                                                                                                                         |

|-------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| DB0 to 7    | 21 to 28           | Data bus Three-state I/O common terminal, terminal for transmitting/receiving data to/from the MPU.                                              |

| CS          | 15                 | Chip select Selection allowed when CS=0                                                                                                          |

| R/W         | 17                 | Read/write R/W=1 MPU ←LC7981<br>R/W=0 MPU → LC7981                                                                                               |

| RS          | 18                 | Register select RS=1 instruction register RS=0 data register                                                                                     |

| E           | 16                 | Enable Data is written on the negative transition of E.  Data can be read while E=1.                                                             |

| CR, R, C    | 6,7,8              | Terminals for the CR oscillator                                                                                                                  |

| RES         | 14                 | Reset Setting RES to 0 selects display OFF, slave mode, and Hp=6.                                                                                |

| MA0 to 15   | 1 to 4<br>49 to 60 | Address output for the display RAM. For character display, raster address for external CG is output at MA12 to 15.                               |

| MD0 to 7    | 30 to 37           | Display data bus Three-state I/O common terminals.                                                                                               |

| RD0 to 7    | 38 to 45           | ROM data input Dot data from the external character generator is input.                                                                          |

| WE          | 13                 | Write enable Display RAM write signal.                                                                                                           |

| CL2         | 46                 | Display data shift clock signal.                                                                                                                 |

| CL1         | 11                 | Display data latch signal.                                                                                                                       |

| FLM         | 10                 | Frame signal,                                                                                                                                    |

| МА          | 19                 | LC drive signal AC signal A system                                                                                                               |

| МВ          | 5 /                | LC drive signal AC signal B system                                                                                                               |

| D1, D2      | 47, 48             | Display data serial output for the upper screen D2 for the lower screen                                                                          |

| сро /       | 9                  | Clock for slave                                                                                                                                  |

| SYNC        | 12                 | Sync signal for parallel operation Three-state input/output common terminal Master mode Sync signal is output.  Slave mode Sync signal is input. |

### Display control instruction

Display is controlled by writing data into the instruction register and 13 data registers. The instruction register and the data register are distinguished by the RS signal. First, write 4-bit data in the instruction register when RS=1, then specify the code of the data register. Next, with RS=0, write 8-bit data in the data register, which executes the specified instruction.

A new instruction cannot be accepted while an old instruction is being executed. As the Busy flag is set under this condition, write an instruction only after reading the Busy flag and making sure that it is 0.

However, the next instruction can be executed without checking the busy flag when the maximum read cycle time or the write cycle time has been exceeded after execution of the previous data read instruction or the data write instruction. The busy flag does not change when data is written into the instruction register (RS=1). Therefore, the busy flag need not be checked immediately after writing data into the instruction register.

#### 1) Mode control

Write code "00H" (in hexadecimal notation) in the instruction register and specify the mode control register.

| Register              | R/W | RS | DB7 | DB6 | DB5/ | DB4 DB3   | DB2 | DB1  | DB0 |

|-----------------------|-----|----|-----|-----|------|-----------|-----|------|-----|

| Instruction register  | 0 - | 1  | 0   | 0   | /0   | 0 0       | 10  | 0    | 0   |

| Mode control register | 0   | 0  | 0   | 0/  |      | MODE Date |     | 7(4) |     |

| DB5               | DB4          | DB3   | DB2    | DB1  | DB0/                        | Cursor/blink               | CG          | Graphic/character display |

|-------------------|--------------|-------|--------|------|-----------------------------|----------------------------|-------------|---------------------------|

|                   |              | 0     | 0      |      | 17                          | Cursor OFF                 | g           |                           |

|                   |              | 0     | 1      | 1 1  | 1/                          | Cursor ON                  | o c         |                           |

|                   |              | 1     | 0      |      | / 0 <                       | Cursor OFF character blink | Built-in CG |                           |

| 1,                | 1,           | 1     | 1      | 1 // |                             | Cursor blink               | 줍           |                           |

| Ó                 | Ó            | 0     | 0      | 1/9  |                             | Cursor OF F                | 5           | Character display         |

|                   |              | 0     | 1 /    |      |                             | Cursor ON                  |             |                           |

|                   |              | 1     | 0//    |      |                             | Cursor ØFF character blink | External    |                           |

|                   |              | 1     | /1/    |      |                             | Cursor blink               | Ä           |                           |

|                   |              | 0     | 0      | 1    | 0                           |                            | $\times$    | Graphic mode              |

| Display<br>ON/OFF | Master/slave | Blink | Cursor | Mode | External/<br>built-in<br>CG |                            |             | <b>Y</b>                  |

1 : master mode 0 : slave mode

1/: display ON 0 : display OFF

### 2) Setting the character pitch

| Register                 | R/W | RS | DB7 | DB6  | DB5     | DB4 | DB3 | DB2 | DB1   | DB0    |

|--------------------------|-----|----|-----|------|---------|-----|-----|-----|-------|--------|

| Instruction register     | 0   | 1  | 0   | 0    | 0       | D   | 0   | 0   | 0     | 1      |

| Character pitch register | 0   | 0  |     | (Vp- | 1) Bina | ary | 0   | /4  | 4p-1) | Binary |

Vp is the number of vertical dots per character. Determine Vp with the pitch between two vertically placed characters taken into consideration. This value is meaningful only in the character display mode: It is invalid in the graphic mode.

In character mode, Hp indicates the number of horizontal dots per character, from the leftmost part of one character to the leftmost part of the next. In the graphic mode, Hp indicates how many bits (or dots) from RAM appear in a 1-byte display.

Hp must take one of the following three values.

| 200         | 62 121            | DB0 | DB1 | DB2 | HP |

|-------------|-------------------|-----|-----|-----|----|

| ter pitch 6 | Horizontal charac | 1   | 0   | 1   | 6  |

| 7           |                   | 0   | 1   | 1   | 7  |

| 8           | 4                 | 1   | 1   | 1   | 8  |

#### 3) Setting the number of characters

| Register                  | R/W | RS | DB7 | DB6 | DB5 | DB4  | DB3    | DB2 | DB1 | DB0 |

|---------------------------|-----|----|-----|-----|-----|------|--------|-----|-----|-----|

| Instruction register      | 0   | 1  | 0   | /6  | 0   | 0    | /0/    | 0   | 1   | 0   |

| Character number register | 0   | 0  |     |     |     | (Hy- | ) Bina | iry |     |     |

In the character display mode, H<sub>N</sub> indicates the number of characters in the horizontal direction. In the graphic mode, it indicates the number of bytes in the horizontal direction. The total number of dots positioned horizontally on the screen n is given by the formula

$n = Hp \times H_N$ .

Even numbers in the range 2 to 256 (decimal) can be set as HN.

#### 4) Setting the time division number (display duty)

| Register               | R/W | RS | DB7 | DB6 | DB5 | DB4  | DB3     | DB2 | DB1 | DB0 |

|------------------------|-----|----|-----|-----|-----|------|---------|-----|-----|-----|

| Instruction register   | 0   | 1  | 0 / | 0   | 0   | 0    | 0       | 0   | 1   | 1   |

| Time division register | o   | 0  |     |     |     | (Nx- | 1) Bina | iry |     |     |

Consequently, 1/Nx is the display duty.

Decimal numbers within the range 1 to 256 can be set as Nx.

### 5) Setting the cursor position

| Register                 | R/W | RS | DB7 | DB6 | DB5 | DB4 | DB3 | DB2  | DB1           | DB0 |  |  |

|--------------------------|-----|----|-----|-----|-----|-----|-----|------|---------------|-----|--|--|

| Instruction register     | //0 | 1  | 0   | 0   | 0   | 0   | 0   | 1    | 0             | 0   |  |  |

| Cursor position register | 0   | 0  | 0   | 0   | 0   | 0   |     | (CP- | (CP-1) Binary |     |  |  |

In the character display mode, Cp indicates the line at which the cursor is displayed. For example, when Cp=8 (decimal) is specified, the cursor is displayed beneath the character of the 5 x 7 dot-font. The horizontal length of the cursor equals Hp (the horizontal character pitch). Decimal values in the range 1 to 16 can be assigned to Cp. When the value is less than the vertical character pitch Vp (Cp  $\cong$  Vp), display priority is given to the cursor (provided the cursor display is ON). The cursor is not displayed when CP<Vp. The horizontal length of the cursor equals Hp.

#### 6) Setting the display start lower address

| Register                                       | R/W | RS | DB7 | DB6 | DB5      | DB4       | DB3      | DB2      | 081 | DB0 |

|------------------------------------------------|-----|----|-----|-----|----------|-----------|----------|----------|-----|-----|

| Instruction register                           | 0   | 1  | 0   | 0   | 0        | 0         | 1        | 0        | 0   | 0   |

| Display start address<br>register (lower byte) | 0   | 0  |     | 1   | (start a | ddress lo | wer byte | ) binary |     |     |

### 7) Setting the display start upper address

| Register                                       | R/W | RS | DB7 | DB6 | DB5      | DB4       | DB3      | DB2       | DB1 | DB0 |

|------------------------------------------------|-----|----|-----|-----|----------|-----------|----------|-----------|-----|-----|

| Instruction register                           | 0   | 1  | 0   | 0   | 0        | 0         | //1      | 0         | 0   | //1 |

| Display start address<br>register (upper byte) | 0   | 0  |     |     | (start a | address u | pper byt | e) binary | 1   |     |

This instruction writes the display start address value in the display start address register. The display start address is the RAM address at which data to be displayed at the leftmost position of the top line of the screen is stored. The start address consists of 16 bits (upper and lower).

#### 8) Setting the cursor (lower) address (RAM read/write lower address)

| Register                               | R/W | RS | DB7 | DBG | DBS     | DB4     | DB3      | DB2       | DB1 | DB0 |

|----------------------------------------|-----|----|-----|-----|---------|---------|----------|-----------|-----|-----|

| Instruction register                   | 0   | 1  | 0   | 0   | 0       | 0       | 1/1      | 0         | 1   | 0   |

| Cursor address counter<br>(lower byte) | 0   | 0  | 1   |     | (cursor | address | ower byt | e) binary | ,   |     |

#### 9) Setting the cursor (upper) address (RAM read/write upper address)

| Register                               | R/W | /RS  | DB7 DB6 | DB5     | DB4     | DB3      | DB2       | DB1 | DB0 |

|----------------------------------------|-----|------|---------|---------|---------|----------|-----------|-----|-----|

| Instruction register                   | 0 / | /1 4 | 8 0     | // 0    | 0       | 1        | 0         | 1   | 1   |

| Cursor address counter<br>(upper byte) | 9   | 0    |         | (cursor | address | upper by | te) binar | У   |     |

This instruction writes the cursor address value in the cursor address counter. The cursor address indicates the address for exchanging display data and character codes with RAM. In other words, data at the address specified by the cursor address is read from or written into RAM. In character display, the cursor is displayed at the position specified by the cursor address.

The cursor address is divided into a lower address (8 bits) and an upper address (8 bits). It should be set in accordance with the following rules.

| 1 | To rewrite (set) both lower and upper addresses: | First set the lower address, then the upper.                       |

|---|--------------------------------------------------|--------------------------------------------------------------------|

| 2 | To rewrite the lower address:                    | Always reset the upper address after setting the lower address.    |

| 3 | To rewrite the upper address only:               | Set the upper address. It is necessary to reset the lower address. |

The cursor address counter is a 16-bit up-counter with set/reset functions: when the Nth bit goes from 1 to 0, the count of the (N + 1)th bit increments by one. Accordingly, when the lower address is set so that the lower MSB (8th bit) changes from 1 to 0, the LSB (1st bit) of the upper counter must increment by one. When setting the cursor address, set the lower and upper addresses as a 2-byte continuous instruction.

### 10) Writing display data

| Regisiter            | R/W | RS | DB7 | DB6       | DB5       | DB4       | DB3 | DB2 | DB1 | DB0     |

|----------------------|-----|----|-----|-----------|-----------|-----------|-----|-----|-----|---------|

| Instruction register | 0   | 1  | 0   | 0         | 0         | 0         | 1   | 1   | 0   | 0       |

| RAM                  | 0   | 0  | MSB | pattern e | data, cha | racter co | de) |     | Ls  | .L<br>B |

Write code "OCH" in the instruction register. Then, write 8-bit data with RS=0, and the data is written into RAM as display data or character codes at the address specified by the cursor address counter. After writing, the count of the cursor address counter increments by 1.

### 11) Reading display data

| Register             | R/W | RS | DB7 | DB6     | DB5       | DB4       | DB3 | DB2 | DB1/ | DB0 |

|----------------------|-----|----|-----|---------|-----------|-----------|-----|-----|------|-----|

| Instruction register | 0   | 1  | 0   | 0       | 0         | 0         | 1   | a   | 0    | 1   |

| RAM                  | 1   | 0  | MSB | pattern | data, cha | racter co | de) |     | LSE  | 3   |

Write "ODH" in the instruction register. Then, establish the read status with RS=0, and data in the RAM can be read. The procedure for reading data is as follows:

This instruction outputs the contents of the data output register to DBO to 7, then transfers the RAM data indicated by the cursor address to the data output register. It then increments the cursor address by 1, which means that correct data cannot be read in the first read operation. The specified value is output in the second read operation. Accordingly, a dummy read operation must be performed once when reading data after setting the cursor address.

#### 12) Bit clear

| Register             | R/W | RS    | D87 | DB6 | DB5/ | DB4 | DB3 | DB2 | DB1   | DB0    |

|----------------------|-----|-------|-----|-----|------|-----|-----|-----|-------|--------|

| Instruction register | 0   | //i _ | 0   | 0   | //0  | 0   | 1   | 1   | 1     | 0      |

| Bit clear            | 0/  | 0     | 0   | 9// | 0    | 0   | 0   | (1  | NB-1) | Binary |

### 13) Bit set

| Register             | R/W | RS | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1   | DB0    |

|----------------------|-----|----|-----|-----|-----|-----|-----|-----|-------|--------|

| Instruction register | 0   | 1/ | 0   | 0   | 0   | 0   | 1   | 1   | 1     | 1      |

| Bit set              | 0   | 0  | 0   | 0   | 0   | 0   | 0   | (1  | VB-1) | Binary |

As the bit-clear or bit-set instruction, 1 bit of a 1 byte of data in display RAM is set to 0 or 1. The bit specified by NB is set to 0 for the bit-clear instruction and 1 for the bit-set instruction. The RAM address is specified by the cursor address, which is automatically incremented by 1 at the completion of the instruction. NB is a value in the range from 1 to 8. The LSB is indicated by NB=1, and the MSB by NB=8.

### 14) Reading the BUSY flag

|               | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|---------------|-----|-----|-----|-----|-----|-----|-----|-----|

| Busy flag 1 1 | 1/0 |     |     |     | *   |     |     |     |

The busy flag is output to DB7 when read mode is established with RS=1. The busy flag is set to 1 while any of the instructions 1) through 13) is being executed. It is set to 0 at the completion of the execution, allowing the next instruction to be accepted. No other instruction can be accepted when the busy flag is 1. Accordingly, before writing an instruction and data, it is necessary to ensure that the busy flag is 0. However, the next instruction can be executed without checking the busy flag when the maximum read cycle time or the write cycle time has been exceeded after execution of the previous data read instruction or the data write instruction.

The busy flag does not change when data is written into the instruction register (RS=1). Therefore, the busy flag need not be checked immediately after writing data into the instruction register.

Specification of the instruction register is unnecessary to read the busy flag.

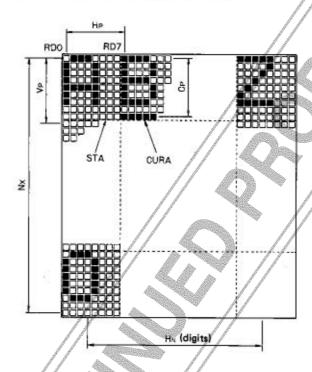

The relation between the LCD panel display and Hp, HN, Vp, Cp, and Nx.

| Symbol | Description //                                         | Contents                                                                                    | Value                             |  |  |

|--------|--------------------------------------------------------|---------------------------------------------------------------------------------------------|-----------------------------------|--|--|

| Нр _   | Horizontal character pitch                             | Character pitch in the horizontal direction                                                 | 6 to 8 dots                       |  |  |

| HN     | Number of characters<br>in the horizontal<br>direction | Number of characters (digits) per horizontal line or the number of words per line (graphic) | Even digits in the range 2 to 256 |  |  |

| Vp     | Vertical character<br>pitch                            | Character pitch in the vertical direction                                                   | 1 to 16 dots                      |  |  |

| Ср     | Cursor position                                        | The line number at which the cursor is to be displayed                                      | 1 to 16 lines                     |  |  |

| Nx     | Number of lines in the vertical direction              | Display duty                                                                                | 1 to 256 lines                    |  |  |

#### Note:

When the number of vertical dots on the screen is m and that of horizontal dots is n,

1/m = 1/Nx = display duty n = Hp x H<sub>N</sub> m/Vp = number of display lines Cp≤Vp

### Display mode

#### Sample application circuit (1)

- Specifications of any and all SANYO Semiconductor products described or contained herein stipulate the performance, characteristics, and functions of the described products in the independent state, and are not guarantees of the performance, characteristics, and functions of the described products as mounted in the customer's products or equipment. To verify symptoms and states that cannot be evaluated in an independent device, the customer should always evaluate and test devices mounted in the customer's products or equipment.

- SANYO Semiconductor Co., Ltd. strives to supply high-quality high-reliability products. However, any and all semiconductor products fail with some probability. It is possible that these probabilistic failures could give rise to accidents or events that could endanger human lives, that could give rise to smoke or fire, or that could cause damage to other property. When designing equipment, adopt safety measures so that these kinds of accidents or events cannot occur. Such measures include but are not limited to protective circuits and error prevention circuits for safe design, redundant design, and structural design.

- In the event that any or all SANYO Semiconductor products (including technical data,services) described or contained herein are controlled under any of applicable local export control laws and regulations, such products must not be exported without obtaining the export license from the authorities concerned in accordance with the above law.

- No part of this publication may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying and recording, or any information storage or retrieval system, or otherwise, without the prior written permission of SANYO Semiconductor Co., Ltd.

- Any and all information described or contained herein are subject to change without notice due to product/technology improvement, etc. When designing equipment, refer to the "Delivery Specification" for the SANYO Semiconductor product that you intend to use.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production. SANYO Semiconductor believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.

Sample application circuit (2) [Composition of graphic display and character display]

### Examples of configuration

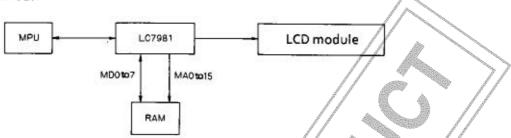

Graphic mode

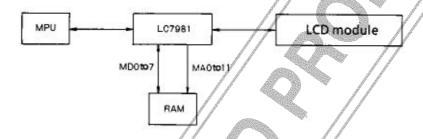

• Character display mode (1) (built-in character generator)

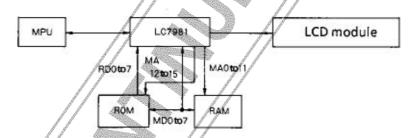

Character display mode (2) (external character generator)

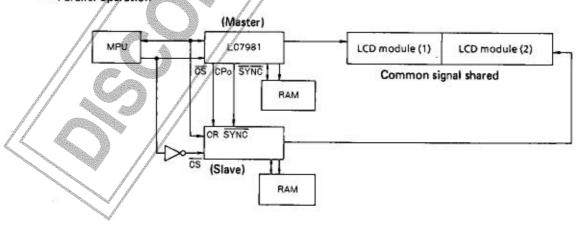

Parallel operation

### Built-in character generator

| Upper<br>Lower 4bit | 0010      | 0011 | 0100     | 0101       | 0110        | 0111           | 1010       | 1011        | 1100         | 1101     | 1170            | 1111 |

|---------------------|-----------|------|----------|------------|-------------|----------------|------------|-------------|--------------|----------|-----------------|------|

| 4bit<br>××××0000    |           | 9    | (ii)     | þ          | ••          | <b>#</b> :-    |            |             | -9           | <i> </i> |                 | R    |

| ××××0001            |           | 1    | A        |            | .::1        | ·:             | 131        | F           | #/           | 14       |                 |      |

| ××××0010            | !!        | 2    | <b>3</b> | R          | <u> </u> :: | <b> </b>       | ľ          |             | 411          |          |                 |      |

| ××××0011            | #         | 3    | <u> </u> | 5          | <u>;</u>    | <b>:::</b> .   |            | <b>A</b>    |              | 1        | 7               |      |

| ××××0100            | \$        | 4    | D        | Ţ          |             | 1,/            |            |             | 1.           | 17       |                 | Ω    |

| ××××0101            | <u>";</u> |      |          | <u> </u> _ |             | <b>/</b> i/.ii | ( <u>"</u> |             |              |          | 5               | Ü    |

| ××××0110            | 8:        | 6    | E        | i,j        | #           | 1,1            |            | 1           | / <u></u>    | =        | p               | Ξ    |

| ****0111            | "         | ï    |          |            |             |                | #          | #           | <u>;;;</u> ; |          | 9               | Л    |

| ****1000            | ı,        |      | 州        | <b>*</b>   |             |                |            | 7           | 7.           | ij       | .J <sup>r</sup> | X    |

| ××××1001            | )         |      |          | 4          | 1           | <b>%!</b>      | ****       | .j          | <u>,i</u>    | ĮĮ,      | ··i             | Ц    |

| ××××1010            | :4;/      | #    |          | <u>;</u>   |             |                | ::::       |             | 'n           | Ŀ        | j.              | #    |

| ××××1011            | 4-        |      | K        |            |             | 4              | 7          | 캦           | <u> </u>     |          | ×               | Fi   |

| ××××1 200           | •         |      |          | <b>#</b>   | 1           |                | †7         | <u>:</u> ,ı | Ţ            | ŋ        | ф.              | P    |

| ×4××1101            | -         |      |          |            | ľη          | }              | .1.        | 7,          | ^,           |          | ŧ               | ÷    |

| ××××110             | •/        |      | H        | •••        | 'n          | •••            | ∄          | 也           | <b>;</b> †;  | •••      | ľΪ              |      |

| ×××× JAJI           |           | ?    |          |            | <u>;;;</u>  | 4:             | ıij.       | 닛           | 7            | III      | Ö               |      |