# **DSP Builder Handbook**

# **Volume 3: DSP Builder Advanced Blockset**

101 Innovation Drive San Jose, CA 95134 www.altera.com

HB\_DSPB\_ADV-8.0

Feedback

© 2014 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

## **Contents**

## Section I. DSP Builder Advanced Blockset User Guide

| Chapter 1. About the DSP Builder Advanced Blockset        |     |

|-----------------------------------------------------------|-----|

| Features                                                  |     |

| Architecture versus Implementation                        |     |

| Libraries                                                 |     |

| Base Library                                              |     |

| FFT Library                                               |     |

| ModelBus Library                                          |     |

| ModelPrim Library                                         | 1–3 |

| ModelIP Libraries                                         | 1–3 |

| Cycle Accuracy and Latency                                |     |

| Sample Rate and Clocks                                    |     |

| Interoperability with the Standard Blockset               |     |

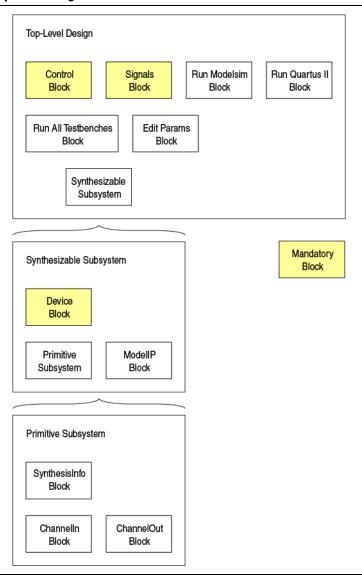

| Typical Design Blocks                                     |     |

| Signals Block                                             |     |

| Control Block                                             |     |

| Device Block                                              |     |

| SynthesisInfo Block                                       |     |

| Other Blocks                                              |     |

|                                                           |     |

| Chapter 2. Design Flow                                    |     |

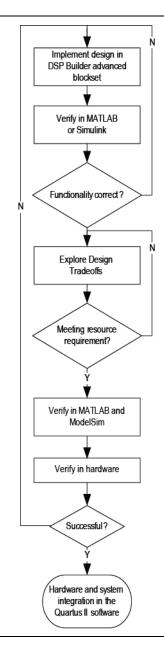

| Implementing your Design in DSP Builder Advanced Blockset |     |

| Staging your Design into Subsystems                       |     |

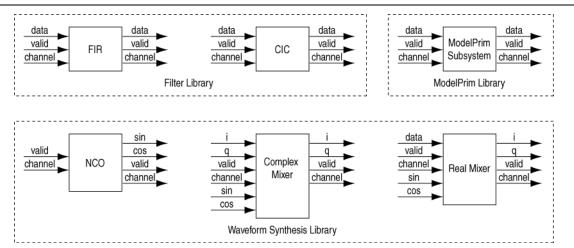

| ModelPrim Blocks                                          |     |

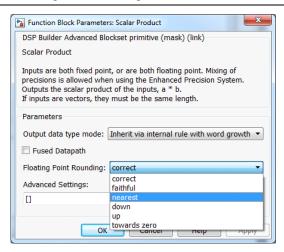

| Specifying the Output Data Type                           |     |

| SynthesisInfo Block                                       |     |

| Loops                                                     |     |

| Vectors                                                   |     |

| ModelPrim Blocks in NonModelPrim Subsystems               |     |

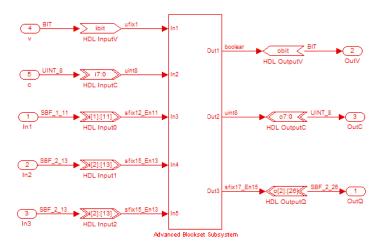

| Interfaces as Subsystem Boundaries                        |     |

| Interfaces as Scheduling Boundaries                       |     |

| Block Interfaces                                          |     |

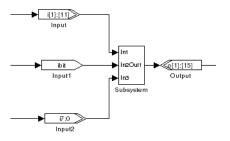

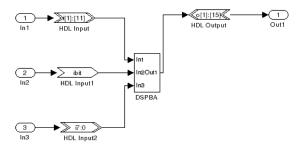

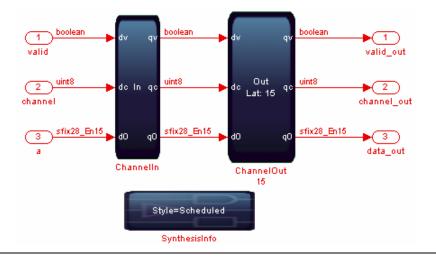

| Interface Example                                         |     |

| Connecting Subsystems                                     |     |

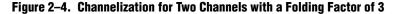

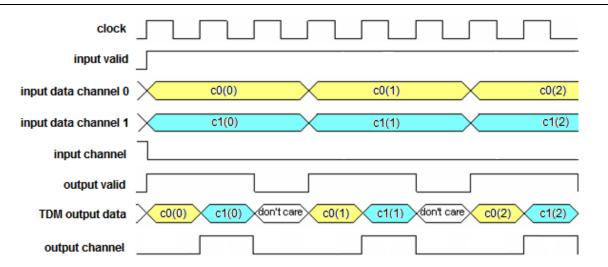

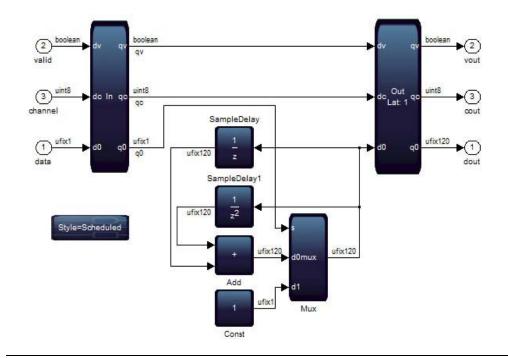

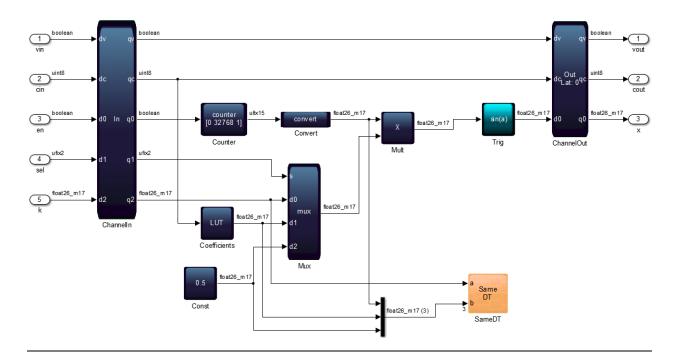

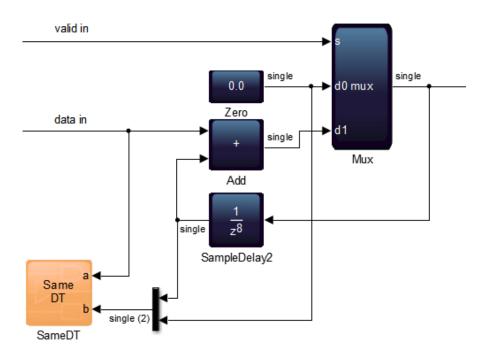

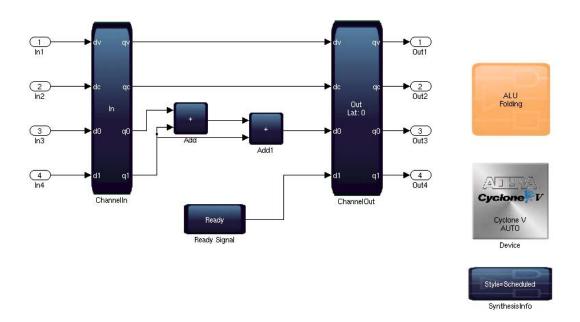

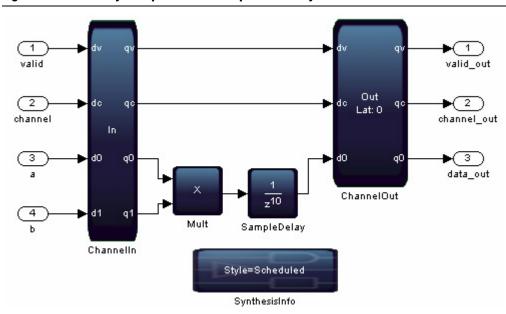

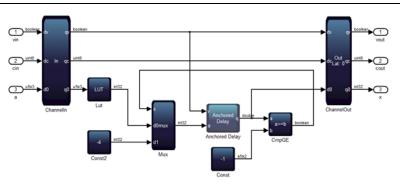

| Building Multichannel Systems                             |     |

| Multichannel Systems                                      |     |

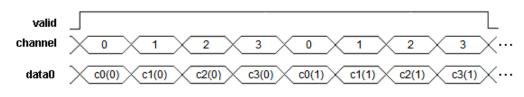

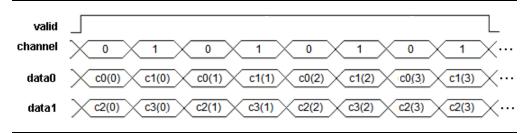

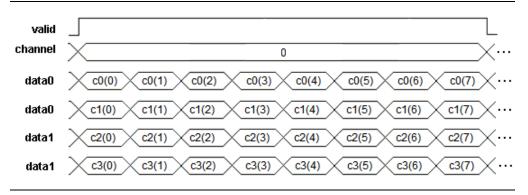

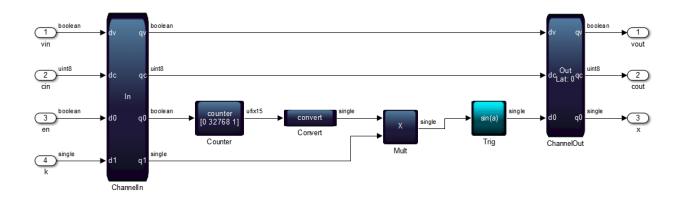

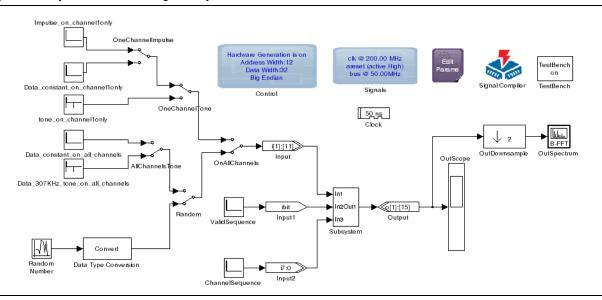

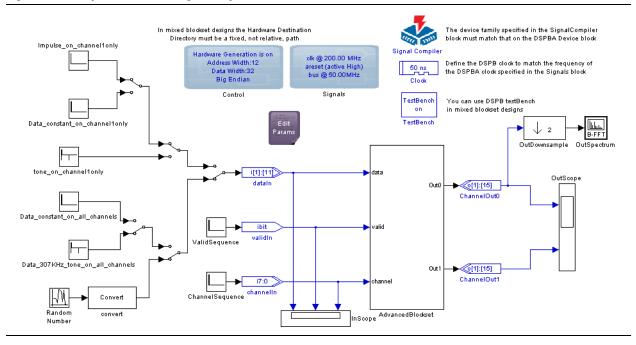

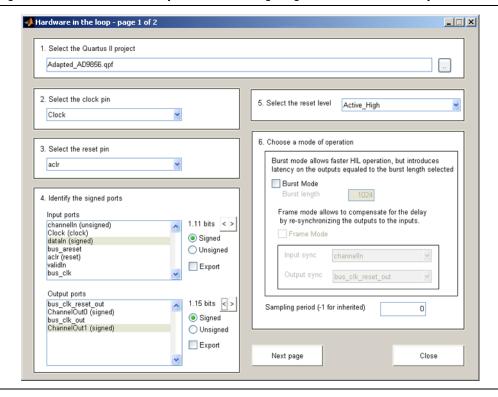

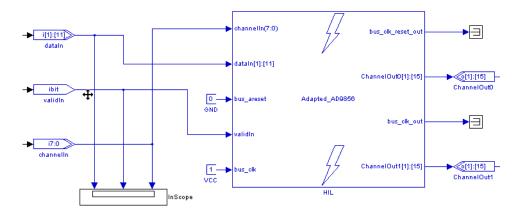

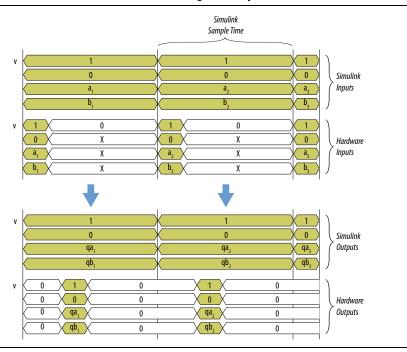

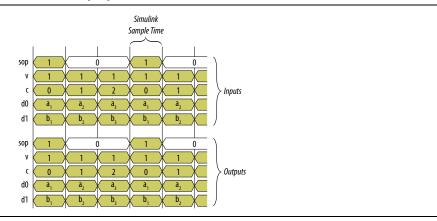

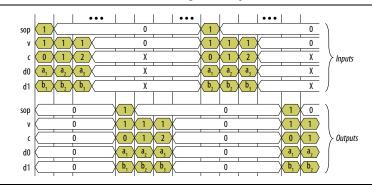

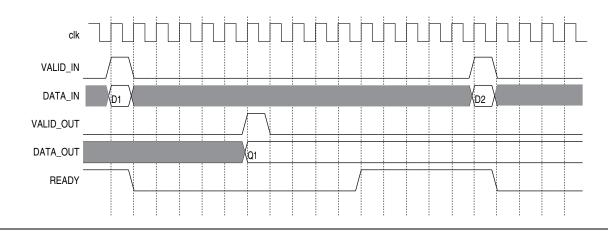

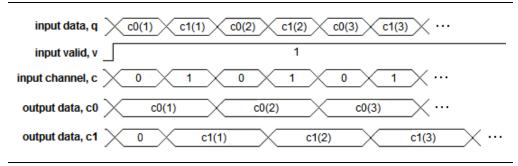

| Channel, Data, and Valid Examples                         |     |

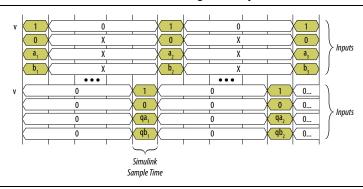

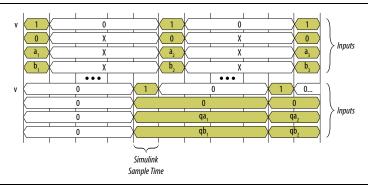

| Vectorized Inputs                                         |     |

| Verifying your Design in Simulink and MATLAB              |     |

| Testbenches                                               |     |

| Using References                                          |     |

| Setting Up Stimulus                                       |     |

| Analyzing your Design                                     |     |

| Exploring Design Tradeoffs                                |     |

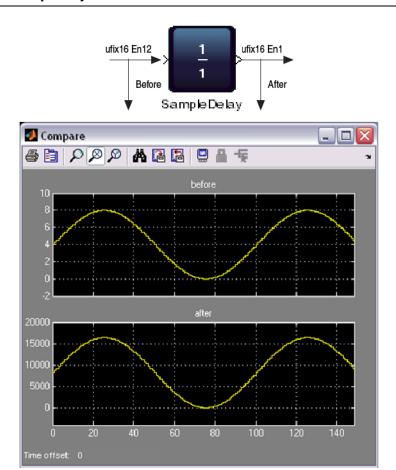

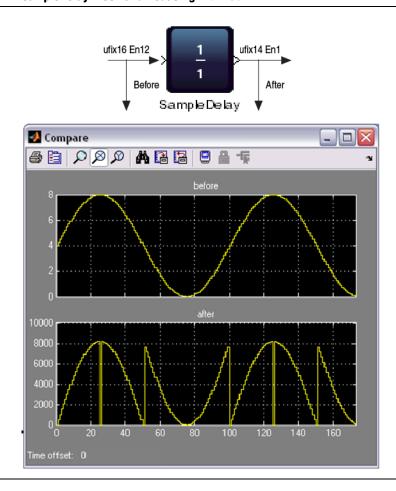

| Bit Growth                                                |     |

| Managing Bit Growth                                       |     |

| Using Rounding and Saturation                             |     |

iv Contents

| Scaling using ModelPrim Blocks                                                  | 2–21 |

|---------------------------------------------------------------------------------|------|

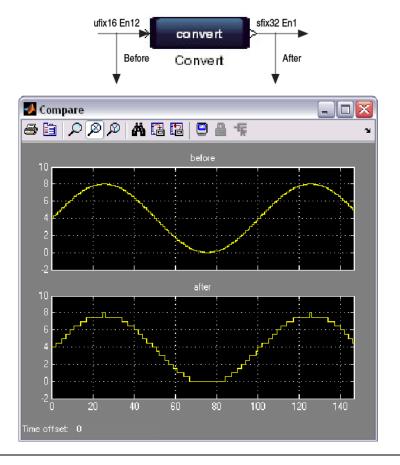

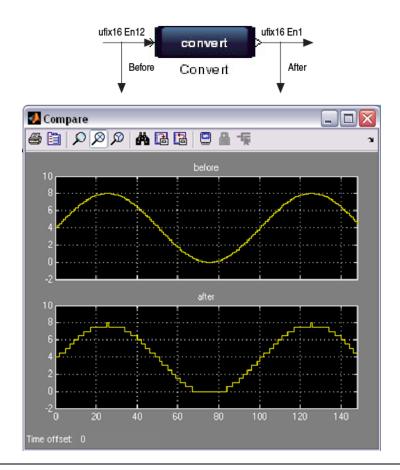

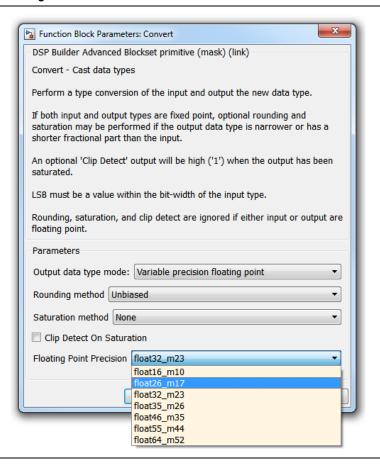

| Using Convert Blocks and Specifying Output Types                                | 2–22 |

| The Convert Block and Real-world Values                                         | 2–23 |

| Output Data Types on ModelPrim Blocks                                           | 2–24 |

| Verifying your Design and Debugging                                             | 2-26 |

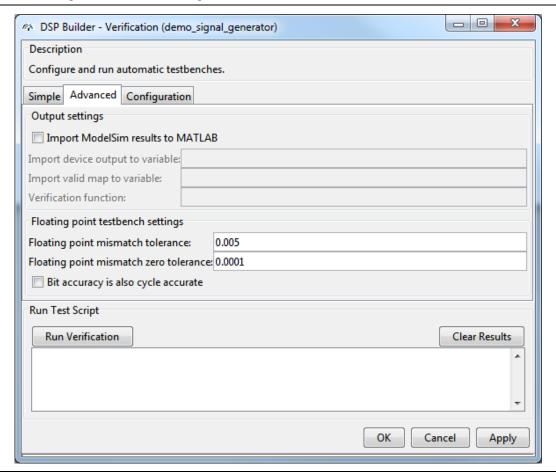

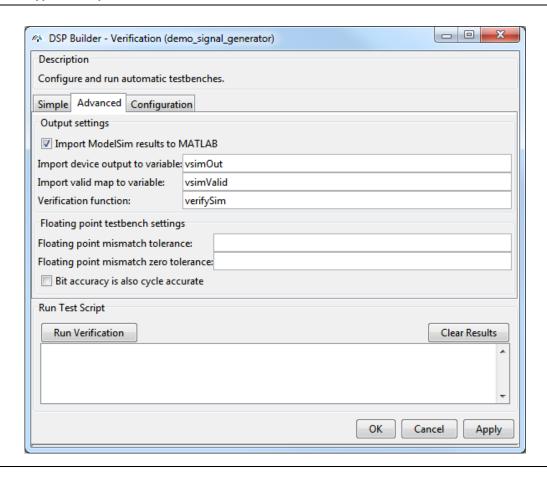

| Automatic Testbench                                                             |      |

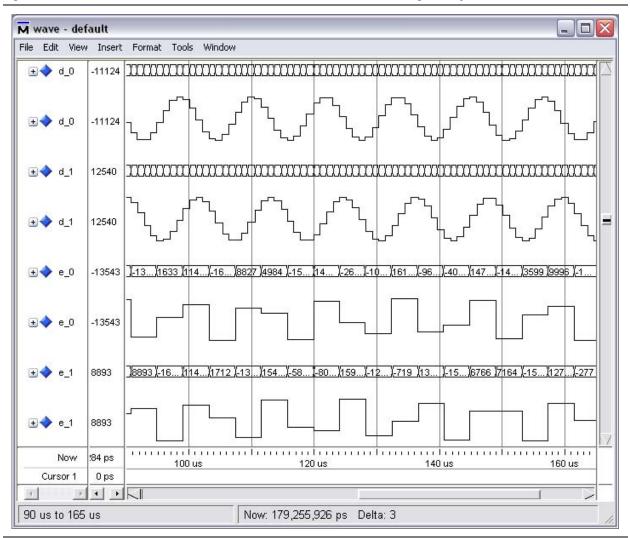

| ModelSim Simulations                                                            | 2–27 |

| Integrating into Hardware                                                       |      |

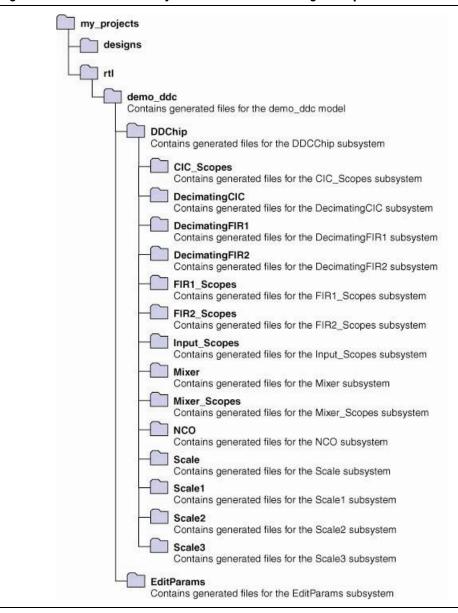

| Directory Structure                                                             |      |

| Generated Files                                                                 |      |

| Automatic Testbench Files                                                       |      |

| DSP Builder Designs and the Quartus II Project                                  |      |

| Adding a DSP Builder Advanced Blockset Design to an Existing Quartus II Project |      |

| Adding Advanced Blockset Components to Qsys                                     |      |

| Guidelines                                                                      |      |

| Essential Guidelines for the Top-Level Design                                   | 2–31 |

| Essential Guidelines for the ModelPrim Blocks                                   |      |

| Simulink Setup Guidelines                                                       | 2–31 |

| Recommended Guidelines for the Top-Level Design                                 |      |

| Recommended Guidelines for ModelPrim Subsystems                                 |      |

| Guidelines for Verifying a Design                                               | 2–33 |

| Obanton 2 Catting Stantad                                                       |      |

| Chapter 3. Getting Started                                                      | 0.1  |

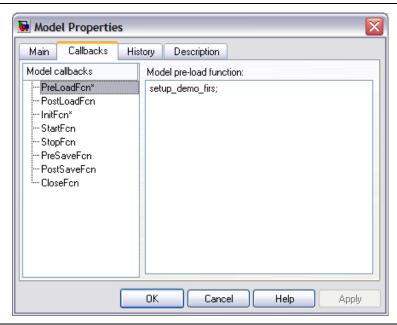

| Setting Up Simulink                                                             | 3–1  |

| Design Examples and Reference Designs                                           | 3-1  |

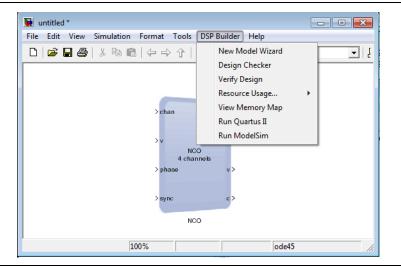

| Using the DSP Builder Menu in Simulink                                          | 2.2  |

| Running Automatic Testbenches                                                   | 2.4  |

| The dspba.runModelsimATB Command Syntax                                         |      |

| Running All Automatic Testbenches                                               |      |

| Testbench Error Messages                                                        |      |

| restbench Error Wessages                                                        | 3–3  |

| Chapter 4. ModelIP Tutorial                                                     |      |

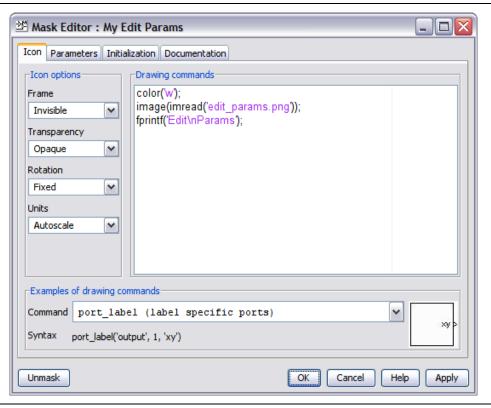

| Creating a ModelIP Design                                                       | 4–1  |

| Simulating the Design                                                           |      |

| Verifying the Design                                                            |      |

| Compiling the Design                                                            |      |

| Reparameterizing the FIR Filter                                                 |      |

| Doubling the Target Clock Rate                                                  |      |

| Retargeting Design to Different Device Family                                   |      |

|                                                                                 |      |

| Chapter 5. ModelPrim Tutorial                                                   |      |

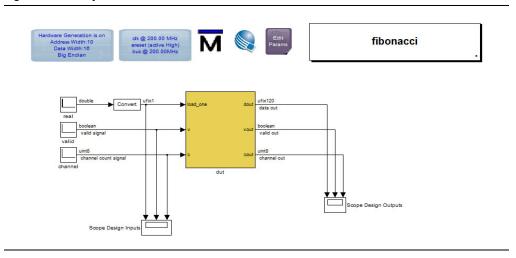

| The Fibonacci Sequence                                                          | 5–1  |

| Creating the Fibonacci Model                                                    |      |

| Creating a New Model                                                            |      |

| Creating a ModelIP Design                                                       |      |

| Adding Blocks from the ModelPrim Library                                        |      |

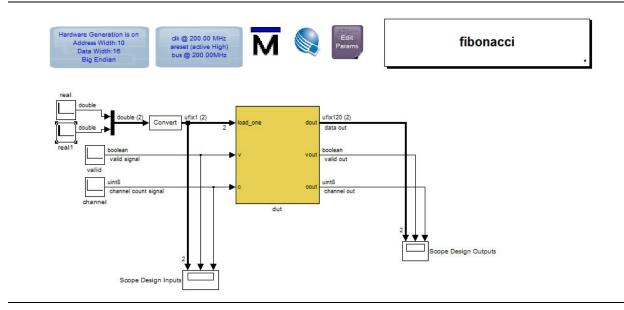

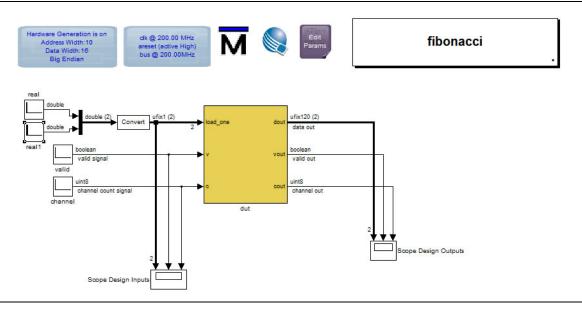

| Completing the Top-Level Model                                                  |      |

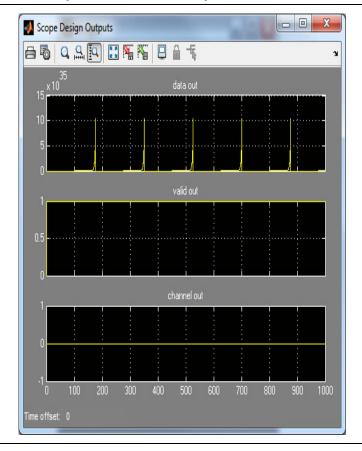

| Simulating the Design in Simulink                                               |      |

| Using Vector Types                                                              |      |

| Exploring the Generated Files                                                   |      |

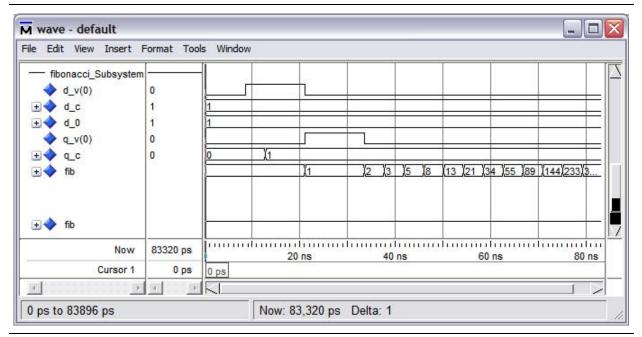

| Simulating the RTL                                                              | 5–7  |

| Compiling with the Quartus II Software                                          | 5–7  |

| Chapter 6. Design Examples and Reference Designs                |      |

|-----------------------------------------------------------------|------|

| Opening a Design Example                                        | 6–1  |

| Copying a Design Example                                        | 6–2  |

| Running a Design Example                                        | 6–2  |

| Base Blocks                                                     | 6–3  |

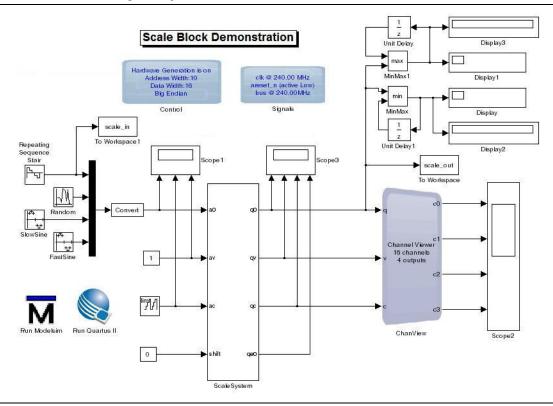

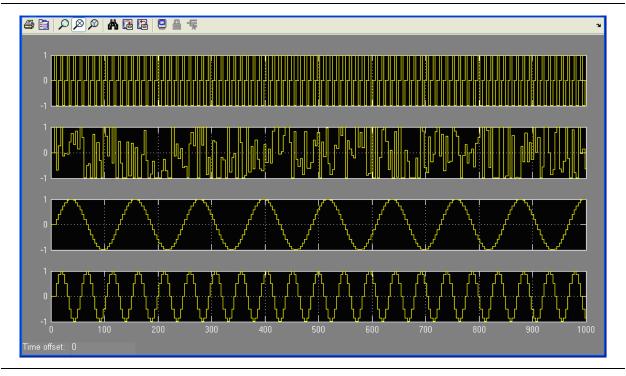

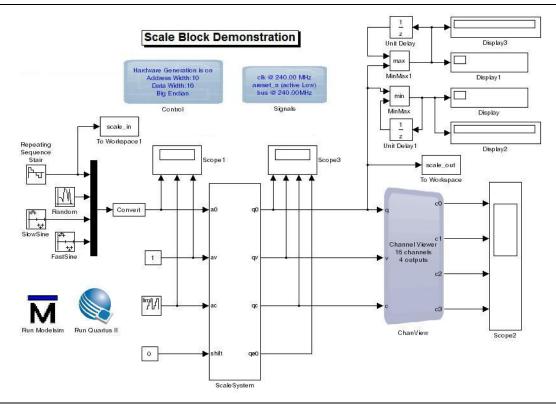

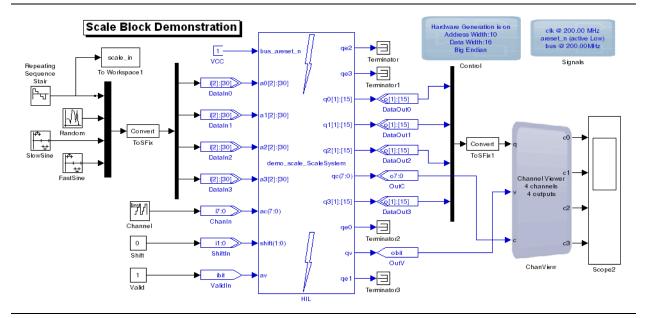

| Scale                                                           | 6–3  |

| Local Threshold                                                 |      |

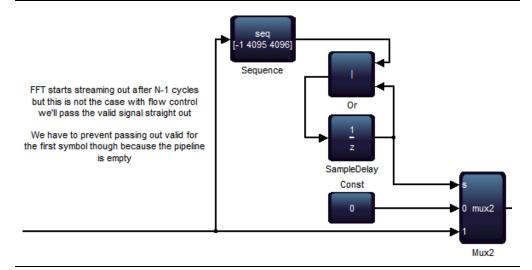

| FFT                                                             |      |

| 1K Floating-Point FFT                                           |      |

| FFT                                                             |      |

| FFT without BitReverseCoreC Block                               |      |

| IFFT                                                            |      |

| IFFT without BitReverseCoreC Block                              |      |

| Floating-Point FFT                                              |      |

| Floating-Point FFT without BitReverseCoreC Block                |      |

| Floating-Point iFFT                                             | 6–7  |

| Floating-Point iFFT without BitReverseCoreC Block               |      |

| Multichannel FFT                                                |      |

| Multiwire Transpose                                             |      |

| Parallel FFT                                                    |      |

| Parallel Floating-Point FFT                                     |      |

| Radix 2 Streaming FFT                                           |      |

| Radix 4 Streaming FFT                                           |      |

| Single-Wire Transpose                                           |      |

| Variable-Size Fixed-Point FFT                                   |      |

| Variable-Size Fixed-Point FFT without BitReverseCoreC Block     |      |

| Variable-Size Fixed-Point iFFT                                  |      |

| Variable-Size Fixed-Point iFFT without BitReverseCoreC Block    |      |

| Variable-Size Floating-Point FFT                                |      |

| Variable-Size Floating-Point FFT without BitReverseCoreC Block  | 6_9  |

| Variable-Size Floating-Point iFFT                               |      |

| Variable-Size Floating-Point iFFT without BitReverseCoreC Block | 6–10 |

| Variable-Size Low-Resource FFT                                  |      |

| Variable-Size Low-Resource Real-Time FFT                        |      |

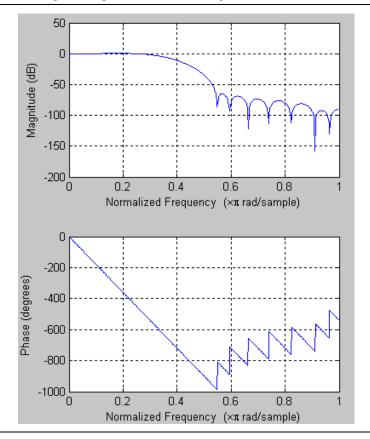

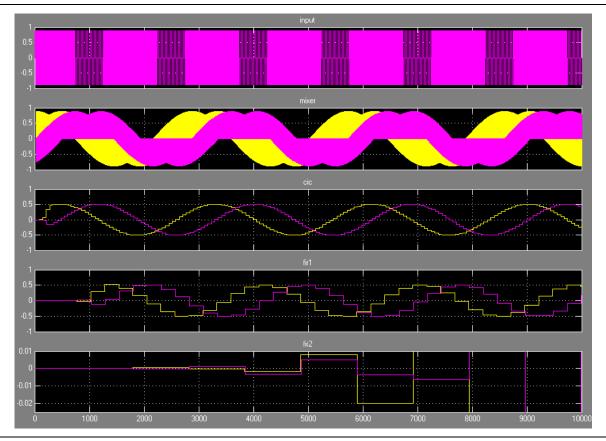

| Filters                                                         |      |

| Complex FIR Filter                                              |      |

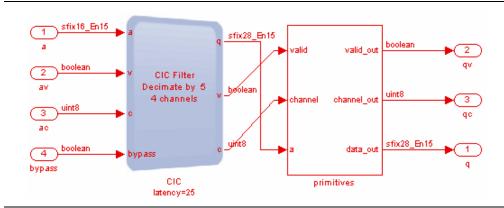

| Decimating CIC Filter                                           |      |

| Decimating FIR Filter                                           |      |

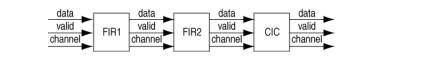

| Filter Chain with Forward Flow Control                          | 6–12 |

| FIR Filter with Exposed Bus                                     |      |

| Fractional FIR Filter Chain                                     | 6–12 |

| Fractional-Rate FIR Filter                                      | 6–13 |

| Half-Band FIR Filter                                            | 6–13 |

| Interpolating CIC Filter                                        |      |

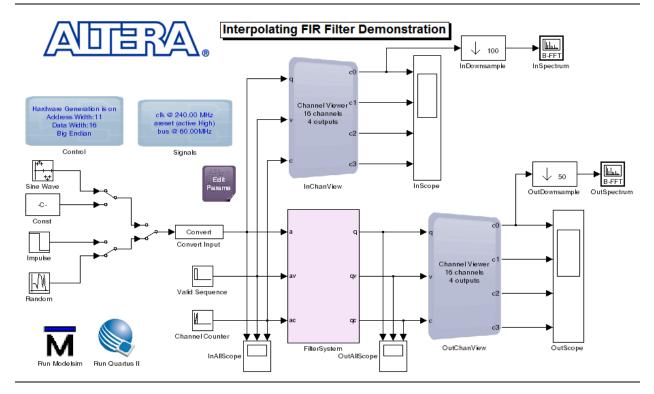

| Interpolating FIR Filter                                        |      |

| Interpolating FIR Filter with Multiple Coefficient Banks        |      |

| Interpolating FIR Filter with Updating Coefficient Banks        |      |

| Root-Raised Cosine FIR Filter                                   |      |

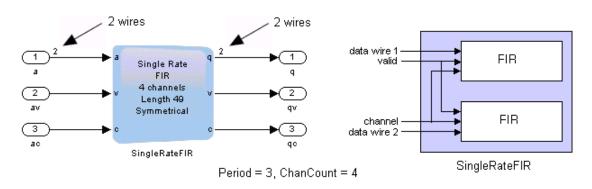

| Single-Rate FIR Filter                                          |      |

| Super-Sample Decimating FIR Filter                              |      |

| Super-Sample Fractional FIR Filter                              |      |

| Super-Sample Interpolating FIR Filter                           |      |

| Variable-Rate CIC Filter                                        | 6–17 |

vi Contents

| Folding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 6_17                                                                                                                                                 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

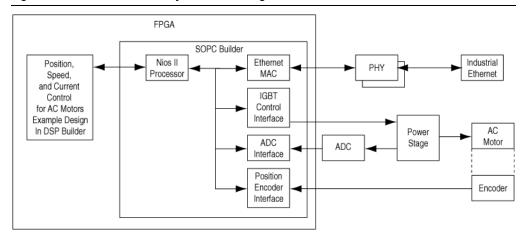

| Position, Speed, and Current Control for AC Motors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                      |

| About FOC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                      |

| Functional Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                      |

| Resource Usage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                      |

| Hardware Generation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                      |

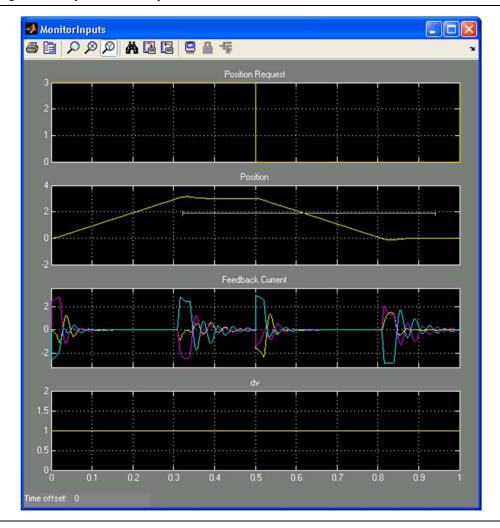

| Input Position Request                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                      |

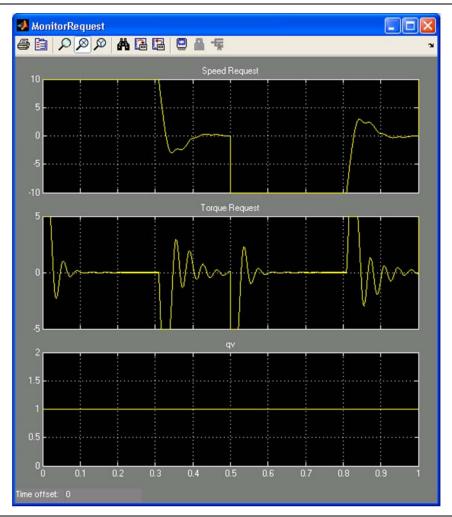

| Output Response for Speed and Torque                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                      |

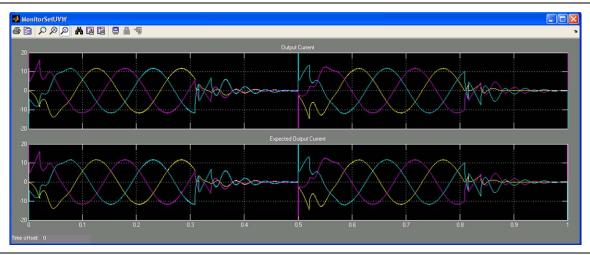

| Output Current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 6–22                                                                                                                                                 |

| Position, Speed, and Current Control for AC Motors (with ALU Folding)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                      |

| Folded FIR Filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 6–23                                                                                                                                                 |

| Floating Point                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 6–23                                                                                                                                                 |

| Black-Scholes Floating Point                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                      |

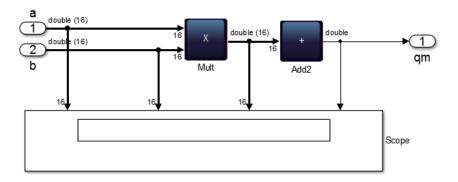

| Double-Precision Real Floating-Point Matrix Multiply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                      |

| Fine Doppler Estimator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                      |

| Floating-Point Mandlebrot Set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                      |

| General Real Matrix Multiply One Cycle Per Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                      |

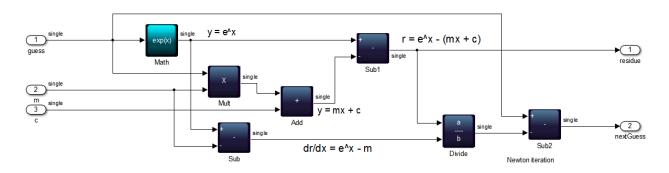

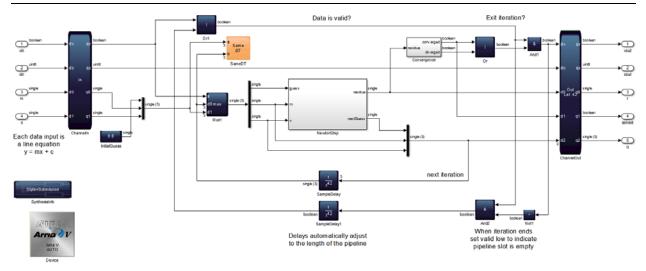

| Newton Root Finding Tutorial Step 1—Iteration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                      |

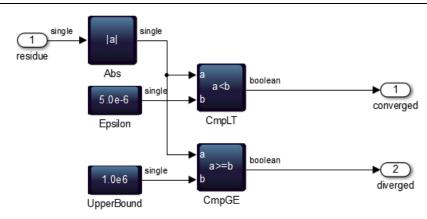

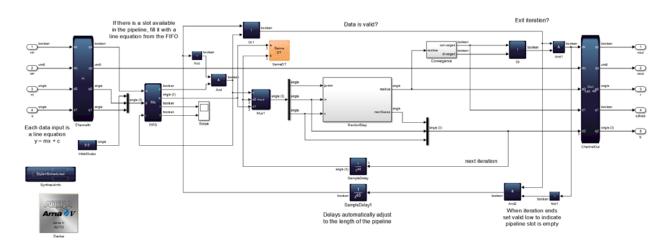

| Newton Root Finding Tutorial Step 2—Convergence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 6–27                                                                                                                                                 |

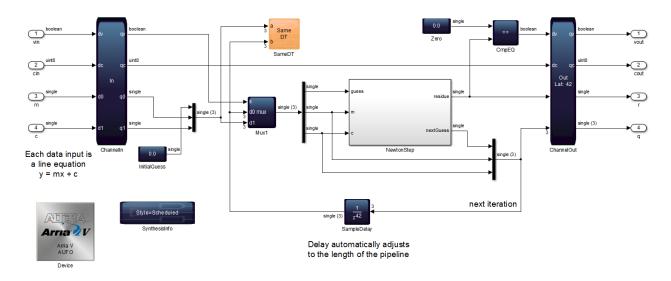

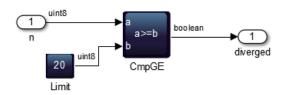

| Newton Root Finding Tutorial Step 3—Valid                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                      |

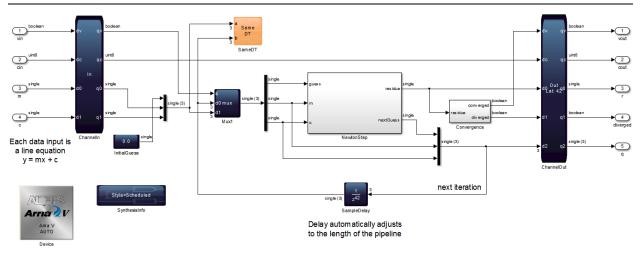

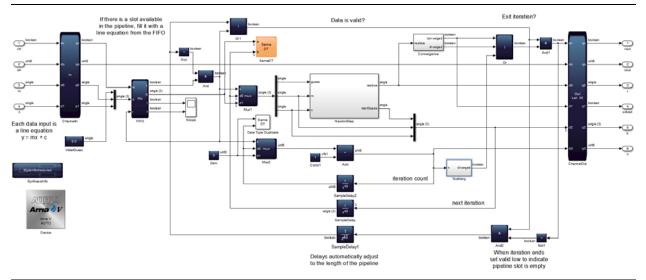

| Newton Root Finding Tutorial Step 4—Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 6–27                                                                                                                                                 |

| Newton Root Finding Tutorial Step 5—Final                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 6–28                                                                                                                                                 |

| Normalizer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 6–28                                                                                                                                                 |

| Single-Precision Complex Floating-Point Matrix Multiply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 6–28                                                                                                                                                 |

| Single-Precision Real Floating-Point Matrix Multiply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 6–29                                                                                                                                                 |

| Simple Nonadaptive 2D Beamformer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 6–29                                                                                                                                                 |

| Flow Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 6–30                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                      |

| Avalon-ST Interface (Input and Output FIFO Buffer) with Backpressure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 6–30                                                                                                                                                 |

| Avalon-ST Interface (Input and Output FIFO Buffer) with Backpressure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 6–30<br>6–30                                                                                                                                         |

| Avalon-ST Interface (Input and Output FIFO Buffer) with Backpressure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 6–30<br>6–30                                                                                                                                         |

| Avalon-ST Interface (Input and Output FIFO Buffer) with Backpressure  Avalon-ST Interface (Output FIFO Buffer) with Backpressure  Kronecker Tensor Product  Parallel Loops                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 6-30<br>6-30<br>6-31                                                                                                                                 |

| Avalon-ST Interface (Input and Output FIFO Buffer) with Backpressure Avalon-ST Interface (Output FIFO Buffer) with Backpressure Kronecker Tensor Product Parallel Loops Primitive FIR with Back Pressure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 6–30<br>6–30<br>6–30<br>6–31                                                                                                                         |

| Avalon-ST Interface (Input and Output FIFO Buffer) with Backpressure Avalon-ST Interface (Output FIFO Buffer) with Backpressure Kronecker Tensor Product Parallel Loops Primitive FIR with Back Pressure Primitive FIR with Forward Pressure                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 6-30<br>6-30<br>6-31<br>6-31<br>6-32                                                                                                                 |

| Avalon-ST Interface (Input and Output FIFO Buffer) with Backpressure Avalon-ST Interface (Output FIFO Buffer) with Backpressure Kronecker Tensor Product Parallel Loops Primitive FIR with Back Pressure Primitive FIR with Forward Pressure Primitive Systolic FIR with Forward Flow Control                                                                                                                                                                                                                                                                                                                                                                                                                             | 6–30<br>6–30<br>6–31<br>6–31<br>6–32<br>6–33                                                                                                         |

| Avalon-ST Interface (Input and Output FIFO Buffer) with Backpressure Avalon-ST Interface (Output FIFO Buffer) with Backpressure Kronecker Tensor Product Parallel Loops Primitive FIR with Back Pressure Primitive FIR with Forward Pressure Primitive Systolic FIR with Forward Flow Control Rectangular Nested Loop                                                                                                                                                                                                                                                                                                                                                                                                     | 6–30<br>6–30<br>6–31<br>6–31<br>6–32<br>6–33                                                                                                         |

| Avalon-ST Interface (Input and Output FIFO Buffer) with Backpressure Avalon-ST Interface (Output FIFO Buffer) with Backpressure Kronecker Tensor Product Parallel Loops Primitive FIR with Back Pressure Primitive FIR with Forward Pressure Primitive Systolic FIR with Forward Flow Control Rectangular Nested Loop Sequential Loops                                                                                                                                                                                                                                                                                                                                                                                    | 6–30<br>6–30<br>6–31<br>6–31<br>6–32<br>6–33<br>6–33                                                                                                 |

| Avalon-ST Interface (Input and Output FIFO Buffer) with Backpressure Avalon-ST Interface (Output FIFO Buffer) with Backpressure Kronecker Tensor Product Parallel Loops Primitive FIR with Back Pressure Primitive FIR with Forward Pressure Primitive Systolic FIR with Forward Flow Control Rectangular Nested Loop Sequential Loops Triangular Nested Loop                                                                                                                                                                                                                                                                                                                                                             | 6-30<br>6-30<br>6-31<br>6-31<br>6-32<br>6-33<br>6-34<br>6-34                                                                                         |

| Avalon-ST Interface (Input and Output FIFO Buffer) with Backpressure Avalon-ST Interface (Output FIFO Buffer) with Backpressure Kronecker Tensor Product Parallel Loops Primitive FIR with Back Pressure Primitive FIR with Forward Pressure Primitive Systolic FIR with Forward Flow Control Rectangular Nested Loop Sequential Loops Triangular Nested Loop Host Interface                                                                                                                                                                                                                                                                                                                                              | 6–30<br>6–30<br>6–31<br>6–31<br>6–33<br>6–33<br>6–34<br>6–34                                                                                         |

| Avalon-ST Interface (Input and Output FIFO Buffer) with Backpressure Avalon-ST Interface (Output FIFO Buffer) with Backpressure Kronecker Tensor Product Parallel Loops Primitive FIR with Back Pressure Primitive FIR with Forward Pressure Primitive Systolic FIR with Forward Flow Control Rectangular Nested Loop Sequential Loops Triangular Nested Loop Host Interface Memory-Mapped Registers                                                                                                                                                                                                                                                                                                                      | 6–30<br>6–30<br>6–31<br>6–31<br>6–32<br>6–33<br>6–34<br>6–34<br>6–34                                                                                 |

| Avalon-ST Interface (Input and Output FIFO Buffer) with Backpressure Avalon-ST Interface (Output FIFO Buffer) with Backpressure Kronecker Tensor Product Parallel Loops Primitive FIR with Back Pressure Primitive FIR with Forward Pressure Primitive Systolic FIR with Forward Flow Control Rectangular Nested Loop Sequential Loops Triangular Nested Loop Host Interface Memory-Mapped Registers Platforms                                                                                                                                                                                                                                                                                                            | 6–30<br>6–30<br>6–31<br>6–31<br>6–32<br>6–33<br>6–34<br>6–34<br>6–34<br>6–34                                                                         |

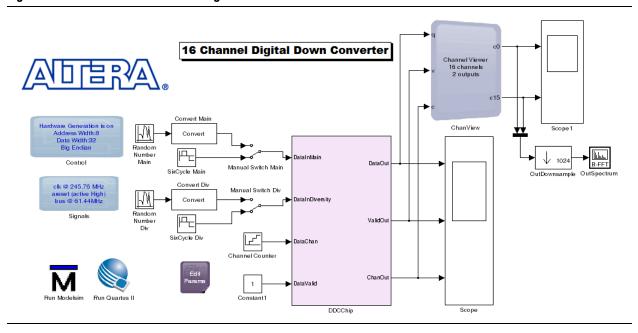

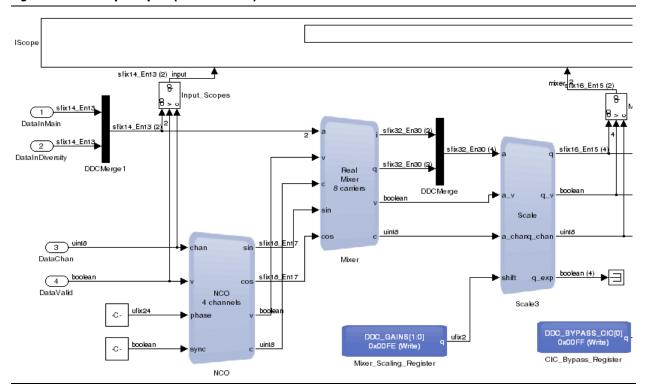

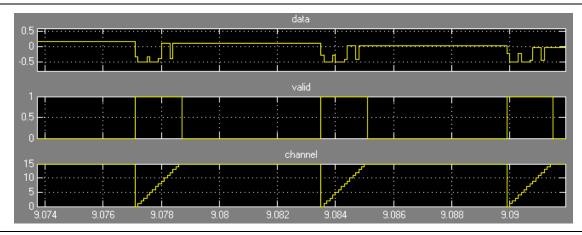

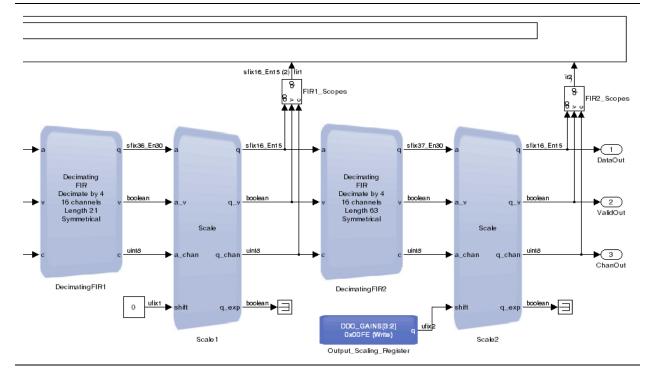

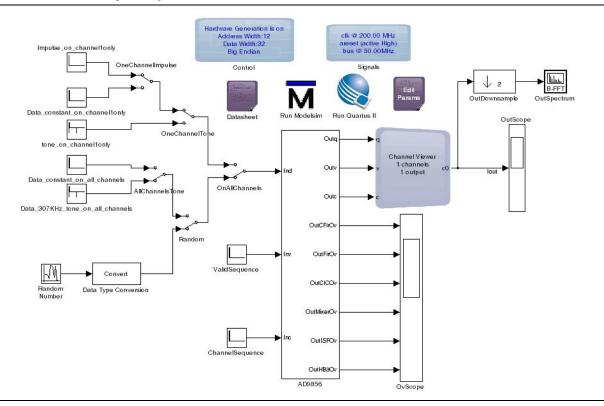

| Avalon-ST Interface (Input and Output FIFO Buffer) with Backpressure Avalon-ST Interface (Output FIFO Buffer) with Backpressure Kronecker Tensor Product Parallel Loops Primitive FIR with Back Pressure Primitive FIR with Forward Pressure Primitive Systolic FIR with Forward Flow Control Rectangular Nested Loop Sequential Loops Triangular Nested Loop Host Interface Memory-Mapped Registers Platforms 16-Channel DDC                                                                                                                                                                                                                                                                                             | 6-30<br>6-30<br>6-31<br>6-31<br>6-32<br>6-33<br>6-34<br>6-34<br>6-34<br>6-35<br>6-35                                                                 |

| Avalon-ST Interface (Input and Output FIFO Buffer) with Backpressure Avalon-ST Interface (Output FIFO Buffer) with Backpressure Kronecker Tensor Product Parallel Loops Primitive FIR with Back Pressure Primitive FIR with Forward Pressure Primitive Systolic FIR with Forward Flow Control Rectangular Nested Loop Sequential Loops Triangular Nested Loop Host Interface Memory-Mapped Registers Platforms 16-Channel DDC 16-Channel DUC                                                                                                                                                                                                                                                                              | 6-30<br>6-30<br>6-31<br>6-31<br>6-32<br>6-33<br>6-34<br>6-34<br>6-34<br>6-35<br>6-35                                                                 |

| Avalon-ST Interface (Input and Output FIFO Buffer) with Backpressure Avalon-ST Interface (Output FIFO Buffer) with Backpressure Kronecker Tensor Product Parallel Loops Primitive FIR with Back Pressure Primitive FIR with Forward Pressure Primitive Systolic FIR with Forward Flow Control Rectangular Nested Loop Sequential Loops Triangular Nested Loop Host Interface Memory-Mapped Registers Platforms 16-Channel DDC 16-Channel DUC 2-Antenna DUC for WiMAX                                                                                                                                                                                                                                                      | 6-30<br>6-30<br>6-31<br>6-31<br>6-33<br>6-33<br>6-34<br>6-34<br>6-34<br>6-35<br>6-35<br>6-35                                                         |

| Avalon-ST Interface (Input and Output FIFO Buffer) with Backpressure Avalon-ST Interface (Output FIFO Buffer) with Backpressure Kronecker Tensor Product Parallel Loops Primitive FIR with Back Pressure Primitive FIR with Forward Pressure Primitive Systolic FIR with Forward Flow Control Rectangular Nested Loop Sequential Loops Triangular Nested Loop Host Interface Memory-Mapped Registers Platforms 16-Channel DDC 16-Channel DUC 2-Antenna DUC for WiMAX 2-Channel DUC                                                                                                                                                                                                                                        | 6-30<br>6-30<br>6-31<br>6-31<br>6-33<br>6-33<br>6-34<br>6-34<br>6-34<br>6-35<br>6-35<br>6-35<br>6-36                                                 |

| Avalon-ST Interface (Input and Output FIFO Buffer) with Backpressure Avalon-ST Interface (Output FIFO Buffer) with Backpressure Kronecker Tensor Product Parallel Loops Primitive FIR with Back Pressure Primitive FIR with Forward Pressure Primitive Systolic FIR with Forward Flow Control Rectangular Nested Loop Sequential Loops Triangular Nested Loop Host Interface Memory-Mapped Registers Platforms 16-Channel DDC 16-Channel DUC 2-Antenna DUC for WiMAX 2-Channel DUC Super-Sample Rate Digital Upconverter                                                                                                                                                                                                  | 6-30<br>6-30<br>6-31<br>6-31<br>6-33<br>6-33<br>6-34<br>6-34<br>6-34<br>6-35<br>6-35<br>6-35<br>6-36<br>6-36                                         |

| Avalon-ST Interface (Input and Output FIFO Buffer) with Backpressure Avalon-ST Interface (Output FIFO Buffer) with Backpressure Kronecker Tensor Product Parallel Loops Primitive FIR with Back Pressure Primitive FIR with Forward Pressure Primitive Systolic FIR with Forward Flow Control Rectangular Nested Loop Sequential Loops Triangular Nested Loop Host Interface Memory-Mapped Registers Platforms 16-Channel DDC 16-Channel DUC 2-Antenna DUC for WiMAX 2-Channel DUC Super-Sample Rate Digital Upconverter Primitive Blocks                                                                                                                                                                                 | 6-30<br>6-30<br>6-31<br>6-31<br>6-32<br>6-33<br>6-34<br>6-34<br>6-34<br>6-35<br>6-35<br>6-35<br>6-36<br>6-36<br>6-37                                 |

| Avalon-ST Interface (Input and Output FIFO Buffer) with Backpressure Avalon-ST Interface (Output FIFO Buffer) with Backpressure Kronecker Tensor Product Parallel Loops Primitive FIR with Back Pressure Primitive FIR with Forward Pressure Primitive Systolic FIR with Forward Flow Control Rectangular Nested Loop Sequential Loops Triangular Nested Loop Host Interface Memory-Mapped Registers Platforms  16-Channel DDC 16-Channel DUC 2-Antenna DUC for WiMAX 2-Channel DUC Super-Sample Rate Digital Upconverter Primitive Blocks 8×8 Inverse Discrete Cosine Transform                                                                                                                                          | 6-30<br>6-30<br>6-31<br>6-31<br>6-33<br>6-33<br>6-34<br>6-34<br>6-34<br>6-35<br>6-35<br>6-35<br>6-36<br>6-37<br>6-37                                 |

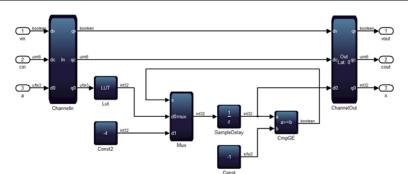

| Avalon-ST Interface (Input and Output FIFO Buffer) with Backpressure Avalon-ST Interface (Output FIFO Buffer) with Backpressure Kronecker Tensor Product Parallel Loops Primitive FIR with Back Pressure Primitive FIR with Forward Pressure Primitive Systolic FIR with Forward Flow Control Rectangular Nested Loop Sequential Loops Triangular Nested Loop Host Interface Memory-Mapped Registers Platforms 16-Channel DDC 16-Channel DUC 2-Antenna DUC for WiMAX 2-Channel DUC Super-Sample Rate Digital Upconverter Primitive Blocks 8×8 Inverse Discrete Cosine Transform Automatic Gain Control                                                                                                                    | 6-30<br>6-30<br>6-31<br>6-31<br>6-33<br>6-33<br>6-34<br>6-34<br>6-34<br>6-35<br>6-35<br>6-35<br>6-36<br>6-36<br>6-37<br>6-37                         |

| Avalon-ST Interface (Input and Output FIFO Buffer) with Backpressure Avalon-ST Interface (Output FIFO Buffer) with Backpressure Kronecker Tensor Product Parallel Loops Primitive FIR with Back Pressure Primitive FIR with Back Pressure Primitive Systolic FIR with Forward Pressure Primitive Systolic FIR with Forward Flow Control Rectangular Nested Loop Sequential Loops Triangular Nested Loop Host Interface Memory-Mapped Registers Platforms  16-Channel DDC 16-Channel DUC 2-Antenna DUC for WiMAX 2-Channel DUC Super-Sample Rate Digital Upconverter Primitive Blocks 8×8 Inverse Discrete Cosine Transform Automatic Gain Control Bit Combine for Boolean Vectors                                         | 6-30<br>6-30<br>6-31<br>6-31<br>6-33<br>6-33<br>6-34<br>6-34<br>6-34<br>6-35<br>6-35<br>6-35<br>6-36<br>6-36<br>6-37<br>6-38<br>6-38                 |

| Avalon-ST Interface (Input and Output FIFO Buffer) with Backpressure Avalon-ST Interface (Output FIFO Buffer) with Backpressure Kronecker Tensor Product Parallel Loops Primitive FIR with Back Pressure Primitive FIR with Forward Pressure Primitive Systolic FIR with Forward Flow Control Rectangular Nested Loop Sequential Loops Triangular Nested Loop Host Interface Memory-Mapped Registers Platforms 16-Channel DDC 16-Channel DUC 2-Antenna DUC for WiMAX 2-Channel DUC Super-Sample Rate Digital Upconverter Primitive Blocks 8×8 Inverse Discrete Cosine Transform Automatic Gain Control Bit Combine for Boolean Vectors Bit Extract for Boolean Vectors                                                    | 6-30<br>6-30<br>6-31<br>6-31<br>6-33<br>6-33<br>6-34<br>6-34<br>6-34<br>6-35<br>6-35<br>6-35<br>6-36<br>6-36<br>6-37<br>6-38<br>6-38<br>6-39<br>6-39 |

| Avalon-ST Interface (Input and Output FIFO Buffer) with Backpressure Avalon-ST Interface (Output FIFO Buffer) with Backpressure Kronecker Tensor Product Parallel Loops Primitive FIR with Back Pressure Primitive FIR with Forward Pressure Primitive Systolic FIR with Forward Flow Control Rectangular Nested Loop Sequential Loops Triangular Nested Loop Host Interface Memory-Mapped Registers Platforms 16-Channel DDC 16-Channel DUC 2-Antenna DUC for WiMAX 2-Channel DUC Super-Sample Rate Digital Upconverter Primitive Blocks 8×8 Inverse Discrete Cosine Transform Automatic Gain Control Bit Combine for Boolean Vectors Bit Extract for Boolean Vectors Color Space Converter                              | 6-30<br>6-30<br>6-31<br>6-32<br>6-33<br>6-34<br>6-34<br>6-34<br>6-35<br>6-35<br>6-35<br>6-36<br>6-36<br>6-37<br>6-38<br>6-38<br>6-39<br>6-39         |

| Avalon-ST Interface (Input and Output FIFO Buffer) with Backpressure Avalon-ST Interface (Output FIFO Buffer) with Backpressure Kronecker Tensor Product Parallel Loops Primitive FIR with Back Pressure Primitive FIR with Forward Pressure Primitive Systolic FIR with Forward Flow Control Rectangular Nested Loop Sequential Loops Triangular Nested Loop Host Interface Memory-Mapped Registers Platforms 16-Channel DDC 16-Channel DUC 2-Antenna DUC for WiMAX 2-Channel DUC Super-Sample Rate Digital Upconverter Primitive Blocks 8×8 Inverse Discrete Cosine Transform Automatic Gain Control Bit Combine for Boolean Vectors Bit Extract for Boolean Vectors Color Space Converter CORDIC from Primitive Blocks | 6-30<br>6-30<br>6-31<br>6-31<br>6-33<br>6-33<br>6-34<br>6-34<br>6-35<br>6-35<br>6-35<br>6-36<br>6-37<br>6-38<br>6-38<br>6-39<br>6-39<br>6-39<br>6-40 |

| Avalon-ST Interface (Input and Output FIFO Buffer) with Backpressure Avalon-ST Interface (Output FIFO Buffer) with Backpressure Kronecker Tensor Product Parallel Loops Primitive FIR with Back Pressure Primitive FIR with Forward Pressure Primitive Systolic FIR with Forward Flow Control Rectangular Nested Loop Sequential Loops Triangular Nested Loop Host Interface Memory-Mapped Registers Platforms 16-Channel DDC 16-Channel DUC 2-Antenna DUC for WiMAX 2-Channel DUC Super-Sample Rate Digital Upconverter Primitive Blocks 8×8 Inverse Discrete Cosine Transform Automatic Gain Control Bit Combine for Boolean Vectors Bit Extract for Boolean Vectors Color Space Converter                              | 6-30<br>6-30<br>6-31<br>6-31<br>6-33<br>6-34<br>6-34<br>6-34<br>6-35<br>6-35<br>6-35<br>6-36<br>6-37<br>6-37<br>6-38<br>6-39<br>6-39<br>6-39<br>6-40 |

| Fractional Square Root Using CORDIC   6-41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    | Folded Vector Sort                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fixed-point Maths Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    | Fractional Square Root Using CORDIC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | . 6–41                                                                                                                                                                                               |

| Hybrid Direct Form and Transpose Form FIR Filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    | Fixed-point Maths Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | . 6–41                                                                                                                                                                                               |

| Loadable Counter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                      |

| Loadable Counter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    | Hybrid Direct Form and Transpose Form FIR Filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | . 6–42                                                                                                                                                                                               |