# TMC2081 Digital Video Mixer

#### **Features**

- Mixes 24//16-bit GBR/YC<sub>B</sub>C<sub>R</sub>444//YC<sub>B</sub>C<sub>R</sub>422 and 8-bit color-index sources

- 24//16-bit GBR/YCBCR444//YCBCR422 output

- 255-step proportional mixing via  $\alpha_{7-0}$  inputs

- 256-step mixing with  $\alpha_{8-0}$  for  $\alpha=100$ h unity gain

- 256 x 8-bit look-up table on  $\alpha$  channel

- · Lap-dissolve and fade effects

- α and crosspoint controls for soft and color-border wipe generation

- Mask register and three 256 x 8 bypassable CLUTs with overlay on A-channel

- · Analog preview output with sync on Green/Y

- D/A power-down modes

- Single +5 volt power supply operation

- Pin compatible with TMC22080 Digital Mixer

#### **Applications**

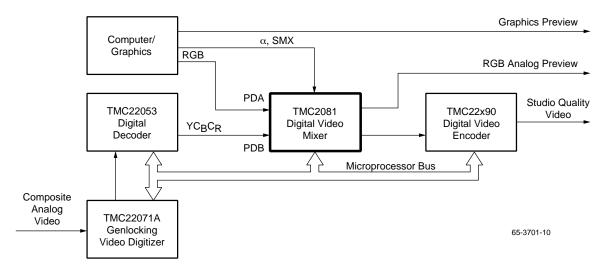

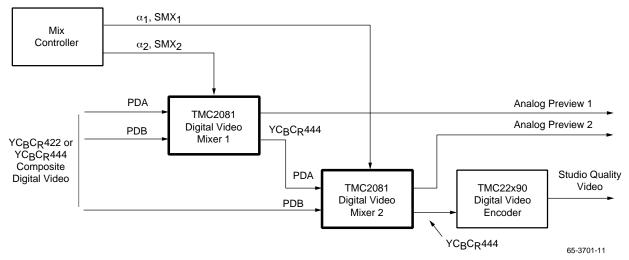

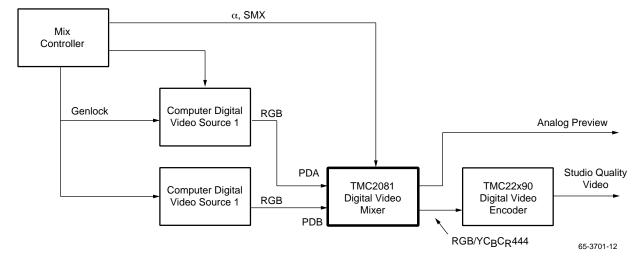

- Mixing computer graphics and live video

- · Lap-dissolve between video sources

- · Fade to black or to user-selectable fill color

- Window/wipe processing

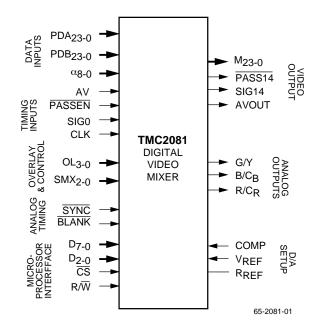

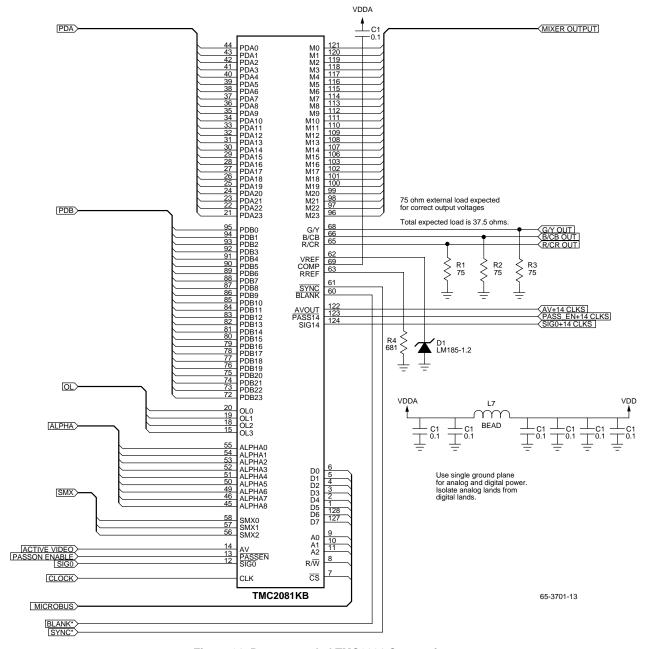

## **Logic Symbol**

#### **Description**

The TMC2081 is a Digital Video Mixer that performs

$$\mathbf{M} = (\alpha) \mathbf{V}_1 + (1-\alpha) \mathbf{V}_2 \quad \text{(for } 0 \le \alpha \le 1)$$

cross-fading at speeds faster than 40 Mpps proportionally controlled by a 9-bit  $\alpha$ -channel input. Variable rate dissolves and fades may be implemented with unity gain at the  $\alpha$  endpoints. With the  $\alpha$ -Look-Up Table ( $\alpha$ LUT), mixing may be controlled by a single bit of the  $\alpha$ -channel input. Setup is via a microprocessor interface.

Supported video formats are 24-bit GBR, YC<sub>B</sub>C<sub>R</sub>444, and 16-bit YC<sub>B</sub>C<sub>R</sub>422 component video. Dissimilar pixel formats may be mixed using on-chip interpolation and decimation filters and GBR/YC<sub>B</sub>C<sub>R</sub> and YC<sub>B</sub>C<sub>R</sub>/GBR color-space conversion matrices.

An additional format accepted by the A-channel is 8-bit color-indexed pixel data which addresses three bypassable 256 x 8 color look-up tables (CLUTs). A 15 color overlay palette and a 24-bit fill register are also included.

Digital and Analog outputs may be programmed to view either mixer inputs,  $V_1$  or  $V_2$  or mixer output, M.

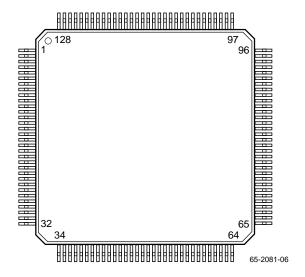

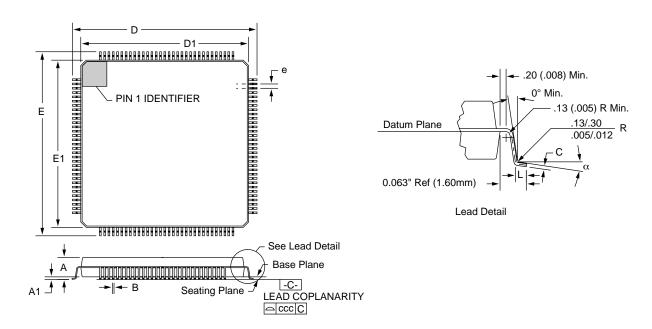

Packaged in a 128-lead plastic metric quad flat-pack (MQFP), the TMC2081 is fabricated with a sub-micron CMOS process. Performance is guaranteed over the commercial, 0°C to 70°C temperature range.

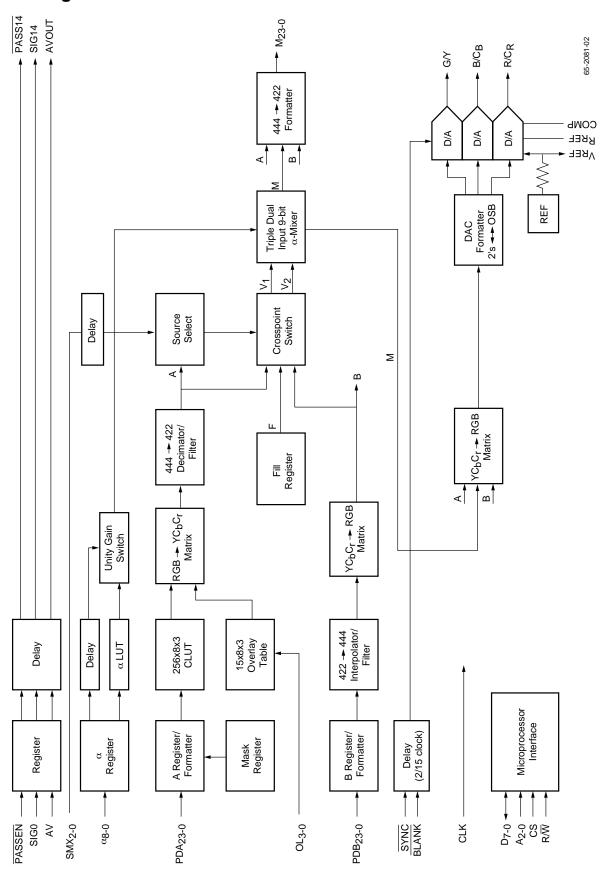

## **Block Diagram**

#### **Functional Description**

The TMC2081 is a monolithic digital video processor that proportionally mixes digital video in GBR, YC<sub>B</sub>C<sub>R</sub>, or color-index formats. Some of the variety of input and output data format combinations are shown in Table 1.

The A-channel data path has transformation circuits that can look up 24-bit GBR values from 8-bit color-index inputs, convert GBR-to- $YC_BC_R$  format, and decimate  $YC_BC_R4444$  to  $YC_BC_R422$ . The B-channel path includes circuits that convert  $YC_BC_R$  to GBR and interpolate  $YC_BC_R422$  to  $YC_BC_R444$ . Prior to mixing, incoming pixel data streams must be converted to matching formats by setting the A and B channel control registers.

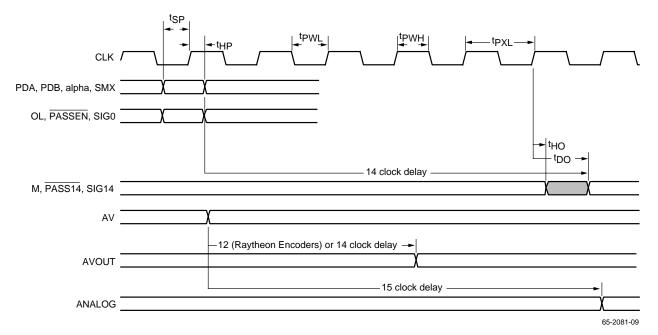

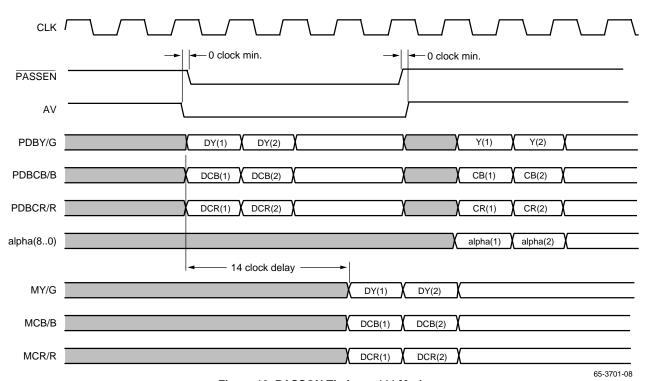

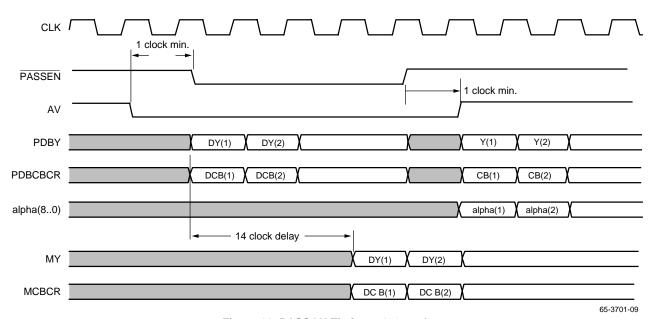

Data enters the TMC2081 through the PDA23-0, PDB23-0,  $\alpha_{8\text{-}0}$ , and OL3-0 ports. Data and video controls (PASSEN and AV) are simultaneously registered on the rising edge of PXCLK. Pipeline latency is 14 clock cycles to the mixed digital video output.

Although PDA<sub>23-0</sub>, PDB<sub>23-0</sub>, and  $M_{23-0}$  data formats may be different,  $V_1$  and  $V_2$  data formats at the  $\alpha$ -Mixer input must be matched: unsigned magnitude for GBR and Y components; 2's complement for  $C_B$  and  $C_R$  components.

Data formats converted within the TMC2081 are determined by the control bits programmed into the internal registers.

Output format may be GBR,  $YC_BC_R444$  or  $YC_BC_R422$ . Either crosspoint switch input, A and B or the Mixer output may be selected at the  $M_{23\text{-}0}$  port. Table 2, Table 3 and Table 4 show examples of the  $M_{23\text{-}0}$  output for 9-bit  $\alpha$ -mixing. In Table 3,  $C_BC_R$  is accepted at the  $C_B$  input. Table 4 exemplifies format conversion.

Mixer output and inputs may be previewed by three video D/A converters. Analog outputs may be either GBR or YC<sub>B</sub>C<sub>R</sub>.

For initialization and control, internal registers and tables may be accessed through a microprocessor interface.

Power may be conserved by disabling the D/A converters or sections of the TMC2081 via internal Control Registers. In the latter mode, the microprocessor interface remains active and Control Register settings are retained but CLUT locations are not accessible.

**Table 1. Input and Output Data Format Examples**

| A Input<br>Format                  | B Input<br>Format                  | A<br>CLUT | A<br>GBR-YC <sub>B</sub> C <sub>R</sub> | A<br>Decimate | B<br>Interpolate | B<br>YC <sub>B</sub> C <sub>R</sub> -GBR | M<br>Format | M Output<br>Format                 |

|------------------------------------|------------------------------------|-----------|-----------------------------------------|---------------|------------------|------------------------------------------|-------------|------------------------------------|

| YC <sub>B</sub> C <sub>R</sub> 444 | YC <sub>B</sub> C <sub>R</sub> 444 | Bypass    | Bypass                                  | Bypass        | Bypass           | Bypass                                   | Low         | YC <sub>B</sub> C <sub>R</sub> 444 |

| YC <sub>B</sub> C <sub>R</sub> 444 | YC <sub>B</sub> C <sub>R</sub> 422 | Bypass    | Bypass                                  | Bypass        | Enable           | Bypass                                   | Low         | YC <sub>B</sub> C <sub>R</sub> 444 |

| YC <sub>B</sub> C <sub>R</sub> 444 | YC <sub>B</sub> C <sub>R</sub> 422 | Bypass    | Bypass                                  | Enable        | Bypass           | Bypass                                   | High        | YC <sub>B</sub> C <sub>R</sub> 422 |

| YC <sub>B</sub> C <sub>R</sub> 422 | YC <sub>B</sub> C <sub>R</sub> 422 | Bypass    | Bypass                                  | Bypass        | Bypass           | Bypass                                   | High        | YC <sub>B</sub> C <sub>R</sub> 422 |

| YC <sub>B</sub> C <sub>R</sub> 422 | YC <sub>B</sub> C <sub>R</sub> 422 | Bypass    | Bypass                                  | Bypass        | Bypass           | Bypass                                   | Low         | YC <sub>B</sub> C <sub>R</sub> 444 |

| GBR, CI                            | YC <sub>B</sub> C <sub>R</sub> 444 | Enable    | Bypass                                  | Bypass        | Bypass           | Enable                                   | Low         | GBR                                |

| GBR, CI                            | YC <sub>B</sub> C <sub>R</sub> 444 | Enable    | Enable                                  | Bypass        | Bypass           | Bypass                                   | Low         | YC <sub>B</sub> C <sub>R</sub> 444 |

| GBR, CI                            | YC <sub>B</sub> C <sub>R</sub> 422 | Enable    | Bypass                                  | Bypass        | Enable           | Enable                                   | Low         | GBR                                |

| GBR, CI                            | YC <sub>B</sub> C <sub>R</sub> 422 | Enable    | Enable                                  | Enable        | Bypass           | Bypass                                   | High        | YC <sub>B</sub> C <sub>R</sub> 422 |

| GBR, CI                            | GBR                                | Enable    | Bypass                                  | Bypass        | Bypass           | Bypass                                   | Low         | GBR                                |

Table 2. GBR Mixing Example (9-bit  $\alpha$ )

| α     | PDA (hex) |    |    | ex) PDB (hex) |    |    | M (hex) |    |    |

|-------|-----------|----|----|---------------|----|----|---------|----|----|

| (hex) | G         | В  | R  | G             | В  | R  | G       | В  | R  |

| 000   | BB        | CC | AA | EE            | FF | DD | EE      | FF | DD |

| 040   | BB        | CC | AA | EE            | FF | DD | E1      | F2 | D0 |

| 080   | BB        | CC | AA | EE            | FF | DD | D5      | E6 | C4 |

| 100   | BB        | CC | AA | EE            | FF | DD | BB      | CC | AA |

Table 3. YC<sub>B</sub>C<sub>R</sub>422 Mixing Example (C<sub>B</sub> and C<sub>R</sub> in 2's Complement)

| α     |    | PDA (hex) |    |    | PDB (hex) |    |    | M (hex) |    |  |

|-------|----|-----------|----|----|-----------|----|----|---------|----|--|

| (hex) | Y  | Св        | CR | Y  | Св        | CR | Y  | Св      | CR |  |

| 40    | 10 | F4        | XX | 20 | 4         | XX | 1C | 00      | 00 |  |

| 80    | 10 | F4        | XX | 20 | 4         | XX | 18 | 00      | 00 |  |

| 40    | 10 | F4        | XX | 20 | 4         | XX | 1C | 00      | 00 |  |

| 40    | 10 | FE        | XX | 20 | 2         | XX | 1C | 01      | 00 |  |

| A0    | 30 | 60        | XX | 40 | 70        | XX | 36 | 66      | 00 |  |

| В0    | 30 | 80        | XX | 40 | 90        | XX | 35 | 86      | 00 |  |

| A0    | 30 | C0        | XX | 40 | D0        | XX | 36 | C6      | 00 |  |

| В0    | 30 | E0        | XX | 40 | F0        | XX | 35 | E5      | 00 |  |

Table 4. YC<sub>B</sub>C<sub>R</sub>422-to-YC<sub>B</sub>C<sub>R</sub>444 Mixing Example

| α     |    | PDA (hex) |         |    | PDB (hex) |         |    | M (hex) |                |  |

|-------|----|-----------|---------|----|-----------|---------|----|---------|----------------|--|

| (hex) | Y  | CB        | $C_{R}$ | Y  | CB        | $C_{R}$ | Y  | CB      | C <sub>R</sub> |  |

| 40    | 10 | F4        | XX      | 20 | 4         | XX      | 1C | 00      | 00             |  |

| 40    | 10 | F4        | XX      | 20 | 4         | XX      | 1C | 00      | 00             |  |

| 40    | 10 | F4        | XX      | 20 | 4         | XX      | 1C | 00      | 01             |  |

| 40    | 10 | FE        | XX      | 20 | 2         | XX      | 1C | 00      | 01             |  |

| A0    | 30 | 60        | XX      | 40 | 70        | XX      | 36 | 66      | 86             |  |

| В0    | 30 | 80        | XX      | 40 | 90        | XX      | 35 | 66      | 86             |  |

| A0    | 30 | C0        | XX      | 40 | D0        | XX      | 36 | C6      | E5             |  |

| В0    | 30 | E0        | XX      | 40 | F0        | XX      | 35 | C6      | E5             |  |

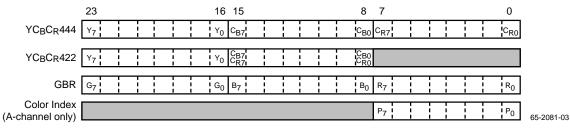

#### **Input Formats**

Data is accepted by PDA and PDB channels in one pair of the following formats:

- 1. YC<sub>B</sub>C<sub>R</sub>444

- $2. YC_BC_R422$

- 3. GBR

- 4. 8-bit color-index mapped to a palette of 256x256x256 colors. (A-channel only)

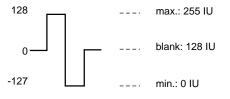

Details of bits assignments are shown in Figure 1. Pixel Data Formats with the expected data ranges are shown in Table 5.

Table 5. YC<sub>B</sub>C<sub>R</sub> and GBR Data Types and Ranges

| Signal                        | Min. | Max. | Format          |

|-------------------------------|------|------|-----------------|

| GBR                           | 0    | 255  | Unsigned Binary |

| Y                             | 16   | 235  | Unsigned Binary |

| C <sub>B</sub> C <sub>R</sub> | -112 | +112 | 2's Complement  |

|                               |      |      | Offset Binary   |

Figure 1. Pixel Data Formats

#### **A-Channel Operation**

A-channel pixel data, PDA, is registered on the rising edge of CLK.  $C_BC_R$  data is either passed or format converted (from offset binary to 2's complement) by MSB inversion. 16-bit  $YC_BC_R422$  data is converted to 24-bit  $YC_BC_R$  data by pixel replication of  $C_BC_R$  data. Each of the three A channel bytes is logically-ANDed with the contents of the Mask Register.

The CLUT in the A-channel pixel data path comprises three 256-word x 8-bit sections. When the CLUT is enabled, pixel data addresses the CLUT, which outputs the address contents for subsequent processing. The CLUT may also be bypassed, passing incoming pixel data directly to subsequent circuits.

For 24-bit GBR operation, each of the 256-word by 8-bit CLUTs is independently addressed by green, blue, and red bytes from PDA<sub>23-0</sub>. For Color-index operation, each of the 256 x 8 CLUTs is addressed by the same pixel data from PDA<sub>7-0</sub>.

CLUT locations may hold GBR or  $YC_BC_R$  color values.  $V_1$  and  $V_2$  mixer input formats must match CLUT formats.

The PDA overlay palette is addressed by four Overlay inputs, OL<sub>3-0</sub> and is enabled via the Control Register. Each valid Overlay address produces one of 15 24-bit colors selected from stored 8-bit red, green, and blue values. If all four overlay inputs are LOW, CLUT data is selected. If any overlay input is HIGH, OL<sub>3-0</sub> is decoded into the corresponding color which is selected at the RGB/YC<sub>B</sub>C<sub>R</sub> matrix. OL<sub>3-0</sub> may be changed on a pixel-by-pixel basis.

Table 6. A-Channel GBR-to-YCBCR Mapping for Fully-Saturated Colors

|         | Inp | out Valu | ıes | Output Values |      |      |

|---------|-----|----------|-----|---------------|------|------|

| Color   | R   | G        | В   | Y             | СВ   | CR   |

| White   | 255 | 255      | 255 | 235           | 0    | 0    |

| Yellow  | 255 | 255      | 0   | 210           | -112 | 18   |

| Cyan    | 0   | 255      | 255 | 169           | 38   | -112 |

| Green   | 0   | 255      | 0   | 144           | -74  | -94  |

| Magenta | 255 | 0        | 255 | 106           | 74   | 94   |

| Red     | 255 | 0        | 0   | 81            | -38  | 112  |

| Blue    | 0   | 0        | 255 | 41            | 112  | -18  |

| Black   | 0   | 0        | 0   | 16            | 0    | 0    |

Table 7. B-Channel YC<sub>B</sub>C<sub>R</sub>-GBR Mapping for Fully-Saturated Colors

|         | Inp | out Valu | ies  | Output Values |     |     |  |

|---------|-----|----------|------|---------------|-----|-----|--|

| Color   | Y   | Св       | CR   | R             | G   | В   |  |

| White   | 235 | 0        | 0    | 255           | 255 | 255 |  |

| Yellow  | 210 | -112     | 18   | 255           | 255 | 0   |  |

| Cyan    | 169 | 38       | -112 | 0             | 255 | 255 |  |

| Green   | 144 | -74      | -94  | 0             | 255 | 0   |  |

| Magenta | 106 | 74       | 94   | 255           | 0   | 255 |  |

| Red     | 81  | -38      | 112  | 255           | 0   | 0   |  |

| Blue    | 41  | 112      | -18  | 0             | 0   | 255 |  |

| Black   | 16  | 0        | 0    | 0             | 0   | 0   |  |

#### **B-Channel Operation**

YC<sub>B</sub>C<sub>R</sub>444, YC<sub>B</sub>C<sub>R</sub>422, or GBR are accepted by the B-channel. PDB<sub>23-0</sub> pixel data is registered on the rising edge of CLK. 16-bit YC<sub>B</sub>C<sub>R</sub>422 data is converted to 24-bit YC<sub>B</sub>C<sub>R</sub>444 data by pixel replication of C<sub>B</sub>C<sub>R</sub> data in the Register/Formatter.

24-bit data is passed to an interpolation filter followed by a color-space converter to ensure that the B-channel data format matches that of the A-channel prior to mixing. Table 1 illustrates the setup of color-space converters, decimation, and interpolation filters. Pipeline latencies of the A and B-channels are matched.

#### Interpolation and Decimation Filters

Digital interpolation and decimation filters in the A- and B-channels suppress unwanted artifacts in the chrominance components. Maximum passband attenuation is 0.06 dB. Minimum stopband rejection is 41 dB.

When the input format is  $YC_BC_R422$ , the incoming pixel following AV transitioning HIGH is assumed to be the  $C_B$  pixel. (See Figure 11.)

## α-Channel Operation

Nine bits of  $\alpha$  data are registered on a pixel-by-pixel basis from  $\alpha_{8\text{-}0}$ . Either 9-bit or 8-bit  $\alpha$  values can be selected by setting Control Register Bit  $\alpha$ GAIN. Table 8 shows the differences between the 8-bit and 9-bit gain settings for a 0FF input.

Bits  $\alpha_{7\text{-}0}$  address a 256 x 8-bit lookup table ( $\alpha$ LUT). The  $\alpha$ LUT may be used to redefine the function of incoming  $\alpha$  data for special effects or low resolution dissolves and fades.

Bit  $\alpha_8$  controls a unity gain switch. If  $\alpha_8 = 1$ , then  $\alpha$  is set to unity gain.  $\alpha_8$  functions independently of the  $\alpha$  gain bit register 0. For 8-bit  $\alpha$  mixing, set  $\alpha_8 = 0$ .

By setting control register bit  $\alpha LUTEN = 0$ , the  $\alpha LUT$  may be completely bypassed, allowing  $\alpha_{8\text{-}0}$  to directly control the mixing of A, B and F.  $\alpha LUT$  locations may be accessed via the  $D_{7\text{-}0}$  microprocessor port.

**Table 8. Alpha Channel Gains**

| α value (hex) | 8-bit Gain | 9-bit Gain |

|---------------|------------|------------|

| 000           | 0/256      | 0/256      |

| 001           | 1/256      | 1/256      |

|               |            |            |

| 07F           | 127/256    | 127/256    |

| 080           | 128/256    | 128/256    |

|               |            |            |

| 0FE           | 254/256    | 254/256    |

| 0FF           | 256/256    | 255/256    |

| 100           | 256/256    | 256/256    |

| 1XX           | 256/256    | 256/256    |

#### **Fill Color Registers**

Three registers, 03, 04, and 05, store a solid fill color, F. Either GBR values or  $YC_BC_R$  values may be stored but the format must match the data format of the A- and B-channels at the input to the crosspoint switch.

Fill color registers are accessed through the D<sub>7-0</sub> microprocessor port. Fill color may be used as an alternative video source for fades.

#### α-Mixer

There are three sources of data for the mixer: A-channel pixels, B-channel pixels, and the stored fill color, F. One pair of inputs, either AB, BF or FA are selected by the Crosspoint Switch to be passed to the  $V_1$  and  $V_2$  inputs of the  $\alpha$ -Mixer. Prior to mixing,  $V_1$  and  $V_2$  data formats must be matched (see Table 1).

Within the  $\alpha$ -Mixer are three dual input 9-bit mixers which mix each of the component channels of  $V_1$  and  $V_2$ . By varying the value on the  $\alpha$ -channel from  $000_h$  to  $100_h$ , the Mixer performs a 256-step transition from one digital video source to the other.

Six dissolve transitions are supported: A-to-B, A-to-F, B-to-A, B-to-F, F-to-A, and F-to-B. Type of dissolve is selected by directing the A-, B-, or F pixels to the  $V_1$  or  $V_2$  mixer input via the ABF Crosspoint Switch. This is done either by internal Control Registers via the microprocessor port or directly through the SMX<sub>2-0</sub> inputs. SMX<sub>2-0</sub> input pins are enabled via SMX Control Register bits. When enabled, SMX<sub>2-0</sub> directly control the ABF Crosspoint Multiplexer on a pixel-by-pixel basis, for externally derived wipe patterns.

Rate of dissolve is controlled directly through the  $\alpha$ -channel. Transfer function of the mixer is:

$$M = (\alpha) V_1 + (1-\alpha) V_2$$

where  $V_1$  and  $V_2$  are two of the three inputs A, B or F selected by the crosspoint switch.

For an A-to-B dissolve transition, as the value of the eight LSBs of the  $\alpha$ -channel change from  $00_h$  to  $FF_h$ , (or  $000_h$  to  $100_h$  in the 9-bit mode), an increasing level of A-channel contribution and a decreasing level of B-channel contribution becomes evident at the output, M.

Bit  $\alpha_8$  of the  $\alpha$ -channel can correct for the 255/256 gain factor in the A-channel that occurs when the 8-bit  $\alpha$  value is FF<sub>h</sub>. When  $\alpha_8$  =1, bits  $\alpha_{7\text{-}0}$  are ignored, A-channel gain is set to 256/256 and B-channel gain is set to 0/256.

Modified transfer functions may be selected for background/ foreground and drop-shadow effects by programming control register bits, MIXTFN.

A Foreground Key may be created such that:

$$M = (\alpha) V_1$$

A Background Key may be created such that:

$$M = (\alpha) V_1 + V_2$$

By using foreground and background mixers in series, drop shadow effects can be implemented.

$\alpha$  may change at pixel rates up to 40 Mpps on a pixel-by-pixel basis, allowing smooth transitions from one video source to another. Transition time interval may vary from many frames to only a few or a single pixel depending upon the  $\alpha$ -channel data rate.

$\alpha_8$  may be used like a key input. Either unity gain  $V_1$  or  $(1-\alpha)V_2$  may be selected. A- and B-channel pixels may be mixed by switching  $\alpha_8$  on a pixel-by-pixel basis. Pipeline latencies of the  $\alpha$ -, A- and B-channels are matched.

#### **Passing of Non-Pixel Data**

In the PASSON mode, the TMC2081 is transparent to data accepted during the PASSEN = LOW period (see Figure 10 and Figure 11). Either PDA or PDB data may be selected to pass on reference signals containing time codes, subcarrier phase and frequency data from upstream video processors.

#### **Digital Outputs**

Data at the  $M_{23-0}$  output port, may be selected from either the mixer or, for digital preview, the A or B crosspoint switch inputs.

The 444-to-422 formatter may be bypassed for 24-bit output. To convert 24-bit  $YC_BC_R$  data to the 16-bit  $YC_BC_R$ 422 format, the formatter needs to be enabled.

Except for color index, all data formats shown in Figure 1 are available:

- YC<sub>B</sub>C<sub>R</sub>444

- YCBCR422

- GBR

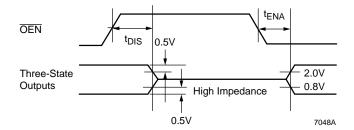

M<sub>23-0</sub> bits are clocked synchronously with the rising edge of CLK. M<sub>23-0</sub> data outputs may be disabled to a high-impedance state by setting the MOUT Control Register bit LOW.

## **Analog Preview**

Either crosspoint switch input (A or B) or the mixed pixel data output ( $M_{23-0}$ ) can be monitored by D/A con-verters. D/A outputs may be either YC<sub>B</sub>C<sub>R</sub> or GBR. A YC<sub>B</sub>C<sub>R</sub>-to-GBR matrix prior to the D/A converters can be selected for color-space conversion.

To view A or B data originating in the C<sub>B</sub>C<sub>R</sub> format, the DACFRM Control Register bit must be set to convert 2's-complement data to the offset binary format.

With the DACSLP bit, D/A converters can be powered down and with the DACOVL bit, the D/A overlay RAM can be powered down.

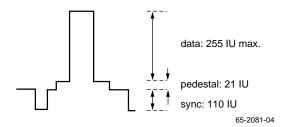

#### **D/A Converter Outputs**

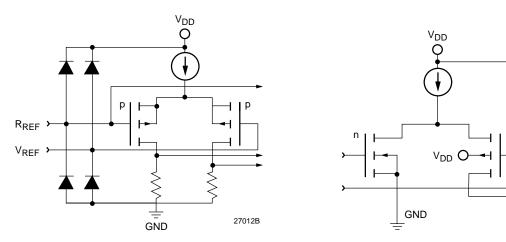

Each D/A converter comprises an array of current sources referenced to  $V_{DD}$  and controlled by the data,  $\overline{BLANK}$ , and  $\overline{SYNC}$  inputs. When  $\overline{BLANK}=HIGH$ , the SETUP Control Register bit determines if a pedestal is activated. With nominal  $R_{REF}$  and  $V_{REF}$ , outputs match SMPTE 170M levels when terminated with a 37.5 $\Omega$  resistive load (75 $\Omega$  at the source and destination). By doubling  $R_{REF}$ , a 75 $\Omega$  load can be accommodated.

Full scale current is set by an external resistor,  $R_{SET}$ , connected between the  $R_{REF}$  pin and  $A_{GND}$  and the reference voltage,  $V_{REF}$ .  $V_{REF}$  may be derived from either a 1.235 volt internal source or an external voltage reference connected to  $V_{REF}$ .

Nominal outputs (see Figure 2 and Figure 3) are expressed in Current Units (IU) where 1 IU is equivalent to the current activated by one unit of D/A input data (Gdata/Ydata, Bdata/CRdata, or Rdata/CBdata). SETUP = HIGH activates a 21 IU pedestal when BLANK= H. SYNC = LOW disables a 110 IU sync pulse. SETUP is programmed through Register 7 bit 2.

Figure 2. GBR/Y DAC Output Levels in Current Units

Figure 3. CBCR DAC Output Levels in Current Units

65-2081-05

To translate IUs to millivolts,  $V_{REF}$  and  $R_{SET}$  must be set to the correct values, nominally  $V_{REF} = 1.235$  volt and  $R_{SET} = 681$  ohms. In each table below, G and the Y outputs have been normalized to 1000 mV with Data = 255.

Since V<sub>REF</sub> and R<sub>REF</sub> are common to all D/A converters, B and R full scale outputs track G. C<sub>B</sub> C<sub>R</sub> full scale outputs track Y. R<sub>REF</sub> may be trimmed to set the G or Y full scale voltage to 1000 mV.

In the equations for the GBR and  $YC_BC_R$  outputs that follow, symbols are defined as:

+ = plus

\* = multiply

& = logical AND

! = logical complement

#### **GBR Output**

Expressed in IUs, the GBR transformation from data to current is as follows:

$G = (Gdata + SETUP * 21) \& \overline{BLANK} + \overline{SYNC} * 110$

$B = (Bdata + SETUP * 21) \& \overline{BLANK}$

$R = (Rdata + SETUP * 21) \& \overline{BLANK}$

Sample outputs are listed in Table 9 and Table 10.

Table 9. GBR DAC Transfer Characteristic without Pedestal (SETUP = L)

| D/A           |      |       | G   |      | Во  | r R |

|---------------|------|-------|-----|------|-----|-----|

| Input<br>Data | SYNC | BLANK | IU  | mV   | IU  | mV  |

| 255           | 1    | 1     | 365 | 1000 | 255 | 699 |

| 128           | 1    | 1     | 238 | 652  | 128 | 351 |

| 0             | 1    | 1     | 110 | 301  | 0   | 0   |

| Х             | 1    | 0     | 110 | 301  | 0   | 0   |

| Х             | 0    | 0     | 0   | 0    | 0   | 0   |

| 128           | 0    | 1     | 128 | 351  | 128 | 351 |

Table 10. GBR DAC Transfer Characteristic with Pedestal (SETUP = H)

| D/A           |      |       | (   | }    | Во  | r R |

|---------------|------|-------|-----|------|-----|-----|

| Input<br>Data | SYNC | BLANK | IU  | mV   | IU  | mV  |

| 255           | 1    | 1     | 386 | 1000 | 276 | 715 |

| 128           | 1    | 1     | 259 | 671  | 149 | 386 |

| 0             | 1    | 1     | 131 | 339  | 21  | 54  |

| Х             | 1    | 0     | 110 | 285  | 0   | 0   |

| Х             | 0    | 0     | 0   | 0    | 0   | 0   |

| 128           | 0    | 1     | 149 | 386  | 149 | 386 |

#### YC<sub>B</sub>C<sub>R</sub> Output

Data inputs are unsigned Ydata and offset-binary format  $C_B$ data and  $C_R$ data.  $\overline{BLANK} = L$  sets  $C_B$  and  $C_R$  outputs to 128, the value for zero chrominance data.  $YC_BC_R$  transfer equations are:

$Y = (Ydata + SETUP * 21) & \overline{BLANK} + \overline{SYNC} * 110$

$C_B = (Cdata + SETUP * 21) \& \overline{BLANK} + 128 \& !\overline{BLANK}$

$C_R = (Cdata + SETUP * 21) \& \overline{BLANK} + 128 \& !\overline{BLANK}$

Sample outputs are listed in Table 11 and Table 12.

Table 11. YCrCb DAC Transfer Characteristic without Pedestal (SETUP = L)

| D/A           |      |       | Y   |      | C <sub>B</sub> or C <sub>R</sub> |     |  |

|---------------|------|-------|-----|------|----------------------------------|-----|--|

| Input<br>Data | SYNC | BLANK | IU  | mV   | IU                               | mV  |  |

| 255           | 1    | 1     | 365 | 1000 | 255                              | 699 |  |

| 128           | 1    | 1     | 238 | 652  | 128.                             | 351 |  |

| 64            | 1    | 1     | 174 | 477  | 64                               | 175 |  |

| 0             | 1    | 1     | 110 | 301  | 0                                | 0   |  |

| Х             | 1    | 0     | 110 | 301  | 128                              | 351 |  |

| X             | 0    | 0     | 0   | 0    | 128                              | 351 |  |

| 64            | 0    | 1     | 64  | 175  | 64                               | 175 |  |

Table 12. YCrCb DAC Transfer Characteristic with Pedestal (SETUP = H)

| D/A  |      |       | Y   |      | C <sub>B</sub> or C <sub>R</sub> |     |

|------|------|-------|-----|------|----------------------------------|-----|

| Data | SYNC | BLANK | IU  | mV   | IU                               | mV  |

| 255  | 1    | 1     | 386 | 1000 | 276                              | 715 |

| 128  | 1    | 1     | 259 | 670  | 149                              | 386 |

| 64   | 1    | 1     | 195 | 505  | 85                               | 220 |

| 0    | 1    | 1     | 131 | 339  | 21                               | 54  |

| Х    | 1    | 0     | 110 | 285  | 149                              | 386 |

| Х    | 0    | 0     | 0   | 0    | 149                              | 386 |

| 64   | 0    | 1     | 85  | 220  | 85                               | 220 |

#### **Dissolve and Crossfade Operation**

Video transitions such as dissolve and fades may be executed by direct  $\alpha$ -channel control. Rate and start time for the transition depends entirely upon the value of the  $\alpha_{8-0}$  inputs. Transitions may be executed as quickly or slowly as values are presented to the  $\alpha$ -channel. Transitions may remain partially executed by keeping  $\alpha$ -values constant.

It is possible to mix modes, bringing data in either 444 or 422 format and outputting data in 422 or 444 format.

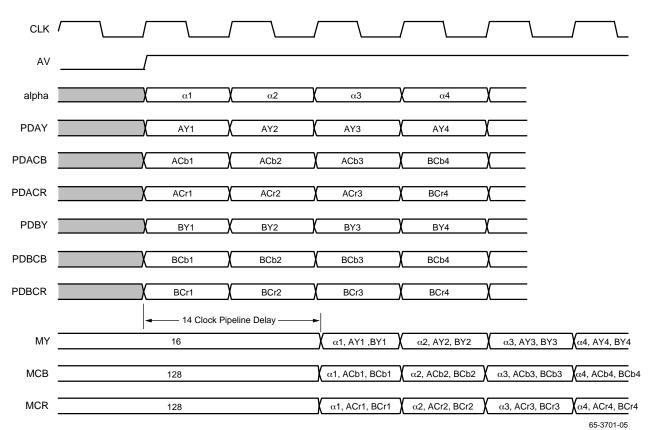

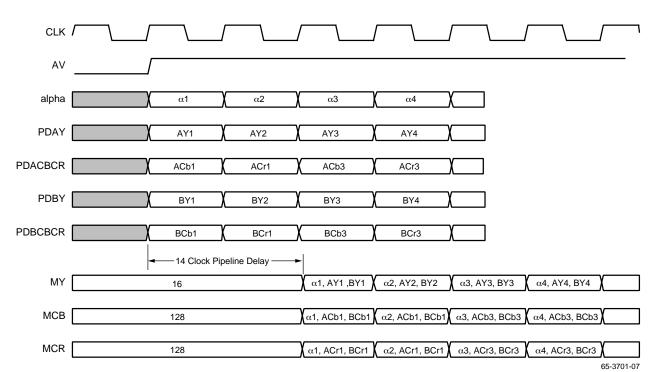

In the 444/444 mode (see Figure 7),  $\alpha$  is applied to each YC<sub>B</sub>C<sub>R</sub> or GBR pixel pair at the input of the mixer. The YC<sub>B</sub>C<sub>R</sub>444 output is mixed at the full  $\alpha$  rate.

In the 422/422 mode (see Figure 8),  $\alpha$  mixes the Y component of incoming PDA and PDB pixels. Only odd indexed  $\alpha$  values mix  $C_BC_R$  components.  $\alpha$ -values applied to  $C_BC_R$  change synchronously with  $C_B$  data. Consequently, full bandwidth  $\alpha$  data is applied to the luminance channel but the chrominance channel  $\alpha$  values are decimated by dropping the even values that are synchronous with  $C_R$  data.

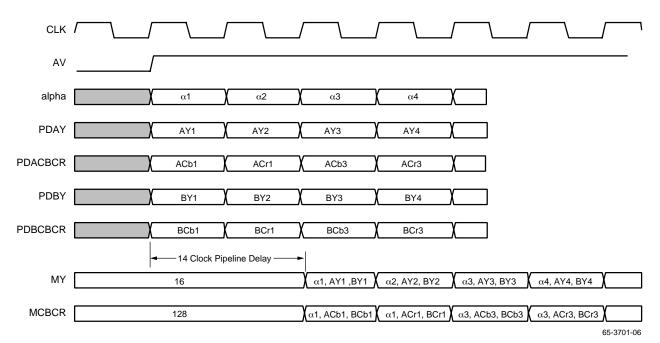

In the 422/444 mode (see Figure 9), YC<sub>B</sub>C<sub>R</sub>422 data is accepted at the PDA and PDB port but the output at the  $M_{23\text{-}0}$  port is YC<sub>B</sub>C<sub>R</sub>444.  $\alpha$  may change from pixel-to-pixel with mixing at the  $M_{23\text{-}0}$  outputs tracking both Y and C<sub>B</sub>C<sub>R</sub>. Although odd values of C<sub>B</sub> and C<sub>R</sub> are repeated at half the pixel rate,  $\alpha$  transitions are applied to C<sub>B</sub> and C<sub>R</sub> at the pixel rate.

## **Microprocessor Interface**

Internal Control Registers, CLUT,  $\alpha$ LUT, and the overlay palette are accessed through a bi-directional microprocessor port, D<sub>7-0</sub>. Table 13 shows how address bits, A<sub>2-0</sub>, select the registers to be accessed.

Table 13. Microprocessor Port Address Map

| A <sub>2-0</sub> | Action                                                                                            |

|------------------|---------------------------------------------------------------------------------------------------|

| 000              | RAM Address Register for CLUT, $\alpha$ LUT, and overlay palette for write operations             |

| 001              | Directs RAM R/W operations selected by the two MSBs of Control Address Register                   |

| 010              | Reserved                                                                                          |

| 011              | RAM Address Register for CLUT, $\alpha$ LUT, and overlay palette for read operations              |

| 100              | Reserved                                                                                          |

| 101              | Directs Control Register R/W operations selected by the four LSBs of the Control Address Register |

| 110              | Mask Register (Default: Load with FF)                                                             |

| 111              | Control Address Register                                                                          |

As shown in Table 14, to access a control register, Control Address Register bits D<sub>3-0</sub> must be set to specify one of the nine control registers shown in Table 17. For access to LUTs and Overlay palettes, Control Address Register bits D<sub>7-6</sub> must be set to select the address of one of the four RAMs shown in Table 14.

**Table 14. Control Address Register Bit Definitions**

| RAM Select     |                | Reserved C     |                | Contro                 | Control Register Address |                |                |

|----------------|----------------|----------------|----------------|------------------------|--------------------------|----------------|----------------|

| D <sub>7</sub> | D <sub>6</sub> | D <sub>5</sub> | D <sub>4</sub> | D <sub>3</sub>         | D <sub>2</sub>           | D <sub>1</sub> | D <sub>0</sub> |

| 0              | 0              | ,              |                | A-channel CLUT         |                          |                |                |

| 0              | 1              |                | A-cha          | nannel Overlay palette |                          |                |                |

| 1              | 0              |                |                | Reserved               |                          |                |                |

| 1              | 1              | αLUT           |                |                        |                          |                |                |

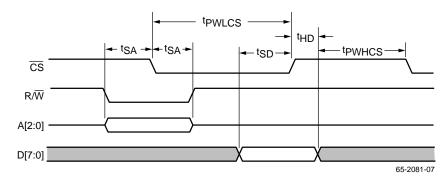

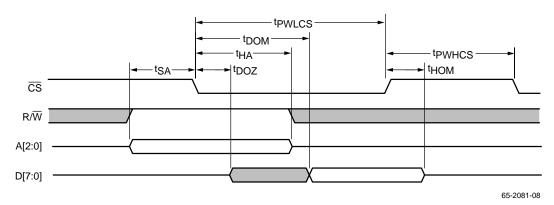

Figure 4 and Figure 5 show the microprocessor port read and write timing cycles. Table 15 shows the Control Register read and write sequences.

When loading or reading look-up tables or the overlay palette, with the exception of  $\alpha$ -LUT write, the address pointer is auto-incremented after each read or write operation. For  $\alpha$ -LUT write, the address pointer is pre-incremented, so that the address must be set one address before the required address. For  $\alpha$ -LUT read, the address pointer is post-incremented.

When accessing the A-channel CLUT, or A-channel Overlay palette, each address location must be written/read three consecutive times for red  $(R/C_R)$ , green (G/Y), and blue  $(B/C_B)$  data. After accessing the blue data, the address pointer autoincrements.

In Table 16, note that:

- To read the α-LUT, Control Register 06h, bit 5 must be set to enable the α-LUT.

- To read the CLUT and Overlay Table, Control Register 00h, bit 4 (CLUT) must be set to enable both the CLUT and Overlay Table.

- 3. Data may be written to the CLUT or  $\alpha$ LUT with Control Register bits set to enable or bypass.

- When writing to the α-LUT, the address pre-increments.

The address pointer is set to FFh, one address before address 00h.

- 5. Load mask register to pass PDA data.

#### **Power and Ground**

The TMC2081 operates from a single +5 Volt power supply. Multiple power and ground pins are assigned and must be connected.

Table 15. Control Register Read/Write Sequences

| Step                           | R/W        | A <sub>2-0</sub> | D <sub>7-0</sub> | Function                                                                      |  |

|--------------------------------|------------|------------------|------------------|-------------------------------------------------------------------------------|--|

| Write to all Control Registers |            |                  |                  |                                                                               |  |

| 1                              | 0          | 111              | x0               | Writes 0 to Address Control Register (selects the A-channel Control Register) |  |

| 2                              | 0          | 101              | aa               | Writes aa into A-channel Control Register                                     |  |

|                                |            |                  |                  | Repeat steps 1 and 2 incrementing data to Address Control Register            |  |

| 15                             | 0          | 111              | 07               | Writes 07 to Address Control Register (selects the D/A Control Register)      |  |

| 16                             | 0          | 101              | bb               | Writes bb into D/A Control Register                                           |  |

| Read/Mod                       | dify/Write | Mixer Co         | ntrol Rec        | gister                                                                        |  |

| 1                              | 0          | 111              | x2               | Writes 02 to Address Control Register (selects the Mixer Control Register)    |  |

| 2                              | 1          | 101              | aa               | Mixer Control Register contents, aa, available on D <sub>7-0</sub> .          |  |

|                                |            |                  |                  | System modifies aa to get bb.                                                 |  |

| 3                              | 0          | 101              | bb               | Writes bb into Mixer Control Register                                         |  |

**Table 16. CLUT Read/Write Sequences**

| Step | R/W                                          | A <sub>2-0</sub> | D <sub>7-0</sub> | Function                                                                   |  |  |

|------|----------------------------------------------|------------------|------------------|----------------------------------------------------------------------------|--|--|

|      | -                                            | Writ             | e Entire A-      | Channel CLUT from Address 00                                               |  |  |

| 1    | 0                                            | 111              | 0x               | Selects A-CLUT for write.                                                  |  |  |

| 2    | 0                                            | 000              | 00               | Presets RAM Address Register to 00.                                        |  |  |

| 3    | 0                                            | 001              | r0               | r0 written into red (R/C <sub>R</sub> ) CLUT address 00.                   |  |  |

| 4    | 0                                            | 001              | g0               | g0 written into green (G/Y) CLUT address 00.                               |  |  |

| 5    | 0                                            | 001              | b0               | b0 written into blue (B/C <sub>B</sub> ) CLUT address 00.                  |  |  |

|      |                                              |                  |                  | repeat steps 3,4,5 until A-CLUT is full.                                   |  |  |

| 768  | 0                                            | 001              | r255             | r255 written into red (R/C <sub>R</sub> ) CLUT address FF.                 |  |  |

| 769  | 0                                            | 001              | g255             | g255 written into green (G/Y) CLUT address FF.                             |  |  |

| 770  | 0                                            | 001              | b255             | b255 written into blue (B/C <sub>B</sub> ) CLUT address FF.                |  |  |

|      | Write GBR Data to A-Overlay Location Address |                  |                  |                                                                            |  |  |

| 1    | 0                                            | 111              | 4x               | Select A-channel Overlay.                                                  |  |  |

| 2    | 0                                            | 000              | a <sub>n</sub>   | Write a <sub>n</sub> into RAM Address Register.                            |  |  |

| 3    | 0                                            | 001              | rn               | r <sub>n</sub> written into red (R/C <sub>R</sub> ) CLUT address.          |  |  |

| 4    | 0                                            | 001              | gn               | g <sub>n</sub> written into green (G/Y) CLUT address.                      |  |  |

| 5    | 0                                            | 001              | bn               | b <sub>n</sub> written into blue (B/C <sub>B</sub> ) CLUT address.         |  |  |

|      | 1                                            | W                | rite all αLU     | JT Locations starting from 00                                              |  |  |

| 1    | 0                                            | 111              | Сх               | Select αLUT.                                                               |  |  |

| 2    | 0                                            | 000              | FF               | Write FF into RAM Address Register (sets address to FF for pre-increment). |  |  |

| 3    | 0                                            | 001              | αα               | Write $\alpha\alpha$ to $\alpha$ LUT location 00.                          |  |  |

|      |                                              |                  |                  | Repeat step 3, 254 times for locations 01h-FEh.                            |  |  |

| 258  | 0                                            | 001              | ξζ               | Write ζζ, to αLUT location FF.                                             |  |  |

|      |                                              | Re               | ead All αLl      | JT Locations Starting from 00                                              |  |  |

| 1    | 0                                            | 111              | C6               | Select αLUT and Register 06 in Address Control Register.                   |  |  |

| 2    | 1                                            | 101              | aa               | Read Control Register 06.                                                  |  |  |

|      |                                              |                  |                  | bb = (aa OR 20h) to set bit 5.                                             |  |  |

| 3    | 0                                            | 101              | bb               | Restores aa with $\alpha$ LUT enabled.                                     |  |  |

| 4    | 0                                            | 011              | 00               | Write 00 into RAM Address Register (sets address to 00).                   |  |  |

| 5    | 1                                            | 001              | СС               | Read contents of $\alpha$ LUT, cc, from location 00.                       |  |  |

|      |                                              |                  |                  | Repeat step 5, 254 times for locations 01h-FEh.                            |  |  |

| 260  | 1                                            | 001              | ζζ               | Read contents of $\alpha$ LUT, $\zeta \zeta$ , from last location FF.      |  |  |

# **Pin Assignments**

## 128 Pin Plastic Quad Flat Pack (PQFP) Package

| Pin | Name              | Pin | Name              | Pin | Name              | Pin | Name            |

|-----|-------------------|-----|-------------------|-----|-------------------|-----|-----------------|

| 1   | D <sub>5</sub>    | 33  | PDA <sub>11</sub> | 65  | R/C <sub>R</sub>  | 97  | M <sub>22</sub> |

| 2   | D <sub>4</sub>    | 34  | PDA <sub>10</sub> | 66  | B/C <sub>B</sub>  | 98  | M <sub>21</sub> |

| 3   | D <sub>3</sub>    | 35  | PDAg              | 67  | AGND              | 99  | M <sub>20</sub> |

| 4   | D <sub>2</sub>    | 36  | PDA <sub>8</sub>  | 68  | G/Y               | 100 | M19             |

| 5   | D <sub>1</sub>    | 37  | PDA <sub>7</sub>  | 69  | COMP              | 101 | M18             |

| 6   | D <sub>0</sub>    | 38  | PDA <sub>6</sub>  | 70  | VDDA              | 102 | M17             |

| 7   | CS                | 39  | PDA <sub>5</sub>  | 71  | VDDA              | 103 | M16             |

| 8   | R/W               | 40  | PDA4              | 72  | PDB <sub>23</sub> | 104 | DGND            |

| 9   | A <sub>0</sub>    | 41  | PDA3              | 73  | PDB <sub>22</sub> | 105 | VDD             |

| 10  | A <sub>1</sub>    | 42  | PDA <sub>2</sub>  | 74  | PDB21             | 106 | M15             |

| 11  | A <sub>2</sub>    | 43  | PDA <sub>1</sub>  | 75  | PDB20             | 107 | M14             |

| 12  | SIG0              | 44  | PDA <sub>0</sub>  | 76  | PDB19             | 108 | M13             |

| 13  | PASSEN            | 45  | α8                | 77  | PDB18             | 109 | M <sub>12</sub> |

| 14  | AV                | 46  | α7                | 78  | PDB17             | 110 | M11             |

| 15  | OL <sub>3</sub>   | 47  | V <sub>DD</sub>   | 79  | PDB16             | 111 | M10             |

| 16  | $V_{DD}$          | 48  | DGND              | 80  | PDB15             | 112 | М9              |

| 17  | DGND              | 49  | α6                | 81  | PDB14             | 113 | Мв              |

| 18  | OL <sub>2</sub>   | 50  | α5                | 82  | PDB13             | 114 | M <sub>7</sub>  |

| 19  | OL <sub>1</sub>   | 51  | α4                | 83  | PDB12             | 115 | M <sub>6</sub>  |

| 20  | OL <sub>0</sub>   | 52  | αз                | 84  | PDB11             | 116 | M <sub>5</sub>  |

| _21 | PDA <sub>23</sub> | 53  | α2                | 85  | PDB10             | 117 | M <sub>4</sub>  |

| 22  | PDA <sub>22</sub> | 54  | α1                | 86  | PDB9              | 118 | Мз              |

| _23 | PDA <sub>21</sub> | 55  | α0                | 87  | PDB8              | 119 | M <sub>2</sub>  |

| 24  | PDA <sub>20</sub> | 56  | SMX <sub>2</sub>  | 88  | PDB7              | 120 | M <sub>1</sub>  |

| 25  | PDA <sub>19</sub> | 57  | SMX <sub>1</sub>  | 89  | PDB6              | 121 | M <sub>0</sub>  |

| 26  | PDA <sub>18</sub> | 58  | SMX <sub>0</sub>  | 90  | PDB5              | 122 | AVOUT           |

| 27  | PDA <sub>17</sub> | 59  | CLK               | 91  | PDB4              | 123 | PASS14          |

| 28  | PDA <sub>16</sub> | 60  | BLANK             | 92  | PDB3              | 124 | SIG14           |

| 29  | PDA <sub>15</sub> | 61  | SYNC              | 93  | PDB2              | 125 | DGND            |

| 30  | PDA <sub>14</sub> | 62  | VREF              | 94  | PDB1              | 126 | VDD             |

| 31  | PDA <sub>13</sub> | 63  | RREF              | 95  | PDB0              | 127 | D <sub>7</sub>  |

| 32  | PDA <sub>12</sub> | 64  | AGND              | 96  | M23               | 128 | D <sub>6</sub>  |

# **Pin Descriptions**

| Name                | Pin Number         | Value | Pin Function Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|---------------------|--------------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Clock               | -                  |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| CLK                 | 59                 | TTL   | <b>Clock Input.</b> TTL-compatible clock. All pixel data is registered on the rising edge of CLK. CLK synchronizes the flow of pixel data through the TMC2081 and the operation of the $\alpha$ -input.                                                                                                                                                                                                                                                                                   |

| Pixel I/O           |                    |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| PDA <sub>23-0</sub> | 21-44              | TTL   | <b>A-Channel Pixel Inputs.</b> A-channel pixel inputs are registered on the rising edge of CLK and specify which of the CLUT locations are addressed after masking. The CLUT in the A-Channel may be bypassed. PDA <sub>7-0</sub> are applied to all three CLUT sections when colorindex pixel data is used.                                                                                                                                                                              |

| PDB <sub>23-0</sub> | 72-95              | TTL   | <b>B-Channel Pixel Inputs.</b> B-channel pixel inputs are registered on the rising edge of CLK and are applied to the mixer after color-space conversion, and interpolation, if selected.                                                                                                                                                                                                                                                                                                 |

| α8-0                | 45,46,49-55        | TTL   | $\alpha$ -Channel Inputs. The $\alpha$ -channel inputs are registered on the rising edge of CLK and control proportional mixing at pixel rates up to 40 Mpps. $\alpha_8$ acts as a key input, switching A- and B-channel pixel data on a pixel-by-pixel basis. $\alpha_0$ is the LSB.                                                                                                                                                                                                     |

| SMX <sub>2-0</sub>  | 56-58              | TTL   | <b>ABF Crosspoint Mux Control.</b> When enabled by setting the SMX Control Register bits to 111, these inputs control the ABF Crosspoint Switch which directs the A- or B-channel pixels or the fill color register values to the $V_1$ or $V_2$ inputs to the mixer. SMX <sub>2-0</sub> input pins are ignored when the SMX Control Register bits are not 111. SMX <sub>2-0</sub> are registered on the rising edge of CLK. ABF Crosspoint Switch control is according to the following: |

|                     |                    |       | SMX <sub>2-0</sub> V <sub>1</sub> V <sub>2</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                     |                    |       | 000 A B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                     |                    |       | 001 A F                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                     |                    |       | 010 B A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                     |                    |       | 011 B F                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                     |                    |       | 100 F A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                     |                    |       | 101 F B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                     |                    |       | 110                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                     |                    |       | 111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| OL <sub>3-0</sub>   | 15,18-20           | TTL   | <b>Overlay Inputs.</b> Overlay inputs select one of 15 overlay colors from the PDA overlay palette. $OL_{3-0}$ are registered on the rising edge of CLK. When PDA or overlay is enabled and $OL_{3-0} > 0$ , the contents of the addressed palette are selected in place of the pixel data. Overlay is inactive when $OL_{3-0} = O_h$ or when disabled via the Control Registers. $OL_0$ is the LSB.                                                                                      |

| M <sub>23-0</sub>   | 96-103,<br>106-121 | TTL   | <b>Mixed Pixel Outputs.</b> Mixer output or digital preview of the $V_1$ and $V_2$ Crosspoint Switch outputs are synchronized to the rising edge of CLK. $M_{23-0}$ date is passed on for further processing (mixing, encoding, etc.). Pipeline latency is 14 clock cycles.                                                                                                                                                                                                               |

# Pin Descriptions (continued)

| Pin Number      | Value                                                         | Pin Function Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----------------|---------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ols             | !                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 13              | TTL                                                           | Pass Enable Input. Data selected by A/BPASS is enabled by PASSEN.                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 12              | TTL                                                           | Signal 0 Input. Input to a 14 CLK delay. Output is at SIG14.                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 123             | TTL                                                           | Pass Enable Output (14 Clock Delay). PASSEN delayed by 14 CLK cycles to match the pipeline latency of pixels                                                                                                                                                                                                                                                                                                                                                                                                |

| 124             | TTL                                                           | <b>Signal 0 Output (14 Clock Delay).</b> SIG0 delayed to match the 14 CLK cycles pipeline latency of pixels                                                                                                                                                                                                                                                                                                                                                                                                 |

| 14              | TTL                                                           | Active Video Input. When HIGH, AV enables data from the PDA and PDB ports. When LOW, at the $M_{23-0}$ output, GBR data is set to zero and YC <sub>B</sub> C <sub>R</sub> data is set to $10_h$ $80_h$ $80_h$ in the offset binary format and $10_h$ $00_h$ $00_h$ in 2's complement format. In the 422 mode, AV transitioning HIGH defines the next pixel to be the first C <sub>B</sub> pixel.                                                                                                            |

| 122             | TTL                                                           | <b>Delayed AV Output.</b> AV delayed by either 12 or 14 clock cycles. A 14 clock cycle delay matches the pipeline delay of the A and B channels. A 12 clock cycle delay is useful for interfacing with Fairchild Encoders.                                                                                                                                                                                                                                                                                  |

| 61              | TTL                                                           | Sync Enable for G/Y D/A. D/A Converter sync enable. SYNC = LOW, disables a current source at the G/Y output, forcing the sync tip to zero volts. SYNC = HIGH, activates the sync current at the G/Y output. SYNC is delayed either 2 or 15 clock cycles according to the status of the DACDLY bit. To disable sync on G/Y, ground SYNC.                                                                                                                                                                     |

| 60              | TTL                                                           | Blanking Control for D/As. D/A Converter blanking input. BLANK = LOW disables the data and pedestal output currents. If BLANK = HIGH, data and pedestal currents are added to the SYNC current. BLANK is delayed either 2 or 15 clock cycles according to the status of the DACDLY bit. For blank levels, see Tables 9, 10, 11, and 12.                                                                                                                                                                     |

| sor I/O         |                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 8               | TTL                                                           | <b>Read/Write Control.</b> Read-Write control input. $R/\overline{W}$ controls the direction of the $D_{7-0}$ port. If $R/\overline{W}$ = HIGH and $\overline{CS}$ is LOW, registers or CLUTs may be read. If $R/\overline{W}$ = LOW and $\overline{CS}$ = LOW, data may be written to control registers or CLUTs via the $D_{7-0}$ port. $R/\overline{W}$ is latched on the falling edge of $\overline{CS}$ .                                                                                              |

| 7               | TTL                                                           | <b>Chip Select.</b> Chip Select Input. If $\overline{CS}$ = HIGH, port, D <sub>7-0</sub> , is set to high-impedance. If $\overline{CS}$ = LOW, port D <sub>7-0</sub> is enabled. Read data (R/ $\overline{W}$ = HIGH) is enabled on the falling edge of $\overline{CS}$ . Write data is latched into the TMC2081 on the rising edge of the $\overline{CS}$ . CLUT, $\alpha$ LUT, or overlay read/write operations require $\overline{CS}$ to be HIGH for at least 4 CLK cycles after $\overline{CS}$ = LOW. |

| 11-9            | TTL                                                           | <b>Register Select Controls.</b> Address bits input. $A_{2-0}$ select registers or tables to be accessed (see Table 13) via $D_{7-0}$ . $A_{2-0}$ are latched on the falling edge of $\overline{CS}$ .                                                                                                                                                                                                                                                                                                      |

| 127,128,<br>1-6 | TTL                                                           | <b>Data I/O Port.</b> Bi-directional data port. $D_0$ is the LSB. Control Registers, CLUT, $\alpha$ LUT and Overlay locations are accessed via $D_{7-0}$ .                                                                                                                                                                                                                                                                                                                                                  |

| ıt              |                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 68              | 1 V P-P                                                       | <b>Green/Luminance Video.</b> The green/luminance analog video output. Sync pulses are included on this output.                                                                                                                                                                                                                                                                                                                                                                                             |

|                 | 0 = 1 / D D                                                   | Disc. 10 Video Disc. 10 constant                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 66              | 0.7 V P-P                                                     | Blue/C <sub>B</sub> Video. Blue/C <sub>B</sub> analog video output.  Red/C <sub>R</sub> Video. Red/C <sub>R</sub> analog video output.                                                                                                                                                                                                                                                                                                                                                                      |

|                 | 13 12 123 124 14 14 122 61 60 8sor I/O 8 11-9 127,128, 1-6 1t | 13 TTL  12 TTL  123 TTL  124 TTL  14 TTL  14 TTL  61 TTL  60 TTL  5sor I/O  8 TTL  7 TTL  11-9 TTL  127,128, 1-6                                                                                                                                                                                                                                                                                                                                                                                            |

# Pin Descriptions (continued)

| Name             | Pin Number    | Value   | Pin Function Description                                                                                                                                                                                                                                                                                                                           |

|------------------|---------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Reference        |               |         |                                                                                                                                                                                                                                                                                                                                                    |

| VREF             | 62            | +1.23 V | Voltage Reference Input/Output. An internal voltage source of +1.2 Volts (nominal) is applied to the VREF terminal. This is the reference for all three D/A converters of the TMC2081. Decoupling VREF to AGND with a $0.1\mu F$ ceramic capacitor is recommended. This pin may also be used as an input for an external voltage reference source. |

| RREF             | 63            | 681 Ω   | Current-Setting Resistor. Full-scale output current of the TMC2081 is determined by the value of the resistor connected between R <sub>REF</sub> and A <sub>GND</sub> . Varying this resistor will vary the "white" output level for all three D/A converters. The TMC2081 is not designed for operation with an external current reference.       |

| COMP             | 69            | 0.1 μF  | Compensation Capacitor. A 0.1 $\mu$ F ceramic capacitor is connected between the COMP and V <sub>DDA</sub> at pin 70 or 71.                                                                                                                                                                                                                        |

| Power, Grou      | ınd           |         |                                                                                                                                                                                                                                                                                                                                                    |

| V <sub>DDA</sub> | 70,71         | +5 V    | <b>Analog Power Supply.</b> The TMC2081 operates from a single +5V supply. All power pins must be connected. V <sub>DDA</sub> and V <sub>DD</sub> must be derived from a common power supply.                                                                                                                                                      |

| V <sub>DD</sub>  | 16,47,105,126 | +5 V    | <b>Digital Power Supply.</b> The TMC2081 operates from a single +5V supply. All power pins must be connected. V <sub>DDA</sub> and V <sub>DD</sub> must be derived from a common power supply.                                                                                                                                                     |

| AGND             | 64,67         | 0.0 V   | Analog Ground. All ground pins must be connected.                                                                                                                                                                                                                                                                                                  |

| D <sub>GND</sub> | 17,48,104,125 | 0.0 V   | Digital Ground. All ground pins must be connected.                                                                                                                                                                                                                                                                                                 |

# **Control Register Map**

| A-Channel Control Register  00 7 AOVLEN A-channel Overlay enable/disable  00 6 ADEC Decimator bypass/enable  00 5 AMAT A-channel GBR-to-YCBCR bypass/enable  00 4 CLUT Bypass/enable CLUT (power down)  00 3 AMSB Inverts CB/CR MSB  00 2 αGAIN Alpha Channel 9-/8-bit gain  00 1-0 AFORMAT A Pixel data path setup (4 formats)  B-Channel/Mixer Control Register  01 7 Reserved  01 6-5 MSOURCE M23-0 pixel source  01 4 BMAT Bypass/enable the B-channel YCBCR-to-GBR  01 3 BINT Bypass/enable Interpolator  01 2 BMSB Inverts CB/CR MSB  01 1-0 BFORMAT B Pixel data path setup (4 formats)  Mixer Control Register  02 7 MIXFMT Mixer format select  02 6-5 DSOURCE Selects data source for the internal D/A converters  02 4-2 SMX Chooses video source to be directed to the mixer imputs, V₁ and V₂  02 1-0 MIXTFN Used to alter the mixer transfer function  Fill Color Registers                                                                                                                                                                                                                                                                             |                            |     |              | ·                                          |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-----|--------------|--------------------------------------------|--|--|--|--|

| 00       7       AOVLEN       A-channel Overlay enable/disable         00       6       ADEC       Decimator bypass/enable         00       5       AMAT       A-channel GBR-to-YCBCR bypass/enable         00       4       CLUT       Bypass/enable CLUT (power down)         00       3       AMSB       Inverts CB/CR MSB         00       2       αGAIN       Alpha Channel 9-/8-bit gain         00       1-0       AFORMAT       A Pixel data path setup (4 formats)         B-Channel/Mixer Control Register         01       7       Reserved         01       7       Reserved         01       8 BMAT       Bypass/enable the B-channel YCBCR-to-GBR         01       3       BINT       Bypass/enable Interpolator         01       3       BINT       Bypass/enable Interpolator         01       2       BMSB       Inverts CB/CR MSB         01       1-0       BFORMAT       B Pixel data path setup (4 formats)         Mixer Control Register         02       7       MIXFMT       Mixer format select         02       7       MIXFMT       Mixer format select         02       4-2       SMX       Chooses v                                    | Reg                        | Bit | Name         | Function                                   |  |  |  |  |