Detects and Corrects Single-Bit Errors

- Detects and Flags Dual-Bit Errors

- Built-In Diagnostic Capability

- Fast Write and Read Cycle Processing Times

- Byte-Write Capability

- Dependable Texas Instruments Quality and Reliability

| DEVICE  | OUTPUT         |

|---------|----------------|

| 'ALS616 | 3-State        |

| 'ALS617 | Open-Collector |

#### description

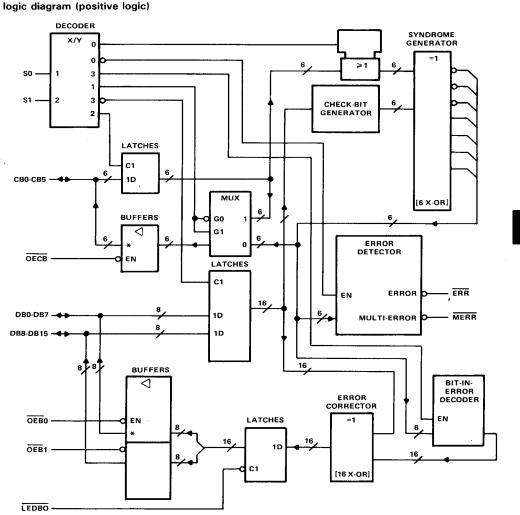

The 'ALS616 and 'ALS617 are 16-bit parallel error detection and correction circuits in 40-pin, 600-mil packages. The EDACs use a modified Hamming code to generate a 6-bit check word from a 16-bit data word. This check word is stored along with the data word during the memory write cycle. During memory read cycles, the 22-bit words from memory are processed by the EDACs to determine if errors have occurred in memory.

Single-bit errors in the 16-bit data word are flagged and corrected. Single-bit errors in the 6-bit check word are flagged, but the data word will remain unaltered. The 6-bit error syndrome code will pinpoint the error-generating location.

Dual-bit errors are flagged but not corrected. These errors may occur in any two bits of the 22-bit word from memory. The gross-error condition of all lows or all highs from memory will be detected. Otherwise, errors in three or more bits of the 22-bit word are beyond the capabilities of these devices to detect.

Read-modify-write (byte-control) operations can be performed with the 'ALS616 and 'ALS617 EDACs by using output latch enable, LEDBO, and individual OEBO and OEB1 byte control pins.

Diagnostics are performed on the EDACs by controls and internal paths that allow the user to read the contents of the DB and CB input latches. These will determine if the failure occurred in memory or in the EDAC.

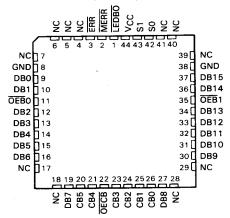

SN54ALS616, SN54ALS617 . . . JD PACKAGE SN74ALS616, SN74ALS617 . . . JD OR N PACKAGE

|         | (TOI        | P VIEW | ")            |

|---------|-------------|--------|---------------|

| LEDBO ( | ₫ī          | U40    | b vcc         |

| MERR (  | ₫2          | 39     |               |

| ERR (   | 3           | 38     | 🕽 so          |

| NC (    | וַ⊿         | 37     | □ NC          |

| NC (    | <b>5</b>    | 36     | □ NC          |

| NC I    | <b>4</b> 6  | 35     | □ NC          |

| GND     | ٦7          | 34     | GND           |

| NC      | <b>□</b> 8  | 33     | DB15          |

| DBO I   | <b>二</b> 9  | 32     | DB14          |

| DB1     | <b>4</b> 10 | 31     | OEB1          |

| OEBO I  | 1٠          | 30     | <b>D</b> DB13 |

| DB2     | <b>□</b> 1: | 2 29   | DB12          |

| DB3     | <b>口</b> 1: | 3 28   | D DB11        |

| DB4 l   | ٦ı          | 1 27   | D DB10        |

| DB5 l   | <b>1</b> 19 | 5 26   | D DB9         |

| DB6     | <b>□</b> 16 | 3 25   | D DB8         |

| DB7     | <b>口</b> 1: | 7 24   | 🗖 сво         |

| CB5     | <b>□</b> 18 | 3 23   | 🛛 СВ1         |

| CB4     | q۱۹         | 22     | CB2           |

| OECB    | <b>□</b> 20 | 21     | Свз           |

SN74ALS616, SN74ALS617 . . . FN PACKAGE (TOP VIEW)

NC-No internal connection

The SN54ALS616 and SN54ALS617 are characterized for operation over the full military temperature range of  $-55\,^{\circ}$ C to 125  $^{\circ}$ C. The SN74ALS616 and SN74ALS617 are characterized for operation from 0  $^{\circ}$ C to 70  $^{\circ}$ C.

This document contains information on products in more than one phase of development. The status of each device is indicated on the page(s) specifying its electrical characteristics.

Copyright © 1984, Texas Instruments Incorporated

2-69

#### TABLE 1. WRITE CONTROL FUNCTION

| MEMORY<br>CYCLE | EDAC<br>FUNCTION       | CON<br>S1 | TROL<br>SO | DATA I/O | DB CONTROL | DB OUTPUT LATCH | CHECK I/O                         | CB<br>CONTROL<br>OECB | ERROF<br>ERR | R FLAGS<br>MERR |

|-----------------|------------------------|-----------|------------|----------|------------|-----------------|-----------------------------------|-----------------------|--------------|-----------------|

| Write           | Generate<br>check word | L         | L          | Input    | н          | х               | Output<br>check bits <sup>†</sup> | L                     | н            | н               |

<sup>&</sup>lt;sup>†</sup>See Table 2 for details on check bit generation.

### memory write cycle details

During a memory write cycle, the check bits (CB0 thru CB5) are generated internally in the EDAC by six 8-input parity generators using the 16-bit data word as defined in Table 2. These six check bits are stored in memory along with the original 16-bit data word. This 22-bit word will later be used in the memory read cycle for error detection and correction.

**TABLE 2. PARITY ALGORITHM**

| CHECK WORD | 1  | 16-BIT DATA WORD |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|------------|----|------------------|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

| BIT        | 15 | 14               | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| CBO        | 1  |                  | X  |    | Х  | Х  | X |   |   | Х |   |   | Х |   | Х | Х |

| CB1        | 1  | X                |    | X  |    | X  | X | X |   |   |   | Х |   | X |   | X |

| CB2        | ×  |                  |    | X  | X  |    |   | Х | Х |   | X |   |   | Х | Х |   |

| CB3        | ×  | Х                | Х  |    |    |    | X | X |   |   | X | Х | Х |   |   |   |

| CB4        | ×  | Х                | Х  | X  | Х  | ×  |   |   | Χ | X |   |   |   |   |   |   |

| CB5        | 1  |                  |    |    |    |    |   |   | Х | X | Χ | Х | X | X | X | Х |

The six check bits are parity bits derived from the matrix of data bits as indicated by "X" for each bit.

#### error detection and correction details

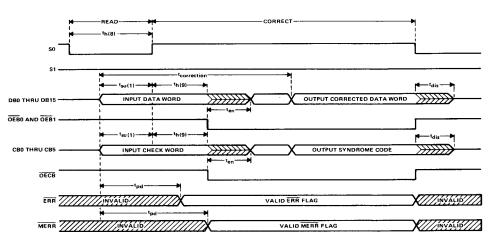

During a memory read cycle, the 6-bit check word is retrieved along with the actual data. In order to be able to determine whether the data from memory is acceptable to use as presented to the bus, the error flags must be tested to determine if they are at the high level.

The first case in Table 3 represents the normal, no-error conditions. The EDAC presents highs on both flags. The next two cases of single-bit errors give a high on  $\overline{ exttt{MERR}}$  and a low on  $\overline{ exttt{ERR}}$ , which is the signal for a correctable error, and the EDAC should be sent through the correction cycle. The last three cases of double-bit errors will cause the EDAC to signal lows on both ERR and MERR, which is the interrupt indication for the CPU.

TABLE 3. ERROR FUNCTION

| TOTAL NUMB       | ER OF ERRORS     | ERROF | RFLAGS | DATA CORRECTION |  |  |  |  |  |  |  |  |

|------------------|------------------|-------|--------|-----------------|--|--|--|--|--|--|--|--|

| 16-BIT DATA WORD | 6-BIT CHECK WORD | ERR   | MERR   | DATA CORRECTION |  |  |  |  |  |  |  |  |

| 0                | 0                | Н     | н      | Not applicable  |  |  |  |  |  |  |  |  |

| 1                | 0                | L     | Н      | Correction      |  |  |  |  |  |  |  |  |

| 0                | 1                | L     | Н      | Correction      |  |  |  |  |  |  |  |  |

| 1                | 1                | L     | L      | Interrupt       |  |  |  |  |  |  |  |  |

| 2                | 0                | L     | L      | Interrupt       |  |  |  |  |  |  |  |  |

| 0                | 2                | L     | L      | Interrupt       |  |  |  |  |  |  |  |  |

| TABLE A | DEAD | EL AG | AND | CODDECT | FUNCTION |

|---------|------|-------|-----|---------|----------|

|         |      |       |     |         |          |

| MEMORY<br>CYCLE | EDAC<br>FUNCTION                                 | CON<br>S1 | TROL<br>SO | DATA I/O                         | DB CONTROL OEBO & OEB1 | DB OUTPUT LATCH | CHECK I/O                               | CB<br>CONTROL<br>OECB | ERROR FLAGS<br>ERR MERR |

|-----------------|--------------------------------------------------|-----------|------------|----------------------------------|------------------------|-----------------|-----------------------------------------|-----------------------|-------------------------|

| Read            | Read & flag                                      | Н         | L          | Input                            | н                      | X               | Input                                   | H                     | Enabled <sup>†</sup>    |

| Read            | Latch input<br>data & check<br>bits              | н         | н          | Latched<br>input<br>data         | н                      | L               | Latched<br>input<br>check word          | н                     | Enabled <sup>†</sup>    |

| Read            | Output<br>corrected data<br>and<br>syndrome bits | Н         | н          | Output<br>corrected<br>data word | L                      | ×               | Output<br>syndrome<br>bits <sup>‡</sup> | Ĺ                     | Enabled <sup>†</sup>    |

<sup>&</sup>lt;sup>†</sup>See Table 3 for error description.

Error detection is accomplished as the 6-bit check word and the 16-bit data word from memory are applied to the internal parity generators/checkers. If the parity of all six groupings of data and check bits are correct, it is assumed that no error has occurred and both error flags will be high.

If the parity of one or more of the check groups is incorrect, an error has occurred and the proper error flag or flags will be set low. The two-bit error is not correctable since the parity tree can only identify single-bit errors. Both error flags are set low when any two-bit error is detected.

Three or more simultaneous bit errors can cause the EDAC to believe that no error, a correctable error, or an uncorrectable error has occurred and will produce erroneous results in all three cases. It should be noted that the gross-error conditions of all highs will be detected.

As the corrected word is made available on the data I/O port (DB0 thru DB15), the check word I/O port (CB0 thru CB5) presents a 6-bit syndrome error code. This syndrome code can be used to locate the bad memory chip. See Table 5 for syndrome decoding.

<sup>&</sup>lt;sup>‡</sup>See Table 5 for error location.

TABLE 5. SYNDROME DECODING

| SY | NDI | RON | ΛE | віт | S | ERROR |

|----|-----|-----|----|-----|---|-------|

| 5  | 4   | 3   | 2  | 1   | 0 | ENNON |

| L  | L   | L   | L  | L   | L | 2-bit |

| L  | L   | L   | L  | L   | н | unc   |

| L  | L   | L   | L  | Н   | Ł | unc   |

| L  | L.  | L   | L  | Н   | Н | 2-bit |

| L  | L   | Ļ   | Н  | Ł   | L | unc   |

| L  | L   | L   | н  | L   | н | 2-bit |

| L  | L   | L   | н  | н   | L | 2-bit |

| L  | L   | L   | H  | Н   | н | unc , |

| ┖  | L   | Н   | L  | L   | L | unc   |

| L  | L   | Н   | L  | L   | Н | 2-bit |

| L  | L   | Н   | L  | Н   | L | 2-bit |

| L  | L   | Н   | L  | н   | Н | DB7   |

| L  | L   | H   | Н  | L   | Ł | 2-bit |

| L  | L   | Н   | Н  | L   | Н | unc   |

| L  | L   | Н   | Н  | Н   | L | DB6   |

| L  | L   | н   | Н  | Н   | н | 2-bit |

| SY | ND | RON | ΛE | BIT | s | ERROR |

|----|----|-----|----|-----|---|-------|

| 5  | 4  | 3   | 2  | 1   | ٥ | ERROR |

| L  | Н  | L   | L  | L   | ۲ | unc   |

| L  | н  | L   | L  | L   | н | 2-bit |

| L  | Н  | L   | L  | н   | L | 2-bit |

| Ļ  | Н  | L   | L  | Н   | н | DB5   |

| L  | Н  | L   | Н  | L   | L | 2-bit |

| L  | Н  | L   | н  | L   | н | DB4   |

| L  | Н  | L   | н  | н   | L | DB3   |

| L  | Н  | L   | н  | Н   | H | 2-bit |

| L  | Н  | Н   | L  | L   | L | 2-bit |

| L  | Н  | Н   | L  | L   | Н | DB2   |

| Ł  | Н  | н   | L  | н   | L | DB1   |

| L  | Н  | Н   | L. | н   | Н | 2-bit |

| L  | Н  | Н   | Н  | L   | L | DB0   |

| L  | н  | н   | н  | Ł   | н | 2-bit |

| L  | Н  | н   | н  | Н   | L | 2-bit |

| L  | Н  | Н   | н  | Н   | Н | CB5   |

| SY | NDI | ROP | s | ERROR |   |       |

|----|-----|-----|---|-------|---|-------|

| 5  | 4   | 3   | 2 | 1     | 0 | Limon |

| Н  | L   | L   | L | L     | L | unc   |

| Н  | L   | L   | L | L     | н | 2-bit |

| н  | L   | L   | L | н     | L | 2-bit |

| н  | L   | L   | L | н     | Н | DB15  |

| Н  | L   | L   | Н | L     | L | 2-bit |

| H  | L   | L   | Н | L     | н | DB14  |

| н  | L   | L   | Н | н     | L | DB13  |

| Н  | L   | L   | Н | н     | н | 2-bit |

| Н  | L   | Н   | L | L     | L | 2-bit |

| н  | L   | н   | L | L     | н | DB12  |

| н  | L   | н   | L | н     | Ł | DB11  |

| н  | L   | Н   | L | Н     | н | 2-bit |

| Н  | L   | Н   | Н | L     | L | DB10  |

| н  | L   | н   | н | L     | Н | 2-bit |

| н  | L   | Н   | Н | н     | L | 2-bit |

| Н  | L   | Н   | H | н     | Н | CB4   |

| SY | NDO | ORI | ΛE | BIT | s | ERROR |

|----|-----|-----|----|-----|---|-------|

| 5  | 4   | 3   | 2  | 1   | 0 | Linon |

| Н  | н   | L   | L  | L   | L | 2-bit |

| Н  | Н   | L   | L  | L   | н | DB8   |

| н  | н   | L   | L  | н   | L | unc   |

| Ι  | н   | L   | L  | н   | н | 2-bit |

| Н  | Н   | L   | Н  | L   | L | DB9   |

| н  | Н   | L   | Н  | L   | Н | 2-bit |

| н  | н   | L   | н  | н   | L | 2-bit |

| Н  | н   | L   | Н  | Н   | н | CB3   |

| Н  | Н   | Н   | L  | L   | L | unc   |

| Н  | Н   | Н   | L  | L   | Н | 2-bit |

| н  | н   | Н   | L  | Н   | L | 2-bit |

| Η  | Н   | Н   | L  | Н   | Н | CB2   |

| Н  | Н   | Н   | Η  | L   | L | 2-bit |

| Н  | н   | Н   | н  | L   | Н | CB1   |

| Н  | Н   | Н   | Н  | Н   | L | СВО   |

| н  | Н   | Н   | Н  | Н   | Н | none  |

CB X = error in check bit X

DB Y = error in data bit Y 2-bit = double-bit error

unc = uncorrectable multibit error

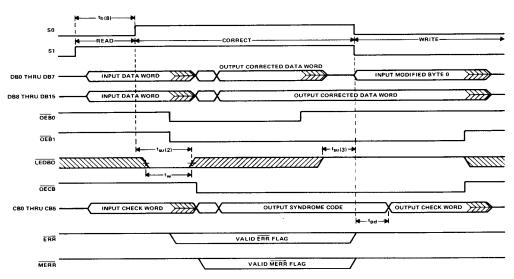

## read-modify-write (byte control) operations

The 'ALS616 and 'ALS617 devices are capable of byte-write operations. The 22-bit word from memory must first be latched into the DB and CB input latches. This is easily accomplished by switching from the read and flag mode (S1 = H, S0 = L) to the latch input mode (S1 = H, S0 = H). The EDAC will then make any corrections, if necessary, to the data word and place it at the input of the output data latch. This data word must then be latched into the output data latch by taking  $\overline{\text{LEDBO}}$  from a low to a high.

Byte control can now be employed on the data word through the  $\overline{\text{OEB0}}$  or  $\overline{\text{OEB1}}$  controls.  $\overline{\text{OEB0}}$  controls DB0-DB7 (byte 0),  $\overline{\text{OEB1}}$  controls DB8-DB15 (byte 1).

Placing a high on the byte control will disable the output and the user can modify the byte. If a low is placed on the byte control, then the original byte is allowed to pass onto the data bus unchanged. If the original data word is altered through byte control, a new check word must be generated before it is written back into memory. This is easily accomplished by taking control S1 and S0 low. Table 6 lists the read-modify-write functions.

| TARIER | DEAD | MODIFY-WRITE | ELIMOTION |

|--------|------|--------------|-----------|

|        |      |              |           |

| MEMORY<br>CYCLE  | EDAC FUNCTION                                                       | CON<br>S1 | TROL<br>SO | BYTEn <sup>†</sup>                          | ŌĒBn† | DB OUTPUT<br>LATCH<br>LEDBO | CHECK I/O                          | CB<br>CONTROL | ERROR FLAG |

|------------------|---------------------------------------------------------------------|-----------|------------|---------------------------------------------|-------|-----------------------------|------------------------------------|---------------|------------|

| Read             | Read & Flag                                                         | Н         | L          | Input                                       | Н     | ×                           | Input                              | Н             | Enabled    |

| Read             | Latch input data<br>& check bits                                    | н         | н          | Latched<br>Input<br>data                    | н     | L                           | Latched<br>input<br>check word     | н             | Enabled    |

| Read ,           | Latch corrected<br>data word into<br>output latch                   | н         | н          | Latched<br>output<br>data<br>word           | ιн    | Н                           | Hi-Z<br>Öutput<br>Syndrome<br>bits | L<br>L        | Enabled    |

| Modify/<br>write | Modify appropriate<br>byte or bytes &<br>generate new<br>check word | L         | L          | Input modified BYTEO Output unchanged BYTEO | H<br> | Н                           | Output<br>check word               | L             | н н        |

<sup>†</sup>OEBO controls DBO-DB7 (BYTEO), OEB1 controls DB8-DB15 (BYTE1)

### diagnostic operations

The 'ALS616 and 'ALS617 are capable of diagnostics that allow the user to determine whether the EDAC or the memory is failing. The diagnostic function tables will help the user to see the possibilities for diagnostic control.

In the diagnostic mode (S1 = L, S0 = H), the checkword is latched into the input latch while the data input latch remains transparent. This lets the user apply various data words against a fixed known checkword. If the user applies a diagnostic data word with an error in any bit location, the  $\overline{ERR}$  flag should be low. If a diagnostic data word with two errors in any bit location is applied, the  $\overline{MERR}$  flag should be low. After the checkword is latched into the input latch, it can be verified by taking  $\overline{OECB}$  low. This outputs the latched checkword. The diagnostic data word can be latched into the output data latch and verified via the  $\overline{LEDBO}$  control pin. By changing from the diagnostic mode (S1 = L, S0 = H), the user can verify that the EDAC will correct the diagnostic data word. Also, the syndrome bits can be produced to verify that the EDAC pinpoints the error location. Table 7 lists the diagnostic functions.

#### TABLE 7. DIAGNOSTIC FUNCTION

| EDAC FUNCTION                                                              | 1 | TROL<br>SO | DATA I/O                                       | DB BYTE<br>CONTROL<br>OEBn | DB OUTPUT<br>LATCH<br>LEDBO | CHECK I/O                          | CB<br>CONTROL<br>OECB                     | ERROR FLAGS |

|----------------------------------------------------------------------------|---|------------|------------------------------------------------|----------------------------|-----------------------------|------------------------------------|-------------------------------------------|-------------|

| Read & flag                                                                | н | L          | Input correct<br>data word                     | н                          | х                           | Input correct check bits           | Н                                         | нн          |

| Latch input check<br>word while data<br>input latch remains<br>transparent | L | н          | Input<br>diagnostic<br>data word <sup>†</sup>  | н                          | L                           | Latched<br>input<br>check bits     | н                                         | Enabled     |

| Latch diagnostic<br>data word into<br>output latch                         | L | н          | Input<br>diagnostic<br>data word <sup>†</sup>  | н                          | н                           | Output latched check bits Hi-Z     | L                                         | Enabled     |

| Latch diagnostic<br>data word into<br>input latch                          | н | н          | Latched<br>input<br>diagnostic<br>data word    | н                          | н                           | Output syndrome bits Hi-Z          | L<br>———————————————————————————————————— | Enabled     |

| Output diagnostic data word & syndrome bits                                | н | н          | Output<br>diagnostic<br>data word              | L                          | н                           | Output<br>syndrome<br>bits<br>Hi-Z | L<br>                                     | Enabled     |

| Output corrected diagnostic data word & output syndrome bits               | н | н          | Output<br>corrected<br>diagnostic<br>data word | L                          | L                           | Output<br>syndrome<br>bits<br>Hi-Z | L<br>                                     | Enabled     |

<sup>†</sup>Diagnostic data is a data word with an error in one bit location except when testing the MERR error flag. In this case, the diagnostic data word will contain errors in two bit locations.

<sup>\*&#</sup>x27;ALS616 has 3-state (♥) check-bit and data outputs.

'ALS617 has open-collector(♠) check-bit and data outputs.

## absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

| Supply voltage, Vcc (see Note 1)      |                                         |

|---------------------------------------|-----------------------------------------|

|                                       | 5.5 V                                   |

|                                       |                                         |

| Operating case temperature range      | SN54ALS616, SN54ALS617, 55 °C to 125 °C |

| Operating free-air temperature range. | SN74ALS616, SN74ALS617 0 °C to 70 °C    |

| Storage temperature range             | -65°C to 150°C                          |

## recommended operating conditions

|                   |                             |                                                                            |      | 154ALS |      |     | 74ALS6 |                                                           | UNIT |

|-------------------|-----------------------------|----------------------------------------------------------------------------|------|--------|------|-----|--------|-----------------------------------------------------------|------|

|                   |                             |                                                                            | MIN  | NOM    | MAX  | MIN | NOM    | 17<br>MAX<br>5.5<br>0.8<br>5.5<br>-0.4<br>-2.6<br>8<br>24 |      |

| Vcc               | Supply voltage              |                                                                            | 4.5  | 5      | 5.5  | 4.5 | 5      | 5.5                                                       | V    |

| VIH               | High-level input voltage    |                                                                            | 2    |        |      | 2   |        |                                                           | V    |

| VIL               | Low-level input voltage     |                                                                            |      |        | 0.8  |     |        | 0.8                                                       | V    |

| VoH               | High-level output voltage   | DB or CB 'ALS617                                                           |      |        | 5.5  |     |        | 5.5                                                       | V    |

| 9.11              |                             | ERR or MERR                                                                |      |        | -0.4 |     |        | -0.4                                                      | mA   |

| ЮН                | High-level output current   | DB or CB /ALS616                                                           |      |        | - 1  |     |        | - 2.6                                                     | IIIA |

|                   |                             | ERR or MERR                                                                |      |        | 4    |     |        | 8                                                         |      |

| loL               | Low-level output current    | DB or CB                                                                   |      |        | 12   |     |        | 24                                                        | mA   |

| t                 | Pulse duration              | LEDBO low                                                                  | 45   |        |      | 25  |        |                                                           | ns   |

| ·w                | 1 0.00                      | (1) Data and check word before S01<br>(S1 = H)                             | 15   |        | .,   | 12  |        |                                                           |      |

|                   |                             | (2) S0 high before LEDBO↑ (S1 = H)†                                        | † 45 |        |      | 45  |        |                                                           |      |

|                   |                             | (3) LEDBO high before the earlier of                                       | 0    |        |      | 0   |        |                                                           |      |

|                   |                             | (4) LEDBO high before S11 (S0 = H)                                         | 0    |        |      | 0   |        |                                                           | ns   |

| <sup>t</sup> su   | Setup time                  | (5) Diagnostic data word before S11 (S0 = H)                               | 28   |        |      | 12  |        |                                                           | ] "" |

| VOH I             |                             | (6) Diagnostic check word before the later of S11 or S01                   | 15   |        |      | 12  |        |                                                           |      |

|                   |                             | (7) Diagnostic data word before<br>LEDBO† (S1 = L and S0 = H) <sup>†</sup> | 35   |        |      | 20  |        | 17<br>MAX<br>5.5<br>0.8<br>5.5<br>-0.4<br>-2.6<br>8       |      |

|                   |                             | (8) Read-mode, S0 low and S1 high                                          | 35   |        |      | 30  |        |                                                           | 1    |

|                   |                             | (9) Data and check word after SO†<br>(S1 = H)                              | 20   |        |      | 15  |        |                                                           | ] .  |

|                   |                             | (10) Data word after S1↑ (S0 = H)                                          | 20   |        |      | 15  |        |                                                           | ns   |

| th                | Hold time                   | (11) Check word after the later of S1↓ or S0↑                              | 20   |        |      | 15  |        |                                                           |      |

|                   |                             | (12) Diagnostic data word after  LEDBO† (S1 = L, S0 = H) ‡                 | 0    |        |      | 0   |        |                                                           |      |

| t <sub>corr</sub> | Correction time (see Figure | 1)                                                                         | 70   |        | 1    | 65  |        |                                                           | ns   |

| TC                | Operating case temperature  | 3                                                                          | - 55 |        | 125  |     |        |                                                           | °C   |

| TA                | Operating free-air temperat | ure                                                                        |      |        |      | 0   |        | 70                                                        | 200  |

<sup>&</sup>lt;sup>†</sup>These times ensure that corrected data is saved in the output data latch.

<sup>&</sup>lt;sup>‡</sup>These times ensure that the diagnostic data word is saved in the output data latch.

## SN54ALS616, SN74ALS616 16-BIT PARALLEL ERROR DETECTION AND CORRECTION CIRCUITS

## 'ALS616 electrical characteristics over recommended operating temperature range (unless otherwise noted)

| P    | ARAMETER              | TEST CO                       | PINDITIONS                     |      | N54AL! | S616 ' | S<br>MIN | N74ALS |                                                                            | UNIT   |

|------|-----------------------|-------------------------------|--------------------------------|------|--------|--------|----------|--------|----------------------------------------------------------------------------|--------|

| VIK  |                       | VCC = 4.5 V,                  | l <sub>j</sub> = -18 mA        | T    |        | -1.5   |          |        | - 1.5                                                                      | >      |

|      | All outputs           | V <sub>CC</sub> = 4.5 V to 5. | 5 V, I <sub>OH</sub> = -0.4 mA | Vcc- | 2      |        | Vcc-     | 2      |                                                                            |        |

| Vон  |                       | V <sub>CC</sub> = 4.5 V,      | IOH = -1 mA                    | 2.4  | 3.3    |        |          |        |                                                                            | V      |

| •    | DB or CB              | V <sub>CC</sub> = 4.5 V,      | IOH = -2.6 mA                  |      |        |        | 2.4      | 3.2    | 0.4<br>0.5<br>0.4<br>0.5<br>0.1<br>0.1<br>20<br>20<br>-0.4<br>-0.1<br>-112 |        |

| VOL  | ERR or MERR           | $V_{CC} = 4.5 \text{ V},$     | IOH = 4 mA                     |      | 0.25   | 0.4    |          | 0.25   | 0.4                                                                        |        |

|      |                       | V <sub>CC</sub> = 4.5 V,      | IOL = 8 mA                     |      |        |        |          | 0.35   | 0.5                                                                        | l v    |

|      |                       | V <sub>CC</sub> = 4.5 V.      | I <sub>OL</sub> = 12 mA        | •    | 0.25   | 0.4    |          | 0.25   | 0.4                                                                        | ٧      |

|      | DB or CB              | V <sub>CC</sub> = 4.5 V,      | IOL = 24 mA                    |      |        |        |          | 0.35   | 0.4<br>0.5<br>0.4<br>0.5<br>0.1<br>0.1<br>20<br>20<br>-0.4                 |        |

|      | SO or S1              | V <sub>CC</sub> = 5.5 V,      | V <sub>1</sub> = 7 V           |      |        | 0.1    |          |        | 0.1                                                                        | mA     |

| կ    | DB or CB              | V <sub>CC</sub> = 5.5 V.      | V <sub>I</sub> = 5.5 V         |      |        | 0.1    |          |        | 0.1                                                                        |        |

|      | SO or S1              |                               |                                |      |        | 20     |          |        | 20                                                                         | μA     |

| ΙΗ   | DB or CB <sup>‡</sup> | $V_{CC} = 5.5 V$              | $V_i = 2.7 V$                  |      |        | 20     |          |        | 20                                                                         | μ.     |

|      | \$0 or \$1            |                               | V 04V                          |      |        | -0.4   |          |        | -0.4                                                                       | mA     |

| ΉL   | DB or CB <sup>‡</sup> | V <sub>CC</sub> = 5.5 V,      | $V_1 = 0.4 V$                  |      | -      | -0.1   |          |        | -0.1                                                                       | I IIIA |

| 10 5 |                       | V <sub>CC</sub> = 5.5 V.      | V <sub>Q</sub> = 2.25 V        | - 30 |        | -112   | - 30     |        | -112                                                                       | mA     |

| lcc  |                       | V <sub>CC</sub> = 5.5 V       | See Note 1                     | 1    | 110    | 190    |          | 110    | 170                                                                        | mA     |

# 'ALS616 switching characteristics, VCC = 4.5 V to 5.5 V, CL = 50 pF, TC = -55 °C to 125 °C for SN54ALS616, TA = 0 °C to 70 °C for SN74ALS616

| PARAMETER        | FROM           | то       |                                        | SN54ALS616 |     | SN74ALS616 ' |                                   | UNIT |

|------------------|----------------|----------|----------------------------------------|------------|-----|--------------|-----------------------------------|------|

| PARAMETER        | (INPUT)        | (OUTPUT) | TEST CONDITIONS                        | MIN        | MAX | MIN          | MAX 40 40 55 55 49 30 50 27 27 27 | Cres |

|                  | DB and CB      | ERR      | S1=H, S0=L, R <sub>L</sub> =500 Ω      | 10         | 43  | 10           | 40                                | ns   |

| <sup>t</sup> pd  | DB             | ERR      | S1 = L, S0 = H, R <sub>L</sub> = 500 Ω | 10         | 43  | 10           | 40                                |      |

|                  | DB and CB      | MERR     | S1 = H, S0 = L, R <sub>L</sub> = 500 Ω | 15         | 65  | 15           | 55                                | ns   |

| <sup>t</sup> pd  | D8             | MERR     | S1 = L, S0 = H, $R_L = 500 \Omega$     | 15         | 65  | 15           | 55                                | 113  |

| tpd              | SOI and S1I    | СВ       | R1 = R2 = 500 Ω                        | 10         | 60  | 10           | 49                                | ns.  |

| t <sub>pd</sub>  | DB             | СВ       | S1 = L, S0 = L, R1 = R2 = 500 Ω        | 10         | 60  | 10           | 49                                | ns   |

| t <sub>pd</sub>  | LEDBO1         | DB       | S1 = X, S0 = H, R1 = R2 = 500 Ω        | 7          | 35  | 7            | 30                                | ns   |

| t <sub>pd</sub>  | S11            | СВ       | SO = H, R1 = R2 = 500 Ω                | 10         | 50  | 10           | 50                                | ns   |

| t <sub>en</sub>  | OECB1          | СВ       | \$0 = H, \$1 = X, R1 = R2 = 500 Ω      | 2          | 30  | 2            | 27                                | ns   |

| <sup>t</sup> dis | <u>O€CB</u> †  | СВ       | SO=H, S1=X, R1=R2=500 Ω                | 2          | 30  | 2            | 27                                | ns   |

| ten              | OEBO and OEB11 | DB       | S0=H, S1=X, R1=R2=500 Ω                | 2          | 30  | 2            | 27                                | ns   |

| <sup>t</sup> dis | OEBO and OEB1↑ | DB       | SO=H, S1=X, R1=R2= 500 Ω               | 2          | 30  | 2            | 27                                | ns   |

PRODUCTION DATA documents contain information current as of publication data. Products conform to specifications per the terms of Texas instruments stendard werranty. Production processing does not necessarily include testing of all parameters.

2-77

$<sup>^{\</sup>dagger}$  All typical values are at VCC = 5 V, TA = 25 °C.  $^{\ddagger}$  For I/O ports, the parameters  $I_{1H}$  and  $I_{1L}$  include the off-state output current.

The output conditions have been chosen to produce a current that closely approximates one half of the true short-circuit output current, IQS. NOTE 1: ICC is measured with SO and S1 at 4.5 V and all CB and DB pins grounded.

## 'ALS617 electrical characteristics over recommended operating temperature range (unless otherwise noted)

|      |                       |                               |                                 | SN                 | 54ALS | 517   | SN                 | 74ALS6           | 17    |                |

|------|-----------------------|-------------------------------|---------------------------------|--------------------|-------|-------|--------------------|------------------|-------|----------------|

| P    | ARAMETER              | TEST CO                       | TEST CONDITIONS                 |                    |       | MAX   | MIN                | TYP <sup>†</sup> | MAX   | UNIT           |

| VIK  |                       | V <sub>CC</sub> = 4.5 V,      | I <sub>I</sub> = -18 mA         |                    |       | - 1.5 |                    |                  | - 1.5 | V              |

| Vон  | ERR or MERR           | V <sub>CC</sub> = 4.5 V to 5. | 5 V, $I_{OH} = -0.4 \text{ mA}$ | V <sub>CC</sub> -2 |       |       | V <sub>CC</sub> -2 |                  |       | V              |

| 10н  | DB or CB              | $V_{CC} = 4.5 \text{ V},$     | V <sub>OH</sub> = 5.5 V         |                    |       | 0.1   |                    |                  | 0.1   | mA             |

| VOL  |                       | $V_{CC} = 4.5 \text{ V},$     | loH = 4 mA                      |                    | 0.25  | 0.4   |                    | 0.25             | 0.4   |                |

|      | ERR or MERR           | V <sub>CC</sub> = 4.5 V,      | I <sub>OL</sub> = 8 mA          |                    |       |       |                    | 0.35             | 0.5   | l <sub>v</sub> |

|      |                       | V <sub>CC</sub> = 4.5 V,      | IOL = 12 mA                     |                    | 0.25  | 0.4   |                    | 0.25             | 0.4   |                |

|      | DB or CB              | V <sub>CC</sub> = 4.5 V,      | I <sub>OL</sub> = 24 mA         |                    |       |       |                    | 0.35             |       |                |

|      | SO or S1              | V <sub>CC</sub> = 5.5 V,      | V <sub>I</sub> = 7 V            |                    |       | 0.1   | 1                  |                  | 0.1   | mA             |

| Ц    | DB or CB              | V <sub>CC</sub> = 5.5 V,      | V <sub>I</sub> = 5.5 V          |                    |       | 0.1   |                    |                  | 0.1   | IUA            |

|      | S0 or S1              | 1                             |                                 |                    |       | 20    |                    |                  | 20    | μΑ             |

| ۱н   | DB or CB <sup>‡</sup> | $V_{CC} = 5.5 V$ ,            | $V_1 = 2.7 V$                   |                    |       | 20    |                    |                  | 20    | μΑ             |

|      | S0 or S1              |                               |                                 | 1.                 |       | -0.4  |                    |                  | -0.4  | mA             |

| ΊL   | DB or CB <sup>‡</sup> | $V_{CC} = 5.5 V,$             | V <sub> </sub> = 0.4 V          |                    |       | -0.1  |                    |                  | - 0.1 | IIIA.          |

| IO § | ERR or MERR           | V <sub>CC</sub> = 5.5 V,      | V <sub>O</sub> = 2.25 V         | - 30               |       | -112  | - 30               |                  | -112  | mA             |

| lcc  | L                     | V <sub>CC</sub> = 5.5 V       | See Note 1                      |                    | 110   |       |                    | 110              |       | mA             |

$<sup>^{\</sup>dagger}AII$  typical values are at  $V_{CC}~=~5$  V,  $T_{A}~=~25\,^{o}C.$

‡For I/O ports, the parameters I<sub>IH</sub> and I<sub>IL</sub> include the off-state output current.

§The output conditions have been chosen to produce a current that closely approximates one half of the true short-circuit output current, IOS. NOTE 1: ICC is measured with S0 and S1 at 4.5 V and all CB and DB pins grounded.

## 'ALS617 switching characteristics, $V_{CC} = 4.5 \text{ V}$ to 5.5 V, $C_L = 50 \text{ pF}$ , $T_{C} = -55 ^{\circ}\text{C}$ to 125 $^{\circ}\text{C}$ for SN54ALS617, $T_A = 0$ °C to 70°C for SN74ALS617

|                 | FROM           | то       |                                               | SN54ALS617   | SN74ALS617   | UNIT |

|-----------------|----------------|----------|-----------------------------------------------|--------------|--------------|------|

| PARAMETER       | (INPUT)        | (OUTPUT) | TEST CONDITIONS                               | MIN TYPT MAX | MIN TYPT MAX |      |

|                 | DB and CB      | ERR      | S1 = H, S0 = L, R <sub>L</sub> = 500 $\Omega$ | 26           | 26           | ns   |

| <sup>t</sup> pd | DB             | ERR      | S1 = L, S0 = H, $R_L = 500 \Omega$            | 26           | 26           |      |

|                 | 55 165         | MERR     | S1 = H, S0 = L, $R_L = 500 \Omega$            | 40           | 40           | ns   |

| <sup>t</sup> pd | DB and CB      | WERK     | S1 = L, S0 = H, $R_L$ = 500 $\Omega$          | 40           | 40           |      |

| t <sub>pd</sub> | S0↓ and S1↓    | СВ       | $R_L = 680 \Omega$                            | 40           | 40           | ns   |

| <sup>t</sup> pd | DB             | СВ       | S1 = L, S0 = L, $R_L = 680 \Omega$            | 40           | 40           | ns   |

| tpd             | <u>LEDBO</u> ↓ | DB       | S1 = X, S0 = H, R <sub>L</sub> = 680 $\Omega$ | 26           | 26           | ns   |

| t <sub>pd</sub> | S11            | СВ       | SO = H, R <sub>L</sub> = 680 Ω                | 40           | 40           | ns   |

| tPLH            | <u>OECB</u> ↑  | СВ       | S1 = X, S0 = H, $R_L = 680 \Omega$            | 24           | 24           | ns   |

| tPHL            | <u>OECB</u> 1  | СВ       | S1 = X, S0 = H, $R_L$ = 680 $\Omega$          | 24           | 24           | ns   |

| tPLH            | OEB0 and OEB1↑ | DB       | S1 = X, S0 = H, R <sub>L</sub> = 680 $\Omega$ | 24           | 24           | ns   |

| tPHL            | OEBO and OEB1↓ | DB       | S1 = X, S0 = H, $R_L$ = 680 $\Omega$          | 24           | 24           | ns   |

$<sup>^{\</sup>dagger}$ All typical values are at  $V_{CC}$  = 5 V,  $T_{A}$  = 25 °C.

Additional information on these products can be obtained from the factory as it becomes available.

PRODUCT PREVIEW documents contain information on products in the formative or design phase of development. Characteristic data and other specifications are design goals. Texas Instruments reserves the right to change or discontinue these products without notice.

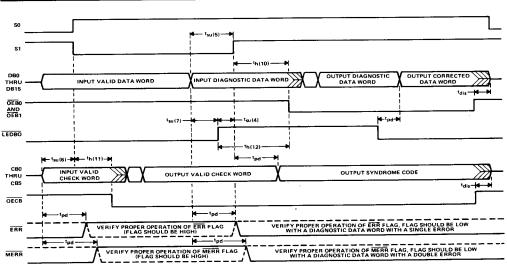

FIGURE 1. READ, FLAG, AND CORRECT MODE SWITCHING WAVEFORMS

FIGURE 2. READ, CORRECT, MODIFY MODE SWITCHING WAVEFORMS

FIGURE 3. DIAGNOSTIC MODE SWITCHING WAVEFORM