# Diagnostic-quality acquisition system for bio-electric sensors and bio-impedance measurements

Datasheet - preliminary data

#### **Features**

- 3 biopotential acquisition channels with integrated analog high pass filters

- 1 bio-impedance measurement channel with 2or 4-wire measurement

- Digital IQ demodulation

- Integrated configurable digital filtering and preprocessing

- Pacemaker pulse acquisition with embedded detection function (down to 0.1 mV impulse amplitude)

- Input connection matrix allows support for different cable configurations

- SPI daisy chain supports up to 4 ICs connection

- Programmable analog gain: 8, 16, 32, 64

- Low supply voltage: 1.62 V to 3.6 V

- Input referred noise: 6 μV<sub>PP</sub> (300 Hz BW, G=64)

- Maximum data rate: 125 kSPS per channel

- Less than 1 mA/channel at full bandwidth and resolution

- DC and AC lead-off detection

- Right leg driver (RLD), Wilson common terminal (WCT) and shield driver (SD)

- Clock reconfigurability

- Built-in ring oscillator (±5% accuracy)

- Built-in crystal oscillator (±0.1% accuracy)

- External clock

- · Low external component count architecture

- Allows compliance with medical standards ANSI/AAMI EC11, ANSI/AAMI EC13 and IEC60601-2-27

- EMI tolerant

#### **Applications**

- · ECG (electrocardiogram)

- · Carts for clinical environments

- Bedside monitoring

- Holter monitors

- Automated external defibrillator (AED)

- EEG (electroencephalogram)

- EMG (electromyography)

- Wearable remote monitoring

- Medical equipment

**Table 1. Device summary**

| Order code | Order code Biopotential channels |     | Bio-impedance channel Marking |             | Packaging |  |

|------------|----------------------------------|-----|-------------------------------|-------------|-----------|--|

| HM301DL    | 3                                | Yes | HM301D                        | LGA 6x6 40L | Tray      |  |

Contents HM301D

### **Contents**

| 1    | Descr  | ription .         |                                                  | . 7 |  |  |  |  |

|------|--------|-------------------|--------------------------------------------------|-----|--|--|--|--|

| 2    | Block  | diagran           | n                                                | . 8 |  |  |  |  |

| 3    | Pin co | Pin configuration |                                                  |     |  |  |  |  |

| 4    | Maxin  | num rati          | ngs                                              | 11  |  |  |  |  |

| 5    |        |                   | racteristics                                     |     |  |  |  |  |

| 6    | Detail | ed desc           | ription                                          | 16  |  |  |  |  |

|      | 6.1    | Overviev          | v                                                | 16  |  |  |  |  |

|      | 6.2    | input cor         | nnection matrix                                  | 17  |  |  |  |  |

|      | 6.3    | Biopoter          | ntial channel                                    | 18  |  |  |  |  |

|      |        | 6.3.1             | Analog section                                   | 18  |  |  |  |  |

|      |        | 6.3.2             | Digital section                                  | 20  |  |  |  |  |

|      |        | 6.3.3             | High resolution low bandwidth signal path (HRLB) | 21  |  |  |  |  |

|      |        | 6.3.4             | Low resolution high bandwidth signal path (LRHB) | 21  |  |  |  |  |

|      | 6.4    | Lead off          | detection                                        | 22  |  |  |  |  |

|      |        | 6.4.1             | DC contact check                                 | 23  |  |  |  |  |

|      |        | 6.4.2             | AC contact check                                 | 23  |  |  |  |  |

|      | 6.5    | Impedan           | ice channel                                      | 24  |  |  |  |  |

| -0// |        | 6.5.1             | Analog section                                   | 25  |  |  |  |  |

| 050  |        | 6.5.2             | Digital section                                  | 25  |  |  |  |  |

|      | 6.6    | Drivers           |                                                  | 26  |  |  |  |  |

|      |        |                   | Right leg driver                                 |     |  |  |  |  |

|      |        |                   | Shield driver                                    |     |  |  |  |  |

|      |        |                   | Wilson common terminal (WCT)                     |     |  |  |  |  |

|      | 6.7    | TM and            | RST pin configuration                            | 28  |  |  |  |  |

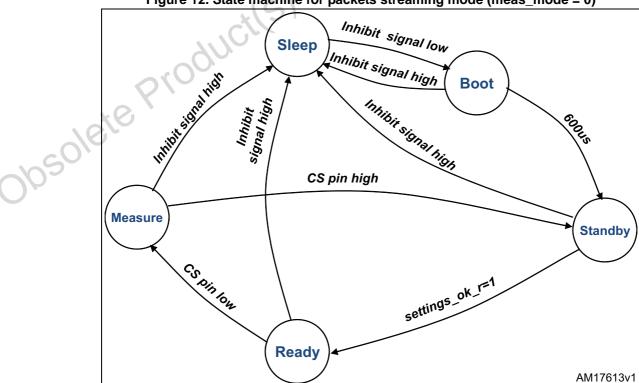

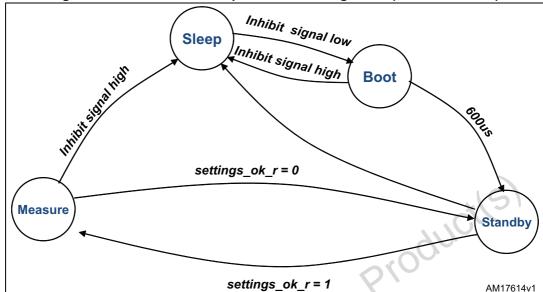

|      | 6.8    | •                 | achine                                           |     |  |  |  |  |

|      |        |                   | Operating modes                                  | 29  |  |  |  |  |

|      |        |                   | Sleep                                            |     |  |  |  |  |

|      |        |                   | Boot                                             |     |  |  |  |  |

|      |        | 6.8.4             | Standby                                          | 29  |  |  |  |  |

|     |       | 6.8.5    | Ready                                           | 30 |

|-----|-------|----------|-------------------------------------------------|----|

|     |       | 6.8.6    | Measure                                         | 30 |

|     |       | 6.8.7    | Fast recovery                                   | 31 |

|     | 6.9   | GPIO c   | onfiguration                                    | 32 |

|     | 6.10  | SPI inte | erface                                          | 36 |

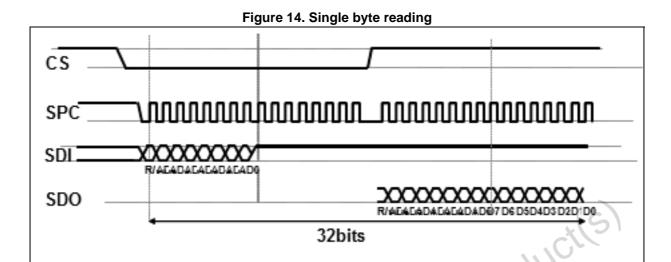

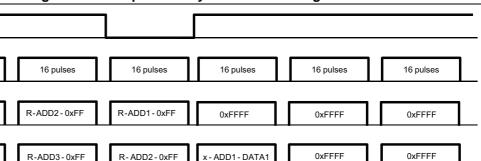

|     |       | 6.10.1   | SPI read                                        | 36 |

|     |       | 6.10.2   | SPI write                                       | 37 |

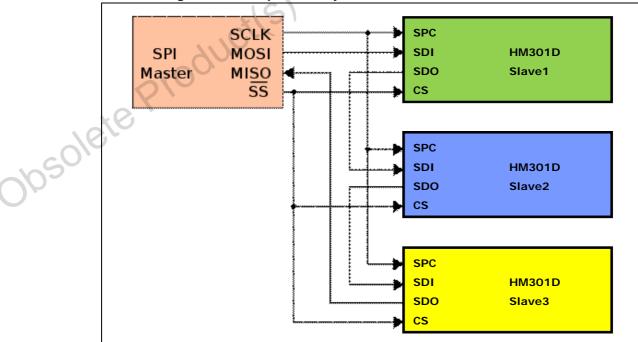

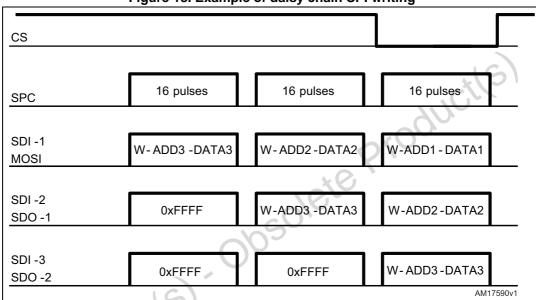

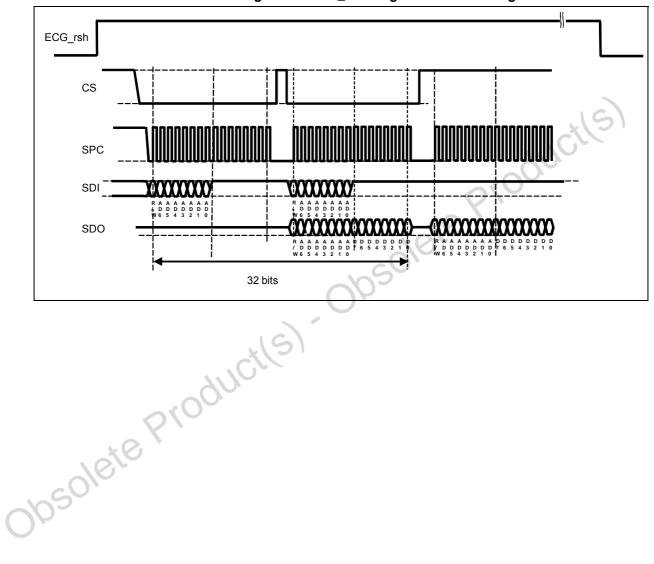

|     |       | 6.10.3   | Daisy chain SPI                                 | 38 |

|     |       | 6.10.4   | SPI timing                                      |    |

|     | 6.11  |          | supply voltage monitor                          |    |

|     | 6.12  | Registe  | ers MAP                                         | 42 |

|     |       | 6.12.1   | Application settings (Read/Write)               | 46 |

|     |       | 6.12.2   | Output flags (read only)                        | 60 |

|     |       | 6.12.3   | Data registers (readable only if MEAS_MODE = 1) | 61 |

|     | 6.13  | Output   | data format                                     | 69 |

|     |       | 6.13.1   | Case 1: complete processed data - 4x packet     | 70 |

|     |       | 6.13.2   | Case 2: pre-filtered data out - 3x packet       | 71 |

|     |       | 6.13.3   | Header description                              | 72 |

|     | 6.14  | Data ra  | te                                              | 74 |

|     | 6.15  | Data re  | ady operation                                   | 75 |

| 7   | Appli | cation I | nformation                                      | 77 |

|     | 7.1   | DC offs  | et removal                                      | 77 |

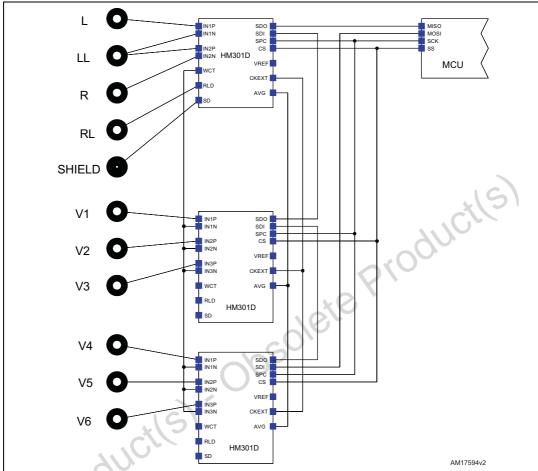

|     | 7.2   | Multi-ch | nip configuration                               | 78 |

| G0/ | 7.3   | Suppor   | ted ECG configurations                          | 80 |

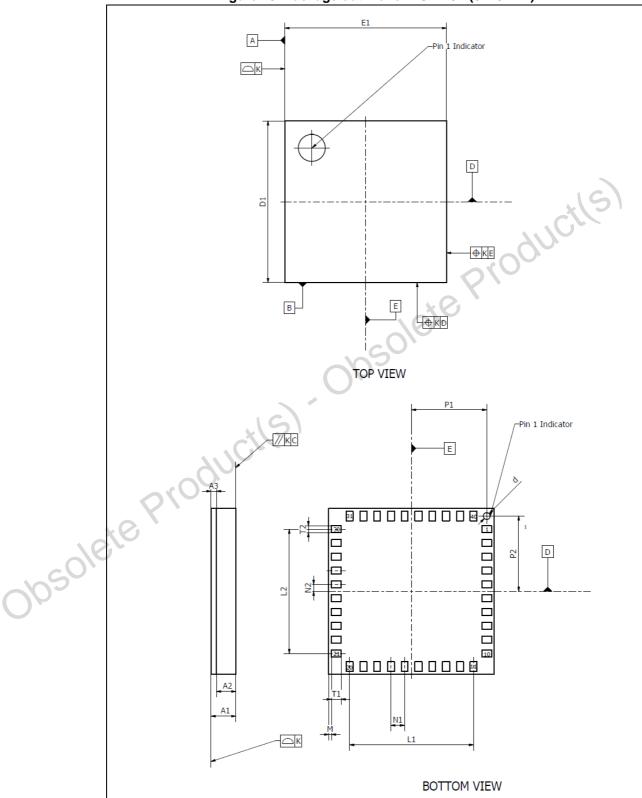

| 8   | Packa | age med  | chanical data                                   | 81 |

| ۵   | Rovie | ion his  | tory                                            | 84 |

List of tables HM301D

### List of tables

| Table 1.             | Device summary                                                                            | 4  |

|----------------------|-------------------------------------------------------------------------------------------|----|

| Table 1.             | Pin description                                                                           |    |

| Table 2.             | Absolute maximum ratings                                                                  |    |

| Table 3.             | Thermal data                                                                              |    |

| Table 4.<br>Table 5. | Electrical characteristics                                                                |    |

|                      |                                                                                           |    |

| Table 6.             | Input-referred noise (µV <sub>RMS</sub> /µV <sub>PP</sub> ) / 3 V analog supply 1         |    |

| Table 7.             | Input connection matrix                                                                   |    |

| Table 8.             | Pad connection settings                                                                   |    |

| Table 9.             | Biopotential channel gain and IDR                                                         |    |

| Table 10.            | Functional modes                                                                          | 29 |

| Table 11.            | Digital GPIO output signals (DGIO0)                                                       |    |

| Table 12.            | Digital GPIO output signals (DGIO1)                                                       | 33 |

| Table 13.            | Digital GPIO output signals (DGIO2)                                                       | 34 |

| Table 14.            | Digital GPIO input signals                                                                | 36 |

| Table 15.            | Read command bytes                                                                        | 3/ |

| Table 16.            | vvrite command byte                                                                       | 38 |

| Table 17.            | Write command byte  SPI slave timings (IOVDD = 1.8 V).  Psmon_out signal.  Registers MAP. | 41 |

| Table 18.            | Psmon_out signal                                                                          | 42 |

| Table 19.            | Registers MAP                                                                             | 42 |

| Table 20.            | Registers war                                                                             | 44 |

| Table 21.            | Data registers (readable only if meas_mode bit is 1)                                      |    |

| Table 22.            | SET0 CH_ENABLE (ADDR 27h)                                                                 |    |

| Table 23.            | SET1 PM_SEL (ADDR 28h)                                                                    |    |

| Table 24.            | SET 2 AVG_CTRL (ADDR 29h)                                                                 |    |

| Table 25.            | SET3 INCON_HCSEL_1 (2Ah)                                                                  |    |

| Table 26.            | SET4 INCON_HCSEL_2 (2Bh)                                                                  |    |

| Table 27.            | SET5 INCON_HCSEL_3 (2Ch)                                                                  |    |

| Table 28.            | SET6 INCON_AVG_1 (2Dh)                                                                    |    |

| Table 29.            | SET7 INCON_AVG_2 (2Eh)                                                                    |    |

| Table 30.            | SET8 INCON_RLD (2Fh)                                                                      |    |

| Table 31.            | SET9 CCK_EN_1 (30h)                                                                       |    |

| Table 32.            | SET10 CCK_EN_2 (31h)                                                                      |    |

| Table 33.            | SET11 CCK_CUR (32h)                                                                       |    |

| Table 34.            | SET12 CCK_TRSH (33h)                                                                      |    |

| Table 35.            | SET13 HC_ANA_CTRL (34h)                                                                   | 53 |

| Table 36.            | SET14 IMP_ANA_CTRL (35h)                                                                  |    |

| Table 37.            | SET15 ECG_DIGFILT_CTRL (36h)                                                              |    |

| Table 38.            | SET16 PM_DIGFILT_CTRL (37h)                                                               |    |

| Table 39.            | SET17 HC_DIGFILT_CTRL (38h)                                                               |    |

| Table 40.            | SET18 HC_HPFANA_CTRL (39h)                                                                |    |

| Table 41.            | SET19 RLD_CTRL (3Ah)                                                                      |    |

| Table 42.            | SET20 RECOVERY_TIME (3Bh)                                                                 |    |

| Table 43.            | SET21 PMD_TRSH (3Ch)                                                                      |    |

| Table 44.            | SET22 FILTER_SWTIME (3Dh)                                                                 |    |

| Table 45.            | SET23 DIGIO_IO (40h)                                                                      |    |

| Table 46.            | SET24 IMP_CUR_EN (44h)                                                                    |    |

| Table 47.            | SET25 DIGIO12_SEL (45h)                                                                   |    |

| Table 48.            | SET26 DIGIO0 SEL (46h)                                                                    |    |

|                      |                                                                                           |    |

HM301D List of tables

| Table 49. | OUT FLAG0 (47h)                                                            | . 60 |

|-----------|----------------------------------------------------------------------------|------|

| Table 50. | OUT_FLAG1 (48h)                                                            | . 60 |

| Table 51. | ECG1_DATAOUT_1 (49h)                                                       |      |

| Table 52. | CG1_DATAOUT_0 (4Ah)                                                        | . 61 |

| Table 53. | ECG2_DATAOUT_1 (4Bh)                                                       |      |

| Table 54. | ECG2_DATAOUT_0 (4Ch)                                                       |      |

| Table 55. | ECG3_DATAOUT_1 (4Dh)                                                       |      |

| Table 56. | ECG3_DATAOUT_0 (4Eh)                                                       | . 62 |

| Table 57. | ECG12_DATAOUT_1 (4Fh)                                                      | . 63 |

| Table 58. | ECG12_DATAOUT_0 (50h)                                                      | . 63 |

| Table 59. | ECG23_DATAOUT_1 (51h)                                                      |      |

| Table 60. | ECG23_DATAOUT_0 (52h)                                                      | . 64 |

| Table 61. | ECG31_DATAOUT_1 (53h)                                                      | . 64 |

| Table 62. | ECG31_DATAOUT_0 (54h)                                                      | . 64 |

| Table 63. | PM1_DATAOUT_1 (55h)                                                        | . 65 |

| Table 64. | PM1_DATAOUT_1 (55h)                                                        | . 65 |

| Table 65. | PM2_DATAOUT_1 (57h)                                                        | . 65 |

| Table 66. | PM2_DATAOUT_0 (58h)                                                        | . 66 |

| Table 67. | IMPEDANCE PHASE AC DATAOUT 1 (59n)                                         | . 66 |

| Table 68. | IMPEDANCE_PHASE_AC_DATAOUT_0 (5Ah)                                         | . 66 |

| Table 69. | IMPEDANCE_PHASE_AC_DATAOUT_0 (5Ah)                                         | . 67 |

| Table 70. | IMPEDANCE_SQUARING_AC_DATAOUT_0 (5Ch)                                      | . 67 |

| Table 71. | IMPEDANCE_PHASE_DC_DATAOUT_1 (5Dh)                                         | . 67 |

| Table 72. | IMPEDANCE_PHASE_DC_DATAOUT_0 (5Eh)                                         |      |

| Table 73. | IMPEDANCE_SQUARING_DC_DATAOUT_1 (5Fh)                                      |      |

| Table 74. | IMPEDANCE_SQUARING_DC_DATAOUT_0 (60h)                                      |      |

| Table 75. | CONTACT_CHECK_DATAOUT_1 (61h)                                              |      |

| Table 76. | CONTACT_CHECK_DATAOUT_0 (62h)                                              |      |

| Table 77. | Data format                                                                |      |

| Table 78. | Base pocket                                                                |      |

| Table 79. | Data packet out with 3 HM301D in chain                                     |      |

| Table 80. | Pre-filtered data out                                                      |      |

| Table 81. | Header packet bits description in 4x packet case                           |      |

| Table 82. | Header packet bits description in 3x packet case                           |      |

| Table 83. | C_DATA packet description bits configurations                              |      |

| Table 84. | Contact check and overflow C_DATA vector                                   |      |

| Table 85. | HRLB data-out sampling frequency vs low pass filter cut-off frequency      |      |

| Table 86. | LRHB data-out sampling frequency vs low pass filter cut-off frequency      |      |

| Table 87. | Impedance data-out sampling frequency vs low pass filter cut-off frequency |      |

| Table 88. | Common ECG configurations                                                  |      |

| Table 89. | LGA 40L (6 x 6 mm) mechanical data                                         | . 83 |

| Table 90  | Document revision history                                                  | 84   |

List of figures HM301D

## **List of figures**

| Figure | 1. HM301D block diagram                                 | 8 |

|--------|---------------------------------------------------------|---|

| Figure | 2. Pin configuration (top view)                         | 9 |

| Figure |                                                         |   |

| Figure | 4. First decimation filter                              | 0 |

| Figure | 5. HRLB digital signal path                             | 1 |

| Figure |                                                         | 2 |

| Figure |                                                         | 3 |

| Figure | 8. Impedance channel architecture                       | 4 |

| Figure | 9. Impedance channel digital section                    | 6 |

| Figure |                                                         |   |

| Figure |                                                         |   |

| Figure |                                                         |   |

| Figure | · · · · · · · · · · · · · · · · · · ·                   |   |

| Figure | 14. Single byte reading                                 | 7 |

| Figure | 14. Single byte reading315. Double byte reading3        | 7 |

| Figure |                                                         | 8 |

| Figure | 17. Example of daisy chain SPI connection with 3 HM301D | 8 |

| Figure |                                                         | 9 |

| Figure | 19. Example of daisy chain SPI reading                  | 0 |

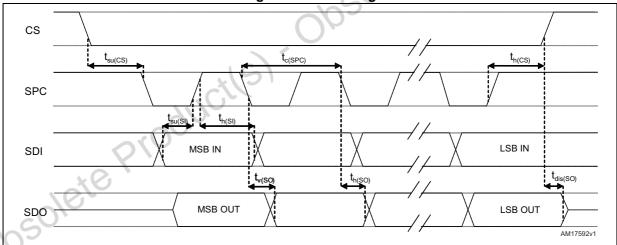

| Figure | 20. SPI timing                                          | 1 |

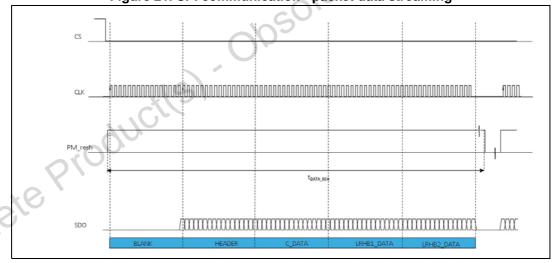

| Figure | 21. SPI communication - packet data streaming           | 5 |

| Figure |                                                         |   |

| Figure |                                                         |   |

| Figure | 24. Example of chain connection: standard 12-lead ECG   | 9 |

| Figure | 25. Package outline for LGA 40L (6 x 6 mm)              | 2 |

| 005    | 24. Example of chain connection: standard 12-lead ECG   |   |

|        |                                                         |   |

HM301D Description

### 1 Description

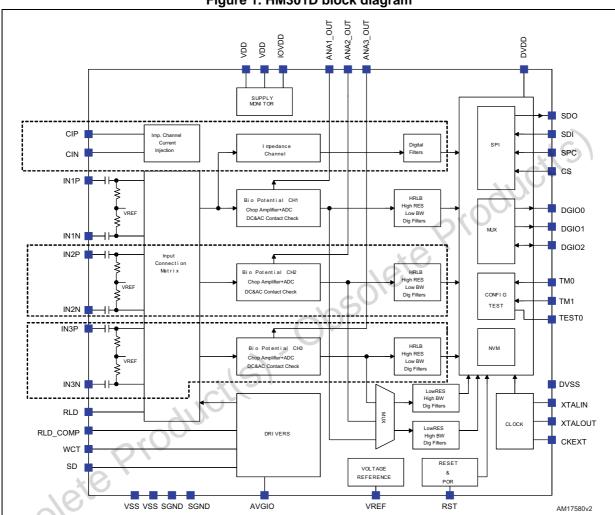

The HM301D is a highly integrated diagnostic-quality biopotential acquisition system with 3 differential channels. Multi master/slave configuration supports up to 16 channels of simultaneous sampling (12 biopotential acquisitions and 4 bio-impedance channels). A fully integrated high-pass filter removes the half-cell DC value to enable the channels to work with the AC component only. Each channel provides high resolution and low noise conversion of biopotential signals up to 10 kHz.

The input connection circuit matrix guarantees maximum flexibility in terms of electrode cables and connectors.

The HM301D includes a dedicated impedance measurement channel that can be used to measure both body impedance average value and variation due to respiration. This channel delivers both the real and the imaginary parts of the body and the breathing impedances. The WCT circuit and driver block implements the driving functions (right leg driver and shield driver) and the Wilson common terminal commonly used in ECG systems.

The electrode-to-skin contact is checked by injecting an AC or DC current. A digital filtering and preprocessing (DFP) block implements configurable band-pass filters, IQ impedance demodulation and enables specific algorithm implementation for lead-off check and pacemaker detection.

The SPI interface allows the exchange of data with both the microcontroller and other HM301D devices in case of chain connection. Full configurability and low power design techniques make it ideal for many applications, including battery-powered devices. High quality recordings are obtained with a small, power-saving system. The 3-channel version is available in a 6 x 6 mm 40-lead LGA.

**Block diagram** HM301D

#### **Block diagram** 2

Figure 1. HM301D block diagram

HM301D Pin configuration

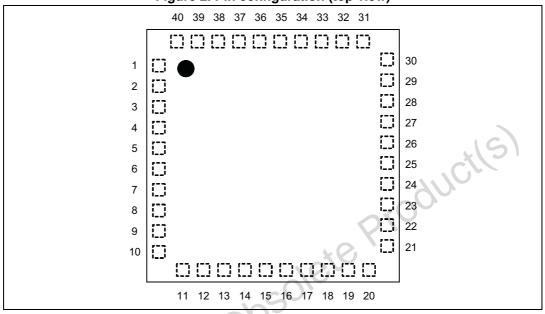

## 3 Pin configuration

Figure 2. Pin configuration (top view)

Table 2. Pin description

| Pin name | Pin n° | Туре    | Description                                                                                              |  |

|----------|--------|---------|----------------------------------------------------------------------------------------------------------|--|

| IN1P     | 1      | ANA IN  | Connected to biopotential channel #1 positive input by default. See input connection matrix to change it |  |

| IN1N     | 2      | ANA IN  | Connected to biopotential channel #1 negative input by default. See input connection matrix to change it |  |

| VDD      | 3      | ANA IN  | Analog supply voltage                                                                                    |  |

| IN2P     | 4      | ANA IN  | Connected to biopotential channel #2 positive input by default. See input connection matrix to change it |  |

| IN2N     | 5      | ANA IN  | Connected to biopotential channel #2 negative input by default. See input connection matrix to change it |  |

| VSS      | 6      | ANA GND | Analog ground                                                                                            |  |

| IN3P     | 7      | ANA IN  | Connected to biopotential channel #3 positive input by default. See input connection matrix to change it |  |

| IN3N     | 8      | ANA IN  | Connected to biopotential channel #3 negative input by default. See input connection matrix to change it |  |

| RLD      | 9      | ANA OUT | Connected to Right Leg Driver output by default. See input connection matrix to change it                |  |

| WCT      | 10     | ANA OUT | Wilson Common Terminal output                                                                            |  |

| RLD_COMP | 11     | ANA IO  | Input of RLD buffer. To be used for compensation in case of instability of RLD loop                      |  |

Pin configuration HM301D

Table 2. Pin description (continued)

| Pin name | Pin n° | Туре    | Description (Continued)                                                                                 |

|----------|--------|---------|---------------------------------------------------------------------------------------------------------|

| AVGIO    | 12     | ANA IO  | Average value of electrode signals connected to ASSP (O) or coming from other chain connected ASSPs (I) |

| SD       | 13     | ANA OUT | Driver output of shield cables                                                                          |

| ANA1_OUT | 14     | ANA OUT | Channel1 single ended analog output                                                                     |

| ANA2_OUT | 15     | ANA OUT | Channel2 single ended analog output                                                                     |

| ANA3_OUT | 16     | ANA OUT | Channel3 single ended analog output                                                                     |

| TEST0    | 17     | ANA IO  | Used for TEST purposes. Leave float in normal operation                                                 |

| VSS      | 18     | ANA GND | Analog ground                                                                                           |

| VDD      | 19     | ANA IN  | Analog supply voltage                                                                                   |

| VREF     | 20     | ANA IO  | Reference voltage to or from other chain connected ASSPs                                                |

| XTALOUT  | 21     | ANA OUT | Crystal pin connection                                                                                  |

| XTALIN   | 22     | ANA IN  | Crystal pin connection                                                                                  |

| SGND     | 23     | ANA GND | Analog ground                                                                                           |

| DVDD     | 24     | ANA IN  | Digital supply voltage                                                                                  |

| CKEXT    | 25     | DIG IO  | Clock signal to/from other devices                                                                      |

| RST      | 26     | DIG OUT | POR (when TM0 = TM1 = 0)                                                                                |

| Kol      | 26     | DIG IN  | Enable (when TM0 = 1, TM1 = 0)                                                                          |

| TM0      | 27     | DIG IN  | Configuration pin # 1                                                                                   |

| TM1      | 28     | DIG IN  | Configuration pin # 2                                                                                   |

| DVSS     | 29     | DIG GND | Digital ground                                                                                          |

| SDO      | 30     | DIG OUT | SPI Serial Data Output                                                                                  |

| IOVDD    | 31     | ANA IN  | Supply voltage for IO pins. It provides the voltage to SPI and GPIOs it must be always lower than VDD.  |

| SDI      | 32     | DIG IN  | SPI Serial Data Input                                                                                   |

| cs       | 33     | DIG IN  | SPI Chip Select                                                                                         |

| SPC      | 34     | DIG IN  | SPI Serial Port Clock                                                                                   |

| DGIO2    | 35     | DIG IO  | General purpose digital IO                                                                              |

| DGIO1    | 36     | DIG IO  | General purpose digital IO                                                                              |

| DGIO0    | 37     | DIG IO  | General purpose digital IO                                                                              |

| SGND     | 38     | ANA GND | Analog ground                                                                                           |

| CIN      | 39     | ANA OUT | AC Current Injection Negative pin for Impedance Measurement                                             |

| CIP      | 40     | ANA OUT | AC Current Injection Positive pin for Impedance Measurement                                             |

10/85

HM301D Maximum ratings

## 4 Maximum ratings

Table 3. Absolute maximum ratings

| Symbol            | Parameter                    | Value <sup>(1)</sup> | Unit |

|-------------------|------------------------------|----------------------|------|

| V <sub>DD</sub>   | Analog Supply Voltage        | -0.3 to 4.8          | V    |

| DV <sub>DD</sub>  | Digital Supply Voltage       | -0.3 to 4.8          | V    |

| IOV <sub>DD</sub> | IOs supply voltage           | -0.3 to 4.8          | V    |

| Analog I/O        | All analog IOs               | -0.3 to 4.8          | V    |

| Digital I/O       | All digital IOs              | -0.3 to 4.8          | V    |

| T <sub>OP</sub>   | Operating temperature range  | -40 to 100           | °C   |

| T <sub>ST</sub>   | Storage Temperature Range    | -65 to 150           | °C   |

| T <sub>J</sub>    | Maximum Junction Temperature | +150                 | °C   |

| 500               | НВМ                          | ±2                   | kV   |

| ESD               | CDM                          | 500                  | V    |

<sup>1.</sup> All values are referred to VSS.

Note:

Absolute maximum ratings are those values beyond which damage to the device may occur. Functional operation under these conditions is not implied.

Table 4. Thermal data

|      | Symbol            | Parameter                              | Value | Unit |

|------|-------------------|----------------------------------------|-------|------|

|      | R <sub>THJA</sub> | Junction to ambient thermal resistance | 55    | °C/W |

| 0/6  |                   |                                        |       |      |

| Open |                   |                                        |       |      |

Electrical characteristics HM301D

### 5 Electrical characteristics

$T_A$  = 0 to 70 °C,  $V_{DD}$  =  $DV_{DD}$  =  $IOV_{DD}$  = 3 V,  $V_{REF}$  = 0.7 V, unless otherwise specified.

**Table 5. Electrical characteristics**

| Symbol                                                    | Parameter                                    | Test conditions                                 | Min.           | Тур.          | Max            | Unit |

|-----------------------------------------------------------|----------------------------------------------|-------------------------------------------------|----------------|---------------|----------------|------|

| General                                                   | section                                      |                                                 |                |               |                |      |

| AV <sub>DD</sub><br>IOV <sub>DD</sub><br>DV <sub>DD</sub> | Supply voltages                              |                                                 | 1.62           |               | 3.6            | V    |

|                                                           |                                              | Power down mode                                 |                | 10            | C              | μΑ   |

|                                                           |                                              | 3 channels ON, Impedance<br>OFF, RLD ON, WCT ON |                | 30            | 3.6            | mA   |

| I <sub>DD</sub>                                           | Current consumption                          | 1 channel ON, Impedance<br>OFF, RLD ON, WCT OFF | 20,            | 1.3           | 1.6            | mA   |

|                                                           |                                              | 1 channel ON, Impedance<br>ON, RLD ON, WCT OFF  | 3/0            | 2.2           | 2.7            | mA   |

| V <sub>IH</sub>                                           | High level input voltage                     | All Inputs                                      | 0.8 x<br>IOVDD |               |                | V    |

| V <sub>IL</sub>                                           | Low level input voltage                      | All inputs                                      |                |               | 0.2 x<br>IOVDD | V    |

| V <sub>OH</sub>                                           | High level output voltage                    | All outputs                                     | 0.9 x<br>IOVDD |               |                | ٧    |

| V <sub>OL</sub>                                           | Low level output voltage                     | All outputs                                     |                |               | 0.1 x<br>IOVDD | ٧    |

| Biopoter                                                  | ntial channels                               |                                                 |                |               |                |      |

| V <sub>BIO-</sub><br>DIFF                                 | Differential input voltage                   | Signal bandwidth<br>0.05 Hz - 10 kHz            |                | ±0.8/<br>GAIN |                | ٧    |

| 05                                                        | Input impedance                              | DC contact check ON                             | 50             |               |                |      |

|                                                           | Signal bandwidth 0.05 Hz-<br>300 Hz          | DC contact check OFF                            | 50             |               |                | ΜΩ   |

|                                                           | Analog high pass RC filter cut off frequency |                                                 |                | 0.05          |                | Hz   |

|                                                           | Input bias current                           |                                                 |                |               | 10             | pА   |

|                                                           | Input differential bias current              |                                                 |                |               | 10             | pА   |

|                                                           | Gain setting                                 |                                                 | 8              | 3, 16, 32, 64 | 1              | V/V  |

|                                                           | Total gain error                             | INA+PGA+ADC+VREF                                |                |               | ±1             | %    |

|                                                           | Gain match between channels                  |                                                 |                | 31.25         | ±0.5           | %    |

|                                                           | Chopping frequency                           |                                                 |                | 31.25         |                | kHz  |

DocID026157 Rev 5

12/85

Table 5. Electrical characteristics (continued)

| Symbol               | Parameter                                              | Test conditions                                                                                                      | Min. | Тур.          | Max  | Unit  |

|----------------------|--------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|------|---------------|------|-------|

|                      | Total accuracy (quantization, linearity, noise)        | V <sub>DIFF-PP</sub> =20mV; GAIN=64;<br>10Hz                                                                         |      | 15            |      | μV    |

|                      | ADC resolution                                         | AC signal only, DC value removed by high-pass filter                                                                 |      | 16            |      | bits  |

| ODR                  | Max data rate (internal filters bypassed)              | After 1 <sup>st</sup> decimation filter                                                                              |      | 125           |      | KSPS  |

|                      |                                                        | GAIN=64                                                                                                              |      | 0.6           |      |       |

|                      | Input referred noise                                   | GAIN=32                                                                                                              |      | 1.1           | 10   |       |

|                      | Signal bandwidth 0.1 Hz - 150<br>Hz Data rate = 488 Hz | GAIN=16                                                                                                              |      | 2             |      | μVrms |

|                      |                                                        | GAIN=8                                                                                                               |      | 4.2           | 70.  |       |

| CMRR                 | Common mode rejection ratio                            | 60Hz, 100mV <sub>PP</sub>                                                                                            |      | 100           |      | dB    |

| CND                  | Circulto naise vetia                                   | Gain=64, Differential input signal frequency 10Hz, 10mVpp; VDD=3V HRLB                                               | 10   | 72            |      | dB    |

| SNR                  | Signal to noise ratio                                  | Gain=16, Differential input<br>signal frequency 1kHz,<br>40mVpp; VDD=3V LRHB                                         |      | 62            |      | dB    |

| Impedan              | ce channel                                             |                                                                                                                      |      |               |      |       |

| V <sub>ZC-DIFF</sub> | Differential input voltage                             | (5)                                                                                                                  |      | ±0.8/<br>GAIN |      | V     |

|                      | Gain setting                                           |                                                                                                                      | 8    | 3, 16, 32, 64 | 4    | V/V   |

|                      | Accuracy (quantization, linearity, noise)              | DC Impedance range [50, 5k] $\Omega$ , point calibration 50 $\Omega$                                                 |      | ±1.5          |      | %     |

|                      | ADC Resolution                                         |                                                                                                                      |      | 16            |      | bits  |

| 050                  | Impedance measurement noise                            | 0.05 Hz to 1 Hz filter,<br>31.25 kHz modulation<br>frequency,<br>100 Ohm baseline resistance<br>20 μA with Gain = 64 |      | 100           |      | mΩ    |

|                      | Total phase shift                                      |                                                                                                                      |      | 115           |      | deg   |

|                      | Gain error                                             |                                                                                                                      |      |               | ±0.1 | %     |

| Impedan              | ce channel current injection                           |                                                                                                                      | I    |               |      |       |

|                      | Injection current                                      |                                                                                                                      |      | 5, 10, 20     |      | μA    |

|                      | Sink/Source current matching                           |                                                                                                                      |      |               | 15   | nA    |

|                      | Current Injection frequency                            |                                                                                                                      |      | 31.25         |      | kHz   |

| RLD amp              | olifier                                                |                                                                                                                      | •    |               |      | •     |

|                      | Integrated noise                                       | bandwidth 0,05Hz-300Hz                                                                                               |      | 20            |      | μVrms |

Electrical characteristics HM301D

Table 5. Electrical characteristics (continued)

| Symbol    | Parameter                    | Test conditions                                          | Min.                       | Тур.         | Max                        | Unit  |

|-----------|------------------------------|----------------------------------------------------------|----------------------------|--------------|----------------------------|-------|

|           | Gain                         | f=50Hz                                                   | 50                         |              |                            | dB    |

|           | Output voltage swing         | ILIM 880 nA                                              | V <sub>SS</sub> +<br>0.325 |              | V <sub>DD</sub> -0.35      | ٧     |

|           | Sink/Source current          | VDD = 3V                                                 |                            |              | 11                         | μA    |

|           | Current consumption          |                                                          |                            | 90           |                            | μA    |

| WCT am    | olifier                      |                                                          |                            |              |                            |       |

|           | Integrated noise             | bandwidth 0,05Hz-300Hz                                   |                            | 1.5          |                            | μVrms |

|           | Gain bandwidth product       |                                                          | 0.5                        |              | 4/6                        | MHz   |

|           | Gain                         |                                                          |                            | 1            | 1000                       | V/V   |

|           | Sink/Source current          |                                                          |                            | 33/18        |                            | μA    |

|           | Output voltage swing         | V <sub>DD</sub> =1.8V                                    | V <sub>REF</sub> -0.5      |              | V <sub>REF</sub> +<br>0.5  | ٧     |

| Shield ar | nplifier                     | \(                                                       | 3/0                        |              |                            | •     |

|           | Integrated Noise             | bandwidth 0.05Hz-300Hz                                   |                            | 8            |                            | μVrms |

|           | Gain                         | 000                                                      |                            | 1            |                            | V/V   |

|           | Bandwidth                    |                                                          | 490                        |              |                            | Hz    |

|           | Sink/Source current          | 16                                                       |                            |              | 10                         | μA    |

|           | Output Voltage Swing         | High Level, V <sub>DD</sub> =1.8V                        | V <sub>REF</sub> -<br>0.63 |              | V <sub>REF</sub> +<br>0.59 | ٧     |

|           | Current consumption          |                                                          |                            | 11           |                            | μA    |

| DC conta  | act check                    |                                                          |                            |              |                            |       |

|           | DC Current                   |                                                          | 25                         | , 50, 100, 2 | 00                         | nA    |

|           | DC current accuracy          | T <sub>A</sub> =25°C                                     |                            | ±5           |                            | %     |

| OS        | Comparator threshold         | T <sub>A</sub> =25°C                                     | VSS +<br>102               |              | VDD-<br>102                | mV    |

|           | Step threshold               |                                                          |                            | 102          |                            | mV    |

| AC conta  | act check                    |                                                          |                            |              |                            |       |

|           | Injection current            |                                                          |                            | 5, 10, 20    |                            | μA    |

|           | Sink/Source current matching |                                                          |                            |              |                            | nA    |

|           | Current Injection frequency  | See hc_curinj_freq bit                                   |                            | 2.5, 5       |                            | kHz   |

| Voltage r | eference                     |                                                          |                            |              |                            |       |

| $V_{REF}$ | Reference voltage            | V <sub>DD</sub> =3.3V; psmon_sel_r=1                     |                            | 1.0          |                            | V     |

|           | Accuracy                     | 1 point temperature<br>calibration; T <sub>A</sub> =25°C |                            |              | ±0.15                      | %     |

Table 5. Electrical characteristics (continued)

| Symbol    | Parameter           | Test conditions                        | Min.           | Тур. | Max            | Unit  |

|-----------|---------------------|----------------------------------------|----------------|------|----------------|-------|

|           | Integrated noise    | bandwidth 0.05Hz-300Hz                 |                | 15   |                | μVrms |

| Ring osc  | illator             |                                        |                |      |                |       |

|           | Frequency           |                                        |                | 2.00 |                | MHz   |

|           | Accuracy            | T <sub>A</sub> =25°C                   |                |      | ±2             | %     |

|           |                     | T <sub>A</sub> =0÷70°C                 |                |      | ±10            | %     |

|           | Current consumption |                                        |                | 12   |                | μA    |

|           | Duty cycle          |                                        | 40             |      | 60             | %     |

| Crystal o | scillator           |                                        |                |      | CIL            |       |

|           | Frequency           | 4 MHz Crystal, internally divided by 2 |                | 2.00 | 7.             | MHz   |

|           | Accuracy            | T <sub>A</sub> =0÷70°C                 |                |      | ±0.1           | %     |

|           | Current consumption |                                        | 10             | 68   |                | μA    |

|           | Duty cycle          |                                        | 40             |      | 60             | %     |

| External  | clock               | 205                                    |                |      |                |       |

|           | Frequency           | OP                                     |                | 2.00 |                | MHz   |

|           | Low level signal    | 15)                                    |                |      | 0.1 x<br>IOVDD | ٧     |

|           | High level signal   |                                        | 0.9 x<br>IOVDD |      |                | V     |

|           | Duty cycle          |                                        | 40             |      | 60             | %     |

Table 6. Input-referred noise (μV<sub>RMS</sub>/μV<sub>PP</sub>) / 3 V analog supply 1

| Output data rate (Hz) | -3 dB Bandwidth (Hz) | Gain = 8 | Gain = 16  | Gain = 32 | Gain = 64 |

|-----------------------|----------------------|----------|------------|-----------|-----------|

| 1953                  | 600                  | 6.2/41.5 | 3.1/20.2   | 1.56/11.3 | 0.931/6.8 |

| 976                   | 300                  | 5.2/37   | 2.7/18.7   | 1.39/10.1 | 0.81/6.4  |

| 651                   | 200                  | 5.5/36   | 3.78/22.1  | 1.3/8.4   | 0.841/5.3 |

| 488                   | 150                  | 4.2/28   | 1.98/14.4  | 1.1/7.17  | 0.615/4.2 |

| 325                   | 100                  | 4.0/27.1 | 3.0/17.7   | 1.01/6.8  | 0.715/4.5 |

| 244                   | 75                   | 3.1/20   | 1.7/11.1   | 0.93/5.87 | 0.554/3.8 |

| 163                   | 50                   | 3.1/19.5 | 1.59/10.04 | 0.83/6.1  | 0.7/3.4   |

| 122                   | 37                   | 2.4/15.8 | 1.2/8.1    | 0.76/4.5  | 0.46/2.6  |

| <u>81.5</u>           | 25                   | 2.5/15.5 | 1.55/8.39  | 0.78/4.5  | 0.47/2.6  |

#### **Detailed description** 6

#### 6.1 **Overview**

The HM301D includes three biopotential channels with bio-impedance channel. Even if specifically designed for ECG application, the HM301D is suitable to collect any biopotential signal including EEG and EMG ones.

The biopotential channels measure both the incoming ECG/EEG/EMG and pacemaker (PM) signals and provide both analog (on ANAx\_OUT pins) and digital (send out over SPI) outputs. An additional feature of each biopotential channel is the contact check whose purpose is to notify the user when the electrode contact has become poor. This is a DC and AC check and gives an indication on the electrode contact resistance.

The architecture of the biopotential channel is described in more detail in Section 6.3.

The bio-impedance channel provides an accurate measurement of the body and electrode impedance. An AC-current is injected at a configurable frequency through the body; the resulting AC-voltage is measured and processed. In order to get rid of the impedance given by the defibrillator protections resistors, a 4 wires measurement (force and sense) can be implemented by connecting two dedicated electrodes to the injection pins (CIP and CIN). Section 6.5 provides more details about the architecture of this channel.

The input connection circuit allows the use of several kinds of cable connectors based on the application. Any of the input signals on INxy, (x = 1, 2, 3; y = P, N) can be switched to any of the 3 biopotential channel inputs. Also the output of the RLD can be connected to any INxy.

The drivers block (see Section 6.6) provides specific reference signals required in both standard ECG applications and multiple chip configuration (e.g. WCT, RLD, SD).

The Wilson common terminal circuit (see Section 6.6.3) averages the signals present on the R,L and LL electrodes and serves as a reference voltage for unipolar measurements (e.g. ECG: V1, V2... V6).

The right leg drive (see Section 6.6.1) sets a proper DC-voltage at the input of the HM301D by connecting the RLD output to the RL electrode on the body. RLD COMP pin allows for the use of an external compensation network, if needed. In case of shielded cables a Shield Driver (see Section 6.6.2) is provided.

In order to enable applications with a large number of electrodes (e.g. R, L, LL, V1, V2, V3, ...) it is possible to use the HM301D in a multiple chip configuration: up to four devices can be connected using a daisy chain SPI. In this case, all the AVGIO pins are tied together in order to provide the overall common mode signal of all system electrodes.

The HM301D contains a dedicated digital signal processing with the following functionalities:

- User configurable signal filtering: low pass and high pass;

- Simultaneous processing of both High Resolution/Low Bandwidth (HRLB) and High Bandwidth/Low resolution (HBLR) signals (e.g. ECG and Pacemaker);

- IQ impedance demodulation (Real and Imaginary part);

- Standard SPI communication;

- Device configuration settings:

The supply monitor gives a 2-bit indication of the battery status. An accurate voltage reference is embedded. The RST pin can be configured to provide a power-on-reset signal or to accept an external enable signal from the MCU.

The clock circuit offers the maximum configurability:

- Embedded ring oscillator;

- Crystal oscillator;

- External clock:

### 6.2 Input connection matrix

The input connection circuit allows the use of several kinds of connectors. Anyone of the input pins INxy (x = 1, 2, 3; y = P/N) can be switched to any of the 3 biopotential channel inputs and to the RLD driver output.

Since the signals of the input pins can change according to the connector used, also the connections of the AVG buffers block must be changed. This is done by setting the right bits according to the following table:

**Table 7. Input connection matrix**

|        | Setting                    | Description                                                                                                                                        | Default |

|--------|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|---------|

|        | inputcon_in1p_hcsel_r<2:0> | Connect input pad IN1P to one of the 6 health channel inputs                                                                                       | 111     |

|        | inputcon_in1n_hcsel_r<2:0> | Connect input pad IN1N to one of the 6 health channel inputs                                                                                       | 111     |

|        | inputcon_in2p_hcsel_r<2:0> | Connect input pad IN2P to one of the 6 health channel inputs                                                                                       | 111     |

|        | inputcon_in2n_hcsel_r<2:0> | Connect input pad IN2N to one of the 6 health channel inputs                                                                                       | 111     |

| ١.     | inputcon_in3p_hcsel_r<2:0> | Connect input pad IN3P to one of the 6 health channel inputs                                                                                       | 111     |

| 1050le | inputcon_in3n_hcsel_r<2:0> | Connect input pad IN3N to one of the 6 health channel inputs                                                                                       | 111     |

| Op     | inputcon_avg1_r<2:0>       | Connect input AVG buffer1 to any of the 6 input pads INxy (x=1,2,3;y=P/N)                                                                          | 111     |

|        | inputcon_avg2_r<2:0>       | Connect input AVG buffer2 to any of the 6 input pads INxy (x=1,2,3;y=P/N)                                                                          | 111     |

|        | inputcon_avg3_r<2:0>       | Connect input AVG buffer3 to any of the 6 input pads INxy (x=1,2,3;y=P/N)                                                                          | 111     |

|        | inputcon_avg4_r<2:0>       | Connect input AVG buffer4 to any of the 6 input pads INxy (x=1,2,3;y=P/N)                                                                          | 111     |

|        | inputcon_rld_sel_r<2:0>    | Connect the RLD out to any of the inputs pads InxN/P, for x=1,2,3. Whatever is the bits configuration, the RLD out is always connected to RLD pin. | 111     |

For all the registers the following configuration is valid:

| Bits configuration | Pad connection |

|--------------------|----------------|

| 000                | IN1P           |

| 001                | IN1N           |

| 010                | IN2P           |

| 011                | IN2N           |

| 100                | IN3P           |

| 101                | IN3N           |

| 110                | NOT CONNECTED  |

| 111                | NOT CONNECTED  |

Table 8. Pad connection settings

The nomenclature used in the pin description and pin configuration is referred to the default setting of the connection matrix. The RLD driver output can be connected to any of the INxy pads but, in any case, it is always connected to RLD pin.

#### 6.3 Biopotential channel

Single ended

| High | Decimation | Filter | PF: 0.05 - 5 Hz | Gain Error | Correction | PM | PF: 0.05 - 1 kHz | Correction | PM | PF: 0.05 - 1 kHz | Correction | PM | PF: 0.05 - 1 kHz | PF: 5k - 10 kHz | PMD |

Figure 3. Biopotential channel block schematic

*Figure 3* shows the architecture of one biopotential channel. Each channel can be selectively switched on/off.

The high resolution low bandwidth signal is available in ECGx\_DATAOUT registers while the a low resolution high bandwidth signal is available in the output data packet.

#### 6.3.1 Analog section

The input signal first passes through the analog high-pass filter with corner frequency of 0.05 Hz, in this way the DC component is removed maintaining the integrity of the signal even at low frequencies.

Due to the very low cut-off frequency, the start-up time of the channel could be very long. In order to avoid this, the HM301D goes in recovery mode in which the high pass filter cut-off frequency is changed to higher values.

At start-up or after overvoltage condition, the cut-off starts from 5 Hz, then goes to 0.7 Hz and finally to 0.05 Hz. The 5 Hz cut-off frequency has a very fast settling speed and will set the common mode level of the instrumentation amplifier. By default, the switching time between the different cut-off frequencies is set at 200 ms but it can be changed in the SET22 register. The recovery mode acts both on analog and digital high pass filters, but the digital filter stops at the frequency which has been set in the hc dig pmhpf sel r bits.

If the recovery mode is OFF, the cut off frequency of this analog high pass filter can be changed at application level by changing the hc[1,2,3]rhpf\_sel\_r bits.

After the high pass filter, the signal is chopped and fed to the amplification stage (instrumentation amplifier and programmable gain amplifier). The signal is filtered by a 110 kHz low pass before being supplied to the ADC.

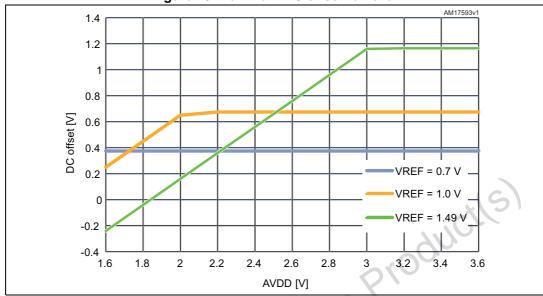

A differential to single-ended block makes the analog signal available at the pins ANA[1,2,3]\_OUT. The output voltage of the differential to single-ended block is equal to:

#### **Equation 1**

DIFF 2SE

$$\_OUT = GAIN \times \frac{V_{INxP} - V_{INxN}}{2} + V_{REI}$$

where  $V_{RFF}$  is 0.7 V or 1 V

Table 9. Biopotential channel gain and IDR

| IA GAIN | PGA GAIN | IDR [mv] |

|---------|----------|----------|

| 8       | 1        | 200      |

| 8       | 2        | 100      |

| 16      | 2        | 50       |

| 16      | 4        | 25       |

The ADC is a  $2^{nd}$  order 16bits  $\Sigma\Delta$  working at 2 MHz. Since the DC component of the signal has been already removed by the high-pass filter, the ADC is sampling just the useful part of the signal so that the 16bits provide a very good resolution for any biopotential signal.

The bit stream is then processed in the digital domain.

The following parameters of the analog portion of the biopotential channel can be modified through the SPI interface:

- IA Gain: 8, 16 (hc ina gain r);

- PGA Gain: 1, 2, 4 (hc\_pga\_gain\_r);

- Chopping frequency: 31.2 kHz;

- Cut-off frequency of the analog high pass filter (hc[1,2,3]rhpf\_sel\_r);

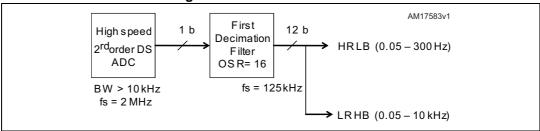

#### 6.3.2 **Digital section**

Figure 4. First decimation filter

The channel converts two signals to the digital domain: a high resolution low bandwidth (HRLB) and a low resolution high bandwidth (LRHB), for example the ECG and the pacemaker signals respectively. Their frequency content is 0.05-300 Hz and 0.05-10 kHz. While the HRLB are available for all the three biopotential channels, there are two LRHB signal paths which can be connected to any of the three biopotential channels. This is configured through the pmd\_sel\_r bits.

For both HRLB and LRHB signals, the digitized data values are in binary one's complement format. The analog input value is calculated according to the following formula:

#### **Equation 2**

$$V_{INxP} - V_{INxN} = \pm \frac{V_{REF}}{GAIN} \cdot \frac{DATA_{10}}{2^{16-1}}$$

where

- SIGN is plus if MSB is 0, minus if MSB is 1;

- DATA10 is the decimal value of the 15 LSBs if MSB is 0 or of the 15bits one's complement if MSB is 1;

- $V_{REF} = 0.8 V;$

- GAIN = IA GAIN x PGA GAIN is the total gain;

The first digital block is a decimation filter. Starting from the 2 MHz 1bit stream provided by the  $\Sigma\Delta$  modulator, a decimation rate of 16 is taken. The first decimation stage is then used for both the two signal paths. The sampling frequency is 2 MHz and the output is a 125 kHz 12 bits digital signal. Since the ADC is implemented as a 2<sup>nd</sup> order delta-sigma, the digital stream has 2<sup>nd</sup> order noise shaping. This must be filtered adequately to prevent aliasing. To obtain this, a 3<sup>rd</sup> order CIC-filter was chosen. This filter has an attenuation of -0.274 dB (3%) at 10 kHz and -0.2 mdB at 300 Hz. The output word length is 12 bit which can be provided to the SPI interface by configuring the bit dataout prefilter en in the SET13 register. In this way all the subsequent filters are bypassed.

#### 6.3.3 High resolution low bandwidth signal path (HRLB)

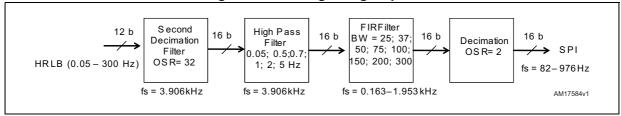

Figure 5. HRLB digital signal path

After the first decimation filter, a second decimation is performed in order to reduce the sampling frequency and, in the same time, to cut the high frequency signal part. The second decimation for HRLB signal is fixed to 32 and the output sampling frequency is 3.906 kHz. After that, a High Pass Filter is implemented. The -3 dB cut-off frequency is variable with 6 possible values: 0.05, 0.5, 0.7, 1, 2 and 5 Hz (hc\_dig\_ecghpf\_sel\_r<0:2>). After the HPF, a FIR filter with selectable bandwidth of 25, 37, 50, 75, 100, 150, 200 and 300 Hz (hc\_dig\_ecglpf\_sel\_r<0:2>) is implemented. At the end, a further decimation by 2 is inserted. Finally, the output signal is sent to the SPI block.

The following parameters can be set through the SPI interface:

- Low Pass Filter cut-off frequency: 25, 37.5, 50, 75, 100, 150, 200, 300, 600 Hz (hc\_dig\_ecglpf\_sel\_r);

- High Pass Filter cut-off frequency: 0.05, 0.5, 0.7, 1, 2, 5 Hz (hc\_dig\_ecghpf\_sel\_r);

- Cut-off start frequency of the high pass digital filter for the start-up procedure (hc[1,2,3]\_dig\_hpf\_sel\_r). Active only when recovery mode is OFF.

#### 6.3.4 Low resolution high bandwidth signal path (LRHB)

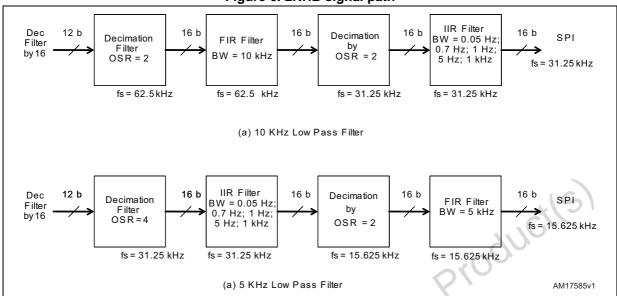

The LRHB signal path takes the same signal of 12 bits 125 kHz, coming from the 1st decimation filter, as input. Linear phase response is an important parameter. This can only be achieved by using FIR filters. Implementing FIR filters to filter a 5 kHz with a sampling frequency of 125 kHz will require a lot of taps in the filter. As with the HRLB path low pass filter, a decimation step is performed to lower the sampling frequency so to decrease the required taps in the FIR filters.

The LRHB signal can be provided with different cut off frequencies for low and high pass filters. As shown in *Figure 6*, the configuration of the digital blocks is changed in case of 5 kHz and 10 kHz low pass cut off frequencies.

A decimation step of 2 is done for the 10 kHz case and a decimation of 4 for the 5 kHz one, in this way the same FIR filter with only 4 taps is used in both cases. Implementing this decimation step with a good pass-band characteristic can be achieved with a CIC decimation filter.

For the 10 kHz low pass filter case, the FIR filter follows the first decimation filter, then a new decimation by 2 and finally the IIR high pass filter.

For the 5 kHz case, the FIR and IIR filters are swapped each other and, the decimation rate of the first filter is doubled.

Figure 6. LRHB signal path

The following parameters can be set through the SPI interface:

- Low Pass Filter cut-off frequency: 5, 10 kHz (hc\_dig\_pmlpf\_sel\_r);

- High Pass Filter cut-off frequency: 0.05, 0.7, 1, 5,1000 Hz (hc dig pmhpf sel r);

- Connection of the two LRHB signal paths to any of the three biopotential channels (pm sel r);

The LRHB signal path provides also a signal amplitude detection function. This function is useful as pacemaker detection (PMD) in ECG systems where reduced ODR, fewer MIPS for the host and low power consumption are key features. Integrated hardware detection of the pacemaker pulse allows the device to meet these requirements.

The 9 most significant bits without sign of the LRHB (16 bit) are compared with a user selectable threshold of 9 bit (hc\_pmd\_thres\_r). When the threshold value is higher than the absolute value of the LRHB signal the output signal (PMD) is asserted high. Two PMD signals are available at DGIO1 and DGIO2 outputs. In ECG application these signals provide the pace maker detection signal. Since the comparison is done at digital level, the threshold value must be changed according to the gain setting.

For example, if a 0.2 mV value must be detected at the input of the channel and the threshold is set at 000000001, since one LSB of the ADC is 24  $\mu V$ , the 0.2 mV represents the 6<sup>th</sup> bit of the LRHB word with a gain of 8 or the 9th bit with a gain of 64. Since the comparison is done with the 9 MSBs, in the first case the PMD signal will be always low while in the second case the PMD will change in the same way as the 9th bit of the LRHB word.

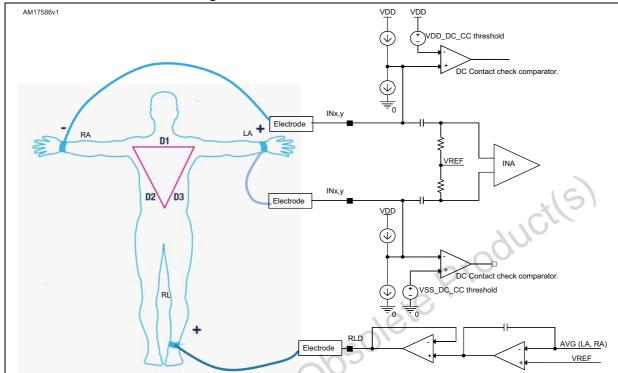

#### 6.4 Lead off detection

During ECG measurement and especially during a long period of monitoring, the electrode to skin contact check is needed in order to guarantee an adequate impedance value for a good signal acquisition. The HM301D provides two types of contact check: DC and AC

Figure 7. Contact check architecture

#### 6.4.1 DC contact check

One current source and one current sink are connected at each of the 6 inputs of the biopotential channels. Two comparators are also connected at each pin. Each of the 6 current sources can be activated by setting the in[1-3]\_contact\_pdp\_r bits while the 6 current sinkers are activated by setting the in[1-3]\_contact\_pdn\_r bits. According to the electrode configuration, the proper current source/sink must be activated. A small selectable current (25, 50, 100, 200 nA) is injected by the current source through one electrode and body of the patient and back into the HM301D through another electrode where the right current sinker is turned on and having the same current value setting. This current generates a voltage drop that is detected by the comparators connected to each pin. The comparator threshold is also selectable in a different way for the high side comparators (cck\_threshp\_sel\_r) and for the low side comparators (cck\_threshn\_sel\_r). There are 16 possible comparator threshold values.

The maximum current mismatch between one current source and one current sinker is 10%, in this way the DC current going to the body is very small.

#### 6.4.2 AC contact check

The AC contact check is based on the same principle of the DC contact check. In this case, an AC current (square wave) with a 2.5 kHz or 5 kHz (hc\_curinj\_freq\_r) frequency is injected through the electrodes. The possible current values are 5, 10 or 20  $\mu$ A. The quality of the electrode contact will be then evaluated by the host MCU by analyzing the injected frequency component in the LRHB signal.

For each biopotential channel the AC current source connected to the positive pin of the differential input is 180° out of phase with the one connected to the negative pin. In this way the current flows through the body and returns to the negative pin. When the contact

between two electrodes, each connected to the positive or negative inputs of two different channels, has to be checked, then it is necessary to reverse the phase of one of two involved AC current generator. The hc[1-3]\_phaserev\_r bits allow doing it so that any electrode configuration can be implemented.

The AC current generator is enabled by setting the relative hc[1-3]\_curinj\_en\_r bit. In addition, by setting the hc\_curinj\_en\_ext bit it is possible to enable/disable the AC current generators through an external logic signal applied to the DIGIO2 pin. This signal will be AND-ed with the hc[1-3]\_curinj\_en\_r bits, so that only the enabled current generators will be turned on

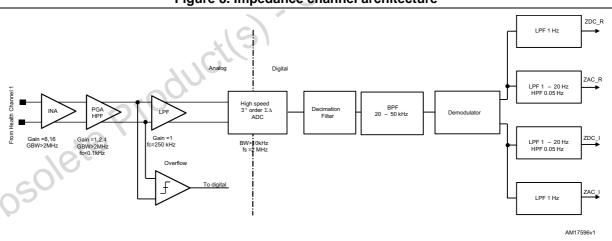

#### 6.5 Impedance channel

The goal of the impedance channel is to measure the impedance of the body and to measure the variation of this impedance due to the respiration. In reality the measured impedance won't be the impedance of the body alone but the series connection of the body with the board protections, the 2 electrodes and with skin and gel impedances. These values must be taken into account when reading the impedance values of HM301D.

The impedance circuit detects impedance values by injecting a high frequency square wave AC current through the CIP and CIN pins and monitoring the resulting voltage (*Figure 8*).

High frequency is imposed both for safety reasons and due to the electrodes' band pass. To avoid electrode polarization the average injected current is minimized.

Figure 8. Impedance channel architecture

The body impedance is used as an indicator to determine biological parameters, such as those used for galvanic skin response evaluation and patient fluid status check. Furthermore, in automated external defibrillator (AED) applications, body impedance evaluation is needed in order to deliver the proper amount of energy to the patient. This function has been designed considering application-specific electrodes (i.e. with polarity).

The modulated impedance (AC impedance) measurement principle is based on bioimpedance measurement on the patient's thorax and allows the measurement of respiration concurrently with the ECG and pacemaker measurements using two standard ECG electrodes. The time variation of body impedance due to respiration and chest movement is measured. This allows breath rate evaluation and provides information about movement artifacts that can affect ECG measurement.

The impedance is measured by the injection of an AC current at 31.25 kHz and by measuring the resulting voltage across it. The current value can be chosen among three different values: 5, 10 and 20  $\mu$ A. Since this current is injected using different pins from the ones where the voltage is measured, a 4 wire measure (force and sense principle) is implemented.

Even if unpractical in real applications, using 4 different electrodes is really helpful to improve the accuracy of the impedance measurement. Anyhow using only 2 electrodes but separating the PCB path of force and sense until the cable connector, will bypass all the impedances of the application (protections, PCB tracks, etc) which usually have higher values than the ones that must be measured. For example, in ECG systems, the defibrillator and ESD protection resistors could be as high as 25 k $\Omega$ , while the measured body resistance is  $\sim 0.5 \ k\Omega$ .

The impedance channel differential input is connected to the same input of biopotential channel 1 (see *Figure 1*).

The impedance channel outputs a real part and an imaginary part of the modulated impedance. This is obtained by IQ demodulation in the digital part of the channel which introduces additional gain and phase shift.

#### 6.5.1 Analog section

All analog blocks of the impedance channel are the same as their counterparts of the biopotential channel except for the low pass filter which has now a cut-off frequency of 250 kHz.

Another difference is the ADC which is now a 3<sup>th</sup> order cascaded (2-1) low pass-delta-sigma. A second order converter plus an extra stage that converts the quantization noise are implemented. Therefore the ADC will have 3<sup>th</sup> order noise shaping.

The following parameters can be set through the SPI interface:

- Current injection frequency: 20, 25, 31, 35, 41, 45, 50 kHz (imp\_curinj\_freq\_r);

- Current injection value: 5, 10 20 μA (imp curinj cur r);

- IA Gain: 8, 16 (imp\_ina\_gain\_r);

- PGA Gain: 1,2, 4 (imp pga gain r);

#### 6.5.2 Digital section

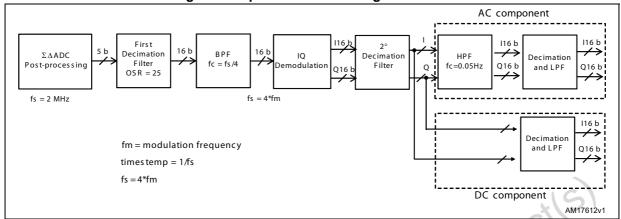

*Figure 9* shows the  $3^{rd}$  order  $\Sigma\Delta$  ADC followed by the filters in the impedance channel. The signal is first decimated and band pass filtered so to get sampling frequency of 4 times the signal frequency. An IQ-demodulator splits the signal in a real (I) and imaginary (Q) component. The result is again decimated before a final high pass filter at 0.05 Hz and low pass filter at 20 Hz or 1 Hz. The high pass filter is used to extract the ac component in combination with the 20 Hz or (after extra decimation) 1 Hz low pass filter. For the dc-component, only the 1 Hz low pass filter is used, without the high pass filter.

Figure 9. Impedance channel digital section

The following parameters can be set through the SPI interface:

Digital Low Pass filter cut-off frequency: 1 or 20 Hz (imp\_dif\_lpf\_sel\_r)

#### 6.6 Drivers

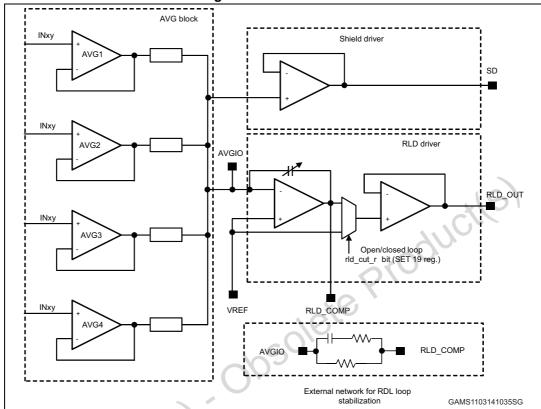

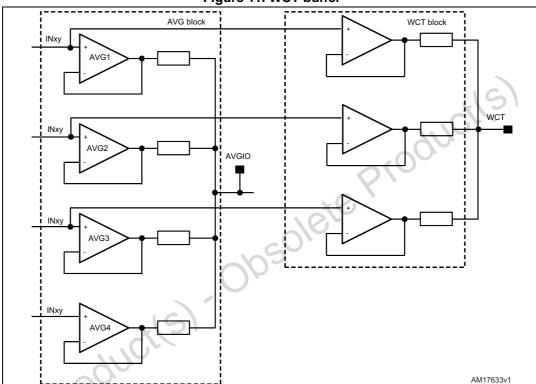

The global architecture for the drivers is shown in *Figure 10*. The drivers operation is specifically designed for ECG systems. In particular the WCT (Wilson common terminal) is used in unipolar ECG systems, while RLD is the right leg driver for ECG which allows reducing system disturbances. The Shield driver is used in case of shielded cable.

An important role is played by the four AVG buffers. The positive inputs of these buffers are connected to any of the INxy pins by programming the input connection matrix (inputcon\_avg[1-4]\_r). In this way, the average value of any combination of the biopotential channels can be created. The output of the AVG buffers is fed to the shield driver and RLD driver. Each of the four AVG buffers can be turned on/off by setting the avg\_en\_buf[1-4]\_r bit. It is important to turn on only the AVG buffers used because the summing resistors will be programmed according to the numbers of AVG buffers which are on.

In addition the right number of AVG buffers used must be written in the avg\_numb\_buf\_r bits. This number will represent the total number of AVG buffers used also in the case of multiple connections of HM301D chips, where all the AVGIO pins are tied together.

The topology of the drivers is based on the following considerations:

It should not load the input signal. Therefore the electrode inputs are buffered with unity gain buffers.

The unipolar measurements should have similar accuracy as the bipolar measurements. This basically means that the total noise contribution of the 3 unity gain buffers must be smaller than the total noise contribution of the entire biopotential channel.

The bandwidth of the WCT circuit must be enough to not generate too much delay.

Figure 10. AVG buffers

#### 6.6.1 Right leg driver