## Isolated, Constant Current LED Driver

### Features

- ▶ Programmable true constant current operation

- ▶  $\pm 3\%$  LED current accuracy

- ▶ Adaptive to external component tolerances and parasitics

- ▶ Primary-side current sensing

- ▶ Output open circuit protection

- ▶ Output short circuit protection

- ▶ Input under voltage lockout

- ▶ PWM dimming / enable

- ▶ Universal 80-264VAC operation

- ▶ Fixed frequency operation

### Applications

- ▶ Low power lighting fixtures

### General Description

The HV9971 is a primary-side control IC for driving a discontinuous conduction mode (DCM) flyback LED driver. The IC is optimized for operation at a constant full-load switching frequency of 100kHz and the universal input AC voltage range of 80-264VAC. It maintains 3% variation of the LED current setting, and features tight line and load regulation. The proprietary primary-side output current control employed in the HV9971 makes the output current setting insensitive to most component tolerances and parasitics without use of an opto-feedback.

The HV9971 LED driver is fully protected against output open and short circuit conditions and input under-voltage. It also offers a logic input for dimming the LED light output by means of pulse-width modulation of the output current.

The HV9971 is ideally suited for driving high-brightness LEDs in low-power lighting fixtures such as incandescent bulb retrofits.

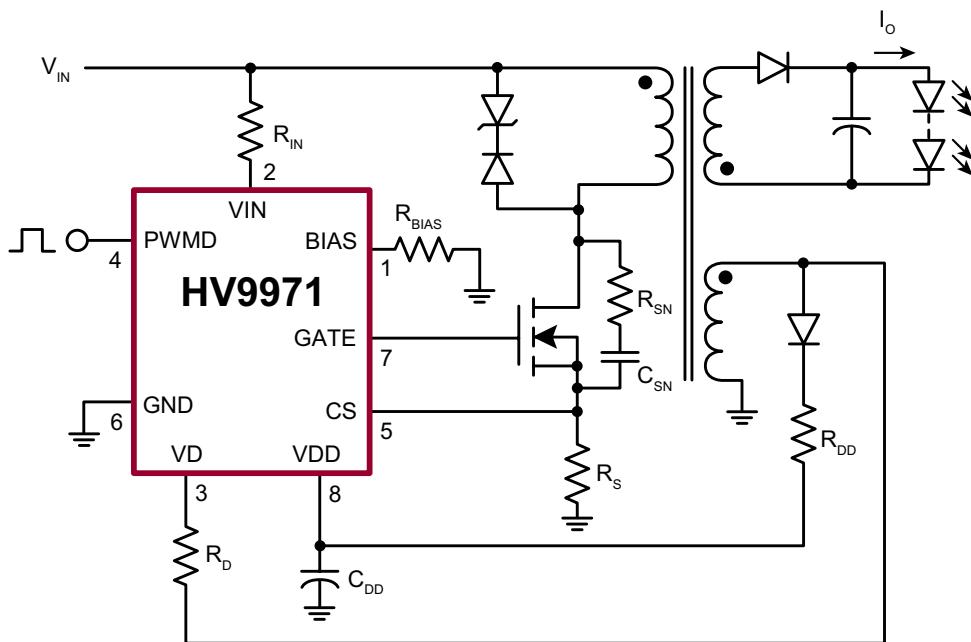

### Typical Application Circuit

## Ordering Information

| Device | Package Options                                                     |

|--------|---------------------------------------------------------------------|

|        | 8-Lead SOIC<br>4.90x3.90mm body<br>1.75mm height (max) 1.27mm pitch |

| HV9971 | HV9971LG-G                                                          |

-G indicates package is RoHS compliant ('Green')

## Absolute Maximum Ratings\*

| Parameter                                                                                | Value                          |

|------------------------------------------------------------------------------------------|--------------------------------|

| VIN, VD, BIAS current                                                                    | $\pm 5.0\text{mA}$             |

| VDD voltage                                                                              | -0.3V to $V_{\text{SHUNT}}$    |

| VDD current                                                                              | 10mA                           |

| GATE voltage                                                                             | -0.3V to $V_{\text{DD}}$ +0.3V |

| CS, PWMD voltage                                                                         | -0.3V to 6.0V                  |

| Continuous power dissipation ( $T_A = +25^\circ\text{C}$ ) (derate 6.3mW/°C above +25°C) | 630mW                          |

| Junction temperature                                                                     | +150°C                         |

| Storage temperature range                                                                | -65°C to +150°C                |

\* All voltages referenced to GND pin.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

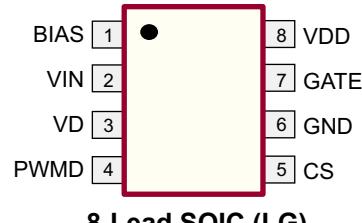

## Pin Configuration

## Product Marking

Y = Last Digit of Year Sealed

WW = Week Sealed

L = Lot Number

— = "Green" Packaging

Package may or may not include the following marks: Si or

8-Lead SOIC (LG)

## Electrical Characteristics

(Specifications are at  $T_A = 25^\circ\text{C}$ ,  $V_{\text{DD}} = 10\text{V}$ ,  $I_{\text{IN}} = 200\mu\text{A}$ ,  $C_{\text{GATE}} = 750\text{pF}$ , BIAS open, unless otherwise noted).

| Sym                       | Description             | Min | Typ  | Max   | Units         | Conditions                   |

|---------------------------|-------------------------|-----|------|-------|---------------|------------------------------|

| <b>Power Supply (VDD)</b> |                         |     |      |       |               |                              |

| $V_{\text{DD}}$           | Shunt voltage           | *   | 10.5 | 11.0  | 11.5          | V                            |

| $V_{\text{DD, START}}$    | Start voltage           | *   | 9.95 | 10.50 | 11.45         | V                            |

| $V_{\text{DD, STOP}}$     | Under voltage threshold | *   | 6.65 | 7.00  | 7.70          | V                            |

| $I_{\text{DDQ}}$          | Supply standby current  | -   | -    | 1.0   | mA            | Gate open                    |

| $I_{\text{DDQ(START)}}$   | Start-up current        | *   | -    | -     | $\mu\text{A}$ | $V_{\text{DD}} = 10\text{V}$ |

### Notes:

\* Specifications which apply over the full operating ambient temperature range of  $-40^\circ\text{C} < T_A < +125^\circ\text{C}$ .

† Parameters guaranteed by design

## Electrical Characteristics

| Sym                                                 | Description                              | Min | Typ   | Max   | Units | Conditions |

|-----------------------------------------------------|------------------------------------------|-----|-------|-------|-------|------------|

| <b>Feed Forward Inputs (VD, VIN) and Oscillator</b> |                                          |     |       |       |       |            |

| $I_{IN}$                                            | Operating current range                  | *   | 0     | -     | 1000  | $\mu A$    |

| $I_D$                                               | Operating current range                  | *   | 0     | -     | 1000  | $\mu A$    |

| $\Delta Q_{IN(MAX)}$                                | VIN Input charge swing                   | *†  | -     | -     | 460   | pC         |

| $K_{Osc}$                                           | Oscillator coefficient                   | *†  | 0.32  | 0.33  | 0.34  | -          |

| $V_D$                                               | VD voltage                               | *   | 2.406 | 2.440 | 2.474 | mV         |

| $F_{S(START)}$                                      | Start-up frequency                       | -   | -     | 10    | -     | kHz        |

| <b>Bias Current Generator (BIAS)</b>                |                                          |     |       |       |       |            |

| $V_{BIAS}$                                          | Output voltage                           | *   | 1198  | 1220  | 1242  | mV         |

| <b>GATE Output</b>                                  |                                          |     |       |       |       |            |

| $T_{RISE}$                                          | GATE output rise time                    | -   | -     | 40    | 75    | ns         |

| $T_{FALL}$                                          | GATE output fall time                    | -   | -     | 20    | 40    | ns         |

| <b>Current Sense Comparator</b>                     |                                          |     |       |       |       |            |

| $V_{CS(TH)}$                                        | CS trip threshold                        | *   | 1198  | 1220  | 1242  | mV         |

| $T_{DELAY}$                                         | Propagation delay CS to GATE             | *   | -     | -     | 100   | ns         |

| $T_{BLANK}$                                         | Leading edge blanking delay              | *   | 200   | 300   | 400   | ns         |

| <b>VIN Under Voltage Comparator</b>                 |                                          |     |       |       |       |            |

| $I_{IN(UVLO)}$                                      | $V_{IN}$ undervoltage threshold current  | -   | 80    | -     | 101   | $\mu A$    |

| $\Delta I_{IN(UVLO)}$                               | $V_{DD}$ undervoltage lockout hysteresis | -   | -     | 15    | -     | $\mu A$    |

| <b>Open Circuit Protection</b>                      |                                          |     |       |       |       |            |

| $I_{D(OV)}$                                         | Output open circuit threshold            | -   | 133   | -     | 147   | $\mu A$    |

| <b>PWM Dimming</b>                                  |                                          |     |       |       |       |            |

| $V_{PWMD,HI}$                                       | PWMD input high voltage                  | *   | 2.0   | -     | -     | V          |

| $V_{PWMD,LO}$                                       | PWMD input low voltage                   | *   | -     | -     | 0.8   | V          |

| <b>Effective Current Sense Reference Voltage</b>    |                                          |     |       |       |       |            |

| $V_{EFF}$                                           | Effective reference voltage              | -   | 195.5 | -     | 207.6 | mV         |

| $\Delta V_{EFF}/V_{EFF}$                            | $I_{IN}, I_D$ regulation of $V_{EFF}$    | †   | -     | 3.0   | -     | %          |

**Notes:**

\* specifications which apply over the full operating ambient temperature range of  $-40^{\circ}C < T_A < +125^{\circ}C$ .

† Parameters guaranteed by design.

1. Effective output current  $V_{EFF} = 0.5 \cdot V_{CS} \cdot K_{Osc}$ . Trimmed to the product of  $V_{CS} \cdot K_{Osc}$ .

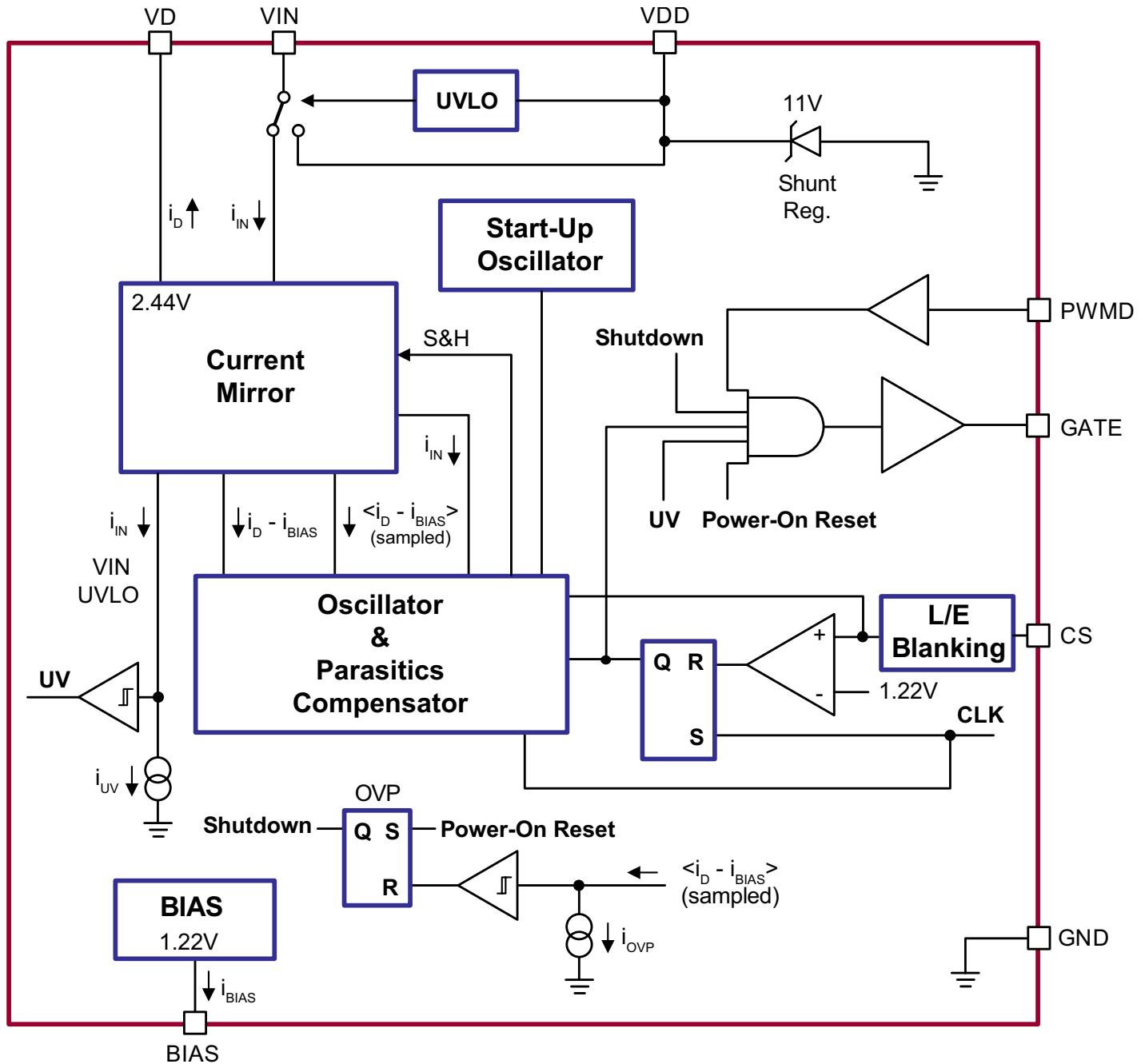

## Functional Block Diagram

## Functional Description

### Power Topology and Control Method

The HV9971 regulates the constant output current of a discontinuous conduction mode (DCM) flyback converter. Although it can be used in other applications, it is optimized for operating from a universal AC line input voltage of 85-264VAC. The HV9971 is a fully integrated peak-current PWM controller IC. It does not require an optocoupler feedback, and includes protection from output open-circuit, short-circuit, and input under-voltage conditions. A proprietary control scheme permits accurate primary-side control of output current, insensitive to most circuit parasitics, external component tolerances and output voltage variation.

Output current of an HV9971 flyback converter can be expressed as:

$$I_O = \frac{I_{PK} \cdot n \cdot K_{Osc}}{2} \quad (1)$$

Where  $K_{Osc} = 0.33$  is an oscillator coefficient,  $n$  is flyback transformer turns ratio of primary to secondary winding, and where  $I_{PK}$  is peak primary winding current given by:

$$I_{PK} = \frac{V_{CS(TH)}}{R_S} \quad (2)$$

In (2),  $V_{CS(TH)}$  is the reference voltage of the current sense comparator at CS, and  $R_S$  is the current sense resistance.

Combining (1) and (2), we can write the output current as:

$$I_O = \frac{V_{CS(TH)} \cdot n \cdot K_{Osc}}{2 \cdot R_S} = \frac{n \cdot V_{EFF}}{R_S} \quad (3)$$

The effective reference voltage  $V_{EFF} = 202\text{mV}$ . Hence, the desired LED current is programmed by merely selecting the current sense resistor as:

$$R_S = \frac{n \cdot V_{EFF}}{I_O} \quad (4)$$

Note that the output current of the HV9971 LED driver is independent of the input and output voltage, the switching frequency or the transformer inductance.

The switching frequency at a given output voltage  $V_O$  can be estimated as:

$$F_S = \frac{n \cdot (V_O + V_F) \cdot K_{Osc}}{L_m \cdot I_{PK}} = \frac{V_{OR} \cdot K_{Osc}}{L_m \cdot I_{PK}} \quad (5)$$

where:

$$V_{OR} = n \cdot (V_O + V_F) \quad (6)$$

In the equation (5),  $L_m$  is magnetizing inductance of the transformer primary winding, and  $V_F$  is the forward voltage drop at the output rectifier diode. (Note that the switching frequency is not a function of the internal timing components of the HV9971 or the absolute value of  $R_{IN}$  and  $R_D$ ).

Proper selection of maximum switching frequency  $F_{S(MAX)}$  at full load, in combination with maximum  $V_{OR(MAX)}$  is critical for proper operation of the HV9971. The oscillator circuit ramp may saturate when the maximum charge swing  $\Delta Q_{IN(MAX)} = 400\text{pC}$  is exceeded at  $V_{IN}$ . Therefore, the circuit components should be selected such that:

$$\Delta Q_{IN} = \frac{V_{IN} \cdot T_{ON}}{R_{IN}} \leq \Delta Q_{IN(MAX)} \quad (7)$$

Note, that the HV9971 is protected against careless oscillator setup. When saturation of the oscillator ramp occurs, the HV9971 shuts off and attempts to go through a start-up cycle again.

The transformer magnetic flux equals the volt-seconds at the transformer winding in the DCM flyback converter:

$$V_{IN} \cdot T_{ON} \approx L_m \cdot I_{PK} \quad (8)$$

Therefore, the charge swing  $\Delta Q_{IN}$  varies only as a function of external component tolerances and circuit parasitic, and it is the same for all  $V_{IN}$  and  $V_O$  operating conditions. Combining equations (5), (7) and (8), and taking into consideration tolerances for  $L_m$ ,  $R_S$  and  $V_{CS(TH)}$ , we get the following design criterion:

$$\frac{V_{OR(MAX)} \cdot K_{Osc(MAX)}}{F_{S(MAX)} \cdot R_{IN(MIN)}} \cdot \frac{L_{m(MAX)}}{L_{m(MIN)}} \cdot \frac{V_{CS(TH)MAX}}{V_{CS(TH)MIN}} \cdot \frac{R_{S(MAX)}}{R_{S(MIN)}} \leq \Delta Q_{IN(MAX)} \quad (9)$$

The equation (9) gives the condition for selecting proper ratio of  $V_{OR(max)}/F_{S(MAX)}$ , which guarantees  $\Delta Q_{IN} \leq Q_{IN(MAX)}$ . Selection of the resistor  $R_{IN}$  is dictated by the desired input under-voltage (UV) and output over-voltage (OV) protection thresholds. The recommended selection of  $R_{IN} = 1\text{M}\Omega$  produces a UV shutdown at  $V_{IN} < 90\text{V}$ , adequate for a universal AC line voltage range of 85-265VAC, and an OV shutdown at  $V_{OR} > 140\text{V}$ . As an example, we can assume the tolerances of  $L_m$  and  $R_S$  as  $\pm 10\%$  and  $\pm 1\%$  correspondingly. We shall also limit the switching frequency under  $F_{S(MAX)} = 130\text{KHz}$ .

With these assumption, the equation (9) gives  $V_{OR(MAX)} \leq 120V$ . (Note, however, that running the HV9971 LED driver with  $V_{OR} > 120V$  does not cause excessive  $\Delta Q_{IN}$ , since the switching frequency  $F_S$  is proportional to  $V_{OR}$ .)

The above example takes full advantage of the available  $V_{IN}$  input dynamic range, and, therefore, achieves the most accurate control over the LED current. For this reason, we will use  $V_{OR(MAX)} = 120V$  and  $F_{S(MAX)} = 130\text{KHz}$  in the following equations, as our recommended design inputs. Given, the primary-to-secondary turn ratio is determined simply as:

$$n = \frac{V_{OR(MAX)}}{(V_{O(MAX)} + V_F)} = \frac{120V}{(V_{O(MAX)} + V_F)} \quad (10)$$

The maximum magnetizing inductance of the primary winding  $L_{m(MAX)}$  is obtained by combining the equations (2), (7) and (8):

$$L_{m(MAX)} = \frac{\Delta Q_{IN(MAX)} \cdot R_{IN(MIN)} \cdot R_{S(MIN)}}{V_{CS(TH)MAX}} \quad (11)$$

If we assume the primary inductance tolerance of  $\pm 10\%$ , the nominal value of  $L_m$  is determined simply as:

$$L_m = \frac{L_{m(MAX)}}{1.1} \quad (12)$$

Selection of the maximum magnetizing inductance in accordance with (11) guarantees DCM operation in the entire working range of the input voltage with the proper selection of the input under-voltage and output over-voltage thresholds. (See “Input Under-Voltage Protection” and “Output Open and Short Circuit Protection” below.)

Due to presence of the leakage inductance  $L_{LK}$ , a voltage spike occurs at the primary winding of the transformer. Although the HV9971 eliminates the effect of the leakage inductance on the LED current, the duration of this spike should be minimized for best efficiency. The time  $t_{LK}$  is the leakage spike duration, determined by:

$$t_{LK} = \frac{L_{LK} \cdot I_{PK}}{V_z - n \cdot (V_{O(MAX)} + V_F)} \quad (13)$$

Here,  $L_{LK}$  is primary winding leakage inductance,  $V_z$  is the Zener clamp voltage. Hence, the Zener clamp voltage  $V_z$  should be selected significantly higher than  $n \cdot (V_{O(MAX)} + V_F)$ .  $V_z$  must also exceed the open-circuit protection threshold.

The HV9971 is powered by an internal shunt regulator, clamping VDD at  $V_{DD(REG)} = 11V$ . The IC shuts down when

the voltage at VDD falls below  $V_{DD(UV)} = 7.0V$ . Under steady-state operation, the IC is powered by an auxiliary bootstrap winding through a ballast resistor  $R_{DD}$ . The primary-to-auxiliary winding turn ratio  $n_{AUX}$  and the value of  $R_{DD}$  should be selected carefully to ensure operation throughout the input and output voltage range with minimum power dissipation in  $R_{DD}$ . Note that the polarity of the auxiliary winding is opposite of the polarity of the secondary winding, such that the auxiliary winding voltage is positive during the on time. The following formulas are providing optimal values for  $n_{AUX}$  and  $R_{DD}$ , given the output voltage range  $V_{O(MIN)}$ ,  $V_{O(MAX)}$  and the input voltage range  $V_{IN(MIN)}$ ,  $V_{IN(MAX)}$ :

$$n_{AUX} = \frac{V_{IN(MIN)} \cdot V_{IN(MAX)}}{2 \cdot V_{DD(UV)} \cdot V_{IN(MAX)} - V_{IN(MIN)} \cdot V_{DD(REG)}} \quad (14)$$

$$R_{DD} = \frac{\left( \frac{V_{DD(UV)}}{V_{IN(MIN)}} - \frac{V_{DD(REG)}}{V_{IN(MAX)}} \right) \cdot n \cdot (V_{O(MIN)} + V_F) \cdot K_{osc}}{I_{DDQ} + Q_{GATE} \cdot \frac{(V_{O(MIN)} + V_F)}{(V_{O(MAX)} + V_F)} \cdot F_{S(MAX)}} \quad (15)$$

$$W_{DD} = \frac{\left( \frac{V_{IN(MAX)}}{n_{AUX}} - V_{DD(REG)} \right)^2 \cdot n \cdot (V_{O(MAX)} + V_F) \cdot K_{osc}}{R_{DD} \cdot V_{IN(MAX)}} \quad (16)$$

where  $W_{DD}$  is power dissipation in  $R_{DD}$ , and  $I_{DDQ}$  is the quiescent current of the HV9971.

## Start-Up

Upon applying the input AC power, the input current of VIN is diverted into the hold-up capacitor connected at VDD. The HV9971 consumes less than  $60\mu\text{A}$  in this mode, and its GATE output is off. When a threshold of  $V_{DD} = 10.5V$  is reached at VDD, VIN is disconnected from VDD, and the GATE output turns on. The GATE turns off upon reaching  $V_{CS(TH)} = 1.22V$  at CS. The frequency of the GATE pulses is determined by the oscillator circuit or by the  $10\text{kHz}$  start-up clock, whichever frequency is higher.

The hold-up capacitor connected at VDD must store enough energy to supply power to the HV9971 until adequate bootstrap power supply becomes available. The HV9971 stops switching and makes another attempt to charge the hold-up capacitor, if the voltage at VDD falls below  $7.0V$ .

Although the resistor  $R_{IN}$  serves a different purpose in operation, its value must be selected with care to ensure the required  $60\mu\text{A}$  start-up current at  $V_{IN(MIN)}$ .

### Current Sense Comparator

The peak current comparator is using an external sense resistor  $R_S$  to compare the primary winding current to the reference voltage  $V_{CS(TH)} = 1.22V$ . The corresponding peak current  $I_{PK}$  is given by equation (2). When the current in the primary winding exceeds  $I_{PK}$ , the comparator resets the PWM flip-flop circuit, and the output pulse is terminated. The next cycle begins upon receiving a clock signal from an internal oscillator circuit. A 300ns leading-edge blanking delay is applied to prevent false triggering of the current sense comparator.

### Oscillator Circuit

Upon the end of the start-up cycle, the input current of  $V_{IN}$  is reverted to a current mirror circuit for generating the current  $i_{IN}$  in accordance with the following equation:

$$i_{IN} = \frac{V_{IN} - 1V}{R_{IN}} \approx \frac{V_{IN}}{R_{IN}} \quad (17)$$

Accordingly, the input current  $i_D$  is derived by connecting a resistor  $R_D$  from the bootstrap winding to  $V_D$ . However, since  $n_{AUX} \gg 1$  normally, the voltage  $V_{AUX}$  is not negligible in comparison to the voltage at the VD pin ( $V_D = 2.44V$ ). Hence, the current  $i_D$  through the resistor  $R_D$  can be expressed as:

$$i_D = \frac{V_D - V_{AUX}}{R_D} \quad (18)$$

From this equation, the current  $i_D$  is not directly proportional to  $V_{AUX}$ . The offset current is given by the following equation:

$$i_{OS} = \frac{V_D}{R_D} \quad (19)$$

The HV9971 cancels out this offset internally by subtracting a current of the same magnitude as  $i_{OS}$ . This correction current is programmed by connecting a resistor at the BIAS pin in accordance with:

$$i_{BIAS} = \frac{V_{BIAS}}{3.5 \cdot i_{OS}} \quad (20)$$

In (20),  $V_{BIAS} = V_D/2$  is the voltage at the BIAS pin. Combining the equations (19) and (20) gives formula for calculating  $R_{BIAS}$  simply as:

$$R_{BIAS} = \frac{R_D}{7} \quad (21)$$

The resulting current  $i_{OR} = (i_D - i_{OS})$  represents the instant-

taneous voltage across the transformer bootstrap winding:

$$i_{OR} = \frac{V_D - V_{AUX}}{R_D} - \frac{V_{BIAS}}{3.5 \cdot R_{BIAS}} = -\frac{V_{AUX}}{R_D} \quad (22)$$

Sampled during the conduction time of the transformer secondary winding, this current represents the reflected output voltage ( $V_O + V_F$ ), where  $V_F$  is the voltage drop across the output rectified diode. The value of  $R_D$  should scale with  $R_{IN}$  in accordance with:

$$R_D = \frac{R_{IN} \cdot k}{n_{AUX}} \quad (23)$$

In (23),  $k$  is the coupling coefficient between the primary and the bootstrap windings. The coupling coefficient can be determined by measuring the leakage inductance  $L_{S(AUX)}$  of the auxiliary winding with respect to the primary winding and calculating it in accordance with the equation:

$$k = \sqrt{1 - \frac{L_{S(AUX)}}{L_{AUX}}} \quad (24)$$

Here,  $L_{AUX}$  is the bootstrap winding inductance. Since the value of the  $k$  is normally very close to 1, then  $k = 1$  could be used as a first approximation.

With proper selection of the resistor  $R_D$  in accordance with (23), the oscillator circuit then generates switching frequency:

$$F_S = \frac{n \cdot (V_O + V_F) \cdot K_{osc} \cdot R_S}{L_m \cdot V_{CS(TH)}} \quad (25)$$

### Output Open and Short Circuit Protection

The HV9971 provides a very reliable open circuit protection. If the sampled current  $i_{OR}$  exceeds the  $70\mu A$  threshold, the HV9971 is forced to go through a power-up cycle again. The corresponding output voltage threshold can be calculated as:

$$V_{O(LIM)} = \frac{R_D \cdot n_{AUX}}{n} \cdot 140\mu A - V_F \quad (26)$$

Normal operation resumes when the adequate LED load is connected.

Output short circuit protection is inherent to the HV9971 since the switching frequency is directly proportional to the output voltage. Moreover, loss of output voltage is likely to cause insufficient bootstrap power at VDD, resulting in a

“hiccup” operating mode and repetitive restart attempts.

### Input Under-Voltage Protection

The GATE output of the HV9971 becomes inhibited when the input current at VIN falls below 90µA. The GATE output is enabled again when the VIN current exceeds 104µA. The corresponding input under-voltage thresholds can be calculated as:

$$V_{IN(STOP)} = R_{IN} \cdot 90\mu A \quad (27)$$

$$V_{IN(START)} = R_{IN} \cdot 104\mu A \quad (28)$$

### R-C Snubber Design Considerations

Detection of  $t_{LK}$  given by the equation (13) is crucial for proper operation of the HV9971. Upon the turn-off of the switching MOSFET, the voltage spike caused by the transformer leakage inductance is followed by high-frequency oscillation. The oscillation occurs at the transformer windings with the period equal to  $2\pi\sqrt{L_{LK} \cdot C_{OSS}}$ , where  $C_{OSS}$  is the output capacitance of the MOSFET. This oscillation is damped naturally by copper and core losses of the transformer, and it subsides during conduction time of the secondary winding. However, extra damping is usually required. Insufficiently damped, the post-spike oscillation may adversely affect accuracy of the output current regulation as well as EMI performance of the LED driver.

Damping of the post-spike oscillation is achieved by connecting of a snubber network ( $R_{SN}$ ,  $C_{SN}$ ) across the switching MOSFET. Selection of the  $R_{SN}$  and  $C_{SN}$  values is based on achieving sufficient damping while minimizing the power losses in the snubber network. At the same time, the oscillation should not be over-damped, as this will prevent detection of  $t_{LK}$ .

We recommend the following choice of the snubber network components:

$$C_{SN} = C_{OSS} \quad (29)$$

$$R_{SN} = 1.6 \sqrt{\frac{L_{LK}}{C_{SN}}} \quad (30)$$

Note that the output capacitance  $C_{OSS}$  is a nonlinear function of the drain voltage. Most datasheets give the  $C_{OSS}$  value at the drain voltage of  $V_{DS} = 25V$ . Typically, the output capacitance characteristic as a function of  $V_{DS}$  is provided in the MOSFET datasheet as well. The equation (29) should use the  $C_{OSS}$  value at  $V_{DS} = (V_{IN(MIN)} + n \cdot V_{O(MIN)})$ , or at the highest  $V_{DS}$  given in the plot, whichever voltage is lower.

Also note that the R-C snubber network must be connected between the drain and the source of the MOSFET, rather than being wired to ground or across the primary winding. Otherwise, the current from  $C_{SN}$  may cause false tripping of the CS comparator.

Power dissipation in  $R_{SN}$  can be estimated by the following formula:

$$W_{RSN} = C_{SN} \cdot V_{IN(MAX)}^2 \cdot F_{S(MAX)} \quad (31)$$

### Layout Considerations

The signal inputs VIN and VD operate at relatively low input current ranging from hundreds down to tens of microamps. Therefore, proximity of the switching potential of the MOSFET drain can cause a displacement current in VD and VIN affecting the normal operation of the HV9971. Proper HV9971 PCB layout should avoid direct proximity of the VD and VIN inputs to the high-voltage switching potential.

The resistor  $R_D$  should be placed as close as possible to the VD input. Otherwise, a long VD trace can be susceptible to noise coupling, or it can introduce parasitic capacitance with respect to ground capable of distorting the VD input signal.

### Design example

The following example illustrates LED driver design with HV9971 for the following conditions:

1. Input:  $V_{IN(MIN)} = 110V$ ,  $V_{IN(MAX)} = 375V$

2. Output:  $V_{O(MIN)} = 6.0V$ ,  $V_{O(MAX)} = 18V$ ,  $V_F = 0.7V$ ,  $I_O = 0.5A$

3. Maximum switching frequency:  $F_{S(MAX)} = 130kHz$

4.  $V_{IN(STOP)} = 90V$

Design:

1. Using formula (27), calculate value of the resistor  $R_{IN}$ :

$$R_{IN} = \frac{V_{IN(STOP)}}{90\mu A} = 1.0M\Omega$$

2. Using formula (9), calculate  $V_{OR(MAX)}$ :

$$V_{OR} = \frac{\Delta Q_{IN(MAX)} \cdot F_{S(MAX)} \cdot R_{IN}}{K_{Osc(MAX)}} \cdot 77.6\% = 115V$$

3. Using formula (10), calculate primary-to-secondary turns ratio of the flyback transformer:

$$n = \frac{V_{OR(MAX)}}{(V_{O(MAX)} + V_F)} = \frac{115V}{(V_{O(MAX)} + V_F)} = 6.15$$

4. Using formula (4), calculate value of the current sense resistor:

$$R_s = \frac{n \cdot V_{EFF}}{I_o} = 2.48\Omega$$

5. Using formula (2), calculate value of the maximum peak current:

$$I_{PK(MAX)} = \frac{V_{CS(TH)MAX}}{R_{S(MIN)}} = \frac{V_{CS(TH)MAX}}{0.99 \cdot R_s} = 0.506A$$

6. Using formula (11), calculate maximum value of the magnetizing inductance:

$$L_m = \frac{L_{m(MAX)}}{110\%} = \frac{\Delta Q_{IN(MAX)} \cdot 0.99 R_{IN} \cdot 0.99 R_s}{V_{CS(TH)MAX} \cdot 110\%} = 770\mu H$$

7. Using formula (14), calculate turns ratio primary-to-auxiliary winding of the flyback transformer:

$$n_{AUX} = \frac{V_{IN(MIN)} \cdot V_{IN(MAX)}}{2 \cdot V_{DD(UV)} \cdot V_{IN(MAX)} - V_{IN(MIN)} \cdot V_{DD(REG)}} = 8.6$$

8. Using formulas (21) and (23), calculate values of the resistors  $R_D$ ,  $R_{BIAS}$ :

$$R_D = \frac{R_{IN}}{n_{AUX}} = 116k\Omega$$

$$R_{BIAS} = \frac{R_D}{7} = 16.6k\Omega$$

## Pin Description

| Pin # | Function | Description                                                                                                                                                                                                                                               |

|-------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | VIN      | This pin is the input voltage feed forward input. Connect a resistor from this pin to the input side of the primary winding of the transformer to program the VIN current. The same resistor is also used for start-up upon initial application of power. |

| 2     | VD       | This pin is the auxiliary winding feedback input. Connect a resistor from this pin to the transformer bootstrap winding.                                                                                                                                  |

| 3     | VDD      | This is a power supply pin for all internal circuits. It must be bypassed with a low ESR capacitor to GND. The capacitor must be able to store sufficient energy for starting up the converter.                                                           |

| 4     | CS       | This pin is for sensing peak output voltage at an external current sense resistor..                                                                                                                                                                       |

| 5     | GATE     | This pin is the output gate driver for an external N-channel power MOSFET.                                                                                                                                                                                |

| 6     | BIAS     | This pin is used for generating a correction current to account for the 2.44V offset at VD. Connect a resistor to ground to program.                                                                                                                      |

| 7     | PWMD     | When this pin is pulled to GND, switching of the HV9971 is disabled. When the PWM pin is released, or external TTL high level is applied to it, switching will resume.                                                                                    |

| 8     | GND      | This pin is the common return for all the internal circuits.                                                                                                                                                                                              |

9. Using formula (15), calculate value of the resistor  $R_{DD}$ :

$$R_{DD} = \frac{\left( \frac{V_{DD(UV)}}{V_{IN(MIN)}} - \frac{V_{DD(REG)}}{V_{IN(MAX)}} \right) \cdot n \cdot (V_{O(MIN)} + V_F) \cdot K_{Osc(MAX)}}{I_{DDQ} + Q_{GATE} \cdot \frac{(V_{O(MIN)} + V_F)}{(V_{O(MAX)} + V_F)} \cdot F_{S(MAX)}} = 358\Omega$$

(We have assumed  $Q_{GATE} = 15nC$  and  $V_{DD(MIN)} = 8V$  to account for the forward voltage drop at the bootstrap winding diode.)

10. Using formula (18), calculate the maximum power dissipation  $W_{DD}$  in the resistor  $R_{DD}$ :

$$W_{DD} = \frac{\left( \frac{V_{IN(MAX)}}{n_{AUX}} - V_{DD(REG)} \right)^2 \cdot n \cdot (V_{O(MAX)} + V_F) \cdot K_{Osc(MAX)}}{R_{DD} \cdot V_{IN(MAX)}} = 0.31W$$

11. Using formula (30), calculate the resistor  $R_{SN}$ . Assume  $C_{OSS} = 33pF$  (IRFUC20, 600V, 1A MOSFET),  $L_{LK} = 20\mu H$ :

$$C_{SN} = 33pF$$

$$R_{SN} = 1.6 \sqrt{\frac{L_{LK}}{C_{SN}}} = 1.25k\Omega$$

12. Using formula (30), calculate the maximum power dissipation  $W_{RSN}$  in the resistor  $R_{SN}$ :

$$W_{RSN} = C_{SN} \cdot V_{IN(MAX)}^2 \cdot F_{S(MAX)} = 0.6W$$

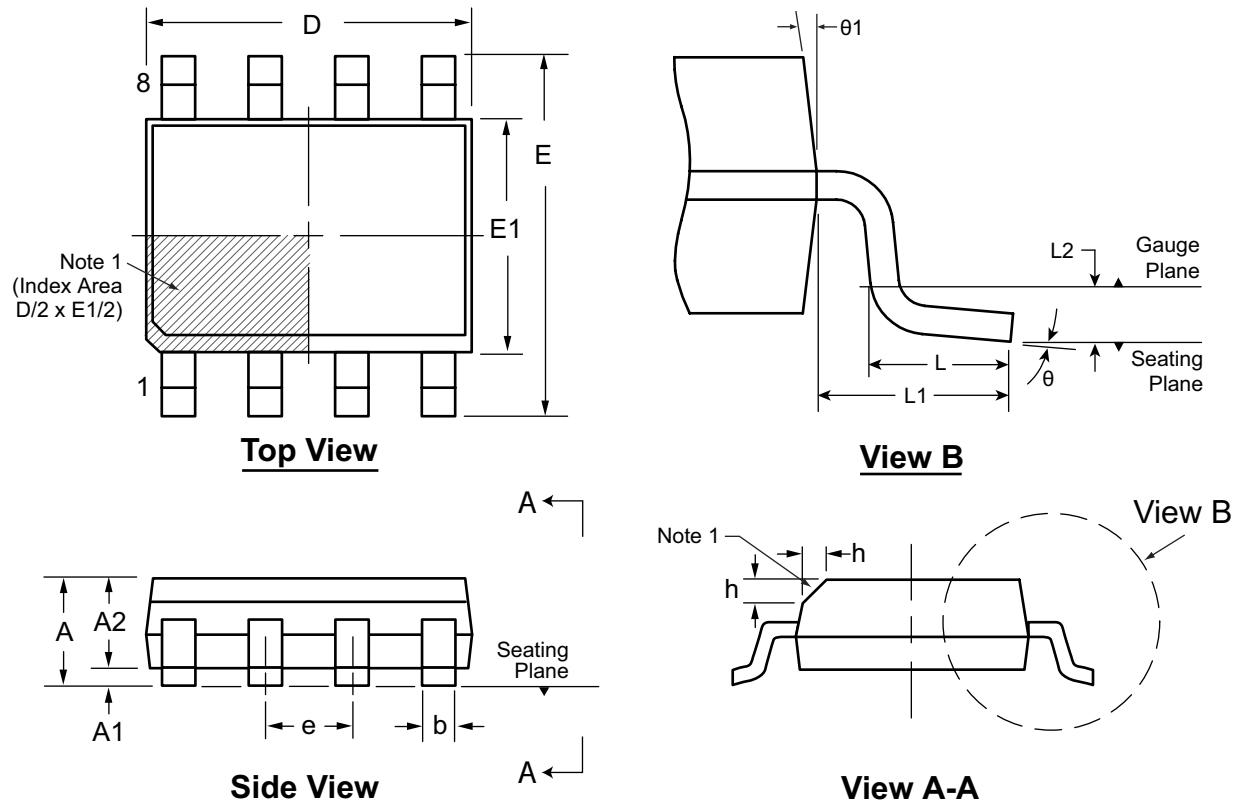

# 8-Lead SOIC (Narrow Body) Package Outline (LG)

4.90x3.90mm body, 1.75mm height (max), 1.27mm pitch

**Note:**

1. This chamfer feature is optional. A Pin 1 identifier must be located in the index area indicated. The Pin 1 identifier can be: a molded mark/identifier; an embedded metal marker; or a printed indicator.

| Symbol         | A   | A1    | A2   | b     | D    | E     | E1    | e     | h        | L    | L1   | L2       | θ  | θ1  |

|----------------|-----|-------|------|-------|------|-------|-------|-------|----------|------|------|----------|----|-----|

| Dimension (mm) | MIN | 1.35* | 0.10 | 1.25  | 0.31 | 4.80* | 5.80* | 3.80* | 1.27 BSC | 0.25 | 0.40 | 1.04 REF | 0° | 5°  |

|                | NOM | -     | -    | -     | -    | 4.90  | 6.00  | 3.90  |          | -    | -    |          | -  | -   |

|                | MAX | 1.75  | 0.25 | 1.65* | 0.51 | 5.00* | 6.20* | 4.00* |          | 0.50 | 1.27 |          | 8° | 15° |

JEDEC Registration MS-012, Variation AA, Issue E, Sept. 2005.

\* This dimension is not specified in the JEDEC drawing.

Drawings are not to scale.

Supertex Doc. #: DSPP-8SOLGTG, Version I041309.

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to <http://www.supertex.com/packaging.html>.)

**Supertex inc.** does not recommend the use of its products in life support applications, and will not knowingly sell them for use in such applications unless it receives an adequate "product liability indemnification insurance agreement." **Supertex inc.** does not assume responsibility for use of devices described, and limits its liability to the replacement of the devices determined defective due to workmanship. No responsibility is assumed for possible omissions and inaccuracies. Circuitry and specifications are subject to change without notice. For the latest product specifications refer to the **Supertex inc.** (website: <http://www.supertex.com>)