## **Freescale Semiconductor**

Data Sheet: Technical Data

Document Number: DSP56367

Rev. 2.1, 1/2007

# **DSP56367**

# 24-Bit Audio Digital Signal Processor

## 1 Overview

This document briefly describes the DSP56367 24-bit digital signal processor (DSP). The DSP56367 is a member of the DSP56300 family of programmable CMOS DSPs. The DSP56367 is targeted to applications that require digital audio compression/decompression, sound field processing, acoustic equalization and other digital audio algorithms. The DSP56367 offers 150 million instructions per second (MIPS) using an internal 150 MHz clock at 1.8 V and 100 million instructions per second (MIPS) using an internal 100 MHz clock at 1.5 V.

#### **Contents**

|   | Overview                       | 1-1 |

|---|--------------------------------|-----|

| 2 | Signal/Connection Descriptions | 2-1 |

| 3 | Specifications                 | 3-1 |

| 4 | Packaging                      | 4-1 |

| 5 | Design Considerations          | 5-1 |

| 4 | Power Consumption Benchmark    | A-1 |

This document contains information on a new product. Specifications and information herein are subject to change without notice.

#### **Data Sheet Conventions** This data sheet uses the following conventions: **OVERBAR** Used to indicate a signal that is active when pulled low (For example, the RESET pin is active when low.) "asserted" Means that a high true (active high) signal is high or that a low true (active low) signal is low "deasserted" Means that a high true (active high) signal is low or that a low true (active low) signal is high **Examples:** Signal/Symbol **Logic State** Signal State Voltage\* PIN $V_{IL} / V_{OL}$ True Asserted PIN False Deasserted V<sub>IH</sub> / V<sub>OH</sub> PIN True Asserted VIH / VOH PIN False Deasserted $V_{IL} / V_{OL}$ Note:\*Values for $V_{IL}$ , $V_{OL}$ , $V_{IH}$ , and $V_{OH}$ are defined by individual product specifications.

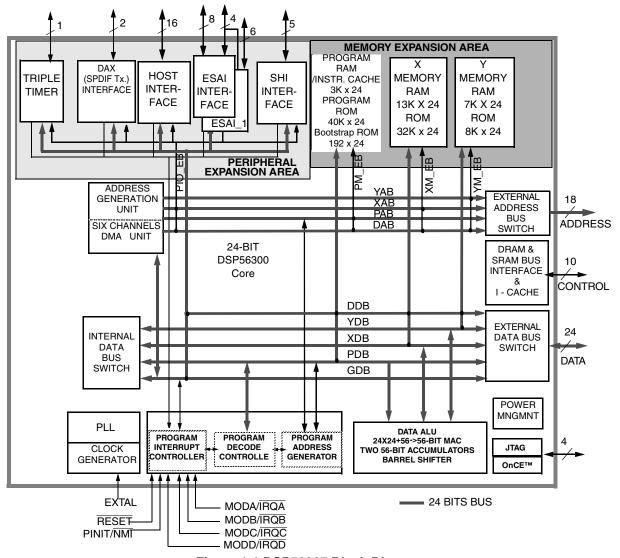

Figure 1-1 DSP56367 Block Diagram

DSP56367 Technical Data, Rev. 2.1

1-2 Freescale Semiconductor

### 1.1 Features

Core features are described fully in the *DSP56300 Family Manual*.

### 1.2 DSP56300 modular chassis

- 150 Million Instructions Per Second (MIPS) with a 150 MHz clock at internal logic supply (QVCCL) of 1.8V.

- 100 Million Instructions Per Second (MIPS) with a 100 MHz clock at internal logic supply (QVCCL) of 1.5V.

- Object Code Compatible with the 56K core.

- Data ALU with a 24 × 24 bit multiplier-accumulator and a 56-bit barrel shifter. 16-bit arithmetic support.

- Program Control with position independent code support and instruction cache support.

- Six-channel DMA controller.

- PLL based clocking with a wide range of frequency multiplications (1 to 4096), predivider factors (1 to 16) and power saving clock divider (2<sup>i</sup>: i=0 to 7). Reduces clock noise.

- Internal address tracing support and OnCE™ for Hardware/Software debugging.

- JTAG port.

- Very low-power CMOS design, fully static design with operating frequencies down to DC.

- STOP and WAIT low-power standby modes.

## 1.3 On-chip Memory Configuration

- $7K \times 24$  Bit Y-Data RAM and  $8K \times 24$  Bit Y-Data ROM.

- 13K × 24 Bit X-Data RAM and 32K × 24 Bit X-Data ROM.

- $40K \times 24$  Bit Program ROM.

- 3K × 24 Bit Program RAM and 192x24 Bit Bootstrap ROM. 1K of Program RAM may be used as Instruction Cache or for Program ROM patching.

- 2K × 24 Bit from Y Data RAM and 5K × 24 Bit from X Data RAM can be switched to Program RAM resulting in up to 10K × 24 Bit of Program RAM.

## 1.4 Off-chip memory expansion

- External Memory Expansion Port.

- Off-chip expansion up to two 16M x 24-bit word of Data memory.

- Off-chip expansion up to 16M x 24-bit word of Program memory.

- Simultaneous glueless interface to SRAM and DRAM.

## 1.5 Peripheral modules

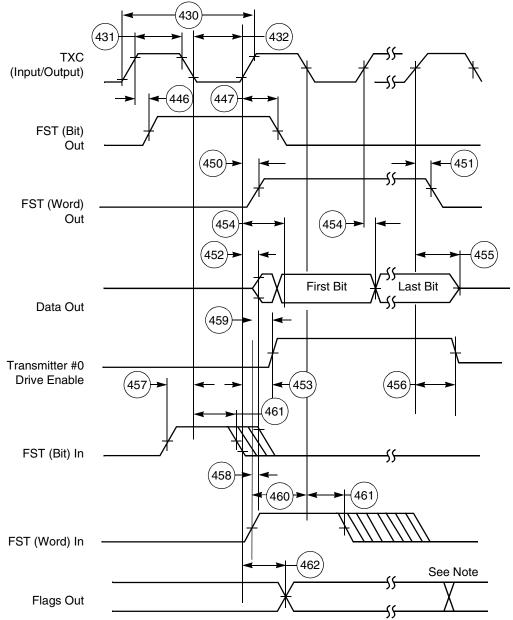

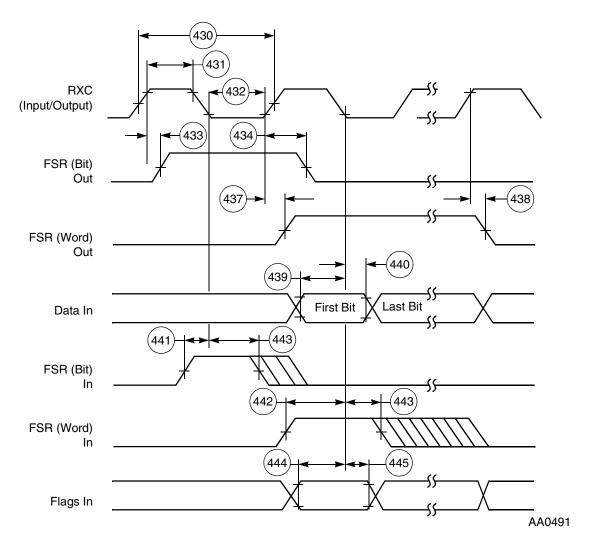

• Serial Audio Interface (ESAI): up to 4 receivers and up to 6 transmitters, master or slave. I<sup>2</sup>S, Sony, AC97, network and other programmable protocols.

#### Overview

- Serial Audio Interface I(ESAI\_1): up to 4 receivers and up to 6 transmitters, master or slave. I<sup>2</sup>S, Sony, AC97, network and other programmable protocols

The ESAI\_1 shares four of the data pins with ESAI, and ESAI\_1 does NOT support HCKR and HCKT (high frequency clocks)

- Serial Host Interface (SHI): SPI and I<sup>2</sup>C protocols, multi master capability, 10-word receive FIFO, support for 8, 16 and 24-bit words.

- Byte-wide parallel Host Interface (HDI08) with DMA support.

- Triple Timer module (TEC).

- Digital Audio Transmitter (DAX): 1 serial transmitter capable of supporting the SPDIF, IEC958, CP-340 and AES/EBU digital audio formats.

- Pins of unused peripherals (except SHI) may be programmed as GPIO lines.

## 1.6 144-pin plastic LQFP package

### 1.7 Documentation

Table 1-1 lists the documents that provide a complete description of the DSP56367 and are required to design properly with the part. Documentation is available from a local Freescale distributor, a Freescale semiconductor sales office, a Freescale Literature Distribution Center, or through the Freescale DSP home page on the Internet (the source for the latest information).

**Description Order Number Document Name** DSP56300 Family Manual Detailed description of the 56000-family architecture DSP56300FM and the 24-bit core processor and instruction set DSP56367 Product Brief Brief description of the chip DSP56367P DSP56367 User's Manual DSP56367 User's Manual DSP56367UM DSP56367 Technical Data Sheet Electrical and timing specifications; pin and package DSP56367 (this document) descriptions **IBIS Model** Input Output Buffer Information Specification For software or simulation models, contact sales or go to www.freescale.com.

Table 1-1 DSP56367 Documentation

1-4 Freescale Semiconductor

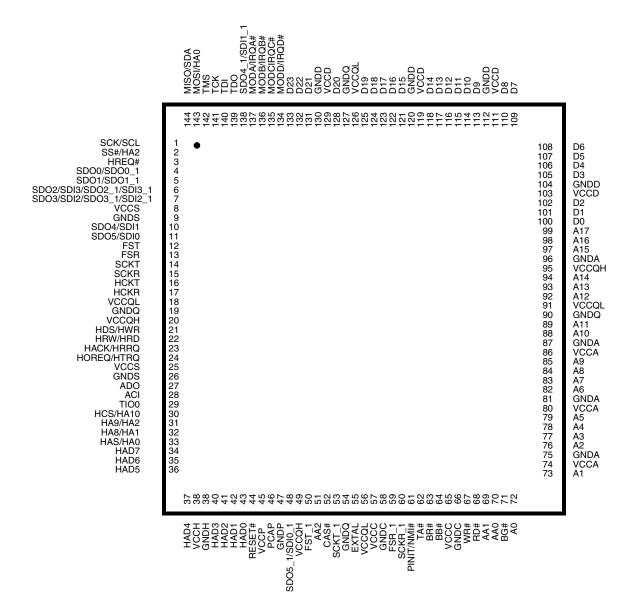

# 2 Signal/Connection Descriptions

## 2.1 Signal Groupings

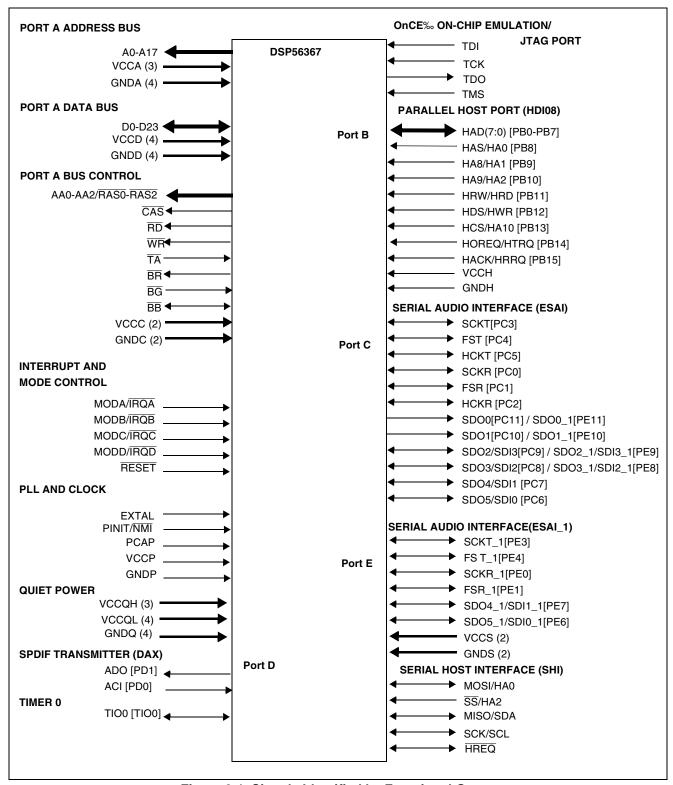

The input and output signals of the DSP56367 are organized into functional groups, which are listed in Table 2-1 and illustrated in Figure 2-1.

The DSP56367 is operated from a 1.8V supply; however, some of the inputs can tolerate 3.3V. A special notice for this feature is added to the signal descriptions of those inputs.

Remember, the DSP56367 offers 150 million instructions per second (MIPS) using an internal 150 MHz clock at 1.8 V and 100 million instructions per second (MIPS) using an internal 100 MHz clock at 1.3.3V.

Table 2-1 DSP56367 Functional Signal Groupings

| Functional Group                | Number of<br>Signals | Detailed<br>Description |            |  |  |

|---------------------------------|----------------------|-------------------------|------------|--|--|

| Power (V <sub>CC</sub> )        |                      | 20                      | Table 2-2  |  |  |

| Ground (GND)                    |                      | 18                      | Table 2-3  |  |  |

| Clock and PLL                   |                      | 3                       | Table 2-4  |  |  |

| Address bus                     |                      | 18                      | Table 2-5  |  |  |

| Data bus                        | Port A <sup>1</sup>  | 24                      | Table 2-6  |  |  |

| Bus control                     |                      | 10                      | Table 2-7  |  |  |

| Interrupt and mode control      | 5                    | Table 2-8               |            |  |  |

| HDI08                           | Port B <sup>2</sup>  | 16                      | Table 2-9  |  |  |

| SHI                             | SHI                  |                         |            |  |  |

| ESAI                            | Port C <sup>3</sup>  | 12                      | Table 2-11 |  |  |

| ESAI_1                          | Port E <sup>4</sup>  | 6                       | Table 2-12 |  |  |

| Digital audio transmitter (DAX) | 2                    | Table 2-13              |            |  |  |

| Timer                           | 1                    | Table 2-14              |            |  |  |

| JTAG/OnCE Port                  | 4                    | Table 2-15              |            |  |  |

<sup>&</sup>lt;sup>1</sup> Port A is the external memory interface port, including the external address bus, data bus, and control signals.

<sup>&</sup>lt;sup>2</sup> Port B signals are the GPIO port signals which are multiplexed with the HDI08 signals.

<sup>&</sup>lt;sup>3</sup> Port C signals are the GPIO port signals which are multiplexed with the ESAI signals.

<sup>&</sup>lt;sup>4</sup> Port E signals are the GPIO port signals which are multiplexed with the ESAI\_1 signals.

<sup>&</sup>lt;sup>5</sup> Port D signals are the GPIO port signals which are multiplexed with the DAX signals.

Figure 2-1 Signals Identified by Functional Group

2-2 Freescale Semiconductor

## 2.2 Power

**Table 2-2 Power Inputs**

| Power Name            | Description                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| V <sub>CCP</sub>      | <b>PLL Power</b> — $V_{CCP}$ is $V_{CC}$ dedicated for PLL use. The voltage should be well-regulated and the input should be provided with an extremely low impedance path to the $V_{CC}$ power rail. There is one $V_{CCP}$ input.                                                                                                          |  |  |  |  |  |

| V <sub>CCQL</sub> (4) | <b>Quiet Core (Low) Power</b> — $V_{CCQL}$ is an isolated power for the internal processing logic. This input must be tied externally to all other $V_{CCQL}$ power pins and the $V_{CCP}$ power pin only. Do not tie with other power pins. The user must provide adequate external decoupling capacitors. There are four $V_{CCQL}$ inputs. |  |  |  |  |  |

| V <sub>CCQH</sub> (3) | Quiet External (High) Power—V <sub>CCQH</sub> is a quiet power source for I/O lines. This input must be tied externally to all other chip power inputs. The user must provide adequate decoupling capacitors. There are three V <sub>CCQH</sub> inputs.                                                                                       |  |  |  |  |  |

| V <sub>CCA</sub> (3)  | <b>Address Bus Power</b> —V <sub>CCA</sub> is an isolated power for sections of the address bus I/O drivers. This input must be tied externally to all other chip power inputs. The user must provide adequate external decoupling capacitors. There are three V <sub>CCA</sub> inputs.                                                       |  |  |  |  |  |

| V <sub>CCD</sub> (4)  | <b>Data Bus Power</b> —V <sub>CCD</sub> is an isolated power for sections of the data bus I/O drivers. This input must be tied externally to all other chip power inputs. The user must provide adequate external decoupling capacitors. There are four V <sub>CCD</sub> inputs.                                                              |  |  |  |  |  |

| V <sub>CCC</sub> (2)  | <b>Bus Control Power</b> —V <sub>CCC</sub> is an isolated power for the bus control I/O drivers. This input must be tied externally to all other chip power inputs. The user must provide adequate external decoupling capacitors. There are two V <sub>CCC</sub> inputs.                                                                     |  |  |  |  |  |

| V <sub>CCH</sub>      | <b>Host Power</b> —V <sub>CCH</sub> is an isolated power for the HDI08 I/O drivers. This input must be tied externally to all other chip power inputs. The user must provide adequate external decoupling capacitors. There is one V <sub>CCH</sub> input.                                                                                    |  |  |  |  |  |

| V <sub>CCS</sub> (2)  | SHI, ESAI, ESAI_1, DAX and Timer Power —V <sub>CCS</sub> is an isolated power for the SHI, ESAI, ESAI_1, DAX and Timer. This input must be tied externally to all other chip power inputs. The user must provide adequate external decoupling capacitors. There are two V <sub>CCS</sub> inputs.                                              |  |  |  |  |  |

# 2.3 Ground

Table 2-3 Grounds

| <b>Ground Name</b>   | Description                                                                                                                                                                                                                                                                                                                       |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GND <sub>P</sub>     | <b>PLL Ground</b> —GND <sub>P</sub> is a ground dedicated for PLL use. The connection should be provided with an extremely low-impedance path to ground. $V_{CCP}$ should be bypassed to GND <sub>P</sub> by a 0.47 $\mu$ F capacitor located as close as possible to the chip package. There is one GND <sub>P</sub> connection. |

| GND <sub>Q</sub> (4) | $\begin{tabular}{ll} \textbf{Quiet Ground} — GND_Q is an isolated ground for the internal processing logic. This connection must be tied externally to all other chip ground connections. The user must provide adequate external decoupling capacitors. There are four GND_Q connections. \end{tabular}$                         |

| GND <sub>A</sub> (4) | <b>Address Bus Ground</b> —GND <sub>A</sub> is an isolated ground for sections of the address bus I/O drivers. This connection must be tied externally to all other chip ground connections. The user must provide adequate external decoupling capacitors. There are four GND <sub>A</sub> connections.                          |

| GND <sub>D</sub> (4) | <b>Data Bus Ground</b> —GND <sub>D</sub> is an isolated ground for sections of the data bus I/O drivers. This connection must be tied externally to all other chip ground connections. The user must provide adequate external decoupling capacitors. There are four GND <sub>D</sub> connections.                                |

DSP56367 Technical Data, Rev. 2.1

Table 2-3 Grounds (continued)

| <b>Ground Name</b>   | Description                                                                                                                                                                                                                                                                                                       |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GND <sub>C</sub> (2) | <b>Bus Control Ground</b> — $GND_C$ is an isolated ground for the bus control I/O drivers. This connection must be tied externally to all other chip ground connections. The user must provide adequate external decoupling capacitors. There are two $GND_C$ connections.                                        |

| GND <sub>H</sub>     | <b>Host Ground</b> —GND <sub>h</sub> is an isolated ground for the HD08 I/O drivers. This connection must be tied externally to all other chip ground connections. The user must provide adequate external decoupling capacitors. There is one GND <sub>H</sub> connection.                                       |

| GND <sub>S</sub> (2) | SHI, ESAI, ESAI_1, DAX and Timer Ground—GND <sub>S</sub> is an isolated ground for the SHI, ESAI, ESAI_1, DAX and Timer. This connection must be tied externally to all other chip ground connections. The user must provide adequate external decoupling capacitors. There are two GND <sub>S</sub> connections. |

### 2.4 Clock and PLL

Table 2-4 Clock and PLL Signals

| Signal Name | Туре  | State During<br>Reset | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------|-------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EXTAL       | Input | Input                 | External Clock Input—An external clock source must be connected to EXTAL in order to supply the clock to the internal clock generator and PLL.                                                                                                                                                                                                                                                                                          |

| PCAP        | Input | Input                 | <b>PLL Capacitor</b> —PCAP is an input connecting an off-chip capacitor to the PLL filter. Connect one capacitor terminal to PCAP and the other terminal to $V_{CCP}$ If the PLL is not used, PCAP may be tied to $V_{CC}$ , GND, or left floating.                                                                                                                                                                                     |

| PINIT/NMI   | Input | Input                 | PLL Initial/Nonmaskable Interrupt—During assertion of RESET, the value of PINIT/NMI is written into the PLL Enable (PEN) bit of the PLL control register, determining whether the PLL is enabled or disabled. After RESET de assertion and during normal instruction processing, the PINIT/NMI Schmitt-trigger input is a negative-edge-triggered nonmaskable interrupt (NMI) request internally synchronized to internal system clock. |

# 2.5 External Memory Expansion Port (Port A)

When the DSP56367 enters a low-power standby mode (stop or wait), it releases bus mastership and tri-states the relevant port A signals: A0–A17, D0–D23, AA0/ $\overline{RAS0}$ –AA2/ $\overline{RAS2}$ ,  $\overline{RD}$ ,  $\overline{WR}$ ,  $\overline{BB}$ ,  $\overline{CAS}$ .

### 2.6 External Address Bus

Table 2-5 External Address Bus Signals

| Signal Name | Туре   | State During<br>Reset | Signal Description                                                                                                                                                                                                                                                                                      |

|-------------|--------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A0-A17      | Output | Tri-Stated            | Address Bus—When the DSP is the bus master, A0–A17 are active-high outputs that specify the address for external program and data memory accesses. Otherwise, the signals are tri-stated. To minimize power dissipation, A0–A17 do not change state when external memory spaces are not being accessed. |

DSP56367 Technical Data, Rev. 2.1

2-4 Freescale Semiconductor

### 2.7 External Data Bus

Table 2-6 External Data Bus Signals

| Signal Name | Туре         | State during<br>Reset | Signal Description                                                                                                                                                                                                            |

|-------------|--------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D0-D23      | Input/Output | Tri-Stated            | <b>Data Bus</b> —When the DSP is the bus master, D0–D23 are active-high, bidirectional input/outputs that provide the bidirectional data bus for external program and data memory accesses. Otherwise, D0–D23 are tri-stated. |

## 2.8 External Bus Control

Table 2-7 External Bus Control Signals

| Signal Name           | Туре   | State During<br>Reset | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----------------------|--------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AA0-AA2/<br>RAS0-RAS2 | Output | Tri-Stated            | Address Attribute or Row Address Strobe—When defined as AA, these signals can be used as chip selects or additional address lines. When defined as $\overline{RAS}$ , these signals can be used as $\overline{RAS}$ for DRAM interface. These signals are tri-statable outputs with programmable polarity.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| CAS                   | Output | Tri-Stated            | <b>Column Address Strobe</b> — When the DSP is the bus master, $\overline{\text{CAS}}$ is an active-low output used by DRAM to strobe the column address. Otherwise, if the bus mastership enable (BME) bit in the DRAM control register is cleared, the signal is tri-stated.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| RD                    | Output | Tri-Stated            | <b>Read Enable</b> —When the DSP is the bus master, $\overline{RD}$ is an active-low output that is asserted to read external memory on the data bus (D0-D23). Otherwise, $\overline{RD}$ is tri-stated.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| WR                    | Output | Tri-Stated            | <b>Write Enable</b> —When the DSP is the bus master, $\overline{WR}$ is an active-low output that is asserted to write external memory on the data bus (D0-D23). Otherwise, $\overline{WR}$ is tri-stated.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| TA                    | Input  | Ignored Input         | <b>Transfer Acknowledge</b> —If the DSP is the bus master and there is no external bus activity, or the DSP is not the bus master, the $\overline{\text{TA}}$ input is ignored. The $\overline{\text{TA}}$ input is a data transfer acknowledge (DTACK) function that can extend an external bus cycle indefinitely. Any number of wait states (1, 2infinity) may be added to the wait states inserted by the BCR by keeping $\overline{\text{TA}}$ deasserted. In typical operation, $\overline{\text{TA}}$ is deasserted at the start of a bus cycle, is asserted to enable completion of the bus cycle, and is deasserted before the next bus cycle. The current bus cycle completes one clock period after $\overline{\text{TA}}$ is asserted synchronous to the internal system clock. The number of wait states is determined by the $\overline{\text{TA}}$ input or by the bus control register (BCR), whichever is longer. The BCR can be used to set the minimum number of wait states in external bus cycles. In order to use the $\overline{\text{TA}}$ functionality, the BCR must be programmed to at least one wait state. A zero wait state access cannot be extended by $\overline{\text{TA}}$ deassertion, otherwise improper operation may result. $\overline{\text{TA}}$ can operate synchronously or asynchronously, depending on the setting of the TAS bit in the operating mode register (OMR). $\overline{\text{TA}}$ functionality may not be used while performing DRAM type accesses, otherwise improper operation may result. |

#### **Interrupt and Mode Control**

Table 2-7 External Bus Control Signals (continued)

| Signal Name | Туре             | State During<br>Reset  | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-------------|------------------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

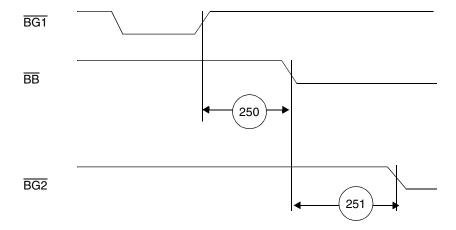

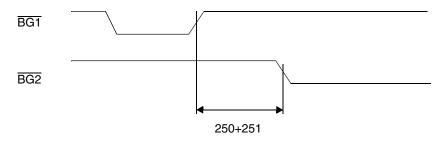

| BR          | Output           | Output<br>(deasserted) | Bus Request— $\overline{BR}$ is an active-low output, never tri-stated. $\overline{BR}$ is asserted when the DSP requests bus mastership. $\overline{BR}$ is deasserted when the DSP no longer needs the bus. $\overline{BR}$ may be asserted or deasserted independent of whether the DSP56367 is a bus master or a bus slave. Bus "parking" allows $\overline{BR}$ to be deasserted even though the DSP56367 is the bus master. (See the description of bus "parking" in the $\overline{BB}$ signal description.) The bus request hold (BRH) bit in the BCR allows $\overline{BR}$ to be asserted under software control even though the DSP does not need the bus. $\overline{BR}$ is typically sent to an external bus arbitrator that controls the priority, parking, and tenure of each master on the same external bus. $\overline{BR}$ is only affected by DSP requests for the external bus, never for the internal bus. During hardware reset, $\overline{BR}$ is deasserted and the arbitration is reset to the bus slave state. |

| BG          | Input            | Ignored Input          | <b>Bus Grant</b> — $\overline{BG}$ is an active-low input. $\overline{BG}$ is asserted by an external bus arbitration circuit when the DSP56367 becomes the next bus master. When $\overline{BG}$ is asserted, the DSP56367 must wait until $\overline{BB}$ is deasserted before taking bus mastership. When $\overline{BG}$ is deasserted, bus mastership is typically given up at the end of the current bus cycle. This may occur in the middle of an instruction that requires more than one external bus cycle for execution.  For proper $\overline{BG}$ operation, the asynchronous bus arbitration enable bit (ABE) in the OMR register must be set.                                                                                                                                                                                                                                                                                                                                                                                |

| BB          | Input/<br>Output | Input                  | Bus Busy—BB is a bidirectional active-low input/output. BB indicates that the bus is active. Only after BB is deasserted can the pending bus master become the bus master (and then assert the signal again). The bus master may keep BB asserted after ceasing bus activity regardless of whether BR is asserted or deasserted. This is called "bus parking" and allows the current bus master to reuse the bus without rearbitration until another device requires the bus. The deassertion of BB is done by an "active pull-up" method (i.e., BB is driven high and then released and held high by an external pull-up resistor).  For proper BB operation, the asynchronous bus arbitration enable bit (ABE) in the OMR register must be set.  BB requires an external pull-up resistor.                                                                                                                                                                                                                                                |

# 2.9 Interrupt and Mode Control

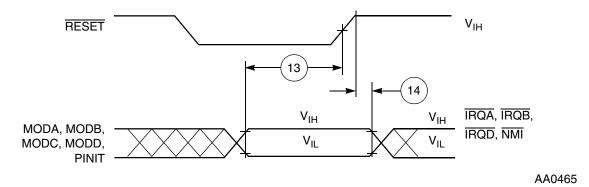

The interrupt and mode control signals select the chip's operating mode as it comes out of hardware reset. After RESET is deasserted, these inputs are hardware interrupt request lines.

2-6 Freescale Semiconductor

**Table 2-8 Interrupt and Mode Control**

| Signal Name | Туре  | State During<br>Reset | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-------------|-------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MODA/ĪRQĀ   | Input | Input                 | Mode Select A/External Interrupt Request A—MODA/IRQA is an active-low Schmitt-trigger input, internally synchronized to the DSP clock. MODA/IRQA selects the initial chip operating mode during hardware reset and becomes a level-sensitive or negative-edge-triggered, maskable interrupt request input during normal instruction processing. MODA, MODB, MODC, and MODD select one of 16 initial chip operating modes, latched into the OMR when the RESET signal is deasserted. If the processor is in the stop standby state and the MODA/IRQA pin is pulled to GND, the processor will exit the stop state.  This input is 3.3V tolerant. |

| MODB/ĪRQB   | Input | Input                 | Mode Select B/External Interrupt Request B—MODB/IRQB is an active-low Schmitt-trigger input, internally synchronized to the DSP clock. MODB/IRQB selects the initial chip operating mode during hardware reset and becomes a level-sensitive or negative-edge-triggered, maskable interrupt request input during normal instruction processing. MODA, MODB, MODC, and MODD select one of 16 initial chip operating modes, latched into OMR when the RESET signal is deasserted.  This input is 3.3V tolerant.                                                                                                                                   |

| MODC/ĪRQC   | Input | Input                 | Mode Select C/External Interrupt Request C—MODC/IRQC is an active-low Schmitt-trigger input, internally synchronized to the DSP clock. MODC/IRQC selects the initial chip operating mode during hardware reset and becomes a level-sensitive or negative-edge-triggered, maskable interrupt request input during normal instruction processing. MODA, MODB, MODC, and MODD select one of 16 initial chip operating modes, latched into OMR when the RESET signal is deasserted.  This input is 3.3V tolerant.                                                                                                                                   |

| MODD/ĪRQD   | Input | Input                 | Mode Select D/External Interrupt Request D—MODD/IRQD is an active-low Schmitt-trigger input, internally synchronized to the DSP clock. MODD/IRQD selects the initial chip operating mode during hardware reset and becomes a level-sensitive or negative-edge-triggered, maskable interrupt request input during normal instruction processing. MODA, MODB, MODC, and MODD select one of 16 initial chip operating modes, latched into OMR when the RESET signal is deasserted.  This input is 3.3V tolerant.                                                                                                                                   |

| RESET       | Input | Input                 | Reset—RESET is an active-low, Schmitt-trigger input. When asserted, the chip is placed in the Reset state and the internal phase generator is reset. The Schmitt-trigger input allows a slowly rising input (such as a capacitor charging) to reset the chip reliably. When the RESET signal is deasserted, the initial chip operating mode is latched from the MODA, MODB, MODC, and MODD inputs. The RESET signal must be asserted during power up. A stable EXTAL signal must be supplied while RESET is being asserted.  This input is 3.3V tolerant.                                                                                       |

Parallel Host Interface (HDI08)

## 2.10 Parallel Host Interface (HDI08)

The HDI08 provides a fast, 8-bit, parallel data port that may be connected directly to the host bus. The HDI08 supports a variety of standard buses and can be directly connected to a number of industry standard microcomputers, microprocessors, DSPs, and DMA hardware.

Table 2-9 Host Interface

| Signal Name | Туре                           | State During<br>Reset | Signal Description                                                                                                                                                                                                                                                                            |

|-------------|--------------------------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| H0-H7       | Input/<br>Output               | GPIO<br>Disconnected  | Host Data—When HDI08 is programmed to interface a nonmultiplexed host bus and the HI function is selected, these signals are lines 0–7 of the bidirectional, tri-state data bus.                                                                                                              |

| HAD0-HAD7   | Input/<br>Output               |                       | <b>Host Address/Data</b> —When HDI08 is programmed to interface a multiplexed host bus and the HI function is selected, these signals are lines 0–7 of the address/data bidirectional, multiplexed, tri-state bus.                                                                            |

| PB0-PB7     | Input, Output, or Disconnected |                       | <b>Port B 0–7</b> —When the HDI08 is configured as GPIO, these signals are individually programmable as input, output, or internally disconnected.                                                                                                                                            |

|             |                                |                       | The default state after reset for these signals is GPIO disconnected.  These inputs are 3.3V tolerant.                                                                                                                                                                                        |

| HA0         | Input                          | GPIO<br>Disconnected  | Host Address Input 0—When the HDI08 is programmed to interface a nonmultiplexed host bus and the HI function is selected, this signal is line 0 of the host address input bus.                                                                                                                |

| HAS/HAS     | Input                          |                       | Host Address Strobe—When HDI08 is programmed to interface a multiplexed host bus and the HI function is selected, this signal is the host address strobe (HAS) Schmitt-trigger input. The polarity of the address strobe is programmable, but is configured active-low (HAS) following reset. |

| PB8         | Input, Output, or Disconnected |                       | <b>Port B 8</b> —When the HDI08 is configured as GPIO, this signal is individually programmed as input, output, or internally disconnected.                                                                                                                                                   |

|             |                                |                       | The default state after reset for this signal is GPIO disconnected.  This input is 3.3V tolerant.                                                                                                                                                                                             |

| HA1         | Input                          | GPIO<br>Disconnected  | Host Address Input 1—When the HDI08 is programmed to interface a nonmultiplexed host bus and the HI function is selected, this signal is line 1 of the host address (HA1) input bus.                                                                                                          |

| HA8         | Input                          |                       | <b>Host Address 8</b> —When HDI08 is programmed to interface a multiplexed host bus and the HI function is selected, this signal is line 8 of the host address (HA8) input bus.                                                                                                               |

| PB9         | Input, Output, or Disconnected |                       | <b>Port B 9</b> —When the HDI08 is configured as GPIO, this signal is individually programmed as input, output, or internally disconnected.                                                                                                                                                   |

|             |                                |                       | The default state after reset for this signal is GPIO disconnected.  This input is 3.3V tolerant.                                                                                                                                                                                             |

Table 2-9 Host Interface (continued)

| Signal Name | Туре                              | State During<br>Reset | Signal Description                                                                                                                                                                                                                                                                                  |

|-------------|-----------------------------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

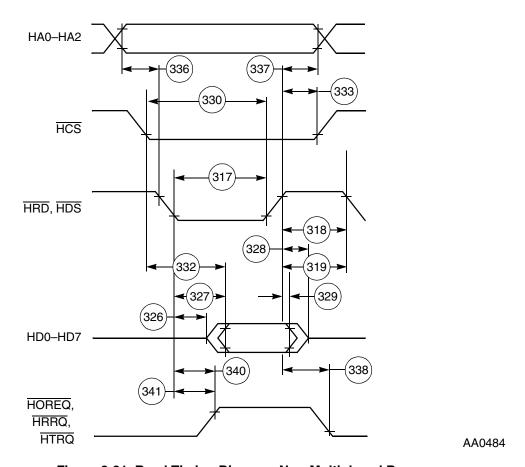

| HA2         | Input                             | GPIO<br>Disconnected  | Host Address Input 2—When the HDI08 is programmed to interface a non-multiplexed host bus and the HI function is selected, this signal is line 2 of the host address (HA2) input bus.                                                                                                               |

| HA9         | Input                             |                       | <b>Host Address 9</b> —When HDI08 is programmed to interface a multiplexed host bus and the HI function is selected, this signal is line 9 of the host address (HA9) input bus.                                                                                                                     |

| PB10        | Input, Output, or Disconnected    |                       | <b>Port B 10</b> —When the HDI08 is configured as GPIO, this signal is individually programmed as input, output, or internally disconnected.                                                                                                                                                        |

|             |                                   |                       | The default state after reset for this signal is GPIO disconnected.                                                                                                                                                                                                                                 |

|             |                                   |                       | This input is 3.3V tolerant.                                                                                                                                                                                                                                                                        |

| HRW         | Input                             | GPIO<br>Disconnected  | Host Read/Write—When HDI08 is programmed to interface a single-data-strobe host bus and the HI function is selected, this signal is the Host Read/Write (HRW) input.                                                                                                                                |

| HRD/<br>HRD | Input                             |                       | Host Read Data—When HDI08 is programmed to interface a double-data-strobe host bus and the HI function is selected, this signal is the host read data strobe (HRD) Schmitt-trigger input. The polarity of the data strobe is programmable, but is configured as active-low (HRD) after reset.       |

| PB11        | Input, Output, or<br>Disconnected |                       | <b>Port B 11</b> —When the HDI08 is configured as GPIO, this signal is individually programmed as input, output, or internally disconnected.                                                                                                                                                        |

|             |                                   |                       | The default state after reset for this signal is GPIO disconnected.                                                                                                                                                                                                                                 |

|             |                                   |                       | This input is 3.3V tolerant.                                                                                                                                                                                                                                                                        |

| HDS/<br>HDS | Input                             | GPIO<br>Disconnected  | Host Data Strobe—When HDI08 is programmed to interface a single-data-strobe host bus and the HI function is selected, this signal is the host data strobe (HDS) Schmitt-trigger input. The polarity of the data strobe is programmable, but is configured as active-low (HDS) following reset.      |

| HWR/<br>HWR | Input                             |                       | Host Write Data—When HDI08 is programmed to interface a double-data-strobe host bus and the HI function is selected, this signal is the host write data strobe (HWR) Schmitt-trigger input. The polarity of the data strobe is programmable, but is configured as active-low (HWR) following reset. |

| PB12        | Input, Output, or<br>Disconnected |                       | <b>Port B 12</b> —When the HDI08 is configured as GPIO, this signal is individually programmed as input, output, or internally disconnected.                                                                                                                                                        |

|             |                                   |                       | The default state after reset for this signal is GPIO disconnected.  This input is 3.3V tolerant.                                                                                                                                                                                                   |

### Parallel Host Interface (HDI08)

Table 2-9 Host Interface (continued)

| Signal Name     | Туре                              | State During<br>Reset | Signal Description                                                                                                                                                                                                                                                                                                                                                 |

|-----------------|-----------------------------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HCS             | Input                             | GPIO<br>Disconnected  | Host Chip Select—When HDI08 is programmed to interface a nonmultiplexed host bus and the HI function is selected, this signal is the host chip select (HCS) input. The polarity of the chip select is programmable, but is configured active-low (HCS) after reset.                                                                                                |

| HA10            | Input                             |                       | Host Address 10—When HDI08 is programmed to interface a multiplexed host bus and the HI function is selected, this signal is line 10 of the host address (HA10) input bus.                                                                                                                                                                                         |

| PB13            | Input, Output, or<br>Disconnected |                       | <b>Port B 13</b> —When the HDI08 is configured as GPIO, this signal is individually programmed as input, output, or internally disconnected.                                                                                                                                                                                                                       |

|                 |                                   |                       | The default state after reset for this signal is GPIO disconnected.                                                                                                                                                                                                                                                                                                |

|                 |                                   |                       | This input is 3.3V tolerant.                                                                                                                                                                                                                                                                                                                                       |

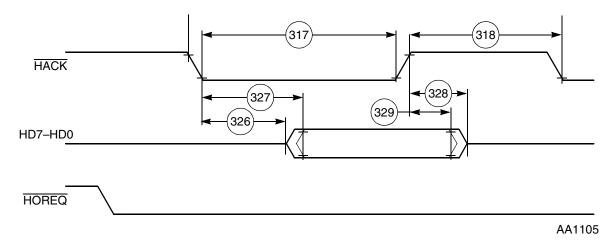

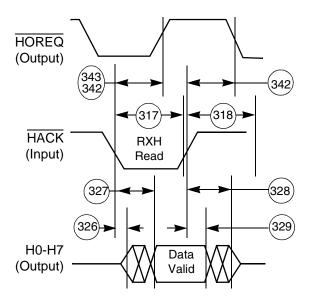

| HOREQ/<br>HOREQ | Output                            | GPIO<br>Disconnected  | Host Request—When HDI08 is programmed to interface a single host request host bus and the HI function is selected, this signal is the host request (HOREQ) output. The polarity of the host request is programmable, but is configured as active-low (HOREQ) following reset. The host request may be programmed as a driven or open-drain output.                 |

| HTRQ/<br>HTRQ   | Output                            |                       | Transmit Host Request—When HDI08 is programmed to interface a double host request host bus and the HI function is selected, this signal is the transmit host request (HTRQ) output. The polarity of the host request is programmable, but is configured as active-low (HTRQ) following reset. The host request may be programmed as a driven or open-drain output. |

| PB14            | Input, Output, or<br>Disconnected |                       | <b>Port B 14</b> —When the HDI08 is configured as GPIO, this signal is individually programmed as input, output, or internally disconnected.                                                                                                                                                                                                                       |

|                 |                                   |                       | The default state after reset for this signal is GPIO disconnected.                                                                                                                                                                                                                                                                                                |

|                 |                                   |                       | This input is 3.3V tolerant.                                                                                                                                                                                                                                                                                                                                       |

| HACK/<br>HACK   | Input                             | GPIO<br>Disconnected  | Host Acknowledge—When HDI08 is programmed to interface a single host request host bus and the HI function is selected, this signal is the host acknowledge (HACK) Schmitt-trigger input. The polarity of the host acknowledge is programmable, but is configured as active-low (HACK) after reset.                                                                 |

| HRRQ/<br>HRRQ   | Output                            |                       | Receive Host Request—When HDI08 is programmed to interface a double host request host bus and the HI function is selected, this signal is the receive host request (HRRQ) output. The polarity of the host request is programmable, but is configured as active-low (HRRQ) after reset. The host request may be programmed as a driven or open-drain output.       |

| PB15            | Input, Output, or<br>Disconnected |                       | Port B 15—When the HDI08 is configured as GPIO, this signal is individually programmed as input, output, or internally disconnected.  The default state after reset for this signal is GPIO disconnected.  This input is 3.3V tolerant.                                                                                                                            |

2-10 Freescale Semiconductor

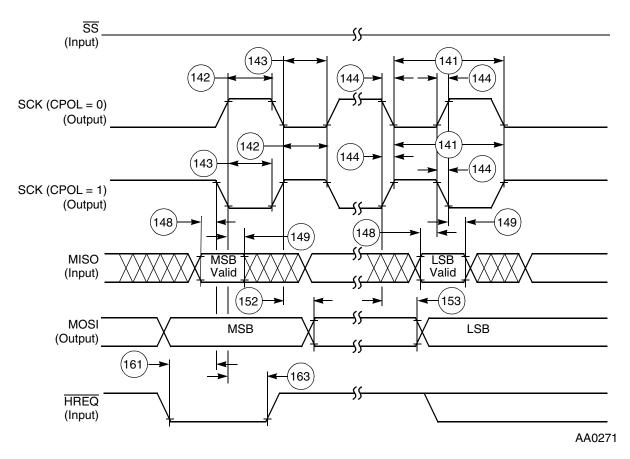

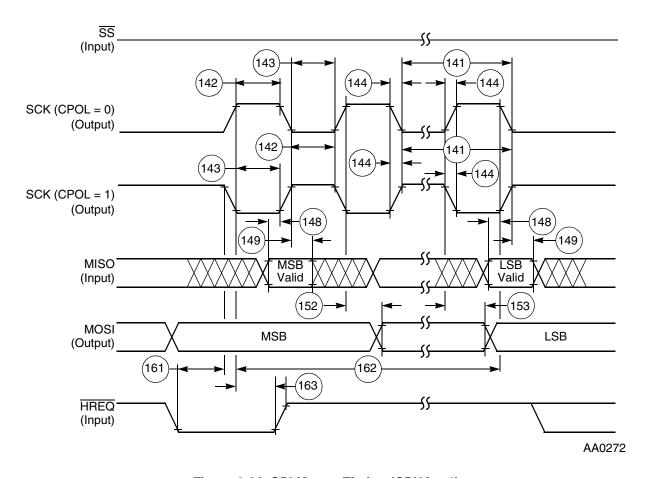

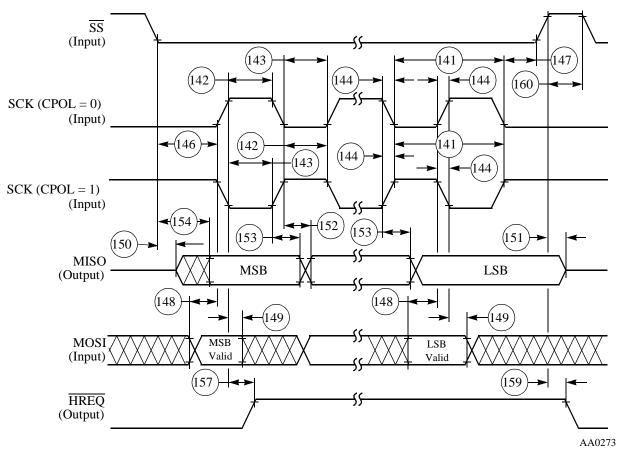

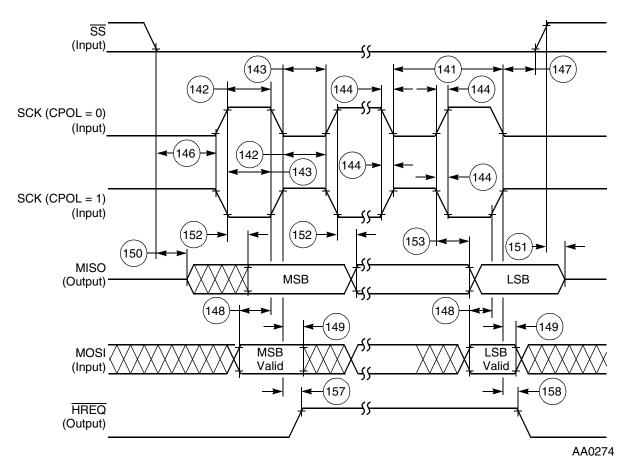

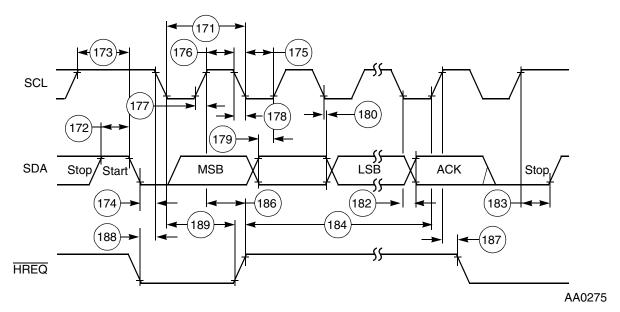

## 2.11 Serial Host Interface

The SHI has five I/O signals that can be configured to allow the SHI to operate in either SPI or  $I^2C$  mode.

Table 2-10 Serial Host Interface Signals

| Signal<br>Name | Signal<br>Type                   | State During<br>Reset | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------------|----------------------------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SCK            | Input or<br>Output               | Tri-Stated            | SPI Serial Clock—The SCK signal is an output when the SPI is configured as a master and a Schmitt-trigger input when the SPI is configured as a slave. When the SPI is configured as a master, the SCK signal is derived from the internal SHI clock generator. When the SPI is configured as a slave, the SCK signal is an input, and the clock signal from the external master synchronizes the data transfer. The SCK signal is ignored by the SPI if it is defined as a slave and the slave select (\$\overline{SS}\$) signal is not asserted. In both the master and slave SPI devices, data is shifted on one edge of the SCK signal and is sampled on the opposite edge where data is stable. Edge polarity is determined by the SPI transfer protocol. |

| SCL            | Input or<br>Output               |                       | $I^2C$ Serial Clock—SCL carries the clock for $I^2C$ bus transactions in the $I^2C$ mode. SCL is a Schmitt-trigger input when configured as a slave and an open-drain output when configured as a master. SCL should be connected to $V_{CC}$ through a pull-up resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                |                                  |                       | This signal is tri-stated during hardware, software, and individual reset. Thus, there is no need for an external pull-up in this state.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                |                                  |                       | This input is 3.3V tolerant.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| MISO           | Input or<br>Output               | Tri-Stated            | SPI Master-In-Slave-Out—When the SPI is configured as a master, MISO is the master data input line. The MISO signal is used in conjunction with the MOSI signal for transmitting and receiving serial data. This signal is a Schmitt-trigger input when configured for the SPI Master mode, an output when configured for the SPI Slave mode, and tri-stated if configured for the SPI Slave mode when SS is deasserted. An external pull-up resistor is not required for SPI operation.                                                                                                                                                                                                                                                                       |

| SDA            | Input or<br>Open-Drain<br>Output |                       | $I^2C$ Data and Acknowledge—In $I^2C$ mode, SDA is a Schmitt-trigger input when receiving and an open-drain output when transmitting. SDA should be connected to $V_{CC}$ through a pull-up resistor. SDA carries the data for $I^2C$ transactions. The data in SDA must be stable during the high period of SCL. The data in SDA is only allowed to change when SCL is low. When the bus is free, SDA is high. The SDA line is only allowed to change during the time SCL is high in the case of start and stop events. A high-to-low transition of the SDA line while SCL is high is a unique situation, and is defined as the start event. A low-to-high transition of SDA while SCL is high is a unique situation defined as the stop event.               |

|                |                                  |                       | This signal is tri-stated during hardware, software, and individual reset. Thus, there is no need for an external pull-up in this state.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                |                                  |                       | This input is 3.3V tolerant.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

#### **Serial Host Interface**

Table 2-10 Serial Host Interface Signals (continued)

| Signal<br>Name | Signal<br>Type     | State During<br>Reset | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|----------------|--------------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MOSI           | Input or<br>Output | Tri-Stated            | SPI Master-Out-Slave-In—When the SPI is configured as a master, MOSI is the master data output line. The MOSI signal is used in conjunction with the MISO signal for transmitting and receiving serial data. MOSI is the slave data input line when the SPI is configured as a slave. This signal is a Schmitt-trigger input when configured for the SPI Slave mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| HA0            | Input              |                       | I <sup>2</sup> C Slave Address 0—This signal uses a Schmitt-trigger input when configured for the I <sup>2</sup> C mode. When configured for I <sup>2</sup> C slave mode, the HA0 signal is used to form the slave device address. HA0 is ignored when configured for the I <sup>2</sup> C master mode. This signal is tri-stated during hardware, software, and individual reset. Thus, there                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                |                    |                       | is no need for an external pull-up in this state.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                |                    |                       | This input is 3.3V tolerant.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 88             | Input              | Tri-Stated            | SPI Slave Select—This signal is an active low Schmitt-trigger input when configured for the SPI mode. When configured for the SPI Slave mode, this signal is used to enable the SPI slave for transfer. When configured for the SPI master mode, this signal should be kept deasserted (pulled high). If it is asserted while configured as SPI master, a bus error condition is flagged. If SS is deasserted, the SHI ignores SCK clocks and keeps the MISO output signal in the high-impedance state.                                                                                                                                                                                                                                                                                                                                                                       |

| HA2            | Input              |                       | I <sup>2</sup> C Slave Address 2—This signal uses a Schmitt-trigger input when configured for the I <sup>2</sup> C mode. When configured for the I <sup>2</sup> C Slave mode, the HA2 signal is used to form the slave device address. HA2 is ignored in the I <sup>2</sup> C master mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                |                    |                       | This signal is tri-stated during hardware, software, and individual reset. Thus, there is no need for an external pull-up in this state.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

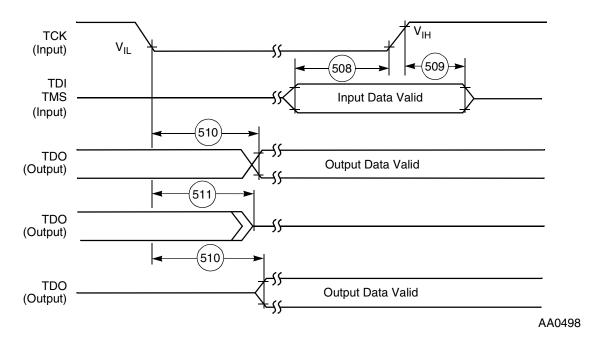

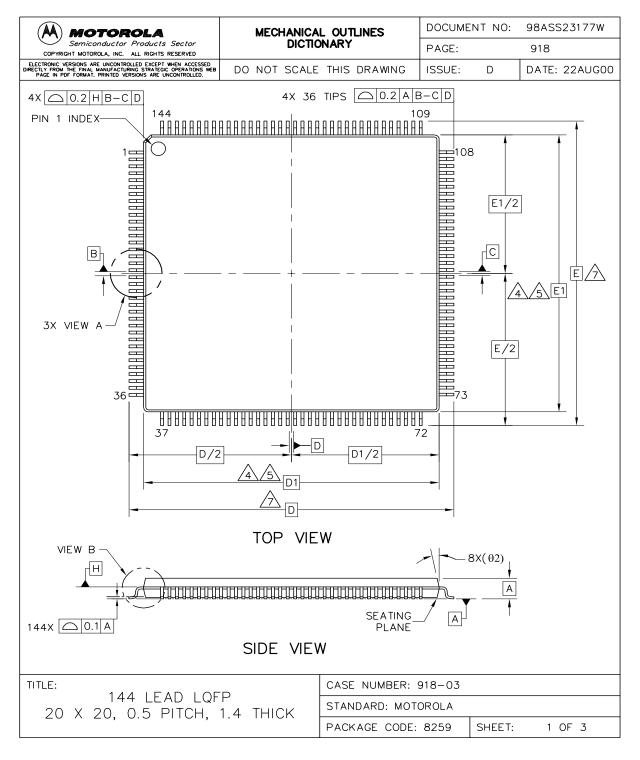

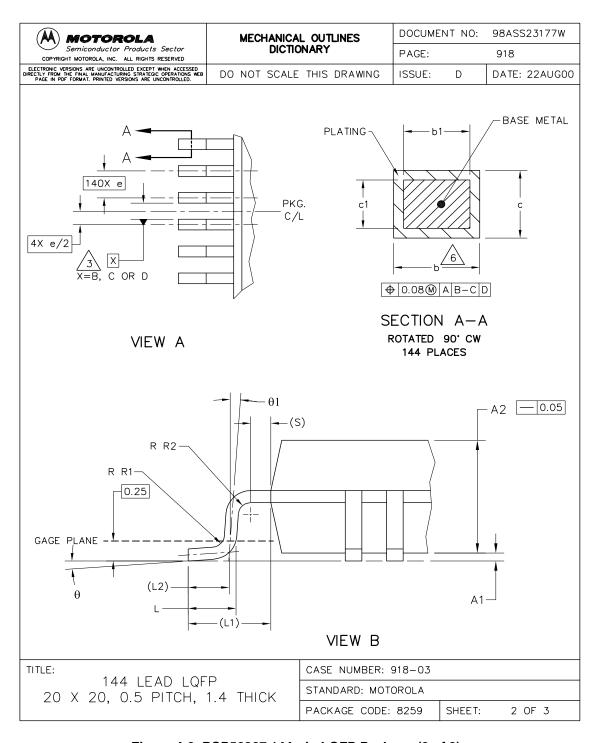

|                |                    |                       | This input is 3.3V tolerant.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |