# NM28C64/C64L/C64A 64k (8k x 8) Parallel Extended Voltage Range CMOS EEPROM

### **General Description**

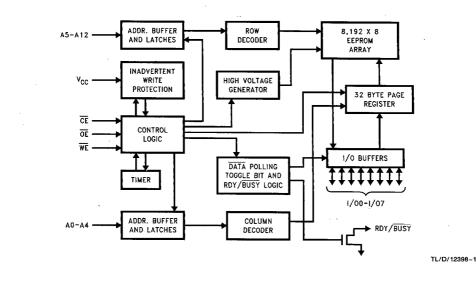

The NM28C64/C64L/C64A are fast, single-power supply CMOS EEPROM organized as 8k by 8 bits. Both READ and WRITE modes function over the full  $V_{CC}$  range of 2.7V-5.5V.

In-system programming of the part requires only a simple interface. On-chip address and data latches, self-timed write cycle with auto-clear and  $V_{\rm CC}$  power-up/down protection eliminate the need for external timing and protection hardware.

DATA and Toggle-Bit Polling and a RDY/BUSY pin provide a convenient means for determining the beginning and end of the internal self-timed WRITE cycle.

Both internal hardware and software WRITE protection are provided. Page organization permits the loading of from one to 32 bytes into a data register, the entire page is programmed at one time in 10 ms.

### **Features**

- Voltage Supply

- Full Read and Write operation

- C64: 4.5V to 5.5V

- C64L: 2.7V to 3.6V

- -- C64A: 2.7V to 5.5V

- Low Power Dissipation

- Low Power Dissipation

8 mA Active Current

- -- 50 μA CMOS Standby Current

- Read Access Time

- --- 200 ns at 2.7V

- 120 ns at 4.5V

- 32 Byte Page Write

- End of Write Detection

- DATA Polling on I/O<sub>7</sub>

- Toggle Bit Polling on I/O6

- READY/BUSY Open Drain Output

- Hardware Data Protection

- High Reliability CMOS Technology

- Endurance 100,000 Cycles

- Data Retention: 10 years

- Low Voltage CMOS and TTL Compatible Inputs and Outputs

- JEDEC Standard Byte-Wide Pinout

- Commercial and Industrial Temperature Ranges

## **Block Diagram**

4-41

http://www.national.com

**■** 6501122 0087523 220 **■**

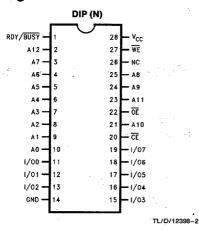

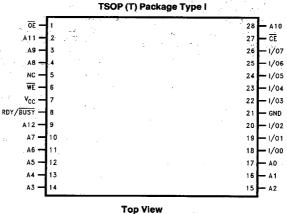

# **Pin Configurations**

| A0-A12    | Addresses           |

|-----------|---------------------|

| CE        | Chip Enable         |

| .OE       | Output Enable       |

| WE        | Write Enable        |

| 1/00-1/07 | Data Inputs/Outputs |

| RDY/BUSY  | Ready/Busy Output   |

| NC        | No Connect          |

\_\_\_\_\_

## **Ordering Information**

Commercial Temperature Range (0°C to +70°C)

| Order Number | 4.5V-5,5V |

|--------------|-----------|

| NM28C64N28   | .43       |

| NM28C64T28   |           |

| <br>Order Number | 2.7V-3.6V |

|------------------|-----------|

| NM28C64LN28      |           |

| NM28C64LT28      |           |

|                  |           |

| <br>Order Number | 2.77-5.57 |

|------------------|-----------|

| NM28C64AN28      |           |

| NM28C64AT28      |           |

|                  |           |

Extended Temperature Range (-40°C to +85°C)

TL/D/12398~3

| Order Number    | 4.5V-5.5V |

|-----------------|-----------|

| NM28C64EN28     |           |

| <br>NM28C64ET28 |           |

| • | Order Number | 2.7V-3,6V |

|---|--------------|-----------|

|   | NM28C64LEN28 |           |

| • | NM28C64LET28 |           |

| Order Number     | 2.7V-5.5V |

|------------------|-----------|

| NM28C64AEN28     |           |

| <br>NM28C64AET28 |           |

http://www.national.com

4-42

■ 6501122 0087524 167 ■

### **Functional Description**

#### **DEVICE OPERATION**

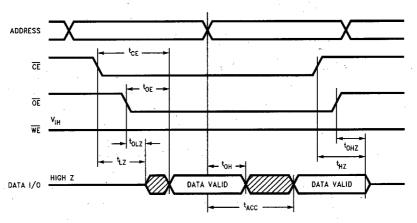

#### Read Mode

Data are transferred from the addressed memory location to the external data bus when WE is held HIGH, OE is held LOW, and CE is held LOW. The 2-line control architecture of the OE and CE pins eliminates bus contention in a system environment. When either the OE or CE lines are set HIGH, the NM28C64A releases the data bus.

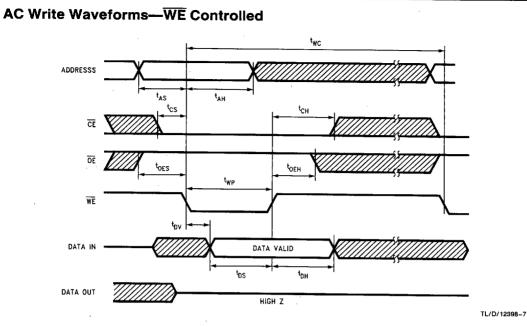

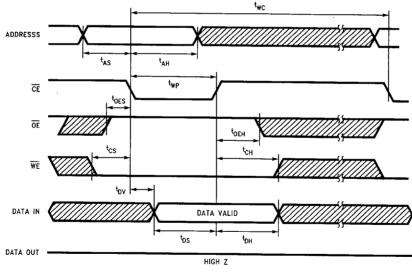

#### Write Mode

A write cycle is initiated when both the  $\overline{WE}$  and  $\overline{CE}$  lines are LOW and  $\overline{OE}$  is HIGH. The address is latched on the falling edge of either  $\overline{WE}$  or  $\overline{CE}$ , whichever occurs last. The data are latched on the rising edge of either the  $\overline{WE}$  or  $\overline{CE}$ , whichever occurs first. It takes approximately 10 ms for the write cycle to erase the addressed memory locations and store the new data.

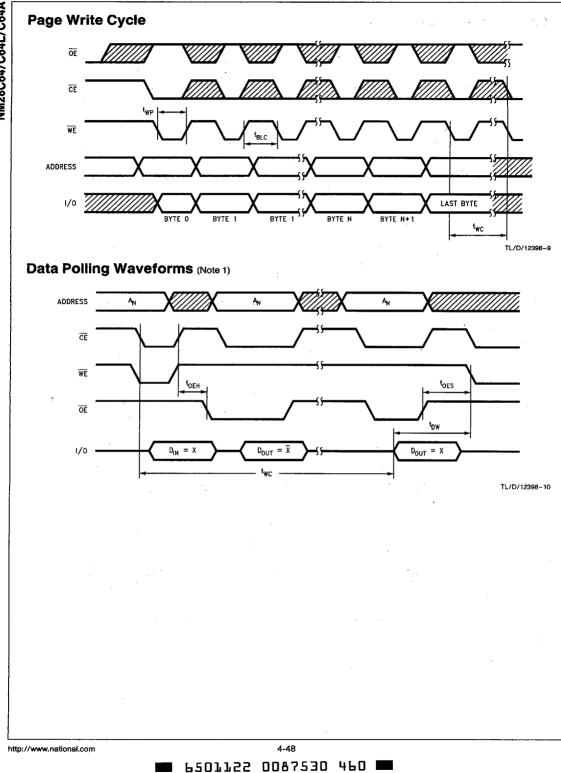

#### Page Write

From one to thirty-two bytes can be written to the selected page address (A5-A12) during any write operation. The page address is latched once the data-load cycle is started. The data latch loading may be intermpted in order to fetch data from another system location. However, data loading must continue again within the byte load cycle time (t<sub>BLC</sub>), otherwise the internal programming cycle will begin. When returning to loading data into the latches, the page address is ignored because of the latched-page register.

There are no page write window limitations; the page write window can continue indefinitely as long as the t<sub>BLC MAX</sub> time is not exceeded.

The program cycle first erases data located in the addressed cells, then writes the new data into these addressed cells. A page write does not rewrite the entire page, only those locations selected during data-latch loading.

#### **Write Abort**

During a data load cycle in preparation for programming,  $\overline{OE}$  must be held at  $V_{IH}$ . If  $\overline{OE}$  is held LOW during the rising edge of  $\overline{CE}$  ( $\overline{CE}$  controlled WRITE), or  $\overline{WE}$  ( $\overline{WE}$ -controlled WRITE), the WRITE operation is aborted and the data latches are reset.

#### RDY/BUSY

The RDY/BUSY pin is an open drain output that monitor the status of a write cycle. The open drain connection allows for OR-tying several devices to the same RDY/BUSY pin. This output is actively pulled LOW during the write cycle and released at the end of the cycle.

Additional methods for monitoring status and internal programming cycles are provided.

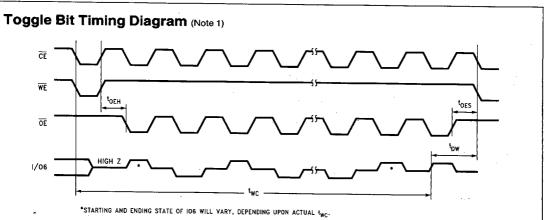

### Toggle Bit (I/O<sub>6</sub>)

The toggle bit (I/O<sub>6</sub>) toggles between ZERO and ONE on alternate READS while the NM28C64A performs an internal write cycle. After the write cycle is completed, I/O<sub>6</sub> stops togolling.

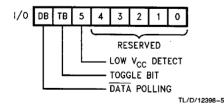

### DATA Polling (I/O<sub>7</sub>)

A third method for determining the end an internal programming cycle is DATA polling. This method allows the host to perform a simple bit test to determine whether the device is in an internal write cycle without the need for system interrupts or external hardware.

After the initiation of the internal programming cycle, bit 7 of the last byte written is complemented and sent to I/O<sub>7</sub>. The host can read I/O<sub>7</sub> to determine whether or not the device is in an internal write cycle. Upon completion of the write cycle, I/O<sub>7</sub> provides the true value.

### Low V<sub>CC</sub> Detect (I/O<sub>5</sub>)

Once an internal write cycle is initiated, it continues to completion even if the supply voltage falls below 2.0V (typical) during the cycle. In the event that  $V_{\rm CC}$  does fall below 2.0V during the programming cycle, an internal latch is set. Its status can be polled by reading the state of  $I/O_5$ .

A high level on  $1/O_5$  indicates that a sub-2.0V level was detected and programmed-data integrity may be suspect.

#### **Hardware Data Protection**

The device is protected from inadvertent memory writes by the following three hardware methods:

- V<sub>CC</sub> Sense: The write function is inhibited if V<sub>CC</sub> falls below 2.0V (typical), prior to the beginning of an internal write cycle.

- Noise Protection: A write cycle will not be initiated if the WE or CE LOW pulse is < 20 ns wide (typical).</li>

- Write Inhibit: Write cycles can be inhibited during poweron and power-off by holding any one or more of the following pins to the indicated levels.

- (a) OE LOW

- (b) CE HIGH

- (c) WE HIGH

### Chip Erase

The entire memory can be erased (set to logic ONE) by a single operation. To activate Chip Erase,  $\overline{\text{OE}}$  must be raised to 12V  $\pm$ 0.5V and all I/O pins set HIGH while  $\overline{\text{CE}}$  and  $\overline{\text{WE}}$  are simultaneously brought LOW. The erase operation occurs within 10 ms.

#### **Device Identification**

The user has an extra 32 bytes (one page) of memory available for device identification. This extra memory can be read or written to just like the regular memory array but only by setting address pin A9 to 12V  $\pm 0.5$ V and selecting addresses 1FE0h-1FFFh.

4-43

http://www.national.com

6501122 0087525 OT3 **==**

### Absolute Maximum Ratings (Note)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

Temperature Under Bias

-55°C to +125°C

Storage Temperature

-65°C to +150°C

All Input Voltage

(including NC pins)

with Respect to Ground

$-0.6 \mbox{V}$  to  $\mbox{V}_{CC}$  +  $0.6 \mbox{V}$

Lead Temperature

(Soldering, 10 seconds)

+300°C

All Output Voltages with

Respect to Ground

-0.6V to  $V_{CC} + 0.6V$

Voltage on OE and A9 with Respect to Ground

**ESD Rating**

-0.6V to +13.5V

Note: Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **DC and AC Operating Range**

|                              |         | NM28C64 NM28 |            | NM28C64A   |

|------------------------------|---------|--------------|------------|------------|

| Operating                    | Comm.   | 0°C-70°C     | 0°C-70°C   | 0°C-70°C   |

| Temperature (Case)           | Indust. | -40°C-85°C   | -40°C-85°C | -40°C-85°C |

| V <sub>CC</sub> Power Supply |         | 4.5V-5.5V    | 2.7V-3.6V  | 2.7V-5.5V  |

## **Operating Modes**

| Mode                   | CE              | ŌĒ              | WE              | 1/0              | Power   | A9        |

|------------------------|-----------------|-----------------|-----------------|------------------|---------|-----------|

| Standby                | V <sub>IH</sub> | Х               | X               | High Z           | Standby |           |

| Read                   | V <sub>IL</sub> | V <sub>IL</sub> | VIH             | Dout             | Active  |           |

| Write (WE Controlled)  | V <sub>IL</sub> | V <sub>IH</sub> | 7               | D <sub>IN</sub>  | Active  |           |

| Write (CE Controlled)  | Ъ               | V <sub>IH</sub> | V <sub>IL</sub> | D <sub>IN</sub>  | Active  |           |

| Read and Write Inhibit | V <sub>IL</sub> | V <sub>IH</sub> | VIH             | High:Z           | Active  | .*        |

| Output Disable         | Х               | V <sub>IH</sub> | Х               | High Z           |         |           |

| Chip Erase*            | V <sub>IL</sub> | 12V ± 0.5V      | 5               | DIN = VIH        | Active  |           |

| Chip ID Read           | V <sub>IL</sub> | V <sub>IL</sub> | V <sub>IH</sub> | D <sub>OUT</sub> | Active  | 12V ±0.5V |

| Chip ID Write          | V <sub>IL</sub> | V <sub>IH</sub> | V <sub>IL</sub> | D <sub>IN</sub>  | Active  | 12V ±0.5V |

<sup>\*</sup> $\overline{OE}$  must be raised to 12V prior to establishing the condition  $\overline{CE} = \overline{WE} = V_{IL}$  to initiate a chip-erase cycle.

### **DC Characteristics**

| Symbol          | Parameter                            | Test Conditions                                                     | Min  | Max | Units       |

|-----------------|--------------------------------------|---------------------------------------------------------------------|------|-----|-------------|

| I <sub>LI</sub> | Input Load Current                   | V <sub>IN</sub> = 0V to V <sub>CC</sub>                             |      | 5   | μΑ          |

| ÎLO             | Output Leakage Current               | $V_{I/O} = 0V \text{ to } V_{CC}$                                   |      | 5   | μA          |

| I <sub>SB</sub> | V <sub>CC</sub> Standby Current CMOS | CE = V <sub>CC</sub>                                                |      | 50  | μΑ          |

| loc             | V <sub>CC</sub> Active Current AC    | $f = 5 \text{ MHz}; I_{OUT} = 0 \text{ mA}; \overline{CE} = V_{IL}$ |      | 8.0 | mA          |

| $V_{IL}$ :      | Input Low Voltage                    | ÷                                                                   |      | 0.6 | <b>&gt;</b> |

| V <sub>IH</sub> | Input High Voltage                   | 1 14 6                                                              | 2.0  | 4   | ٧           |

| V <sub>OL</sub> | Output Low Voltage                   | I <sub>OL</sub> = 1 mA                                              |      | 0.3 | V           |

|                 |                                      | I <sub>OL</sub> = 2 mA for RDY/BUSY                                 |      | 0.3 | V           |

| VOH             | Output High Voltage                  | I <sub>OH</sub> = -100 μA                                           | 2.0. | 7   | ٧           |

http://www.national.com

4-44

6501122 0087526 T3T

# Capacitance (f = 1.0 MHz, $T_A = 25^{\circ}C$ )

| Symbol | Conditions     | Тур | Max | Units |

|--------|----------------|-----|-----|-------|

| CIN    | $V_{IN} = 0V$  | 4   | 6   | рF    |

| Cvo    | $V_{I/O} = 0V$ | 8   | 12  | pF    |

# AC Read Characteristics—NM28C64

| Symbol                        | Parameter                       | V <sub>CC</sub> | Min | Тур | Max  | Units |

|-------------------------------|---------------------------------|-----------------|-----|-----|------|-------|

| tACC                          | Address to Output Delay         | 4.5V-5.5V       |     |     | 120  | ns    |

| t <sub>CE</sub>               | CE to Output Delay              | 4.5V-5.5V       |     |     | 120  | ns    |

| toe                           | OE to Output Delay              | 4.5V-5.5V       | 0   |     | 50   | ns    |

| toн                           | Output Hold from Address Change | 4.5V-5.5V       | 0   |     |      | ns    |

| t <sub>LZ</sub> (Note 1)      | CE Low to Output Active         | 4.5V-5.5V       | 0   |     |      | ns    |

| t <sub>OLZ</sub> (Note 1)     | OE Low to Output Active         | 4.5V-5.5V       | 0   |     | -    | ns    |

| t <sub>HZ</sub> (Notes 1, 2)  | CE High to Output Float         | 4.5V-5.5V       |     |     | 50   | ns    |

| t <sub>OHZ</sub> (Notes 1, 2) | OE High to Output Float         | 451/-551/       |     |     | - 50 | 115   |

# AC Read Characteristics—NM28C64L

| Symbol                        | Parameter                       | Vcc       | Min | Тур | Max | Units |

|-------------------------------|---------------------------------|-----------|-----|-----|-----|-------|

| tacc                          | Address to Output Delay         | 2.7V-3.6V |     |     | 200 | ns    |

| t <sub>CE</sub>               | CE to Output Delay              | 2.7V-3.6V |     |     | 200 | ns    |

| toE                           | OE to Output Delay              | 2.7V-3.6V | 0   | ٠   | 80  | ns    |

| t <sub>ОН</sub>               | Output Hold from Address Change | 2.7V-3.6V | 0   |     |     | ns    |

| t <sub>LZ</sub> (Note 1)      | CE Low to Output Active         | 2.7V-3.6V | 0   |     |     | пѕ    |

| t <sub>OLZ</sub> (Note 1)     | OE Low to Output Active         | 2.7V-3.6V | 0   |     |     | ns    |

| t <sub>HZ</sub> (Notes 1, 2)  | CE High to Output Float         | 2.7V-3.6V |     |     | 50  | ns    |

| t <sub>OHZ</sub> (Notes 1, 2) | OE High to Output Float         | 2.7V-3.6V | -   |     | 50  | ns    |

# AC Read Characteristics—NM28C64A

| Symbol                        | Parameter                       | Vcc       | Min | Тур | Max | Units |

|-------------------------------|---------------------------------|-----------|-----|-----|-----|-------|

| tacc                          | Address to Output Delay         | 2.7V-4.4V |     |     | 200 | ns    |

|                               |                                 | 4.5V-5.5V |     |     | 120 | ns    |

| t <sub>CE</sub>               | CE to Output Delay              | 2.7V-4.4V |     |     | 200 | ns    |

|                               |                                 | 4.5V-5.5V |     |     | 120 | ns    |

| <sup>t</sup> OE               | OE to Output Delay              | 2.7V-4.4V |     |     | 80  | ns    |

|                               |                                 | 4.5V-5.5V | 0   |     | 50  | ns    |

| <sup>†</sup> ОН               | Output Hold from Address Change | 2.7V-4.4V |     |     | ••• | пѕ    |

|                               |                                 | 4.5V-5.5V |     |     |     | ns    |

| t <sub>LZ</sub> (Note 1)      | CE Low to Output Active         | 2.7V-4.4V | 0   |     |     | ns    |

|                               |                                 | 4.5V-5.5V | 0   |     |     | ns    |

| t <sub>OLZ</sub> (Note 1)     | OE Low to Output Active         | 2.7V-4.4V | 0   |     |     | ns    |

|                               |                                 | 4.5V-5.5V | 0   |     | 50  | пв    |

| t <sub>HZ</sub> (Notes 1, 2)  | CE High to Output Float         | 2.7V-4.4V |     |     | 50  | ns    |

|                               |                                 | 4.5V-5.5V |     | *   | 50  | ns    |

| t <sub>OHZ</sub> (Notes 1, 2) | OE High to Output Float         | 2.7V-4.4V |     |     | 50  | ns    |

|                               |                                 | 4.5V-5.5V |     |     | 50  | ns    |

4-45

Note 1: This parameter is characterized and is not 100% tested.

Note 2: Output floating (High Z) is defined as the state when the external data line is no longer driven by the output buffer.

6501122 0087527 976 1

http://www.national.com

## **AC Read Waveforms**

TL/D/12398-6

## **AC Write Characteristics**

| Symbol           | Parameter                           | Condition | Min   | Тур | Max | Units |

|------------------|-------------------------------------|-----------|-------|-----|-----|-------|

| twc              | Write Cycle Time                    |           |       |     | 10  | ms    |

| <sup>t</sup> AH  | Address Hold Time                   |           | 100   |     |     | ns    |

| tAS              | Address Setup                       |           | 10    | ,   |     | ns    |

| t <sub>CH</sub>  | Write Hold Time                     |           | 0     |     |     | ns    |

| tcs              | Write Setup Time                    |           | 0     |     |     | . ns  |

| t <sub>DH</sub>  | Data Hold                           |           | 10    |     |     | ns    |

| tos              | Data Setup Time                     |           | 100   |     |     | ns    |

| t <sub>OEH</sub> | OE High Hold Time                   |           | 10    |     |     | ns    |

| t <sub>OES</sub> | OE High Setup Time                  |           | 10    |     |     | ns    |

| t <sub>RB</sub>  | WE Low to RSY/BUSY Low              |           |       |     | 120 | ns    |

| t <sub>WP</sub>  | Write Pulse Width (WE or CE)        | ,         | - 150 |     |     | ns    |

| t <sub>BLC</sub> | Byte Load Cycle Time                |           | 1     |     | 100 | μs    |

| tiNIT            | Write Inhibit Period after Power Up |           | 5     |     | 15  | ms    |

http://www.national.com

4-46

■ 6501122 0087528 802 |

# AC Write Waveforms—CE Controlled

TL/D/12398-8

<sup>4-47</sup> ■ **6**501122 0087529 749 **■**

TL/D/12398-11

Note 1: Polling operations are by definition read cycles and are therefore subject to read cycle timings

4-49

■ 6501122 0087531 3T7 I

http://www.national.com