TOSHIBA CMOS Digital Integrated Circuit Silicon Monolithic

# TC9324F

Single-Chip DTS Microcontroller (DTS-20)

The TC9324F is a single-chip digital tuning system (DTS) microcontroller incorporating a 230 MHz prescaler, PLL, and LCD driver. In addition to a 20-bit IF counter, an 8-channel, 8-bit AD converter, two types of serial interface, and buzzer function, the TC9324F offers a range of functions required for DTS, including an interrupt function, an 8-bit timer-counter, and an 8-bit pulse counter. In addition, the LCD driver features six modes combining 1/4, 1/3, and 1/2 duty and 1/2 and 1/3 bias. This product is suitable for use in a wide variety of DTS systems, from automobile to home audio, including compact stereo systems.

Weight: 1.6 g (typ.)

#### **Features**

- CMOS DTS microcontroller LSI with built-in 230 MHz prescaler, PLL, and LCD driver

- Operating voltage: PLL operating: VDD = 4.0 to 5.5 V (typ. 5.0 V) PLL off: VDD = 3.5 to 5.5 V (when CPU only operating)

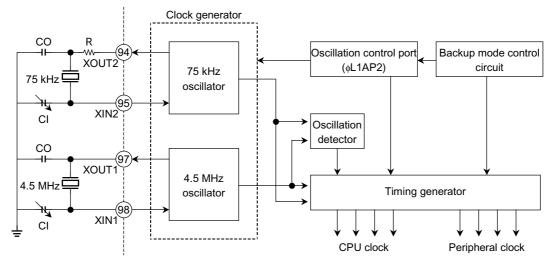

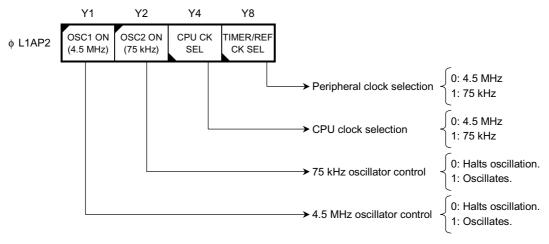

- Crystal oscillator frequency: 4.5 MHz, 75 kHz

- Current dissipation: PLL operating: IDD = 3 mA (typ.) (crystal oscillator frequency 4.5 MHz, VHF mode) PLL off: IDD = 1 mA (typ.) (crystal oscillator frequency 4.5 MHz, CPU only operating) PLL off: IDD = 0.3 mA (typ.) (crystal oscillator frequency 75 kHz, CPU only operating)

- Operating temperature range: Ta = -40 to  $85^{\circ}C$

- Program memory (ROM): 16 bits × 16,384 steps

- Data memory (RAM): 4 bits × 4,096 words

- Instruction execution time: 1.78 μs (crystal oscillator frequency 4.5 MHz)

40 μs (crystal oscillator frequency 75 kHz)

- Stack levels: 16

- General-purpose IF counter: 20-bit (CMOS input supported)

- AD converter: 8 bits × 8 channels

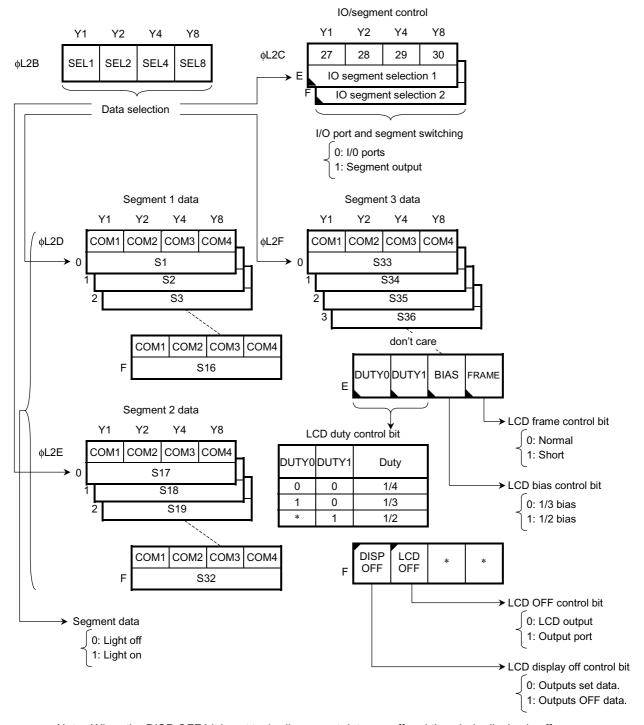

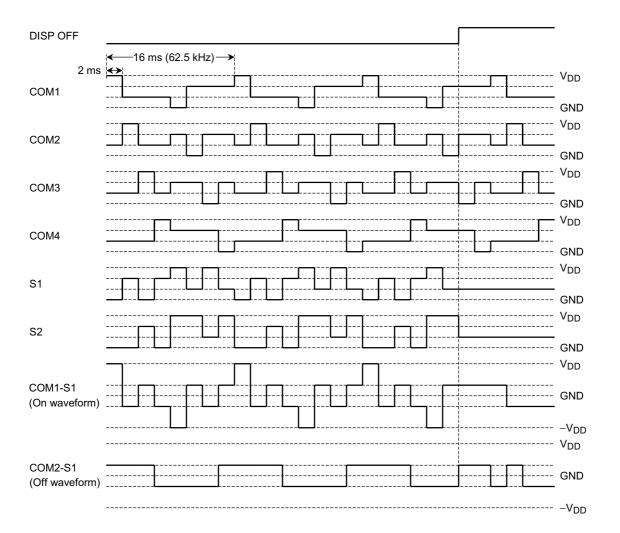

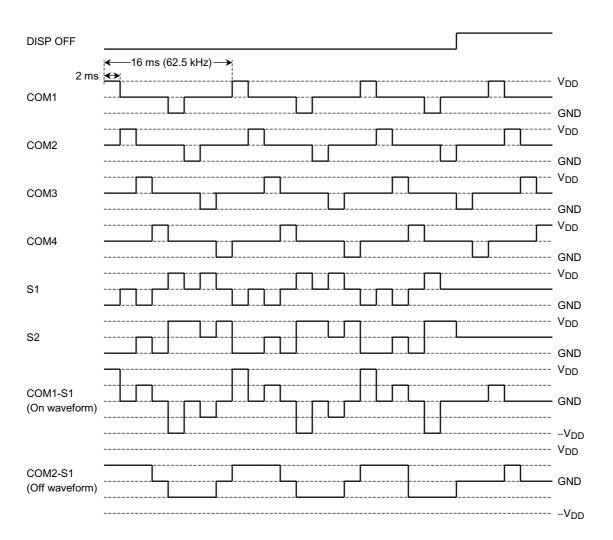

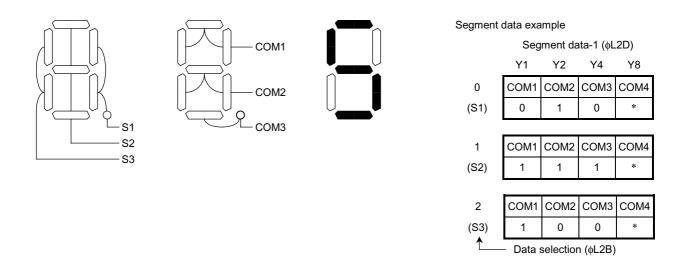

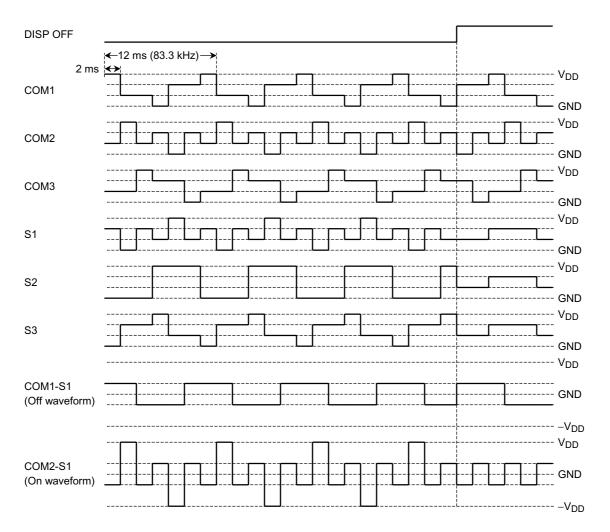

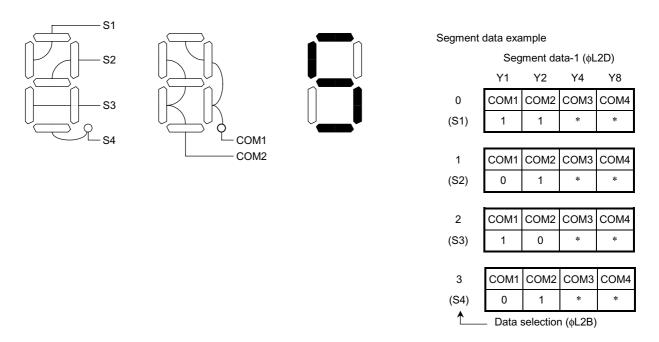

- LCD driver: 1/4, 1/3, 1/2 duty, 1/2, 1/3 bias modes selectable, 136 segments maximum

- I/O ports: CMOS I/O ports: 40 Output-only ports: Up to 31, input-only ports: Up to 5

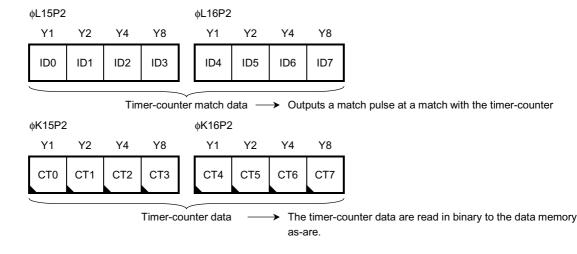

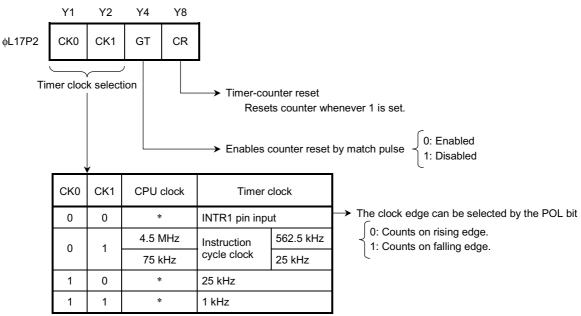

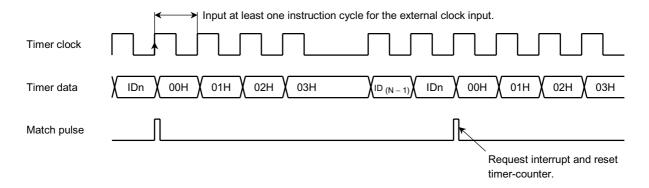

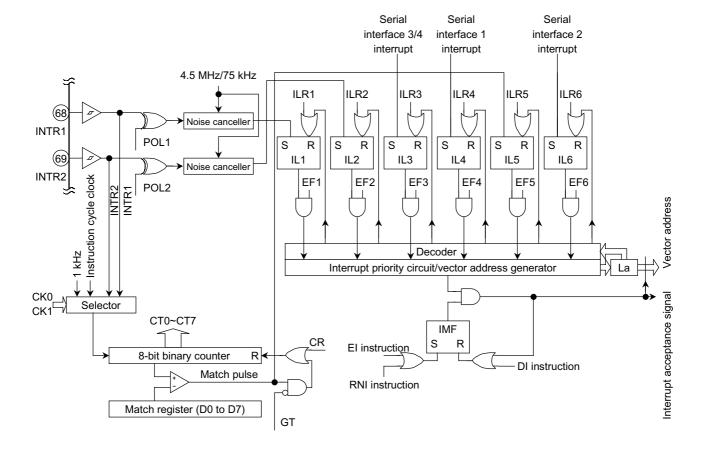

- Timer-counter: 8-bit (as timer clock: INTR1, INTR2, instruction cycle, or 1 kHz selectable)

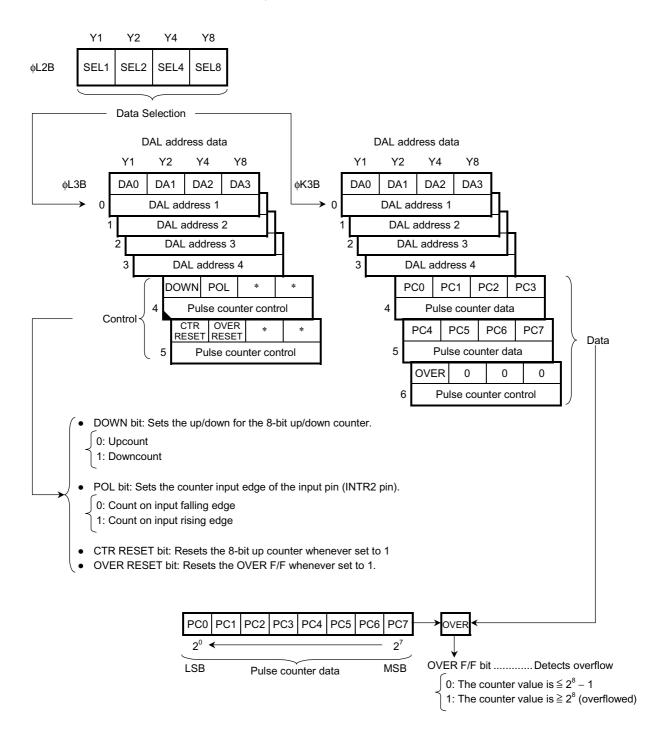

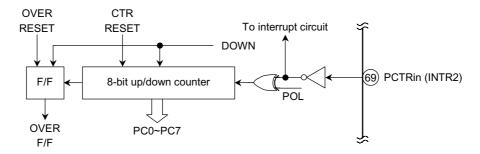

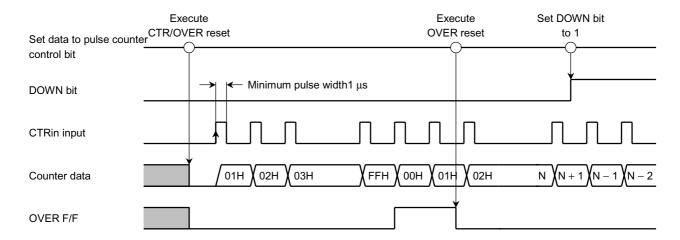

- Pulse counter: 8-bit up/down counter (input from INTR2 pin)

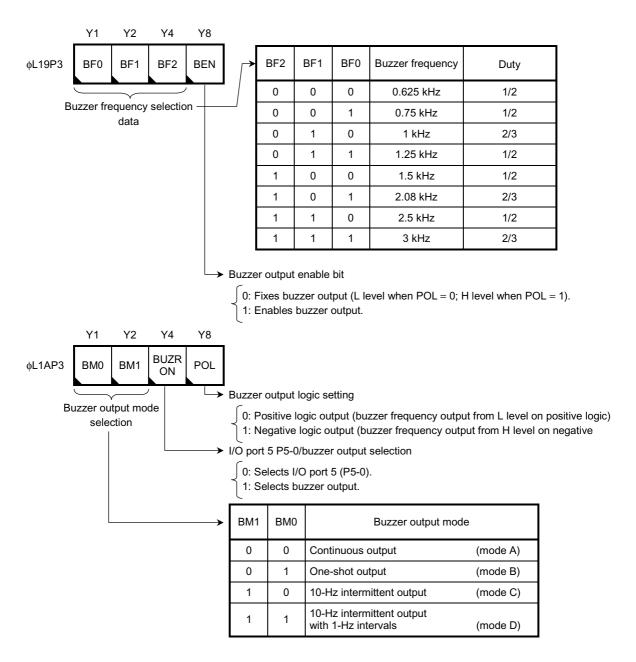

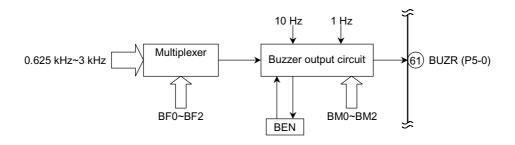

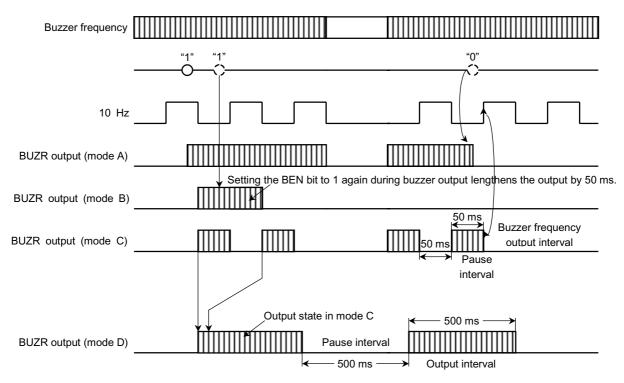

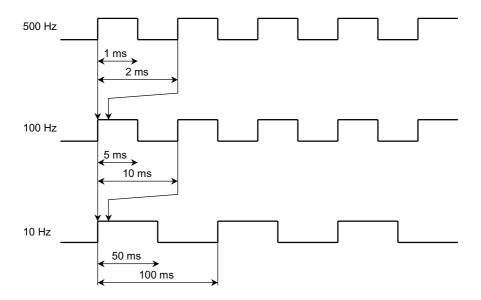

- Buzzer: 0.625 to 3 kHz (8 settings)

Four modes: Continuous, Single-Shot, 10-Hz Intermittent, 10-Hz Intermittent at 1-Hz Intervals

- Interrupts: 2 external, 4 internal (three types of serial interface, 8-bit timer)

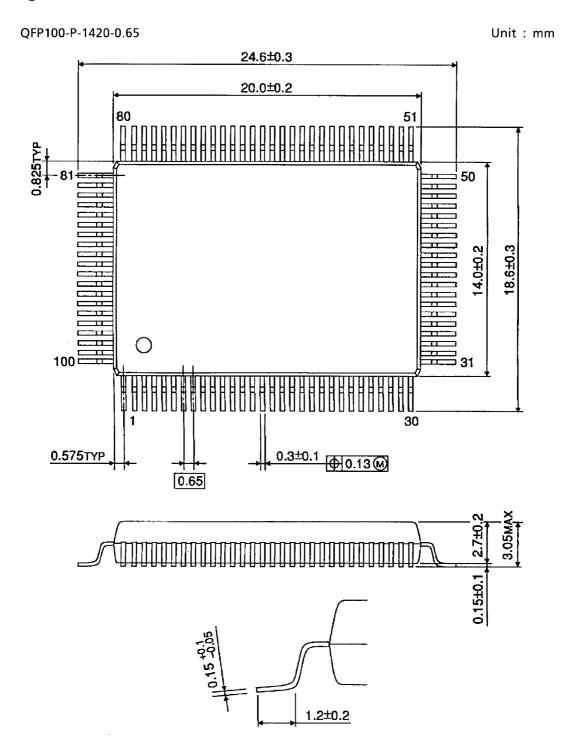

- Package: QFP-100 (0.65-mm pitch)

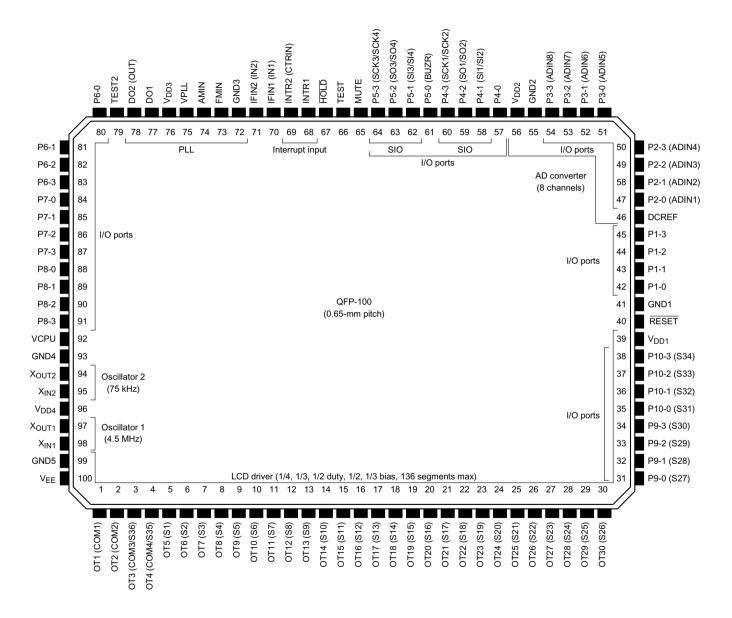

#### Pin Assignment

2

2001-07-24

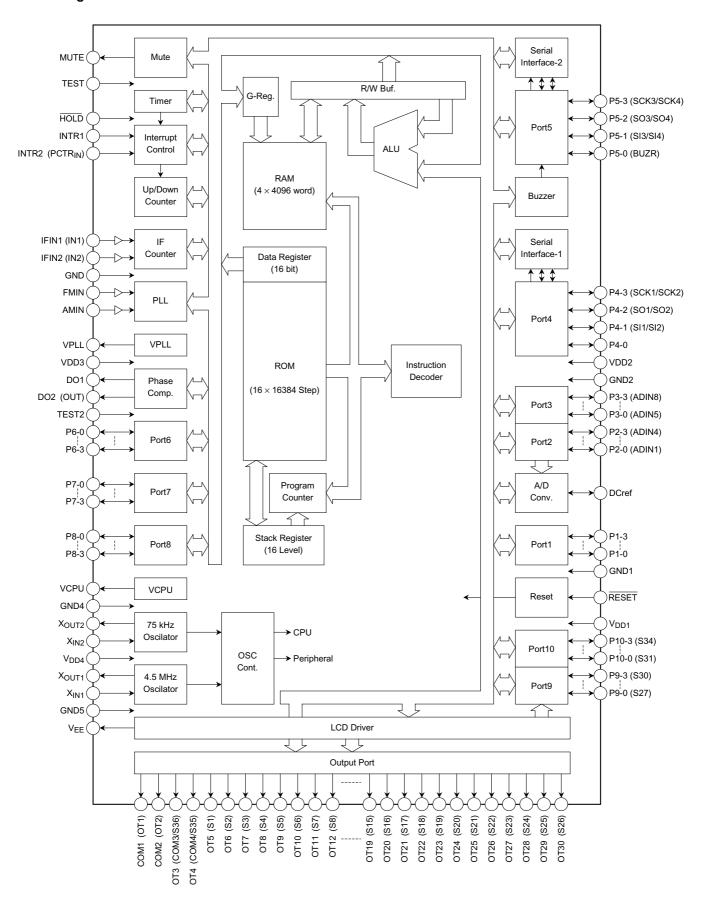

## **Block Diagram**

| Pin No. | Symbol           | Pin Name                           | Function and Operation                                                                                                                                                                                                                                                                            | Remarks                         |  |  |

|---------|------------------|------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|--|--|

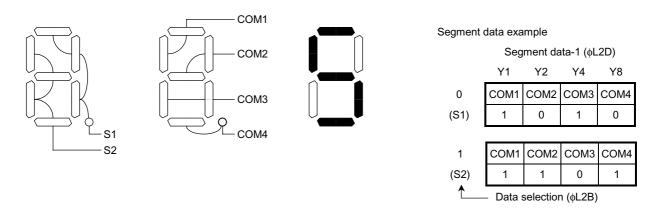

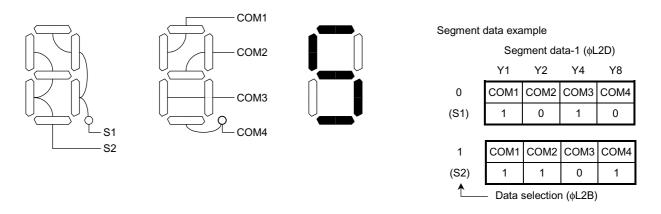

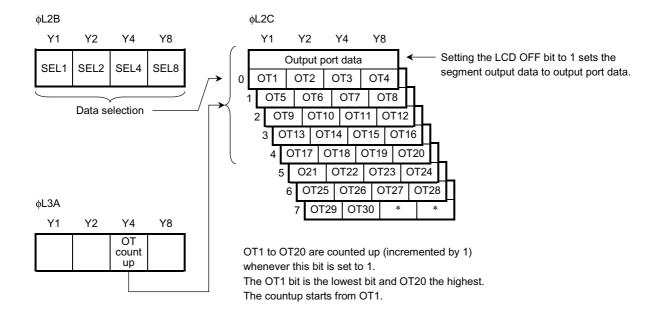

| 1       | OT1/COM1         | Output port                        | Output ports. Pins OT1 to OT20 can be incremented by software, allowing easy data access to external RAM/ROM.                                                                                                                                                                                     |                                 |  |  |

| 2       | OT2/COM2         | /LCD common output                 | Can be set to LCD driver output by software. At 1/4 duty, controller can display up                                                                                                                                                                                                               | <b>ℱ</b> V <sub>DD</sub>        |  |  |

| 3       | OT3/COM3<br>/S36 | Output port                        | to 136 segments using a matrix consisting of COM1 to 4 and SEG1 to 34. At 1/3 duty, can display up to 105                                                                                                                                                                                         | VEEH NEEM NEEL                  |  |  |

| 4       | OT4/COM4<br>/S35 | /LCD segment output                | segments using a matrix consisting of COM1 to 3 and SEG1 to 35. At 1/2 duty, can display up to 72 segments using a matrix consisting of                                                                                                                                                           | di di                           |  |  |

| 5~30    | OT5/S1           | Output port<br>/LCD segment output | COM1 to 2 and SEG1 to 36. Set to output ports after a system reset or clock stop.                                                                                                                                                                                                                 |                                 |  |  |

| 31~34   | P9-0/S27         | I/O port 9<br>/LCD segment output  | 4-bit CMOS I/O ports. Input and output can be programmed in 1-bit units. These can be set bit by bit to LCD driver output by software.                                                                                                                                                            | V <sub>DD</sub>                 |  |  |

| 35~38   | P10-0/S31        | I/O port 10<br>/LCD segment output | After a system reset, set to I/O port input. When a clock stop is executed, the pins used as the LCD driver must be set to output Low level (function as an I/O port).                                                                                                                            | Input instruction               |  |  |

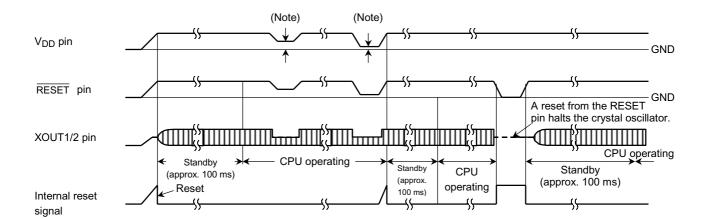

| 40      | RESET            | Reset input                        | Device's system reset signal input pin. Setting RESET to Low level triggers a reset. When the pin is set to High, the program starts from address 0. Since system reset will start if the voltage beyond 0 V to 3.5 V is supplied to V <sub>DD</sub> pin, this pin is used by fixed to "H" level. | V <sub>DD</sub>                 |  |  |

| 42~45   | P1-0             | I/O port 1                         | 4-bit CMOS I/O port.<br>Input and output can be programmed<br>in 1-bit unit.                                                                                                                                                                                                                      | V <sub>DD</sub> V <sub>DD</sub> |  |  |

| Pin No.  | Symbol                         | Pin Name                                                                | Function and Operation                                                                                                                                                                                                                                                                                                                                                                                                                           | Remarks                               |

|----------|--------------------------------|-------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|

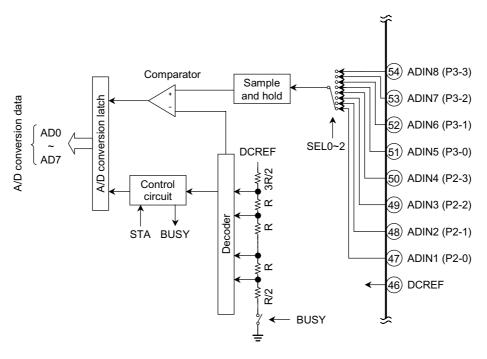

| 46       | DCREF                          | AD converter reference voltage input                                    | AD converter reference voltage input pin. Normally apply V <sub>DD</sub> .                                                                                                                                                                                                                                                                                                                                                                       | → To AD converter                     |

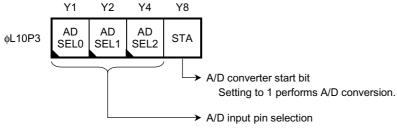

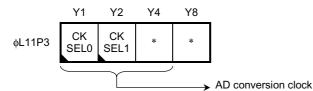

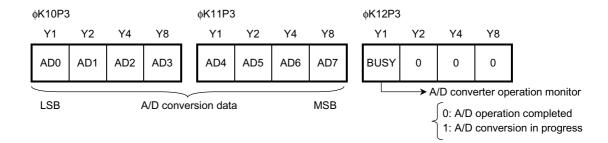

| 47~50    | P2-0<br>/ADIN1                 | I/O port 2<br>/A/D analog voltage<br>input                              | 4-bit CMOS I/O ports. Input and output can be programmed in 1-bit unit. Pins P2-0 to P3-3 are also used for the built-in 8-bit, 8-channel AD converter analog input. A built-in AD converter is a comparison system one by one. When using a 4.5 MHz oscillator, the conversion clock can be selected                                                                                                                                            | V <sub>DD</sub>                       |

| 51~54    | P3-0<br>/ADIN5                 | I/O port 3<br>/A/D analog voltage<br>input                              | among 900 kHz, 100 kHz, and 50 kHz. When using a 75 kHz oscillator, the conversion clock is set to 75 kHz. The conversion times are respectively 23, 192, 382, and 294 µs. The necessary pins can be programmed to A/D analog input in 1-bit units. Voltage up to the V <sub>DD</sub> can be input as the AD converter analog input voltage. Settings for the AD converter and its associated control can be performed by software.              | To AD converter Input instruction     |

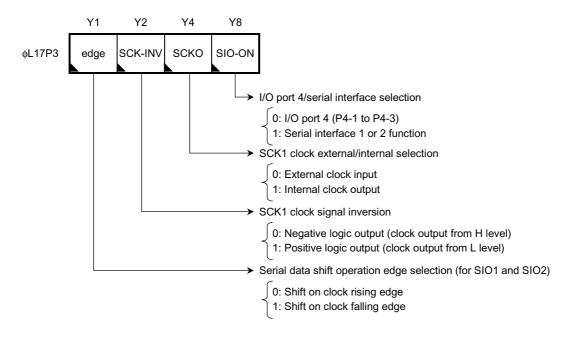

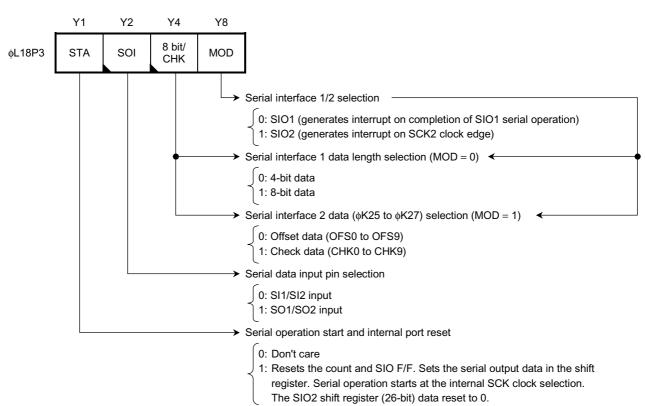

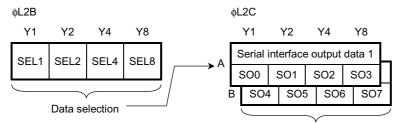

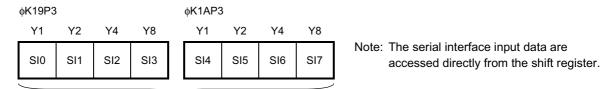

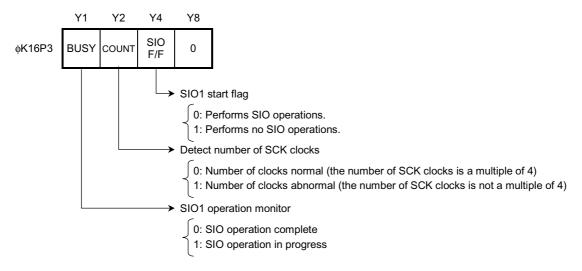

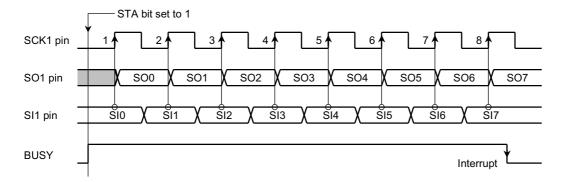

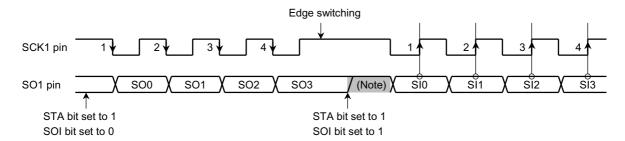

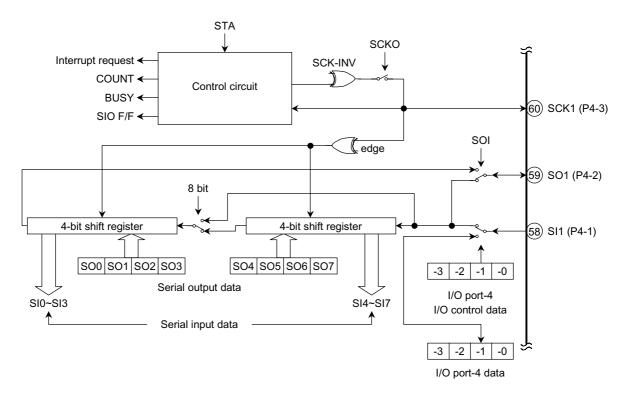

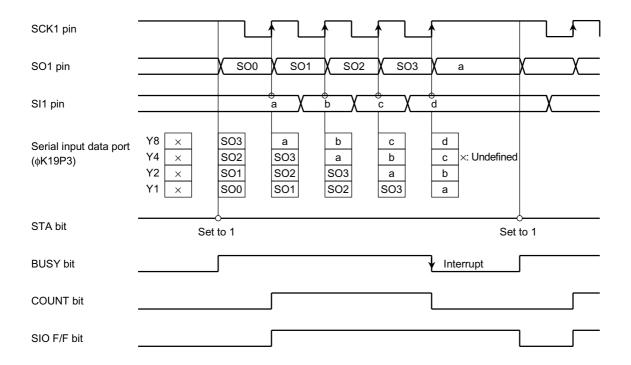

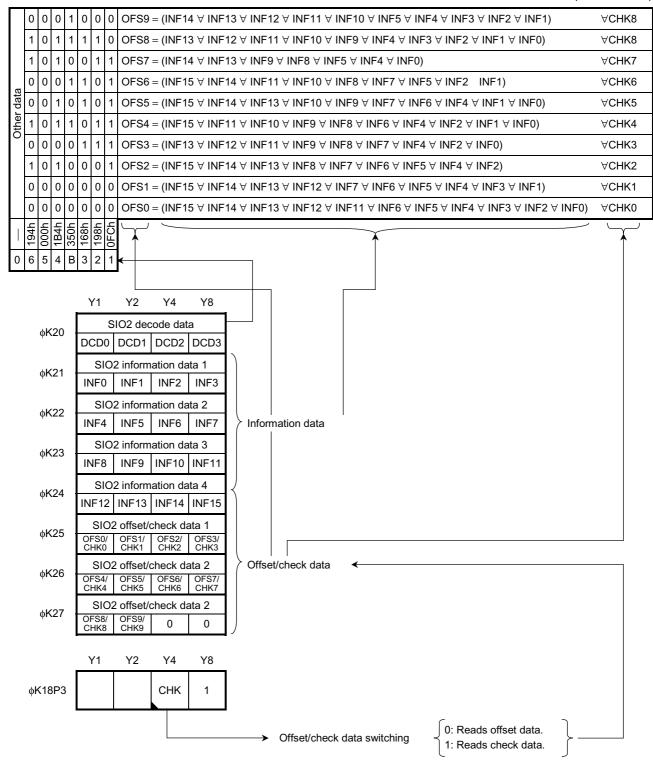

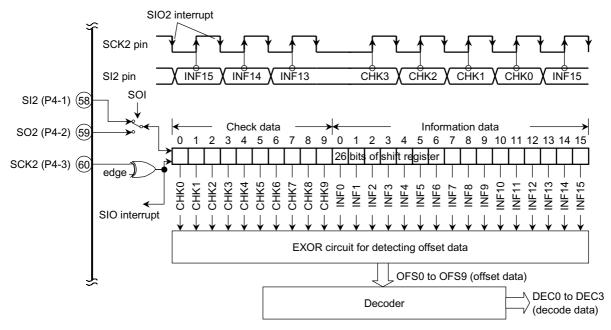

| 57<br>58 | P4-0<br>P4-1                   | I/O port 4 Serial data input 1                                          | 4-bit CMOS I/O ports. Input and output can be programmed in 1-bit unit. Pins P4-1 to P4-3 also input/output the two serial interface circuits (SIO1, SIO2). On the clock edge of the SCK1 pin, SIO1 can input 4-bit or 8-bit serial data to pin SI1 or input/output data to pin SO1. The clock (SCK1) of serial                                                                                                                                  | V <sub>DD</sub>                       |

| 59       | /SI1<br>/SI2<br>P4-2<br>/SO1   | /Serial data input 2  Serial data input/output 1                        | operation can perform selection of an inside (SCK = 37.5 kHz) /exterior, and can perform control of various LSI, and communication between controllers easily.  Enabling the SIO1 interrupt jumps the                                                                                                                                                                                                                                            | Input instruction (P4-0)              |

| 60       | /SO2<br>P4-3<br>/SCK1<br>/SCK2 | /Serial data input 2  Serial clock input/output 1 /Serial clock input 2 | program to address 4 when SIO1 execution completes. On the falling edge of the SCK2 pin, SIO2 can input 26-bit serial data to the SI2 pin. SIO2 incorporates a data detector. Enabling the SIO2 interrupt triggers the interrupt on the falling edge of the SCK2 pin and jumps the program to address 6. The SIO1 and SIO2 inputs all incorporate Schmitt circuits. SIO1 and SIO2 and their associated controls can be used and set by software. | Input instruction + SIOon (P4-1~P4-3) |

| Pin No.              | Symbol                                              | Pin Name                                                                                                                                                            | Function and Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Remarks                                                                     |

|----------------------|-----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|

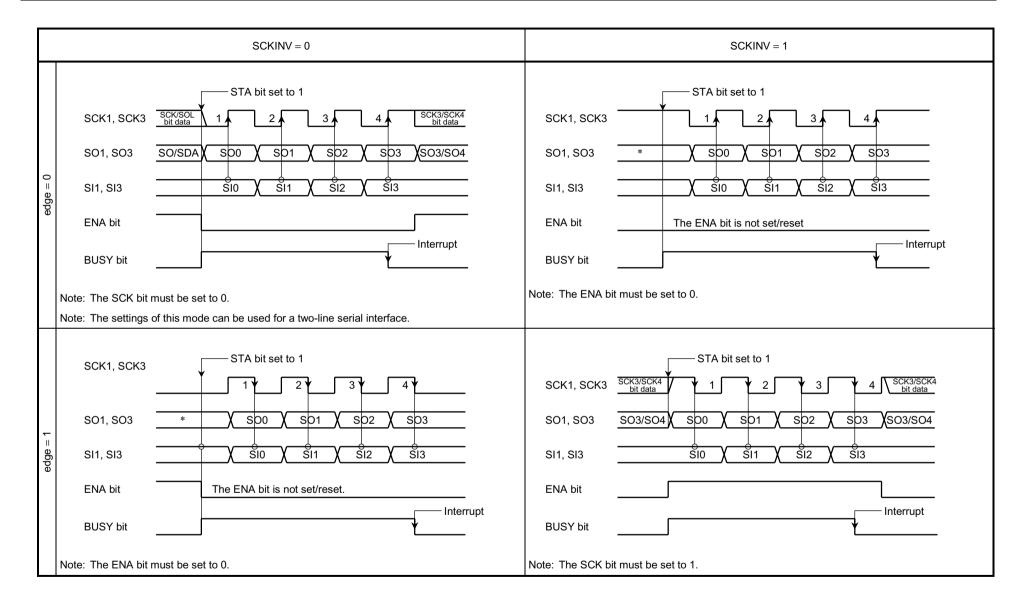

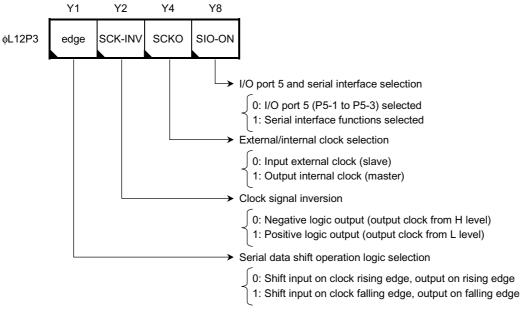

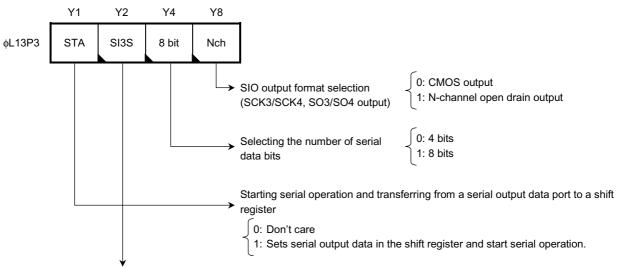

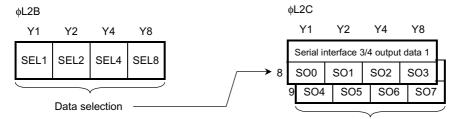

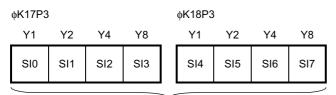

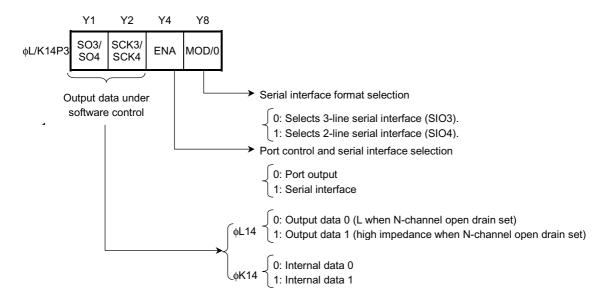

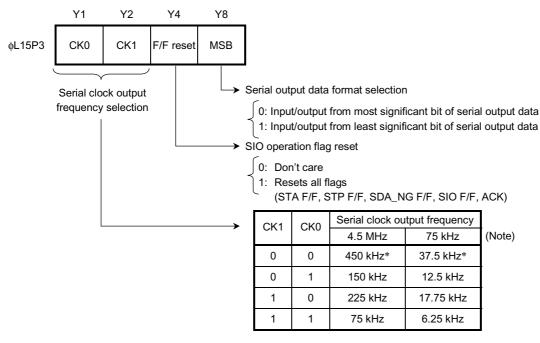

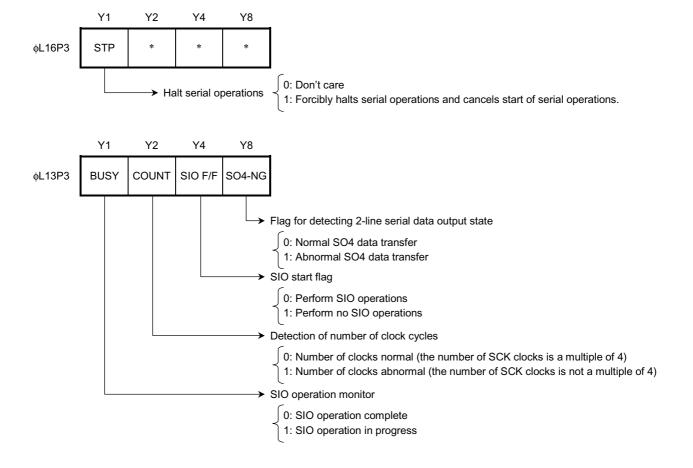

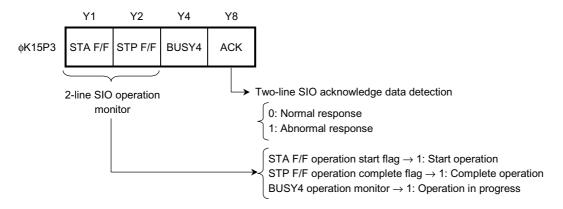

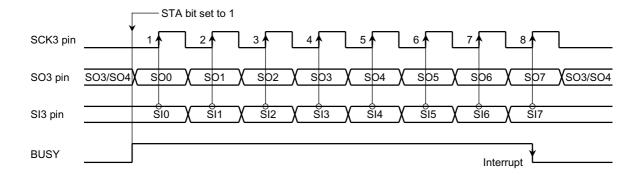

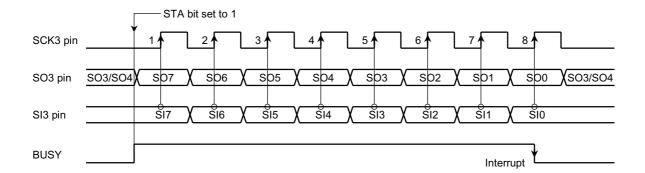

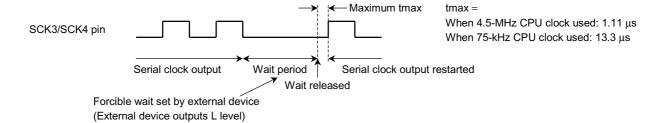

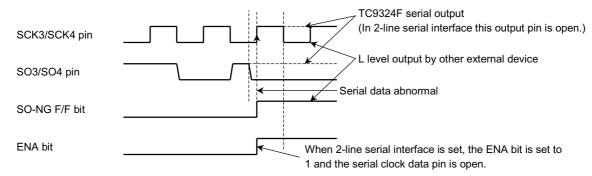

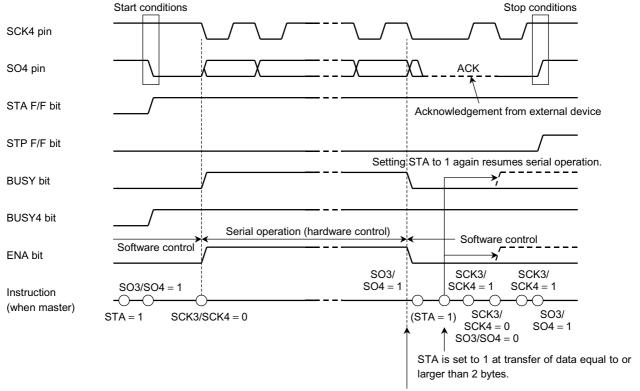

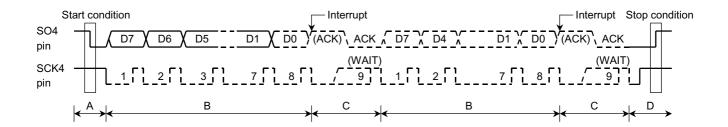

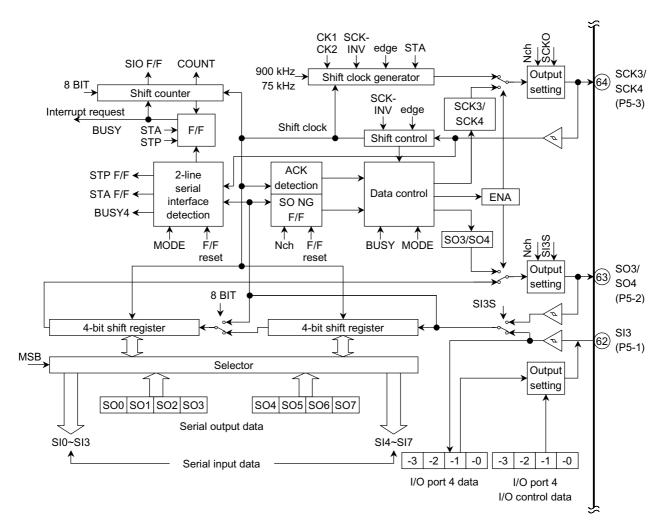

| 61<br>62<br>63<br>64 | P5-0/BUZR P5-1 /SI3 P5-2 /SO3 /SO4 P5-3 /SCK3 /SCK4 | I/O port 5 /buzzer output  /Serial data input 3  /Serial data input/output 3 /Serial data input/output 4  /Serial clock input/output 3 /Serial clock input/output 4 | 4-bit CMOS I/O ports. Input and output can be programmed in 1-bit unit. Pin 5-0 is also used to output a buzzer signal. Pins P5-1 to P5-3 are also used to input/output the two serial interface circuits (SIO3, SIO4). The buzzer output can be selected between eight frequency settings (0.625 to 3 kHz), which can be output in four modes: Continuous, Single-Shot, 10 Hz-Intermittent, and 10-Hz Intermittent at 1-Hz Intervals. SIO3 is a serial interface supporting three lines, while the SIO4 serial interface supports two lines. On the clock edge of the SCK3/SCK4 pin, SIO3/SIO4 can input 4- or 8-bit serial data to pin SI3 or output data to the SO3/SO4 pin. As the serial operating clock (SCK3/SCK4), an internal (450/225/150/75 kHz) clock or external clock can be selected. Rising and falling shift can also be selected. The clock data output is N-channel open drain. This design facilitates LSI control and communication between controllers. Enabling the SIO3 or SIO4 interrupts triggers the interrupt and jumps the program to address 3 when interface SIO3 or SIO4 completes execution. This is effective for high-speed serial communications. All of the input of SIO3 and SIO4 built-in the Schmitt circuits. SIO3, SIO4, and their associated controls can be used and set by software. | Input instruction (P5-0)  VDD VDD VDD Input instruction + SIOon (P5-1~P5-3) |

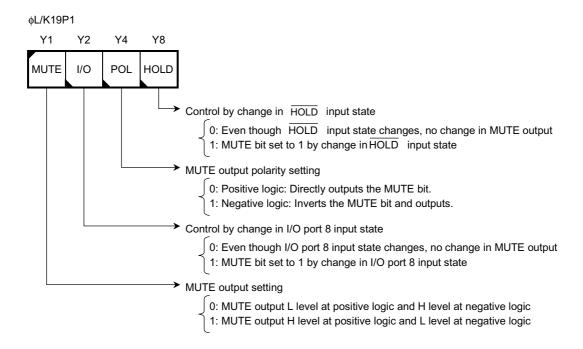

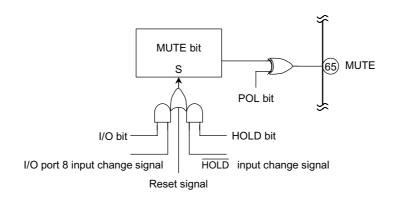

| 65                   | MUTE                                                | Muting output port                                                                                                                                                  | 1-bit output port. Normally used as a muting control signal output. This pin can set the internal MUTE bit to 1 according to changes in the I/O port 8 input and HOLD input. The MUTE bit output logic can be changed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | V <sub>DD</sub>                                                             |

| 66                   | TEST                                                | Test mode control<br>input                                                                                                                                          | Input pin for controlling Test mode. When the pins are at High level, the device is in Test mode; at Low level, in normal operation. Normally, set the pins to Low level or NC (pull-down resistors are incorporated).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | V <sub>DD</sub>                                                             |

| Pin No.  | Symbol                    | Pin Name                                          | Function and Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Remarks         |

|----------|---------------------------|---------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

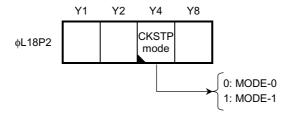

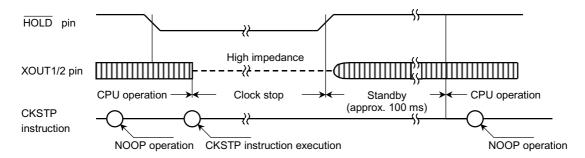

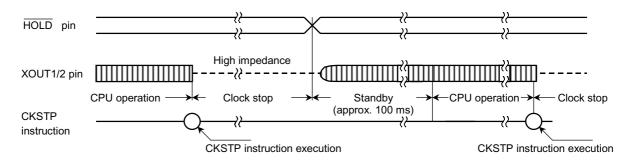

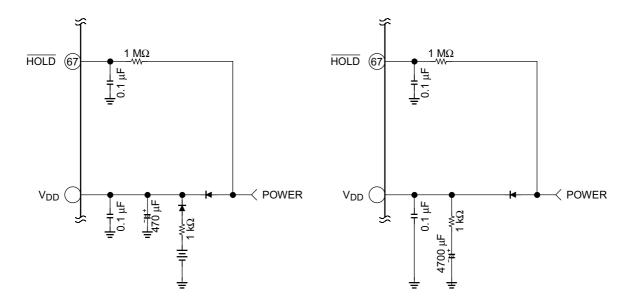

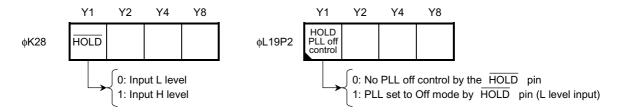

| 67       | HOLD                      | Hold mode control<br>input                        | Input pin for requesting and releasing Hold mode. Normally used to input radio mode selection or battery detection signals. Hold mode includes Clock Stop mode (crystal oscillator stopped) and Wait mode (CPU stopped), which can be set by the CKSTP and WAIT instructions respectively. Clock Stop mode can be entered by software in one of two ways: forcibly or when Low level is detected on the HOLD pin. Clock Stop mode can be released when High level is detected on the HOLD pin or when the input changes. Executing the CKSTP instruction stops the clock generator and CPU, entering memory backup mode. In this state the device is set to low current dissipation (10 µA max). Wait mode is executed, regardless of the HOLD pin input state, and the device is set to low current dissipation. To set wait mode, specify by software either crystal oscillator only operating or CPU suspended. Wait mode is released when the HOLD pin input changes. | V <sub>DD</sub> |

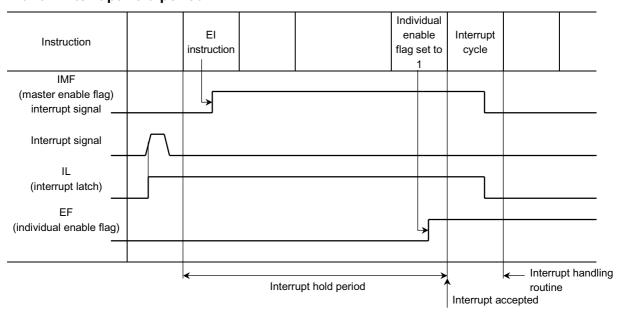

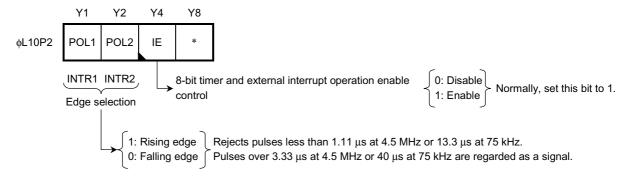

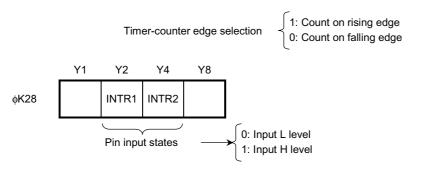

| 68<br>69 | INTR1<br>INTR2<br>/PCTRin | External interrupt<br>input<br>/pulse count input | External interrupt input pins. Enabling the interrupt function and inputting a pulse (of at least 1.11 to 3.33 μs when the 4.5 MHz clock is in use, or at least 13.3 to 40 μs when the 75 kHz clock used) to these input pins generates an interrupt (INTR1/2) and jumps the program to address 1/2. The input logic and the clock edge (rising/falling) can be individually selected for each interrupt input. The internal 8-bit timer clock can be selected as input to the pins. At the pulse count or when the count reaches a specified value, an interrupt can be generated (to address 5). These pins are also used to input an 8-bit pulse counter. This counter can be selected between rising and falling edge input and between an up-counter and a down-counter. These pins are Schmitt inputs and can also be used as input ports. The pins can also be utilized as ports for inputting remote control signals or tape counts.                              | V <sub>DD</sub> |

| Pin No.  | Symbol                                           | Pin Name                             | Function and Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Remarks  |

|----------|--------------------------------------------------|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

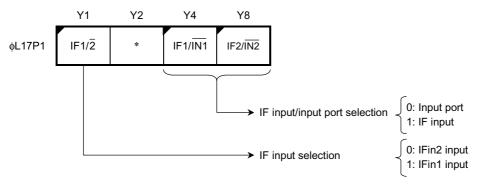

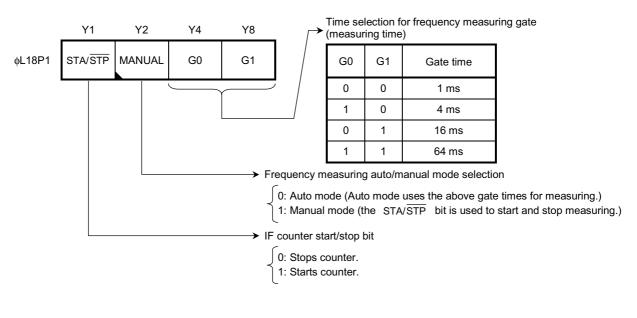

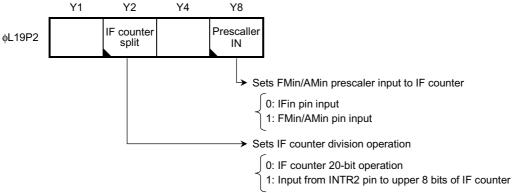

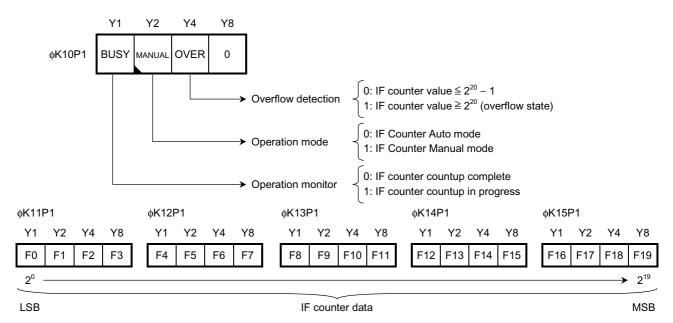

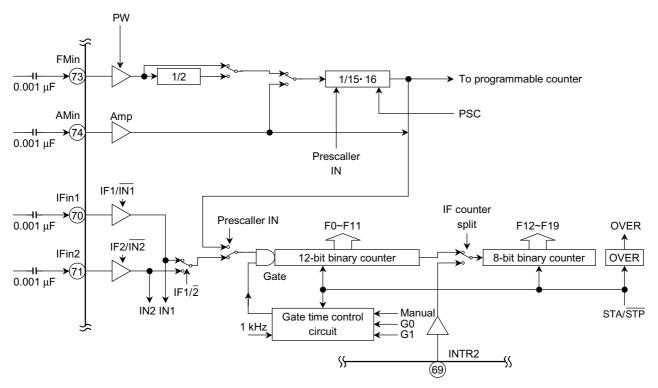

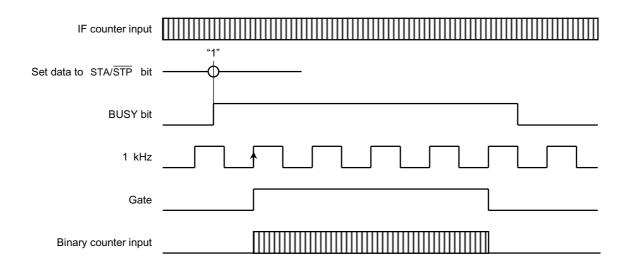

| 70<br>71 | IF <sub>IN1</sub> /IN1<br>IF <sub>IN2</sub> /IN2 | IF signal inputs<br>/input port      | IF signal input pins for the IF counter to count the IF signals of the FM and AM bands and detect the automatic stop position.  The input frequency is in the range 0.3 to 20 MHz. A built-in input amp and capacitive coupling support low-amplitude operation.  The IF counter is a 20-bit counter with selectable gate times of 1, 4, 16, and 64 ms. 20 bits of data can be easily stored in memory. In Manual mode, the gates can be switched on and off by instruction.  These input pins can also be programmed as an input port (IN port). At that time, they become CMOS inputs and the clocks of those inputs can be counted using the IF counter.  Note: Pins set as IF input go Low in PLL Off mode. | RFIN     |

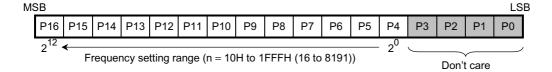

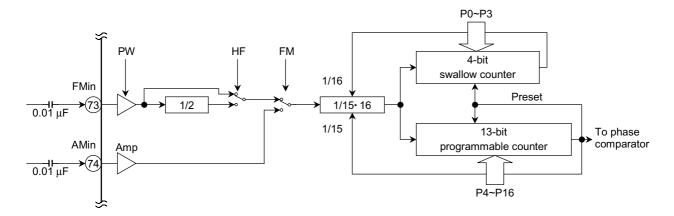

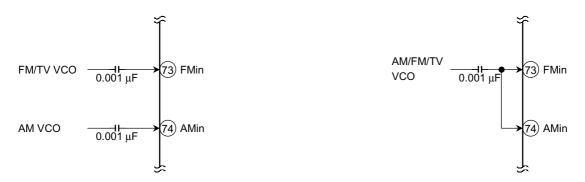

| 73       | FMIN                                             | FM local oscillation<br>signal input | Programmable counter input pins for the FM/AM band. Their input mode can be switched by software among 1/2 + pulse swallow (VHF/FM) mode for FM input, and pulse swallow (HF) or direct division (LF) mode for AM input. The local oscillation output (voltage-controlled oscillator or VCO output) is normally input at the following frequencies: 50 to 230 MHz in VHF mode, 50 to 140 MHz in FM1                                                                                                                                                                                                                                                                                                             | RFIN VDD |

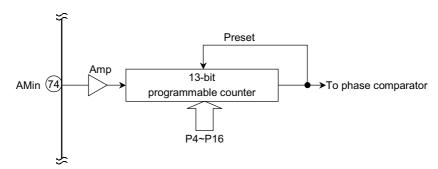

| 74       | AMIN                                             | AM local oscillation<br>signal input | mode, 10 to 60 MHz in FM2 mode, 1 to 30 MHz in HF mode, and 0.5 to 20 MHz in LF mode.  A built-in input amp and capacitive coupling support low-amplitude operation.  Note: In PLL Off mode or when the pins are not set for input, the input goes to high impedance.                                                                                                                                                                                                                                                                                                                                                                                                                                           | RFIN VDD |

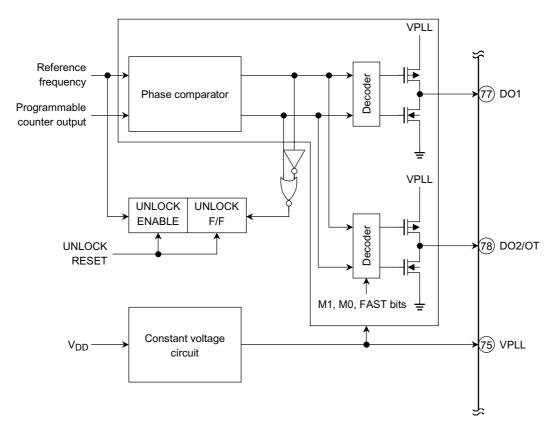

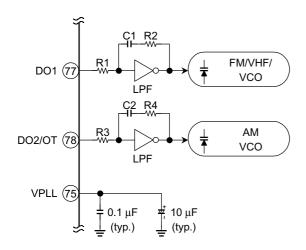

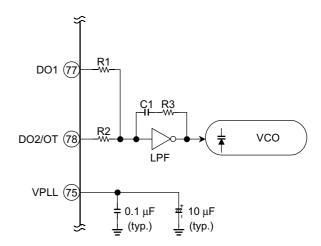

| 75       | VPLL                                             | PLL constant voltage output          | Constant voltage output for the PLL. The PLL constant voltage is used as the power supply for the PLL and IF counter. In PLL On mode, the constant voltage power supply is 3.55 V (typ.). In PLL Off mode, the V <sub>DD</sub> is output. Connecting a capacitor (0.1 $\mu$ F, 10 $\mu$ F typ.) stabilizes the power supply.                                                                                                                                                                                                                                                                                                                                                                                    | VPLL     |

| Pin No.  | Symbol            | Pin Name                                   | Function and Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Remarks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------|-------------------|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

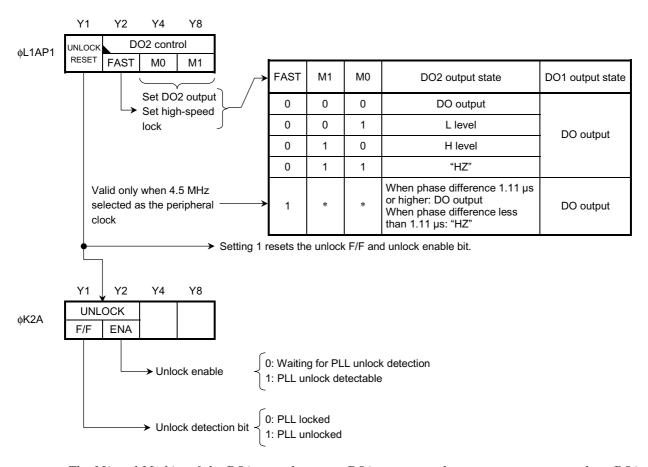

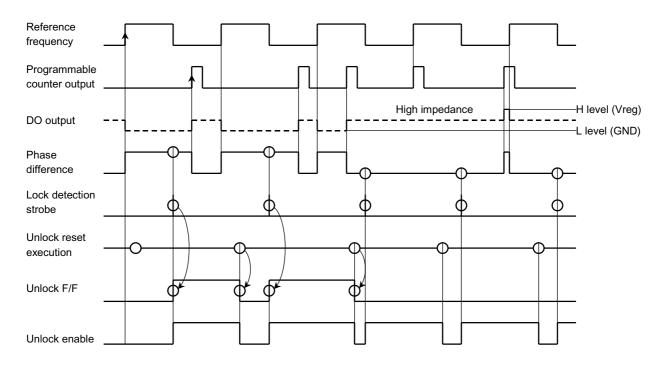

| 77<br>78 | DO1<br>DO2/OUT    | Phase comparator<br>output<br>/output port | PLL phase comparator output pins. In tri-state output, when the programmable counter divider output is higher than the reference frequency, the pins output High level; when the output is lower than the reference frequency, the pins output Low level. When the outputs match, the pins go to high impedance. Because DO1 and DO2 are output in parallel, optimal filter constants can be designed for both the AM and FM bands. The DO2 pin can be programmed to high impedance or set as an output port (OUT). Therefore, lockup time can be improved using the DO1 and DO2 pins or the pins can be effectively used as output ports. Lock-up time can also be improved by using DO1 and DO2 together by setting the pins to High-Speed Lock mode when using a 4.5 MHz oscillator. When the phase difference equals or exceeds ±1.11 µs, DO1 and DO2 output the phase difference is less than ±1.11 µs, the DO2 output goes to high impedance and only DO1 outputs the phase difference pulse. | VDD THE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 79       | TEST2             | Test mode control input 2                  | Input pin for controlling Test mode. When the pins are at High level, the device is in Test mode; at Low level, in normal operation. Normally, set the pins to Low level or NC (pull-down resistors are incorporated).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | V <sub>DD</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 80~83    | P6-0<br>≀<br>P6-3 | I/O port 6                                 | 4-bit CMOS I/O ports. Input and output can be programmed in 1-bit units.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | V <sub>DD</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

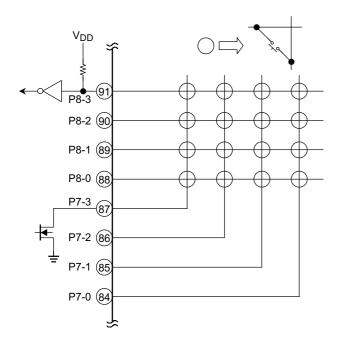

| 84~87    | P7-0<br>≀<br>P7-3 | I/O port 7                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

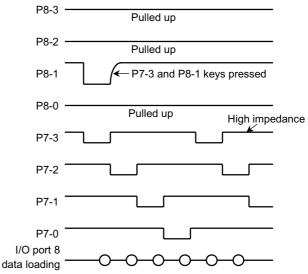

| 88~91    | P8-0<br>≀<br>P8-3 | I/O port 8                                 | 4-bit CMOS I/O port. Input and output can be programmed in 1-bit unit. As the pins can be pulled up or pulled down by software they can be used as key input pins. When set to an I/O port input, that input can be varied to release Clock Stop or Wait modes or to set the MUTE bit of the MUTE pin to 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | V <sub>DD</sub> V <sub>DD</sub> V <sub>DD</sub> V <sub>DD</sub> V <sub>DD</sub> R <sub>IN1</sub> V <sub>DD</sub> R |

| Pin No.                    | Symbol                                                                       | Pin Name                           | Function and Operation                                                                                                                                                                                                                                                                                                                                                                               | Remarks                                         |

|----------------------------|------------------------------------------------------------------------------|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|

| 92                         | VCPU                                                                         | CPU constant<br>voltage output     | Constant voltage output pin for the CPU or oscillators. In normal mode, a constant voltage power supply of 2.95 V (typ.) is output; in Clock Stop mode, VDD is output. Connecting a capacitor (0.1 $\mu$ F, 10 $\mu$ F typ.) stabilizes the power supply.                                                                                                                                            | VCPU                                            |

| 94                         | X <sub>OUT2</sub>                                                            | 75 kHz crystal                     | Crystal oscillator pins. Connect a 4.5 MHz crystal (Ci = Co = $30 \text{ pF typ.}$ ) to $X_{\text{IN1}}$ and $X_{\text{OUT1}}$ and a 75 kHz crystal (Ci = Co = $30 \text{ pF typ.}$ ) to $X_{\text{IN2}}$ and $X_{\text{OUT2}}$ . Two different types of crystal resonators (4.5 MHz and 75 kHz) can be connected, or simply connect one                                                             | XOUT2 ROUT2 W RfXT2 VDD                         |

| 95                         | X <sub>IN2</sub>                                                             | oscillator pins                    | (4.5 MHz or 75 kHz). Note that if a 75 kHz crystal only is connected, X <sub>IN1</sub> must be fixed to GND level. If a 4.5 MHz crystal only is connected, it is not necessary to fix the 75 kHz crystal oscillator pins. If both 4.5 MHz and 75 kHz crystal oscillators are connected, after a reset the CPU operates on the 4.5 MHz crystal oscillator clock. The clock can be readily switched by | XIN2                                            |

| 97                         | X <sub>OUT1</sub>                                                            | 4.5 MHz crystal                    | software between the CPU operating clock and the peripheral clock. Oscillation stops during execution of the CKSTP instruction.                                                                                                                                                                                                                                                                      | X <sub>OUT1</sub> ROUT1  RfXT1  V <sub>DD</sub> |

| 98                         | XIN1                                                                         | oscillator pins                    |                                                                                                                                                                                                                                                                                                                                                                                                      | XIN1 PIE M                                      |

| 100                        | V <sub>EE</sub>                                                              | LCD driver bias voltage output pin | This is the bias voltage output pin for the LCD driver.                                                                                                                                                                                                                                                                                                                                              | _                                               |

| 39<br>56<br>76<br>96       | V <sub>DD1</sub><br>V <sub>DD2</sub><br>V <sub>DD3</sub><br>V <sub>DD4</sub> |                                    | Pins used for supplying power. In PLL On mode, the pins supply $V_{DD}$ = 4.0 to 5.5 V; in PLL Off mode, the pins supply $V_{DD}$ = 3.5 to 5.5 V. In backup state (when execution of the CKSTP instruction), current dissipation becomes low (10 $\mu$ A max), dropping the power supply voltage to                                                                                                  | V <sub>DD</sub>                                 |

| 41<br>55<br>72<br>93<br>99 | GND1<br>GND2<br>GND3<br>GND4<br>GND5                                         | Power supply pins                  | 2.0 V.  If 3.5 V or more is applied to these pins when the voltage is 0 V, a system reset is applied to the device and the program starts from address 0 (power-on reset).  Note: To operate the power-on reset, allow 10 to 100 ms while the device power supply voltage rises.                                                                                                                     | GND                                             |

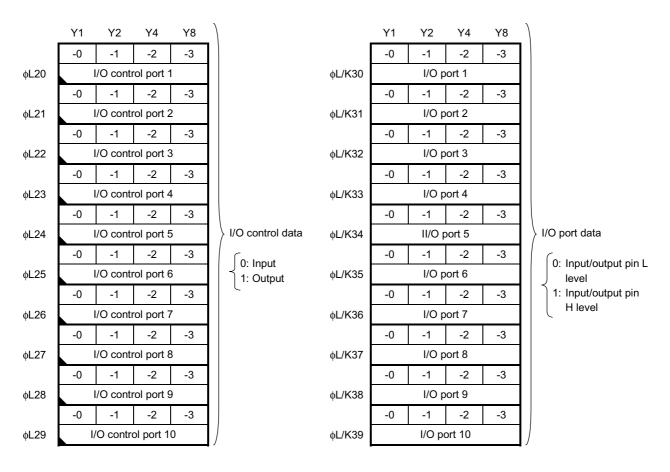

## **Description of Operations**

#### o CPU

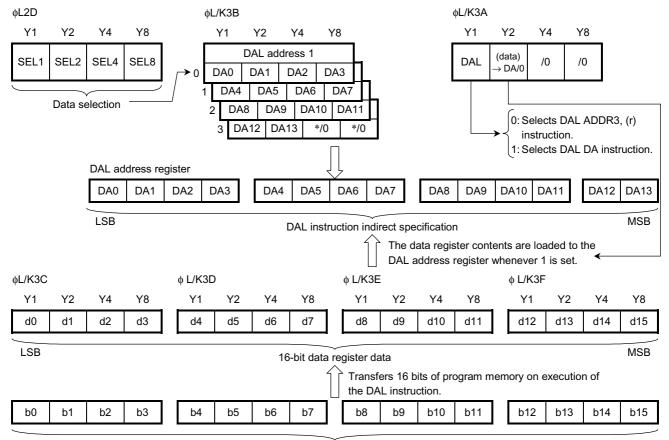

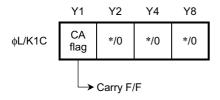

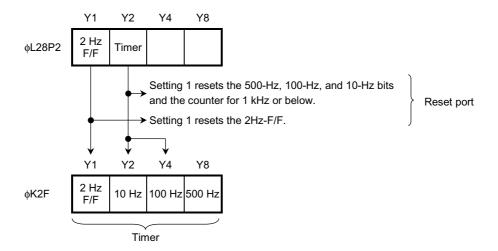

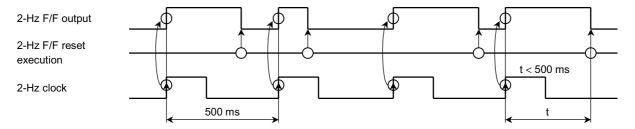

The CPU consists of a program counter, a stack register, an ALU, program memory, data memory, a G-register, a data register, a DAL address register, a carry flip-flop (F/F), a judge circuit, and an interrupt circuit.

## 1. Program Counter (PC)

The program counter is a 14-bit binary up counter used to address program memory (ROM). The program counter is cleared by a system reset and starts from address 0.

The PC is normally incremented by 1 at the execution of each instruction. However, executing a Jump or Call instruction loads the address specified in the instruction's operand to the PC.

When an instruction with a skip function (for example, the AIS, SLTI, TMT, and RNS instructions) is executed and the result matches the skip condition, the PC is incremented by 2 and the next instruction is skipped.

When an interrupt is received, the system loads the vector address corresponding to the interrupt.

Note: Program memory (ROM) uses the address range 0000H to 3FFFH. Access to addresses outside this range is prohibited.

| Instruction                        |      |                                  |                                        |      | Co  | ontents | of prog   | ram cou  | ınter (P | C)  |     |     |     |          |

|------------------------------------|------|----------------------------------|----------------------------------------|------|-----|---------|-----------|----------|----------|-----|-----|-----|-----|----------|

| Instruction                        | PC13 | PC12                             | PC11                                   | PC10 | PC9 | PC8     | PC7       | PC6      | PC5      | PC4 | PC3 | PC2 | PC1 | PC0      |

| JUMP ADDR1                         | •    | Instruction operand (ADDR1)      |                                        |      |     |         |           |          |          |     |     |     |     |          |

| CALL ADDR2                         | 0    | 0 0 Instruction operand (ADDR2)  |                                        |      |     |         |           |          |          |     |     |     |     |          |

| DAL ADDR3, (r)<br>(DAL bit = 0)    | 0    | 0                                | 0 0 0 Contents of general register (r) |      |     |         |           |          |          |     |     |     |     |          |

| DAL (DA)<br>(DAL bit = 1)          | •    |                                  |                                        |      |     | DAL a   | ıddress   | registe  | r (DA)   |     |     |     |     | <b>→</b> |

| RN, RNS, RNI                       | •    |                                  |                                        |      |     | Conte   | ents of s | stack re | gister   |     |     |     |     |          |

| When interrupt received            | •    | ✓ Vector address for interrupt — |                                        |      |     |         |           |          |          |     |     |     |     |          |

| Power-on reset, reset by RESET pin | 0    | 0                                | 0                                      | 0    | 0   | 0       | 0         | 0        | 0        | 0   | 0   | 0   | 0   | 0        |

| Priority | Interrupt source     | Vector address |  |  |

|----------|----------------------|----------------|--|--|

| 1        | INTR1 pin            | 0001H          |  |  |

| 2        | INTR2 pin            | 0002H          |  |  |

| 3        | Serial interface 1   | 0003H          |  |  |

| 4        | Serial interface 3/4 | 0004H          |  |  |

| 5        | Timer-counter        | 0005H          |  |  |

| 6        | Serial interface 2   | 0006H          |  |  |

#### 2. Stack Register

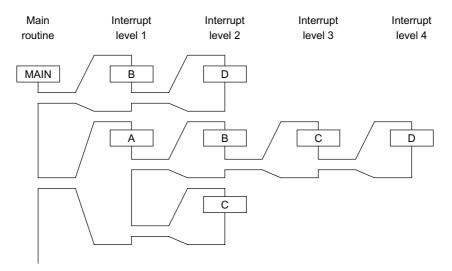

The stack register consists of  $16 \times 14$  bits. When a subroutine call instruction is executed or an interrupt is processed, this register stores a value equal to the contents of the program counter + 1 (that is, the return address). Executing a return instruction (RN, RNS, RNI) loads the contents of the stack register to the program counter.

The stack register can nest to 16 stack levels.

## 3. ALU

The arithmetic and logic unit (ALU) has a binary 4-bit parallel addition-subtraction function, a logical operation function, a compare function, and a multiple bit judge function. The CPU does not include an accumulator; all operations directly use the contents of the data memory.

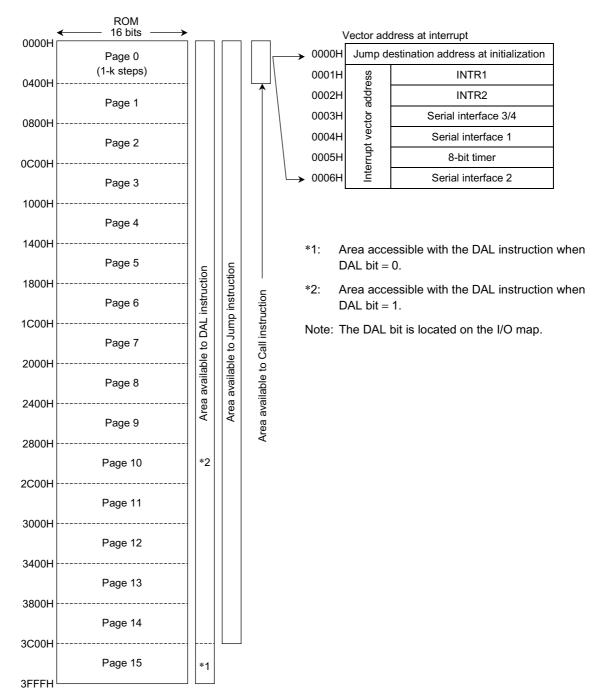

## 4. Program Memory (ROM)

Program memory, which stores the program, is made up of 16 bits  $\times$  16,384 steps. The useable address range is the 16.384 steps of the range 0000H to 3FFFH.

The program memory divides the 16,384 steps into 16 pages (pages 0 to 15). The address area available to Jump instructions is from 0000H to 3BFFH (pages 0 to 14). The area for Call instructions is 0000H to 03FFH (page 0). When the DAL bit (located in the I/O map) is set to 0 (DAL ADDR3, (r) instruction), area 3C00H to 3FFFH (page 15) of program memory can be used as data area. When the DAL bit is set to 1 (DAL (DA) instruction) the area 0000H to 3FFFH (pages 0 to 7) is available as data area. At that time the DAL instruction can load any 16 bits within the data area to the data register.

Note: Set the data area in program memory to addresses outside the program loop.

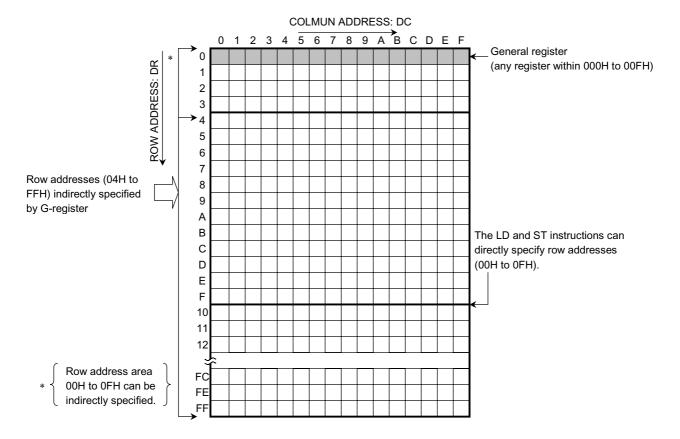

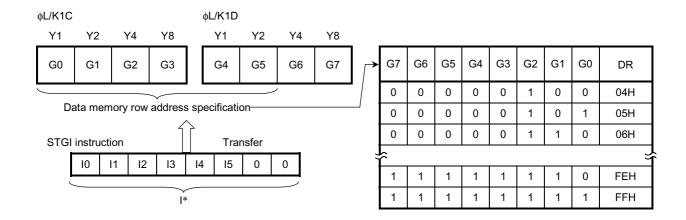

## 5. Data Memory (RAM)

Data memory, which stores the data, is made up of 4 bits x 4,096 words. The 4,096 words are identified by a row address (8 bits) and a column address (4 bits). 3,932 words (row address = 04H to FFH) are for indirect addressing by the G-register. Accordingly, when processing data in this area be sure to first set the G-register to specify the row address.

Data memory area 00H to 0FH is called the general registers and can be used simply by specifying the (4 bits) column address. The 16 general registers can be used in data memory operations and transfers. The general registers can also be used as normal data memory.

Note: The (4 bits) column address specifying the general register is used as the general register's register number.

Note: All row addresses (00H to FFH) can be indirectly specified by the G-register.

Note: The LD and ST instructions can directly address 256 words of data memory (row address area 00H to 0FH).

## 6. G-register (G-REG)