#### CMOS 4-Bit Microcontroller

## TMP47P823VF

The TMP47P823V is the system evaluation LSI of the TMP47C623/823 with 64 Kbits one-time PROM. The TMP47P823V programs / verifies using an adapter socket to connect with PROM programmer, an it is in TMM27128AD.

In addition, the TMP47P823V and the TMP47C623/823 are pin compatible. The TMP47P823V operates as the same as the TMP47C623/823 by programming to the internal PROM.

| Part No.    | ROM                 | RAM         | Package            | Adapter Socket |  |

|-------------|---------------------|-------------|--------------------|----------------|--|

| TMP47P823VF | OTP<br>8192 × 8-bit | 512 × 4-bit | P-QFP64-1420-1.00A | BM1146         |  |

For a discussion of how the reliability of microcontrollers can be predicted, please refer to Section 1.3 of the chapter entitled

Quality and Reliability Assurance / Handling Precautions.

TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to comply with the standards of safety in making a safe design for the entire system, and to avoid situations in which a malfunction or failure of such TOSHIBA

making a safe design for the entire system, and to avoid situations in which a malfunction or failure of such TOSHIBA products could cause loss of human life, bodily injury or damage to property.

In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent TOSHIBA products specifications. Also, please keep in mind the precautions and conditions set forth in the "Handling Guide for Semiconductor Devices," or "TOSHIBA Semiconductor Reliability Handbook" etc..

■ The TOSHIBA products listed in this document are intended for usage in general electronics applications (computer, personal equipment, office equipment, measuring equipment, industrial robotics, domestic appliances, etc.). These TOSHIBA products are neither intended nor warranted for usage in equipment that requires extraordinarily high quality and/or reliability or a malfunction or failure of which may cause loss of human life or bodily injury ("Unintended Usage"). Unintended Usage include atomic energy control instruments, airplane or spaceship instruments traffic signal instruments control instruments medical instruments. all types of transportation instruments, traffic signal instruments, combustion control instruments, medical instruments, all types of safety devices, etc.. Unintended Usage of TOSHIBA products listed in this document shall be made at the customer's

The products described in this document are subject to the foreign exchange and foreign trade laws.

The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA CORPORATION for any infringements of intellectual property or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any intellectual property or other rights of TOSHIBA CORPORATION or others.

The information contained herein is subject to change without notice.

3-23-31 2000-10-19

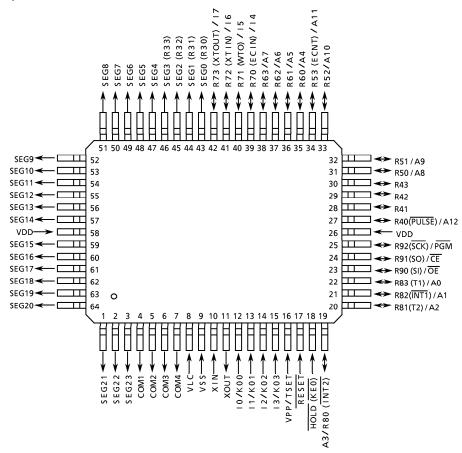

# Pin Assignment (Top View)

P-QFP64-1420-1.00A

## **Pin Function**

The TMP47P823V has MCU mode and PROM mode.

## (1) MCU mode

The TMP47C823 and the TMP47P823V are pin compatible (TEST pin for out-going test, Be fixed to low level).

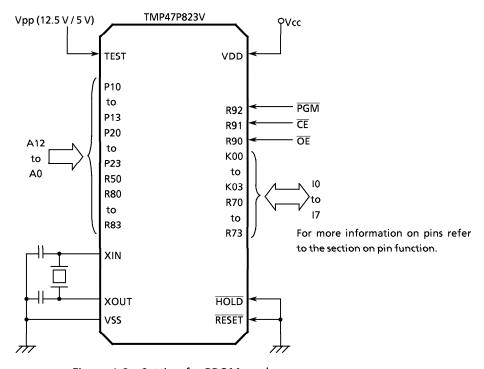

# (2) PROM mode

| Pin Name      | Input / Output                                        | Functions                                      | Pin Name (MCU Mode) |  |  |  |

|---------------|-------------------------------------------------------|------------------------------------------------|---------------------|--|--|--|

| A12           |                                                       |                                                | R40                 |  |  |  |

| A11 to A8     |                                                       |                                                | R50 to R53          |  |  |  |

| A7 to A4      | Input  I/O  Input  Power supply  Output  Power supply | Address inputs                                 | R60 to R63          |  |  |  |

| A3 to A0      |                                                       |                                                | R80 to R83          |  |  |  |

| 17 to 14      |                                                       |                                                | R73 to R70          |  |  |  |

| 13 to 10      | 1/0                                                   | Data inputs / outputs                          | K03 to K00          |  |  |  |

| PGM           |                                                       | Program control input                          | R92                 |  |  |  |

| CE            | Input                                                 | Chip Enable input                              | R91                 |  |  |  |

| ŌĒ            |                                                       | Chip Enable input                              | R90                 |  |  |  |

| VPP           |                                                       | + 12.5 V / 6 V (Program supply voltage)        | TEST                |  |  |  |

| vcc           | Power supply                                          | +5 V                                           | VDD                 |  |  |  |

| VSS           |                                                       | 0 V                                            | VSS                 |  |  |  |

| SEG31 to SEG0 |                                                       |                                                |                     |  |  |  |

| COM4 to COM1  | Output                                                | Open                                           |                     |  |  |  |

| VLC           |                                                       |                                                |                     |  |  |  |

| N.C.          | Power supply                                          |                                                |                     |  |  |  |

| R53 to R51    |                                                       |                                                |                     |  |  |  |

| R63 to R60    | ]                                                     | Be fixed to low level                          |                     |  |  |  |

| R43 to R40    | 1/0                                                   |                                                |                     |  |  |  |

| R33 to R30    |                                                       |                                                |                     |  |  |  |

| RESET         | Input                                                 |                                                |                     |  |  |  |

| HOLD          | Input                                                 | PROM mode setting pins. Be fixed to low level. |                     |  |  |  |

| XIN           | Input                                                 |                                                |                     |  |  |  |

| XOUT          | Output                                                | Resonator connecting pins                      |                     |  |  |  |

### **Operational Description**

The following is an explanation of hardware configuration and operation in relation to the TMP47P823V. The TMP47P823V is the same as the TMP47C623/823 except that an EPROM or OTP is used instead of a Mask ROM.

### 1. Operation Mode

The TMP47P823V has an MCU mode and a PROM mode.

#### 1.1 MCU mode

The MCU mode is set by fixing the TEST / VPP pin at the "L" level. Operation in the MCU mode is the same as for the TMP47C623/823, except that the TEST / VPP pin does not have pull-down resistor and cannot be used open.

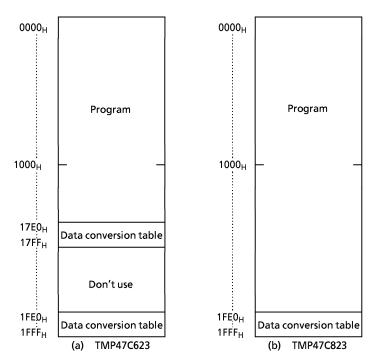

### 1.1.1 Program memory

The program storage area is the same as for the TMP47C823. Data conversion tables must be set in two locations when using the TMP47P823V to check TMP47C623 operation.

Figure 1-1. Program area

### 1.1.2 Data memory

The TMP47P823V has two 256  $\times$  4-bit data memory banks (DMB0, DMB1).

When using the TMP47P823V as a TMP47C623 evaluator, do not write data to address  $80_{\rm H}$  and following, even though the DMB1 addresses are  $00\text{-}FF_{\rm H}$ . There is no necessary to take into consideration a special function Shared area because one is built in DMB0.

# 1.1.3 Input/output circuitry

## (1) Control pins

This is the same as for the TMP47C623/823 except that there is no built-in pull-down resistance for the TEST pin.

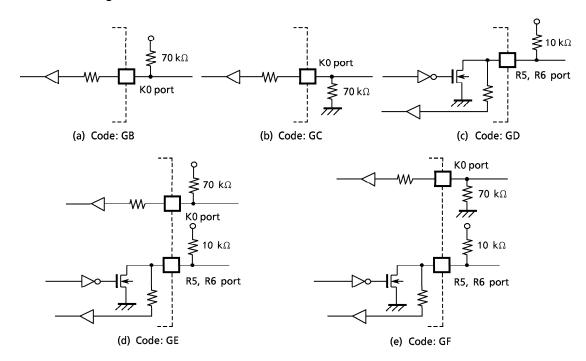

# (2) I/O Ports

The input/output circuit of the TMP47P823V is the same as I/O code GA of the TMP47C623/823. External resistance, for example, is required when using as evaluator of other I/O codes (GB to GF) (Refer to Figure 1-3).

Figure 1-2. I/O code and external circuitry

#### 1.2 PROM mode

The PROM mode is set by setting the RESET, HOLD pins to the "L" level. The PROM mode can be used as a general-purpose PROM writer for program writing and verification (A high-speed program mode is used set the ROM type the same as for the TMM2764AD).

An adapter socket (part No. BM1146) is available for connecting a PROM writer.

Figure 1-3. Setting for PROM mode

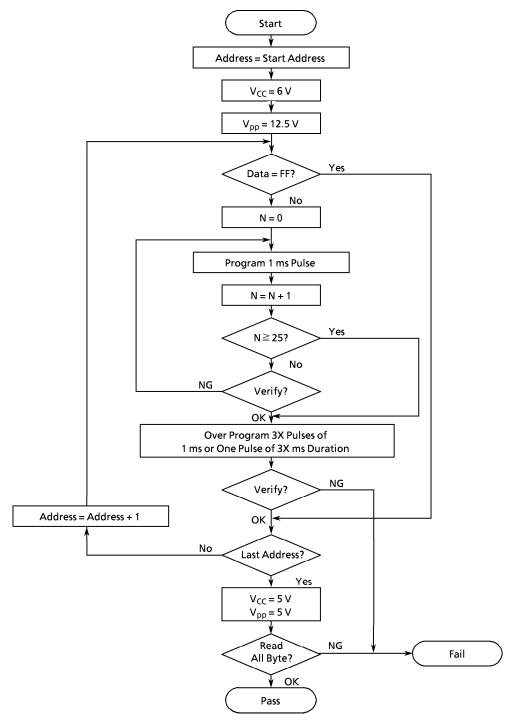

### 1.2.1 High-speed programming mode

The device is set up in the high speed programming mode when the programming voltage (12.5 V) is applied to the Vpp terminal with Vcc = 6 V and  $\overline{PGM} = V_{IH4}$ . The programming is achieved by applying a Single TTL low level 1 ms, pulse the  $\overline{PGM}$  input after addresses and data are stable. Then the programmed data is verified by using program Verify Mode. If the programmed data is not correct, another program pulse of 1 ms is applied and then programmed data is verified. This should be repeated until the program operates correctly (max. 25 times). After correctly programming the selected address, one additional program pulse with pulse width 3 times that needed for programming is applied. When programming has been completed, the data in all addresses should be verified with Vcc = Vpp = 5 V.

Figure 1-4. Flowchart

# **Electrical Characteristics**

Absolute Maximum Ratings  $(V_{SS} = 0 V)$

| Parameter                       | Symbol             | Pins                                                 | Ratings                        | Unit |  |

|---------------------------------|--------------------|------------------------------------------------------|--------------------------------|------|--|

| Supply Voltage                  | $V_{DD}$           |                                                      | – 0.3 to 7                     | V    |  |

| Supply Voltage (LCD drive)      | $V_{LC}$           |                                                      | $-0.3$ to $V_{DD} + 0.3$       | ٧    |  |

| Input Voltage                   | $V_{IN}$           |                                                      | $-0.3$ to $V_{DD} + 0.3$       | ٧    |  |

| Output Voltage                  | V <sub>OUT1</sub>  | Except sink open drain pin, but include ports R7, R3 | - 0.3 to V <sub>DD</sub> + 0.3 | V    |  |

|                                 | Vout2              | Sink open drain pin, but include ports R7, R3        | – 0.3 to 10                    |      |  |

| Output Coment (Box 1 min)       | I <sub>OUT1</sub>  | I <sub>OUT1</sub> Exept port R4                      |                                |      |  |

| Output Current (Per 1 pin)      | I <sub>OUT2</sub>  | Port R4                                              | 30                             | mA   |  |

| Output Current (Total)          | Σ I <sub>OUT</sub> | Port R4                                              | 60                             | mA   |  |

| Power Dissipation [Topr = 50°C] | PD                 |                                                      | 600                            | mW   |  |

| Soldering Temperature (time)    | Tsld               |                                                      | 260 (10 s)                     | °C   |  |

| Storage Temperature             | Tstg               |                                                      | – 55 to 125                    | °C   |  |

| Operating Temperature           | Topr               |                                                      | – 40 to 70                     | °C   |  |

Note: The absolute maximum ratings are rated values which must not be exceeded during operation, even for an instant. Any one of the ratings must not be exceeded. If any absolute maximum rating is exceeded, a device may break down or its performance may be degraded, causing it to catch fire or explode resulting in injury to the user. Thus, when designing products which include this device, ensure that no absolute maximum rating value will ever be exceeded.

**Recommended Opeating Conditions**

$(V_{SS} = 0 \text{ V}, \text{ Topr} = -40 \text{ to } 70^{\circ}\text{C})$

| Parameter          | Symbol           | Pins                    | Conditions                                  | Min                  | Max                  | Unit |

|--------------------|------------------|-------------------------|---------------------------------------------|----------------------|----------------------|------|

|                    |                  |                         | In the Normal mode<br>(fc = 4.2 MHz)        | 2.7                  |                      |      |

| CompleMala         | .,               |                         | In the Normal mode<br>(fc = 5.0 MHz) Note 2 |                      |                      | .,   |

| Supply Voltage     | V <sub>DD</sub>  |                         | In the Normal mode<br>(fc = 6.0 MHz)        | 4.5                  | 6.0                  | V    |

|                    |                  |                         | In the SLOW mode                            | 2.7                  |                      |      |

|                    |                  |                         | In the HOLD mode                            | 2.0                  |                      |      |

|                    | $V_{IH1}$        | Except Hysteresis Input | $V_{DD} \ge 4.5 V$                          | $V_{DD} \times 0.7$  |                      | v    |

| Input High Voltage | $V_{\text{IH}2}$ | Hysteresis Input        |                                             | $V_{DD} \times 0.75$ | $V_{DD}$             |      |

|                    | V <sub>IH3</sub> |                         | V <sub>DD</sub> < 4.5 V                     | $V_{DD} \times 0.9$  |                      |      |

|                    | V <sub>IL1</sub> | Except Hysteresis Input | \/ > A 5 \/                                 | $V_{DD} \ge 4.5 V$   |                      |      |

| Input Low Voltage  | $V_{IL2}$        | Hysteresis Input        | V <sub>DD</sub> = 4.3 V                     | 0                    | $V_{DD} \times 0.25$ | V    |

|                    | $V_{IL3}$        |                         | V <sub>DD</sub> < 4.5 V                     |                      | $V_{DD} \times 0.1$  |      |

| Clock Frequency    | fc XIN, XOUT     | XIN, XOUT               | High freq. $V_{DD} \ge 2.7 V$               |                      | 4.2                  |      |

|                    |                  |                         | High freq. $V_{DD} \ge 2.9  V$ Note 3       | 0.4                  | 5.0                  | MHz  |

|                    |                  |                         | High freq. $V_{DD} \ge 4.5 V$               |                      | 6.0                  |      |

|                    | fs               | XTIN, XTOUT             | Low freq.                                   | 30.0                 | 34.0                 | kHz  |

Note 1: The recommended operating conditions for a device are operating conditions under which it can be guaranteed that the device will operate as specified. If the device is used under operating conditions other than the recommended operating conditions (supply voltage, operating temperature range, specified AC/DC values etc.), malfunction may occur. Thus, when designing products which include this device, ensure that the recommended operating conditions for the device are always adhered to.

Note 2: Input Voltage VIH3, VIL3: in the SLOW and HOLD mode.

Note 3: Operating Temperature −30 to 50°C

**DC Characteristics**

$(V_{SS} = 0 \text{ V}, \text{ Topr} = -40 \text{ to } 70^{\circ}\text{C})$

| Parameter                              | Symbol                          | Pins                                                              | Conditions                                                   | Min | Тур.   | Max | Unit     |

|----------------------------------------|---------------------------------|-------------------------------------------------------------------|--------------------------------------------------------------|-----|--------|-----|----------|

| Hysteresis Voltage                     | V <sub>HS</sub>                 | Hysteresis Input                                                  |                                                              | 1   | 0.7    | 1   | <b>V</b> |

| Input Current                          | I <sub>IN1</sub>                | Port K0, TEST, RESET, HOLD  Open drain R port                     | V <sub>DD</sub> = 5.5 V,<br>V <sub>IN</sub> = 5.5 V /0 V     | _   |        | ± 2 | μΑ       |

| Input Low Current                      | I <sub>IL</sub>                 | Push-pull R port $V_{DD} = 5.5 \text{ V}, V_{IN} = 0.4 \text{ V}$ |                                                              | _   | _      | - 2 | mA       |

|                                        | R <sub>IN1</sub>                | Port K0 with pull-up/pull-down                                    |                                                              | 30  | 70     | 150 |          |

| Input Registance                       | R <sub>IN2</sub>                | RESET                                                             |                                                              | 100 | 220    | 450 | kΩ       |

| Output Leakage<br>Current              | I <sub>LO</sub>                 | Open drain port R                                                 | V <sub>DD</sub> = 5.5 V, V <sub>OUT</sub> = 5.5 V            | _   | _      | 2   | μΑ       |

| Output High Voltage                    | V <sub>OH</sub>                 | Push-pull R port                                                  | $V_{DD} = 4.5 \text{ V}, I_{OH} = -200 \ \mu\text{A}$        | 2.4 | _      | ı   | V        |

| Output Low Voltage                     | V <sub>OL</sub>                 | Except XOUT                                                       | $V_{DD} = 4.5 \text{ V, } I_{OL} = 1.6 \text{ mA}$           | ı   | _      | 0.4 | V        |

| Output Low Current                     | I <sub>OL</sub>                 | Port 4                                                            | $V_{DD} = 4.5 \text{ V}, V_{OL} = 1.0 \text{ V}$             | 15  | 20     | 1   | mA       |

| Segment Output Low<br>Registance       | R <sub>OS1</sub>                | SEG pin                                                           |                                                              |     | 40/20  |     |          |

| Common Output Low Registance           | R <sub>OC1</sub>                | COM pin                                                           |                                                              | ı   | 10/20  | ı   |          |

| Segment Output High<br>Registance      | R <sub>OS2</sub>                | SEG pin                                                           |                                                              |     |        | kΩ  |          |

| Common Output High<br>Registance       | R <sub>OC2</sub>                | COM pin                                                           | $V_{DD} = 5 \text{ V}, V_{DD} - V_{LC} = 3 \text{ V}$        | _   | 70/200 |     |          |

|                                        | V <sub>O2/3</sub>               |                                                                   |                                                              | 3.8 | 4.0    | 4.2 |          |

| Segment/Common Output Registance       | V <sub>O1/2</sub> SEG / COM pin | SEG / COM pin                                                     |                                                              | 3.3 | 3.5    | 3.7 | V        |

| Output Registance                      | V <sub>O1/3</sub>               |                                                                   |                                                              | 2.8 | 3.0    | 3.2 |          |

| Supply Current<br>(in the Normal mode) | I <sub>DD</sub>                 |                                                                   | $V_{DD} = 5.5 \text{ V}, V_{LC} = V_{SS}$<br>fc = 4 MHz      | 1   | 3      | 6   | mA       |

| Supply Current<br>(in the SLOW mode)   | I <sub>DDS</sub>                |                                                                   | $V_{DD} = 3.0 \text{ V}, V_{LC} = V_{SS}$<br>fs = 32.768 kHz | ı   | 30     | 60  | μΑ       |

| Supply Current<br>(in the HOLD mode)   | I <sub>DDH</sub>                |                                                                   | V <sub>DD</sub> = 5.5 V                                      | _   | 0.5    | 10  | μΑ       |

Note 1: Typ. values show those at  $T_{opr} = 25$ °C,  $V_{DD} = 5$  V.

Note 2: Input Current  $I_{\text{IN1}}$ ; The current through resistor is not included, when the input

resistor (pull-up/pull-down) is contained.

Note 3: Output Resistance  $R_{os}$ ,  $R_{oc}$ ; Shows on-resistance at the level switching.

Note 4:  $V_{O2/3}$ ; Shows 2/3 level output voltage, when the 1/4 or 1/3 duty LCD is used.

Note 5:  $V_{O1/2}$ ; Shows 1/2 level output voltage, when the 1/2 duty or static LCD is used.

Note 6:  $V_{O1/3}$ ; Shows 1/3 level output voltage, when the 1/4 or 1/3 duty LCD is used.

Note 7: Supply Current  $I_{DD}$ ,  $I_{DDH}$  ;  $V_{IN} = 5.3 \text{ V} / 0.2 \text{ V}$

The K0 port is open when the input resistor is contained. The voltage applied to the R port is within the valid range.

Supply Current  $I_{DDS}$  ;  $V_{IN} = 2.8 \text{ V} / 0.2 \text{ V}$ . Only low frequency clock is only osillated

(connecting XTIN, XTOUT).

Note 8: When using LCD, it is necessary to consider values of  $R_{OS1/2}$  and  $R_{OC1/2}$ .

Note 9: Times for SEG / COM output switching on ;  $R_{OS1}$ ,  $R_{OC1}$ : 2/fs (s)

$R_{OS2}$ ,  $R_{OC2}$ :  $1/(n \cdot f_F)$  (1/n: duty,  $f_F$ : frame frequency)

3-23-39 2000-10-19

**AC Characteristics**

$$(V_{SS} = 0 \text{ V}, T_{opr} = -40 \text{ to } 70^{\circ}\text{C})$$

| Parameter                                  | Symbol           | Conditions                   | Min           | Тур. | Max | Unit |

|--------------------------------------------|------------------|------------------------------|---------------|------|-----|------|

|                                            |                  | in the Normal mode           | 1.3           | _    | 20  | μS   |

| Instruction Cycle Time                     | tcy              | in the SLOW mode             | 235           | ı    | 267 | μS   |

| High Level Clock Pulse Width               | t <sub>WCH</sub> |                              |               |      |     |      |

| Low Level Clock Pulse Width                | t <sub>WCL</sub> | For external clock operation | ation 80      |      | _   | ns   |

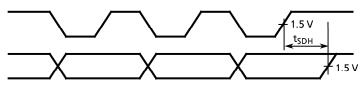

| Shift data Hold Time                       | t <sub>SDH</sub> |                              | 0.5 tcy – 0.3 | _    | _   | μS   |

| High Speed Timer / Counter input frequency | f <sub>HT</sub>  | ECIN input                   | _             | _    | fc  | MHz  |

Note: Shift data Hold time:

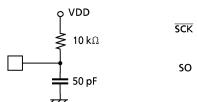

External circuit for SCK pin and SO pin

Serial port (completion of transmission)

**Recommended Oscillating Conditions**

$(V_{SS} = 0 \text{ V}, T_{opr} = -40 \text{ to } 70^{\circ}\text{C})$

Recommended oscillating conditions of the TMP47P823V are equal to the TMP47C623/823's.

DC / AC Characteristics

$(V_{SS} = 0 V)$

## (1) Read Operation

| Parameter                 | Symbol           | Condition                      | Min                   | Тур. | Max                   | Unit |

|---------------------------|------------------|--------------------------------|-----------------------|------|-----------------------|------|

| Output Level High Voltage | V <sub>IH4</sub> |                                | V <sub>CC</sub> × 0.7 | -    | V <sub>CC</sub>       | ٧    |

| Output Level Low Voltage  | V <sub>IL4</sub> |                                | 0                     | -    | V <sub>CC</sub> × 0.1 | ٧    |

| Supply Voltage            | V <sub>CC</sub>  |                                |                       |      |                       |      |

| Programming Voltage       | V <sub>PP</sub>  |                                | 4.75                  | -    | 6.0                   | V    |

| Address Access Time       | t <sub>ACC</sub> | V <sub>CC</sub> = 5.0 ± 0.25 V | 0                     | -    | 350                   | ns   |