# 74LVC1G79

# Single D-type flip-flop; positive-edge trigger Rev. 11 — 2 July 2012

**Product data sheet**

#### 1. **General description**

The 74LVC1G79 provides a single positive-edge triggered D-type flip-flop.

Information on the data input is transferred to the Q-output on the LOW-to-HIGH transition of the clock pulse. The D-input must be stable one set-up time prior to the LOW-to-HIGH clock transition for predictable operation.

Inputs can be driven from either 3.3 V or 5 V devices. This feature allows the use of this device in a mixed 3.3 V and 5 V environment.

This device is fully specified for partial power-down applications using I<sub>OFF</sub>. The I<sub>OFF</sub> circuitry disables the output, preventing the damaging backflow current through the device when it is powered down.

#### **Features and benefits** 2.

- Wide supply voltage range from 1.65 V to 5.5 V

- High noise immunity

- Complies with JEDEC standard:

- ◆ JESD8-7 (1.65 V to 1.95 V)

- ◆ JESD8-5 (2.3 V to 2.7 V)

- ◆ JESD8B/JESD36 (2.7 V to 3.6 V)

- ESD protection:

- HBM JESD22-A114F exceeds 2000 V

- MM JESD22-A115-A exceeds 200 V

- $\pm$  24 mA output drive (V<sub>CC</sub> = 3.0 V)

- CMOS low power consumption

- Latch-up performance exceeds 250 mA

- Direct interface with TTL levels

- Inputs accept voltages up to 5 V

- Multiple package options

- Specified from -40 °C to +85 °C and -40 °C to +125 °C.

# Single D-type flip-flop; positive-edge trigger

# 3. Ordering information

Table 1. Ordering information

| Type number | Package           |        |                                                                                                                                |          |  |  |  |  |

|-------------|-------------------|--------|--------------------------------------------------------------------------------------------------------------------------------|----------|--|--|--|--|

|             | Temperature range | Name   | Description                                                                                                                    | Version  |  |  |  |  |

| 74LVC1G79GW | –40 °C to +125 °C | TSSOP5 | plastic thin shrink small outline package;<br>5 leads; body width 1.25 mm                                                      | SOT353-1 |  |  |  |  |

| 74LVC1G79GV | –40 °C to +125 °C | SC-74A | plastic surface-mounted package; 5 leads                                                                                       | SOT753   |  |  |  |  |

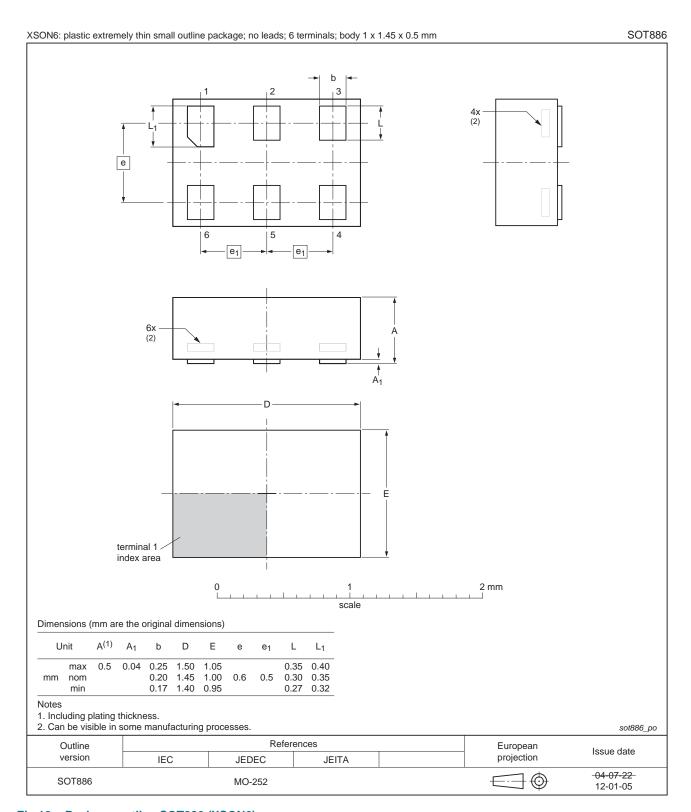

| 74LVC1G79GM | –40 °C to +125 °C | XSON6  | plastic extremely thin small outline package; no leads; 6 terminals; body $1 \times 1.45 \times 0.5$ mm                        | SOT886   |  |  |  |  |

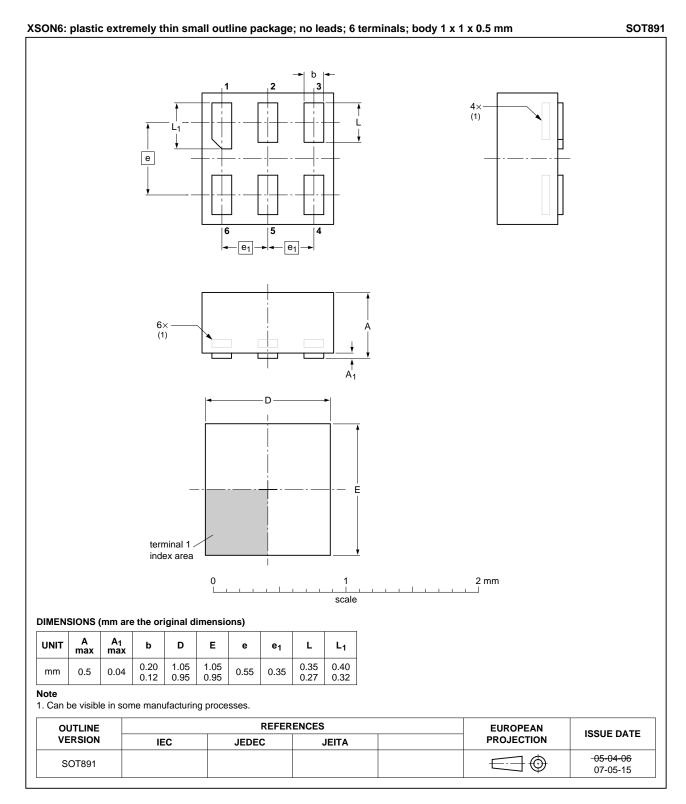

| 74LVC1G79GF | –40 °C to +125 °C | XSON6  | plastic extremely thin small outline package; no leads; 6 terminals; body $1 \times 1 \times 0.5$ mm                           | SOT891   |  |  |  |  |

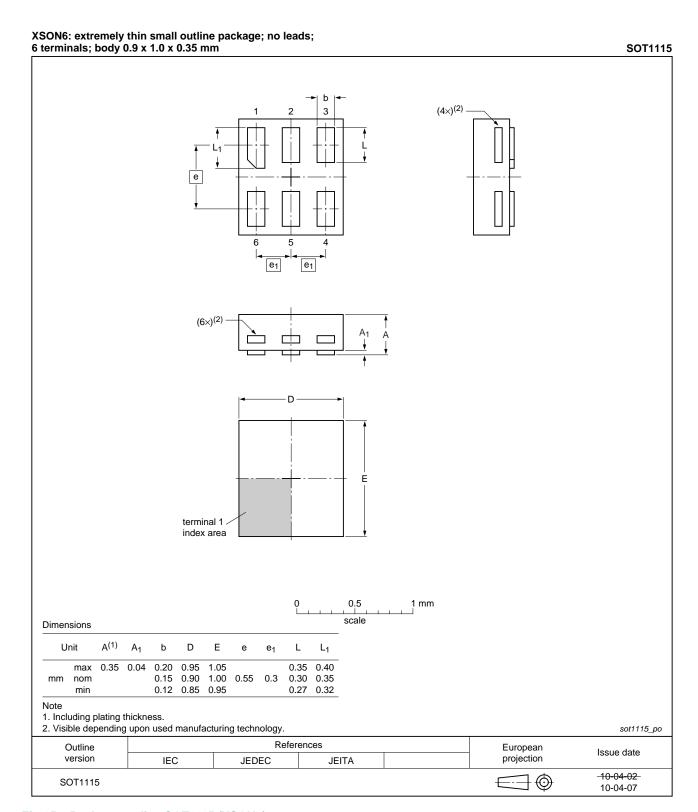

| 74LVC1G79GN | –40 °C to +125 °C | XSON6  | extremely thin small outline package; no leads; 6 terminals; body $0.9 \times 1.0 \times 0.35$ mm                              | SOT1115  |  |  |  |  |

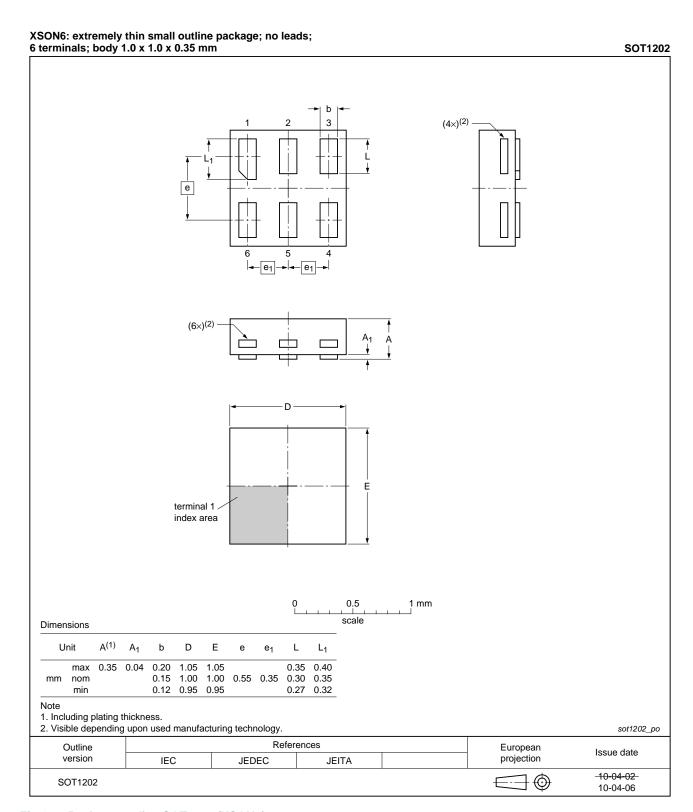

| 74LVC1G79GS | –40 °C to +125 °C | XSON6  | extremely thin small outline package; no leads; 6 terminals; body $1.0 \times 1.0 \times 0.35$ mm                              | SOT1202  |  |  |  |  |

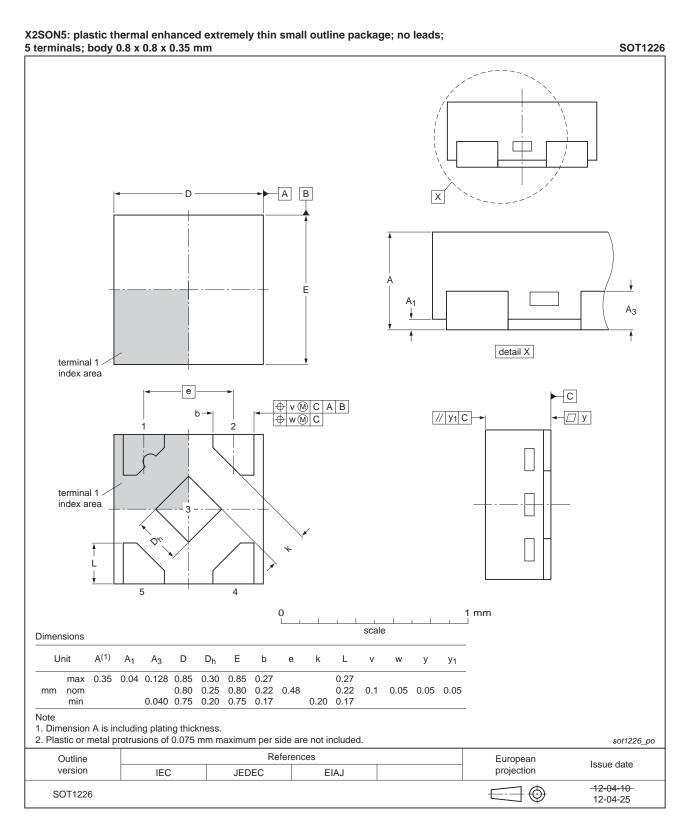

| 74LVC1G79GX | –40 °C to +125 °C | X2SON5 | X2SON5: plastic thermal enhanced extremely thin small outline package; no leads; 5 terminals; body $0.8\times0.8\times0.35$ mm | SOT1226  |  |  |  |  |

# 4. Marking

Table 2. Marking codes

| Type number | Marking <sup>[1]</sup> |

|-------------|------------------------|

| 74LVC1G79GW | VP                     |

| 74LVC1G79GV | V79                    |

| 74LVC1G79GM | VP                     |

| 74LVC1G79GF | VP                     |

| 74LVC1G79GN | VP                     |

| 74LVC1G79GS | VP                     |

| 74LVC1G79GX | VP                     |

<sup>[1]</sup> The pin 1 indicator is located on the lower left corner of the device, below the marking code.

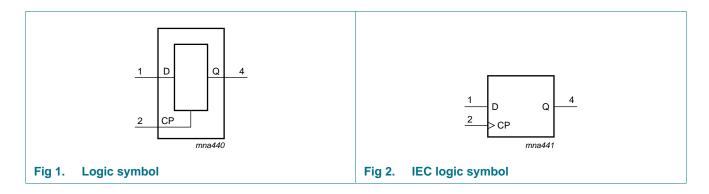

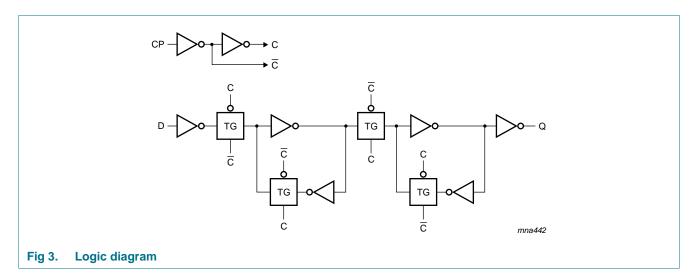

# 5. Functional diagram

74LVC1G79

All information provided in this document is subject to legal disclaimers.

### Single D-type flip-flop; positive-edge trigger

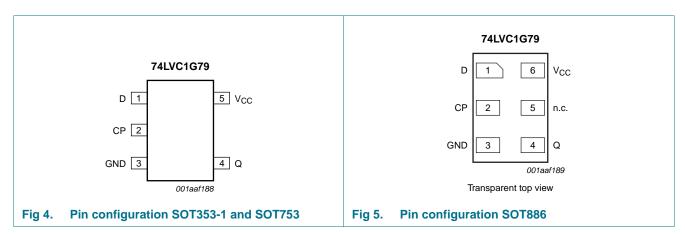

# 6. Pinning information

### 6.1 Pinning

# Single D-type flip-flop; positive-edge trigger

# 6.2 Pin description

Table 3. Pin description

| Symbol   | Pin               | Pin   |                   |  |

|----------|-------------------|-------|-------------------|--|

|          | TSSOP5 and X2SON5 | XSON6 | _                 |  |

| D        | 1                 | 1     | data input        |  |

| CP       | 2                 | 2     | clock pulse input |  |

| GND      | 3                 | 3     | ground (0 V)      |  |

| Q        | 4                 | 4     | data output       |  |

| n.c.     | -                 | 5     | not connected     |  |

| $V_{CC}$ | 5                 | 6     | supply voltage    |  |

# 7. Functional description

Table 4. Function table[1]

| •          |   | Output |

|------------|---|--------|

| СР         | D | Q      |

| $\uparrow$ | L | L      |

| $\uparrow$ | Н | Н      |

| L          | X | q      |

<sup>[1]</sup> H = HIGH voltage level;

L = LOW voltage level;

$<sup>\</sup>uparrow$  = LOW-to-HIGH CP transition;

X = don't care;

q = lower case letter indicates the state of referenced input, one set-up time prior to the LOW-to-HIGH CP transition.

### Single D-type flip-flop; positive-edge trigger

# 8. Limiting values

Table 5. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134). Voltages are referenced to GND (ground = 0 V).

| Symbol           | Parameter               | Conditions                                                         | Min              | Max            | Unit |

|------------------|-------------------------|--------------------------------------------------------------------|------------------|----------------|------|

| $V_{CC}$         | supply voltage          |                                                                    | -0.5             | +6.5           | V    |

| I <sub>IK</sub>  | input clamping current  | V <sub>I</sub> < 0 V                                               | -50              | -              | mA   |

| VI               | input voltage           |                                                                    | [ <u>1]</u> -0.5 | +6.5           | V    |

| I <sub>OK</sub>  | output clamping current | $V_O > V_{CC}$ or $V_O < 0$ V                                      | -                | ±50            | mA   |

| Vo               | output voltage          | Active mode                                                        | [1][2] -0.5      | $V_{CC} + 0.5$ | V    |

|                  |                         | Power-down mode                                                    | [1][2] -0.5      | +6.5           | V    |

| Io               | output current          | $V_O = 0 V \text{ to } V_{CC}$                                     | -                | ±50            | mA   |

| I <sub>CC</sub>  | supply current          |                                                                    | -                | 100            | mA   |

| $I_{GND}$        | ground current          |                                                                    | -100             | -              | mA   |

| P <sub>tot</sub> | total power dissipation | $T_{amb} = -40 ^{\circ}\text{C} \text{ to } +125 ^{\circ}\text{C}$ | [3] _            | 250            | mW   |

| T <sub>stg</sub> | storage temperature     |                                                                    | -65              | +150           | °C   |

<sup>[1]</sup> The input and output voltage ratings may be exceeded if the input and output current ratings are observed.

# 9. Recommended operating conditions

Table 6. Recommended operating conditions

| Symbol              | Parameter                           | Conditions                                  | Min  | Тур | Max      | Unit |

|---------------------|-------------------------------------|---------------------------------------------|------|-----|----------|------|

| $V_{CC}$            | supply voltage                      |                                             | 1.65 | -   | 5.5      | V    |

| $V_{I}$             | input voltage                       |                                             | 0    | -   | 5.5      | V    |

| Vo                  | output voltage                      | Active mode                                 | 0    | -   | $V_{CC}$ | V    |

|                     |                                     | V <sub>CC</sub> = 0 V; Power-down mode      | 0    | -   | 5.5      | V    |

| T <sub>amb</sub>    | ambient temperature                 |                                             | -40  | -   | +125     | °C   |

| $\Delta t/\Delta V$ | input transition rise and fall rate | $V_{CC} = 1.65 \text{ V to } 2.7 \text{ V}$ | -    | -   | 20       | ns/V |

|                     |                                     | $V_{CC} = 2.7 \text{ V to } 5.5 \text{ V}$  | -    | -   | 10       | ns/V |

<sup>[2]</sup> When  $V_{CC} = 0 \text{ V}$  (Power-down mode), the output voltage can be 5.5 V in normal operation.

<sup>[3]</sup> For TSSOP5 and SC-74A packages: above 87.5 °C the value of P<sub>tot</sub> derates linearly with 4.0 mW/K. For XSON6 and X2SON5 packages: above 118 °C the value of P<sub>tot</sub> derates linearly with 7.8 mW/K.

# Single D-type flip-flop; positive-edge trigger

# 10. Static characteristics

Table 7. Static characteristics

At recommended operating conditions. Voltages are referenced to GND (ground = 0 V).

| Symbo              | l Parameter               | Conditions                                                                                                    | Min                  | Typ[1] | Max                      | Unit         |

|--------------------|---------------------------|---------------------------------------------------------------------------------------------------------------|----------------------|--------|--------------------------|--------------|

| T <sub>amb</sub> = | –40 °C to +85 °C          |                                                                                                               |                      |        |                          |              |

| V <sub>IH</sub>    | HIGH-level input voltage  | V <sub>CC</sub> = 1.65 V to 1.95 V                                                                            | $0.65 \times V_{CC}$ | -      | -                        | V            |

|                    |                           | $V_{CC} = 2.3 \text{ V to } 2.7 \text{ V}$                                                                    | 1.7                  | -      | -                        | V            |

|                    |                           | $V_{CC} = 2.7 \text{ V to } 3.6 \text{ V}$                                                                    | 2.0                  | -      | -                        | V            |

|                    |                           | V <sub>CC</sub> = 4.5 V to 5.5 V                                                                              | $0.7 \times V_{CC}$  | -      | -                        | V            |

| $V_{IL}$           | LOW-level input voltage   | V <sub>CC</sub> = 1.65 V to 1.95 V                                                                            | -                    | -      | $0.35 \times V_{CC}$     | V            |

|                    |                           | V <sub>CC</sub> = 2.3 V to 2.7 V                                                                              | -                    | -      | 0.7                      | V            |

|                    |                           | V <sub>CC</sub> = 2.7 V to 3.6 V                                                                              | -                    | -      | 0.8                      | V            |

|                    |                           | V <sub>CC</sub> = 4.5 V to 5.5 V                                                                              | -                    | -      | $0.3 \times V_{CC}$      | V            |

| V <sub>OH</sub>    | HIGH-level output voltage | $V_I = V_{IH}$ or $V_{IL}$                                                                                    |                      |        |                          |              |

|                    |                           | $I_{O} = -100 \ \mu A; \ V_{CC} = 1.65 \ V \ to \ 5.5 \ V$                                                    | $V_{CC}-0.1$         | -      | -                        | V            |

|                    |                           | $I_{O} = -4 \text{ mA}; V_{CC} = 1.65 \text{ V}$                                                              | 1.2                  | -      | -                        | V            |

|                    |                           | $I_{O} = -8 \text{ mA}; V_{CC} = 2.3 \text{ V}$                                                               | 1.9                  | -      | -                        | V            |

|                    |                           | $I_{O} = -12 \text{ mA}; V_{CC} = 2.7 \text{ V}$                                                              | 2.2                  | -      | -                        | V            |

|                    |                           | $I_{O} = -24 \text{ mA}; V_{CC} = 3.0 \text{ V}$                                                              | 2.3                  | -      | -                        | V            |

|                    |                           | $I_{O} = -32 \text{ mA}; V_{CC} = 4.5 \text{ V}$                                                              | 3.8                  | -      | -                        | V            |

| $V_{OL}$           | LOW-level output voltage  | $V_I = V_{IH}$ or $V_{IL}$                                                                                    |                      |        |                          |              |

|                    |                           | $I_O = 100 \mu A$ ; $V_{CC} = 1.65 \text{ V to } 5.5 \text{ V}$                                               | -                    | -      | 0.1                      | V            |

|                    |                           | $I_{O} = 4 \text{ mA}; V_{CC} = 1.65 \text{ V}$                                                               | -                    | -      | 0.45                     | V            |

|                    |                           | $I_{O} = 8 \text{ mA}; V_{CC} = 2.3 \text{ V}$                                                                | -                    | -      | 0.3                      | V            |

|                    |                           | $I_O = 12 \text{ mA}; V_{CC} = 2.7 \text{ V}$                                                                 | -                    | -      | 0.4                      | V            |

|                    |                           | $I_O = 24 \text{ mA}; V_{CC} = 3.0 \text{ V}$                                                                 | -                    | -      | 0.55                     | V            |

|                    |                           | $I_O = 32 \text{ mA}; V_{CC} = 4.5 \text{ V}$                                                                 | -                    | -      | 0.55                     | V            |

| I <sub>I</sub>     | input leakage current     | $V_I = 5.5 \text{ V or GND}$ ; $V_{CC} = 0 \text{ V to } 5.5 \text{ V}$                                       | -                    | ±0.1   | ±5                       | μΑ           |

| I <sub>OFF</sub>   | power-off leakage current | $V_{CC} = 0 \text{ V}$ ; $V_{I} \text{ or } V_{O} = 5.5 \text{ V}$                                            | -                    | ±0.1   | ±10                      | μΑ           |

| I <sub>CC</sub>    | supply current            | $V_I = 5.5 \text{ V or GND};$<br>$V_{CC} = 1.65 \text{ V to } 5.5 \text{ V}; I_O = 0 \text{ A}$               | -                    | 0.1    | 10                       | μΑ           |

| Δl <sub>CC</sub>   | additional supply current | per pin; $V_{CC} = 2.3 \text{ V to } 5.5 \text{ V};$<br>$V_{I} = V_{CC} - 0.6 \text{ V}; I_{O} = 0 \text{ A}$ | -                    | 5      | 500                      | μА           |

| Cı                 | input capacitance         | $V_{CC} = 3.3 \text{ V}; V_I = \text{GND to } V_{CC}$                                                         | -                    | 5      | -                        | pF           |

| T <sub>amb</sub> = | –40 °C to +125 °C         |                                                                                                               |                      |        |                          |              |

| $V_{IH}$           | HIGH-level input voltage  | V <sub>CC</sub> = 1.65 V to 1.95 V                                                                            | $0.65 \times V_{CC}$ | -      | -                        | V            |

|                    |                           | V <sub>CC</sub> = 2.3 V to 2.7 V                                                                              | 1.7                  | -      | -                        | V            |

|                    |                           | V <sub>CC</sub> = 2.7 V to 3.6 V                                                                              | 2.0                  | -      | -                        | V            |

|                    |                           | V <sub>CC</sub> = 4.5 V to 5.5 V                                                                              | $0.7 \times V_{CC}$  | -      | -                        | V            |

| V <sub>IL</sub>    | LOW-level input voltage   | V <sub>CC</sub> = 1.65 V to 1.95 V                                                                            | -                    | -      | $0.35 \times V_{CC}$     | V            |

|                    |                           | V <sub>CC</sub> = 2.3 V to 2.7 V                                                                              | -                    | -      | 0.7                      | V            |

|                    |                           | V <sub>CC</sub> = 2.7 V to 3.6 V                                                                              | -                    | -      | 0.8                      | V            |

|                    |                           | V <sub>CC</sub> = 4.5 V to 5.5 V                                                                              | -                    | -      | $0.3 \times V_{CC}$      | V            |

| 4LVC1G79           |                           | All information provided in this document is subject to legal disc                                            | laimers.             |        | © NXP B.V. 2012. All riç | ghts reserve |

|                    | data about                | Boy 11 3 July 2012                                                                                            |                      |        | ,                        | 6 05 2       |

### Single D-type flip-flop; positive-edge trigger

**Table 7. Static characteristics** ...continued

At recommended operating conditions. Voltages are referenced to GND (ground = 0 V).

| Symbol           | Parameter                 | Conditions                                                                                                      | Min          | Typ[1] | Max  | Unit |

|------------------|---------------------------|-----------------------------------------------------------------------------------------------------------------|--------------|--------|------|------|

| $V_{OH}$         | HIGH-level output voltage | $V_I = V_{IH}$ or $V_{IL}$                                                                                      |              |        |      |      |

|                  |                           | $I_O = -100~\mu A;~V_{CC} = 1.65~V$ to 5.5 $V$                                                                  | $V_{CC}-0.1$ | -      | -    | V    |

|                  |                           | $I_O = -4 \text{ mA}; V_{CC} = 1.65 \text{ V}$                                                                  | 0.95         | -      | -    | V    |

|                  |                           | $I_O = -8 \text{ mA}; V_{CC} = 2.3 \text{ V}$                                                                   | 1.7          | -      | -    | V    |

|                  |                           | $I_{O} = -12 \text{ mA}; V_{CC} = 2.7 \text{ V}$                                                                | 1.9          | -      | -    | V    |

|                  |                           | $I_{O} = -24 \text{ mA}; V_{CC} = 3.0 \text{ V}$                                                                | 2.0          | -      | -    | V    |

|                  |                           | $I_{O} = -32 \text{ mA}; V_{CC} = 4.5 \text{ V}$                                                                | 3.4          | -      | -    | V    |

| $V_{OL}$         | LOW-level output voltage  | $V_I = V_{IH}$ or $V_{IL}$                                                                                      |              |        |      |      |

|                  |                           | $I_{O}$ = 100 $\mu$ A; $V_{CC}$ = 1.65 V to 5.5 V                                                               | -            | -      | 0.1  | V    |

|                  |                           | $I_O = 4 \text{ mA}; V_{CC} = 1.65 \text{ V}$                                                                   | -            | -      | 0.70 | V    |

|                  |                           | $I_{O} = 8 \text{ mA}; V_{CC} = 2.3 \text{ V}$                                                                  | -            | -      | 0.45 | V    |

|                  |                           | $I_{O} = 12 \text{ mA}; V_{CC} = 2.7 \text{ V}$                                                                 | -            | -      | 0.60 | V    |

|                  |                           | $I_O = 24 \text{ mA}; V_{CC} = 3.0 \text{ V}$                                                                   | -            | -      | 0.80 | V    |

|                  |                           | $I_O = 32 \text{ mA}; V_{CC} = 4.5 \text{ V}$                                                                   | -            | -      | 0.80 | V    |

| I <sub>I</sub>   | input leakage current     | $V_I = 5.5 \text{ V or GND}$ ; $V_{CC} = 0 \text{ V to } 5.5 \text{ V}$                                         | -            | -      | ±100 | μΑ   |

| I <sub>OFF</sub> | power-off leakage current | $V_{CC} = 0 \text{ V}; V_{I} \text{ or } V_{O} = 5.5 \text{ V}$                                                 | -            | -      | ±200 | μΑ   |

| I <sub>CC</sub>  | supply current            | $V_I = 5.5 \text{ V or GND};$<br>$V_{CC} = 1.65 \text{ V to 5.5 V}; I_O = 0 \text{ A}$                          | -            | -      | 200  | μΑ   |

| Δl <sub>CC</sub> | additional supply current | per pin; $V_{CC} = 2.3 \text{ V to } 5.5 \text{ V};$<br>$V_{I} = V_{CC} - 0.6 \text{ V};$ $I_{O} = 0 \text{ A}$ | -            | -      | 5000 | μΑ   |

<sup>[1]</sup> All typical values are measured at  $V_{CC}$  = 3.3 V and  $T_{amb}$  = 25 °C.

# 11. Dynamic characteristics

Table 8. Dynamic characteristics

Voltages are referenced to GND (ground = 0 V). For test circuit see Figure 10.

| Symbol Parameter |                   | Conditions                                   | -40 | -40 °C to +85 °C |     | -40 °C to +125 °C |      | Unit |

|------------------|-------------------|----------------------------------------------|-----|------------------|-----|-------------------|------|------|

|                  |                   |                                              | Min | Typ[1]           | Max | Min               | Max  |      |

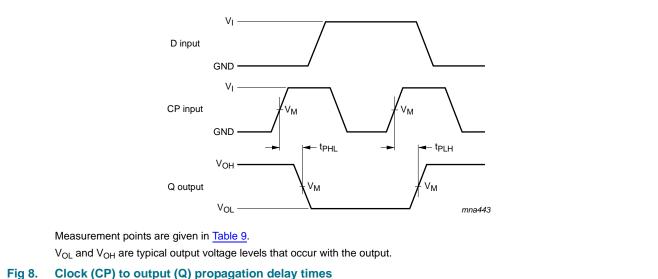

| t <sub>pd</sub>  | propagation delay | CP to Q; see Figure 8 [2]                    |     |                  |     |                   |      |      |

|                  |                   | $V_{CC} = 1.65 \text{ V to } 1.95 \text{ V}$ | 1.0 | 3.6              | 9.9 | 1.0               | 12.5 | ns   |

|                  |                   | $V_{CC} = 2.3 \text{ V to } 2.7 \text{ V}$   | 0.5 | 2.3              | 7.0 | 0.5               | 9.0  | ns   |

|                  |                   | $V_{CC} = 2.7 \text{ V}$                     | 0.5 | 2.6              | 6.0 | 0.5               | 8.0  | ns   |

|                  |                   | $V_{CC} = 3.0 \text{ V to } 3.6 \text{ V}$   | 0.5 | 2.2              | 5.0 | 0.5               | 6.5  | ns   |

|                  |                   | $V_{CC} = 4.5 \text{ V to } 5.5 \text{ V}$   | 0.5 | 1.7              | 3.8 | 0.5               | 5.0  | ns   |

| t <sub>su</sub>  | set-up time       | D to CP; see Figure 9                        |     |                  |     |                   |      |      |

|                  |                   | $V_{CC} = 1.65 \text{ V to } 1.95 \text{ V}$ | 2.5 | 1.4              | -   | 2.5               | -    | ns   |

|                  |                   | $V_{CC} = 2.3 \text{ V to } 2.7 \text{ V}$   | 1.7 | 0.9              | -   | 1.7               | -    | ns   |

|                  |                   | $V_{CC} = 2.7 \text{ V}$                     | 1.7 | 0.9              | -   | 1.7               | -    | ns   |

|                  |                   | $V_{CC} = 3.0 \text{ V to } 3.6 \text{ V}$   | 1.3 | 0.6              | -   | 1.2               | -    | ns   |

|                  |                   | $V_{CC} = 4.5 \text{ V to } 5.5 \text{ V}$   | 1.2 | 0.6              | -   | 1.2               | -    | ns   |

### Single D-type flip-flop; positive-edge trigger

Table 8.

Dynamic characteristics ...continued

Voltages are referenced to GND (ground = 0 V). For test circuit see Figure 10.

| Symbol           | Parameter                     | Conditions                                                  | -4    | 10 °C to +85 | 5 °C | -40 °C to | o +125 °C | Unit |

|------------------|-------------------------------|-------------------------------------------------------------|-------|--------------|------|-----------|-----------|------|

|                  |                               |                                                             | Min   | Typ[1]       | Max  | Min       | Max       |      |

| t <sub>h</sub>   | hold time                     | D to CP; see Figure 9                                       | '     | '            | •    | '         |           |      |

|                  |                               | $V_{CC} = 1.65 \text{ V to } 1.95 \text{ V}$                | 0     | -0.7         | -    | 0         | -         | ns   |

|                  |                               | $V_{CC} = 2.3 \text{ V to } 2.7 \text{ V}$                  | 0     | -0.4         | -    | 0         | -         | ns   |

|                  |                               | $V_{CC} = 2.7 \text{ V}$                                    | +0.5  | -0.3         | -    | 0.5       | -         | ns   |

|                  |                               | $V_{CC} = 3.0 \text{ V to } 3.6 \text{ V}$                  | +0.5  | -0.3         | -    | 0.5       | -         | ns   |

|                  |                               | $V_{CC} = 4.5 \text{ V to } 5.5 \text{ V}$                  | +0.5  | -0.2         | -    | 0.5       | -         | ns   |

| t <sub>W</sub>   | pulse width                   | CP HIGH or LOW; see Figure 9                                |       |              |      |           |           |      |

|                  |                               | $V_{CC} = 1.65 \text{ V to } 1.95 \text{ V}$                | 3.0   | 1.1          | -    | 3.0       | -         | ns   |

|                  |                               | $V_{CC} = 2.3 \text{ V to } 2.7 \text{ V}$                  | 2.5   | 0.7          | -    | 2.5       | -         | ns   |

|                  |                               | $V_{CC} = 2.7 \text{ V}$                                    | 2.5   | 0.6          | -    | 2.5       | -         | ns   |

|                  |                               | $V_{CC} = 3.0 \text{ V to } 3.6 \text{ V}$                  | 2.5   | 0.6          | -    | 2.5       | -         | ns   |

|                  |                               | $V_{CC} = 4.5 \text{ V to } 5.5 \text{ V}$                  | 2.0   | 0.5          | -    | 2.0       | -         | ns   |

| f <sub>max</sub> | maximum                       | CP; see Figure 9                                            |       |              |      |           |           |      |

|                  | frequency                     | $V_{CC} = 1.65 \text{ V to } 1.95 \text{ V}$                | 160   | 250          | -    | 160       | -         | MHz  |

|                  |                               | $V_{CC} = 2.3 \text{ V to } 2.7 \text{ V}$                  | 160   | 300          | -    | 160       | -         | MHz  |

|                  |                               | $V_{CC} = 2.7 \text{ V}$                                    | 160   | 350          | -    | 160       | -         | MHz  |

|                  |                               | $V_{CC} = 3.0 \text{ V to } 3.6 \text{ V}$                  | 160   | 450          | -    | 160       | -         | MHz  |

|                  |                               | $V_{CC} = 4.5 \text{ V to } 5.5 \text{ V}$                  | 200   | 500          | -    | 200       | -         | MHz  |

| $C_{PD}$         | power dissipation capacitance | $V_I = GND \text{ to } V_{CC};$<br>$V_{CC} = 3.3 \text{ V}$ | [3] _ | 17           | -    | -         | -         | pF   |

<sup>[1]</sup> Typical values are measured at  $T_{amb} = 25$  °C and  $V_{CC} = 1.8$  V, 2.5 V, 2.7 V, 3.3 V and 5.0 V respectively.

$$P_D = C_{PD} \times V_{CC}^2 \times f_i \times N + \sum (C_L \times V_{CC}^2 \times f_o) \text{ where:}$$

$f_i$  = input frequency in MHz;

$f_o$  = output frequency in MHz;

$C_1$  = output load capacitance in pF;

$V_{CC}$  = supply voltage in V;

N = number of inputs switching;

$\sum (C_L \times V_{CC}^2 \times f_o) = \text{sum of outputs.}$

<sup>[2]</sup>  $t_{pd}$  is the same as  $t_{PLH}$  and  $t_{PHL}$ .

<sup>[3]</sup>  $C_{PD}$  is used to determine the dynamic power dissipation ( $P_D$  in  $\mu W$ ).

74LVC1G79 **NXP Semiconductors**

# Single D-type flip-flop; positive-edge trigger

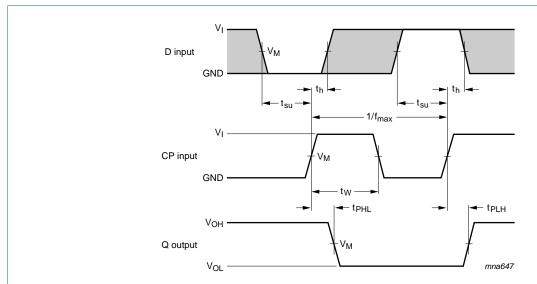

# 12. Waveforms

Measurement points are given in Table 9.

$V_{OL}$  and  $V_{OH}$  are typical output voltage levels that occur with the output.

Clock (CP) to output (Q) propagation delay times, clock pulse width, D to set-up times, the CP to D hold Fig 9. times and maximum clock pulse frequency

### Single D-type flip-flop; positive-edge trigger

Table 9. Measurement points

| Supply voltage   | Input               | Output                |

|------------------|---------------------|-----------------------|

| V <sub>CC</sub>  | V <sub>M</sub>      | V <sub>M</sub>        |

| 1.65 V to 1.95 V | $0.5 \times V_{CC}$ | $0.5 \times V_{CC}$   |

| 2.3 V to 2.7 V   | $0.5 \times V_{CC}$ | $0.5 \times V_{CC}$   |

| 2.7 V            | 1.5 V               | 1.5 V                 |

| 3.0 V to 3.6 V   | 1.5 V               | 1.5 V                 |

| 4.5 V to 5.5 V   | $0.5 \times V_{CC}$ | 0.5 × V <sub>CC</sub> |

Test data is given in Table 10.

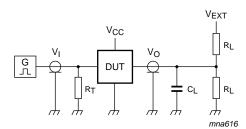

Definitions for test circuit:

$R_L$  = Load resistance.

$C_L$  = Load capacitance including jig and probe capacitance.

$R_T$  = Termination resistance should be equal to the output impedance  $Z_0$  of the pulse generator.

$V_{\text{EXT}}$  = External voltage for measuring switching times.

Fig 10. Test circuit for measuring switching times

Table 10. Test data

| Supply voltage   | Input           |             | Load  |                | V <sub>EXT</sub>                    |

|------------------|-----------------|-------------|-------|----------------|-------------------------------------|

| V <sub>CC</sub>  | VI              | $t_r = t_f$ | CL    | R <sub>L</sub> | t <sub>PLH</sub> , t <sub>PHL</sub> |

| 1.65 V to 1.95 V | V <sub>CC</sub> | ≤ 2.0 ns    | 30 pF | 1 kΩ           | open                                |

| 2.3 V to 2.7 V   | V <sub>CC</sub> | ≤ 2.0 ns    | 30 pF | 500 Ω          | open                                |

| 2.7 V            | 2.7 V           | ≤ 2.5 ns    | 50 pF | 500 Ω          | open                                |

| 3.0 V to 3.6 V   | 2.7 V           | ≤ 2.5 ns    | 50 pF | 500 Ω          | open                                |

| 4.5 V to 5.5 V   | V <sub>CC</sub> | ≤ 2.5 ns    | 50 pF | 500 Ω          | open                                |

### Single D-type flip-flop; positive-edge trigger

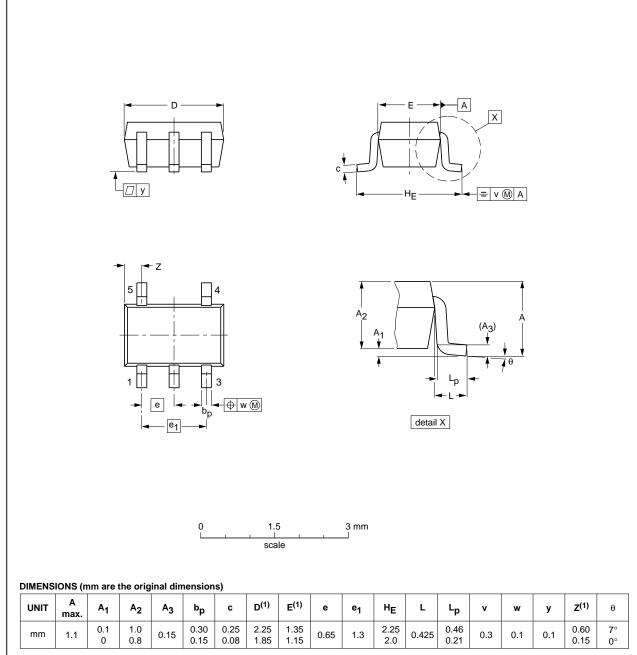

# 13. Package outline

TSSOP5: plastic thin shrink small outline package; 5 leads; body width 1.25 mm

SOT353-1

#### Note

<sup>1.</sup> Plastic or metal protrusions of 0.15 mm maximum per side are not included.

| OUTLINE<br>VERSION | REFERENCES |        |        |  | EUROPEAN   | ISSUE DATE                       |

|--------------------|------------|--------|--------|--|------------|----------------------------------|

|                    | IEC        | JEDEC  | JEITA  |  | PROJECTION | ISSUE DATE                       |

| SOT353-1           |            | MO-203 | SC-88A |  |            | <del>-00-09-01</del><br>03-02-19 |

Fig 11. Package outline SOT353-1 (TSSOP5)

74LVC1G79 All information provided in this document is subject to legal disclaimers.

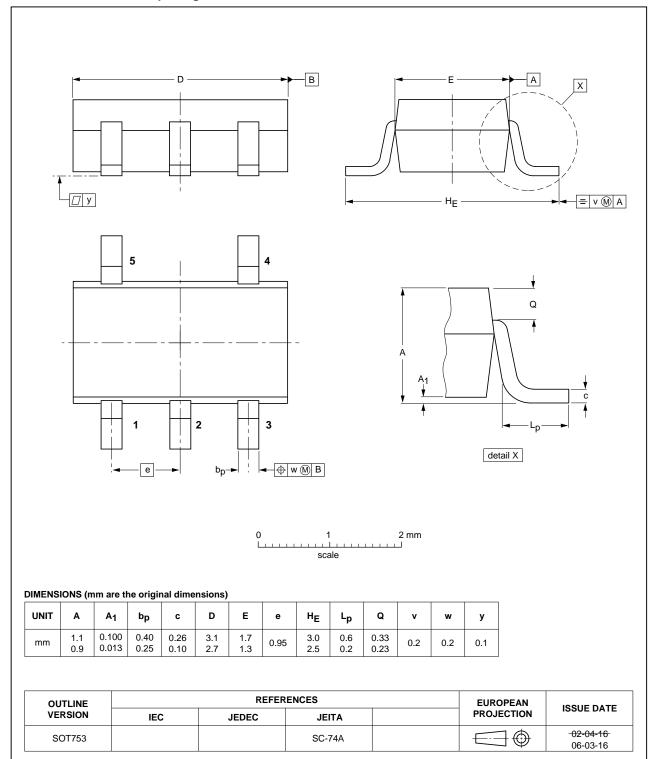

### Single D-type flip-flop; positive-edge trigger

### Plastic surface-mounted package; 5 leads

**SOT753**

Fig 12. Package outline SOT753 (SC-74A)

74LVC1G79 All information provided in this document is subject to legal disclaimers.

### Single D-type flip-flop; positive-edge trigger

Fig 13. Package outline SOT886 (XSON6)

74LVC1G79 All information provided in this document is subject to legal disclaimers.

74LVC1G79 **NXP Semiconductors**

Single D-type flip-flop; positive-edge trigger

Fig 14. Package outline SOT891 (XSON6)

All information provided in this document is subject to legal disclaimers.

### Single D-type flip-flop; positive-edge trigger

Fig 15. Package outline SOT1115 (XSON6)

74LVC1G79 All information provided in this document is subject to legal disclaimers.

74LVC1G79 **NXP Semiconductors**

### Single D-type flip-flop; positive-edge trigger

Fig 16. Package outline SOT1202 (XSON6)

74LVC1G79 All information provided in this document is subject to legal disclaimers.

16 of 21

### Single D-type flip-flop; positive-edge trigger

Fig 17. Package outline SOT1226 (X2SON5)

74LVC1G79 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2012. All rights reserved.

# Single D-type flip-flop; positive-edge trigger

# 14. Abbreviations

### Table 11. Abbreviations

| Acronym | Description                             |

|---------|-----------------------------------------|

| CMOS    | Complementary Metal Oxide Semiconductor |

| DUT     | Device Under Test                       |

| ESD     | ElectroStatic Discharge                 |

| НВМ     | Human Body Model                        |

| MM      | Machine Model                           |

| TTL     | Transistor-Transistor Logic             |

# 15. Revision history

### Table 12. Revision history

| Document ID    | Release date                      | Data sheet status            | Change notice | Supersedes     |

|----------------|-----------------------------------|------------------------------|---------------|----------------|

| 74LVC1G79 v.11 | 20120702                          | Product data sheet           | -             | 74LVC1G79 v.10 |

| Modifications: | <ul> <li>Added type</li> </ul>    | number 74LVC1G79GX (Se       | OT1226)       |                |

| 74LVC1G79 v.10 | 20120402                          | Product data sheet           | -             | 74LVC1G79 v.9  |

| Modifications: | <ul> <li>Errata in tal</li> </ul> | oel 3 corrected (description | CP input).    |                |

| 74LVC1G79 v.9  | 20111202                          | Product data sheet           | -             | 74LVC1G79 v.8  |

| Modifications: | <ul> <li>Legal pages</li> </ul>   | s updated.                   |               |                |

| 74LVC1G79 v.8  | 20100930                          | Product data sheet           | -             | 74LVC1G79 v.7  |

| 74LVC1G79 v.7  | 20070829                          | Product data sheet           | -             | 74LVC1G79 v.6  |

| 74LVC1G79 v.6  | 20061009                          | Product data sheet           | -             | 74LVC1G79 v.5  |

| 74LVC1G79 v.5  | 20040910                          | Product specification        | -             | 74LVC1G79 v.4  |

| 74LVC1G79 v.4  | 20040317                          | Product specification        | -             | 74LVC1G79 v.3  |

| 74LVC1G79 v.3  | 20030516                          | Product specification        | -             | 74LVC1G79 v.2  |

| 74LVC1G79 v.2  | 20030130                          | Product specification        | -             | 74LVC1G79 v.1  |

| 74LVC1G79 v.1  | 20010404                          | Product specification        | -             | -              |

|                |                                   |                              |               |                |

# Single D-type flip-flop; positive-edge trigger

# 16. Legal information

#### 16.1 Data sheet status

| Document status[1][2]          | Product status[3] | Definition                                                                            |

|--------------------------------|-------------------|---------------------------------------------------------------------------------------|

| Objective [short] data sheet   | Development       | This document contains data from the objective specification for product development. |

| Preliminary [short] data sheet | Qualification     | This document contains data from the preliminary specification.                       |

| Product [short] data sheet     | Production        | This document contains the product specification.                                     |

- [1] Please consult the most recently issued document before initiating or completing a design.

- [2] The term 'short data sheet' is explained in section "Definitions"

- [3] The product status of device(s) described in this document may have changed since this document was published and may differ in case of multiple devices. The latest product status information is available on the Internet at URL <a href="http://www.nxp.com">http://www.nxp.com</a>.

#### 16.2 Definitions

Draft — The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information.

Short data sheet — A short data sheet is an extract from a full data sheet with the same product type number(s) and title. A short data sheet is intended for quick reference only and should not be relied upon to contain detailed and full information. For detailed and full information see the relevant full data sheet, which is available on request via the local NXP Semiconductors sales office. In case of any inconsistency or conflict with the short data sheet, the full data sheet shall prevail.

**Product specification** — The information and data provided in a Product data sheet shall define the specification of the product as agreed between NXP Semiconductors and its customer, unless NXP Semiconductors and customer have explicitly agreed otherwise in writing. In no event however, shall an agreement be valid in which the NXP Semiconductors product is deemed to offer functions and qualities beyond those described in the Product data sheet.

#### 16.3 Disclaimers

Limited warranty and liability — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. NXP Semiconductors takes no responsibility for the content in this document if provided by an information source outside of NXP Semiconductors.

In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the *Terms and conditions of commercial sale* of NXP Semiconductors.

Right to make changes — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Suitability for use — NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors and its suppliers accept no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP Semiconductors accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the NXP Semiconductors product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.

NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using NXP Semiconductors products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). NXP does not accept any liability in this respect.

Limiting values — Stress above one or more limiting values (as defined in the Absolute Maximum Ratings System of IEC 60134) will cause permanent damage to the device. Limiting values are stress ratings only and (proper) operation of the device at these or any other conditions above those given in the Recommended operating conditions section (if present) or the Characteristics sections of this document is not warranted. Constant or repeated exposure to limiting values will permanently and irreversibly affect the quality and reliability of the device.

Terms and conditions of commercial sale — NXP Semiconductors products are sold subject to the general terms and conditions of commercial sale, as published at <a href="http://www.nxp.com/profile/terms">http://www.nxp.com/profile/terms</a>, unless otherwise agreed in a valid written individual agreement. In case an individual agreement is concluded only the terms and conditions of the respective agreement shall apply. NXP Semiconductors hereby expressly objects to applying the customer's general terms and conditions with regard to the purchase of NXP Semiconductors products by customer.

**No offer to sell or license** — Nothing in this document may be interpreted or construed as an offer to sell products that is open for acceptance or the grant, conveyance or implication of any license under any copyrights, patents or other industrial or intellectual property rights.

74LVC1G79

All information provided in this document is subject to legal disclaimers.

### Single D-type flip-flop; positive-edge trigger

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

Non-automotive qualified products — Unless this data sheet expressly states that this specific NXP Semiconductors product is automotive qualified, the product is not suitable for automotive use. It is neither qualified nor tested in accordance with automotive testing or application requirements. NXP Semiconductors accepts no liability for inclusion and/or use of non-automotive qualified products in automotive equipment or applications.

In the event that customer uses the product for design-in and use in automotive applications to automotive specifications and standards, customer (a) shall use the product without NXP Semiconductors' warranty of the product for such automotive applications, use and specifications, and (b) whenever customer uses the product for automotive applications beyond

NXP Semiconductors' specifications such use shall be solely at customer's own risk, and (c) customer fully indemnifies NXP Semiconductors for any liability, damages or failed product claims resulting from customer design and use of the product for automotive applications beyond NXP Semiconductors' standard warranty and NXP Semiconductors' product specifications.

**Translations** — A non-English (translated) version of a document is for reference only. The English version shall prevail in case of any discrepancy between the translated and English versions.

### 16.4 Trademarks

Notice: All referenced brands, product names, service names and trademarks are the property of their respective owners.

### 17. Contact information

For more information, please visit: http://www.nxp.com

For sales office addresses, please send an email to: salesaddresses@nxp.com

74LVC1G79 **NXP Semiconductors**

# Single D-type flip-flop; positive-edge trigger

# 18. Contents

| 1    | General description              | . 1 |

|------|----------------------------------|-----|

| 2    | Features and benefits            | . 1 |

| 3    | Ordering information             | . 2 |

| 4    | Marking                          | . 2 |

| 5    | Functional diagram               | . 2 |

| 6    | Pinning information              | . 3 |

| 6.1  | Pinning                          | . 3 |

| 6.2  | Pin description                  | . 4 |

| 7    | Functional description           | . 4 |

| 8    | Limiting values                  | . 5 |

| 9    | Recommended operating conditions | . 5 |

| 10   | Static characteristics           | . 6 |

| 11   | Dynamic characteristics          | . 7 |

| 12   | Waveforms                        | . 9 |

| 13   | Package outline                  | 11  |

| 14   | Abbreviations                    | 18  |

| 15   | Revision history                 | 18  |

| 16   | Legal information                | 19  |

| 16.1 | Data sheet status                | 19  |

| 16.2 | Definitions                      | 19  |

| 16.3 | Disclaimers                      | 19  |

| 16.4 | Trademarks                       | 20  |

| 17   | Contact information              | 20  |

| 12   | Contents                         | 21  |

Please be aware that important notices concerning this document and the product(s) described herein, have been included in section 'Legal information'.

Document identifier: 74LVC1G79

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

# NXP:

74LVC1G79GM-G 74LVC1G79GM-H 74LVC1G79GV 74LVC1G79GW-G 74LVC1G79GW-R