## Dolby Digital Decoder **M65863FP**

### **Product Note**

**April 1998**

MITSUBISHI ELECTRIC CORPORATION

### **Chapter 1**

### **Features**

This Audio Decoder for Dolby Digital (AC-3) M65863FP is a single device. The device decodes AC-3 bitstreams into PCM audio. Dolby Digital (AC-3) is a multi-channel audio coding algorithm developed by Dolby Laboratories, Inc.

- Decoding

- 1) 5.1 ch AC-3 bitstream

- 2) Dolby Pro Logic encoded 2ch Dolby Digital (AC-3) bitstream

- 3) Dolby Pro Logic encoded 2ch PCM data

- All input combinations from 1 to 5.1 channels

- Output: mono 5.1 surround

- Sampling rates: 32kHz, 44.1 kHz, 48 kHz and 96 kHz (96 kHz is for linear PCM only)

- Supports a maximum bit rate of 640 kbps at a full service (up to 448 kbps when 32 kHz sampling rates)

- 2 DIR (Digital Audio Interface Receiver)/ADC input interfaces

- · Serial input bitstream interface for DEMUX

- PCM output interface

- Standard 3-wire DAC output interface (data,clock,LR clock), 16/18/20/24 bit DAC word size

- Supports IEC958 digital audio output for Dolby Digital (AC-3) data stream

- I<sup>2</sup>C<sup>2</sup> interface and clocked serial (4 line) interface for host microcontroller

- · Generates audio test noise

- 2nd DSP I/F (twice higher PCM transfer rate)

- Controllable dynamic range compression

- · Programmable center and surround channel delays

- · Dialogue level control

- No external memory required (M65863FP doos not have memory space for surround delay)

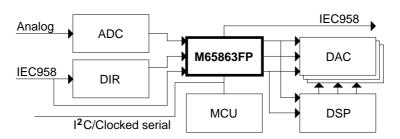

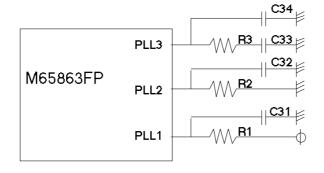

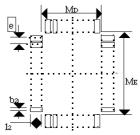

Figure 1.1 M65863FP Configuration Diagram (DIR I/F)

<sup>\*1</sup> Dolby, Dolby Digital (AC-3), and Pro Logic are registered trademarks of Dolby Laboratories Licensing Corp. Available only to licensees of Dolby Laboratories Licensing Corporation, San Francisco, CA 94111, USA, (415) 558-0200, from whom licensing and application information must be obtained.

<sup>\*2</sup> Phillips Semiconductors, "I2C bus specification", January, 1992

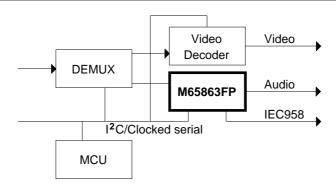

Figure 1.2 M65963FP Configuration Diagram (DEMUX I/F)

### **Chapter 2**

### **Device Overview**

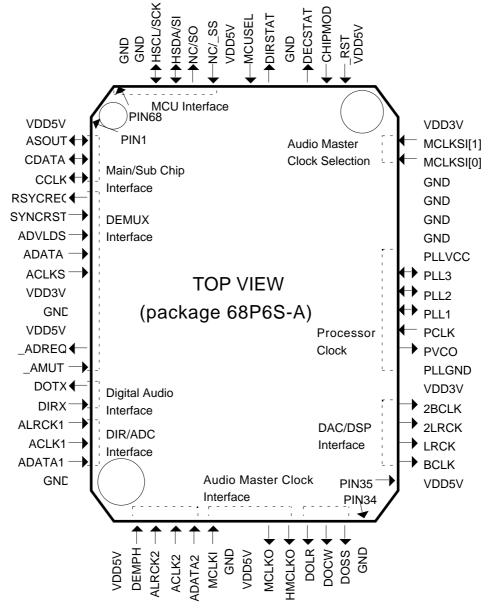

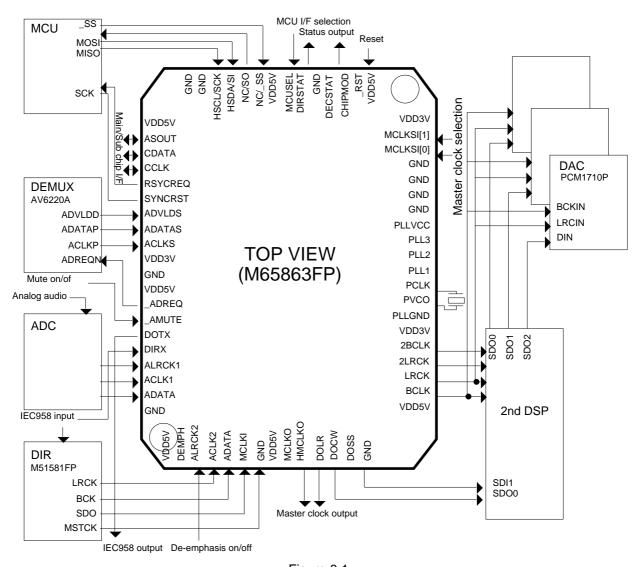

The figure 2.1 show the M65863FP I/O interface.

Figure 2.1 M65863FP I/O Interface

### **Chapter 3**

### **Input/Output Pins**

Table 3.1 shows input/output pins. "low active" pins are added "\_" to tail of pin name (ex. \_AERR).

Table 3.1 Input/Output Pins

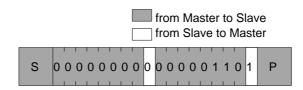

| Pin |          |      |     |     |         | able 3.1 Input/Output Fins                                                              |

|-----|----------|------|-----|-----|---------|-----------------------------------------------------------------------------------------|

| No. | Pin Name | Pins | I/O | Out | Voltage | Description                                                                             |

| 1   | VDD5V    | 7    | -   |     |         | Voltage supply 5V (I/O)                                                                 |

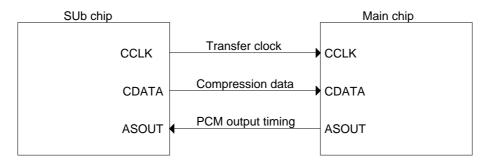

|     |          |      |     |     |         | Indication of audio data output timing (main chip output / sub chip                     |

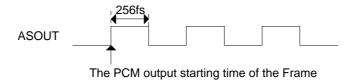

| 2   | ASOUT    | 1    | I/O | 2mA | D5      | input)                                                                                  |

|     |          |      |     |     |         | Dynamic range compression data input from sub chip / output to main chip                |

| 3   | CDATA    | 1    | I/O | 2mA | D5      | '                                                                                       |

|     |          |      |     |     |         | Dynamic range compression data transfer clock input from sub chip / output to main chip |

| 4   | CCLK     | 1    | I/O | 2mA | D5      | output to main only                                                                     |

| 5   | RSYCREQ  | 1    | 0   | 2mA | D5      | Indication of sync word lock condition                                                  |

| 6   | SYNCRST  | 1    |     |     | D5      | Sync world detection start signal                                                       |

| 7   | ADVLDS   | 1    |     | Щ   | D5      | Indication of valid data                                                                |

| 8   | ADATAS   | 1    |     |     | D5      | Data input from DEMUX                                                                   |

| 9   | ACLKS    | 1    |     |     | D5      | Clock input from DEMUX                                                                  |

| 10  | VDD3V    | 3    |     |     |         | Voltage supply 3.3V                                                                     |

| 11  | GND      | 7    | ı   |     |         | GND                                                                                     |

| 12  | VDD5V    |      |     |     |         |                                                                                         |

| 13  | _ADREQ   | 1    | 0   | 2mA | D5      | Data Request for DEMUX                                                                  |

| 14  | _AMUTE   | 1    |     |     | D5      | Mute sound0 (0 : Mute ON, 1 : Mute OFF)                                                 |

| 15  | DOTX     | 1    | 0   | 2mA | D5      | Digital audio interface IEC958 output                                                   |

| 16  | DIRX     | 1    |     |     | D5      | Digital audio interface IEC958 input                                                    |

| 17  | ALRCK1   | 1    |     |     | D5      | L/R clock from DIR/ADC                                                                  |

| 18  | ACLK1    | 1    | Ι   |     | D5      | Data from DIR                                                                           |

| 19  | ADATA1   | 1    |     |     | D5      | Bit clock from DIR/ADC                                                                  |

| 20  | GND      |      |     |     |         |                                                                                         |

| 21  | VDD5V    |      |     |     |         |                                                                                         |

| 22  | DEMPH    | 1    |     |     | D5      | De-emphasis control                                                                     |

| 23  | ALRCK2   | 1    |     |     | D5      | L/R clock from DIR/ADC                                                                  |

| 24  | ACLK2    | 1    |     |     | D5      | Bit clock from DIR                                                                      |

| 25  | ADATA2   | 1    |     |     | D5      | Data from DIR                                                                           |

| 26  | MCLKI    | 1    |     |     | D5      | Audio master clock input                                                                |

| 27  | GND      |      |     |     |         |                                                                                         |

| 28  | VDD5V    |      |     |     |         |                                                                                         |

| 29  | MCLKO    | 1    |     |     | D5      | Audio master clock output                                                               |

| 30  | HMCLKO   | 1    |     |     | D5      | Audio master clock output (1/2MCLKI)                                                    |

| 31  | DOLR     | 1    | 0   | 2mA | D5      | PCM output for L ch and R ch                                                            |

| 32  | DOCW     | 1    | 0   | 2mA | D5      | PCM output for C channel SW ch                                                          |

| 33  | DOSS     | 1    | 0   | 2mA | D5      | PCM output for SL ch and SR ch                                                          |

| Pin<br>No. | Pin Name             | Pins | I/O | Out | Voltage | Description                                                                                    |

|------------|----------------------|------|-----|-----|---------|------------------------------------------------------------------------------------------------|

| 34         | GND                  |      |     |     |         |                                                                                                |

|            | VDD5V                |      |     |     |         |                                                                                                |

|            | BCLK                 | 1    | 0   | 4mA | D5      | Bit clock for PCM output                                                                       |

|            | LRCK                 | 1    | 0   | 4mA | D5      | LR clock for PCM output                                                                        |

| 38         | 2LRCK                | 1    | 0   | 2mA | D5      | LR clock for 2nd DSP                                                                           |

| 39         | 2BCLK                | 1    | 0   | 2mA | D5      | Bit clock for 2nd DSP                                                                          |

| 40         | VDD3V                |      |     |     |         |                                                                                                |

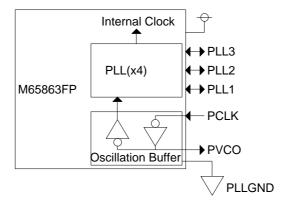

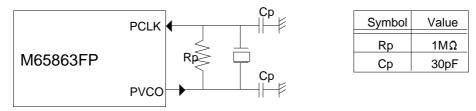

| 41         | PLLGND               | 1    | -   |     |         | GND for PLL                                                                                    |

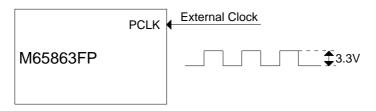

| 42         | PVCO                 | 1    | 0   |     | P3.3    | Processor clock output for crystal                                                             |

| 43         | PCLK                 | 1    | 1   |     | P3.3    | Processor clock input                                                                          |

| 44         | PLL1                 | 1    | 1/0 |     |         |                                                                                                |

|            | PLL2                 | 1    | 1/0 |     |         |                                                                                                |

|            | PLL3                 | 1    | I/O |     |         |                                                                                                |

|            | PLLVCC               | 1    | -   |     | P3.3    | VDD for PLL                                                                                    |

| 48         | GND                  |      |     |     |         |                                                                                                |

| 49         | GND                  |      |     |     |         |                                                                                                |

| 50         | GND                  |      |     |     |         |                                                                                                |

| 51         | GND                  |      |     |     |         |                                                                                                |

| 50         | MCI CITOI            | 2    |     |     | D5      | Selection of audio master clock<br>([0:1] = 00 : 512fs, 01 : 384fs, 10 : 256fs, 11 : Reserved) |

|            | MCLSI[0]<br>MCLSI[1] |      |     |     | DS      | ([0.1] = 00.01210, 01.00110, 10.20010, 11.1100011004)                                          |

|            | VDD3V                |      |     |     |         |                                                                                                |

|            | VDD5V                |      |     |     |         |                                                                                                |

|            | RST                  | 1    |     |     | D5      | Reset                                                                                          |

|            | CHIPMOD              | 1    |     |     | D5      | Chip mode                                                                                      |

|            | DECSTAT              | 1    | 0   | 2mA | D5      | Decode status (Normal : 1, Error : 0)                                                          |

|            | GND                  |      |     |     |         |                                                                                                |

|            | DIRSTAT              | 1    | 0   | 2mA | D5      | (AC-3:1, PCM:0)                                                                                |

|            | MCUSEL               | 1    | ı   |     | D5      | MCU I/F Selection (Clocked serial : 0, I2C : 1)                                                |

|            | VDD5V                |      |     |     |         | ,                                                                                              |

| 63         | _NC/SS               | 1    |     |     | D5      |                                                                                                |

|            | ADR/SO               | 1    | 0   | 4mA | D5      |                                                                                                |

|            | HSDA/SI              | 1    | I/O | 4mA | D5      |                                                                                                |

| 66         | HSCL/SCK             | 1    | I/O | 4mA | D5      |                                                                                                |

| 67         | GND                  |      |     |     |         |                                                                                                |

| 68         | GND                  |      |     |     |         |                                                                                                |

Note) D5 : Degital 5V I/O P3.3 : PLL oscillation I/O

#### <Audio input interface>

ACLK1 Bit clock input for DIR/ADC input (Line 1).

ADATA1 Data input for DIR/ADC interface (Line 1). Latched at the rising edge of ACLK1.

ALRCK1 LR clock input for DIR/ADC interface (Line 1).

ACLK2 Bit clock input for DIR/ADC input (Line 2).

ADATA2 Data input for DIR/ADC interface (Line 2). Latched at the rising edge of ACLK2.

ALRCK2 LR clock input for DIR/ADC interface (Line 2)

ACLKS Clock for DEMUX interface.

Product Note

M65863FP

April 1998

Dolby Digital Decoder

| ADATAS  | Data input for DEMUX interface. Latched at the rising edge of ACLKS.                                  |

|---------|-------------------------------------------------------------------------------------------------------|

| _AVLDS  | Data enable instruction for DEMUX interface. Data is input when this signal is enabled                |

|         | (0).                                                                                                  |

| _ADREQ  | Used in the data transmission control of DEMUX interface.                                             |

| SYNCRST | Synchronization lock cancel signal. M65863FP starts detecting sync word when this signal is disabled. |

| RSYCREQ | SYNCRST request signal which is enabled when M65863FP comes out of synchronization.                   |

synchronization

\_AMUTE Audio mute output signal. Output is muted when this signal is enabled (0). This signal is

valid for both DIR/ADC interface and DEMUX interface.

#### <Audio output interface>

DOLR PCM output terminal. When control register dspif is 0, L and R channel data are output.

When dspif is 1, L, R, C and SW channel data are output.

DOCW PCM output terminal. When control register dspif is 0, C and SW channel data are

output. When dspif is 1, SL and SR channel data are output.

DOSS PCM output terminal. When control register dspif is 0, SL and SR channel data are

output.

BCLK Bit clock output. LRCK LR clock output.

2BCLK Double-rate bit clock. Used in DSP interface.

2LRCK Double-rate LR clock. Used in DSP interface.

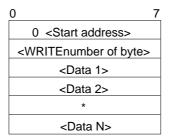

#### <Main/Sub Chip interface>

CHIPMOD Specifies the chip mode. Decodes the main service when 0, and decodes the associate

service when 1. Select decoding of main service when it is not necessary to decode dual

streams.

CCLK Transmission clock used in data transmission between main and sub chips during dual-

stream decoding. Sub chip becomes the clock master. This is valid only when control

register asmix is 1.

CDATA Data transmission line from sub chip to main chip during dual-stream decoding. This is

valid only when control register asmix is 1.

ASOUT Synchronization signal for dual-stream output. CCLK, CDATA and ASOUT terminals

may be open when dual-stream decoding is not required (when control register asmix is

0).

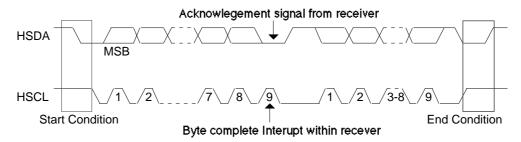

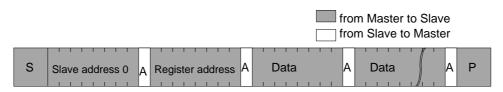

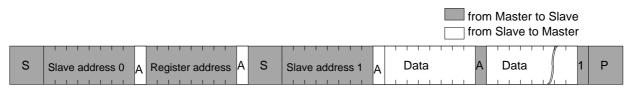

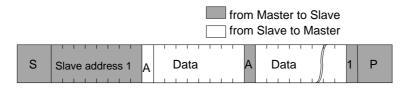

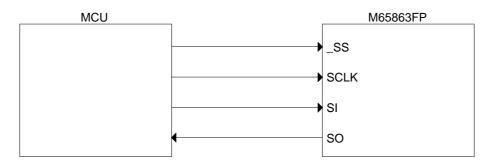

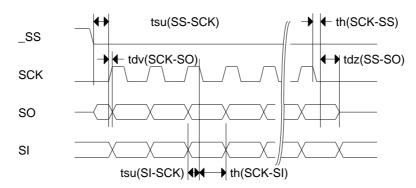

#### <MCU interface>

MCUSEL Selects which of synchronized serial and I2C is to be used as MCU interface.

Synchronized serial is selected when this is 0, and I<sup>2</sup>C is selected when 1.

HSCL/SCK Becomes data transmission clock input in either case of I<sup>2</sup>C or synchronized serial.

HSDA/SI Becomes data input/output terminal in the case of I<sup>2</sup>C, and data input terminal in the case

of synchronized serial.

ADR/SO Becomes chip address selection terminal in the case of I<sup>2</sup>C, and data output terminal in

the case of synchronized serial.

NC/SS Becomes enable signal in the case of synchronized serial. In the case of l<sup>2</sup>C, this may be

left open because it is not used.

#### <Audio master clock>

MCLKI Audio master clock input.

MCLSI [0:1] Indicates whether the audio master clock which is input from MCLKI is 512 fs, 384 fs or

256 fs. Only 384 fs or 256 fs can be selected when the sampling frequency is 96kHz.

MCLKO Audio master clock output which gives MCLKI as through-output.

Product Note

M65863FP

April 1998

Dolby Digital Decoder

HMCLKO Audio master clock output which gives MCLKI at 1/2-divided frequency.

<Dolby Digital encoded data input/output>

DIRX Digital audio interface IEC958 input.

DOTX Digital audio interface IEC958 output.

<Others>

DEMPH Enabled when control register demph is 10, turning de-emphasis ON when this is 0, and

de-emphasis OFF when 1.

DECSTAT Indicates the current decoding status: 1 during normal decoding and 0 at a time of error.

DIRSTAT Indicates the current DIR input stream: 1 in the case of Dolby Digital AC-3 input, 0 in the

case of PCM input.

### **Chapter 4**

### **Registers**

Table 4.1 shows the registers overview.

Table 4.1 Registers Overview

| Register                                   | Byte | Description                       |

|--------------------------------------------|------|-----------------------------------|

| Dolby Digital (AC-3) Bitstream Information | 13   | Synchronization Information       |

|                                            |      | Bitstream Information             |

| IEC958 Burst Information                   | 1    | IEC958 Burst Information          |

| Status                                     | 6    | CRC Result                        |

|                                            |      | Synchronization Condition         |

|                                            |      | Pointer to the input buffer       |

| Control                                    | 36   | I/O Signals Control               |

|                                            |      | Decoding Status Control           |

|                                            |      | Channel delay control             |

|                                            |      | Dynamic Range Control             |

|                                            |      | Pro Logic Control                 |

|                                            |      | Calibration Noise Control         |

|                                            |      | Mute Control                      |

|                                            |      | IEC958 Category code input        |

| Test                                       | 1    | Monitor of overflow and underflow |

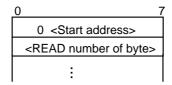

#### Register Address

Dual stream (main effect and Associate service) can be decoded with 2 M65863FP. In the case, the register addresses for a main chip (which decodes main effect) and those for a sub chip (which decodes associate service) are different.

In the following sections, only the register address for a main chip will be shown. For a sub chip you should add h'40 to the corresponding register address for a main chip. For a example, the address of the control register "synclock" is h'14 for a main chip and h'54 for a sub chip. In this may, the address range will be following.

Main chip : h'00~h'3f Sub chip : h'40~h'7f

### 4.1 Dolby Digital (AC-3) Bitstream Information Registers

Table 4.2 shows Dolby Digital (AC-3) bitstream information registers.

Table 4.2 Dolby Digital (AC-3) Bitstream Information Registers

| 1.14    | 1          |            |       | 1          |   | 1         |       | 1 | 7          |

|---------|------------|------------|-------|------------|---|-----------|-------|---|------------|

| bit     |            | !          |       | !          |   | !!        |       |   | ! <b>!</b> |

| Address | 0          | 1          | 2     | 3          | 4 | 5         | 6     | 7 | R/W        |

| h'00    |            |            |       | frmsizecod |   |           | fscod |   | R          |

| h'01    |            | bsmod      |       |            |   | bsid      |       |   | R          |

| h'02    | origbs     | copyrightb | lfeon | dsurmod    |   | acmod     |       |   | R          |

| h'03    | compre     | dynrnge    |       |            |   | dialnorm  |       |   | R          |

| h'04    |            |            |       | compr      |   |           |       |   | R          |

| h'05    |            |            |       | langcod    |   |           |       |   | R          |

| h'06    |            |            |       | dynrng     |   |           |       |   | R          |

| h'07    | audprodie  | roomtyp    |       |            |   | mixlevel  |       |   | R          |

| h'08    | compr2e    | dynrng2e   |       |            |   | dialnorm2 |       |   | R          |

| h'09    |            |            |       | compr2     |   |           |       |   | R          |

| h'0A    |            |            |       | langcod2   |   |           |       |   | R          |

| h'0B    |            |            | ·     | dynrng2    |   |           |       |   | R          |

| h'0C    | audprodi2e | roomtyp2   |       |            |   | mixlevel2 |       |   | R          |

#### address h'00

Sample Rate Code (fscod)

2 bits

This field indicates sampling rate according to the following table.

| fscod | Sampling Rate |

|-------|---------------|

| 0 0   | 48 kHz        |

| 0 1   | 44.1 kHz      |

| 1 0   | 32 kHz        |

| 1 1   | Reserved      |

Frame Size Code(frmsizecod)

6 bits

This field indicates nominal bit rate. This code is used along with the sample rate code to determine the number of bytes per frame.

#### address h'01

Bitstream Identification (bsid)

5 bits

This field contains the version number of the coder syntax.

M65863FP only supports 0 to 8.

#### Bitstream Mode(bsmod)

3 bits

This field indicates the type of service that the bitstream conveys as defined by the following table.

| bsmod | acmod   | Type of Service                             |

|-------|---------|---------------------------------------------|

| 000   | any     | Main audio service : complete main (CM)     |

| 0 0 1 | any     | Main audio service : music and effects (ME) |

| 010   | any     | Associated service : visually impaired (VI) |

| 011   | any     | Associated service : hearing impaired (HI)  |

| 100   | any     | Associated service : dialogue (D)           |

| 101   | any     | Associated service : commentary (C)         |

| 110   | any     | Associated service : emergency (E)          |

| 111   | 0 0 1   | Associated service : voice-over (VO)        |

| 111   | 010~111 | Main audio service : karaoke                |

#### address h'02

Audio Coding Mode (acmod)

3 bits

This field indicates channel array for audio service.

| acmod | Audio Coding Mode | Channel Array Ordering |

|-------|-------------------|------------------------|

| 000   | 1+1               | [Ch1,Ch2]              |

| 0 0 1 | 1/0               | [C]                    |

| 010   | 2/0               | [L,R]                  |

| 011   | 3/0               | [L,C,R]                |

| 100   | 2/1               | [L,R,S]                |

| 101   | 3/1               | [L,C,R,S]              |

| 110   | 2/2               | [L,R,SL,SR]            |

| 111   | 3/2               | [L,C,R,SL,SR]          |

#### **Dolby Surround Mode (dsurmod)**

2 bits

When acmod is 010, these bits indicate whether or not the program has been encoded in Dolby Surround.

| dsurmod | Indication                 |

|---------|----------------------------|

| 0 0     | Not indicated              |

| 0 1     | NOT Dolby Surround encoded |

| 1 0     | Dolby Surround encoded     |

| 11      | Reserved                   |

#### Low Frequency Effects ch On (Ifeon)

1 bit

If this bit has a value of 1, the sub-woofer channel is on. If this bit has a value of 0, the sub-woofer channel is off.

#### Copyright Bit (copyrightb)

1 bit

If this bit has a value of 1, the bitstream is protected by copyright. If this bit has a value of 0, the bitstream is not protected by copyright.

#### Original Bitstream (origbs)

<u>1 bit</u>

If this bit has a value of 1, this bitstream is an original bitstream. If this bit has a value of 0, this bitstream is a copy of another bitstream.

#### M65863FP

**Dolby Digital Decoder**

#### address h'03

**Dialogue Normalization (dialnorm)**

5 bits

This field contains how far the average dialogue level is below digital 100%.

**Dynamic Range Gain Word Exists (dynrnge)**

1 bit

If this bit is a 1, this bitstream has dynamic range gain word which can use dynamic range compression.

Heavy dynamic range Compression Code Exists (compre)

1 bit

If this bit is a 1, this bitstream has compression gain word which can use heavy dynamic range compression.

#### address h'04

Compression Gain Word (compr)

8 bits

If compre is a 1, this field indicates scale for the reproduced audio level in order to reproduce a very narrow dynamic range.

#### address h'05

Language Code (langcod)

8 bits

This field indicates the audio service language. If the language code doesn't exist in bitstream, this value indicates h'00.

#### address h'06

Dynamic Range Gain Word (dynrng)

8 bits

If dynrnge is a 1, this field indicates the scale of the reproduced audio level in order to reproduce an ordinary dynamic range.

#### address h'07

Mixing Level (mixlevel)

5 bits

This field contains the acoustic sound pressure level of the dialogue level of the final audio mixing session.

Room Type (roomtyp)

2 bits

This field indicates the type of mixing room used for the final audio mixing session.

| roomtyp | Type of Mixing Room         |

|---------|-----------------------------|

| 0 0     | Not indicated               |

| 0 1     | Large room. X curve monitor |

| 1 0     | Small room. flat monitor    |

| 1 1     | Reserved                    |

Audio Production Information Exists (audprodie)

1 bit

If this bit is a 1,this bitstream has mixing level data and room type data.

#### address h'08

Dialogue Normalization, Ch2 (dianorm2)

5 bits

This field contains dialogue normalization for ch2 when acmod indicates dual mono mode (acmod=000).

Dynamic Range Gain Word Exists, Ch2 (dynrng2e)

<u>1 bit</u>

If this bit is a 1, this bitstream has a dynamic range gain word for ch2 when acmod indicates dual mono mode (acmod=000).

Compression Gain Word Exists, Ch2 (compr2e)

1 bit

If this bit is a 1,this bitstream has a compression gain word for ch2 when acmod indicates dual mono

mode (acmod=000).

#### address h'09

Compression Gain Word, Ch2 (compr2)

8 bits

This field indicates compression gain word for ch2 when acmod indicates dual mono mode (acmod=000).

#### address h'0A

Language Code, Ch2 (langcod2)

8 bits

This field indicates language code for ch2 when acmod indicates dual mono mode (acmod=000).

#### address h'0B

Dynamic Range Gain Word, Ch2 (dynrng2)

8 bits

This field indicates dynamic range gain word for ch2 when acmod indicates dual mono mode (acmod=000).

#### address h'0C

Mixing Level, Ch2 (mixlevel2)

5 bits

This field contains mixing level for ch2 when acmod indicates dual mono mode (acmod=000).

Room Type, Ch2 (roomtyp2)

2 bits

This field contains room type for ch2 when acmod indicates dual mono mode (acmod=000).

Audio Production Information Exists, Ch2 (audprodi2e)

1 bit

This bit indicates audio production information for ch2 when acmod indicates dual mono mode (acmod=000).

#### 4.2 IEC958 Burst Information Registers

IEC958 burst information registers are provided. Table 4.3 shows IEC958 burst information registers.

Table4.3 IEC958 Burst Information Registers

| bit     |        | • |         | • | • | •      | • |   |     |

|---------|--------|---|---------|---|---|--------|---|---|-----|

| Address | 0      | 1 | 2       | 3 | 4 | 5      | 6 | 7 | R/W |

| h'0D    | burste | 0 | ierrflg |   |   | idtdep |   |   | R   |

#### address h'0D

Data Type Dependent Code (idtdep)

5 bits

3rd and 4th bit are reserved, and these values set '0'. If Data Type Code indicates Dolby Digital (AC-3) Data, other 3 bits field indicates same as bsmod code.

| idtdep | Type of Service                                                        |  |  |  |  |  |

|--------|------------------------------------------------------------------------|--|--|--|--|--|

| 00000  | Main audio service : complete main (CM)                                |  |  |  |  |  |

| 00001  | Main audio service : music and effects (ME)                            |  |  |  |  |  |

| 00010  | Associated service : visually impaired (VI)                            |  |  |  |  |  |

| 00011  | Associated service : hearing impaired (HI)                             |  |  |  |  |  |

| 00100  | Associated service : dialogue (D)                                      |  |  |  |  |  |

| 00101  | Associated service : commentary (C)                                    |  |  |  |  |  |

| 00110  | Associated service : emergency (E)                                     |  |  |  |  |  |

| 00111  | Associated service : voice-over (VO) , or main audio service : karaoke |  |  |  |  |  |

Error Flag (ierrflg)

<u>1 bit</u>

This field indicates error condition for burst data, according to the following table.

| ierrflg | Status   |  |  |  |

|---------|----------|--|--|--|

| 0       | No error |  |  |  |

| 1       | Error    |  |  |  |

Burst Data Exists (burste)

<u>1 bit</u>

If this bit is a1, burst data which is assigned "istrnums" in control register exists.

#### 4.3 Status Registers

The default values are described in the bit fields shown in table 4.4.

Table 4.4 Status Registers

| bit     |         |         |        |              |   |   |         |       |     |

|---------|---------|---------|--------|--------------|---|---|---------|-------|-----|

| Address | 0       | 1       | 2      | 3            | 4 | 5 | 6       | 7     | R/W |

| h'0E    | synccon | syncdet | decode |              |   |   |         | bserr | R   |

|         | 1       | 1       | 0      | 0            | 0 | 0 | 0       | 1     |     |

| h'0F    | crc1err |         |        |              |   |   | crc2err |       | R   |

|         | 0 0     |         | 0      | 0            | 0 | 0 | 0 0     |       |     |

| h'10    |         |         |        | readpointer  |   |   |         |       | R/W |

| h'11    |         |         |        | ,            |   |   |         |       |     |

| h'12    |         |         |        | writepointer |   |   |         |       | R   |

| h'13    |         |         |        |              |   |   |         |       |     |

#### address h'0E

Error Information (bserr)

<u>1 bit</u>

This bit indicates error status.

| bserr | Description                                                     |  |  |  |  |  |

|-------|-----------------------------------------------------------------|--|--|--|--|--|

| 0     | The value of bsid is less than 8 and encode error doesn't exist |  |  |  |  |  |

| 1     | The value of bsid is more than 9, or encode error exists        |  |  |  |  |  |

#### **Decoding Condition Information (decode)**

<u>1 bit</u>

| decode | Description    |

|--------|----------------|

| 0      | Regular decode |

| 1      | Mute           |

#### Synchronous Detection Information (syncdet)

<u>1 bit</u>

This bit indicates whether sync word was detected per frame or not.

| syncdet | Description                |

|---------|----------------------------|

| 0       | Sync word was detected     |

| 1       | Sync word was not detected |

#### Synchronous Lock Information (synccon)

<u>1 bit</u>

This bit indicates whether sync word is locked or not.

| synccon | Description             |  |  |  |  |

|---------|-------------------------|--|--|--|--|

| 0       | Sync word is locked     |  |  |  |  |

| 1       | Sync word is not locked |  |  |  |  |

2 bits

2 bits

#### address h'0F

CRC2 Checked Data (crc2err)

This field indicates the status of CRC error for CRC2.

| crc2err | Description                   |

|---------|-------------------------------|

| 0 0     | No error                      |

| 0 1     | One error                     |

| 1 0     | More than 2 sequential errors |

| 11      | Reserved                      |

#### CRC1 Checked Data (crc1err)

This field indicates the status of CRC error for CRC1.

| crc1err | Description                   |

|---------|-------------------------------|

| 0 0     | No error                      |

| 0 1     | One error                     |

| 1 0     | More than 2 sequential errors |

| 1 1     | Reserved                      |

### address h'10 address h'11

Read Pointer to the Input Data Buffer (readpointer)

16 bits

Read pointer to the input data buffer. Read/Write operation are allowed when M65863FP is not decoding. Only read operation is allowed when M65863FP is decoding.

### address h'12 address h'13

Write Pointer to the Input Data Buffer (writepointer)

16 bits

Write pointer to the input data buffer. Only read operation is allowed.

### 4.4 Control Registers

The default values are described in the bit fields shown in table 4.5.

Table 4.5 Control Registers

|          |           |          | rabi     | 0 110 001111 | or Registers                                 |           |            |          |          |

|----------|-----------|----------|----------|--------------|----------------------------------------------|-----------|------------|----------|----------|

| bit      |           |          |          |              |                                              |           |            |          | ŢŢ       |

| Address  | 0         | 1        | 2        | 3            | 4                                            | 5         | 6          | 7        | R/W      |

| h'14     | outbitlen |          |          | dacform      |                                              |           | synclock   |          | R/W      |

|          | 0 0       |          |          | 000          |                                              |           | 010        |          | <u> </u> |

| h'15     | dempha    |          |          | dirform      |                                              | dspif     | dacclkmode |          | R/W      |

|          | 0 0       |          |          | 000          |                                              | 0         | 0          | 0        | <u> </u> |

| h'16     |           | Inoise   | cnoise   | rnoise       | srnoise                                      | slnoise   | swnoise    | noisesel | R/W      |

|          | 0         | 0        | 0        | 0            | 0                                            | 0         | 0          | 0        | <u> </u> |

| h'17     | inbitlen  |          | pdecmode |              | pfsmode                                      |           | inportsel  |          | R/W      |

|          | 0 0       |          | 0 0      |              | 0 0                                          |           | 0 0        |          | <u> </u> |

| h'18     |           |          |          |              |                                              |           | narwid     | autobal  | R/W      |

|          |           |          | 000000   |              |                                              |           | 0          | 0        | <u> </u> |

| h'19     | asmix     |          | outchmod |              | stereo                                       |           | compmod    |          | R/W      |

|          | 0         |          | 111      |              | 0 0                                          |           | 0.0        |          | <u> </u> |

| h'1A     |           |          |          |              | dirdatamode                                  | )         | syncrsten  |          | R/W      |

|          |           | 0000     |          |              | 0 0                                          |           | 0 0        |          | <u> </u> |

| h'1B     |           |          |          | hcompsc      |                                              |           |            |          | R/W      |

|          |           |          | ,        | 011111       | <u>1 1                                  </u> |           |            |          | Щ        |

| h'1C     |           |          |          | Icompsc      |                                              |           |            |          | R/W      |

|          |           |          |          | 011111       | 1 1                                          |           |            |          | <u> </u> |

| h'1D     |           |          |          |              | kcapdef                                      |           | kcapmod    | karaply  | R/W      |

|          |           |          |          |              | 0 0                                          |           | 0          | 0        | <u> </u> |

| h'1E     |           |          |          | dialevel     |                                              |           |            |          | R/W      |

|          |           |          |          | 011111       | 1 1                                          |           |            |          | ļ ļ      |

| h'1F     |           |          |          | 111111       |                                              |           |            |          | <u> </u> |

| h'20     |           | istrnums |          |              | copyrightb                                   | burstcont | muteonoff  | attlevel | R/W      |

|          |           | 000      |          | 0            | 0                                            | 0         | 1          | 0        |          |

| h'21     |           |          |          | catecode     |                                              |           |            |          | R/W      |

|          |           |          |          | 000000       | 0 0                                          |           |            |          | <u> </u> |

| h'22     |           |          |          | kcoeffa      |                                              |           |            |          | R/W      |

|          |           |          |          | 000000       |                                              |           |            |          |          |

| h'23     |           |          |          | 000000       | 0 0                                          |           |            |          | <u> </u> |

| h'24     |           |          |          | kcoeffb      |                                              |           |            |          | R/W      |

|          |           |          |          | 000000       | 0 0                                          |           |            |          |          |

| h'25     |           |          |          | 000000       |                                              |           |            |          | <u> </u> |

| h'26     |           |          |          | kcoeffc      |                                              |           |            |          | R/W      |

| <u> </u> |           |          |          | 000000       |                                              |           |            |          | ļ ļ      |

| h'27     |           |          |          | 000000       | 0 0                                          |           |            |          | <u> </u> |

| h'28     |           |          |          | kcoeffd      |                                              |           |            |          | R/W      |

|          |           |          |          | 000000       |                                              |           |            |          | ļ ļ      |

| h'29     |           |          |          | 000000       | 0 0                                          |           |            |          |          |

| bit      |   |   |   |         |     |   |   |   |     |

|----------|---|---|---|---------|-----|---|---|---|-----|

| Address  | 0 | 1 | 2 | 3       | 4   | 5 | 6 | 7 | R/W |

| h'2A     |   |   | • | kcoeffe |     |   |   |   | R/W |

|          |   |   |   | 0000000 | 0   |   |   |   |     |

| h'2B     |   |   |   | 0000000 | 0   |   |   |   |     |

| h'2C     |   |   |   | kcoefff |     |   |   |   | R/W |

|          |   |   |   | 0000000 | 0   |   |   |   |     |

| h'2D     |   |   |   | 0000000 | 0   |   |   |   |     |

| h'2E     |   |   |   | kcoeffg |     |   |   |   | R/W |

|          |   |   |   | 0000000 | 0 0 |   |   |   |     |

| h'2F     |   |   |   | 0000000 | 0 0 |   | _ |   |     |

| h'30     |   |   |   | kcoeffh |     |   |   |   | R/W |

|          |   |   |   | 0000000 | 0 0 |   |   |   |     |

| h'31     |   |   |   | 0000000 | 0   |   |   |   |     |

| h'32     |   |   |   | kcoeffi |     |   |   |   | R/W |

|          |   |   |   | 0000000 | 0 0 |   |   |   |     |

| h'33     |   |   |   | 0000000 | 0   |   |   |   |     |

| h'34     |   |   | • | kcoeffj |     | • |   |   | R/W |

|          |   |   |   | 0000000 | 0 0 |   |   |   |     |

| h'35     |   |   |   | 0000000 | 0 0 | _ |   |   |     |

| h'36     |   |   |   | kcoeffk |     |   |   |   | R/W |

| <u> </u> |   |   |   | 0000000 | 0 0 |   |   |   | ĺĺ  |

| h'37     |   |   |   | 0000000 | 0   |   |   |   |     |

#### address h'14

Synchronous Lock Control (synclock)

3 bits

Set the number of sync words required for entering the state where synchronization is established. Default value is 2 (b'010). Set the value only once when M65863FP is in the initial state.

| synclock | Description                                                         |

|----------|---------------------------------------------------------------------|

| 000      | Reserved                                                            |

| 001~111  | Number of sync words which must be detected before mute is canceled |

Output Format (dacform)

3 bits

Specify the output format. Default value is 000 (MSB first right-justified, when LRCK is 1, Lch output). This field can be changed at any time.

| dacform | Description                                                   |

|---------|---------------------------------------------------------------|

| 000     | MSB first right-justified format (when LRCK is 1, Lch output) |

| 0 0 1   | LSB first right-justified format (when LRCK is 1, Lch output) |

| 010     | I2S format (when LRCK is 1, Lch output)                       |

| 011     | Reserved                                                      |

| 100     | MSB first right-justified format (when LRCK is 0, Lch output) |

| 1 0 1   | LSB first right-justified format (when LRCK is 0, Lch output) |

| 110     | I2S format (when LRCK is 0, Lch output)                       |

| 111     | Reserved                                                      |

#### Number of PCM Output Bits (outbitlen)

2 bits

Specify the output bit length. Default value is 00 (16 bits output). This field can be changed at any time.

| outbitlen | Description |

|-----------|-------------|

| 0 0       | 16 bit      |

| 0 1       | 18 bit      |

| 1 0       | 20 bit      |

| 1 1       | 24 bit      |

#### address h'15

#### DSP/DAC Clock Mode (dacclkmode)

1 bit

Specify the LR clock and bit clock to be used in the DAC/DSP interface. When dacclkmode=0, M65863FP becomes the clock master and divides the audio master clock to generate LR clock (LRCK)/bit clock (BCLK). When dacclkmode=1, M65863FP becomes the slave and uses the DIR/ADC input clocks (ALRCK, ACLK) as the LR clock and bit clock, respectively. In the default setting, M65863FP becomes the clock master. Set this value only once when M65863FP is in the initial status.

| dacclkmode | Description  |

|------------|--------------|

| 0          | Clock master |

| 1          | Slave        |

#### Selection of DSP/DAC Interface (dspif)

1 bit

Specify the output interface mode. Default value is 0 (DAC interface). This field can be changed at any time.

| dspif | Description |

|-------|-------------|

| 0     | DAC/IF      |

| 1     | DSP I/F     |

#### DIR/ADC Data Input Format (dirform)

3 bits

Specify the format of data input from DIR/ADC. Default value is 000 (MSB first right-justified, when ALRCK is 1, Lch input). This field can be changed at any time.

| dirform | Description                                                   |

|---------|---------------------------------------------------------------|

| 000     | MSB first right-justified format (when ALRCK is 1, Lch input) |

| 0 0 1   | LSB first right-justified format (when ALRCK is 1, Lch input) |

| 010     | I2S format (when ALRCK is 1, Lch input)                       |

| 011     | Reserved                                                      |

| 100     | MSB first right-justified format (when ALRCK is 0, Lch input) |

| 101     | MSB first right-justified format (when ALRCK is 0, Lch input) |

| 110     | I2S first right-justified format (when ALRCK is 0, Lch input) |

| 111     | Reserved                                                      |

#### De-emphasis Control (dempha)

3 bits

This field controls whether or not to carry out de-emphasis processing during PCM input. If the value is 00 (default), de-emphasis processing is not carried out. If the value is 01, de-emphasis processing is carried out. Value 10 enables control at the level of external input terminal DEMPHA. Value 0 turns de-emphasis off, and value 1 turns de-emphasis on. This field can be changed at any time.

| dempha | Description                                   |

|--------|-----------------------------------------------|

| 0 0    | De-emphasis always off                        |

| 0 1    | De-emphasis always on                         |

| 1 0    | Control with external input terminal (dempha) |

| 1 1    | Reserved                                      |

#### address h'16

#### Noise Selection (noisesel)

1 bit

Select the kind of noise. Default value is 0 (pink noise). Setting of the value in this field should be done under the state of noise off for every channel.

| noisesel | Description  |

|----------|--------------|

| 0        | Pink noise   |

| 1        | Shaped noise |

#### SW-ch Noise (swnoise)

<u>1 bit</u>

Control of noise generation for SW channel. When set to noise on, M65863FP enters noise output mode while ignoring the audio input from DIR/ADC and DEMUX. Noise generation can be turned on/off at any time. Default setting is noise off.

| swnoise | Description |

|---------|-------------|

| 0       | Noise off   |

| 1       | Noise on    |

#### SL-ch Noise (slnoise)

<u>1 bit</u>

Control of noise generation for SL channel. When set to noise on, M65863FP enters noise output mode while ignoring the audio input from DIR/ADC and DEMUX. Noise generation can be turned on/off at any time. Default setting is noise off.

| slnoise | Description |

|---------|-------------|

| 0       | Noise off   |

| 1       | Noise on    |

#### SR-ch Noise (srnoise)

1 bit

Control of noise generation for SR channel. When set to noise on, M65863FP enters noise output mode while ignoring the audio input from DIR/ADC and DEMUX. Noise generation can be turned on/off at any time. Default setting is noise off.

| srnoise | Description |

|---------|-------------|

| 0       | Noise off   |

| 1       | Noise on    |

#### R-ch Noise (srnoise)

1 bit

Control of noise generation for R channel. When set to noise on, M65863FP enters noise output mode while ignoring the audio input from DIR/ADC and DEMUX. Noise generation can be turned on/off at any time. Default setting is noise off.

| srnoise | Description |

|---------|-------------|

| 0       | Noise off   |

| 1       | Noise on    |

#### C-ch Noise (srnoise)

1 bit

Control of noise generation for C channel. When set to noise on, M65863FP enters noise output mode while ignoring the audio input from DIR/ADC and DEMUX. Noise generation can be turned on/off at any time. Default setting is noise off.

| Cnoise | Description |

|--------|-------------|

| 0      | Noise off   |

| 1      | Noise on    |

#### L-ch Noise (Inoise)

1 bit

Control of noise generation for L channel. When set to noise on, M65863FP enters noise output mode while ignoring the audio input from DIR/ADC and DEMUX. Noise generation can be turned on or off at any time. Default setting is noise off.

| srnoise | Description |

|---------|-------------|

| 0       | Noise off   |

| 1       | Noise on    |

#### address h'17

Data input Port Selection Control(inportsel)

2 bits

Select the audio input port of M65863FP in this field. In the default setting, data stream from DIR/ADC1 is received. This field can be changed at any time.

| inportsel | Description                                         |  |

|-----------|-----------------------------------------------------|--|

| 0 0       | M65863FP receives audio stream from DIR/ADC input 1 |  |

| 0 1       | M65863FP receives audio stream from DIR/ADC input 2 |  |

| 1 0       | M65863FP receives audio stream from DEMUX           |  |

| 1 1       | Reserved                                            |  |

#### Selection of Sampling Frequency for Pro Logic,

De-emphasis and Noise Generator (pfsmode)

2 bits

Select the sampling frequency for Pro Logic, de-emphasis processing for linear PCM and noise generation, in this field. This field must be correctly set in the case of Pro Logic decoding, de-emphasis processing for linear PCM and noise generation, because the filtering factor is determined according to this information. Default setting is 00 (48 kHz).

| pfsmode | Description |

|---------|-------------|

| 0 0     | 48 kHz      |

| 0 1     | 44.1 kHz    |

| 1 0     | 32 kHz      |

| 1 1     | Reserved    |

Pro Logic Decoding Mode Selection (pdecmode)

2 bits

Controls on/off of Pro Logic decoding. Default setting is off. This field can be changed at any time.

| pdecmode | Description                                                  |

|----------|--------------------------------------------------------------|

| 0 0      | No decoding                                                  |

| 0 1      | Full-time decoding                                           |

| 1 0      | Decoding done if dsurmod-specified Dolby surround is encoded |

| 1 1      | Reserved                                                     |

Number of DIR/ADC Input Bits (inbitlen)

2 bits

Specify the bit length of DIR/ADC input. Default value is 16 bit. This field can be changed at any time.

| inbitlen | Description |

|----------|-------------|

| 0 0      | 16 bit      |

| 0 1      | 18 bit      |

| 1 0      | 20 bit      |

| 1 1      | 24 bit      |

#### address h'18

Auto-balance On/Off (autobal)

1 bit

Selected only during Pro Logic decoding mode.

| autobal | Description      |

|---------|------------------|

| 0       | Auto-balance ON  |

| 1       | Auto-balance OFF |

Narrow/wide Selection (narwid)

1 bit

Selected only during Pro Logic decoding mode.

| narwid | Description |

|--------|-------------|

| 0      | Wide mode   |

| 1      | Narrow mode |

#### address h'19

Dynamic Range Compression Mode Control (compmod)

2 bits

Specify the mode of dynamic range compression and dialog normalization on/off during Dolby Digital (AC-3) decoding. Default value is 00 (line-out mode). While this field can be changed at any time, set value is reflected in synchronization with the frame during Dolby Digital (AC-3) decoding.

| compmod | Description   |

|---------|---------------|

| 0 0     | Line-out mode |

| 0 1     | RF mode       |

| 1 0     | Custom mode B |

| 1 1     | Custom mode A |

Line-out mode is useful for products which generate line-out signals of base band. Details are as follows.

- · Dialog normalization is always effective.

- Dynamic compression (dynmg) is used.

- Low-level boost compression scaling is enabled.

- High-level cut compression scaling is enabled when there is no down-mixing.

- Play-back with constant level of dialog (-31dB FS).

RF mode is useful for products which generate down-mixing signal for RF modulation. Details are as follows.

Dialog normalization is always effective.

- · Heavy compression (dynmg and compr) is used.

- · Compression scaling is disabled.

- +11dB gain shift is provided.

- Play-back with constant level of dialog (-20dB FS).

Custom mode B makes finer level adjustment possible. Details are as follows.

- Dialog normalization is effective.

- Dynamic compression (dynmg) is used.

- Compression scaling is enabled.

- Dialog is played back with constant level (-31dB FS). (In the case of no down mixing.)

- Provided with -11dB gain shift when down mixing is applied up to over-loading of peak level.

Dialog normalization is not carried out in custom mode A. Details are as follows.

- Dialog normalization is not effective.

- Dynamic compression (dynmg) is used.

- · Compression scaling is enabled.

- Provided with -11dB gain shift when down mixing is applied up to over-loading of peak level.

#### Main Stereo Control (stereo)

2 bits

When acmod indicates dual monaural mode, user uses these 2 bits to select the desired audio output from the following options. Default value is 00. While this field can be changed at any time, set value is reflected in synchronization with the frame during Dolby Digital (AC-3) decoding.

| stereo | Type of Dual Monaural Output Mode |

|--------|-----------------------------------|

| 0 0    | Lch:ch1, Rch:ch2                  |

| 0 1    | Lch:ch1, Rch:ch1                  |

| 1 0    | Lch:ch2, Rch:ch2                  |

| 1 1    | Lch:ch1+ch2, Rch:ch1+ch2          |

#### Output Channel Mode Control (outchmod)

3 bits

Specify the output channel mode. Default value is b'111 (3/2 mode). While this field can be changed at any time, set value is reflected in synchronization with the audio block during Dolby Digital (AC-3) decoding.

| outchmod | Output Channel Mode           | Output Channel |

|----------|-------------------------------|----------------|

| 000      | Dolby Pro Logic encode stereo | [Lt,Rt]        |

| 0 0 1    | 1/0                           | [C]            |

| 010      | 2/0                           | [L,R]          |

| 011      | 3/0                           | [L,C,R]        |

| 100      | 2/1                           | [L,R,S]        |

| 101      | 3/1                           | [L,C,R,S]      |

| 110      | 2/2                           | [L,R,SL,SR]    |

| 111      | 3/2                           | [L,C,R,SL,SR]  |

#### Associate Service Decoding Mode Control (asmix)

1 bit

When this bit is set to 1, compression gain word and dynamic range gain word are transferred from the sub chip to the main chip via the main/sub chip interface, thus enabling it to decode dual streams. Default value is 0 (single stream mode). Set the value in this field only once when M65863FP is in the initial status.

| asmix | Description                 |

|-------|-----------------------------|

| 0     | Single stream decoding mode |

| 1     | Dual stream mixing mode     |

#### address h'1A

syncrst Enable (syncrsten)

2 bits

Specify the method of synchronization control which uses SYNCRST terminal in the case of DEMUX interface. Default setting is 00 (synchronization control by using SYNCRST terminal is not carried out). Although control by using SYNCRST is carried out when the value is 01 or 10, the operation differs as to whether input stream is transferred to the input buffer or not when SYNCRST is asserted. Refer to section 5.1.2 for details. Set this value only once when M65863FP is in the initial status.

| syncrsten | Description                                                               |

|-----------|---------------------------------------------------------------------------|

| 0 0       | Synchronization control by using SYNCRST terminal is not carried out      |

| 0 1       | Synchronization control by using SYNCRST terminal is carried out (mode A) |

| 1 0       | Synchronization control by using SYNCRST terminal is carried out (mode B) |

| 1 1       | Reserved                                                                  |

#### dir input Data mode Enable (dirdatamode)

2 bits

Specify whether or not to make judgment to determine the input data is AC-3 or PCM in the case of DIR/ADC interface. When the value is 00, AC-3/PCM is automatically determined according to the sync preamble, and decoding mode of M65863FP is automatically switched. When the value is 01, the mode is fixed to AC-3 input. When PCM is input in this case, synchronization is lost and the output is muted. When the value is 10 or 11, the mode is fixed to PCM input, except that value 10 causes sync preamble to be searched and, when sync preamble is detected, causes the output to be muted. When the value is 11, sync preamble is not searched. Therefore, mistaken input of AC-3 stream results in its output as it is. Default value is 00 (automatic judgment of AC-3/PCM). This field can be set at any time.

| dirdatamode | Description                                                              |

|-------------|--------------------------------------------------------------------------|

| 0 0         | Automatic judgment of AC-3/PCM based on sync preamble                    |

| 0 1         | Fixed to AC-3 input                                                      |

| 1 0         | Fixed to PCM input (sync preamble detection & mute control provided)     |

| 1 1         | Fixed to PCM input (sync preamble detection & mute control not provided) |

#### address h'1B

<u>Dynamic Range Compression Scale Factor for High Level Signal (hcompsc)</u> 8 bits

This field determines the scale of dynamic range control word for high level signal. Available range is from h'00 to h'7F in binary number. Value h'7F corresponds to 1.0. Default value is h'7F (1.0). While this field can be changed at any time, set value is reflected in synchronization with the audio block during Dolby Digital (AC-3) decoding.

#### address h'1C

<u>Dynamic Range Compression Scale Factor for Low Level Signal (Icompsc)</u> 8 bits

This field determines the scale of dynamic range control word for low level signal. Available range is from h'00 to h'7F in binary number. Value h'7F corresponds to 1.0. Default value is h'7F (1.0). While this field can be changed at any time, set value is reflected in synchronization with the audio block during Dolby Digital (AC-3) decoding.

#### address h'1D

#### Karaoke Player Mode (karaply)

1 bit

This field indicates whether the player has karaoke function or not. Value 0 indicates karaoke aware mode and 1 indicates karaoke capable mode. Default value is 0 (karaoke aware mode). While this field can be changed at any time, set value is reflected in synchronization with the audio block during Dolby Digital (AC-3) decoding.

#### Karaoke Capable Mixing Coefficient Mode (kcapmod)

1 bit

This field indicates whether the default coefficient value is to be used or not. This flag is valid only in the karaoke capable mode (when control register karaply = 1). When this flag is 0, M65863FP uses the default coefficient value. When it is 1, value of control register (address IE-33) is used in karaoke mixing. Default value is 0. While this field can be changed at any time, set value is reflected in synchronization with the audio block during Dolby Digital (AC-3) decoding.

#### Karaoke Capable Default Vocal (kcapdef)

2 bits

This field indicates the vocal reproduction when the default coefficient value is used in karaoke capable mode. Default value is 00. While this field can be changed at any time, set value is reflected in synchronization with the audio block during Dolby Digital (AC-3) decoding.

| kcapdef | Vocal Reproduction |

|---------|--------------------|

| 0 0     | No vocal           |

| 0 1     | V1 vocal           |

| 1 0     | V2 vocal           |

| 1 1     | Both vocal         |

### address h'1E address h'1F

#### Dialogue Normalization Control (dialevel)

16 bits

This field indicates dialogue normalization control value. h'7FFF is 1.0. Default value is h'7FFF(1.0). While this field can be changed at any time, set value is reflected at the beginning of a new audio block.

#### address h'20

Output Attenuator (attlevel)

1 bit

This field controls output data gain. Default value is 0 (0dB). While this field can be changed at any time, set value is reflected at the beginning of a new audio block.

| attlevel | Attenuate Level |

|----------|-----------------|

| 0        | 0 dB            |

| 1        | -12 dB          |

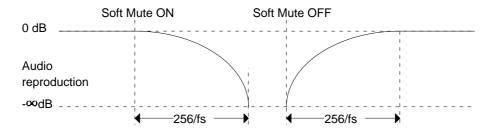

Soft Mute Control (muteonoff)

1 bit

This field controls soft muting. M65863FP starts to mute output when the field is changed to 1 and finishes muting when the field is changed to 0. Default value is 1 (mute on). While this field can be changed at any time, set value is reflected at the beginning at a new audio block.

| muteonoff | muteonoff Description |  |

|-----------|-----------------------|--|

| 0         | Mute OFF              |  |

| 1         | Mute ON               |  |

#### **DEMUX I/F Protocol Control (burstcont)**

1 bit

This field is valid. when using DEMUX I/F (inportsel=10) and specifies a interface protocol. When the field is '1', M65863FP inputs Dolby Digital (AC-3) stream for exactly 1 frame at a time. When the field is '0', M65863FP inputs Dolby Digital (AC-3) stream until the input buffer is full. Default value is '0'. Set the value in the field only once when M65863FP is in the initial state.

#### Copy Right Bit (copyrightb)

1 bit

The value in this filed is written in the "copyrightb" field in IEC958 when using DEMUX I/F.

#### IEC958 Data Stream Number Selection (istrnums)

3 bits

M65863FP decodes the data stream whose number is same as this field. Default value is b'000. Set value in the field is reflected at the beginning at a new audio frame.

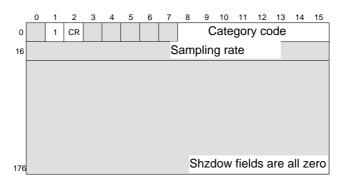

#### address h'21

#### Category Code (catecode)

8 bits

Value specified in this field is written in the category code field of the channel status word of IEC958 output. Default value is h'00. This field can be set at any time.

#### address h'22

#### address h'23

#### Karaoke Mixing Coefficient (kcoeffa)

16 bits

Coefficient for mixing V1 with Lk. Value h'7FFF corresponds to 1.0. Default value is h'0000 (0.0). While this field can be changed at any time, set value is reflected in synchronization with the audio block during Dolby Digital (AC-3) decoding.

#### address h'24

#### address h'25

#### Karaoke Mixing Coefficient (kcoeffb)

16 bits

Coefficient for mixing V2 with Lk. Value h'7FFF corresponds to 1.0. Default value is h'0000 (0.0). While this field can be changed at any time, set value is reflected in synchronization with the audio block during Dolby Digital (AC-3) decoding.

#### address h'26

#### address h'27

#### Karaoke Mixing Coefficient (kcoeffc)

<u>16 bits</u>

Coefficient for mixing M with Lk. Value h'7FFF corresponds to 1.0. Default value is h'0000 (0.0). While this field can be changed at any time, set value is reflected in synchronization with the audio block during Dolby Digital (AC-3) decoding.

#### address h'28

#### address h'29

#### Karaoke Mixing Coefficient (kcoeffd)

16 bits

Coefficient for mixing V1 with Ck. Value h'7FFF corresponds to 1.0. Default value is h'0000 (0.0). While

April 1998 Dolby Digital Decoder

this field can be changed at any time, set value is reflected in synchronization with the audio block during Dolby Digital (AC-3) decoding.

#### address h'2A

#### address h'2B

Karaoke Mixing Coefficient (kcoeffe)

16 bits

Coefficient for mixing V2 with Ck. Value h'7FFF corresponds to 1.0. Default value is h'0000 (0.0). While this field can be changed at any time, set value is reflected in synchronization with the audio block during Dolby Digital (AC-3) decoding.

#### address h'2C

#### address h'2D

Karaoke Mixing Coefficient (kcoefff)

16 bits

Coefficient for mixing M with Ck. Value h'7FFF corresponds to 1.0. Default value is h'0000 (0.0). While this field can be changed at any time, set value is reflected in synchronization with the audio block during Dolby Digital (AC-3) decoding.

#### address h'2E

#### address h'2F

Karaoke Mixing Coefficient (kcoeffg)

16 bits

Coefficient for mixing V1 with Rk. Value h'7FFF corresponds to 1.0. Default value is h'0000 (0.0). While this field can be changed at any time, set value is reflected in synchronization with the audio block during Dolby Digital (AC-3) decoding.

#### address h'30

#### address h'31

Karaoke Mixing Coefficient (kcoeffh)

16 bits

Coefficient for mixing V2 with Rk. Value h'7FFF corresponds to 1.0. Default value is h'0000 (0.0). While this field can be changed at any time, set value is reflected in synchronization with the audio block during Dolby Digital (AC-3) decoding.

#### address h'32

#### address h'33

Karaoke Mixing Coefficient (kcoeffi)

16 bits

Coefficient for mixing M with Rk. Value h'7FFF corresponds to 1.0. Default value is h'0000 (0.0). While this field can be changed at any time, set value is reflected in synchronization with the audio block during Dolby Digital (AC-3) decoding.

#### address h'34

#### address h'35

Karaoke Mixing Coefficient (kcoeffj)

16 bits

Coefficient for mixing L with Lk. Value h'7FFF corresponds to 1.0. Default value is h'0000 (0.0). While this field can be changed at any time, set value is reflected in synchronization with the audio block during Dolby Digital (AC-3) decoding.

#### address h'36

#### address h'37

Karaoke Mixing Coefficient (kcoeffk)

16 bits

Coefficient for mixing R with Rk. Value h'7FFF corresponds to 1.0. Default value is h'0000 (0.0). While this field can be changed at any time, set value is reflected in synchronization with the audio block during Dolby Digital (AC-3) decoding.

<u>1 bit</u>

<u>1 bit</u>

<u>1 bit</u>

<u>1 bit</u>

### 4.5 Test Registers

The default values are described in the bit fields shown in table 4.6.

Table 4.6 Test Registers

| bit     |   |   |   | • |        | •      |         | •       |     |

|---------|---|---|---|---|--------|--------|---------|---------|-----|

| Address | 0 | 1 | 2 | 3 | 4      | 5      | 6       | 7       | R/W |

| h'38    |   |   |   |   | inputh | inputl | outputh | outpuyl | R   |

|         | 0 | 0 | 0 | 0 | 0      | 0      | 0       | 0       |     |

#### address h'38

Output Buffer Underflow Status(outputl)

This bit is to indicate output buffer underflow.

| outputl | Description   |  |

|---------|---------------|--|

| 0       | Not underflow |  |

| 1       | Underflow     |  |

Output Buffer Overflow Status (outputh)

This bit is to indicate output buffer overflow.

| outputh | Description  |  |  |  |

|---------|--------------|--|--|--|

| 0       | Not overflow |  |  |  |

| 1       | Overflow     |  |  |  |

Input Buffer Underflow Status (inputl)

This bit is to indicate input buffer underflow.

| inputl | Description   |

|--------|---------------|

| 0      | Not underflow |

| 1      | Underflow     |

Input Buffer Overflow Status (inputh)

This bit is to indicate input buffer overflow.

| inputh | Description  |

|--------|--------------|

| 0      | Not overflow |

| 1      | Overflow     |

# Chapter 5 Interface

### 5.1 Audio Input Interface

#### 5.1.1 DIR/ADC Interface

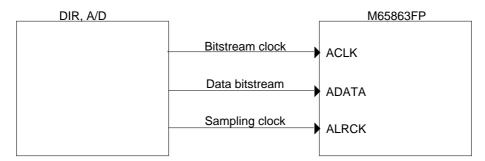

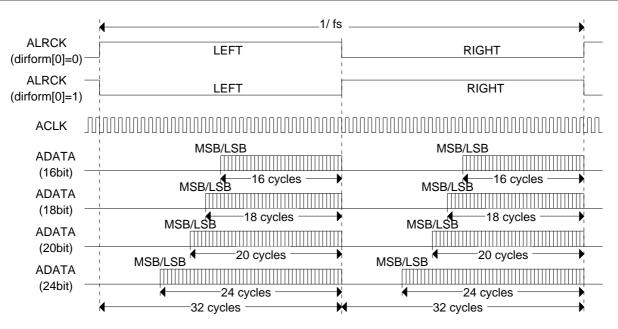

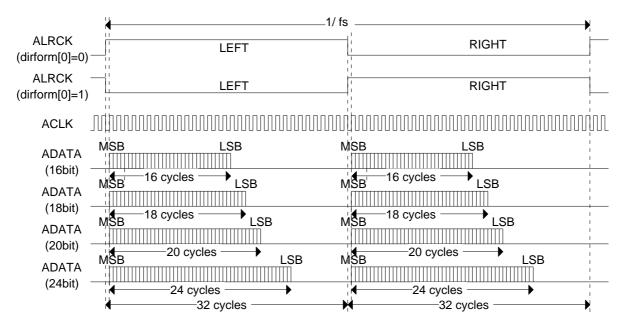

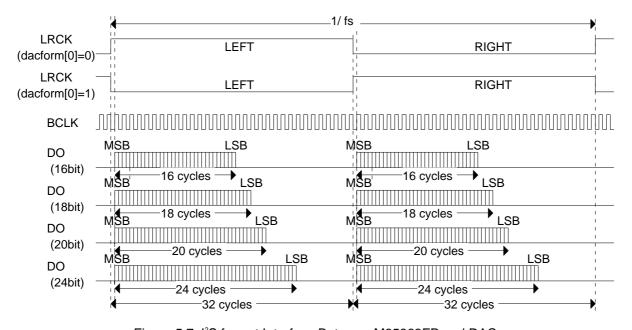

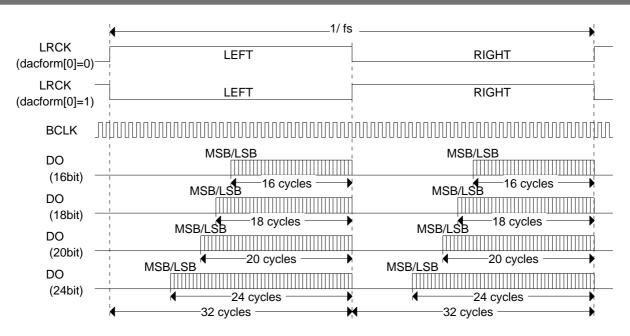

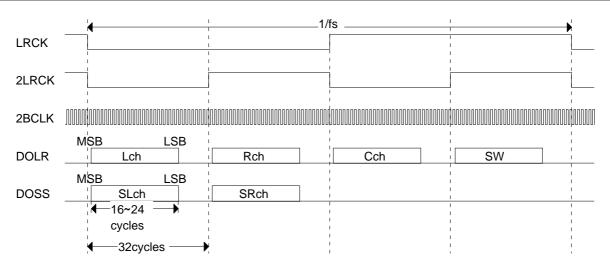

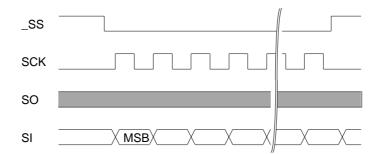

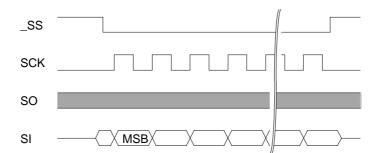

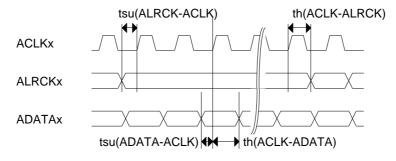

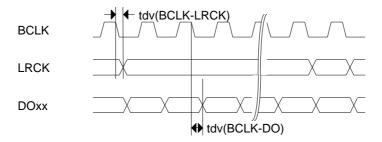

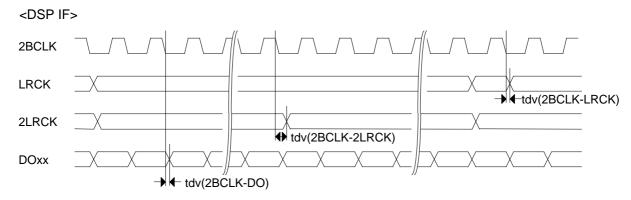

The interface between M65863FP and Digital Audio I/F Receiver or A/D converter consists of the signals ACLK, ADATA, ALRCK as follows (see figure 5.1). M65863FP supports 3 kinds of input formats(MSB first right-justified, LSB first right-justified and I<sup>2</sup>S) and 4 word sizes(16, 18, 20 and 24bit).

Figure 5.1 Connections Between DIR and M65863FP

The input format can be chosen among MSB first right-justified format , LSB first right-justified format and I<sup>2</sup>S format with the control register 'dirformt' (address h'15). Also, the word size can be chosen among 16, 18, 20 and 24bit with the control register 'inbitlen' (address h'17). The relationship between the signal level of ALRCK and output channel (L/R, C/SW, SL/SR) is selective. The details are shown in figure 5.2 and figure 5.3.

When M65863FP accepts Dolby Digital (AC-3) data from Digital Audio I/F Receiver, 16 bit mode must be selected.

Figure 5.2 MSB/LSB right-justified Format (16bit, 18bit, 20bit, 24bit)

Figure 5.3 I<sup>2</sup>S Format (16bit, 18bit, 20bit, 24bit)

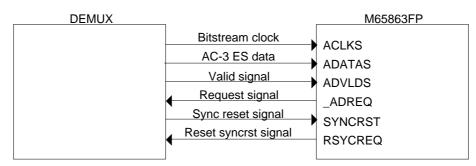

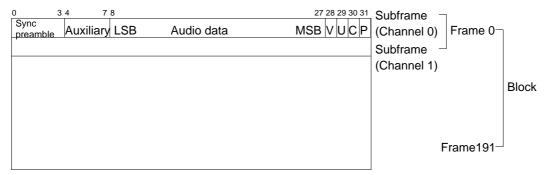

#### 5.1.2 Serial Dolby Digital (AC-3) Stream Interface

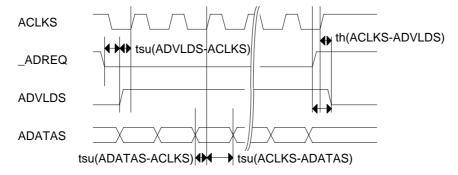

The interface between MPEG2 system decoder (DEMUX) that outputs Dolby Digital (AC-3) elementary stream and M65863FP consists of the signals ACLKS, ADATAS, ADVLDS, \_ADREQ, SYNCRST and RSYNCREQ as follows (see figure 5.4).

Figure 5.4 Connections Between DEMUX and M65863FP

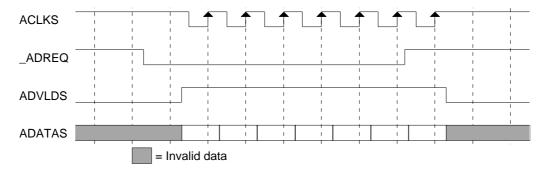

When M65863F accepts AC-3 data from MPEG2 System decoder (DEMUX), the protocol is shown in figure 5.5.

Figure 5.5 Interface Between DEMUX and M65863FP

If burstcont is a 0, \_ADREQ will be high when the input buffer becomes full. If burstcont is a 1, \_ADREQ will be high when M65863FP relieves 1 sync frame. The burstcont returns to low when M65863FP outputs the first PCM of the frame.

#### 5.1.3 Sync Word Detection Start Signal

If SYNCRST is asserted when receiving DEMUX input (control register inportsel is 10) and the control register syncrsten is either 01 or 10, M65863FP returns to the state of being out of synchronization. Operation when SYNCRST is asserted varies depending on the value of control register syncrsten.

When syncrsten = 01 (mode A)

While SYNCRST is asserted, detection of sync word is not carried out with out-of-sync status persisting, and AC-3 stream is not stored in the input buffer. When SYNCRST is negated, M65863FP begins detection of sync word and, when sync word is detected, transfers the AC-3 stream to the input buffer and restarts decoding.

When syncrsten =  $10 \pmod{B}$

When SYNCRST is asserted, M65863FP enters out-of-sync status and, at the same time, begins detection of sync word and, when sync word is detected, transfers the AC-3 stream to the input buffer. In

the period when SYNCRST is asserted, however, decoding is not done. Decoding is started when SYNCRST is negated. At this time, M65863FP restarts decoding at the nearest frame behind the address indicated by Read Pointer of the input buffer. Therefore, any desired frame which is input during assertion period and the subsequent data can be played back, by writing over the Read Pointer during assertion period. In the period when SYNCRST is asserted, M65863FP processes AC-3 stream input and overwrites the contents of the buffer even if the input buffer overflows.

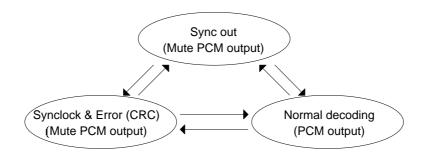

#### 5.1.4 Out-of-sync Signal

When M65863FP fails to detect sync word twice successively, M65863FP is determined to be out of synchronization. M65863FP sets the RSYCREQ pin and "synccon" (status register) to 1 and mutes the output. "synccon" remains to be 1 until M65863FP is locked in synchronization. RSYCREQ changes to 0 when M65863FP detects sync word next time.

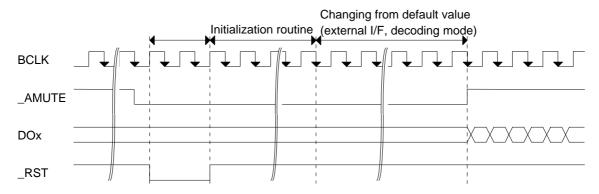

#### 5.1.5 Mute Signal

M65863FP mutes the output signal when \_AMUTE becomes 0. \_AMUTE can be asserted or negated asynchronously. However, M65863FP starts/ends muting in the next synchronization frame when assert/negate signal is received.

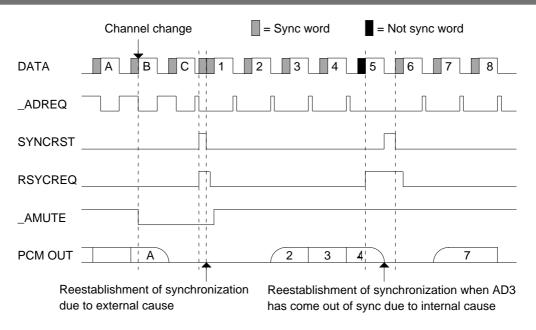

#### 5.1.6 Reestablishment of Synchronization

In case an external cause such as channel change takes place during DEMUX input (control register inportsel is 10), M65863FP can reestablish synchronization by using the external terminal SYNCRST as follows. As mentioned in 5.1.3, operation varies depending on whether the control register syncrsten is 01 or 10.

In the case of mode A (control register syncrsten is 01)

- 1) SYNCRST is asserted.

- 2) When M65863FP detects rising edge of SYNCRST, M65863FP comes out of synchronization and asserts RSYCREQ. In the case of mode A, M65863FP does not detect sync word and remains out of synchronization while SYNCRST is enabled. When M65863FP is out of synchronization, input stream is not stored in the input buffer.

- 3) When M65863FP detects rising edge of SYNCRST, it starts detection of sync word.

- 4) When M65863FP detects sync word, it stores input stream in the input buffer and starts decoding. RSYCREQ is negated at this time.

When an internal cause necessitates it to establish synchronization again, M65863FP requests DEMUX to assert SYNCRST by asserting RSYCREQ (Second SYNCRST and RSYCREQ in Figure 5.6).

Figure 5.6 Timing of Interface Between DEMUX and M65863FP

In the case of mode B (control register syncrsten is 10)

- 1) SYNCRST is asserted.

- 2) When M65863FP detects rising edge of SYNCRST, M65863FP comes out of synchronization and asserts RSYCREQ. In the case of mode B, M65863FP inputs Dolby Digital (AC-3) stream and searches for sync word even when SYNCRST is enabled.

- 3) When M65863FP detects sync word, it negates RSYCREQ and stores Dolby Digital (AC-3) stream in the internal input buffer. It should be noted, however, that decoding is not restarted under this condition.

- 4) When M65863FP detects the falling edge of SYNCRST, it restarts decoding at the nearest audio frame behind the address indicated by Readpointer.

In mode B, decoding can be restarted at any desired audio frame which is input after assertion of SYNCRST, by writing over the Readpointer for the input buffer during the period of asserting SYNCRST (It is limited to the frame following the detection of sync word and restart of transfer to the input buffer.).

When an internal cause necessitates it to establish synchronization again, M65863FP requests DEMUX to assert SYNCRST by asserting RSYCREQ.

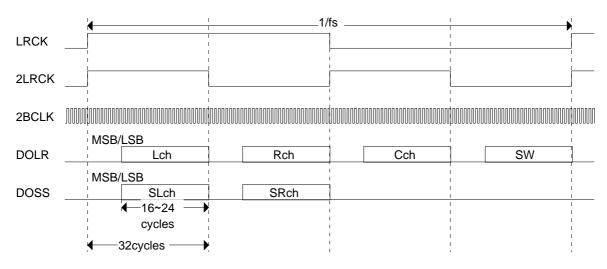

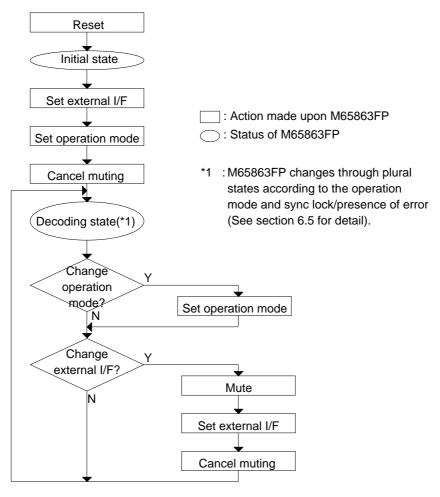

#### 5.2 Audio Output Interface