RTL8139D RTL8139DL RTL8139D-LF RTL8139DL-LF RTL8139D-GR RTL8139DL-GR

### SINGLE-CHIP MULTI-FUNCTION 10/100Mbps ETHERNET CONTROLLER WITH POWER MANAGEMENT

#### **DATASHEET**

Rev. 1.2

08 Aug 2005

**Track ID: JATR-1076-21**

#### Realtek Semiconductor Corp.

No. 2, Industry E. Rd. IX, Science-Based Industrial Park, Hsinchu 300, Taiwan Tel: +886-3-5780211 Fax: +886-3-5776047 www.realtek.com.tw

#### **COPYRIGHT**

©2005 Realtek Semiconductor Corp. All rights reserved. No part of this document may be reproduced, transmitted, transcribed, stored in a retrieval system, or translated into any language in any form or by any means without the written permission of Realtek Semiconductor Corp.

#### **DISCLAIMER**

Realtek provides this document "as is", without warranty of any kind, neither expressed nor implied, including, but not limited to, the particular purpose. Realtek may make improvements and/or changes in this document or in the product described in this document at any time. This document could include technical inaccuracies or typographical errors.

#### **TRADEMARKS**

Realtek is a trademark of Realtek Semiconductor Corporation. Other names mentioned in this document are trademarks/registered trademarks of their respective owners.

#### **USING THIS DOCUMENT**

Though every effort has been made to ensure that this document is current and accurate, more information may have become available subsequent to the production of this guide. In that event, please contact your Realtek representative for additional information that may help in the development process.

#### **REVISION HISTORY**

| Revision | Release Date | Summary                                                                                   |

|----------|--------------|-------------------------------------------------------------------------------------------|

| 1.2      | 2005/08/08   | Added section 13 Ordering Information, on page 61.                                        |

|          |              | Added lead (Pb)-free and version package identification information on page 2 and page 3. |

### **Table of Contents**

| 1. GEN | GENERAL DESCRIPTION1                               |    |  |  |  |  |

|--------|----------------------------------------------------|----|--|--|--|--|

| 2. FEA | TURES                                              | 2  |  |  |  |  |

| 3. PIN | ASSIGNMENTS                                        | 2  |  |  |  |  |

| 3.1.   | PACKAGE IDENTIFICATION                             | 2  |  |  |  |  |

| 3.2.   | PACKAGE IDENTIFICATION                             | 3  |  |  |  |  |

| 4. PIN | DESCRIPTIONS                                       | 4  |  |  |  |  |

| 4.1.   | POWER MANAGEMENT/ISOLATION INTERFACE               | 4  |  |  |  |  |

| 4.2.   | PCI Interface                                      | 4  |  |  |  |  |

| 4.3.   | EEPROM INTERFACE                                   | 6  |  |  |  |  |

| 4.4.   | POWER PINS                                         | 6  |  |  |  |  |

| 4.5.   | LED Interface                                      |    |  |  |  |  |

| 4.6.   | ATTACHMENT UNIT INTERFACE                          | 7  |  |  |  |  |

| 4.7.   | MULTI-FUNCTION INTERFACE                           | 7  |  |  |  |  |

| 4.8.   | TEST AND OTHER PINS                                | 7  |  |  |  |  |

| 5. REC | GISTER DESCRIPTIONS                                | 8  |  |  |  |  |

| 5.1.   | RECEIVE STATUS REGISTER IN RX PACKET HEADER        | 10 |  |  |  |  |

| 5.2.   | Transmit Status Register                           |    |  |  |  |  |

| 5.3.   | ERSR: EARLY RX STATUS REGISTER                     |    |  |  |  |  |

| 5.4.   | COMMAND REGISTER                                   |    |  |  |  |  |

| 5.5.   | Interrupt Mask Register                            |    |  |  |  |  |

| 5.6.   | Interrupt Status Register                          | 13 |  |  |  |  |

| 5.7.   | Transmit Configuration Register                    | 14 |  |  |  |  |

| 5.8.   | RECEIVE CONFIGURATION REGISTER                     | 15 |  |  |  |  |

| 5.9.   | 9346CR: 93C46 COMMAND REGISTER                     | 18 |  |  |  |  |

| 5.10.  | CONFIG 0: Configuration Register 0                 | 19 |  |  |  |  |

| 5.11.  | CONFIG 1: Configuration Register 1                 | 20 |  |  |  |  |

| 5.12.  | Media Status Register                              | 21 |  |  |  |  |

| 5.13.  | CONFIG 3: CONFIGURATION REGISTER3                  | 22 |  |  |  |  |

| 5.14.  | CONFIG 4: Configuration Register4                  | 23 |  |  |  |  |

| 5.15.  | MULTIPLE INTERRUPT SELECT REGISTER                 | 24 |  |  |  |  |

| 5.16.  | PCI REVISION ID                                    | 24 |  |  |  |  |

| 5.17.  | TRANSMIT STATUS OF ALL DESCRIPTORS (TSAD) REGISTER | 24 |  |  |  |  |

| 5.18.  | BASIC MODE CONTROL REGISTER                        |    |  |  |  |  |

| 5.19.  | BASIC MODE STATUS REGISTER                         | 26 |  |  |  |  |

| 5.20.  | AUTO-NEGOTIATION ADVERTISEMENT REGISTER            | 26 |  |  |  |  |

| 5.21.  | AUTO-NEGOTIATION LINK PARTNER ABILITY REGISTER     | 27 |  |  |  |  |

| 5.22.  | AUTO-NEGOTIATION EXPANSION REGISTER                | 28 |  |  |  |  |

| 5.23.  | DISCONNECT COUNTER                                 | 28 |  |  |  |  |

iii

| 29 29 30 31 33 33 34 34 40 41                |

|----------------------------------------------|

| 30<br>31<br>33<br>33<br>34<br>36<br>40<br>41 |

| 31<br>33<br>33<br>34<br>34<br>36<br>40       |

| 33<br>33<br>34<br>34<br>36<br>40             |

|                                              |

|                                              |

|                                              |

| 36<br>40                                     |

| 36<br>40                                     |

| 40<br>41                                     |

| 41                                           |

|                                              |

|                                              |

| TV                                           |

| 46                                           |

| 46                                           |

| 46                                           |

| 46                                           |

| 46                                           |

| 47                                           |

| 47                                           |

| 47                                           |

| 47                                           |

| 48                                           |

| 48                                           |

| 48                                           |

| 48                                           |

| 49                                           |

| 49<br>49                                     |

| 50                                           |

| 50                                           |

| 51                                           |

| 31                                           |

| 52                                           |

| 52                                           |

| 52                                           |

| 52                                           |

| 52                                           |

| 53                                           |

| 53                                           |

|                                              |

iv

|                   | 59                |

|-------------------|-------------------|

|                   | 59                |

|                   | 60                |

| ERING INFORMATION | 61                |

| •                 | ERING INFORMATION |

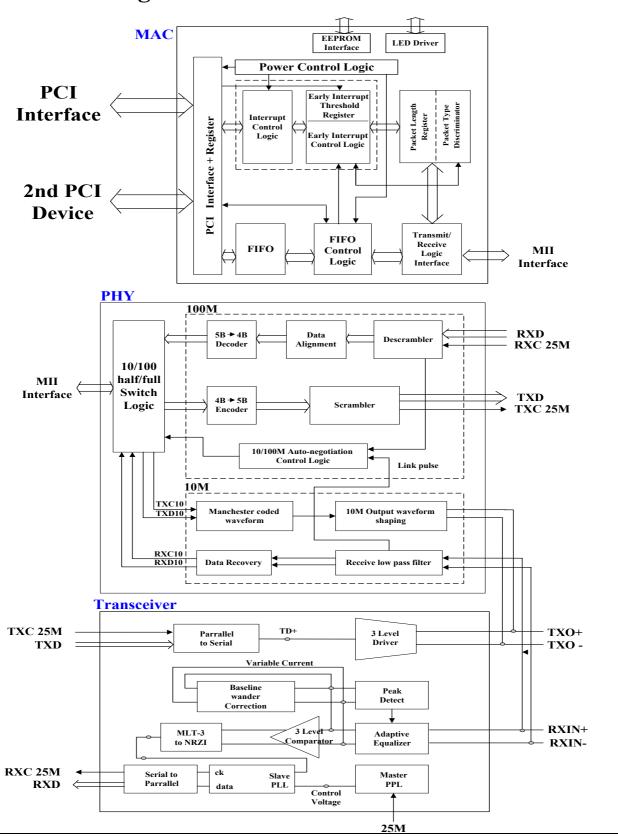

#### 1. General Description

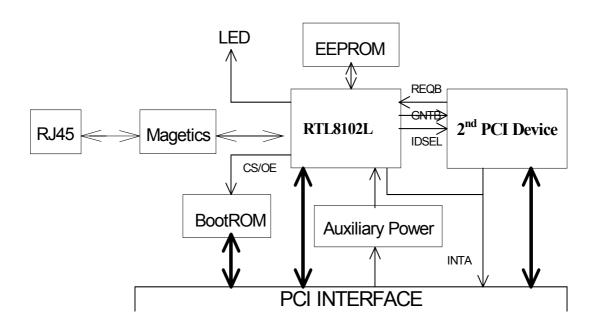

The Realtek RTL8139D(L) is a highly integrated and cost-effective single-chip Fast Ethernet controller that provides 32-bit performance, PCI bus master capability, and full compliance with IEEE 802.3u 100Base-T specifications and IEEE 802.3x Full Duplex Flow Control. It also supports Advanced Configuration Power management Interface (ACPI), PCI power management for modern operating systems that are capable of Operating System Directed Power Management (OSPM) to achieve the most efficient power management possible. The RTL8139D(L) also supports shared Boot ROM pins & clock run pin.

In addition to the ACPI feature, the RTL8139D(L) also supports remote wake-up (including AMD Magic Packet, LinkChg, and Microsoft® wake-up frame) in both ACPI and APM environments. The RTL8139D(L) is capable of performing an internal reset through the application of auxiliary power. When auxiliary power is applied and the main power remains off, the RTL8139D(L) is ready and is waiting for the Magic Packet or Link Change to wake the system up. Also, the LWAKE pin provides 4 different output signals including active high, active low, positive pulse, and negative pulse. The versatility of the RTL8139D(L) LWAKE pin provides motherboards with Wake-On-LAN (WOL) functionality.

The RTL8139D(L) also supports Analog Auto-Power-down, that is, the analog part of the RTL8139D(L) can be shut down temporarily according to user requirement or when the RTL8139D(L) is in a power down state with the wakeup function disabled. In addition, when the analog part is shut down and the IsolateB pin is low (i.e. the main power is off), then both the analog and digital parts stop functioning and the power consumption of the RTL8139D(L) will be negligible. The RTL8139D(L) also supports an auxiliary power auto-detect function, and will auto-configure related bits of their own PCI power management registers in PCI configuration space.

PCI Vital Product Data (VPD) is also supported to provide the information that uniquely identifies hardware (Ex., the OEM brand name of RTL8139D(L) LAN card). The information may consist of part number, serial number, and other detailed information.

To provide cost down support, the RTL8139D(L) is capable of using a 25MHz crystal or OSC as its internal clock source.

The RTL8139D(L) keeps network maintenance costs low and eliminates usage barriers. It is the easiest way to upgrade a network from 10 to 100Mbps. It also supports full-duplex operation, making 200Mbps bandwidth possible at no additional cost. To improve compatibility with other brands' products, the RTL8139D(L) is also capable of receiving packets with InterFrameGap no less than 40 Bit-Time. The RTL8139D(L) is highly integrated and requires no "glue" logic or external memory.

The RTL8139D(L) provides a flexible multi-function mode (Realtek patent pending) to incorporate other PCI master devices, like a hardware modem. When in multi-function mode, the RTL8139D(L) acts as an arbiter to distinguish LAN signals from those of other devices. The second device recognizes no difference between being connected to the RTL8139D or a regular PCI bus.

The RTL8139D(L) includes a PCI and Expansion Memory Share Interface (Realtek's patent pending) for a boot ROM and can be used in diskless workstations, providing maximum network security and ease of management.

#### 2. Features

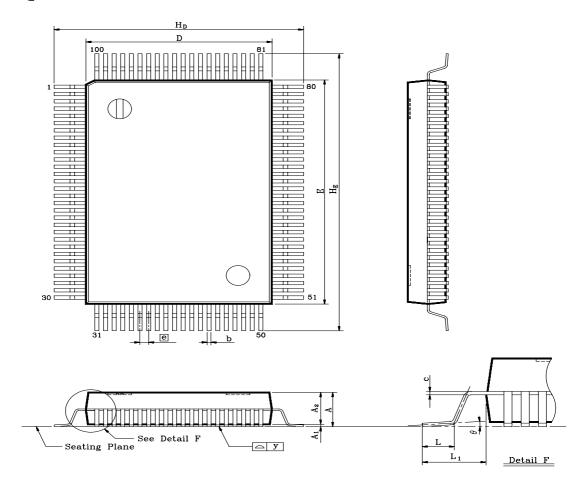

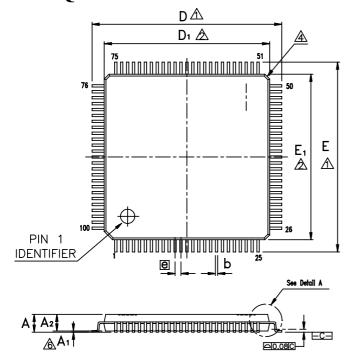

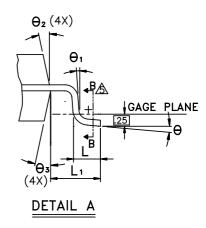

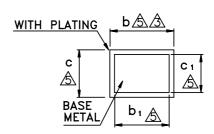

- 100 pin QFP/LQFP

- Integrated Fast Ethernet MAC, Physical chip and transceiver in one chip

- 10Mbps and 100Mbps operation

- Supports 10Mbps and 100Mbps N-way Auto-negotiation operation

- Supports PCI multi-function capabilities

- PCI local bus single-chip Fast Ethernet controller

- ◆ Complies with PCI Revision 2.2

- ◆ Supports PCI clock 16.75MHz-40MHz

- Supports PCI target fast back-to-back transaction

- Provides PCI bus master data transfers and PCI memory space or I/O space mapped data transfers of RTL8139D(L)'s operational registers

- Supports PCI VPD (Vital Product Data)

- Supports ACPI, PCI power management

- Supports PCI multi-function to incorporate with other PCI master device

- ◆ Supports 25MHz crystal or 25MHz OSC as the internal clock source. The frequency deviation of either crystal or OSC must be within 50 PPM.

- Complies with PC99 and PC2001 standards

- Supports Wake-On-LAN function and remote wake-up (Magic Packet\*, LinkChg and Microsoft® wake-up frame)

- Supports 4 Wake-On-LAN (WOL) signals (active high, active low, positive pulse, and negative pulse)

- Supports auxiliary power-on internal reset, to be ready for remote wake-up when main power remains off

- Supports auxiliary power auto-detect, and sets the related capability of power management registers in PCI configuration space

- Includes a programmable, PCI burst size and early Tx/Rx threshold

- Supports a 32-bit general-purpose timer with the external PCI clock as clock source, to generate timer-interrupt

- Contains two large (2Kbyte) independent receive and transmit FIFO's

- Advanced power saving mode when LAN function or wakeup function is not used

- Uses 93C46 (64\*16-bit EEPROM) to store resource configuration, ID parameter, and VPD data

- Supports LED pins for various network activity indications

- Supports loopback capability

- Half/Full duplex capability

- Supports Full Duplex Flow Control (IEEE 802.3x)

- 2.5/3.3V power supply with 5V tolerant I/Os

- Up to 128K byte Boot ROM interface for both EPROM and Flash memory is supported

- 0.25u CMOS process

### 3. Pin Assignments

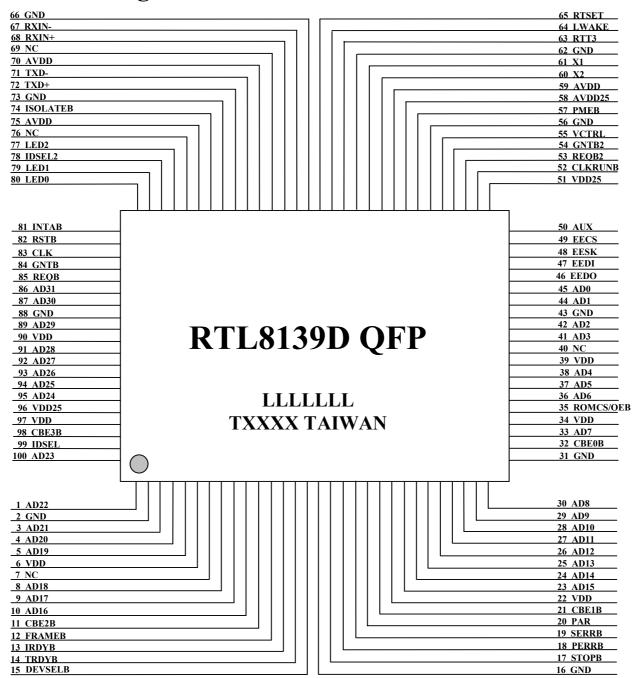

Figure 1. Pin Assignments (100-Pin QFP)

### 3.1. Package Identification

Lead (Pb)-free package is indicated by an 'L' in the location marked 'T' in Figure 1.

'Green' package is indicated by a 'G' in the location marked 'T' in Figure 1.

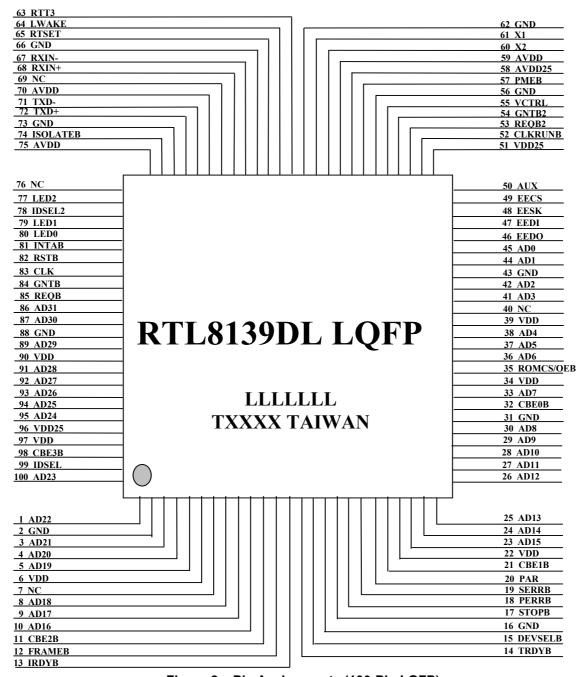

Figure 2. Pin Assignments (100-Pin LQFP)

### 3.2. Package Identification

Lead (Pb)-free package is indicated by an 'L' in the location marked 'T' in Figure 2.

'Green' package is indicated by a 'G' in the location marked 'T' in Figure 2.

### 4. Pin Descriptions

Note that some pins have multiple functions. Refer to the Pin Assignment diagrams for a graphical representation.

### 4.1. Power Management/Isolation Interface

| Symbol                 | Type | Pin No | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|------------------------|------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PMEB<br>(PME#)         | O/D  | 57     | <b>Power Management Event:</b> Open drain, active low. Used by the RTL8139D(L) to request a change in its current power management state and/or to indicate that a power management event has occurred.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| ISOLATEB<br>(ISOLATE#) | I    | 74     | <b>Isolate pin:</b> Active low. Used to isolate the RTL8139D(L) from the PCI bus. The RTL8139D(L) does not drive its PCI outputs (excluding PME#) and does not sample its PCI input (including RST# and PCICLK) as long as the Isolate pin is asserted.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| LWAKE                  | O    | 64     | LAN WAKE-UP signal: This signal is used to inform the motherboard to execute the wake-up process. The motherboard must support Wake-On-LAN (WOL). There are 4 choices of output, including active high, active low, positive pulse, and negative pulse, that may be asserted from the LWAKE pin. Please refer to the LWACT bit in the CONFIG1 register and the LWPTN bit in the CONFIG4 register for the setting of this output signal. The default output is an active high signal. Once a PME event is received, the LWAKE and PMEB assert at the same time when the LWPME (bit4, CONFIG4) is set to 0. If the LWPME is set to 1, the LWAKE asserts only when the PMEB asserts and the ISOLATEB is low. This pin is a 3.3V signaling output pin. |

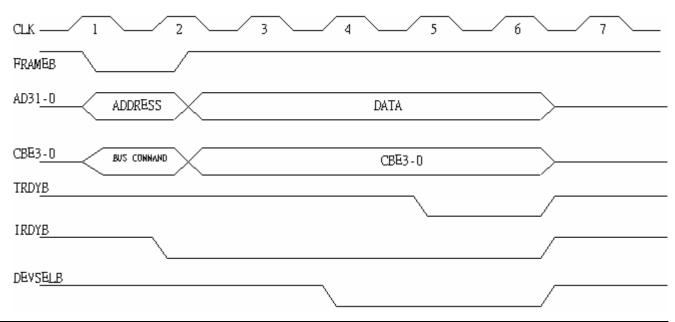

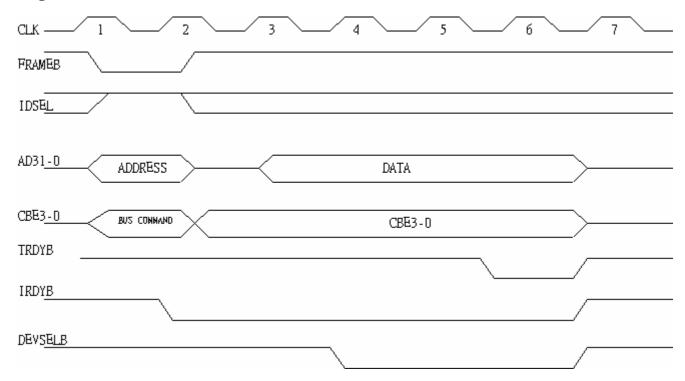

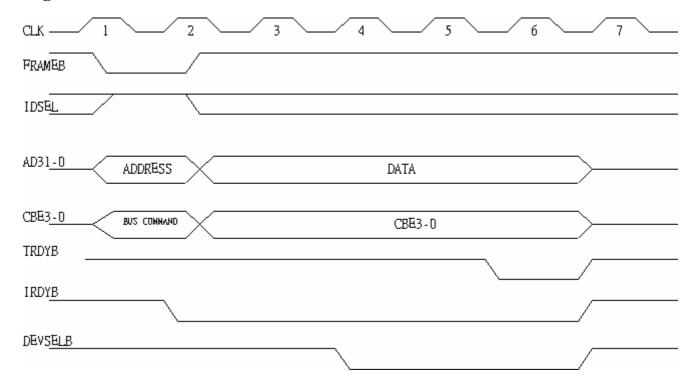

#### 4.2. PCI Interface

| Type  | Pin No               | Description                                                                                     |

|-------|----------------------|-------------------------------------------------------------------------------------------------|

| T/S   | 86,87,89,91-95,100,  | PCI address and data multiplexed pins.                                                          |

|       | 1,3-5,8-10,23-30,33, | Pins AD31-24 are shared with BootROM data pins, while AD16-0 are                                |

|       | 36-38,41,42,44,45    | shared with BootROM address pins.                                                               |

| T/S   | 98,11,21,32          | PCI bus command and byte enables multiplexed pins.                                              |

| I     | 83                   | Clock: This PCI Bus clock provides timing for all transactions and bus                          |

|       |                      | phases, and is input to PCI devices. The rising edge defines the start of                       |

|       |                      | each phase. The clock frequency ranges from 0 to 33MHz.                                         |

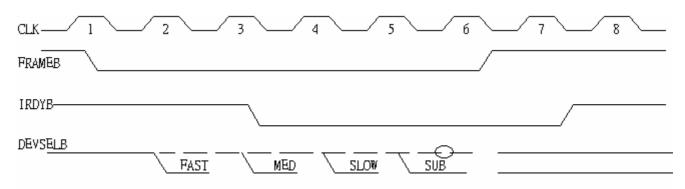

| S/T/S | 15                   | <b>Device Select:</b> As a bus master, the RTL8139D(L) samples this signal                      |

|       |                      | to insure that a PCI target recognizes the destination address for the data                     |

|       |                      | transfer. As a target, the RTL8139D(L) asserts this signal low when it                          |

|       |                      | recognizes its target address after FRAMEB is asserted.                                         |

| S/T/S | 12                   | Cycle Frame: As a bus master, this pin indicates the beginning and                              |

|       |                      | duration of an access. FRAMEB is asserted low to indicate the start of a                        |

|       |                      | bus transaction. While FRAMEB is asserted, data transfer continues.                             |

|       |                      | When FRAMEB is deasserted, the transaction is in the final data phase.                          |

|       |                      | As a target, the device monitors this signal before decoding the address                        |

|       |                      | to check if the current transaction is addressed to it.                                         |

|       | T/S  T/S  I  S/T/S   | T/S 86,87,89,91-95,100, 1,3-5,8-10,23-30,33, 36-38,41,42,44,45  T/S 98,11,21,32  I 83  S/T/S 15 |

| Symbol | Type  | Pin No | Description                                                                                                                                                                                                                                                                                                                                                                                                                                |

|--------|-------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

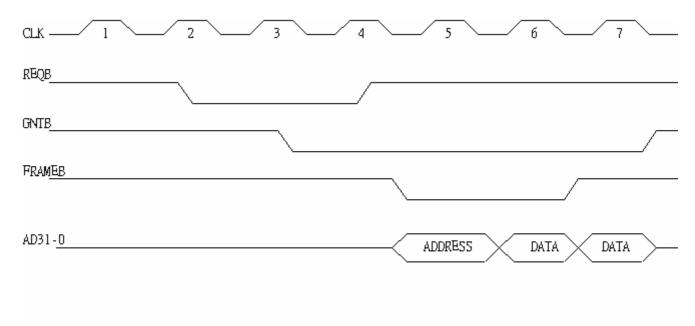

| GNTB   | I     | 84     | <b>Grant:</b> This signal is asserted low to indicate to the RTL8139D(L) that the central arbiter has granted ownership of the bus to the RTL8139D(L). This input is used when the RTL8139D(L) is acting as a bus master.                                                                                                                                                                                                                  |

| REQB   | T/S   | 85     | <b>Request:</b> The RTL8139D(L) will assert this signal low to request the ownership of the bus from the central arbiter.                                                                                                                                                                                                                                                                                                                  |

| IDSEL  | I     | 99     | <b>Initialization Device Select</b> : This pin allows the RTL8139D(L) to identify when configuration read/write transactions are intended for it.                                                                                                                                                                                                                                                                                          |

| INTAB  | O/D   | 81     | <b>INTAB:</b> Used to request an interrupt. It is asserted low when an interrupt condition occurs, as defined by the Interrupt Status, Interrupt Mask and Interrupt Enable registers.                                                                                                                                                                                                                                                      |

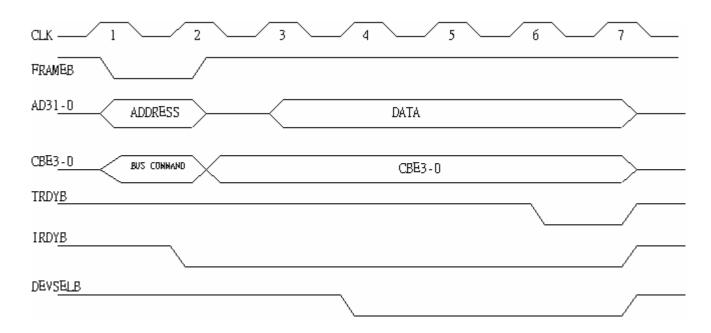

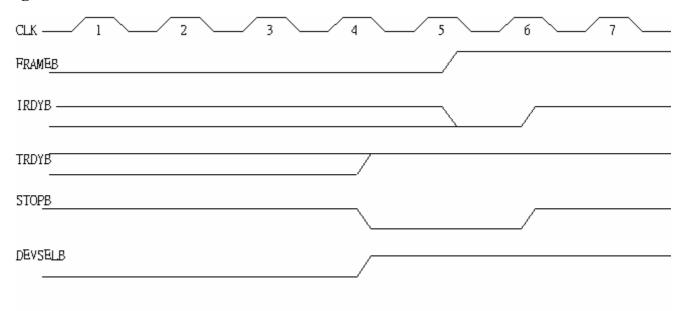

| IRDYB  | S/T/S | 13     | <b>Initiator Ready</b> : This indicates the initiating agent's ability to complete the current data phase of the transaction.                                                                                                                                                                                                                                                                                                              |

|        |       |        | As a bus master, this signal will be asserted low when the RTL8139D(L) is ready to complete the current data phase transaction. This signal is used in conjunction with the TRDYB signal. Data transaction takes place at the rising edge of CLK when both IRDYB and TRDYB are asserted low. As a target, this signal indicates that the master has put data on the bus.                                                                   |

| TRDYB  | S/T/S | 14     | <b>Target Ready:</b> This indicates the target agent's ability to complete the current phase of the transaction.                                                                                                                                                                                                                                                                                                                           |

|        |       |        | As a bus master, this signal indicates that the target is ready for the data during write operations and with the data during read operations. As a target, this signal will be asserted low when the (slave) device is ready to complete the current data phase transaction. This signal is used in conjunction with the IRDYB signal. Data transaction takes place at the rising edge of CLK when both IRDYB and TRDYB are asserted low. |

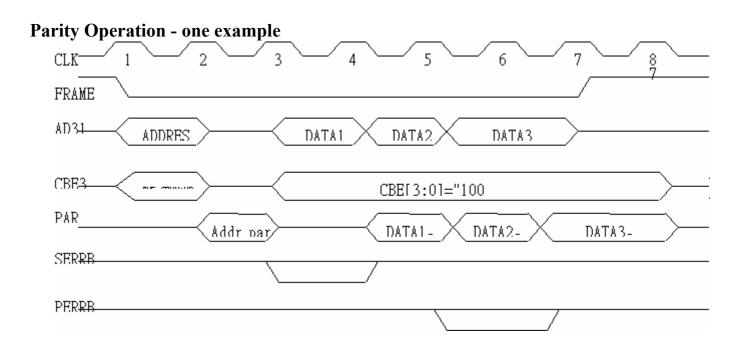

| PAR    | T/S   | 20     | <b>Parity:</b> This signal indicates even parity across AD31-0 and C/BE3-0 including the PAR pin. As a master, PAR is asserted during address and write data phases. As a target, PAR is asserted during read data phases.                                                                                                                                                                                                                 |

| PERRB  | S/T/S | 18     | Parity Error: When the RTL8139D(L) is the bus master and a parity error is detected, the RTL8139D(L) asserts both SERR bit in ISR and Configuration Space command bit 8 (SERRB enable). Next, it completes the current data burst transaction, then stops operation and resets itself. After the host clears the system error, the RTL8139D(L) continues its operation.                                                                    |

|        |       |        | When the RTL8139D(L) is the bus target and a parity error is detected, the RTL8139D(L) asserts this PERRB pin low.                                                                                                                                                                                                                                                                                                                         |

| SERRB  | O/D   | 19     | <b>System Error:</b> If an address parity error is detected and Configuration Space Status register bit 15 (detected parity error) is enabled, RTL8139D(L) asserts both SERRB pin low and bit 14 of Status register in Configuration Space.                                                                                                                                                                                                |

| STOPB  | S/T/S | 17     | <b>Stop:</b> Indicates the current target is requesting the master to stop the current transaction.                                                                                                                                                                                                                                                                                                                                        |

| RSTB   | I     | 82     | <b>Reset:</b> When RSTB is asserted low, the RTL8139D(L) performs internal system hardware reset. RSTB must be held for a minimum of 120 ns.                                                                                                                                                                                                                                                                                               |

### 4.3. EEPROM Interface

| Symbol | Type | Pin No | Description                                                                                                                                                                                                                                                                                                                                                                                  |

|--------|------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AUX    | I    | 50     | Aux. Power Detect: This pin is used to notify the RTL8139D(L) of the existence of Aux. power during initial power-on or a PCI reset.  This pin should be pulled high to the Aux. power via a resistor to detect the Aux. power. Doing so, will enable wakeup support from ACPI D3 cold or APM power-down. If this pin is not pulled high, the RTL8139D(L) assumes that no Aux. power exists. |

| EESK   | О    | 48     | The MA2-0 pins are switched to EESK, EEDI, EEDO in 93C46                                                                                                                                                                                                                                                                                                                                     |

| EEDI   | О    | 47     | programming or auto-load mode.                                                                                                                                                                                                                                                                                                                                                               |

| EEDO   | O, I | 46     |                                                                                                                                                                                                                                                                                                                                                                                              |

| EECS   | О    | 49     | EEPROM chip select                                                                                                                                                                                                                                                                                                                                                                           |

### 4.4. Power Pins

| Symbol | Type | Pin No           | Description     |

|--------|------|------------------|-----------------|

| VDD    | P    | 6,22,34,39,90,97 | +3.3V (Digital) |

| AVDD   | P    | 59,70,75         | +3.3V (Analog)  |

| VDD25  | P    | 51,96            | +2.5V (Digital) |

| AVDD25 | P    | 58               | +2.5V (Analog)  |

| GND    | P    | 2,16,31,43,56,   | Ground          |

|        |      | 62,66,73,88      |                 |

#### 4.5. LED Interface

| Symbol     | Type | Pin No   |                 | ]             | Description   |            |         |

|------------|------|----------|-----------------|---------------|---------------|------------|---------|

| LED0, 1, 2 | О    | 80,79,77 | LED pins        |               |               |            |         |

|            |      |          | LEDS1-0         | 00            | 01            | 10         | 11      |

|            |      |          | LED0            | TX/RX         | TX/RX         | TX         | TX      |

|            |      |          | LED1            | LINK100       | LINK10/100    | LINK10/100 | LINK100 |

|            |      |          | LED2            | LINK10        | FULL          | RX         | LINK10  |

|            |      |          | During power de | own mode, the | e LED's are C | FF.        |         |

#### 4.6. Attachment Unit Interface

| Symbol | Type | Pin No | Description                                                                |

|--------|------|--------|----------------------------------------------------------------------------|

| TXD+   | О    | 72     | 100/10BASE-T transmit (Tx) data.                                           |

| TXD-   | О    | 71     |                                                                            |

| RXIN+  | I    | 68     | 100/10BASE-T receive (Rx) data.                                            |

| RXIN-  | I    | 67     |                                                                            |

| X1     | I    | 61     | 25 MHz crystal/OSC. input.                                                 |

| X2     | О    | 60     | Crystal feedback output: This output is used in crystal connection only.   |

|        |      |        | It must be left open when X1 is driven with an external 25 MHz oscillator. |

#### 4.7. Multi-Function Interface

| Symbol | Type  | Pin No | Description                                                                         |

|--------|-------|--------|-------------------------------------------------------------------------------------|

| REQB2  | IN    | 53     | <b>Request2:</b> The 2 <sup>nd</sup> device will assert this pin low to request the |

|        |       |        | ownership of the PCI bus.                                                           |

| GNTB2  | T/S,O | 54     | <b>Grant2:</b> This signal is asserted low to indicate that the central arbiter     |

|        |       |        | has granted ownership of the bus to the 2 <sup>nd</sup> device.                     |

| IDSEL2 | О     | 78     | Initialization Device Select 2: Used as a chip-select during                        |

|        |       |        | configuration read and write transactions to the 2 <sup>nd</sup> device.            |

#### 4.8. Test And Other Pins

| Symbol    | Type   | Pin No     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

|-----------|--------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| RTT3      | TEST   | 63         | Chip test pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| RTSET     | I/O    | 65         | This pin must be pulled low by a resistor. Please refer to the application circuit for correct value.                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| VCTRL     | Analog | 55         | Use this pin and an external PNP type transistor to generate +2.5V for the RTL8139D(L).                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| ROMCS/OEB | О      | 35         | <b>ROM Chip Select and Output Enable:</b> This is the chip select signal and output enable for the Boot PROM.                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| CLKRUNB   | I/O    | 52         | Clock Run: This signal is used by the RTL8139D(L) to request starting (or speeding up) the clock, CLK. CLKRUNB also indicates the clock status. For the RTL8139D(L), CLKRUNB is an open drain output as well as an input. The RTL8139D(L) requests the central resource to start, speed up, or maintain the interface clock by the assertion of CLKRUNB. For the host system, it is an S/T/S signal. The host system (central resource) is responsible for maintaining CLKRUNB asserted, and for driving it high to the negated (deasserted) state. |  |  |  |  |  |

| NC        | -      | 7,40,69,76 | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

### 5. Register Descriptions

The RTL8139D(L) provides the following set of operational registers mapped into PCI memory space or I/O space.

| Offset      | R/W | Tag     | Description                                                              |  |  |  |  |  |

|-------------|-----|---------|--------------------------------------------------------------------------|--|--|--|--|--|

| 0000h       | R/W | IDR0    | ID Register 0, The ID register0-5 are only permitted to read/write by    |  |  |  |  |  |

|             |     |         | 4-byte access. Read access can be byte, word, or double word access.     |  |  |  |  |  |

|             |     |         | The initial value is autoloaded from EEPROM EthernetID field.            |  |  |  |  |  |

| 0001h       | R/W | IDR1    | ID Register 1                                                            |  |  |  |  |  |

| 0002h       | R/W | IDR2    | ID Register 2                                                            |  |  |  |  |  |

| 0003h       | R/W | IDR3    | ID Register 3                                                            |  |  |  |  |  |

| 0004h       | R/W | IDR4    | ID Register 4                                                            |  |  |  |  |  |

| 0005h       | R/W | IDR5    | ID Register 5                                                            |  |  |  |  |  |

| 0006h-0007h | -   | -       | Reserved                                                                 |  |  |  |  |  |

| 0008h       | R/W | MAR0    | Multicast Register 0, The MAR register 0-7 are only permitted to         |  |  |  |  |  |

|             |     |         | read/write by 4-byte access. Read access can be byte, word, or double    |  |  |  |  |  |

|             |     |         | word access. Driver is responsible for initializing these registers.     |  |  |  |  |  |

| 0009h       | R/W | MAR1    | Multicast Register 1                                                     |  |  |  |  |  |

| 000Ah       | R/W | MAR2    | Multicast Register 2                                                     |  |  |  |  |  |

| 000Bh       | R/W | MAR3    | Multicast Register 3                                                     |  |  |  |  |  |

| 000Ch       | R/W | MAR4    | Multicast Register 4                                                     |  |  |  |  |  |

| 000Dh       | R/W | MAR5    | Multicast Register 5                                                     |  |  |  |  |  |

| 000Eh       | R/W | MAR6    | Multicast Register 6                                                     |  |  |  |  |  |

| 000Fh       | R/W | MAR7    | Multicast Register 7                                                     |  |  |  |  |  |

| 0010h-0013h | R/W | TSD0    | Transmit Status of Descriptor 0                                          |  |  |  |  |  |

| 0014h-0017h | R/W | TSD1    | Transmit Status of Descriptor 1                                          |  |  |  |  |  |

| 0018h-001Bh | R/W | TSD2    | Transmit Status of Descriptor 2                                          |  |  |  |  |  |

| 001Ch-001Fh | R/W | TSD3    | Transmit Status of Descriptor 3                                          |  |  |  |  |  |

| 0020h-0023h | R/W | TSAD0   | Transmit Start Address of Descriptor0                                    |  |  |  |  |  |

| 0024h-0027h | R/W | TSAD1   | Transmit Start Address of Descriptor1                                    |  |  |  |  |  |

| 0028h-002Bh | R/W | TSAD2   | Transmit Start Address of Descriptor2                                    |  |  |  |  |  |

| 002Ch-002Fh | R/W | TSAD3   | Transmit Start Address of Descriptor3                                    |  |  |  |  |  |

| 0030h-0033h | R/W | RBSTART | Receive (Rx) Buffer Start Address                                        |  |  |  |  |  |

| 0034h-0035h | R   | ERBCR   | Early Receive (Rx) Byte Count Register                                   |  |  |  |  |  |

| 0036h       | R   | ERSR    | Early Rx Status Register                                                 |  |  |  |  |  |

| 0037h       | R/W | CR      | Command Register                                                         |  |  |  |  |  |

| 0038h-0039h | R/W | CAPR    | Current Address of Packet Read                                           |  |  |  |  |  |

| 003Ah-003Bh | R   | CBR     | Current Buffer Address: The initial value is 0000h. It reflects total    |  |  |  |  |  |

|             |     |         | received byte-count in the rx buffer.                                    |  |  |  |  |  |

| 003Ch-003Dh | R/W | IMR     | Interrupt Mask Register                                                  |  |  |  |  |  |

| 003Eh-003Fh | R/W | ISR     | Interrupt Status Register                                                |  |  |  |  |  |

| 0040h-0043h | R/W | TCR     | Transmit (Tx) Configuration Register                                     |  |  |  |  |  |

| 0044h-0047h | R/W | RCR     | Receive (Rx) Configuration Register                                      |  |  |  |  |  |

| 0048h-004Bh | R/W | TCTR    | Timer CounT Register: This register contains a 32-bit general-purpose    |  |  |  |  |  |

|             |     |         | timer. Writing any value to this 32-bit register will reset the original |  |  |  |  |  |

|             |     |         | timer and begin to count from zero.                                      |  |  |  |  |  |

| 004Ch-004Fh | R/W | MPC     | Missed Packet Counter: Indicates the number of packets discarded due     |  |  |  |  |  |

|             |     |         | to Rx FIFO overflow. It is a 24-bit counter. After s/w reset, MPC is     |  |  |  |  |  |

|             |     |         | cleared. Only the lower 3 bytes are valid.                               |  |  |  |  |  |

| Offset      | R/W     | Tag          | Description                                                           |  |  |  |

|-------------|---------|--------------|-----------------------------------------------------------------------|--|--|--|

|             |         |              | When written any value, MPC will be reset also.                       |  |  |  |

| 0050h       | R/W     | 9346CR       | 93C46 Command Register                                                |  |  |  |

| 0051h       | R/W     | CONFIG0      | Configuration Register 0                                              |  |  |  |

| 0052h       | R/W     | CONFIG1      | Configuration Register 1                                              |  |  |  |

| 0053H       | -       | -            | Reserved                                                              |  |  |  |

| 0054h-0057h | R/W     | TimerInt     | Timer Interrupt Register. Once having written a nonzero value to this |  |  |  |

|             |         |              | register, the Timeout bit of ISR register will be set whenever the    |  |  |  |

|             |         |              | TCTR reaches to this value. The Timeout bit will never be set as long |  |  |  |

|             |         |              | as TimerInt register is zero.                                         |  |  |  |

| 0058h       | R/W     | MSR          | Media Status Register                                                 |  |  |  |

| 0059h       | R/W     | CONFIG3      | Configuration register 3                                              |  |  |  |

| 005Ah       | R/W     | CONFIG4      | Configuration register 4                                              |  |  |  |

| 005Bh       | -       | -            | Reserved                                                              |  |  |  |

| 005Ch-005Dh | R/W     | MULINT       | Multiple Interrupt Select                                             |  |  |  |

| 005Eh       | R       | RERID        | PCI Revision ID = 10h.                                                |  |  |  |

| 005Fh       | -       | -            | Reserved.                                                             |  |  |  |

| 0060h-0061h | R       | TSAD         | Transmit Status of All Descriptors                                    |  |  |  |

| 0062h-0063h | R/W     | BMCR         | Basic Mode Control Register                                           |  |  |  |

| 0064h-0065h | R       | BMSR         | Basic Mode Status Register                                            |  |  |  |

| 0066h-0067h | R/W     | ANAR         | Auto-Negotiation Advertisement Register                               |  |  |  |

| 0068h-0069h | R       | ANLPAR       | Auto-Negotiation Link Partner Register                                |  |  |  |

| 006Ah-006Bh | R       | ANER         | Auto-Negotiation Expansion Register                                   |  |  |  |

| 006Ch-006Dh | R       | DIS          | Disconnect Counter                                                    |  |  |  |

| 006Eh-006Fh | R       | FCSC         | False Carrier Sense Counter                                           |  |  |  |

| 0070h-0071h | R/W     | NWAYTR       | N-way Test Register                                                   |  |  |  |

| 0072h-0073h | R       | REC          | RX_ER Counter                                                         |  |  |  |

| 0074h-0075h | R/W     | CSCR         | CS Configuration Register                                             |  |  |  |

| 0076-0077h  | - D/III | - DID/1 DADA | Reserved.                                                             |  |  |  |

| 0078h-007Bh | R/W     | PHY1_PARM    | PHY parameter 1                                                       |  |  |  |

| 007Ch-007Fh | R/W     | TW_PARM      | Twister parameter                                                     |  |  |  |

| 0080h       | R/W     | PHY2_PARM    | PHY parameter 2                                                       |  |  |  |

| 0081-0083h  | -       | -            | Reserved                                                              |  |  |  |

| 0084h       | R/W     | CRC0         | Power Management CRC register0 for wakeup frame0                      |  |  |  |

| 0085h       | R/W     | CRC1         | Power Management CRC register1 for wakeup frame1                      |  |  |  |

| 0086h       | R/W     | CRC2         | Power Management CRC register2 for wakeup frame2                      |  |  |  |

| 0087h       | R/W     | CRC3         | Power Management CRC register3 for wakeup frame3                      |  |  |  |

| 0088h       | R/W     | CRC4         | Power Management CRC register4 for wakeup frame4                      |  |  |  |

| 0089h       | R/W     | CRC5         | Power Management CRC register5 for wakeup frame5                      |  |  |  |

| 008Ah       | R/W     | CRC6         | Power Management CRC register6 for wakeup frame6                      |  |  |  |

| 008Bh       | R/W     | CRC7         | Power Management CRC register7 for wakeup frame7                      |  |  |  |

| 008Ch-0093h | R/W     | Wakeup0      | Power Management wakeup frame0 (64bit)                                |  |  |  |

| 0094h-009Bh | R/W     | Wakeup1      | Power Management wakeup frame1 (64bit)                                |  |  |  |

| 009Ch-00A3h | R/W     | Wakeup2      | Power Management wakeup frame2 (64bit)                                |  |  |  |

| 00A4h-00ABh | R/W     | Wakeup3      | Power Management wakeup frame3 (64bit)                                |  |  |  |

| 00ACh-00B3h | R/W     | Wakeup4      | Power Management wakeup frame4 (64bit)                                |  |  |  |

| 00B4h-00BBh | R/W     | Wakeup5      | Power Management wakeup frame 5 (64bit)                               |  |  |  |

| 00BCh-00C3h | R/W     | Wakeup6      | Power Management wakeup frame6 (64bit)                                |  |  |  |

| 00C4h-00CBh | R/W     | Wakeup7      | Power Management wakeup frame7 (64bit)                                |  |  |  |

| 00CCh       | R/W     | LSBCRC0      | LSB of the mask byte of wakeup frame0 within offset 12 to 75          |  |  |  |

| Offset      | R/W | Tag     | Description                                                  |

|-------------|-----|---------|--------------------------------------------------------------|

| 00CDh       | R/W | LSBCRC1 | LSB of the mask byte of wakeup frame1 within offset 12 to 75 |

| 00CEh       | R/W | LSBCRC2 | LSB of the mask byte of wakeup frame2 within offset 12 to 75 |

| 00CFh       | R/W | LSBCRC3 | LSB of the mask byte of wakeup frame3 within offset 12 to 75 |

| 00D0h       | R/W | LSBCRC4 | LSB of the mask byte of wakeup frame4 within offset 12 to 75 |

| 00D1h       | R/W | LSBCRC5 | LSB of the mask byte of wakeup frame5 within offset 12 to 75 |

| 00D2h       | R/W | LSBCRC6 | LSB of the mask byte of wakeup frame6 within offset 12 to 75 |

| 00D3h       | R/W | LSBCRC7 | LSB of the mask byte of wakeup frame7 within offset 12 to 75 |

| 00D4h-00D7h | -   | -       | Reserved.                                                    |

| 00D8h       | R/W | Config5 | Configuration register 5                                     |

| 00D9h-00FFh | -   | -       | Reserved.                                                    |

### 5.1. Receive Status Register in Rx Packet Header

| Bit  | R/W | Symbol | Description                                                                                                                                                     |

|------|-----|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15   | R   | MAR    | <b>Multicast Address Received:</b> This bit set to 1 indicates that a multicast packet is received.                                                             |

| 14   | R   | PAM    | <b>Physical Address Matched:</b> This bit set to 1 indicates that the destination address of this packet matches the value written in ID registers.             |

| 13   | R   | BAR    | <b>Broadcast Address Received:</b> This bit set to 1 indicates that a broadcast packet is received. BAR, MAR bit will not be set simultaneously.                |

| 12-6 | -   | -      | Reserved                                                                                                                                                        |

| 5    | R   | ISE    | <b>Invalid Symbol Error:</b> (100BASE-TX only) This bit set to 1 indicates that an invalid symbol was encountered during the reception of this packet.          |

| 4    | R   | RUNT   | <b>Runt Packet Received:</b> This bit set to 1 indicates that the received packet length is smaller than 64 bytes ( i.e. media header + data + CRC < 64 bytes ) |

| 3    | R   | LONG   | <b>Long Packet:</b> This bit set to 1 indicates that the size of the received packet exceeds 4k bytes.                                                          |

| 2    | R   | CRC    | <b>CRC Error:</b> When set, indicates that a CRC error occurred on the received packet.                                                                         |

| 1    | R   | FAE    | <b>Frame Alignment Error:</b> When set, indicates that a frame alignment error occurred on this received packet.                                                |

| 0    | R   | ROK    | Receive OK: When set, indicates that a good packet is received.                                                                                                 |

### 5.2. Transmit Status Register

#### (TSD0-3)(Offset 0010h-001Fh, R/W)

The read-only bits (CRS, TABT, OWC, CDH, NCC3-0, TOK, TUN) will be cleared by the RTL8139D(L) when the Transmit Byte Count (bits 12-0) in the corresponding Tx descriptor is written. It is not affected when software writes to these bits. These registers are only permitted to write by double-word access. After software reset, all bits except OWN bit are reset to "0".

| Bit   | R/W | Symbol    | Description                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

|-------|-----|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 31    | R   | CRS       | <b>Carrier Sense Lost:</b> This bit is set to 1 when the carrier is lost during                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

|       |     |           | transmission of a packet.                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| 30    | R   | TABT      | <b>Transmit Abort:</b> This bit is set to 1 if the transmission of a packet was aborted. This bit is read only, writing to this bit is not affected.                                                                                                                                                                                                                                          |  |  |  |  |  |

| 29    | R   | OWC       | <b>Out of Window Collision:</b> This bit is set to 1 if the RTL8139D(L) encountered an "out of window" collision during the transmission of a packet.                                                                                                                                                                                                                                         |  |  |  |  |  |

| 28    | R   | CDH       | <b>CD Heart Beat:</b> The NIC watches for a collision signal (ie, CD Heartbeat signal) during the first 6.4us of the interframe gap following a transmission. This bit is set if the transceiver fails to send this signal. This bit is cleared in the 100 Mbps mode.                                                                                                                         |  |  |  |  |  |

| 27-24 | R   | NCC3-0    | <b>Number of Collision Count:</b> Indicates the number of collisions encountered during the transmission of a packet.                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| 23-22 | -   | -         | Reserved                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| 21-16 | R/W | ERTXTH5-0 | Early Tx Threshold: Specifies the threshold level in the Tx FIFO to begin the transmission. When the byte count of the data in the Tx FIFO reaches this level, (or the FIFO contains at least one complete packet) the RTL8139D(L) will transmit this packet.  000000 = 8 bytes  These fields count from 000001 to 111111 in unit of 32 bytes.  This threshold must avoid exceeding 2K bytes. |  |  |  |  |  |

| 15    | R   | TOK       | <b>Transmit OK:</b> Set to 1 indicates that the transmission of a packet was completed successfully and no transmit underrun has occurred.                                                                                                                                                                                                                                                    |  |  |  |  |  |

| 14    | R   | TUN       | <b>Transmit FIFO Underrun:</b> Set to 1 if the Tx FIFO was exhausted during the transmission of a packet. The RTL8139D(L) can re-transfer data if the Tx FIFO underruns and can also transmit the packet to the wire successfully even though the Tx FIFO underruns. That is, when TSD <tun>=1, TSD<tok>=0 and ISR<tok>=1 (or ISR<ter>=1).</ter></tok></tok></tun>                            |  |  |  |  |  |

| 13    | R/W | OWN       | <b>OWN:</b> The RTL8139D(L) sets this bit to 1 when the Tx DMA operation of this descriptor was completed. The driver must set this bit to 0 when the Transmit Byte Count (bits 0-12) is written. The default value is 1.                                                                                                                                                                     |  |  |  |  |  |

| 12-0  | R/W | SIZE      | <b>Descriptor Size:</b> The total size in bytes of the data in this descriptor. If the packet length is more than 1792 byte (0700h), the Tx queue will be invalid, i.e. the next descriptor will be written only after the OWN bit of that long packet's descriptor has been set.                                                                                                             |  |  |  |  |  |

11

### 5.3. ERSR: Early Rx Status Register

(Offset 0036h, R)

| Bit | R/W | Symbol | Description                                                             |  |  |  |  |

|-----|-----|--------|-------------------------------------------------------------------------|--|--|--|--|

| 7-4 | -   | -      | Reserved                                                                |  |  |  |  |

| 3   | R   | ERGood | Early Rx Good packet: This bit is set whenever a packet is completely   |  |  |  |  |

|     |     |        | received and the packet is good. Writing a 1 to this bit will clear it. |  |  |  |  |

| 2   | R   | ERBad  | Early Rx Bad packet: This bit is set whenever a packet is completely    |  |  |  |  |

|     |     |        | received and the packet is bad. Writing a 1 to this bit will clear it.  |  |  |  |  |

| 1   | R   | EROVW  | Early Rx OverWrite: This bit is set when the RTL8139D(L)'s local        |  |  |  |  |

|     |     |        | address pointer is equal to CAPR. In the early mode, this is different  |  |  |  |  |

|     |     |        | from buffer overflow. It happens that the RTL8139D(L) detected an Rx    |  |  |  |  |

|     |     |        | error and wanted to fill another packet data from the beginning address |  |  |  |  |

|     |     |        | of that error packet. Writing a 1 to this bit will clear it.            |  |  |  |  |

| 0   | R   | EROK   | Early Rx OK: The power-on value is 0. It is set when the Rx byte count  |  |  |  |  |

|     |     |        | of the arriving packet exceeds the Rx threshold. After the whole packet |  |  |  |  |

|     |     |        | is received, the RTL8139D(L) will set ROK or RER in ISR and clear       |  |  |  |  |

|     |     |        | this bit simultaneously. Setting this bit will invoke a ROK interrupt.  |  |  |  |  |

### 5.4. Command Register

(Offset 0037h, R/W)

This register is used for issuing commands to the RTL8139D(L). These commands are issued by setting the corresponding bits for the function. A global software reset along with individual reset and enable/disable for transmitter and receiver are provided here.

| Bit | R/W | Symbol | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----|-----|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-5 | -   | -      | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 4   | R/W | RST    | <b>Reset:</b> Setting to 1 forces the RTL8139D(L) to a software reset state which disables the transmitter and receiver, reinitializes the FIFOs, resets the system buffer pointer to the initial value (Tx buffer is at TSAD0, Rx buffer is empty). The values of IDR0-5 and MAR0-7 and PCI configuration space will have no changes. This bit is 1 during the reset operation, and is cleared to 0 by the RTL8139D(L) when the reset operation is complete. |

| 3   | R/W | RE     | Receiver Enable: When set to 1, and the receive state machine is idle, the receive machine becomes active. This bit will read back as a 1 whenever the receive state machine is active. After initial power-up, software must insure that the receiver has completely reset before setting this bit.                                                                                                                                                          |

| 2   | R/W | TE     | <b>Transmitter Enable:</b> When set to 1, and the transmit state machine is idle, then the transmit state machine becomes active. This bit will read back as a 1 whenever the transmit state machine is active. After initial power-up, software must insure that the transmitter has completely reset before setting this bit.                                                                                                                               |

| 1   | -   | -      | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 0   | R   | BUFE   | <b>Buffer Empty:</b> Rx Buffer Empty. There is no packet stored in the Rx buffer ring.                                                                                                                                                                                                                                                                                                                                                                        |

### 5.5. Interrupt Mask Register (Offset 003Ch-003Dh, R/W)

This register masks the interrupts that can be generated from the Interrupt Status Register. A hardware reset will clear all mask bits. Setting a mask bit allows the corresponding bit in the Interrupt Status Register to cause an interrupt. The Interrupt Status Register bits are always set to 1 if the condition is present, regardless of the state of the corresponding mask bit.

| Bit  | R/W | Symbol      | Description                                                      |  |  |  |  |  |

|------|-----|-------------|------------------------------------------------------------------|--|--|--|--|--|

| 15   | R/W | SERR        | <b>System Error Interrupt:</b> 1 => Enable, 0 => Disable.        |  |  |  |  |  |

| 14   | R/W | TimeOut     | <b>Time Out Interrupt:</b> 1 => Enable, 0 => Disable.            |  |  |  |  |  |

| 13   | R/W | LenChg      | <b>Cable Length Change Interrupt:</b> 1 => Enable, 0 => Disable. |  |  |  |  |  |

| 12-7 | ı   | -           | Reserved                                                         |  |  |  |  |  |

| 6    | R/W | FOVW        | <b>Rx FIFO Overflow Interrupt:</b> 1 => Enable, 0 => Disable.    |  |  |  |  |  |

| 5    | R/W | PUN/LinkChg | Packet Underrun/Link Change Interrupt: 1 => Enable, 0 =>         |  |  |  |  |  |

|      |     |             | Disable.                                                         |  |  |  |  |  |

| 4    | R/W | RXOVW       | <b>Rx Buffer Overflow Interrupt:</b> 1 => Enable, 0 => Disable.  |  |  |  |  |  |

| 3    | R/W | TER         | <b>Transmit Error Interrupt:</b> 1 => Enable, 0 => Disable.      |  |  |  |  |  |

| 2    | R/W | TOK         | <b>Transmit OK Interrupt:</b> 1 => Enable, 0 => Disable.         |  |  |  |  |  |

| 1    | R/W | RER         | <b>Receive Error Interrupt:</b> 1 => Enable, 0 => Disable.       |  |  |  |  |  |

| 0    | R/W | ROK         | <b>Receive OK Interrupt:</b> 1 => Enable, 0 => Disable.          |  |  |  |  |  |

# 5.6. Interrupt Status Register (Offset 003Eh-003Fh, R/W)

This register indicates the source of an interrupt when the INTA pin goes active. Enabling the corresponding bits in the Interrupt Mask Register (IMR) allows bits in this register to produce an interrupt. When an interrupt is active, one of more bits in this register are set to a "1". The interrupt Status Register reflects all current pending interrupts, regardless of the state of the corresponding mask bit in the IMR. Reading the ISR clears all interrupts. Writing to the ISR has no effect.

| Bit    | R/W | Symbol      | Description                                                                                                                                 |

|--------|-----|-------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| 15     | R/W | SERR        | <b>System Error:</b> Set to 1 when the RTL8139D(L) signals a system error on the PCI bus.                                                   |

| 14     | R/W | TimeOut     | <b>Time Out:</b> Set to 1 when the TCTR register reaches to the value of the TimerInt register.                                             |

| 13     | R/W | LenChg      | Cable Length Change: Cable length is changed after Receiver is enabled.                                                                     |

| 12 - 7 | -   | -           | Reserved                                                                                                                                    |

| 6      | R/W | FOVW        | <b>Rx FIFO Overflow:</b> Set when an overflow occurs on the Rx status FIFO.                                                                 |

| 5      | R/W | PUN/LinkChg | <b>Packet Underrun/Link Change:</b> Set to 1 when CAPR is written but Rx buffer is empty, or when link status is changed.                   |

| 4      | R/W | RXOVW       | <b>Rx Buffer Overflow:</b> Set when receive (Rx) buffer ring storage resources have been exhausted.                                         |

| 3      | R/W | TER         | <b>Transmit (Tx) Error:</b> Indicates that a packet transmission was aborted, due to excessive collisions, according to the TXRR's setting. |

| 2      | R/W | TOK         | <b>Transmit (Tx) OK:</b> Indicates that a packet transmission is completed successfully.                                                    |

| 1      | R/W | RER         | Receive (Rx) Error: Indicates that a packet has either CRC error or                                                                         |

| Bit | R/W | Symbol | Description                                                               |  |  |  |  |  |

|-----|-----|--------|---------------------------------------------------------------------------|--|--|--|--|--|

|     |     |        | frame alignment error (FAE). The collided frame will not be recognized    |  |  |  |  |  |

|     |     |        | as CRC error if the length of this frame is shorter than 16 byte.         |  |  |  |  |  |

| 0   | R/W | ROK    | Receive (Rx) OK: In normal mode, indicates the successful completion      |  |  |  |  |  |

|     |     |        | of a packet reception. In early mode, indicates that the Rx byte count of |  |  |  |  |  |

|     |     |        | the arriving packet exceeds the early Rx threshold.                       |  |  |  |  |  |

# 5.7. Transmit Configuration Register (Offset 0040h-0043h, R/W)

This register defines the Transmit Configuration for the RTL8139D(L). It controls such functions as Loopback, Heartbeat, Auto Transmit Padding, programmable Interframe Gap, Fill and Drain Thresholds, and maximum DMA burst size.

| Bit    | R/W | Symbol       | Description                         |             |           |         |          |         |           |           |

|--------|-----|--------------|-------------------------------------|-------------|-----------|---------|----------|---------|-----------|-----------|

| 31     | =   | -            | Reserved                            |             |           |         |          |         |           |           |

| 30-26  | R   | HWVERID_A    | Hardware Version ID A:              |             |           |         |          |         |           |           |

|        |     | _            |                                     | Bit30       | Bit29     | Bit28   | Bit27    | Bit26   | Bit23     | Bit22     |

|        |     |              | RTL8139                             | 1           | 1         | 0       | 0        | 0       | 0         | 0         |

|        |     |              | RTL8139A                            | 1           | 1         | 1       | 0        | 0       | 0         | 0         |

|        |     |              | RTL8139A-G                          | 1           | 1         | 1       | 0        | 1       | 0         | 0         |

|        |     |              | RTL8139B                            | 1           | 1         | 1       | 1        | 0       | 0         | 0         |

|        |     |              | RTL8130                             | 1           | 1         | 1       | 1        | 0       | 0         | 0         |

|        |     |              | RTL8139C                            | 1           | 1         | 1       | 0        | 1       | 0         | 0         |

|        |     |              | RTL8100                             | 1           | 1         | 1       | 1        | 0       | 1         | 0         |

|        |     |              | RTL8100B/                           | 1           | 1         | 1       | 0        | 1       | 0         | 1         |

|        |     |              | 8139D                               |             |           |         |          |         |           |           |

|        |     |              | RTL8139C+                           | 1           | 1         | 1       | 0        | 1       | 1         | 0         |

|        |     |              | RTL8101                             | 1           | 1         | 1       | 0        | 1       | 1         | 1         |

|        |     |              | Reserved                            |             |           | Other   | combin   | nation  |           |           |

|        | - / | TTG1 0       |                                     |             | ent :     | ~       |          |         |           |           |

| 25-24  | R/W | IFG1, 0      | Interframe Ga                       |             |           |         |          |         |           |           |

|        |     |              | interframe gap ti                   |             |           |         |          |         |           |           |

|        |     |              | 100Mbps. The time                   |             |           |         |          |         |           |           |

|        |     |              | and 960ns to 840 will violate the I |             |           |         | nat any  | value ( | omer ma   | m (1, 1)  |

|        |     |              | The formula for                     |             |           |         |          |         |           |           |

|        |     |              | 10 Mbps                             | tiic iiitei | maine ;   |         | s + 0.40 | IFG(1:0 | ))) 116   |           |

|        |     |              | 100 Mbps                            |             |           |         | ,        | IFG(1:0 | //        |           |

| 23-22  | R   | HWVERID B    | Hardware Vers                       | ion ID 1    | B         | 3.01    |          | . =(1.0 | ,,,       |           |

| 21-19  | -   | <del>-</del> | Reserved                            |             |           |         |          |         |           |           |

| 18, 17 | R/W | LBK1, LBK0   | Loopback test:                      | There w     | vill be n | o packe | et on th | e TX+/- | - lines ı | ınder the |

| ĺ      |     | , ,          | Loopback test con                   |             |           |         |          |         |           |           |

|        |     |              | the link state.                     |             |           |         |          |         |           |           |

|        |     |              | 00 : normal operation               |             |           |         |          |         |           |           |

|        |     |              | 01 : Reserved                       |             |           |         |          |         |           |           |

|        |     |              | 10 : Reserved                       |             |           |         |          |         |           |           |

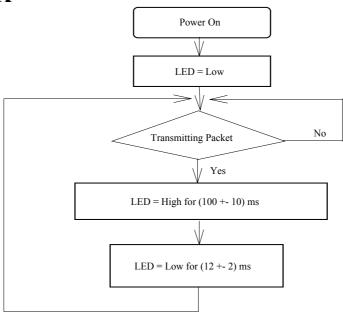

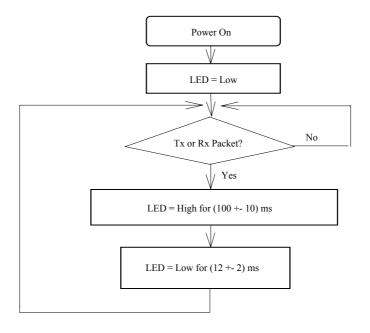

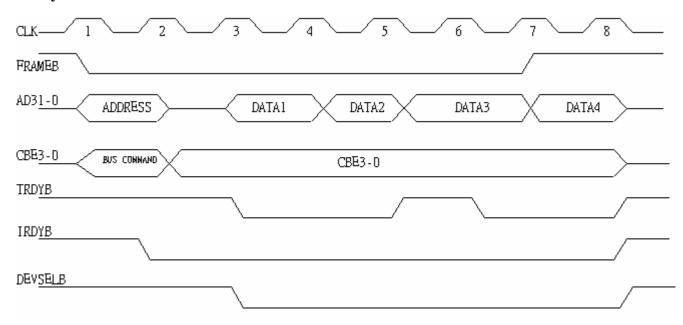

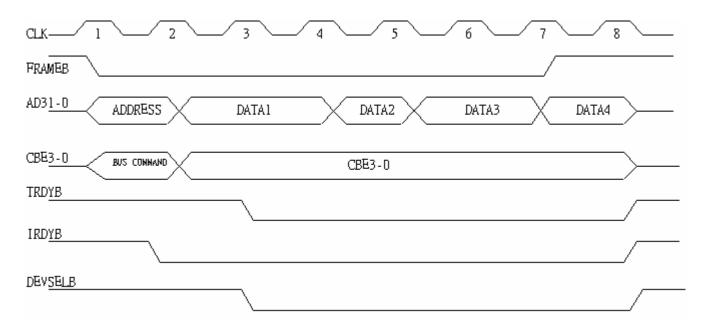

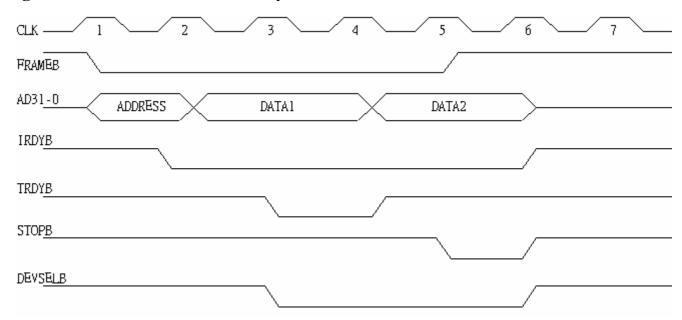

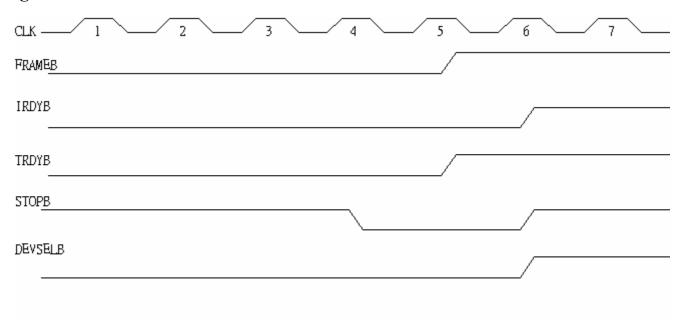

|        |     |              | 11 : Loopback m                     | ode         |           |         |          |         |           |           |