**High Performance Regulators for PCs**

# Termination Regulators for DDR-SDRAMs

BD3538F.BD3538HFN

No.10030EAT33

#### Description

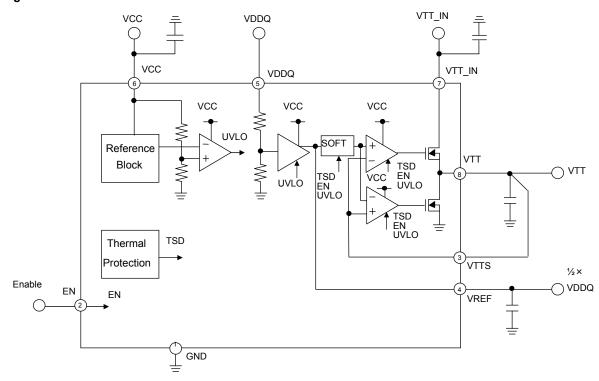

BD3538F/HFN is a termination regulator compatible with JEDEC DDR-SDRAM, which functions as a linear power supply incorporating an N-channel MOSFET and provides a sink/source current capability up to 1A respectively. A built-in high-speed OP-AMP specially designed offers an excellent transient response. Requires 3.3 volts or 5.0 volts as a bias power supply to drive the N-channel MOSFET. Has an independent reference voltage input pin (VDDQ) and an independent feedback pin (VTTS) to maintain the accuracy in voltage required by JEDEC, and offers an excellent output voltage accuracy and load regulation. Also has a reference power supply output pin (VREF) for DDR-SDRAM or a memory controller. When EN pin turns to "Low", VTT output becomes "Hi-Z" while VREF output is kept unchanged, compatible with "Self Refresh" state of DDR-SDRAM.

#### Features

- 1) Incorporates a push-pull power supply for termination (VTT)

- 2) Incorporates a reference voltage circuit (VREF)

- 3) Incorporates an enabler

- 4) Incorporates an undervoltage lockout (UVLO)

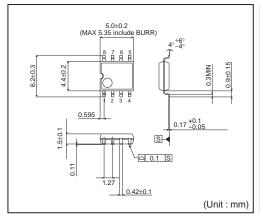

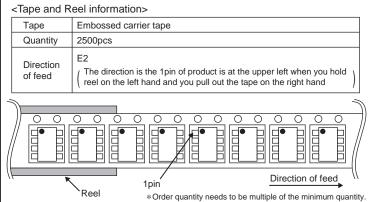

- 5) Employs SOP8 package

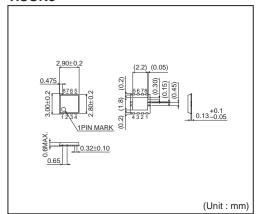

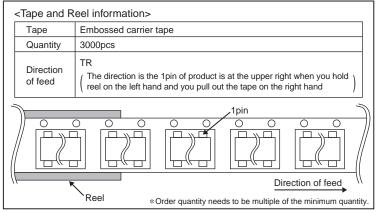

- 6) Employs HSON8 package

- 7) Incorporates a thermal shutdown protector (TSD)

- 8) Operates with input voltage from 2.7 to 5.5 volts

- 9) Compatible with Dual Channel (DDR-II)

#### ●Use

Power supply for DDR I / II / III - SDRAM

Absolute Maximum Ratings

| Parameter                    | Cymbol | Rat               | Unit               |          |

|------------------------------|--------|-------------------|--------------------|----------|

| Farameter                    | Symbol | BD3538F           | BD3538HFN          | - Office |

| Input Voltage                | VCC    | 7 *1*2            | 7 *1*2             | V        |

| Enable Input Voltage         | VEN    | 7 *1*2            | 7 *1*2             | V        |

| Termination Input Voltage    | VTT_IN | 7 *1*2            | 7 *1*2             | V        |

| VDDQ Reference Voltage       | VDDQ   | 7 *1*2            | 7 *1*2             | V        |

| Output Current               | ITT    | 1                 | 1                  | Α        |

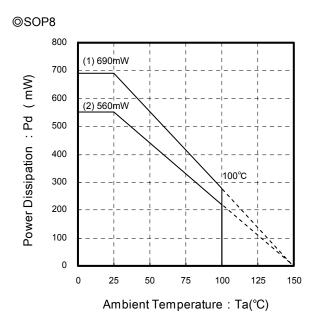

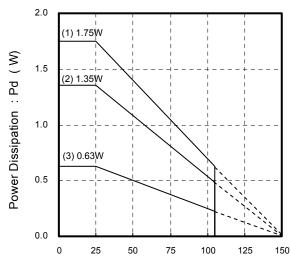

| Power Dissipation1           | Pd1    | 560 <sup>*3</sup> | 630 <sup>*5</sup>  | mW       |

| Power Dissipation2           | Pd2    | 690 <sup>*4</sup> | 1350 <sup>*6</sup> | mW       |

| Power Dissipation3           | Pd3    | -                 | 1750 <sup>*7</sup> | mW       |

| Operating Temperature Range  | Tstg   | -40 <b>~</b> +105 | -40 <b>~</b> +105  | °C       |

| Storage Temperature Range    | Tjmax  | -55 <b>~</b> +150 | -55 <b>~</b> +150  | °C       |

| Maximum Junction Temperature | Tjmax  | +150              | +150               | °C       |

<sup>\*1</sup> Should not exceed Pd.

<sup>\*2</sup> Instantaneous surge voltage, back electromotive force and voltage under less than 10% duty cycle.

<sup>\*3</sup> Reduced by 4.48mW for each increase in Ta of 1°C over 25°C(With no heat sink).

<sup>\*4</sup> Reduced by 5.52mW for each increase in Ta of 1°C over 25°C(When mounted on a board 70mm×70mm×1.6mm Glass-epoxyPCB).

<sup>\*5</sup> Reduced by 5.04mW/°C for each increase in Ta≧25°C (when mounted on a 70mm × 70mm × 1.6mm glass-epoxy board, 1-layer)

On less than 0.2% (percentage occupied by copper foil.

<sup>\*6</sup> Reduced by 10.8mW/°C for each increase in Ta≧25°C (when mounted on a 70mm × 70mm × 1.6mm glass-epoxy board, 1-layer)

On less than 7.0% (percentage occupied by copper foil.

<sup>\*7</sup> Reduced by 14.0mW/°C for each increase in Ta≥25°C (when mounted on a 70mm × 70mm × 1.6mm glass-epoxy board, 1-layer)

On less than 65.0% (percentage occupied by copper foil.

●Operating Conditions (Ta=25°C)

| Darameter                 | Symbol | Rat  | Unit |       |

|---------------------------|--------|------|------|-------|

| Parameter                 |        | Min  | Max  | UIIIL |

| Input Voltage             | VCC    | 2.7  | 5.5  | V     |

| Termination Input Voltage | VTT_IN | 1.0  | 5.5  | V     |

| VDDQ Reference Voltage    | VDDQ   | 1.0  | 2.75 | V     |

| Enable Input Voltage      | VEN    | -0.3 | 5.5  | V     |

<sup>★</sup> No radiation-resistant design is adopted for the present product.

●Electrical Characteristics (unless otherwise noted, Ta=25°C VCC=3.3V VEN=3V VDDQ=1.8V VTT\_IN=1.8V)

| Limite                          |         |                    |               |                    |      |                                                                             |

|---------------------------------|---------|--------------------|---------------|--------------------|------|-----------------------------------------------------------------------------|

| Parameter                       | Symbol  | Min                | Limits<br>Typ | Max                | Unit | Condition                                                                   |

| Standby Current                 | IST     | -                  | 0.5           | 1.0                | mA   | VEN=0V                                                                      |

| Bias Current                    | ICC     | -                  | 2             | 4                  | mA   | VEN=3V                                                                      |

| [Enable]                        |         |                    |               |                    |      |                                                                             |

| High Level Enable Input Voltage | VENHIGH | 2.3                | -             | 5.5                | V    |                                                                             |

| Low Level Enable Input Voltage  | VENLOW  | -0.3               | -             | 0.8                | V    |                                                                             |

| Enable Pin Input Current        | IEN     | -                  | 7             | 10                 | μA   | VEN=3V                                                                      |

| [Termination]                   |         |                    |               | 11                 |      |                                                                             |

| Termination Output Voltage 1    | VTT1    | VREF-30m           | VREF          | VREF+30m           | V    | ITT=-1.0A to 1.0A<br>Ta=0°C to 105°C *6                                     |

| Termination Output Voltage 2    | VTT2    | VREF-30m           | VREF          | VREF+30m           | V    | VCC=5V, VDDQ=2.5V<br>VTT_IN=2.5V<br>ITT=-1.0A to 1.0A<br>Ta=0°C to 105°C *6 |

| Source Current                  | ITT+    | 1.0                | -             | -                  | Α    |                                                                             |

| Sink Current                    | ITT-    | -                  | -             | -1.0               | Α    |                                                                             |

| Load Regulation                 | ∠VTT    | -                  | -             | 50                 | mV   | ITT=-1.0A to 1.0A                                                           |

| Line Regulation                 | Reg.I   | -                  | 20            | 40                 | mV   |                                                                             |

| Upper Side ON Resistance 1      | HRON1   | -                  | 0.45          | 0.9                | Ω    |                                                                             |

| Lower Side ON Resistance 1      | LRON1   | -                  | 0.45          | 0.9                | Ω    |                                                                             |

| Upper Side ON Resistance 2      | HRON2   | ı                  | 0.4           | 0.8                | Ω    | VCC=5V, VDDQ=2.5V<br>VTT_IN=2.5V                                            |

| Lower Side ON Resistance 2      | LRON2   | ı                  | 0.4           | 0.8                | Ω    | VCC=5V, VDDQ=2.5V<br>VTT_IN=2.5V                                            |

| [Reference Voltage Input]       |         |                    |               |                    |      |                                                                             |

| Input Impedance                 | ZVDDQ   | 70                 | 100           | 130                | kΩ   |                                                                             |

| Output Voltage 1                | VREF1   | 1/2 × VDDQ<br>-18m | 1/2×VDDQ      | 1/2 × VDDQ<br>+18m | V    | IREF=-5mA to 5mA<br>Ta=0°C to 105°C <sup>*6</sup>                           |

| Output Voltage 2                | VREF2   | 1/2 × VDDQ<br>-40m | 1/2×VDDQ      | 1/2 × VDDQ<br>+40m | V    | IREF=-10mA to 10mA<br>Ta=0°C to 105°C*6                                     |

| Output Voltage 3                | VREF3   | 1/2 × VDDQ<br>-25m | 1/2×VDDQ      | 1/2 × VDDQ<br>+25m | ٧    | VCC=5V, VDDQ=2.5V<br>VTT_IN=2.5V<br>IREF=-5mA to 5mA<br>Ta=0°C to 105°C *6  |

| Output Voltage 4                | VREF4   | 1/2 × VDDQ<br>-40m | 1/2×VDDQ      | 1/2 × VDDQ<br>+40m | V    | VCC=5V, VDDQ=2.5V<br>VTT_IN=2.5V<br>ITT=-10mA to 10mA<br>Ta=0°C to 105°C *6 |

| [UVLO]                          |         |                    |               |                    |      |                                                                             |

| Threshold Voltage               | VUVLO   | 2.40               | 2.55          | 2.70               | ٧    | VCC : sweep up                                                              |

| Hysteresis Voltage              | ⊿VUVLO  | 100                | 160           | 220                | mV   | VCC : sweep down                                                            |

<sup>\*6</sup> Design Guarantee

# ● Reference Data

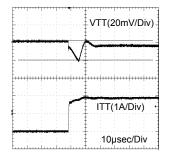

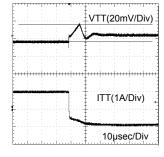

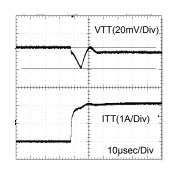

Fig.1 DDR1 (-1A→1A)

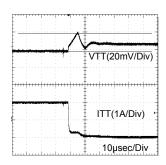

Fig.4 DDR2 (1A→-1A)

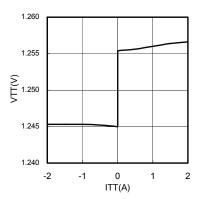

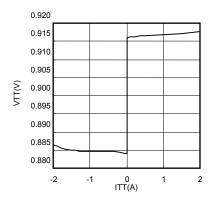

Fig.7 ITT-VTT (DDR1)

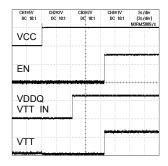

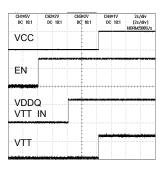

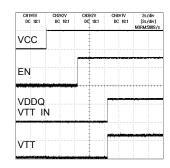

Fig.10 Input Sequence 2

Fig.2 DDR1 (1A→-1A)

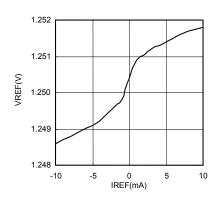

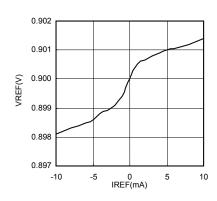

Fig.5 IREF-VREF (DDR1)

Fig.8 ITT-VTT (DDR2)

Fig.11 Input Sequence 3

Fig.3 DDR2 (-1A→1A)

Fig.6 IREF-VREF (DDR2)

Fig.9 Input Sequence 1

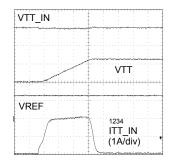

Fig.12 Start up Wave Form

# ●Block Diagram

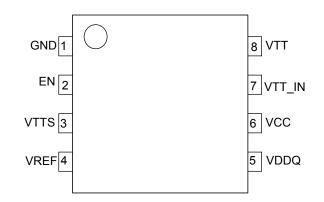

# **●PIN** Configration

# ●PIN Function

| PIN No. | PIN Name | PIN Function                         |

|---------|----------|--------------------------------------|

| 1       | GND      | GND Pin                              |

| 2       | EN       | Enable Input Pin                     |

| 3       | VTTS     | Detector Pin for Termination Voltage |

| 4       | VREF     | Reference Voltage Output Pin         |

| 5       | VDDQ     | Reference Voltage Input Pin          |

| 6       | VCC      | VCC Pin                              |

| 7       | VTT_IN   | Termination Input Pin                |

| 8       | VTT      | Termination Output Pin               |

| Bottom  | FIN      | Substraight (Conntct to GND)         |

#### Description of operations

#### VCC

In BD3538F/HFN, an independent power input pin is provided for an internal circuit operation of the IC. This is used to drive the amplifier circuit of the IC, and its maximum current rating is 4 mA. The power supply voltage is 3.3 to 5.5 volts. It is recommended to connect a bypass capacitor of 1  $\mu$ F or so to VCC.

#### VDDQ

Reference input pin for the output voltage, that may be used to satisfy the JEDEC requirement for DDR-SDRAM (VTT = 1/2VDDQ) by dividing the voltage inside the IC with two 50 k $\Omega$  voltage-divider resistors

For BD3538F/HFN, care must be taken to an input noise to VDDQ pin because this IC also cuts such noise input into half and provides it with the voltage output divided in half. Such noise may be reduced with an RC filter consisting of such resistance and capacitance (220  $\Omega$  and 2.2  $\mu$ F, for instance) that may not give significant effect to voltage dividing inside the IC.

#### · VTT IN

VTT\_IN is a power supply input pin for VTT output. Voltage in the range between 1.0 and 5.5 volts may be supplied to this VTT\_IN terminal, but care must be taken to the current limitation due to on-resistance of the IC and the change in allowable loss due to input/output voltage difference.

Generally, the following voltages are supplied:

DDR I VTT\_IN=2.5VDDRII VTT\_IN=1.8VDDRIII VTT\_IN=1.5V

Higher impedance of the voltage input at VTT\_IN may result in oscillation or degradation in ripple rejection, which must be noted. To VTT\_IN terminal, it is recommended to use a 10 µF capacitor characterized with less change in capacitance. But it may depend on the characteristics of the power supply input and the impedance of the pc board wiring, which must be carefully checked before use.

#### VREF

In BD3538F/HFN, a reference voltage output pin independent from VTT output is given to provide a reference input for a memory controller and a DRAM. Even if EN pin turns to "Low" level, VREF output is kept unchanged, compatible with "Self Refresh" state of DRAM. The maximum current capability of VREF is 20 mA, and a suitable capacitor is needed to stabilize the output voltage. It is recommended to use a combination of a 1.0 to 2.2  $\mu$ F ceramic capacitor characterized with less change in capacitance and a 0.5 to 2.2  $\Omega$  phase compensator resistor, or a 10 $\mu$ F ceramic or tantalum capacitor instead. For an application where VREF current is low, a capacitor of lower capacitance may be used. If VREF current is 1 mA or less, it is possible to secure a phase margin with a ceramic capacitor of 1  $\mu$ F more or less.

#### VTTS

An independent pin provided to improve load regulation of VTT output. In case that longer wiring is needed to the load at VTT output, connecting VTTS from the load side may improve the load regulation.

#### VTT

A DDR memory termination output pin. BD3538F/HFN has a sink/source current capability of ±1.0A respectively. The output voltage tracks the voltage divided in half at VDDQ pin. VTT output is turned to OFF when VCC UVLO or thermal shutdown protector is activated with EN pin level turned to "Low". Do not fail to connect a capacitor to VTT output pin for a loop gain phase compensation and a reduction in output voltage variation in the event of sudden change in load. Insufficient capacitance may cause an oscillation. High ESR (Equivalent Series Resistance) of the capacitor may result in increase in output voltage variation in the event of sudden change in load. It is recommended to use a 220 µF functional polymer capacitor (OS-CON, POS-CAP, NEO-CAP), though it depends on ambient temperature and other conditions. A low ESR ceramic capacitor may reduce a loop gain phase margin and may cause an oscillation, which may be improved by connecting a resistor in series with the capacitor.

#### • EN

With an input of 2.3 volts or higher, the level at EN pin turns to "High" to provide VTT output. If the input is lowered to 0.8 volts or less, the level at EN pin turns to "Low" and VTT status turns to Hi-Z. But if VCC and VDDQ are established, VREF output is maintained.

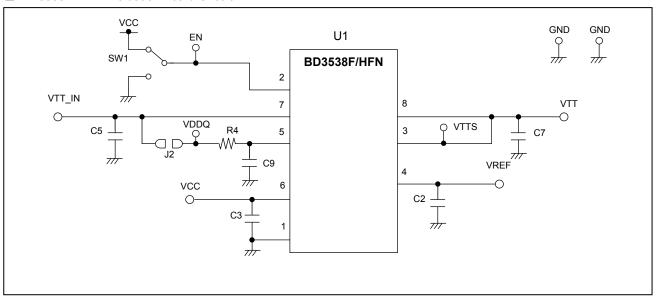

# ●Evaluation Board

# ■ BD3538F/HFN Evaluation Board Circuit

# ■ BD3538F/HFN Evaluation Board Application Components

| BB3550171111 Evaluation Board Application Components |       |         |              |  |  |  |

|------------------------------------------------------|-------|---------|--------------|--|--|--|

| Part No                                              | Value | Company | Parts Name   |  |  |  |

| U1                                                   | -     | ROHM    | BD3538F/HFN  |  |  |  |

| R4                                                   | 220Ω  | ROHM    | MCR032200    |  |  |  |

| J1                                                   | 0Ω    | -       | -            |  |  |  |

| C2                                                   | 10µF  | MURATA  | GRM21 Series |  |  |  |

| C3                                                   | 1µF   | MURATA  | GRM18 Series |  |  |  |

| C5                                                   | 10µF  | MURATA  | GRM21 Series |  |  |  |

| C7                                                   | 220µF | SANYO   | 2R5TPE220MF  |  |  |  |

| C9                                                   | 2.2µF | MURATA  | GRM18 Series |  |  |  |

#### Notes for use

#### 1. Absolute maximum ratings

For the present product, thoroughgoing quality control is carried out, but in the event that applied voltage, working temperature range, and other absolute maximum rating are exceeded, the present product may be destroyed. Because it is unable to identify the short mode, open mode, etc., if any special mode is assumed, which exceeds the absolute maximum rating, physical safety measures are requested to be taken, such as fuses, etc.

#### 2. GND potential

Bring the GND terminal potential to the minimum potential in any operating condition.

# 3. Thermal design

Consider allowable loss (Pd) under actual working condition and carry out thermal design with sufficient margin provided.

# 4. Terminal-to-terminal short-circuit and erroneous mounting

When the present IC is mounted to a printed circuit board, take utmost care to direction of IC and displacement. In the event that the IC is mounted erroneously, IC may be destroyed. In the event of short-circuit caused by foreign matter that enters in a clearance between outputs or output and power-GND, the IC may be destroyed.

# 5. Operation in strong electromagnetic field

The use of the present IC in the strong electromagnetic field may result in maloperation, to which care must be taken.

#### 6. Built-in thermal shutdown protection circuit

The present IC incorporates a thermal shutdown protection circuit (TSD circuit). The working temperature is 175°C (standard value) and has a -15°C (standard value) hysteresis width. When the IC chip temperature rises and the TSD circuit operates, the output terminal is brought to the OFF state. The built-in thermal shutdown protection circuit (TSD circuit) is first and foremost intended for interrupt IC from thermal runaway, and is not intended to protect and warrant the IC. Consequently, never attempt to continuously use the IC after this circuit is activated or to use the circuit with the activation of the circuit premised.

# 7. Capacitor across output and GND

In the event a large capacitor is connected across output and GND, when Vcc and VIN are short-circuited with 0V or GND for some kind of reasons, current charged in the capacitor flows into the output and may destroy the IC. Use a capacitor smaller than 1000  $\mu$ F between output and GND.

# 8. Inspection by set substrate

In the event a capacitor is connected to a pin with low impedance at the time of inspection with a set substrate, there is a fear of applying stress to the IC. Therefore, be sure to discharge electricity for every process. As electrostatic measures, provide grounding in the assembly process, and take utmost care in transportation and storage. Furthermore, when the set substrate is connected to a jig in the inspection process, be sure to turn OFF power supply to connect the jig and be sure to turn OFF power supply to remove the jig.

# 9. Inputs to IC terminals

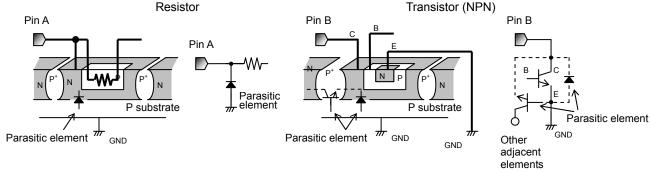

This device is a monolithic IC with P<sup>+</sup> isolation between P-substrate and each element as illustrated below. This P-layer and the N-layer of each element form a PN junction which works as:

- a diode if the electric potentials at the terminals satisfy the following relationship; GND>Terminal A>Terminal B, or

- a parasitic transistor if the electric potentials at the terminals satisfy the following relationship; Terminal B>GND Terminal A. The structure of the IC inevitably forms parasitic elements, the activation of which may cause interference among circuits, and/or malfunctions contributing to breakdown. It is therefore requested to take care not to use the device in such manner that the voltage lower than GND (at P-substrate) may be applied to the input terminal, which may result in activation of parasitic elements.

#### 10. GND wiring pattern

When both a small-signal GND and high current GND are present, single-point grounding (at the set standard point) is recommended, in order to separate the small-signal and high current patterns, and to be sure the voltage change stemming from the wiring resistance and high current does not cause any voltage change in the small-signal GND. In the same way, care must be taken to avoid wiring pattern fluctuations in any connected external component GND.

# 11. Output capacitor (C1)

Do not fail to connect a output capacitor to VREF output terminal for stabilization of output voltage. The capacitor connected to VREF output terminal works as a loop gain phase compensator. Insufficient capacitance may cause an oscillation. It is recommended to use a low temperature coefficient 1-10 µF ceramic capacitor, though it depends on ambient temperature and load conditions. It is therefore requested to carefully check under the actual temperature and load conditions to be applied.

# 12. Output capacitor (C4)

Do not fail to connect a capacitor to VTT output pin for stabilization of output voltage. This output capacitor works as a loop gain phase compensator and an output voltage variation reducer in the event of sudden change in load. Insufficient capacitance may cause an oscillation. And if the equivalent series resistance (ESR) of this capacitor is high, the variation in output voltage increases in the event of sudden change in load. It is recommended to use a 47-220 µF functional polymer capacitor, though it depends on ambient temperature and load conditions. Using a low ESR ceramic capacitor may reduce a loop gain phase margin and cause an oscillation, which may be improved by connecting a resistor in series with the capacitor. It is therefore requested to carefully check under the actual temperature and load conditions to be applied.

# 13. Input capacitors (C2 and C3)

These input capacitors are used to reduce the output impedance of power supply to be connected to the input terminals (VCC and VTT\_IN). Increase in the power supply output impedance may result in oscillation or degradation in ripple rejecting characteristics. It is recommended to use a low temperature coefficient 1µF (for VCC) and 10µF (for VTT\_IN) capacitor, but it depends on the characteristics of the power supply input, and the capacitance and impedance of the pc board wiring pattern. It is therefore requested to carefully check under the actual temperature and load conditions to be applied.

# 14. Input terminals (VCC, VDDQ, VTT\_IN and EN)

VCC, VDDQ, VTT\_IN and EN terminals of this IC are made up independent one another. To VCC terminal, the UVLO function is provided for malfunction protection. Irrespective of the input order of the inputs terminals, VTT output is activated to provide the output voltage when UVLO and EN voltages reach the threshold voltage while VREF output is activated when UVLO voltage reaches the threshold. If VDDQ and VTT\_IN terminals have equal potential and common impedance, any change in current at VTT\_IN terminal may result in variation of VTT\_IN voltage, which affects VDDQ terminal and may cause variation in the output voltage. It is therefore required to perform wiring in such manner that VDDQ and VTT\_IN terminals may not have common impedance. If impossible, take appropriate corrective measures including suitable CR filter to be inserted between VDDQ and VTT\_IN terminals.

#### 15. VTTS terminal

A terminal used to improve load regulation of VTT output. Connection with VTT terminal must be done not to have common impedance with high current line, which may offer better load regulation of VTT output.

# 16. Operating range

Within the operating range, the operation and function of the circuits are generally guaranteed at an ambient temperature within the range specified. The values specified for electrical characteristics may not be guaranteed, but drastic change may not occur to such characteristics within the operating range.

#### 17. Allowable loss Pd

For the allowable loss, the thermal derating characteristics are shown in the Exhibit, which should be used as a guide. Any uses that exceed the allowable loss may result in degradation in the functions inherent to IC including a decrease in current capability due to chip temperature increase. Use within the allowable loss.

# 18. Built-in thermal shutdown protection circuit

Thermal shutdown protection circuit is built-in to prevent thermal breakdown. Turns VTT output to OFF when the thermal shutdown protection circuit activates. This thermal shutdown protection circuit is originally intended to protect the IC itself. It is therefore requested to conduct a thermal design not to exceed the temperature under which the thermal shutdown protection circuit can work.

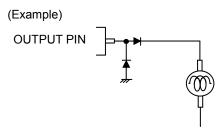

- 19. The use in the strong electromagnetic field may sometimes cause malfunction, to which care must be taken. In the event that load containing a large inductance component is connected to the output terminal, and generation of back-EMF at the start-up and when output is turned OFF is assumed, it is requested to insert a protection diode.

- 20. In the event that load containing a large inductance component is connected to (Example) the output terminal, and generation of back-EMF at the start-up and when output is turned OFF is assumed, it is requested to insert a protection diode.

- 21. We are certain that examples of applied circuit diagrams are recommendable, but you are requested to thoroughly confirm the characteristics before using the IC.In addition, when the IC is used with the external circuit changed, decide the IC with sufficient margin provided while consideration is being given not only to static characteristics but also variations of external parts and our IC including transient characteristics.

#### Heat Loss

Thermal design must be conducted with the operation under the conditions listed below (which are the guaranteed temperature range requiring consideration on appropriate margins etc.):

- 1. Ambient temperature Ta: 100°C or lower

- 2. Chip junction temperature Tj: 150°C or lower

The chip junction temperature Tj can be considered as follows. See Page 2/10 for θja.

For the package has FIN at the bottoms of IC, package power depends on the connected copper foil area. Be sure to keep the board surface area or release the heat with setting enough through holes to inside pattern.

Most of heat loss in BD3538F/HFN occurs at the output N-channel FET. The power lost is determined by multiplying the voltage between VIN and Vo by the output current. As this IC employs the power PKG, the thermal derating characteristics significantly depends on the pc board conditions. When designing, care must be taken to the size of a pc board to be used.

Power dissipation (W) =  $\{Input \ voltage \ (V_{TT} \ IN) - Output \ voltage \ (V_{TT} = 1/2VDDQ)\} \times Io \ (Ave)$

If VTT\_IN = 1.8 volts, VDDQ=1.8 volts, and Io (Ave)=0.5 A, for instance, the power dissipation is determined as follows: Power dissipation (W) =  $\{1.8 \text{ (V)} - 0.9 \text{ (V)}\} \times 0.5 \text{ (A)} = 0.4 \text{ (W)}$

# Power Dissipation

(1) 70mm × 70mm × 1.6mm Glass-epoxy PCB  $\theta$  j-c=181°C/W (2) With no heat sink  $\theta$  j-a=222°C/W

Ambient Temperature: Ta(°C)

- (1) 1 layer (copper foil density : 65%)  $\theta$  ja=71.4°C/W

- (2) 1 layer (copper foil density : 7%)  $\theta$  ja=92.4°C/W

- (3) 1 layer (copper foil density : 0.2%)  $\theta$  ja=198.4°C/W

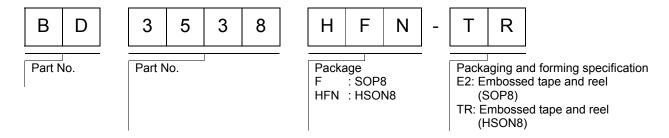

# Ordering part number

# SOP8

# **HSON8**

# Notes

No copying or reproduction of this document, in part or in whole, is permitted without the consent of ROHM Co.,Ltd.

The content specified herein is subject to change for improvement without notice.

The content specified herein is for the purpose of introducing ROHM's products (hereinafter "Products"). If you wish to use any such Product, please be sure to refer to the specifications, which can be obtained from ROHM upon request.

Examples of application circuits, circuit constants and any other information contained herein illustrate the standard usage and operations of the Products. The peripheral conditions must be taken into account when designing circuits for mass production.

Great care was taken in ensuring the accuracy of the information specified in this document. However, should you incur any damage arising from any inaccuracy or misprint of such information, ROHM shall bear no responsibility for such damage.

The technical information specified herein is intended only to show the typical functions of and examples of application circuits for the Products. ROHM does not grant you, explicitly or implicitly, any license to use or exercise intellectual property or other rights held by ROHM and other parties. ROHM shall bear no responsibility whatsoever for any dispute arising from the use of such technical information.

The Products specified in this document are intended to be used with general-use electronic equipment or devices (such as audio visual equipment, office-automation equipment, communication devices, electronic appliances and amusement devices).

The Products specified in this document are not designed to be radiation tolerant.

While ROHM always makes efforts to enhance the quality and reliability of its Products, a Product may fail or malfunction for a variety of reasons.

Please be sure to implement in your equipment using the Products safety measures to guard against the possibility of physical injury, fire or any other damage caused in the event of the failure of any Product, such as derating, redundancy, fire control and fail-safe designs. ROHM shall bear no responsibility whatsoever for your use of any Product outside of the prescribed scope or not in accordance with the instruction manual.

The Products are not designed or manufactured to be used with any equipment, device or system which requires an extremely high level of reliability the failure or malfunction of which may result in a direct threat to human life or create a risk of human injury (such as a medical instrument, transportation equipment, aerospace machinery, nuclear-reactor controller, fuel-controller or other safety device). ROHM shall bear no responsibility in any way for use of any of the Products for the above special purposes. If a Product is intended to be used for any such special purpose, please contact a ROHM sales representative before purchasing.

If you intend to export or ship overseas any Product or technology specified herein that may be controlled under the Foreign Exchange and the Foreign Trade Law, you will be required to obtain a license or permit under the Law.

Thank you for your accessing to ROHM product informations. More detail product informations and catalogs are available, please contact us.

# ROHM Customer Support System

http://www.rohm.com/contact/