# Z89175 Z89176 (ROMLESS)

# **VOICE PROCESSING CONTROLLERS**

#### **FEATURES**

| Device | ROM<br>(KB) | RAM*<br>(Bytes) | I/O<br>Lines | Voltage<br>Range |

|--------|-------------|-----------------|--------------|------------------|

| Z89175 | 24          | 256             | 47           | 4.5V to 5.5V     |

| Z89176 | -           | 256             | 31           | 4.5V to 5.5V     |

Note: \*General-Purpose

- Watch-Dog Timer and Power-On Reset

- Improved Low Power Stop Mode

- On-Chip Oscillator which Accepts a Crystal or External Clock Drive

- Improved Global Power-Down Mode

- Low Power Consumption 200 mW (typical)

- Two Comparators

- RAM and ROM Protect

- On-Board Oscillator for 32.768 kHz Real-Time Clock

- Clock Speeds of 20.48 or 29.49 MHz

- 16-Bit Digital Signal Processor (DSP)

- 8K Word DSP Program ROM

- 512 Words On-Chip DSP RAM

- 8-Bit A/D Converter with up to 16 kHz Sample Rate

- 10-Bit PWM D/A Converter

- Six Vectored, Prioritized Z8 Interrupts

- Three Vectored, Prioritized DSP Interrupts

- Two DSP Timers to Support Different A/D and D/A Sampling Rates

- IBM<sup>®</sup> PC-Based Development Tools

- Developer's Toolbox for T.A.M. Applications

#### **GENERAL DESCRIPTION**

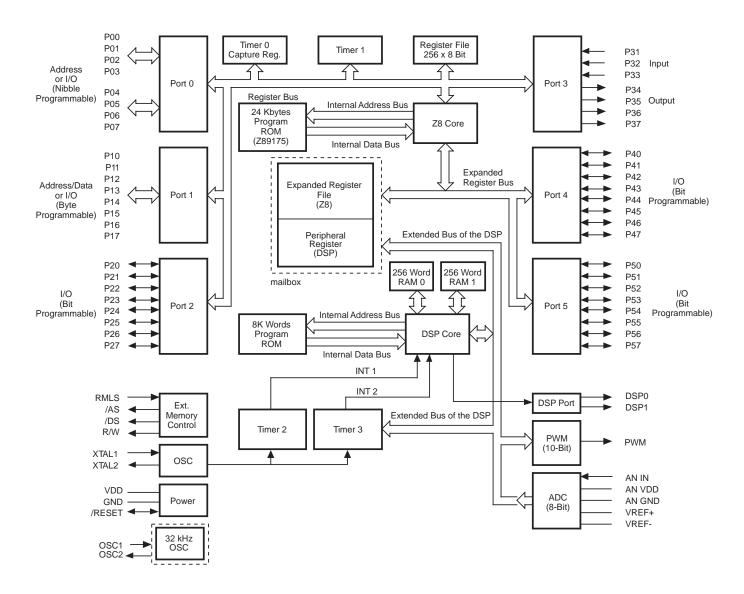

The Z89175/176 is a fully integrated, dual processor controller designed for voice processing applications. The I/O control processor is a Z8® with 24 KB of program memory, two 8-bit counter/timers, and up to 47 I/O pins. The DSP is a 16-bit processor with a 24-bit ALU and accumulator, 512x16 bits of RAM, single cycle instructions, and 8K words of program ROM. The chip also contains a half-flash 8-bit A/D converter with up to a 16 kHz sample rate and a 10-bit PWM D/A converter. The sampling rates for the converters are programmable. The precision of the 8-bit A/D can be extended by resampling the data at a lower rate in software. The Z8 and DSP processors are coupled by mailbox registers and an interrupt system. DSP or Z8 programs can be directed by events in each other's domain.

The Z89176 is the ROMless version of the Z89175. However, the on-chip DSP is not ROMless.

**Notes:** All Signals with a preceding front slash, "/", are active Low, e.g., B//W (WORD is active Low); /B/W (BYTE is active Low, only).

Power connections follow conventional descriptions below:

| Connection | Circuit         | Device   |

|------------|-----------------|----------|

| Power      | V <sub>CC</sub> | $V_{DD}$ |

| Ground     | GND             | $V_{SS}$ |

### **GENERAL DESCRIPTION** (Continued)

#### **Z8 Core Processor**

The on-chip Z8 is Zilog's 8-bit microcontroller core with an Expanded Register File to allow access to register-mapped peripheral and I/O circuits. The Z8 offers a flexible I/O scheme, an efficient register and address space structure and a number of ancillary features which makes it ideally suited for high-volume processing, peripheral controllers and consumer applications.

For applications demanding powerful I/O capabilities, the Z89175 provides 47 pins dedicated to input and output. These I/O lines are grouped into six ports. Each port is configurable under software control to provide timing, status signals and parallel I/O with or without handshake.

Four basic memory resources for the Z8 are available to support a wide range of configurations: Program Memory, Register File, Data Memory, and Expanded Register File. The Z8 core processor is supported by an efficient register file that allows any of 256 on-board data and control registers to be either the source and/or the destination of almost any instruction. This unique architecture eliminates traditional microprocessor Accumulator bottlenecks and permits rapid content switching.

The Register File is composed of 236 bytes of general-purpose registers, four I/O port registers, and 15 control and status registers. The Expanded Register File consists of mailbox registers, WDT mode register, DSP Control register, Stop-Mode Recovery register, Port Configuration register, and the control and data registers for Port 4 and Port 5. Some of these registers are shared with the DSP.

To unburden the software from supporting real-time problems such as counting/timing and data communication, the Z8 offers two on-chip counter/timers with a large number of user-selectable modes.

Watch-Dog Timer and Stop-Mode Recovery features are software driven by setting specific bits in control registers.

STOP and HALT instructions support reduced power operation. The low-power Stop Mode allows parameter information to be stored in the register file if power fails. An external capacitor or battery will retain device memory and power the 32 kHz timer.

#### **DSP Coprocessor**

The DSP coprocessor is a second generation, 16-bit two's complement CMOS Digital Signal Processor (DSP). Most instructions, including multiply and accumulate, are accomplished in a single clock cycle. The processor contains two on-chip data RAM blocks of 256 words, a 8K word program ROM, 24-bit ALU, 16x16 multiplier, 24-bit Accumulator, shifter, six-level stack, three vectored interrupts and two inputs for conditional program jumps. Each RAM block contains a set of four pointers which can be incremented or decremented automatically to affect hardware looping without software overhead. The data RAMs can be simultaneously addressed and loaded to the multiplier for a true single-cycle scalar multiply.

Four external DSP registers are mapped into the expanded register file of the Z8. Communication between the Z8 and the DSP occurs through those common registers which form the mailbox registers.

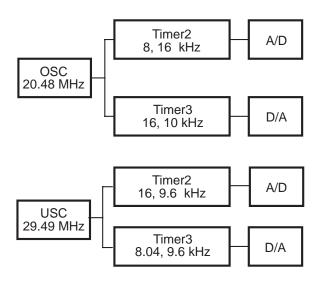

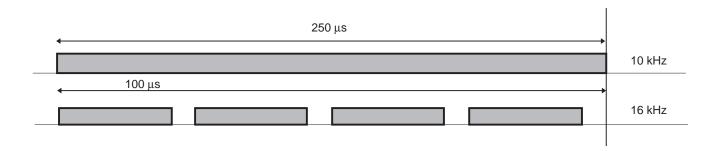

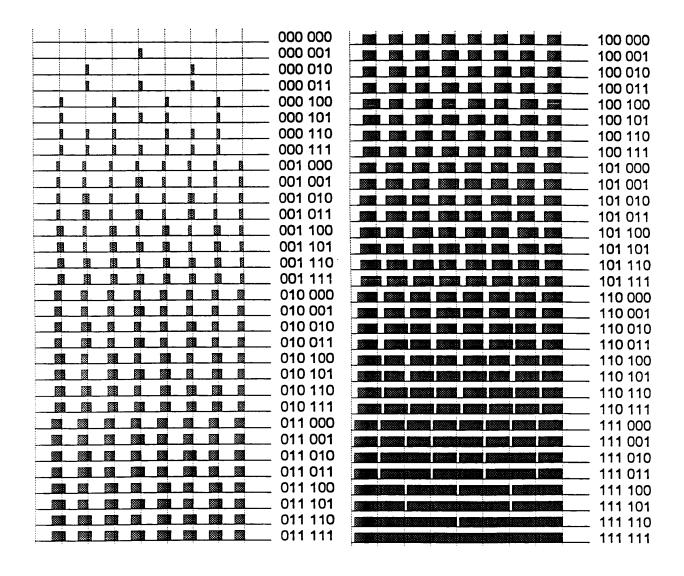

The analog output is generated by a 10-bit resolution Pulse Width Modulator. The PWM output is a digital signal with CMOS output levels. The output signal has a resolution of 1 in 1024 with a sampling rate of 16 kHz (XTAL = 20.48 MHz). The sampling rate can be changed under software control and can be set at 10 and 16 kHz. The dynamic range of the PWM is from 0 to 4V.

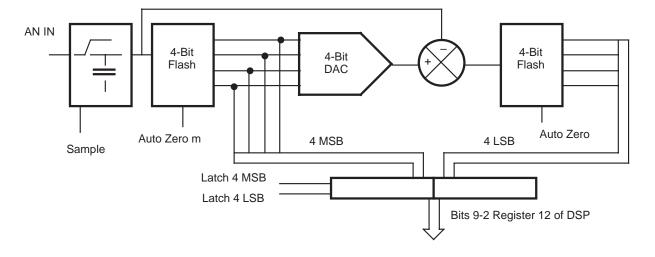

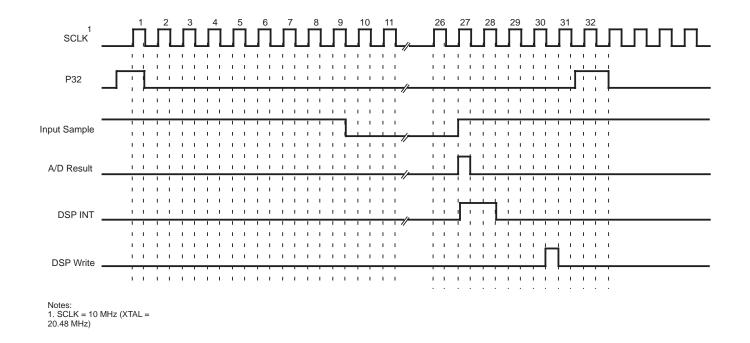

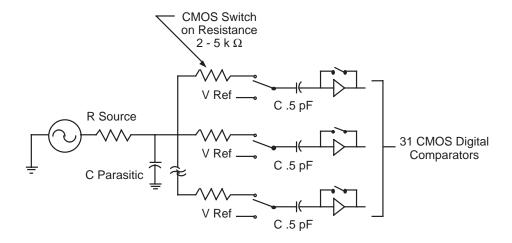

An 8-bit resolution half-flash A/D converter is provided. The conversion is conducted with a sampling frequency of 16 kHz. (XTAL = 20.48 MHz) in order to provide oversampling. The input signal is 4V peak to peak.

Two additional timers (Timer2 and Timer3) have been added to support different sampling rates for the A/D and D/A converters. These timers are free-running counters that divide the crystal frequency to the appropriate sampling of frequency. Two DSP I/O pins: DSP0, DSP1 are provided for application.

#### PIN DESCRIPTION

Figure 1. Z89175/176 Functional Block Diagram

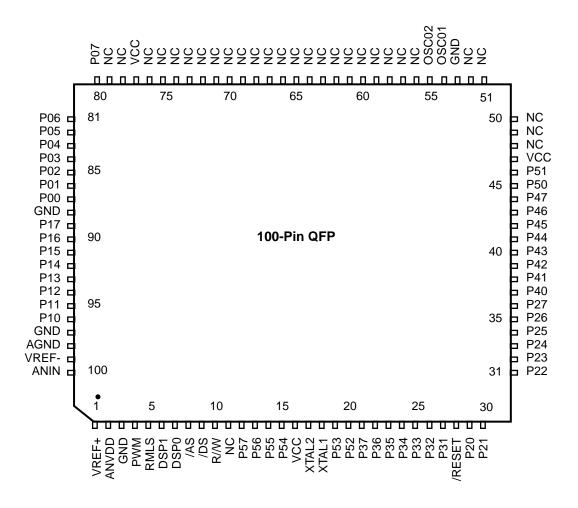

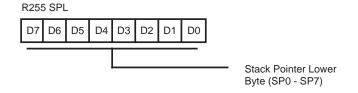

Figure 2. Z89175 100-Pin QFP Pin Configuration

Table 1. Z89175 100-Pin QFP Pin Identification

| I/O Port        | Pin           |              |                                     |

|-----------------|---------------|--------------|-------------------------------------|

| Symbol          | Number        | Direction    | Function                            |

| GND             | 3, 53, 88, 97 |              | Digital Ground                      |

| V <sub>CC</sub> | 16, 47, 77    |              | Digital V <sub>CC</sub> = +5V       |

| VREF+           | 1             | Input/Output | Analog Voltage Ref+                 |

| $ANV_DD$        | 2             |              | Analog V <sub>DD</sub>              |

| PWM             | 4             | Output       | PWM Output                          |

| RMLS            | 5             | Input        | Control Input                       |

| DSP1-0          | 6, 7          | Output       | DSP User Output 1, 0                |

| /AS             | 8             | Output       | Address Strobe                      |

| /DS             | 9             | Output       | Data Strobe                         |

| R//W            | 10            | Output       | Read/Write                          |

| NC              | 11            |              | No Connection                       |

| P57-P54         | 12-15         | Input/Output | Port 5 Bit 7-4                      |

| XTAL2           | 17            | Output       | Crystal Output (20.48 or 29.49 MHz) |

| XTAL1           | 18            | Input        | Crystal Input (20.48 or 29.49 MHz)  |

| P53-P52         | 19, 20        | Input/Output | Port 5 Bit 3-2                      |

| P37-P34         | 21-24         | Output       | Port 3 Bit 7-4                      |

| P33-P31         | 25-27         | Input        | Port 3 Bit 3-1                      |

| /RESET          | 28            | Input/Output | Reset                               |

| P20-P27         | 29-36         | Input/Output | Port 2, Bit 0-7                     |

| P40-P47         | 37-44         | Input/Output | Port 4, Bit 0-7                     |

| P50-P51         | 45, 46        | Input/Output | Port 5, Bit 0-1                     |

| NC              | 48-52         |              | No Connection                       |

| OSC1            | 54            | Input        | Crystal Input (32.768 kHz)          |

| OSC2            | 55            | Output       | Crystal Output (32.768 kHz)         |

| NC              | 56-76         |              | No Connection                       |

| NC              | 78, 79        |              | No Connection                       |

| P07-P00         | 80-87         | Input/Output | Port 0, Bit 7-0                     |

| P17-P10         | 89-96         | Input/Output | Port 1, Bit 7-0                     |

| ANGND           | 98            |              | Analog GND                          |

| VREF-           | 99            | Input        | Analog Voltage Ref-                 |

| ANIN            | 100           | Input        | Analog Input                        |

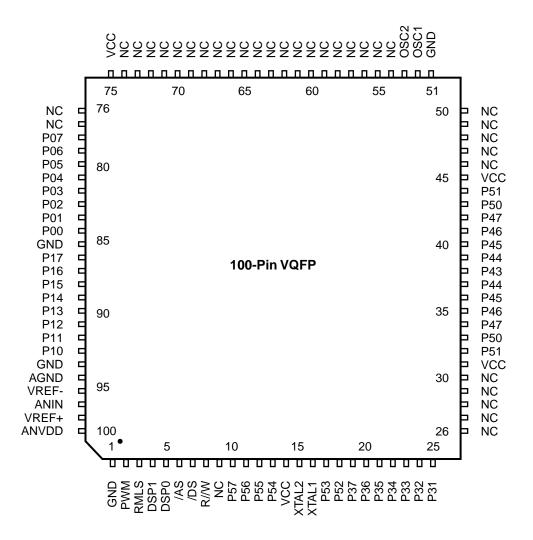

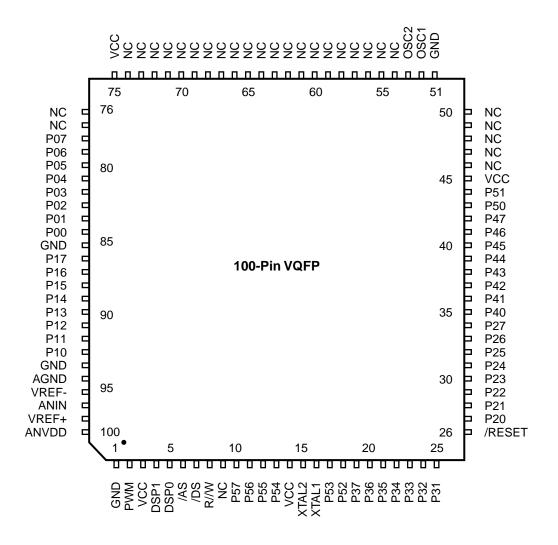

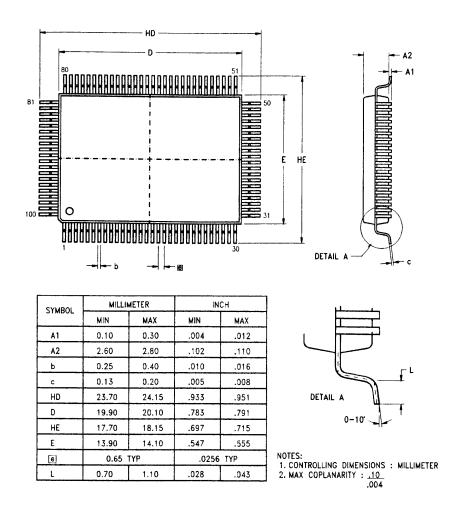

Figure 3. Z89175 100-Pin VQFP Pin Configuration

Table 2. Z89175 100-Pin VQFP Pin Identification

| I/O Port<br>Symbol | Pin<br>Number | Direction    | Symbol                              |

|--------------------|---------------|--------------|-------------------------------------|

| GND                | 1, 51, 86, 95 |              | Digital Ground                      |

| V <sub>CC</sub>    | 14, 45, 75    |              | Digital VCC = +5V                   |

| VREF+              | 99            | Input/Output | Analog Voltage Ref+                 |

| ANV <sub>DD</sub>  | 100           |              | Analog VDD                          |

| PWM                | 2             | Output       | PWM Output                          |

| RMLS               | 3             | Input        | Control Input                       |

| DSP1-0             | 4, 5          | Output       | DSP User Output 1, 0                |

| /AS                | 6             | Output       | Address Strobe                      |

| /DS                | 7             | Output       | Data Strobe                         |

| R//W               | 8             | Output       | Read/Write                          |

| NC                 | 9             |              | No Connection                       |

| P57-P54            | 10-13         | Input/Output | Port 5 Bit 7-4                      |

| XTAL2              | 15            | Output       | Crystal Output (20.48 or 29.49 MHz) |

| XTAL1              | 16            | Input        | Crystal Input (20.48 or 29.49 MHz)  |

| P53-P52            | 17, 18        | Input/Output | Port 5 Bit 3-2                      |

| P37-P34            | 19-22         | Output       | Port 3 Bit 7-4                      |

| P33-P31            | 23-25         | Input        | Port 3 Bit 3-1                      |

| /RESET             | 26            | Input/Output | Reset                               |

| P20-P27            | 27-34         | Input/Output | Port 2, Bit 0-7                     |

| P40-P47            | 35-42         | Input/Output | Port 4, Bit 0-7                     |

| P50-P51            | 43, 44        | Input/Output | Port 5, Bit 0-1                     |

| NC                 | 46-50         |              | No Connection                       |

| OSC1               | 52            | Input        | Crystal Input (32.768 kHz)          |

| OSC2               | 53            | Output       | Crystal Output (32.768 kHz)         |

| NC                 | 54-74         |              | No Connection                       |

| NC                 | 76, 77        |              | No Connection                       |

| P07-P00            | 78-85         | Input/Output | Port 0, Bit 7-0                     |

| P17-P10            | 87-94         | Input/Output | Port 1, Bit 7-0                     |

| ANGND              | 96            |              | Analog GND                          |

| VREF-              | 97            | Input        | Analog Voltage Ref-                 |

| ANIN               | 98            | Input        | Analog Input                        |

|                    |               |              |                                     |

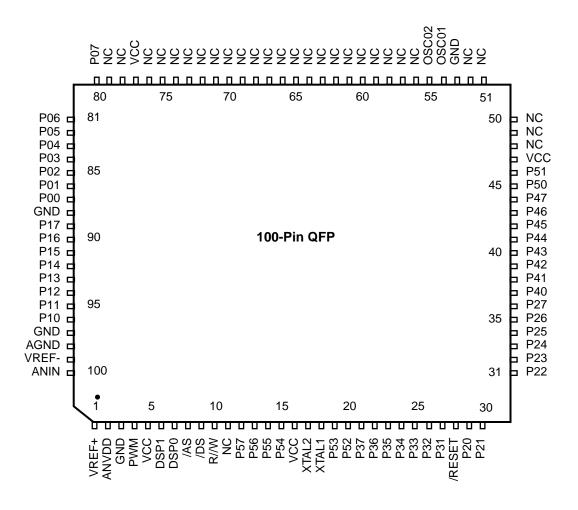

Figure 4. Z89176 100-Pin QFP Pin Configuration

Table 3. Z89176 100-Pin QFP Pin Identification

| I/O Port<br>Symbol  | Pin Number    | Direction    | Function                            |

|---------------------|---------------|--------------|-------------------------------------|

| GND                 | 3, 53, 88, 97 |              | Digital Ground                      |

| $\overline{V_{CC}}$ | 5, 16, 47, 77 |              | Digital V <sub>CC</sub> = +5V       |

| VREF+               | 1             | Input/Output | Analog Voltage Ref+                 |

| ANV <sub>DD</sub>   | 2             |              | Analog V <sub>DD</sub>              |

| PWM                 | 4             | Output       | PWM Output                          |

| DSP1-0              | 6, 7          | Output       | DSP User Output 1, 0                |

| /AS                 | 8             | Output       | Address Strobe                      |

| /DS                 | 9             | Output       | Data Strobe                         |

| R//W                | 10            | Output       | Read/Write                          |

| NC                  | 11            |              | No Connection                       |

| P57-P54             | 12-15         | Input/Output | Port 5 Bit 7-4                      |

| XTAL2               | 17            | Output       | Crystal Output (20.48 or 29.49 MHz) |

| XTAL1               | 18            | Input        | Crystal Input (20.48 or 29.49 MHz)  |

| P53-P52             | 19, 20        | Input/Output | Port 5 Bit 3-2                      |

| P37-P34             | 21-24         | Output       | Port 3 Bit 7-4                      |

| P33-P31             | 25-27         | Input        | Port 3 Bit 3-1                      |

| /RESET              | 28            | Input/Output | Reset                               |

| P20-P27             | 29-36         | Input/Output | Port 2, Bit 0-7                     |

| P40-P47             | 37-44         | Input/Output | Port 4, Bit 0-7                     |

| P50-P51             | 45, 46        | Input/Output | Port 5, Bit 0-1                     |

| NC                  | 48-52         |              | No Connection                       |

| OSC1                | 54            | Input        | Crystal Input (32.768 kHz)          |

| OSC2                | 55            | Output       | Crystal Output (32.768 kHz)         |

| NC                  | 56-76         |              | No Connection                       |

| NC                  | 78-79         |              | No Connection                       |

| P07-P00             | 80-87         | Input/Output | Port 0, Bit 7-0                     |

| P17-P10             | 89-96         | Input/Output | Port 1, Bit 7-0                     |

| ANGND               | 98            |              | Analog GND                          |

| VREF-               | 99            | Input        | Analog Voltage Ref-                 |

| ANIN                | 100           | Input        | Analog Input                        |

|                     |               |              | ·                                   |

Figure 5. Z89176 100-Pin VQFP Pin Configuration

Table 4. Z89176 100-Pin VQFP Pin Identification

| I/O Port<br>Symbol  | Pin Number    | Direction    | Function                           |

|---------------------|---------------|--------------|------------------------------------|

| GND                 | 1, 51, 86, 95 |              | Digital Ground                     |

| $\overline{V_{CC}}$ | 3, 14, 45, 75 |              | Digital V <sub>CC</sub> = +5V      |

| VREF+               | 99            | Input/Output | Analog Voltage Ref+                |

| ANV <sub>DD</sub>   | 100           |              | Analog VDD                         |

| PWM                 | 2             | Output       | PWM Output                         |

| DSP1-0              | 4, 5          | Output       | DSP User Output 1, 0               |

| /AS                 | 6             | Output       | Address Strobe                     |

| /DS                 | 7             | Output       | Data Strobe                        |

| R//W                | 8             | Output       | Read/Write                         |

| NC                  | 9             |              | No Connection                      |

| P57-P54             | 10-13         | Input/Output | Port 5 Bit 7-4                     |

| XTAL2               | 15            | Output       | Crystal Output (20.48 or 29.49 MHz |

| XTAL1               | 16            | Input        | Crystal Input (20.48 or 29.49 MHz) |

| P53-P52             | 17, 18        | Input/Output | Port 5 Bit 3-2                     |

| P37-P34             | 19-22         | Output       | Port 3 Bit 7-4                     |

| P33-P31             | 23-25         | Input        | Port 3 Bit 3-1                     |

| /RESET              | 26            | Input/Output | Reset                              |

| P20-P27             | 27-34         | Input/Output | Port 2, Bit 0-7                    |

| P40-P47             | 35-42         | Input/Output | Port 4, Bit 0-7                    |

| P50-P51             | 43, 44        | Input/Output | Port 5, Bit 0-1                    |

| NC                  | 46-50         |              | No Connection                      |

| OSC1                | 52            | Input        | Crystal Input (32.768 kHz)         |

| OSC2                | 53            | Output       | Crystal Output (32.768 kHz)        |

| NC                  | 54-74         |              | No Connection                      |

| NC                  | 76, 77        |              | No Connection                      |

| P07-P00             | 78-85         | Input/Output | Port 0, Bit 7-0                    |

| P17-P10             | 87-94         | Input/Output | Port 1, Bit 7-0                    |

| ANGND               | 96            |              | Analog GND                         |

| VREF-               | 97            | Input        | Analog Voltage Ref-                |

| ANIN                | 98            | Input        | Analog Input                       |

|                     |               |              | <del></del>                        |

#### **ABSOLUTE MAXIMUM RATINGS**

| Sym              | Description               | Min  | Max   | Units |

|------------------|---------------------------|------|-------|-------|

| V <sub>CC</sub>  | Supply<br>Voltage (*)     | -0.3 | +7.0  | V     |

| T <sub>STG</sub> | Storage Temp              | –65° | +150° | С     |

| T <sub>A</sub>   | Oper.<br>Ambient<br>Temp. |      | †     | С     |

Notes:

Stresses greater than those listed under Absolute Maximum Ratings can cause permanent damage to the device. This is a stress rating only; operation of the device at any condition above those indicated in the operational sections of these specifications is not implied. Exposure to absolute maximum rating conditions for an extended period can affect device reliability.

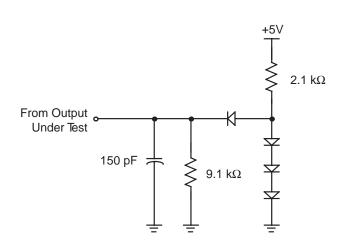

#### STANDARD TEST CONDITIONS

The characteristics listed below apply for standard test conditions as noted. All voltages are referenced to GND. Positive current flows into the referenced pin (Figure 6).

Figure 6. Test Load Diagram

#### **CAPACITANCE**

$T_A = 25$ °C,  $V_{CC} = GND = 0V$ , f = 1.0 MHz, unmeasured pins returned to GND.

| Parameter          | Min | Max   |

|--------------------|-----|-------|

| Input capacitance  | 0   | 12 pF |

| Output capacitance | 0   | 12 pF |

| I/O capacitance    | 0   | 12 pF |

<sup>\*</sup>Voltage on all pins with respect to GND.

<sup>†</sup>See Ordering Information.

|                      |                             | $V_{CC}$ $T_A = 0^{\circ}C$ |                      | to +70°C             | Typical             |       |                                        |  |

|----------------------|-----------------------------|-----------------------------|----------------------|----------------------|---------------------|-------|----------------------------------------|--|

| Sym                  | Parameter                   | Note 1                      | Min                  | Max                  | @ 25°C              | Units | Conditions                             |  |

| I <sub>CC</sub>      | Supply Current              | 5.0V                        |                      | 65                   | 40                  | mA    |                                        |  |

| I <sub>CC1</sub>     | Halt Mode Current           | 5.0V                        |                      | 20                   | 6                   | mA    |                                        |  |

| I <sub>CC2</sub>     | Stop Mode Current           | 5.0V                        |                      | 20                   | 6                   | μΑ    | See Note 2                             |  |

| $\overline{V_{MAX}}$ | Max Input Voltage           | 5.0V                        |                      | 7                    |                     |       |                                        |  |

| V <sub>CH</sub>      | Clock Input High<br>Voltage | 5.0V                        | 0.9 V <sub>CC</sub>  | V <sub>CC</sub> +0.3 | 2.5                 | V     | Driven by External Clock Generator     |  |

| V <sub>CL</sub>      | Clock Input Low<br>Voltage  | 5.0V                        | GND -0.3             | 0.1 V <sub>CC</sub>  | 1.5                 | V     | Driven by External Clock Generator     |  |

| $\overline{V_{IH}}$  | Input High Voltage          | 5.0V                        | 0.7 V <sub>CC</sub>  | V <sub>CC</sub> +0.3 | 2.5                 | V     |                                        |  |

| $\overline{V_IL}$    | Input Low Voltage           | 5.0V                        | GND -0.3             | 0.2 V <sub>CC</sub>  | 1.5                 | V     |                                        |  |

| $\overline{V_{OH}}$  | Output High Voltage         | 5.0V                        | V <sub>CC</sub> -0.4 |                      | 4.8                 | V     | $I_{OH} = -2.0 \text{ mA}$             |  |

| $\overline{V_{OL1}}$ | Output Low Voltage          | 5.0V                        |                      | 0.4                  | 0.1                 | V     | $I_{OL} = +4.0 \text{ mA}$             |  |

| $\overline{V_{OL2}}$ | Output Low Voltage          | 5.0V                        |                      | 1.2                  | 0.3                 | V     | I <sub>OL</sub> = +12 mA, 3 Pin<br>Max |  |

| $\overline{V_{RH}}$  | Reset Input High<br>Voltage | 5.0V                        | .8 V <sub>CC</sub>   | V <sub>CC</sub>      | 2.1                 | V     |                                        |  |

| $V_{RI}$             | Reset Input Low<br>Voltage  | 5.0V                        | GND -0.3             |                      | 0.2 V <sub>CC</sub> | 1.7   |                                        |  |

| V <sub>OFFSET</sub>  | Comparator Input<br>Offset  | 5.0V                        |                      |                      | 25                  | 10    | mV                                     |  |

|                      | Voltage                     |                             |                      |                      |                     |       |                                        |  |

| I <sub>IL</sub>      | Input Leakage               | 5.0V                        | -10                  |                      | 10                  | 10    | μΑ                                     |  |

| I <sub>OL</sub>      | Output Leakage              | 5.0V                        | -10                  |                      | 10                  | 10    | μΑ                                     |  |

| I <sub>IR</sub>      | Reset Input Current         | 5.0V                        |                      |                      | -55                 | -30   | μΑ                                     |  |

#### Notes:

<sup>1. 5.0</sup>V ±0.5V

<sup>2.</sup> When a 32 kHz crystal is used, additional value must be added to the Stop Mode current ICC2. The sum will be 200  $\mu$ A/max, 150  $\mu$ A/typical.

Z89175 A/D Converter

| $T_A = 0^{\circ} C \text{ to } +70^{\circ}C$ |                               |          |     |       |       |                   |           |      |   |  |

|----------------------------------------------|-------------------------------|----------|-----|-------|-------|-------------------|-----------|------|---|--|

| Sym                                          | Parameter                     | $V_{DD}$ | Min | Max   | Units |                   | Condition | ons  |   |  |

| I <sub>IL</sub>                              | Input Leakage<br>Analog Input | 5.5V     |     | 1.00  | μΑ    | $ANV_DD$          | =         | 5.50 | ٧ |  |

|                                              |                               |          |     |       |       | V <sub>IN</sub>   | =         | 0.00 | ٧ |  |

|                                              |                               |          |     |       |       | $V_{REFH}$        | =         | 5.50 | ٧ |  |

|                                              |                               |          |     |       |       | $V_{REFL}$        | =         | 0.00 | ٧ |  |

| I <sub>IH</sub>                              | Input Leakage<br>Analog Input | 5.5V     |     | 2.00  | μΑ    | ANV <sub>DD</sub> | =         | 5.50 | V |  |

|                                              |                               |          |     |       |       | V <sub>IN</sub>   | =         | 5.50 | V |  |

|                                              |                               |          |     |       |       | $V_{REFH}$        | =         | 5.50 | V |  |

|                                              |                               |          |     |       |       | V <sub>REFL</sub> | =         | 0.00 | ٧ |  |

| I <sub>VREFH</sub>                           | Input Current                 | 5.5V     |     | 1.00  | mA    | V <sub>IN</sub>   | =         | 5.50 | \ |  |

|                                              |                               |          |     |       |       | V <sub>REFL</sub> | =         | 0.00 | \ |  |

|                                              |                               |          |     |       |       | $ANV_DD$          | =         | 5.50 | ٧ |  |

| I <sub>VREFL</sub>                           | Input Current                 | 5.5V     |     | 2     | μΑ    | V <sub>IN</sub>   | =         | 5.50 | \ |  |

|                                              |                               |          |     |       |       | V <sub>REFL</sub> | =         | 5.50 | V |  |

|                                              |                               |          |     |       |       | $ANV_DD$          | =         | 5.50 | V |  |

| $I_{VEFL}$                                   | Input Current                 | 5.5V     |     | -2.00 | mA    | V <sub>IN</sub>   | =         | 0.00 | V |  |

|                                              |                               |          |     |       |       | $V_{REFH}$        | =         | 5.50 | \ |  |

|                                              |                               |          |     |       |       | $ANV_DD$          | =         | 0.00 | ٧ |  |

| I <sub>VREFL</sub>                           | Input Current                 | 5.5V     |     | 2     | μΑ    | V <sub>IN</sub>   | =         | 0.00 | ٧ |  |

|                                              |                               |          |     |       |       | $V_{REFH}$        | =         | 5.50 | V |  |

|                                              |                               |          |     |       |       | $ANV_{DD}$        | =         | 5.50 | V |  |

### 21 Other Non-Regular I/O

|                   | $T_A = 0^{\circ} C \text{ to } +70^{\circ}C$     |          |      |      |       |                           |  |  |

|-------------------|--------------------------------------------------|----------|------|------|-------|---------------------------|--|--|

| Sym               | Parameter                                        | $V_{DD}$ | Min  | Max  | Units | Conditions                |  |  |

| I <sub>IRH</sub>  | Input Current ROMless Pin                        | 5.5V     |      | 6.00 | μΑ    | V <sub>IN</sub> = 5.50 V  |  |  |

| I <sub>IR1</sub>  | Input Current ROMless Pin                        | 5.5V     |      | 6.00 | μΑ    | $V_{IN} = 0.00 V$         |  |  |

| I <sub>IR</sub>   | Input Current ROMless Pin<br>During Reset Active | 5.5V     |      | 1.00 | mA    | V <sub>IN</sub> = 5.50 V  |  |  |

| I <sub>IHX2</sub> | Input Current<br>XTAL2 pin in STOP mode          | 5.5V     |      | 1.00 | μА    | $V_{IN} = 0.00 \text{ V}$ |  |  |

| I <sub>ILX2</sub> | Input Current<br>XTAL2 Pin in STOP mode          | 5.5V     |      | 1.00 | μА    | V <sub>IN</sub> = 5.50 V  |  |  |

| I <sub>IHX1</sub> | Input current<br>XTAL1 Pin                       | 5.5V     |      | 30   | μΑ    | $V_{IN} = 0.00 \text{ V}$ |  |  |

| I <sub>ILX1</sub> | Input Current<br>XTAL1 Pin                       | 5.5V     |      | 30   | μА    | V <sub>IN</sub> = 5.50 V  |  |  |

| $V_{OLXR}$        | Output Low<br>Voltage XTAL2 Reset Inactive       | 5.5V     |      | 1.20 | V     | I <sub>OL</sub> = 4.00 mA |  |  |

| V <sub>OLX</sub>  | Output Low<br>Voltage XTAL2 Reset Inactive       | 5.5V     |      | 0.60 | V     | I <sub>OL</sub> =1.00 mA  |  |  |

| V <sub>OHXR</sub> | Output High<br>Voltage XTAL2 Reset Inactive      | 5.5V     | 4.00 |      | V     | I <sub>OH</sub> = 4.00 mA |  |  |

| I <sub>VOHX</sub> | Output High<br>Voltage XTAL2 Reset Inactive      | 5.5V     | 4.00 |      | V     | I <sub>OH</sub> =1.00 mA  |  |  |

| I <sub>IH</sub>   | Input Current<br>P31, P32, P33                   | 5.5V     |      | 1.00 | μΑ    | V <sub>IN</sub> = 5.50 V  |  |  |

| I <sub>IL</sub>   | Input Current<br>P31, P32, P33                   | 5.5V     |      | 1.00 | μΑ    | $V_{IN} = 0.00 \text{ V}$ |  |  |

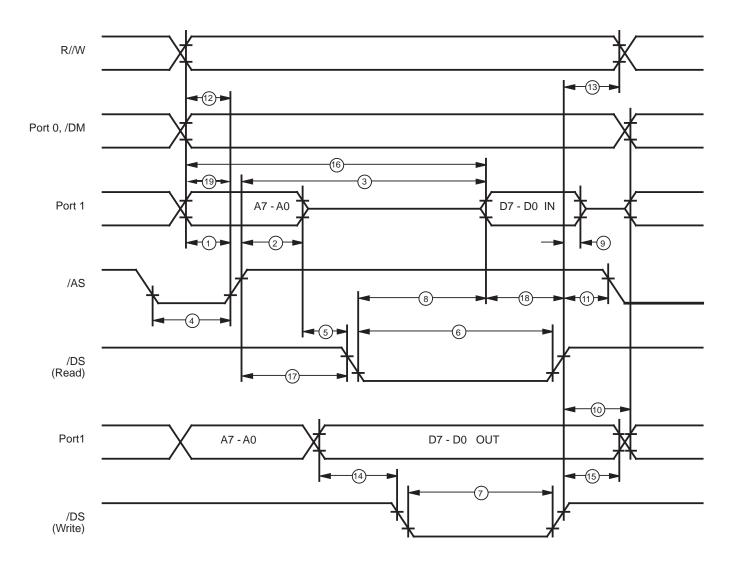

### **AC CHARACTERISTICS**

### External I/O or Memory Read and Write Timing Diagram

Figure 7. External I/O or Memory Read/Write Timing

#### **AC CHARACTERISTICS**

#### **External I/O or Memory Read and Write Timing Table**

|    |           |                                           |        | T <sub>A</sub> = 0°C | to +70°C |       |       |

|----|-----------|-------------------------------------------|--------|----------------------|----------|-------|-------|

| No | Symbol    | Parameter                                 | Note 4 | Min                  | Max      | Units | Notes |

| 1  | TdA(AS)   | Address Valid to /AS Rise Delay           | 5.0V   | 25                   |          | ns    | 2,3   |

| 2  | TdAS(A)   | /AS Rise to Address Float Delay           | 5.0V   | 35                   |          | ns    | 2,3   |

| 3  | TdAS(DR)  | /AS Rise to Read Data Req'd Valid         | 5.0V   |                      | 150      | ns    | 1,2,3 |

| 4  | TwAS      | /AS Low Width                             | 5.0V   | 35                   |          | ns    | 2,3   |

| 5  | TdAZ(DS)  | Address Float to /DS Fall                 | 5.0V   | 0                    |          | ns    |       |

| 6  | TwDSR     | /DS (Read) Low Width                      | 5.0V   | 125                  |          | ns    | 1,2,3 |

| 7  | TwDSW     | /DS (Write) Low Width                     | 5.0V   | 75                   |          | ns    | 1,2,3 |

| 8  | TdDSR(DR) | /DS Fall to Read Data Req'd Valid         | 5.0V   |                      | 90       | ns    | 1,2,3 |

| 9  | ThDR(DS)  | Read Data to /DS Rise Hold Time           | 5.0V   | 0                    |          | ns    | 2,3   |

| 10 | TdDS(A)   | /DS Rise to Address Active Delay          | 5.0V   | 40                   |          | ns    | 2,3   |

| 11 | TdDS(AS)  | /DS Rise to /AS Fall Delay                | 5.0V   | 35                   |          | ns    | 2,3   |

| 12 | TdR/W(AS) | R//W Valid to /AS Rise Delay              | 5.0V   | 25                   |          | ns    | 2,3   |

| 13 | TdDS(R/W) | /DS Rise to R//W Not Valid                | 5.0V   | 35                   |          | ns    | 2,3   |

| 14 | TdDW(DSW) | Write Data Valid to /DS Fall (Write)      | 5.0V   | 40                   |          | ns    | 2,3   |

| 15 | TdDS(DW)  | /DS Rise to Write Data Not Valid Delay    | 5.0V   | 25                   |          | ns    | 2,3   |

| 16 | TdA(DR)   | Address Valid to Read Data Req'd<br>Valid | 5.0V   |                      | 180      | ns    | 1,2,3 |

| 17 | TdAS(DS)  | /AS Rise to /DS Fall Delay                | 5.0V   | 48                   |          | ns    | 2,3   |

| 18 | TdDI(DS)  | Data Input Setup to /DS Rise              | 5.0V   | 50                   |          | ns    | 1,2,3 |

| 19 | TdDM(AS)  | /DM Valid to /AS Fall Delay               | 5.0V   | 20                   |          | ns    | 2,3   |

#### Notes:

- 1. When using extended memory timing add 2 TpC.

- 2. Timing numbers given are for minimum TpC.

- 3. See clock cycle dependent characteristics table.

- 4. 5.0 V ±0.5 V.

#### Standard Test Load

All timing references use 0.9 VCC for a logic 1 and 0.1 VCC for a logic 0.

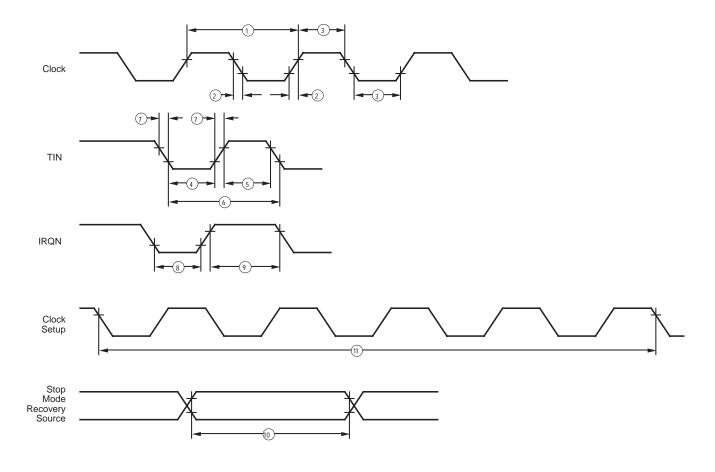

### **Additional Timing Diagram**

Figure 8. Additional Timing

#### **Additional Timing Table**

|    |              |                               | v <sub>cc</sub> | T <sub>A</sub> = 0°C to +70°C |     |       |                    |

|----|--------------|-------------------------------|-----------------|-------------------------------|-----|-------|--------------------|

| No | Sym          | Parameter                     | Note 5          | Min                           | Max | Units | Notes              |

| 1  | ТрС          | Input Clock Period            | 5.0V            | 48.83                         |     | ns    | 1, 6               |

| 2  | TrC,TfC      | Clock Input Rise & Fall Times | 5.0V            |                               | 6   | ns    | 1                  |

| 3  | TwC          | Input Clock Width             | 5.0V            | 17                            |     | ns    | 1,7                |

| 4  | TwTinL       | Timer Input Low Width         | 5.0V            | 70                            |     | ns    |                    |

| 5  | TwTinH       | Timer Input High Width        | 5.0V            | 3ТрС                          |     |       | 1                  |

| 6  | TpTin        | Timer Input Period            | 5.0V            | 8TpC                          |     |       | 1                  |

| 7  | TrTin, TfTin | Timer Input Rise & Fall Timer | 5.0V            |                               | 100 | ns    | 1                  |

| 8a | TwIL         | Int. Request Low Time         | 5.0V            | 70                            |     | ns    | 1,2                |

| 8b | TwIL         | Int. Request Low Time         | 5.0V            | 3ТрС                          |     |       | 1                  |

| 9  | TwIH         | Int. Request Input High Time  | 5.0V            | 3ТрС                          |     |       | 1                  |

| 10 | Twsm         | Stop-Mode Recovery Width Spec | 5.0V            | 12                            |     | ns    | 1                  |

| 11 | Tost         | Oscillator Start-up Time      | 5.0V            | 5TpC                          |     |       | 3                  |

| 12 | Twdt         | Watch-Dog Timer               | 5.0V            | 5                             |     | ms    | D1 = 0, D0 = 0 [4] |

|    |              |                               | 5.0V            | 15                            |     | ms    | D1 = 0, D0 = 1 [4] |

|    |              |                               | 5.0V            | 25                            |     | ms    | D1 = 1, D0 = 0 [4] |

|    |              |                               | 5.0V            | 100                           |     | ms    | D1 = 1, D0 = 1 [4] |

#### Notes

- 1. Timing Reference uses 0.9 VCC for a logic 1 and 0.1 VCC for a logic 0.

- 2. Interrupt request via Port 3 (P31-P33).

- 3. SMR-D5 = 0

- 4. Reg. WDT

- 5.  $5.0 \text{ V} \pm 0.5 \text{ V}$

- 6. For 29.49 MHz, it will be 30.53 ns.

- 7. For 29.49 MHz, it will be 9 ns.

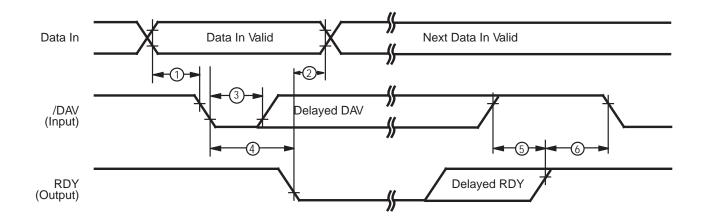

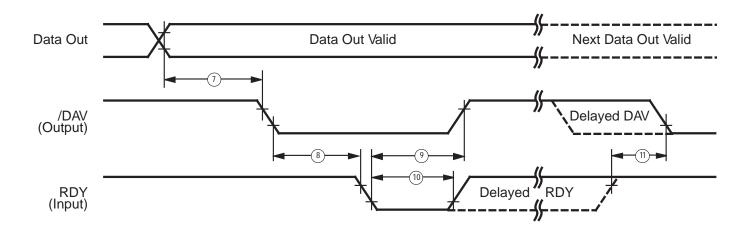

### **Handshake Timing Diagrams**

Figure 9. Input Handshake Timing

Figure 10. Output Handshake Timing

**Handshake Timing Table**

|    |              |                            | v <sub>cc</sub> | T <sub>A</sub> = 0°C to +70°C |     |       | Data      |

|----|--------------|----------------------------|-----------------|-------------------------------|-----|-------|-----------|

| No | Symbol       | Parameter                  | Note            | Min                           | Max | Units | Direction |

| 1  | TsDI(DAV)    | Data In Setup Time         | 5.0V            | 0                             |     | ns    | IN        |

| 2  | ThDI(RDY)    | RDY to Data Hold Time      | 5.0V            | 0                             |     | ns    | IN        |

| 3  | TwDAV        | Data Available Width       | 5.0V            | 40                            |     | ns    | IN        |

| 4  | TdDAVI(RDY)  | DAV Fall to RDY Fall Delay | 5.0V            |                               | 70  | ns    | IN        |

| 5  | TdDAVId(RDY) | DAV Rise to RDY Rise Delay | 5.0V            |                               | 40  | ns    | IN        |

| 6  | TdDO(DAV)    | RDY Rise to DAV Fall Delay | 5.0V            | 0                             |     | ns    | IN        |

| 7  | TcLDAV0(RDY) | Data Out to DAV Fall Delay | 5.0V            | ТрС                           |     | ns    | OUT       |

| 8  | TcLDAV0(RDY) | DAV Fall to RDY Fall Delay | 5.0V            | 0                             |     | ns    | OUT       |

| 9  | TdRDY0(DAV)  | RDY Fall to DAV Rise Delay | 5.0V            |                               | 70  | ns    | OUT       |

| 10 | TwRDY        | RDY Width                  | 5.0V            | 40                            |     | ns    | OUT       |

| 11 | TdRDY0d(DAV) | RDY Rise to DAV Fall Delay | 5.0V            |                               | 40  | ns    | OUT       |

Note:

$5.0V \pm 0.5V$

#### **PIN FUNCTIONS**

**/RESET** (input, active Low). This pin initializes the MCU. Reset is accomplished either through Power-On Reset (POR), Watch-Dog Timer (WDT) reset, Stop-Mode Recovery, or external reset. During POR and WDT Reset, the internally generated reset signal is driving the reset pin Low for the POR time. Any devices driving the reset line must be open-drain to avoid damage from a possible conflict during reset conditions. A /RESET will reset both the Z8 and the DSP.

For the Z8: After the POR time, /RESET is a Schmitt-triggered input. To avoid asynchronous and noisy reset problems, the Z8 is equipped with a reset filter of four external clocks (4TpC). If the external reset signal is less than 4TpC in duration, no reset occurs. On the fifth clock after the /RESET is detected, an internal RST signal is latched and held for an internal register count of 18 external clocks, or for the duration of the external reset, whichever is longer. Program execution begins at location 000CH (hexadecimal), 5-10 TpC cycles after /RESET is released. The Z8 does not reset WDT, SMR, P2M, and P3M registers on a Stop-Mode Recovery operation.

**For the DSP:** After POR, the DSP is in RUN mode. The Z8 controls the DSP commands to HALT, RUN or RESET. When the DSP is in HALT mode, it cannot be woke up with WDT or SMR.

**RMLS** ROMless (input, active High). This pin, when connected to VDD, disables the internal Z8 ROM. (Note that, when pulled Low to GND, the device functions normally as the ROM version.) The DSP cannot be configured as ROMless. This pin is only available on the Z89175.

**R//W** Read/Write (output, write Low). The R//W signal defines the signal flow when the Z8 is reading or writing to an external program or data memory. The Z8 is reading when this pin is High and writing when this pin is Low.

/AS Address Strobe (output, active Low). Address Strobe is pulsed once at the beginning of each machine cycle. Address output is through Port 0/Port 1 for all external programs. Memory address transfers are valid at the trailing edge of /AS. Under program control, /AS is placed in the high-impedance state along with Ports 0 and 1, Data Strobe, and Read/Write.

**/DS** Data Strobe (output, active Low). Data Strobe is activated once for each external memory transfer. For read operations, data must be available prior to the trailing edge of /DS. For write operations, the falling edge of /DS indicates that output data is valid.

**XTAL1** Crystal 1 (time-based input). This pin connects a parallel-resonant crystal, ceramic resonator, LC, RC network, or an external single-phase clock to the on-chip oscillator input.

**XTAL2** Crystal 2 (time-based output). This pin connects a parallel-resonant, crystal, ceramic resonant, or LC network to the on-chip oscillator output.

**DSP0** (output). DSP0 is a general-purpose output pin connected to bit 6 of the Analog Control Register (DSP EXT4). This bit has no special significance and can be used to output data by writing to bit 6 of the ACR.

**DSP1** (output). DSP1 is a general-purpose output pin connected to bit 7 of the Analog Control Register (DSP EXT4). This bit has no special significance and can be used to output data by writing to bit 7 of the ACR.

**PWM** Pulse Width Modulator (Output). The PWM is a 10-bit resolution D/A converter. This output is a digital signal with CMOS output levels.

**AN**<sub>IN</sub> (input). Analog input for the A/D converter.

**ANV**<sub>DD</sub>. Analog power supply for the A/D converter.

**VREF+** (input). Reference voltage (High) for the A/D converter.

**V<sub>DD</sub>.** Digital power supply for the Z89175.

GND. Digital ground for the Z89175.

**OSC1** Oscillator 1 (time-based input). This pin connects a parallel-resonant crystal, ceramic resonator, LC, RC network to the on-chip oscillator input.

**OSC2** Oscillator 2 (time-based output). This pin connects a parallel-resonant crystal, ceramic resonator, LC, RC network to the on-chip oscillator output.

**NC** No Connect. For the 100-pin QFP package, pins 63 through 76, and pins 78 and 79 should be tied to Ground. Other NC pins must float.

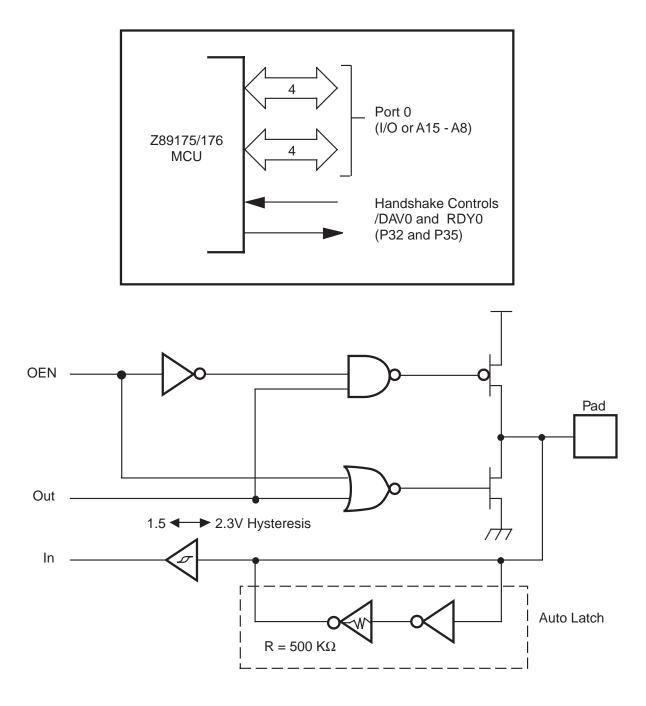

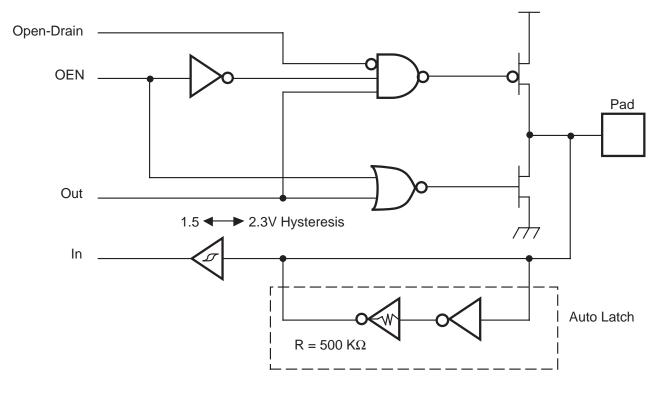

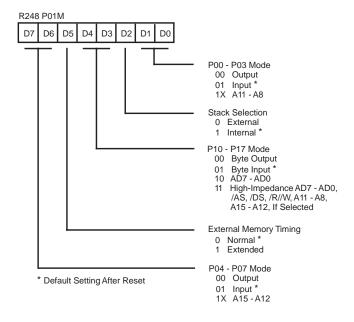

**Port 0** (P07-P00). Port 0 is an 8-bit, bidirectional, CMOS compatible port. These eight I/O lines are configured under software control as a nibble I/O port, or as an address port for interfacing external memory. The input buffers are Schmitt-triggered and the output drivers are push-pull. Port 0 is placed under handshake control. In this configuration, Port 3, lines P32 and P35 are used as the handshake control /DAV0 and RDY0. Handshake signal direction is dictated by the I/O direction to Port 0 of the upper nibble P07-P04. The lower nibble must have the same direction as the upper nibble.

The Auto Latch on Port 0 puts valid CMOS levels on all CMOS inputs which are not externally driven. Whether this level is 0 or 1 cannot be determined. A valid CMOS level, rather than a floating node, reduces excessive supply current flow in the input buffer.

For external memory references, Port 0 provides address bits A11-A8 (lower nibble) or A15-A8 (lower and upper nibble) depending on the required address space. If the address range requires 12 bits or less, the upper nibble of Port 0 can be programmed independently as I/O while the lower nibble is used for addressing. If one or both nibbles are needed for I/O operation, they are configured by writing to the Port 0 mode register.

In ROMless mode, after a hardware reset, Port 0 is configured as address lines A15-A8, and extended timing is set to accommodate slow memory access. The initialization routine can include reconfiguration to eliminate this extended timing mode. (In ROM mode, Port 0 is defined as input after reset.)

Port 0 is set in the high-impedance mode if selected as an address output state along with Port 1 and the control signals /AS, /DS, and R//W (Figure 11).

Figure 11. Port 0 Configuration

#### **PIN FUNCTIONS** (Continued)

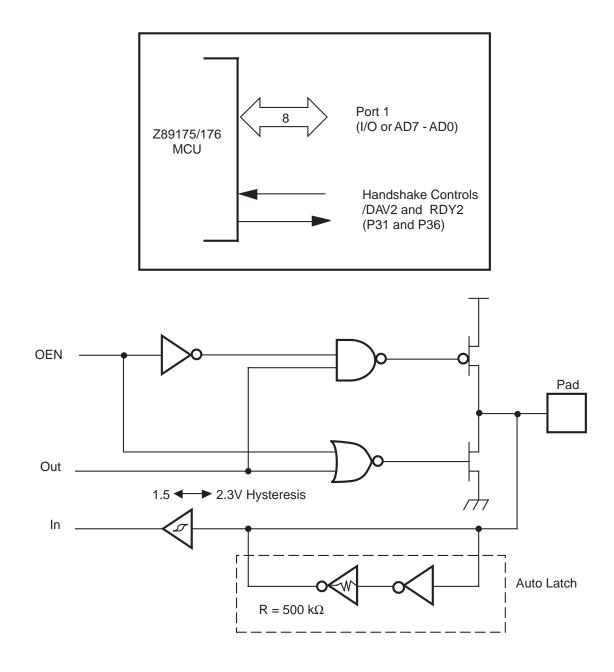

**Port 1** (P17-P10). Port 1 is an 8-bit, bidirectional, CMOS compatible port (Figure 12). It has multiplexed Address (A7-A0) and Data (D7-D0) ports. These eight I/O lines are programmed as inputs or outputs, or can be configured under software control as an Address/Data port for interfacing external memory. The input buffers are Schmitt-triggered and the output drivers are push-pull.

Port 1 can be placed under handshake control. In this configuration, Port 3, lines P33 and P34 are used as the handshake controls RDY1 and /DAV1 (Ready and Data Avail-

able). Memory locations greater than 24575 (Z89175) (in ROM mode) are referenced through Port 1. To interface external memory, Port 1 must be programmed for the multiplexed Address/Data mode. If more than 256 external locations are required, Port 0 outputs the additional lines.

Port 1 can be placed in the high-impedance state along with Port 0, /AS, /DS, and R//W, allowing the Z89175/176 to share common resources in multiprocessor and DMA applications.

Figure 12. Port 1 Configuration

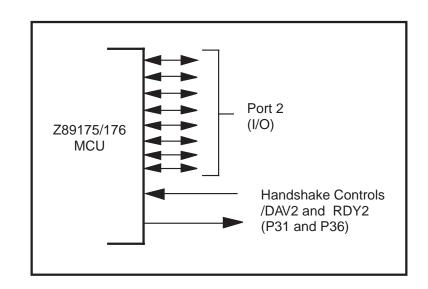

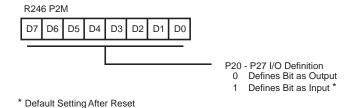

**Port 2** (P27-P20). Port 2 is an 8-bit, bidirectional, CMOS compatible I/O port. These eight I/O lines are configured under software control independently as inputs or outputs. Port 2 is always available for I/O operation. The input buffers are Schmitt-triggered. Bits programmed as outputs can be globally programmed as either push-pull or open-drain.

Port 2 can be placed under handshake control. In this configuration, Port 3 lines P31 and P36 are used as the handshake controls lines /DAV2 and RDY2. The handshake

signal assignment for Port 3 lines P31 and P36 is dictated by the direction (input or output) assigned to bit 7, Port 2 (Figure 13).

The Auto Latch on Port 2 puts valid CMOS levels on all CMOS inputs which are not externally driven. Whether this level is 0 or 1, cannot be determined. A valid CMOS level, rather than a floating node, reduces excessive supply current flow in the input buffer.

Figure 13. Port 2 Configuration

#### **PIN FUNCTIONS** (Continued)

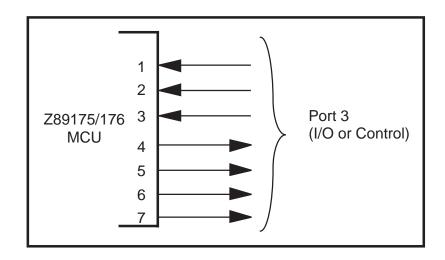

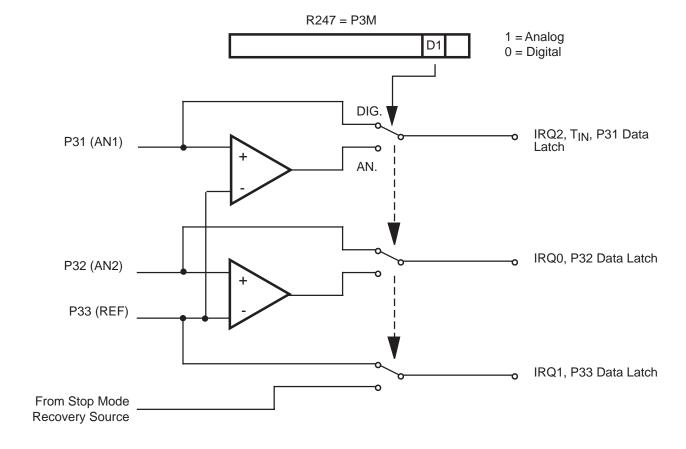

**Port 3** (P37-P31). Port 3 is a 7-bit, CMOS compatible port with three fixed inputs (P33-P31) and four fixed outputs (P37-P34). It is configured under software control for input/output, counter/timers, interrupt, and port handshakes. Pins P31, P32, and P33 are standard CMOS inputs; outputs are push-pull.

Two on-board comparators can process analog signals on P31 and P32 with reference to the voltage on P33. The analog function is enabled by programming bit 1 of the Port 3 Mode Register. Port 3, pin 3 is a falling edge interrupt input. P31 and P32 are programmable as rising, falling or both edge-triggered interrupts (IRQ register bits 6 and 7). P33 is the comparator reference voltage input. Access to counter/timer1 is made through P31 ( $T_{\rm IN}$ ) and P36 ( $T_{\rm OLT}$ ).

Handshake lines for ports 0, 1, and 2 are available on P31 through P36.

Port 3 also provides the following control functions: handshake for Ports 0, 1, and 2 (/DAV and RDY); three external interrupt request signals (IRQ3-IRQ1); timer input and output signals ( $T_{IN}$  and  $T_{OUT}$ ) (Figure 14).

Comparator Inputs. Port 3, pins P31 and P32 all have a comparator front end. The comparator reference voltage, pin P33, is common to both comparators. In analog mode, P31 and P32 are the positive inputs to the comparators and P33 is the reference voltage supplied to both comparators. In digital mode, pin P33 can be used as a P33 register input or IRQ1 source.

Table 5. Port 3 Pin Assignments

| Pin | I/O | CTC1 | AN IN | Int. | P0 HS | P1 HS | P2 HS | EXT |

|-----|-----|------|-------|------|-------|-------|-------|-----|

| P31 | IN  | TIN  | AN1   | IRQ2 |       |       | D/R   |     |

| P32 | IN  |      | AN2   | IRQ0 | D/R   |       |       |     |

| P33 | IN  |      | REF   | IRQ1 |       | D/R   |       |     |

| P34 | OUT |      |       |      |       | R/D   |       | DM  |

| P35 | OUT |      |       |      | R/D   |       |       |     |

| P36 | OUT | TOUT |       |      |       |       | R/D   |     |

| P37 | OUT |      |       |      |       |       |       |     |

#### Notes:

HS = Handshake Signals

D = DAV

R = RDY

Figure 14. Port 3 Configuration

#### **PIN FUNCTIONS** (Continued)

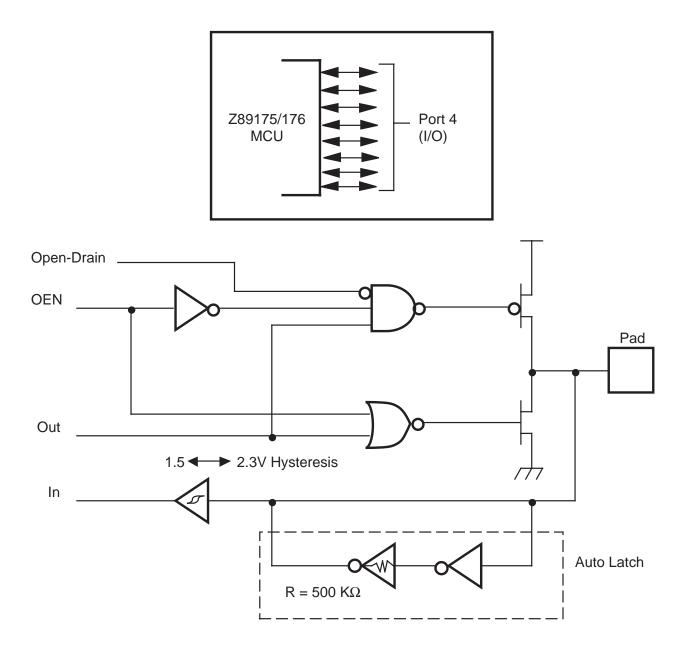

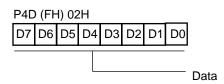

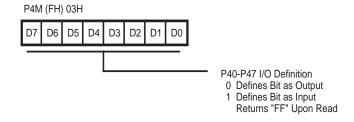

**Port 4** (P47-P40). Port 4 is an 8-bit, bidirectional, CMOS compatible I/O port (Figure 15). These eight I/O lines are configured under software control independently as inputs or outputs. Port 4 is always available for I/O operation. The input buffers are Schmitt-triggered. Bits programmed as outputs can be globally programmed as either push-pull or open-drain.

Port 4 is a bit programmable general-purpose I/O port. The control registers for Port 4 are mapped into the expanded register file (Bank F) of the Z8.

**Auto Latch.** The Auto Latch on Port 4 puts valid CMOS levels on all CMOS inputs which are not externally driven. Whether this level is 0 or 1 cannot be determined. A valid CMOS level, rather than a floating node, reduces excessive supply current flow in the input buffer.

Figure 15. Port 4 Configuration

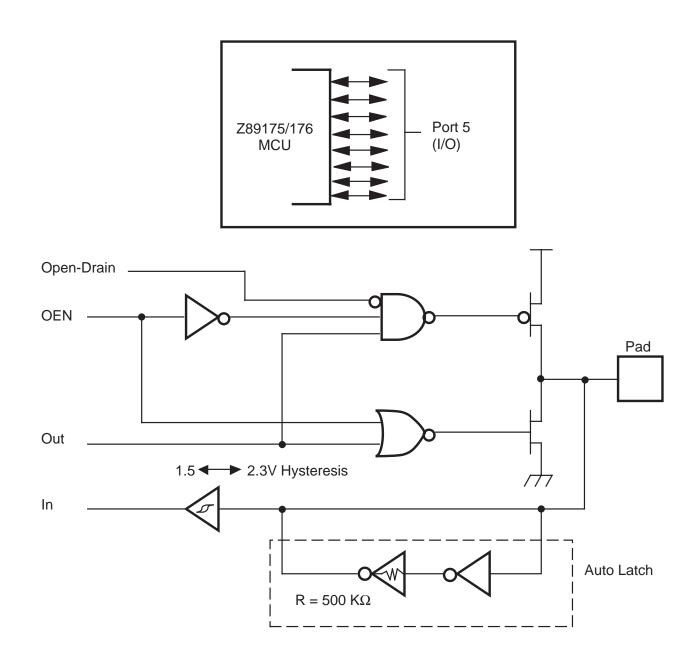

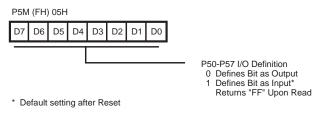

**Port 5** (P53-P50). Port 5 is a 4-bit, bidirectional, CMOS compatible I/O port (Figure 16). These four I/O lines are configured under software control independently as inputs or outputs. Port 5 is always available for I/O operation. The input buffers are Schmitt-triggered. Bits programmed as outputs can be globally programmed as either push-pull or open-drain.

Port 5 is a bit programmable general-purpose I/O port. The control registers for Port 5 are mapped into the expanded register file (Bank F) of the Z8.

**Auto Latch.** The Auto Latch on Port 5 puts valid CMOS levels on all CMOS inputs which are not externally driven. Whether this level is 0 or 1 cannot be determined. A valid CMOS level, rather than a floating node, reduces excessive supply current flow in the input buffer.

Figure 16. Port 5 Configuration

### **Z8® FUNCTIONAL DESCRIPTION**

The Z8 core of the Z89175/176 incorporates special functions to enhance the Z8's application in a variety of voice-processing applications.

**Reset.** The device is reset in one of the following conditions:

- Power-On Reset

- Watch-Dog Timer

- Stop-Mode Recovery Source

- External Reset

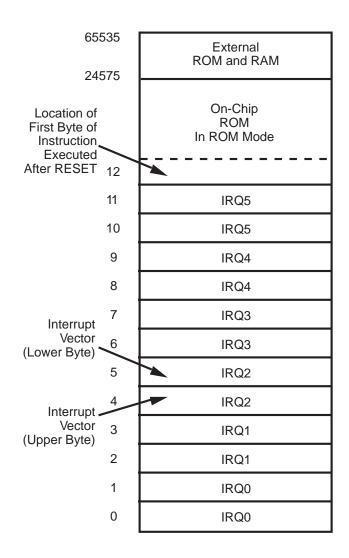

**Program Memory.** The Z8 addresses up to 24 KB of internal program memory and 40 KB external memory (Figure 17). The first 12 bytes of program memory are reserved for the interrupt vectors. These locations contain six 16-bit vectors which correspond to the five user interrupts and one DSP interrupt. Byte 12 to byte 24575 consist of onchip mask-programmed ROM. At addresses 24576 and greater the Z8 executes external program memory. In ROMless mode, the Z8 will execute external program memory beginning at byte 12 and continuing through byte 65535.

Figure 17. Program Memory

**ROM Protect.** The 24 KB of internal program memory for the Z8 is mask programmable. A ROM protect feature prevents "dumping" of the ROM contents of Program Memory by inhibiting execution of LDC, LDCI, LDE, and LDEI instructions. The ROM Protect option is mask-programmable, to be selected by the customer at the time the ROM code is submitted.

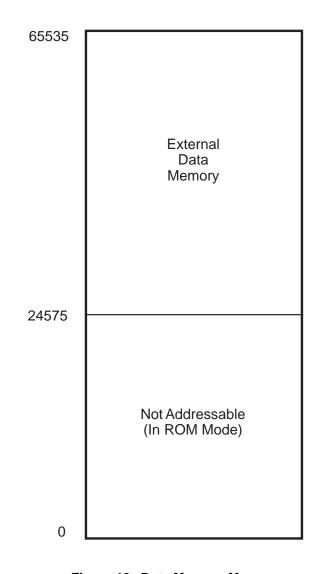

**Data Memory** (/DM). In ROM mode, the Z8 can address up to 40 KB of external data memory beginning at location 24576 (Figure 18). In ROMless mode, the Z8 can address the full 64 KB of external data memory beginning at location 12. External data memory can be included with, or separated from, the external program memory space. /DM, an optional I/O function that can be programmed to appear on Port 34, is used to distinguish between data and program memory space (Table 5). The state of the /DM signal is controlled by the type of instruction being executed. An LDC opcode references PROGRAM (/DM inactive)

memory, and an LDE instruction references data (/DM active Low) memory.

Figure 18. Data Memory Map

# **Z8® FUNCTIONAL DESCRIPTION** (Continued)

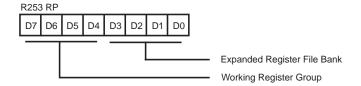

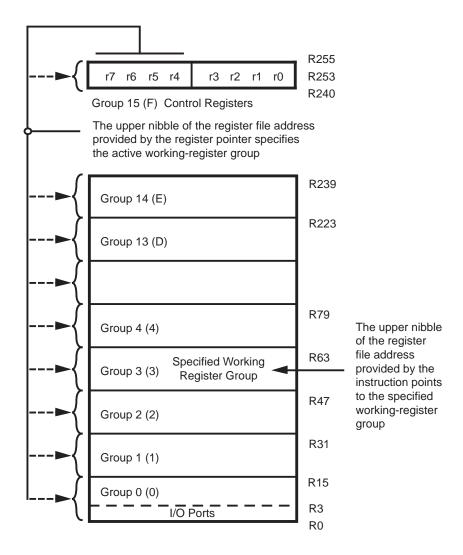

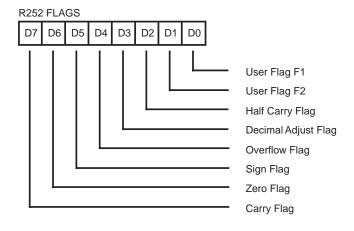

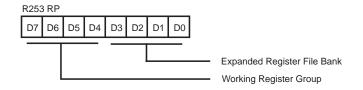

Register File. The standard Z8<sup>®</sup> register file consists of four I/O port registers, 236 general-purpose registers, and 15 control and status registers (R0-R3, R4-R239, and R241-R255, respectively). The instructions access registers directly or indirectly through an 8-bit address field. This allows a short, 4-bit register address using the Register Pointer (Figure 19). In the 4-bit mode, the register file is divided into 16 working register groups, each occupying 16 continuous locations. The Register Pointer addresses the starting location of the active working register group (Figure 20).

**Note:** Register Group E (Registers EF-E0) is only accessed through a working register and indirect addressing modes.

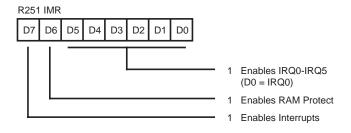

**RAM Protect.** The upper portion of the Z8's RAM address spaces 80H to EFH (excluding the control registers) is protected from reading and writing. The RAM Protect bit option is mask-programmable and is selected by the customer when the ROM code is submitted. After the mask option is selected, the user activates the RAM Protect from the internal ROM code by loading a bit D6 in the IMR register to either a 0 (OFF) or a 1 (ON). A 1 in D6 indicates RAM Protect enabled.

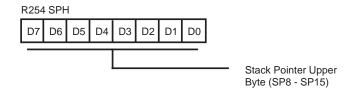

**Stack.** The Z8's external data memory or the internal register file is used for the stack. The 16-bit Stack Pointer (R255-R254) is used for the external stack which can reside only from 24576 to 65535 in ROM mode or 0 to 65535 in ROMless mode. An 8-bit Stack Pointer (R255) is used for the internal stack residing within the 236 general-purpose registers (R239-R4). SPH can be used as a general-purpose register when using internal stack only.

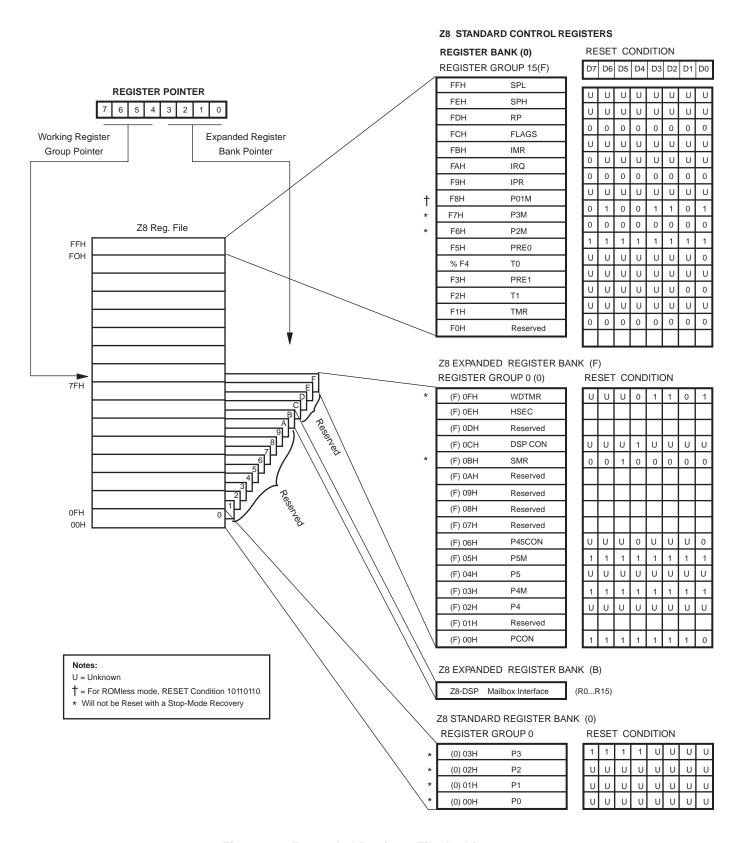

**Expanded Register File.** The register file on the Z8 has been expanded to allow for additional system control registers and for mapping of additional peripheral devices along with I/O ports into the register address area. The Z8 register address space has been implemented as 16 banks of 16 register groups per bank (Figure 20). These register banks are known as the ERF (Expanded Register File). Bits 7-4 of register RP (Register Pointer) select the working register group. Bits 3-0 of register RP select the Expanded Register bank (Figure 21).

The SMR register, WDT Register, control and data registers for Port 4 and Port 5, and the DSP control register are located in Bank F of the Expanded Register File. Bank B of the Expanded Register File consists of the Mailbox Interface through which the Z8 and the DSP communicate. The rest of the Expanded Register is not physically implemented and is open for future expansion.

Figure 19. Register Pointer Register

Figure 20. Register Pointer

# **Z8® FUNCTIONAL DESCRIPTION** (Continued)

Figure 21. Expanded Register File Architecture

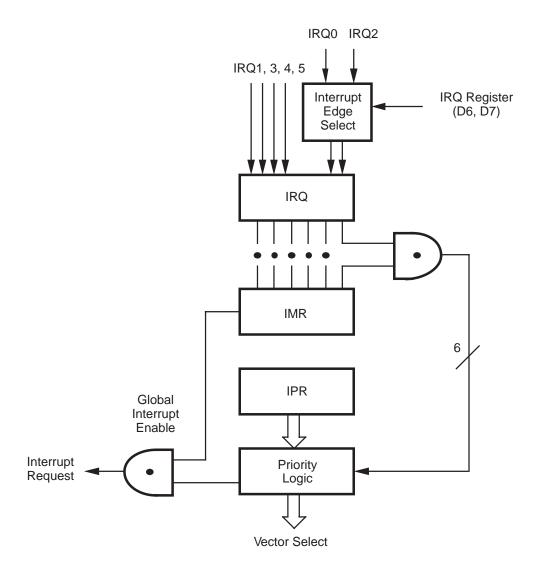

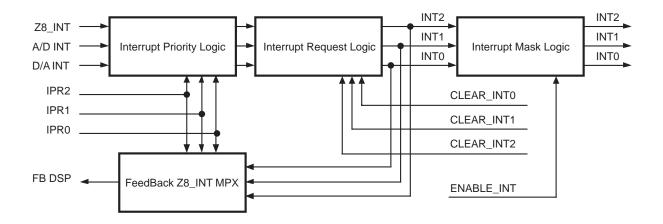

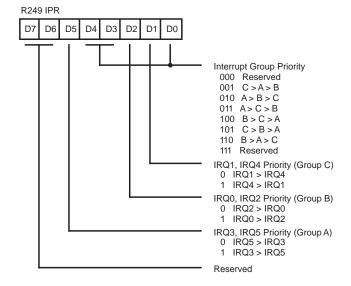

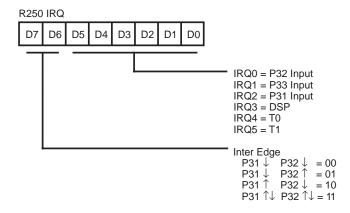

**Interrupts.** The Z8 has six different interrupts from six different sources. The interrupts are maskable and prioritized (Figure 22). The six sources are divided as follows; three sources are claimed by Port 3 lines P33-P31, two by

counter/timers, and one by the DSP (Table 6). The Interrupt Mask Register globally or individually enables or disables the six interrupt requests.

Figure 22. Interrupt Block Diagram

# **Z8® FUNCTIONAL DESCRIPTION** (Continued)

Table 6. Interrupt Types, Sources, and Vectors

|      |                         | Vector   |                                                                   |

|------|-------------------------|----------|-------------------------------------------------------------------|

| Name | Source                  | Location | Comments                                                          |

| IRQ0 | /DAV0, P32,<br>AN2      | 0, 1     | External (P32),<br>Programmable Rise<br>or Fall Edge<br>Triggered |

| IRQ1 | /DAV1, P33              | 2, 3     | External (P33), Fall<br>Edge Triggered                            |

| IRQ2 | /DAV2, P31,<br>TIN, AN2 | 4, 5     | External (P31),<br>Programmable Rise<br>or Fall Edge<br>Triggered |

| IRQ3 | IRQ3                    | 6, 7     | Internal (DSP activated), Fall Edge Triggered                     |

| IRQ4 | T0                      | 8, 9     | Internal                                                          |

| IRQ5 | TI                      | 10, 11   | Internal                                                          |

When more than one interrupt is pending, priorities are resolved by a programmable priority encoder controlled by the Interrupt Priority Register. An interrupt machine cycle is activated when an interrupt request is granted. This disables all subsequent interrupts, pushes the Program Counter and Status Flags to the stack, and then branches to the program memory vector location reserved for that interrupt.

All Z8 interrupts are vectored through locations in the program memory. This memory location and the next byte contain the 16-bit address of the interrupt service routine for that particular interrupt request. To accommodate polled interrupt systems, interrupt inputs are masked and the Interrupt Request Register can be polled to determine which of the interrupt requests needs service.

An interrupt resulting from AN1 is mapped into IRQ2, and an interrupt from AN2 is mapped into IRQ0. Interrupts IRQ2 and IRQ0 can be rising, falling or both edge triggered, and are programmable by the user. The software can poll to identify the state of the pin.

Programming bits for the Interrupt Edge Select are located in the IRQ Register (R250), bits D7 and D6. The configuration is shown in Table 7.

Table 7. IRQ Register

|    | IRQ | Interrupt Edge |     |  |  |

|----|-----|----------------|-----|--|--|

| D7 | D6  | P31            | P32 |  |  |

| 0  | 0   | F              | F   |  |  |

| 0  | 1   | F              | R   |  |  |

| 1  | 0   | R              | F   |  |  |

| 1  | 1   | R/F            | R/F |  |  |

#### Notes:

F = Falling Edge R = Rising Edge

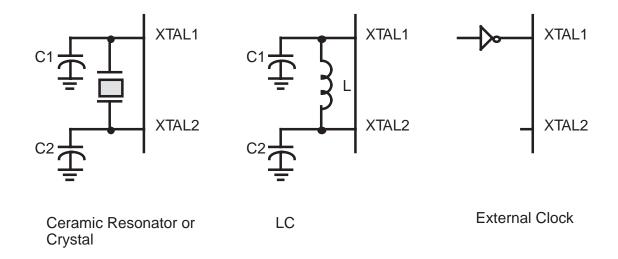

Clock. The Z89175/176 on-chip oscillator has a high-gain, parallel-resonant amplifier for connection to a crystal, LC, ceramic resonator, or any suitable external clock source (XTAL1 = Input, XTAL2 = Output). The crystal should be AT cut, 20.48 MHz maximum, with a series resistance (RS) less than or equal to 100 Ohms. The system clock (SCLK) is one half the crystal frequency.

The crystal is connected across XTAL1 and XTAL2 using capacitors from each pin to Ground (Figure 23).

Figure 23. Oscillator Configuration

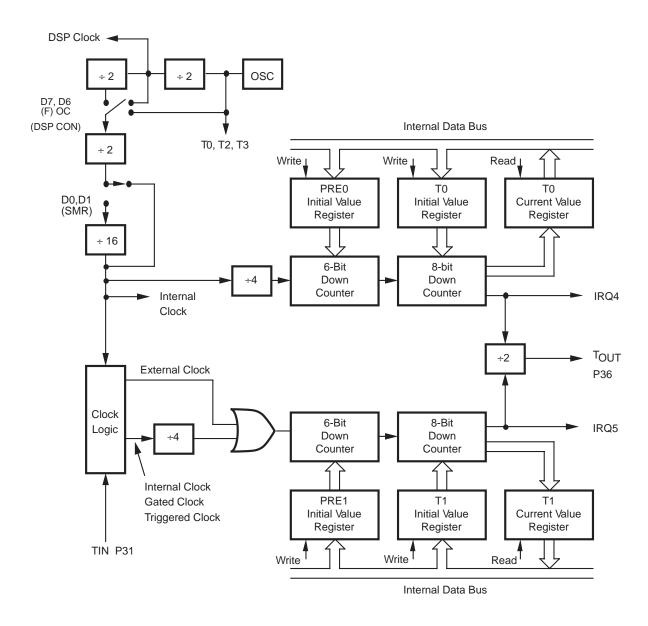

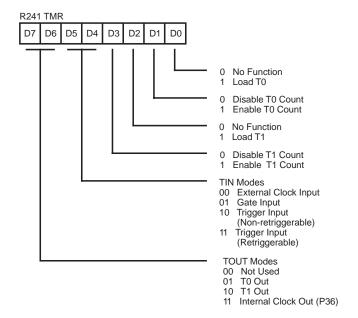

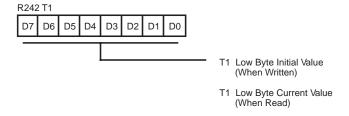

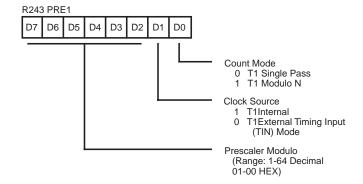

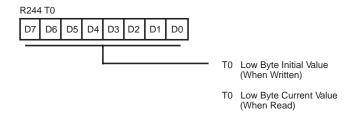

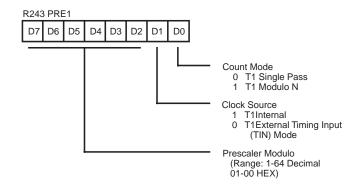

**Counter/Timers.** There are two 8-bit programmable counter/timers (T1,T0), each driven by its own 6-bit programmable prescaler. The T1 prescaler is driven by internal or external clock sources. However, the T0 prescaler is driven by the internal clock only (Figure 24).

The 6-bit prescalers can divide the input frequency of the clock source by any integer number from 1 to 64. Each prescaler drives its counter, which decrements the value (0 to 256) that has been loaded into the counter. When the counter reaches the end of the count, a timer interrupt request, IRQ4 (T0) or IRQ5 (T1), is generated.

The counters can be programmed to start, stop, restart to continue, or restart from the initial value. The counters can also be programmed to stop upon reaching zero (single pass mode) or to automatically reload the initial value and continue counting (modulo-n continuous mode).

The counters, but not the prescalers, are read at any time without disturbing their value or count mode. The clock source for T1 is user-definable and is either the internal microprocessor clock divided by four, or an external signal input via Port 31. The Timer Mode register configures the external timer input (P31) as an external clock, a trigger input that can be retriggerable or non-retriggerable, or as a gate input for the internal clock. The counter/timers can be cascaded by connecting the T0 output to the input of T1.

#### **Z8® FUNCTIONAL DESCRIPTION** (Continued)

Figure 24. Counter/Timer Block Diagram

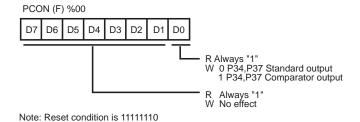

**Port Configuration Register** (PCON). The PCON register configures the comparator output on Port 3. The PCON register (Figure 25) is located in the Expanded Register File at Bank F, location 00H.

**Comparator Output Port 3** (D0). Bit 0 controls the comparator use in Port 3. A 1 in this location brings the comparator outputs to P34 and P35, and a 0 releases the Port to its standard I/O configuration.

Figure 25. Port Configuration Register (PCON)

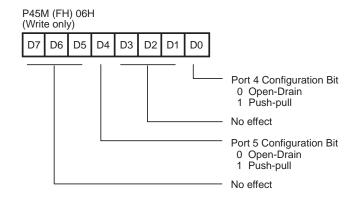

**Port 4 and 5 Configuration Register** (P45CON). The P45CON register configures Port 4 and Port 5, individually, to open-drain or push-pull active. This register is located in the Expanded Register File at Bank F, location 06H (Figure 26).

**Port 4 Open-Drain** (D0). Port 4 can be configured as an open-drain by resetting this bit (D0 = 0) or configured as push-pull active by setting this bit (D0 = 1). The default value is 1.

**Port 5 Open-Drain** (D4). Port 5 can be configured as an open-drain by resetting this bit (D4 = 0) or configured as push-pull active by setting this bit (D4 = 1). The default value is 1.

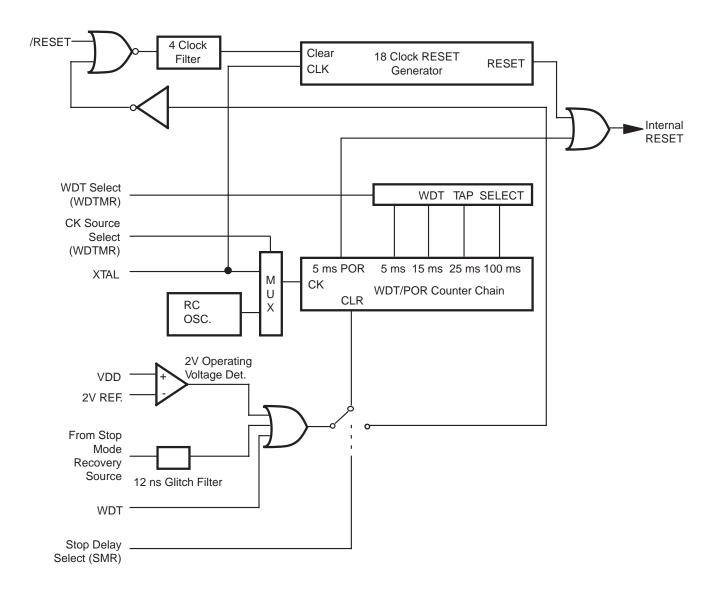

**Power-On Reset** (POR). A timer circuit clocked by a dedicated on-board RC oscillator is used for the Power-On Reset (POR) timer function. The POR time allows VCC and the oscillator circuit to stabilize before instruction execution begins.

The POR timer circuit is a one-shot timer triggered by one of three conditions:

- 1. Power fail to Power OK status;

- Stop-Mode Recovery (if D5 of SMR=1);

- 3. WDT time-out.

The POR time is a nominal 5 ms. Bit 5 of the STOP mode register determines whether the POR timer is bypassed after Stop-Mode Recovery (typical for external clock, RC/LC oscillators).

**HALT.** HALT turns off the internal CPU clock, but not the XTAL oscillation. The counter/timers and external interrupts IRQ0, IRQ1, IRQ2, and IRQ3 remain active. The devices are recovered by interrupts, either externally or internally generated.

**STOP.** This instruction turns off the internal clock and external crystal oscillation. It reduces the standby current to 20  $\mu$ A or less. The STOP mode is terminated by a reset only, either by WDT time-out, POR, SMR, or external reset. This causes the processor to restart the application program at address 000CH. In order to enter STOP (or HALT) mode, it is necessary to first flush the instruction pipeline to avoid suspending execution in mid-instruction. To do this, the user must execute a NOP (opcode=FFH) immediately before the appropriate Sleep instruction, i.e.,

| FF | NOP  | ; clear the pipeline |

|----|------|----------------------|

| 6F | STOP | ; enter Stop mode    |

|    |      | or                   |

| FF | NOP  | ; clear the pipeline |

| 7F | HALT | ; enter Halt mode    |

#### **Z8® FUNCTIONAL DESCRIPTION** (Continued)

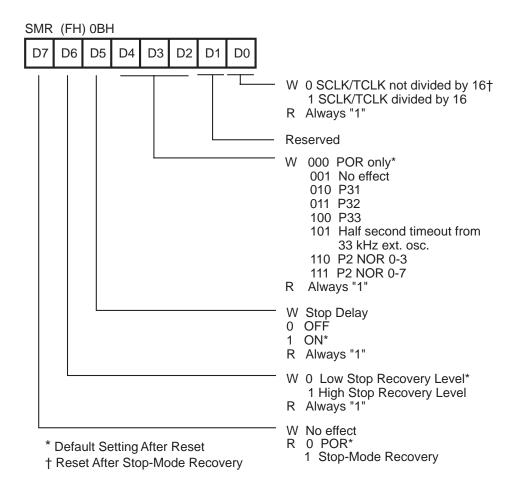

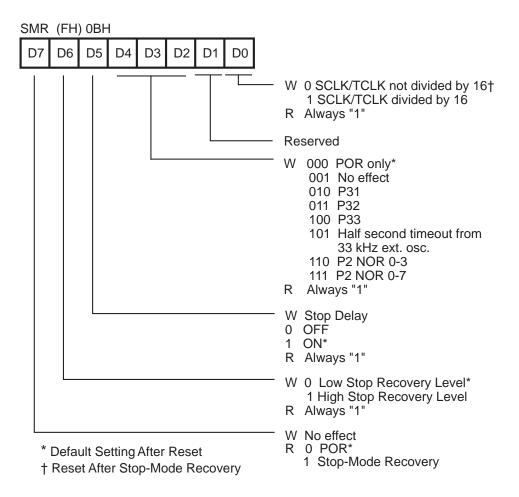

**Stop-Mode Recovery Register** (SMR). This register selects the clock divide value and determines the mode of Stop-Mode Recovery (Figure 26). All bits are Write-Only except bit 7, which is Read-Only. Bit 7 is a flag bit that is hardware set on the condition of STOP recovery and reset by a power-on cycle. Bit 6 controls whether a low level or

a high level is required from the recovery source. Bit 5 controls the reset delay after recovery. Bits 2, 3, and 4, or the SMR register, specify the source of the Stop-Mode Recovery signal. Bits 0 and 1 determine the time-out period of the WDT. The SMR is located in Bank F of the Expanded Register group at address 0BH.

Figure 26. Stop-Mode Recovery Register (SMR)

**SCLK/TCLK** divide-by-16 Select (D0). D0 of the SMR controls a divide-by-16 prescaler of SCLK/TCLK. The purpose of this control is to selectively reduce device power consumption during normal processor execution (SCLK

control) and/or HALT mode (where TCLK sources counter/timers and interrupt logic).

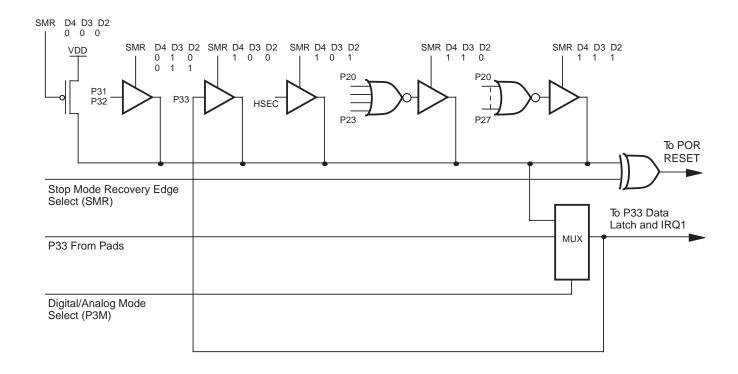

**Stop-Mode Recovery Source** (D4-D2). These three bits of the SMR specify the wake-up source of the STOP recovery (Figure 27 and Table 8).

Figure 27. Stop-Mode Recovery Source

Table 8. Stop-Mode Recovery Source

|    | SMR:432 |    | Operation                      |

|----|---------|----|--------------------------------|

| D4 | D3      | D2 | Description of Action          |

| 0  | 0       | 0  | POR and/or external reset      |

|    |         |    | recovery                       |

| 0  | 0       | 1  | No effect                      |

| 0  | 1       | 0  | P31 transition                 |

| 0  | 1       | 1  | P32 transition                 |

| 1  | 0       | 0  | P33 transition                 |

| 1  | 0       | 1  | HSEC                           |

| 1  | 1       | 0  | Logical NOR of P20 through P23 |

| 1  | 1       | 1  | Logical NOR of P20 through P27 |

**Stop-Mode Recovery Delay Select** (D5). When Low, this bit disables the 5 ms /RESET delay after Stop-Mode Recovery. The default configuration of this bit is 1. If the "fast" wake up is selected, the Stop-Mode Recovery source is kept active for at least 5 TpC.

**Stop-Mode Recovery Edge Select** (D6). A 1 in this bit position indicates that a high level on any one of the recovery sources wakes the Z89175/176 from STOP mode. A 0 indicates low level recovery. The default is 0 on POR (Table 8).

**Cold or Warm Start** (D7). This bit is set by the device upon entering STOP mode. It is active High, and is 0 (cold) on POR/WDT /RESET. This bit is Read-Only. It is used to distinguish between a cold or warm start.

**DSP Control Register** (DSPCON). The DSPCON register controls various aspects of the Z8 and the DSP. It can configure the internal system clock (SCLK) or the Z8, /RESET, and HALT of the DSP, and control the interrupt interface between the Z8 and the DSP (Table 9).

#### **Z8® FUNCTIONAL DESCRIPTION** (Continued)

Table 9. DSP Control Register (F) OCH [Read/Write]

| Field<br>DSPCON (F)0CH | Position | Attrib | Value | Label        |

|------------------------|----------|--------|-------|--------------|

| Z8_SCLK                | 76       | R/W    | 00    | (OSC/8)      |

|                        |          |        | 01    | (OSC/4)      |

|                        |          |        | 1x    | (OSC/2)      |

| DSP_Reset              | 5        | R      |       | Return "0"   |

|                        |          | W      | 0     | No effect    |

|                        |          |        | 1     | Reset DSP    |

| DSP_Run                | 4        | R/W    | 0     | Halt_DSP     |

|                        |          |        | 1     | Run_DSP      |

| Reserved               | 32       | W      |       | No effect    |

|                        |          | R      |       | Return "0"   |

|                        |          |        |       | No effect    |

| DSP_INT2               | 1-       | R      |       | FB_DSP_INT2  |

|                        |          | W      | 1     | Set DSP_INT2 |

|                        |          |        | 0     | No effect    |

| Z8_IRQ3                | 0        | R      |       | FB_Z8_IRQ3   |

|                        |          | W      | 1     | Clear IRQ3   |

|                        |          |        | 0     | No effect    |

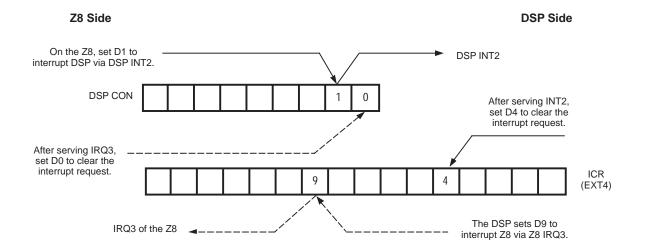

**Z8 IRQ3** (D0). When read, this bit indicates the status of the Z8 IRQ3. The Z8 IRQ3 is set by the DSP by writing to D9 of DSP External Register 4 (ICR). By writing a 1 to this bit, Z8 IRQ3 is Reset.

**DSP INT2** (D1). This bit is linked to DSP INT2. Writing a 1 to this bit sets the DSP INT2. Reading this bit indicates the status of the DSP INT2.

**DSP RUN** (D4). This bit defines the HALT mode of the DSP. If this bit is set to 0, then the DSP clock is turned off to minimize power consumption. After this bit is set to 1, then the DSP will continue code execution from where it was halted. After a hardware reset, this bit is reset to 1.

**DSP RESET** (D5). Setting this bit to 1 will reset the DSP. If the DSP was in HALT mode, this bit is automatically preset to 1. Writing a 0 has no effect.

**Z8 SCLK** (D7-D6). These bits define the SCLK frequency of the Z8. The oscillator can be divided by 8, 4, or 2. After a reset, both bits default to 00.

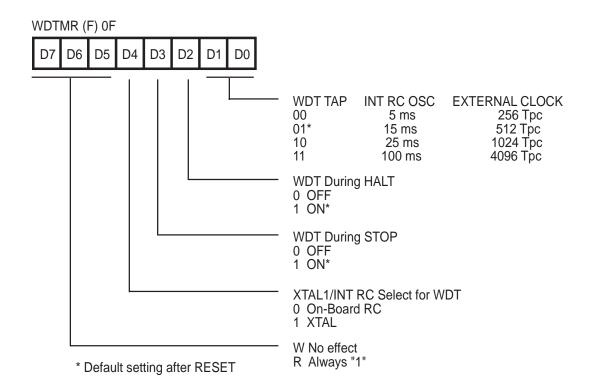

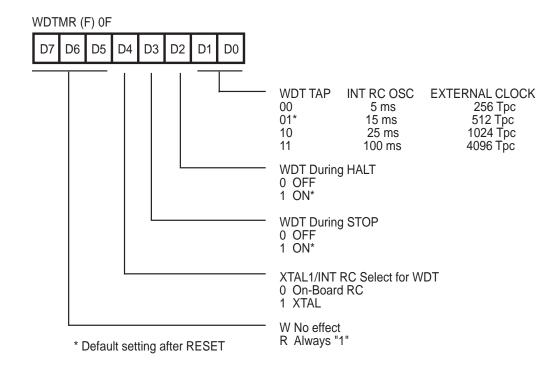

Watch-Dog Timer Mode Register (WDTMR). The WDT is a retriggerable one-shot timer that resets the Z8 if it reaches its terminal count. The WDT is initially enabled by executing the WDT instruction and refreshed on subsequent executions of the WDT instruction. The WDT circuit is driven by an on-board RC oscillator or external oscillator from the XTAL1 pin. The POR clock source is selected with bit 4 of the WDT register (Figure 29). The WDTMR register is accessible only within 64 Z8 clock cycles after POR.

Figure 28. Watch-Dog Timer Mode Register

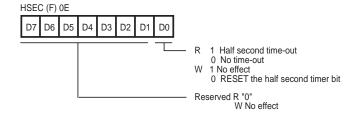

Half-Second Timer Status Register (HSEC). The half-second timer status register (Figure 30) is a free-running timer clocked by the external 32.768 kHz crystal. In normal operation mode, every half-second, the timer will time-out and set bit 0 (D0) of the HSEC register to 1. The user can reset this bit for real timing. In Stop mode, this timer can be used as a Stop-Mode Recovery source. Every half-second, the timer will recover the Stop mode and bit 0 of the HSEC register will be set to 1. Therefore, in Stop mode, the user can keep real time.

Figure 29. Half-Second Timer Status Register

#### **Z8® FUNCTIONAL DESCRIPTION** (Continued)

**WDT Time Select** (D0, D1). These bits selects the WDT time period. The configuration is shown in Table 10.

Table 10. WDT Time Select

|    |             | Time-out of     | Time-out of |

|----|-------------|-----------------|-------------|

| D1 | <b>D0</b> ' | Internal RC OSC | XTAL Clock  |

| 0  | 0           | 5 ms min        | 256 TpC     |

| 0  | 1           | 15 ms min       | 512 TpC     |

| 1  | 0           | 25 ms min       | 1024 TpC    |

| 1  | 1           | 100 ms min      | 4096 TpC    |

#### Notes:

TpC = XTAL clock cycle.

Tolerance =  $\pm 10\%$

**WDT During HALT** (D2). This bit determines whether or not the WDT is active during HALT mode. A 1 indicates active during HALT. The default is 1.

**WDT During STOP** (D3). This bit determines whether or not the WDT is active during STOP mode. Since XTAL clock is stopped during STOP mode, the on-board RC must be selected as the clock source to the POR counter. A 1 indicates active during STOP. The default is 1.

Clock Source for WDT (D4). This bit determines which oscillator source is used to clock the internal POR and WDT counter chain. If the bit is a 1, the internal RC oscillator is bypassed and the POR and WDT clock source is driven from the external pin, XTAL1. The default configuration of this bit is 0 which selects the RC oscillator.

Figure 30. Resets and WDT

#### **DSP REGISTERS DESCRIPTION**

**General.** The DSP is a high-performance second generation CMOS Digital Signal Processor with a modified Harvard-type architecture with separate program and data ports. The design has been optimized for processing power and saving silicon space.

**Registers.** The DSP has eight internal registers and seven external registers. The external registers are for the A/D

and D/A converters, and the mailbox and interrupt interfacing between DSP to the Z8. External registers are accessed in one machine cycle, the same as internal registers.

#### **DSP Registers**

There are 15 internal and extended 16-bit registers which are defined in Table 11.

Table 11. DSP Registers

| Register | Attribute  | Register Definition                     |  |  |

|----------|------------|-----------------------------------------|--|--|

| BUS      | Read       | Data-Bus                                |  |  |

| X        | Read/Write | X Multiplier Input, 16-Bit              |  |  |

| Υ        | Read/Write | Y Multiplier Input, 16-Bit              |  |  |

| A        | Read/Write | Accumulator, 24-Bit                     |  |  |

| SR       | Read/Write | Status Register                         |  |  |

| SP       | Read/Write | Stack Pointer                           |  |  |

| PC       | Read/Write | Program Counter                         |  |  |

| Р        | Read       | Output of MAC, 24-Bit                   |  |  |

| EXT0     | Read       | Z8 ERF Bank B, Register 00-01 (from Z8) |  |  |

|          | Write      | Z8 ERF Bank B, Register 08-09 (to Z8)   |  |  |

| EXT1     | Read       | Z8 ERF Bank B, Register 02-03 (from Z8) |  |  |

|          | Write      | Z8 ERF Bank B, Register 0A-0B (to Z8)   |  |  |

| EXT2     | Read       | Z8 ERF Bank B, Register 04-05 (from Z8) |  |  |

|          | Write      | Z8 ERF Bank B, Register 0C-0D (to Z8)   |  |  |

| EXT3     | Read       | Z8 ERF Bank B, Register 06-07 (from Z8) |  |  |

|          | Write      | Z8 ERF Bank B, Register 0E-0F (to Z8)   |  |  |

| EXT4     | Read/Write | DSP Interrupt Control Register          |  |  |

| EXT5     | Read       | A/D Converter                           |  |  |

|          | Write      | D/A Converter                           |  |  |

| EXT6     | Read/Write | Analog Control Register                 |  |  |

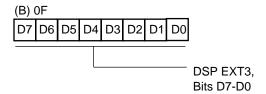

**EXT3-EXT0** (External Registers 3-0). These are the Mailbox Registers used by the DSP and Z8 to communicate. These four 16-bit registers correspond to the eight outgoing and eight incoming 8-bit registers in Bank B of the Z8's Expanded Register File.

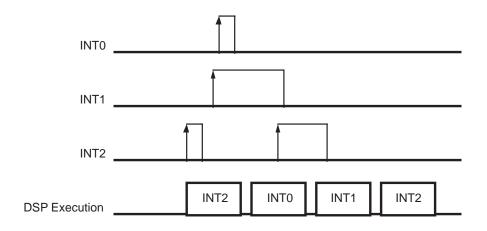

**EXT4** (DSP Interrupt Control Register (ICR)). This register controls the interrupts in the DSP as well as the interrupts in common between the DSP and the Z8. It is accessible by the DSP only, except for bit F and bit 9.

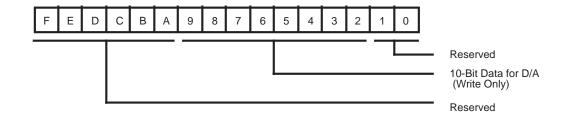

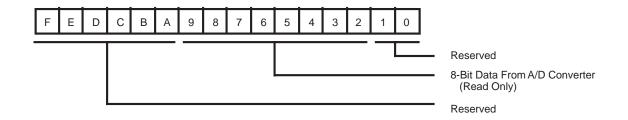

**EXT5** (D/A and A/D Data Register). This register is used by both D/A and A/D converters. The D/A converter is loaded by writing to this register, while the A/D converter is addressed by reading from this register. The Register EXT5 is accessible only by the DSP.

**EXT6** (Analog Control Register). This register controls the D/A and A/D converters. It is a read/write register accessible only by the DSP.

#### **DSP Z8 Mail Box**

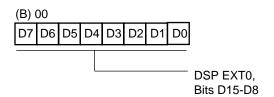

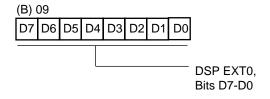

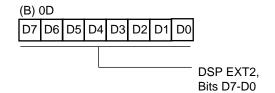

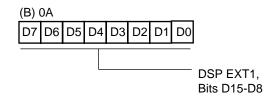

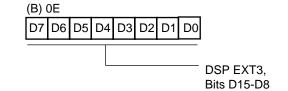

To receive information from the DSP, the Z8 uses eight incoming registers which are mapped in the Z8 extended Register File (Bank B, 08 to 0F). The DSP treats these as four 16-bit registers that correspond to the eight incoming Z8 registers (Figure 32).

#### **DSP REGISTERS DESCRIPTION** (Continued)

The Z8 can supply the DSP with data through eight outgoing registers mapped into both the Z8 Expanded Register File (Bank B, Registers 00 to 07) and the external register interface of the DSP. These registers are Read/Write and can be used as general-purpose registers of the Z8. The DSP can only read information from these registers. Since the DSP uses a 16-bit data format and the Z8 an 8-bit data format, eight outgoing registers of the Z8 correspond to

four DSP registers. The DSP can only read information from the outgoing registers.

Both the outgoing registers and the incoming registers share the same DSP address (EXT3-EXT0).

**Note:** The Z8 can read and write to ERF Bank B R00-R07, Registers 08-0F are Read-Only from the Z8.

Figure 31. Z8-DSP Interface

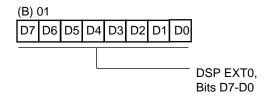

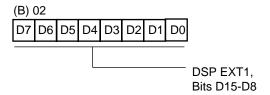

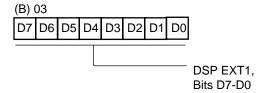

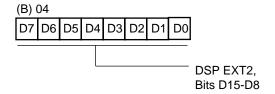

Table 12. Z8 Outgoing Registers (Read-Only from DSP)

| Field              | Position | Attrib | Value | Label             |

|--------------------|----------|--------|-------|-------------------|

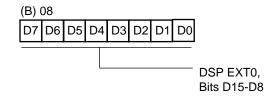

| Outgoing [0] (B)00 | 76543210 | R/W    | %NN   | (B)00/DSP_ext0_hi |

| Outgoing [1] (B)01 | 76543210 | R/W    | %NN   | (B)01/DSP_ext0_lo |

| Outgoing [2] (B)02 | 76543210 | R/W    | %NN   | (B)02/DSP_ext1_hi |

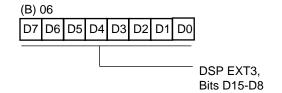

| Outgoing [3] (B)03 | 76543210 | R/W    | %NN   | (B)03/DSP_ext1_lo |

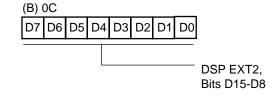

| Outgoing [4] (B)04 | 76543210 | R/W    | %NN   | (B)04/DSP_ext2_hi |

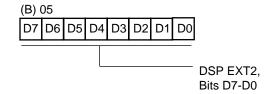

| Outgoing [5] (B)05 | 76543210 | R/W    | %NN   | (B)05/DSP_ext2_lo |