6

# MC10319

### **HIGH SPEED** 8-BIT ANALOG-TO-DIGITAL CONVERTER

The MC10319 is an 8-bit high speed parallel flash A/D converter. The device employs an internal Gray Code structure to eliminate large output errors on fast slewing input signals. It is fully TTL compatible, requiring a +5.0 V supply and a wide tolerance negative supply of -3.0 to -6.0 V. Three-state TTL outputs allow direct drive of a data bus or common I/O memory.

The MC10319 contains 256 parallel comparators across a precision input reference network. The comparator outputs are fed to latches and then to an encoder network, to produce an 8-bit data byte plus an overrange bit. The data is latched and converted to 3-state LS-TTL outputs. The overrange bit is always active to allow for either sensing of the overrange condition or ease of interconnecting a pair of devices to produce a 9-bit A/D converter.

Applications include Video Display and Radar processing, high speed instrumentation and TV Broadcast encoding.

- Internal Gray Code for Speed and Accuracy, Binary Outputs

- 8-Bit Resolution/9-Bit Typical Accuracy

- · Easily Interconnected for 9-Bit Conversion

- 3-State LS-TTL Outputs with True and Complement Enable Inputs

- 25 MHz Sampling Rate

- Wide Input Range: 1.0-2.0 V<sub>D-D</sub> Between ± 2.0 V

- Low Input Capacitance: 50 pF

- Low Power Dissipation: 618 mW

- No Sample/Hold Required for Video Bandwidth Signals

- Single Clock Cycle Conversion

### **BLOCK DIAGRAM** Analog VCC(D) O VEE Input (11, 17) 16, 22) MC10319 Bias VRT 0 Range (3) D7 (4) O D6 (5) O D5 (6) Latche Grav Cod O 04 (7) VRM 0 Latch Translato FCI-TTI Array O D3 (8) O D2 (9) O D1 (10) O DO (21) VRB ( (19) (20) Clock (18)

# **HIGH SPEED** 8-BIT ANALOG-TO-DIGITAL **FLASH CONVERTER**

SILICON MONOLITHIC INTEGRATED CIRCUIT

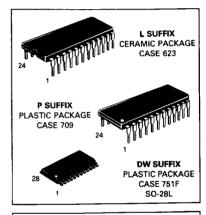

### ORDERING INFORMATION

| Device                            | Temperature Range | Package                      |

|-----------------------------------|-------------------|------------------------------|

| MC10319DW<br>MC10319L<br>MC10319P | 0° to +70°C       | SO-28L<br>Ceramic<br>Plastic |

| Parameter                                         | Symbol                                     | Value          | Unit |

|---------------------------------------------------|--------------------------------------------|----------------|------|

| Supply Voltage                                    | VCC(A),(D)<br>VEE                          | + 7.0<br>- 7.0 | Vdc  |

| Positive Supply Voltage Differential              | V <sub>CC(D)</sub> -<br>V <sub>CC(A)</sub> | -0.3 to +0.3   | Vdc  |

| Digital Input Voltage (Pins 18-20)                | V <sub>I(D)</sub>                          | -0.5 to +7.0   | Vdc  |

| Analog Input Voltage (Pins 1, 14, 23, 24)         | V <sub>I(A)</sub>                          | -2.5 to +2.5   | Vdc  |

| Reference Voltage Span (Pin 24-Pin 23)            |                                            | 2.3            | Vdc  |

| Applied Output Voltage (Pins 4-10, 21 in 3-State) | _                                          | -0.3 to +7.0   | Vdc  |

| Junction Temperature                              | ТЈ                                         | + 150          | °C   |

| Storage Temperature                               | T <sub>stq</sub>                           | -65 to +150    | °C   |

Devices should not be operated at these values. The "Recommended Operating Limits" provide guidelines for actual device operation.

### RECOMMENDED OPERATING LIMITS

| Parameter                                         | Symbol                                   | Min       | Тур      | Max   | Unit |

|---------------------------------------------------|------------------------------------------|-----------|----------|-------|------|

| Power Supply Voltage (Pin 15)<br>(Pins 11, 17)    | V <sub>CC(A)</sub><br>V <sub>CC(D)</sub> | + 4.5     | + 5.0    | + 5.5 | Vdc  |

| $V_{CC(D)} - V_{CC(A)}$                           | ΔV <sub>CC</sub>                         | -0.1      | 0        | + 0.1 | Vdc  |

| Power Supply Voltage (Pin 13)                     | VEE                                      | -6.0      | - 5.0    | -3.0  | Vdc  |

| Digital Input Voltages (Pins 18-20)               | V <sub>I</sub> (D)                       | 0         | _        | + 5.0 | Vdc  |

| Analog Input (Pin 14)                             | V <sub>I(A)</sub>                        | - 2.1     | _        | + 2.1 | Vdc  |

| Voltage @ VRT (Pin 24)                            | V <sub>RT</sub>                          | - 1.0     | _        | + 2.1 | Vdc  |

| Voltage @ V <sub>RB</sub> (Pin 23)                | V <sub>RB</sub>                          | -2.1      | _        | + 1.0 | Vdc  |

| V <sub>RT</sub> - V <sub>RB</sub>                 | ΔVR                                      | +1.0      | _        | + 2.1 | Vdc  |

| V <sub>RB</sub> - V <sub>EE</sub>                 |                                          | 1.3       | _        | _     | Vdc  |

| Applied Output Voltage (Pins 4-10, 21 in 3-State) | Vo                                       | 0         | _        | 5.5   | Vdc  |

| Clock Pulse Width — High<br>Low                   | tCKH<br>tCKL                             | 5.0<br>15 | 20<br>20 |       | пѕ   |

| Clock Frequency                                   | fCLK                                     | 0         |          | 25    | MHz  |

| Operating Ambient Temperature                     | TA                                       | 0         |          | +70   | °C   |

# $\textbf{ELECTRICAL CHARACTERISTICS} \ \text{(0°} < \text{T}_{\mbox{\scriptsize A}} < 70^{\circ}\text{C}, \ V_{\mbox{\scriptsize CC}} = 5.0 \ \mbox{V}, \ V_{\mbox{\scriptsize EE}} = -5.2 \ \mbox{V}, \ V_{\mbox{\scriptsize RT}} = +1.0 \ \mbox{V}, \ V_{\mbox{\scriptsize RB}} = -1.0 \ \mbox{V}, \ \text{except}$ where noted.)

| Parameter                                                                           | Symbol | Min | Тур   | Max   | Unit  |

|-------------------------------------------------------------------------------------|--------|-----|-------|-------|-------|

| TRANSFER CHARACTERISTICS (f <sub>CKL</sub> = 25 MHz)                                |        |     | 1     |       | 1     |

| Resolution                                                                          | N      | _   |       | 8.0   | Bits  |

| Monotonicity                                                                        | MON    |     | Bits  |       |       |

| Integral Nonlinearity                                                               | INL    |     | ± 1/4 | ± 1.0 | LSB   |

| Differential Nonlinearity                                                           | DNL    |     |       | ± 1.0 | LSB   |

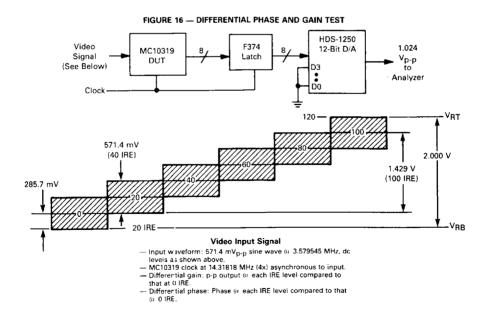

| Differential Phase (See Figure 16)                                                  | DP     | _   | 1.0   | _     | Deg.  |

| Differential Gain (See Figure 16)                                                   | DG     |     | 1.0   | _     | %     |

| Power Supply Rejection Ratio                                                        | PSRR   |     |       |       | LSB/V |

| $(4.5 \text{ V} < \text{V}_{CC} < 5.5 \text{ V}, \text{V}_{EE} = -5.2 \text{ V})$   | [      |     | 0.1   | _     |       |

| $(-6.0 \text{ V} < \text{V}_{EE} < -3.0 \text{ V}, \text{V}_{CC} = +5.0 \text{ V})$ |        |     | 0     | _     |       |

## ELECTRICAL CHARACTERISTICS — continued (0° < T<sub>A</sub> < 70°C, V<sub>CC</sub> = 5.0 V, V<sub>EE</sub> = -5.2 V, V<sub>RT</sub> = +1.0 V, $V_{RR} = -1.0 \text{ V, except where noted.}$

| Parameter                                           | Symbol          | Min   | Тур | Max | Unit |

|-----------------------------------------------------|-----------------|-------|-----|-----|------|

| ANALOG INPUT (PIN 14)                               |                 |       |     |     |      |

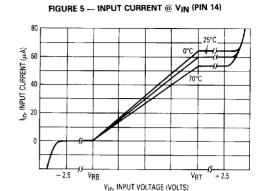

| Input Current (a Vin = VRB (See Figure 5)           | INL             | - 100 | 0   |     | μА   |

| Input Current (a Vin = VRT (See Figure 5)           | INH             | _     | 60  | 150 | μА   |

| Input Capacitance (VRT - VRB = 2.0 V, See Figure 4) | Cin             | _     | 36  | _   | pF   |

| Input Capacitance (VRT - VRB = 1.0 V, See Figure 4) | C <sub>in</sub> | _     | 55  | _   | pF   |

| Bipolar Offset Error                                | Vos             | _     | 0.1 | _   | LSB  |

## REFERENCE

| Ladder Resistance (VRT to VRB, TA = 25°C) | R <sub>ref</sub> | 104 | 130    | 156 | Ω    |

|-------------------------------------------|------------------|-----|--------|-----|------|

| Temperature Coefficient                   | TC               | _   | + 0.29 | _   | %/°C |

| Ladder Capacitance (Pin 1 open)           | C <sub>ref</sub> | _   | 25     | _   | pF   |

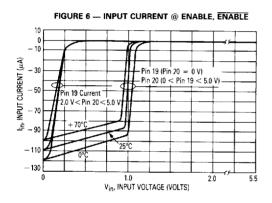

## ENABLE INPUTS (V<sub>CC</sub> = 5.5 V) (See Figure 6)

| Input Voltage — High (Pins 19-20)              | VIHE             | 2.0      |       | _   | V  |

|------------------------------------------------|------------------|----------|-------|-----|----|

| Input Voltage — Low (Pins 19–20)               | VILE             | <u> </u> |       | 0.8 | v  |

| Input Current @ 2.7 V                          | IHE              | _        | 0     | 20  | μΑ |

| Input Current (a 0.4 V (a EN (0 < EN < 5.0 V)  | liL1             | - 400    | - 100 |     | μА |

| Input Current (a 0.4 V (a EN (EN = 0 V)        | I <sub>IL2</sub> | -400     | - 100 |     | μΑ |

| Input Current (a 0.4 V (a EN (EN = 2.0 V)      | lL3              | -20      | - 2.0 |     | μА |

| Input Clamp Voltage (I <sub>IK</sub> = -18 mA) | VIKE             | -1.5     | - 1.3 | _   | V  |

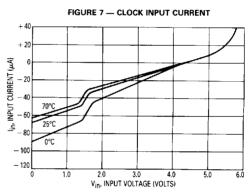

# CLOCK INPUT (VCC = 5.5 V)

| 0200K III 01 (1/CC                             |      |       |       |     | 1   |

|------------------------------------------------|------|-------|-------|-----|-----|

| Input Voltage High                             | VIHC | 2.0   | -     |     | Vdc |

| Input Voltage Low                              | VILC |       | -     | 0.8 | Vdc |

| Input Current (a 0.4 V (See Figure 7)          | lilc | -400  | -80   | _   | μΑ  |

| Input Current (a 2.7 V (See Figure 7)          | Інс  | - 100 | - 20  |     | μΑ  |

| Input Clamp Voltage (I <sub>IK</sub> = -18 mA) | VIKC | - 1.5 | - 1.3 |     | Vdc |

# **DIGITAL OUTPUTS**

| DIG::::12:00                                                                                                |                 |      |      |      |    |

|-------------------------------------------------------------------------------------------------------------|-----------------|------|------|------|----|

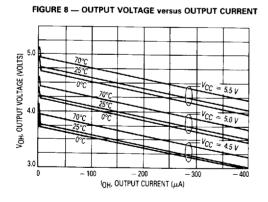

| High Output Voltage ( $I_{OH} = -400 \mu A$ , $V_{CC} = 4.5 V$ , See Figure 8)                              | Voн             | 2.4  | 3.0  | _    | V  |

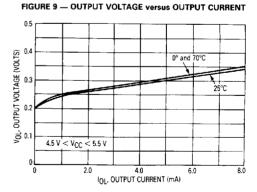

| Low Output Voltage (IOL = 4.0 mA, See Figure 9)                                                             | V <sub>OL</sub> | _    | 0.35 | 0.4  | V  |

| Output Short Circuit Current* (V <sub>CC</sub> = 5.5 V)                                                     | Isc             | _    | 35   |      | mA |

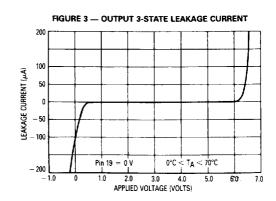

| Output Leakage Current (0.4 $<$ V $_{O}$ $<$ 2.4 V, See Figure 3, V $_{CC}$ = 5.5 V, D0-D7 in 3-State Mode) | <sup>I</sup> LK | - 50 | _    | + 50 | μΑ |

| Output Capacitance (D0-D7 in 3-State Mode)                                                                  | Cout            | _    | 9.0  | _    | pF |

<sup>\*</sup>Only one output is to be shorted at a time, not to exceed 1 second.

| POWER SUPPLIES                                                                     |        | ,    |      |      |    |

|------------------------------------------------------------------------------------|--------|------|------|------|----|

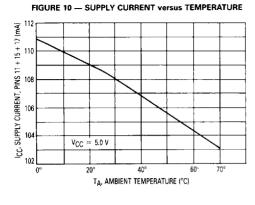

| V <sub>CC(A)</sub> Current (4.5 V < V <sub>CC(A)</sub> < 5.5 V) (Outputs unloaded) | ICC(A) | 10   | 17   | 25   | mA |

| V <sub>CC(D)</sub> Current (4.5 V < V <sub>CC(D)</sub> < 5.5 V) (Outputs unloaded) | ICC(D) | 50   | 90   | 133  | mA |

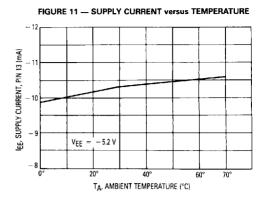

| VEF Current (-6.0 V < VEE < -3.0 V)                                                | IEE    | - 14 | - 10 | -6.0 | mA |

| Power Dissipation (VRT - VRB = 2.0 V) (Outputs unloaded)                           | PD     |      | 618  | 995  | mW |

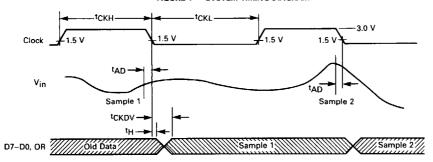

TIMING CHARACTERISTICS ( $T_A = 25^{\circ}C$ ,  $V_{CC} = +5.0$  V,  $V_{EE} = -5.2$  V,  $V_{RT} = +1.0$  V,  $V_{RB} = -1.0$  V, See System Timing Diagram.)

| Parameter                                    | Symbol           | Min      | Тур | Max   | Unit   |

|----------------------------------------------|------------------|----------|-----|-------|--------|

| INPUTS                                       |                  |          | 171 | IVIAX | Unit   |

| Min Clock Pulse Width — High                 | tCKH             | Γ        | 5.0 |       | ns     |

| Min Clock Pulse Width — Low                  | tCKL             | <u> </u> | 15  |       | ns     |

| Max Clock Rise, Fall Time                    | tR.F             |          | 100 |       | ns     |

| Clock Frequency                              | fCLK             | 0        | 30  | 25    | MHz    |

| OUTPUTS                                      | OLK_             | · -      |     |       | IVITIZ |

| New Data Valid from Clock Low                | tCKDV            |          | 19  |       | ns     |

| Aperture Delay                               | tAD              |          | 4.0 |       | ns     |

| Hold Time                                    | tH t             |          | 6.0 |       | ns     |

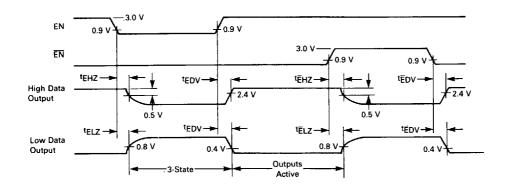

| Data High to 3-State from Enable Low*        | t <sub>EHZ</sub> | _        | 27  |       | ns     |

| Data Low to 3-State from Enable Low*         | tELZ             |          | 18  |       | ns     |

| Data High to 3-State from Enable High*       | tĒHZ             |          | 32  |       | ns     |

| Data Low to 3-State from Enable High*        | tĒLZ             |          | 18  |       | ns     |

| Valid Data from Enable High (Pin 20 = 0 V)*  | tEDV             |          | 15  |       | ns     |

| Valid Data from Enable Low (Pin 19 = 5.0 V)* | tĒDV             |          | 16  |       | ns     |

| Output Transition Time* (10%-90%)            | ttr              |          | 8.0 |       | ne     |

<sup>\*</sup>See Figure 2 for output loading.

# PIN DESCRIPTIONS

| PIN DESCRIPTIONS   |                   |                         |                                                                                                                                                                       |  |  |

|--------------------|-------------------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Symbol             | Pin<br>L,P Suffix | DW Suffix               | Description                                                                                                                                                           |  |  |

| VRM                | 1                 | 1                       | The midpoint of the reference resistor ladder. Bypassing can be done at this point to improve performance at high frequencies.                                        |  |  |

| GND                | 2, 12<br>16, 22   | 2, 13, 17<br>18, 25, 26 | Digital ground. The pins should be connected directly together, and through a low impedance path to the power supply.                                                 |  |  |

| OVR                | 3                 | 3                       | Overrange output. Indicates V <sub>in</sub> is more positive than V <sub>RT</sub> 1/2 LSB. This output does not have 3-state capability.                              |  |  |

| D7-DØ              | 4-10, 21          | 4–10, 24                | Digital Outputs. D7 (Pin 4) is the MSB. DØ (Pin 21 or 24) is the LSB. LSTTL compatible with 3-state capability.                                                       |  |  |

| V <sub>CC(D)</sub> | 11, 17            | 11, 12<br>19, 20        | Power supply for the digital section. $\pm 5.0 \text{ V}$ , $\pm 10\%$ required. Reference to digital ground.                                                         |  |  |

| V <sub>EE</sub>    | 13                | 14                      | Negative Power supply. Nominally $-5.2$ V, it can range from $-3.0$ to $-6.0$ V, and must be more negative than V <sub>RB</sub> by $>1.3$ V. Reference to analog gnd. |  |  |

| V <sub>in</sub>    | 14                | 15                      | Signal voltage input. This voltage is compared to the reference<br>to generate a digital equivalent. Input impedance is nominally<br>16–33K in parallel with 36 pF.   |  |  |

| V <sub>CC(A)</sub> | 15                | 16                      | Power supply for the analog section. $\pm 5.0  \text{V}, \pm 10\%$ required. Reference to analog ground.                                                              |  |  |

| CLK                | 18                | 21                      | Clock input. TTL compatible.                                                                                                                                          |  |  |

| EN                 | 19                | 22                      | Enable input. TTL compatible, a logic 1 (and $\overline{EN}$ at a logic 0 enables the data outputs. A logic 0 puts the outputs in a 3-state mode.                     |  |  |

| EN                 | 20                | 23                      | Enable input. TTL compatible, a logic 0 (and EN at a logic 1) enables the data outputs. A logic 1 puts the outputs in a 3-state mode.                                 |  |  |

| V <sub>RB</sub>    | 23                | 27                      | The bottom (most negative point) of the internal reference resistor ladder.                                                                                           |  |  |

| V <sub>RT</sub>    | 24                | 28                      | The top (most positive point) of the internal reference resistor ladder.                                                                                              |  |  |

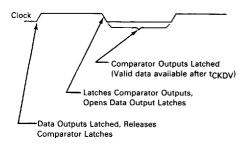

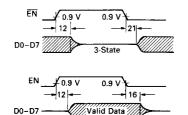

### FIGURE 1 -- SYSTEM TIMING DIAGRAM

tCKDV and tH measured at output levels of 0.8 and 2.4 volts.

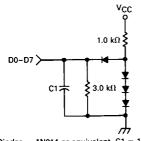

# FIGURE 2 — DATA OUTPUT TEST CIRCUIT

Diodes = 1N914 or equivalent, C1 ≈ 15 pF

FIGURE 4 - INPUT CAPACITANCE @ VIN (PIN 14) 100 C, CAPACITANCE (pF)  $V_{RT} - V_{RB} = 1.0 V$ 40  $V_{RT} - V_{RB} = 2.0 V$ VRB VRT Vin, INPUT VOLTAGE (VOLTS)

### **DESIGN GUIDELINES**

### INTRODUCTION

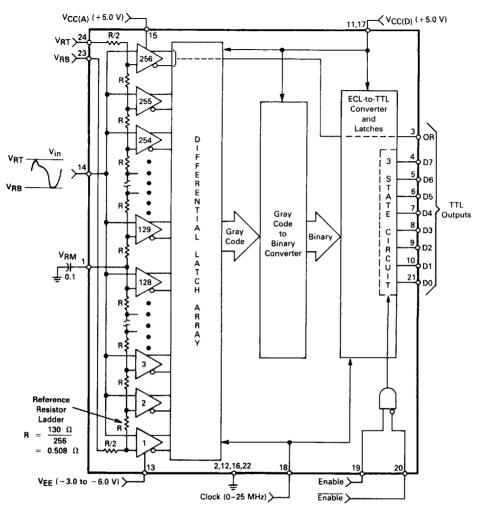

The MC10319 is a high-speed, 8-bit, parallel ("Flash") type analog-to-digital converter containing 256 comparators at the front end. See Figure 17 for a block diagram. The comparators are arranged such that one input of each is referenced to evenly spaced voltages, derived from the reference resistor ladder. The other input of the comparators is connected to the input signal (Vin). Some of the comparator's differential outputs will be "true," while other comparators will have "not true" outputs, depending on their relative position. Their outputs are then latched, and converted to an 8-bit Grey code by the Differential Latch Array. The Grey code ensures any input errors due to cross talk, feed-thru, or timing disparaties, result in glitches at the output of only a few LSBs, rather than the more traditional 1/2 scale and 1/4 scale glitches.

The Grey code is then translated to an 8-bit binary code, and the differential levels are translated to TTL levels before being applied to the output latches. EN-ABLE inputs at this final stage permit the TTL outputs (except Overrange) to be put into a high impedance (3-state) condition.

### **ANALOG SECTION**

### SIGNAL INPUT

The signal voltage to be digitized (Vin) is applied simultaneously to one input of each of the 256 comparators through Pin 14. The other inputs of the comparators are connected to 256 evenly spaced voltages derived from the reference ladder. The output code depends on the relative position of the input signal and the reference voltages. The comparators have a bandwidth of >50 MHz, which is more than sufficient for the allowable (Nyquist theory) input frequency of 12.5 MHz.

The current into Pin 14 varies linearly from 0 (when  $V_{in} = V_{RB}$ ) to  $\approx$ 60  $\mu$ A (when  $V_{in} = V_{RT}$ ). If  $V_{in}$  is taken below VRB or above VRT, the input current will remain at the value corresponding to VRB and VRT respectively (see Figure 5). However, Vin must be maintained within the absolute range of  $\pm 2.5$  volts (with respect to ground) - otherwise excessive currents will result at Pin 14, due to internal clamps.

The input capacitance at Pin 14 is typically 36 pF if  $[V_{RT} - V_{RB}]$  is 2.0 volts, and increases to 55 pF if  $[V_{RT}]$ VRB] is reduced to 1.0 volt (see Figure 4). The capacitance is constant as Vin varies from VRT down to ≈0.1 volt above VRB. Taking Vin to VRB will show an increase in the capacitance of  $\approx$ 50%. If  $V_{\text{in}}$  is taken above VRT, or below VRB, the capacitance will stay at the values corresponding to VRT and VRB, respectively.

The source impedance of the signal voltage should be maintained below 100  $\Omega$  (at the frequencies of interest) in order to avoid sampling errors.

### REFERENCE

The reference resistor ladder is composed of a string of equal value resistors so as to provide 256 equally spaced voltages for the comparators (see Figure 17 for the actual configuration). The voltage difference between adjacent comparators corresponds to 1 LSB of the input range. The first comparator (closest to VRR) is referenced 1/2 LSB above VBB, and the 256th comparator (for the overrange) is referenced 1/2 LSB below VRT. The total resistance of the ladder is nominally 130  $\Omega_{\rm r}$  ± 20%, requiring 15.4 mA @ 2.0 volts, and 7.7 mA @ 1.0 volt. There is a nominal warm-up change of  $\approx +9.0\%$ in the ladder resistance due to the +0.29%/°C temperature coefficient.

The minimum recommended span [VRT - VRR] is 1.0 volt. A lower span will allow offsets and nonlinearities to become significant. The maximum recommended span is 2.1 volts due to power limitations of the resistor ladder. The span may be anywhere within the range of -2.1 to +2.1 volts with respect to ground. and VRR must be at least 1.3 volts more positive than VFF. The reference voltages must be stable and free of noise and spikes, since the accuracy of a conversion is directly related to the quality of the reference.

In most applications, the reference voltages will remain fixed. In applications involving a varying reference for modulation or signal scrambling, the modulating signal may be applied to VRT, or VRB, or both. The output will vary inversly with the reference signal, introducing a nonlinearity into the transfer function. The addition of the modulating signal and the dc level applied to the reference must be such that the absolute voltage at VRT and VRB are maintained within the values listed in the Recommended Operating Limits. The RMS value of the span must be maintained ≤2.1 volts.

VRM (Pin 1) is the midpoint of the resistor ladder, excluding the Overrange comparator. The voltage at VRM is:

$$\frac{V_{RT} + V_{RB}}{2.0} - 1/2 LSB$$

In most applications, bypassing this pin to ground (0.1 μF) is sufficient to maintain accuracy. In applications involving very high frequencies, and where linearity is critical, it may be necessary to trim the voltage at the midpoint. A means for accomplishing this is indicated in Figure 18.

### **POWER SUPPLIES**

VCC(A) is the positive power supply for the comparators, and VCC(D) is the positive power supply for the digital portion. Both are to be  $\pm 5.0$  volts,  $\pm 10\%$ , and the two are to be within 100 millivolts of each other. There is indirect internal coupling between VCC(D) and VCC(A). If they are powered separately, and one supply fails, there will be current flow through the MC10319 to the failed supply.

ICC(A) is nominally 17 mA, and does not vary with clock frequency or with Vin. It does vary linearly with VCC(A), ICC(D) is nominally 90 mA, and is independent of clock frequency. It does vary, however, by 6-7 mA as Vin is changed, with the lowest current occuring when  $V_{in} = V_{RT}$ . It varies linearly with  $V_{CC(D)}$ .

VEF is the negative power supply for the comparators, and is to be within the range -3.0 to -6.0 volts. Additionally, VEE must be at least 1.3 volts more negative than VRB. IEE is a nominal - 10 mA, and is independent of clock frequency, Vin, and VFF.

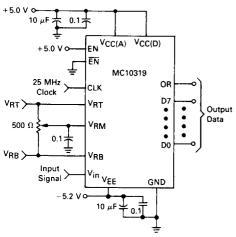

For proper operation, the supplies must be bypassed at the IC. A 10  $\mu$ F tantalum, in parallel with a 0.1  $\mu$ F ceramic is recommended for each supply to ground.

### DIGITAL SECTION

### CLOCK

The Clock input is TTL compatible with a typical frequency range of 0 to 30 MHz. There is no duty cycle limitations, but the minimum low and high times must be adhered to. See Figure 7 for the input current requirements.

The conversion sequence is shown in Figure 19, and is as follows:

- On the rising edge, the data output latches are latched with old data, and the comparator output latches are released to follow the input signal (Vin).

- During the high time, the comparators track the input signal. The data output latches retain the old data.

- On the falling edge, the comparator outputs are latched with the data immediately prior to this edge. The conversion to digital occurs within the device, and the data output latches are released to indicate the new data within 20 ns.

- · During the clock low time, the comparator outputs remain latched, and the data output latches remain transparent.

A summary of the sequence is that data present at Vin just prior to the Clock falling edge is digitized and available at the data outputs immediately after that same falling edge.

The comparator output latches provide the circuit with an effective sample-and-hold function, eliminating the need for an external sample-and-hold.

### **ENABLE INPUTS**

The two Enable inputs are TTL compatible, and are used to change the data outputs (D7-D0) from active to 3-state. This capability allows cascading two MC10319s into a 9-bit configuration, flip-flopping two MC10319s into a 50 MHz configuration, connecting the outputs directly to a data bus, multiplexing multiple converters, etc. See the Applications Information section for more details. For the outputs to be active, Pin 19 must be a Logic "1," and Pin 20 must be a Logic "0." Changing either input will put the outputs into the high impedance mode. The Enable inputs affect only the state of the outputs - they do not inhibit a conversion. The input current into Pins 19 and 20 is shown in Figure 6, and the input — output timing is shown in Figure 1 and 20. Leaving either pin open is equivalent to a Logic "1," although good design practice dictates that an input should never be left open.

The Overrange output (Pin 3) is not affected by the Enable inputs as it does not have 3-state capability.

### OUTPUTS

The data outputs are TTL level outputs with high impedance capabilility. Pin 4 is the MSB (D7), and Pin 21 is the LSB (D0). The eight outputs are active as long as the Enable inputs are true (Pin 19 = high, Pin 20 = low). The timing of the outputs relative to the Clock input and the Enable inputs is shown in Figures 1 and 20. Figures 8 and 9 indicate the output voltage versus load current, while Figure 3 indicates the leakage current when in the high impedance mode.

The output code is natural binary, depicted in the table

The Overrange output (Pin 3) goes high when the input, Vin, is more positive than VRT - 1/2 LSB. This output is always active - it does not have high impedance capability. Besides being used to indicate an input overrange, it is additionally used for cascading two MC10319s to form a 9-bit A/D converter (see Figure 27).

|                             |              | V <sub>RT</sub> , V <sub>RB</sub> (volts) | Output       |                                   |           |

|-----------------------------|--------------|-------------------------------------------|--------------|-----------------------------------|-----------|

| Input                       | 2.048 V, 0 V | +1.0 V, -1.0 V                            | + 1.0 V, 0 V | Code                              | Overrange |

| >V <sub>RT</sub> - 1/2 LSB  | >2.044 V     | >0.9961 V                                 | >0.9980 V    | FFH                               | 1         |

| V <sub>RT</sub> - 1/2 LSB   | 2.044 V      | 0.9961 V                                  | 0.9980 V     | FFH                               | 0 ↔ 1     |

| V <sub>RT</sub> - 1 LSB     | 2.040 V      | 0.992 V                                   | 0.9961 V     | FFH                               | 0         |

| V <sub>RT</sub> - 1-1/2 LSB | 2.036 V      | 0.988 V                                   | 0.9941 V     | FE <sub>H</sub> ↔ FF <sub>H</sub> | 0         |

| Midpoint                    | 1.024 V      | 0.000 V                                   | 0.5000 V     | 80H                               | 0         |

| V <sub>RB</sub> + 1/2 LSB   | 4.0 mV       | - 0.9961 V                                | 1.95 mV      | 00 <sub>H</sub> ↔ 01 <sub>H</sub> | 0         |

| <v<sub>RB</v<sub>           | <0 V         | < - 1.0 V                                 | <0 V         | 00 <sub>H</sub>                   | 0         |

### APPLICATIONS INFORMATION

### **POWER SUPPLIES, GROUNDING**

The PC board layout, and the quality of the power supplies and the ground system at the IC are very important in order to obtain proper operation. Noise, from any source, coming into the device on  $V_{\mbox{\footnotesize{CC}}}$ ,  $V_{\mbox{\footnotesize{EE}}}$ , or ground can cause an incorrect output code due to interaction with the analog portion of the circuit. At the same time, noise generated within the MC10319 can cause incorrect operation if that noise does not have a clear path to ac ground.

Both the VCC and VEE power supplies must be decoupled to ground at the IC (within 1" max) with a 10  $\mu F$  tantalum and a 0.1  $\mu F$  ceramic. Tantalum capacitors are recommended since electrolytic capacitors simply have too much inductance at the frequencies of interest. The quality of the VCC and VEE supplies should then be checked at the IC with a high frequency scope. Noise spikes (always present when digital circuits are present) can easily exceed 400 mV peak, and if they get into the analog portion of the IC, the operation can be disrupted. Noise can be reduced by inserting resistors and/or inductors between the supplies and the IC.

If switching power supplies are used, there will usually be spikes of 0.5 volts or greater at frequencies of 50-200 kHz. These spikes are generally more difficult to reduce because of their greater energy content. In extreme cases, 3-terminal regulators (MC78L05ACP, MC7905.2CT), with appropriate high frequency filtering, should be used and dedicated to the MC10319.

The ripple content of the supplies should not allow their magnitude to exceed the values in the Recommended Operating Limits.

The PC board tracks supplying VCC and VEE to the MC10319 should preferably not be at the tail end of the bus distribution, after passing through a maze of digital circuitry. The MC10319 should be close to the power supply, or the connector where the supply voltages enter the board. If the VCC and VEE lines are supplying considerable current to other parts of the boards, then it is preferable to have dedicated lines from the supply or connector directly to the MC10319

The four ground pins (2, 12, 16, 22) must be connected directly together. Any long path beween them can cause stability problems due to the inductance (@25 MHz) of the PC tracks. The ground return for the signal source must be noise free.

## REFERENCE VOLTAGE CIRCUITS

Since the accuracy of the conversion is directly related to the quality of the references, it is imperative that accurate and stable voltages be provided to VRT and VRB. If the reference span is 2 volts, then 1/2 LSB is only 3.9 millivolts, and it is desireable that VRT and VRB be accurate to within this amount, and furthermore, that they do not drift more than this amount once set. Over the temperature range of 0 to 70°C, a maximum temperature coefficient of 28 ppm/°C is required.

The voltage supplies used for digital circuits should preferably not be used as a source for generating VRT and VRB, due to the noise spikes (50-400 mV) present on the supplies and on their ground lines. Generally  $\pm$  15 volts, or  $\pm$  12 volts, are available for analog circuits. and are usually clean compared to supplies used for digital circuits, although ripple may be present in varying amounts. Ripple is easier to filter out than spikes. however, and so these supplies are preferred.

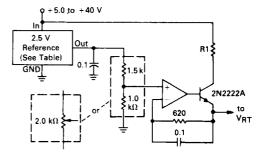

Figure 21 depicts a circuit which can provide an extremely stable voltage to VRT at the current required (the maximum reference current is 19.2 mA @ 2.0 volts). The MC1403 series of reference sources has very low temperature coefficients, good noise rejection, and a high initial accuracy, allowing the circuit to be built without an adjustment pot if the VRT voltage is to remain fixed at one value. Using 0.1% wirewound resistors for the divider provides sufficient accuracy and stability in many cases. Alternately, resistor networks provide high ratio accuracies, and close temperature tracking. If the application requires VRT to be changed periodically, the two resistors can be replaced with a 20 turn, cermet potentiometer. Wirewound potentiometers should not be used for this type of application since the pot's slider jumps from winding to winding, and an exact setting can be difficult to obtain. Cermet pots allow for a smooth continuous adjustment.

In Figure 21, R1 reduces the power dissipation in the transistor, and can be carbon composition. The 0.1  $\mu$ F capacitor in the feedback path provides stability in the unity gain configuration. Recommended op amps are: LM358, MC34001 series, LM308A, LM324, and LM11C. Offset drift is the key parameter to consider in choosing an op amp, and the LM308A has the lowest drift of those mentioned. Bypass capacitors are not shown in Figure 21, but should always be provided at the input to the 2.5 volt reference, and at the power supply pins of the

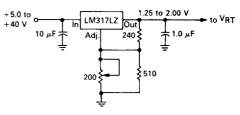

Figure 22 shows a simpler and more economical circuit, using the LM317LZ regulator, but with lower initial accuracy and temperature stability. The op amp/current booster is not needed since the LM317LZ can supply the current directly. In a well controlled environment, this circuit will suffice for many applications. Because of the lower initial accuracy, an adjustment pot is a necessity.

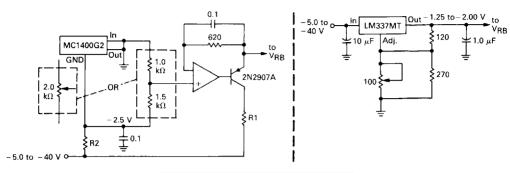

Figure 23 shows two circuits for providing the voltage to VRB. The circuits are similar to those of Figures 21 and 22, and have similar accuracy and stability. The output transistor is a PNP in this case since the circuit must sink the reference current.

65E D

### VIDEO APPLICATIONS

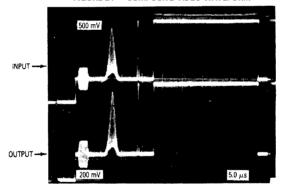

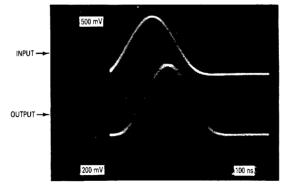

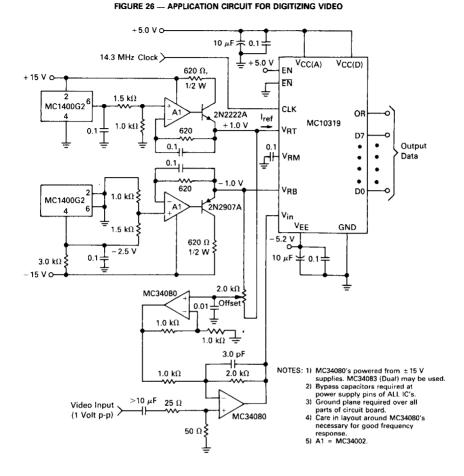

The MC10319 is suitable for digitizing video signals directly without signal conditioning, although the standard 1 volt p-p video signal can be amplified to a 2.0 volt p-p signal for slightly better accuracy. Figure 24 shows the input (top trace) and reconstructed output of a standard NTSC test signal, sampled at 25 MSPS, consisting of a sync pulse, 3.58 MHz color burst, a 3.58 MHz signal in a Sin<sup>2</sup>x envelope, a pulse, a white level signal, and a black level signal. Figure 25 shows a Sin<sup>2</sup>x pulse that has been digitized and reconstructed at 25 MSPS. The width of the pulse is  $\approx 450$  ns at the base. Figure 26 shows an application circuit for digitizing video.

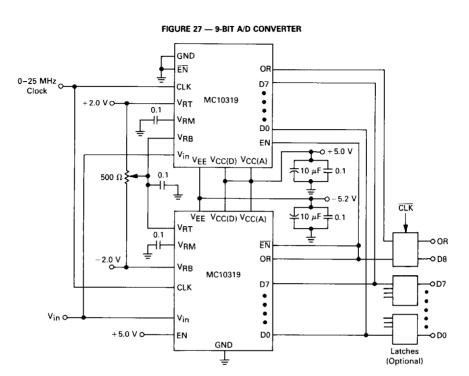

### 9-BIT A/D CONVERTER

Figure 27 shows how two MC10319s can be connected to form a 9-bit converter. In this configuration, the outputs (D7–D0) of the two 8-bit converters are paralleled. The outputs of one device are active, while the outputs of other are in the 3-state mode. The selection is made by the Overrange output of the lower MC10319, which controls Enable inputs on the two devices. Additionally, this output provides the 9th bit.

The reference ladders are connected in series, providing the 512 steps required for 9 bits. The input voltage range is determined by VRT of the upper MC10319, and VRB of the lower device. A minimum of 1.0 volt is required across each converter. The 500  $\Omega$  pot (20 turn cermet) allows for adjustment of the midpoint since the reference resistors of the two MC10319s may not be identical in value. Without the adjustment, a non-equal voltage division would occur, resulting in a nonlinear

conversion. If the references are to be symmetrical about ground (e.g.,  $\pm$  1.0 volt), the adjustment can be eliminated, and the midpoint connected to ground.

The use of latches on the outputs is optional, depending on the application.

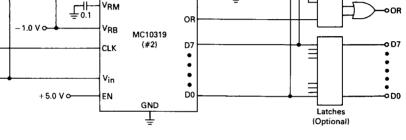

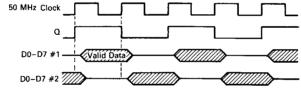

### 50 MHz, 8-BIT A/D CONVERTER

Figure 28 shows how two MC10319s can be connected together in a flip-flop arrangement in order to have an effective conversion speed of 50 MHz. The 74F74 D-type flip-flop provides a 25 MHz clock to each converter, and at the same time, controls the ENABLES so as to alternately enable and disable the outputs. The Overranges do not have 3-state capability, and so cannot be paralleled. Instead they are OR'd together. The use of latches is optional, and depends on the application. Data should be latched, or written to RAM (in a DMA operation), on the high-to-low transition of the 50 MHz clock.

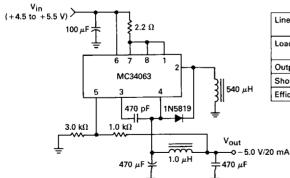

### NEGATIVE VOLTAGE REGULATOR

In the cases where a negative power supply is not available — neither the -3.0 to -6.0 volts, nor a higher negative voltage from which to derive it — the circuit of Figure 29 can be used to generate -5.0 volts from the +5.0 volts supply. The PC board space required is small (~2.0 in²), and it can be located physically close to the MC10319. The MC34063 is a switching regulator, and in Figure 29 is configured in an inverting mode of operation. The regulator operating specifications are also given.

### FIGURE 17 - MC10319

# FIGURE 18 -- ADJUSTING VRM FOR IMPROVED LINEARITY

### FIGURE 19 — CONVERSION SEQUENCE

### FIGURE 20 - ENABLE TO OUTPUT CRITICAL TIMING

Timing @ D7–D0 measured where waveform starts to change. Indicated time values are typical @ 25°C, and are in ns.

# FIGURE 21 — PRECISION V<sub>RT</sub> VOLTAGE SOURCE

R1 = 100  $\Omega$  for +5.0 V 620 Ω for + 15 V

| 2.5 V References             | MC1403U | MC1403AU |

|------------------------------|---------|----------|

| Line Regulation              | 0.5 mV  | 0.5 mV   |

| T <sub>C</sub> (ppm/°C) max  | 40      | 25       |

| ΔV <sub>out</sub> for 0-70°C | 7.0 mV  | 4.4 mV   |

| Initial Accuracy             | ± 1%    | ± 1%     |

# FIGURE 22 — $V_{RT}$ , VOLTAGE SOURCE

| LM317L2                      | Z      |

|------------------------------|--------|

| Line Regulation              | 1.0 mV |

| T <sub>C</sub> (ppm/°C) max  | 60     |

| ΔV <sub>out</sub> for 0-70°C | 8.4 mV |

| Initial Accuracy             | ± 4%   |

# FIGURE 23 - VRB VOLTAGE SOURCES

R1 = 100  $\Omega$  for -5.0 V 620  $\Omega$  for -15 V

R2 = 620  $\Omega$  for -5.0 V 3.0 k $\Omega$  for -15 V

### FIGURE 24 — COMPOSITE VIDEO WAVEFORM

FIGURE 25 — SIN2 X WAVEFORM

74F32

Vino

6

# MC10319

### FIGURE 28 - 50 MHz 8-BIT A/D CONVERTER GND 50 MHz o-Clock CK 74F74 0 ΕN OR CLK D7 + 1.0 V MC10319 VRT (#1)ĒH. **VRM** ٠ D0 ٧RB o + 5.0 V Vin VEE VCC(D) VCC(A)

EN VEE VCC(D) VCC(A)

**VRT**

VRM

# FIGURE 29 — -5.0 VOLT REGULATOR

| Line Regulation    | 4.5 V < V <sub>in</sub> < 5.5 V,<br>I <sub>out</sub> = 10 mA  | 0.16%               |

|--------------------|---------------------------------------------------------------|---------------------|

| Load Regulation    | V <sub>in</sub> = 5.0 V, 8.0 mA <<br>l <sub>out</sub> < 20 mA | 0.4%                |

| Output Ripple      | Vin = 5.0 V, lout = 20 mA                                     | 2 mV <sub>p-p</sub> |

| Short Circuit lout | $V_{in} = 5.0 \text{ V, R1} = 0.1 \Omega$                     | 140 mA              |

| Efficiency         | Vin = 5.0 V, I <sub>out</sub> = 50 mA                         | 52%                 |

APERTURE DELAY - The time difference between the sampling signal (typically a clock edge) and the actual analog signal converted. The actual signal converted may occur before or after the sampling signal, depending on the internal configuration of the converter.

BIPOLAR INPUT - A mode of operation whereby the analog input (of an A-D), or output (of a DAC), includes both negative and positive values. Examples are -1.0 to +1.0 V, -5.0 to +5.0 V, -2.0 to +8.0 V, etc.

BIPOLAR OFFSET ERROR -- The difference between the actual and ideal locations of the 00H to 01H transition, where the ideal location is 1/2 LSB above the most negative reference voltage.

BIPOLAR ZERO ERROR — The error (usually expressed in LSBs) of the input voltage location (of an A-D) of the 80H to 81H transition. The ideal location is 1/2 LSB above zero volts in the case of an A-D setup for a symmetrical bipolar input (e.g., -1.0 to +1.0 V).

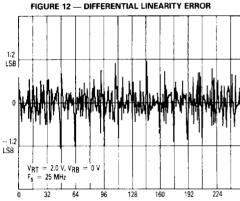

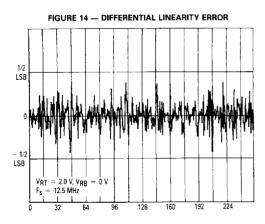

**DIFFERENTIAL NONLINEARITY** — The maximum deviation in the actual step size (one transition level to another) from the ideal step size. The ideal step size is defined as the Full Scale Range divided by 2n (n = number of bits). This error must be within  $\pm 1$  LSB for proper operation.

ECL — Emitter coupled logic.

FULL SCALE RANGE (ACTUAL) - The difference between the actual minimum and maximum end points of the analog input (of an A-D).

FULL SCALE RANGE (IDEAL) — The difference between the actual minimum and maximum end points of the analog input (of an A-D), plus one LSB.

GAIN ERROR — The difference between the actual and expected gain (end point to end point), with respect to the reference, of a data converter. The gain error is usually expressed in LSBs.

GREY CODE - Also known as reflected binary code, it is a digital code such that each code differs from adjacent codes by only one bit. Since more than one bit is never changed at each transition, race condition errors are eliminated.

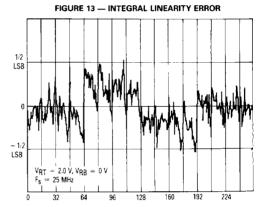

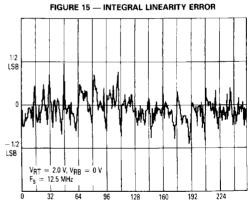

INTEGRAL NONLINEARITY - The maximum error of an A-D, or DAC, transfer function from the ideal straight line connecting the analog end points. This parameter is sensitive to dynamics, and test conditions must be specified in order to be meaningfull. This parameter is the best overall indicator of the device's performance.

LSB — Least Significant Bit. It is the lowest order bit of a binary code.

LINE REGULATION -- The ability of a voltage regulator to maintain a certain output voltage as the input to the regulator is varied. The error is typically expressed as a percent of the nominal output voltage.

LOAD REGULATION — The ability of a voltage regulator to maintain a certain output voltage as the load current is varied. The error is typically expressed as a percent of the nominal output voltage.

MONOTONICITY — The characteristic of the transfer function whereby increasing the input code (of a DAC), or the input signal (of an A-D), results in the output never decreasing.

MSB - Most Significant Bit. It is the highest order bit of a binary code.

NATURAL BINARY CODE — A binary code defined by:  $N = A_{n}2^{n} + \ldots + A_{3}2^{3} + A_{2}2^{2} + A_{1}2^{1} + A_{0}2^{0}$

where each "A" coefficient has a value of 1 or 0. Typically, all zeroes correspond to a zero input voltage of an A-D, and all ones correspond to the most positive input voltage.

NYQUIST THEORY — See Sampling Theorem.

OFFSET BINARY CODE - Applicable only to bipolar input (or output) data converters, it is the same as Natural Binary, except that all zeroes correspond to the most negative input voltage (of an A-D), while all ones correspond to the most positive input.

POWER SUPPLY SENSITIVITY — The change in a data converter's performance with changes in the power supply voltage(s). This parameter is usually expressed in percent of full scale versus  $\Delta V$ .

QUANTITIZATION ERROR — Also known as digitization error or uncertainty. It is the inherent error involved in digitizing an analog signal due to the finite number of steps at the digital output versus the infinite number of values at the analog input. This error is a minimum of ± 1/2 LSB.

RESOLUTION — The smallest change which can be discerned by an A-D converter, or produced by a DAC. It is usually expressed as the number of bits, n, where the converter has 2<sup>n</sup> possible states.

SAMPLING THEOREM — Also known as the Nyquist Theorem. It states that the sampling frequency of an A-D must be no less than 2x the highest frequency (of interest) of the analog signal to be digitized in order to preserve the information of that analog signal.

UNIPOLAR INPUT — A mode of operation whereby the analog input range (of an A-D), or output range (of a DAC), includes values of a signal polarity. Examples are 0 to +2.0 V, 0 to -5.0 V, +2.0 to +8.0 V, etc.

UNIPOLAR OFFSET ERROR — The difference between the actual and ideal locations of the 00H to 01H transition, where the ideal location is 1/2 LSB above the most negative input voltage.