# Sianetics

### **Logic Products**

#### **FEATURES**

- · Synchronous counting and loading

- Up/down counting

- Modulo 16 binary counter 169A

- BCD decade counter '168A

- Two Count Enable inputs for n-bit cascading

- Positive edge-triggered clock

#### DESCRIPTION

The '168A is a synchronous, presettable BCD decade up/down counter featuring an internal carry look-ahead for applications in high-speed counting designs. Synchronous operation is provided by having all flip-flops clocked simultaneously so that the outputs change coincident with each other when so instructed by the Count Enable inputs and internal gating. This mode of operation eliminates the output spikes which are normally associated with asynchronous (ripple clock) counters. A buffered Clock input triggers the flip-flops on the LOWto-HIGH transition of the clock.

# 74LS168A, 74LS169A. S168A, S169A **4-Bit Bidirectional Counters**

4-Bit Up/Down Synchronous Counter **Product Specification**

| TYPE ,   | TYPICAL IMAX | TYPICAL SUPPLY CURRENT (TOTAL) |

|----------|--------------|--------------------------------|

| 74LS168A | 32MHz        | 20mA                           |

| 74S168A  | 70MHz        | 100mA                          |

| 74LS169A | 32MHz        | 20mA                           |

| 74S169A  | 70MHz        | 100mA                          |

#### **ORDERING CODE**

| PACKAGES Plastic DIP | COMMERCIAL RANGE<br>V <sub>CC</sub> = 5V ±5%; T <sub>A</sub> = 0°C to +70°C |

|----------------------|-----------------------------------------------------------------------------|

| Plastic DIP          | N74LS168AN, N74S168AN<br>N74LS169AN, N74S169AN                              |

| Plastic SO           | N74LS169AD, N74LS169AD, N74S169AD                                           |

#### NOTE:

For information regarding devices processed to Military Specifications, see the Signetics Military Products Data Manual

### INPUT AND OUTPUT LOADING AND FAN-OUT TABLE

| PINS  | DESCRIPTION | 74S   | 74LS   |

|-------|-------------|-------|--------|

| PE    | Input       | 1Sul  | 2LSul  |

| CET   | Input       | 2Sul  | 1LSul  |

| Other | Inputs      | 1Sul  | 1LSul  |

| All   | Outputs     | 10Sul | 10LSul |

#### NOTE:

Where a 74S unit load (Sul) is understood to be  $50\mu$ A I<sub>IH</sub> and -2.0mA I<sub>IL</sub> and a 74LS unit load (LSul) is  $20\mu$ A I<sub>IH</sub> and -0.4mA I<sub>II</sub>.

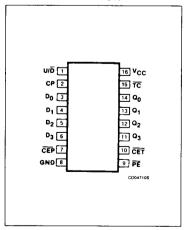

#### PIN CONFIGURATION

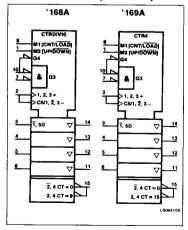

# LOGIC SYMBOL

### LOGIC SYMBOL (IEEE/IEC)

December 4, 1985

5-310

853-0457 81502

# 74LS168A, 74LS169A, S168A, S169A

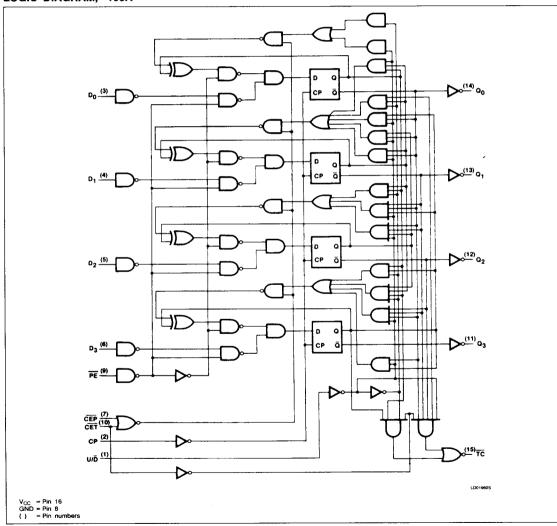

The counter is fully programmable; that is, the outputs may be preset to either level. Presetting is synchronous with the clock and takes place regardless of the levels of the Count Enable inputs. A LOW level on the Parallel Enable (PE) input disables the counter and causes the data at the  $D_{\rm n}$  input to be loaded into the counter on the next LOW-to-HIGH transition of the clock.

The direction of counting is controlled by the  $Up/Down (U/\overline{D})$  input; a HIGH will cause the

count to increase, a LOW will cause the count to decrease.

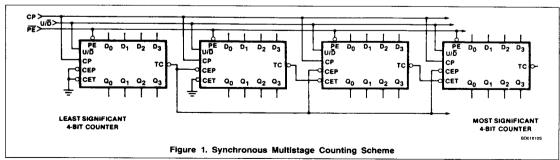

The carry look-ahead circuitry provides for cascading counters for n-bit synchronous applications without additional gating. Instrumental in accomplishing this function are two Count Enable inputs (CET • CEP) and a Terminal Count (TC) output. Both Count Enable inputs must be LOW to count. The CET input is fed forward to enable the TC output. The TC output thus enabled will produce a LOW

output pulse with a duration approximately equal to the HIGH level portion of the  $Q_0$  output. This LOW level  $\overline{\text{TC}}$  pulse is used to enable successive cascaded stages. See Figure A for the fast synchronous multistage counting connections.

The '169A is identical except that it is a Modulo 16 counter.

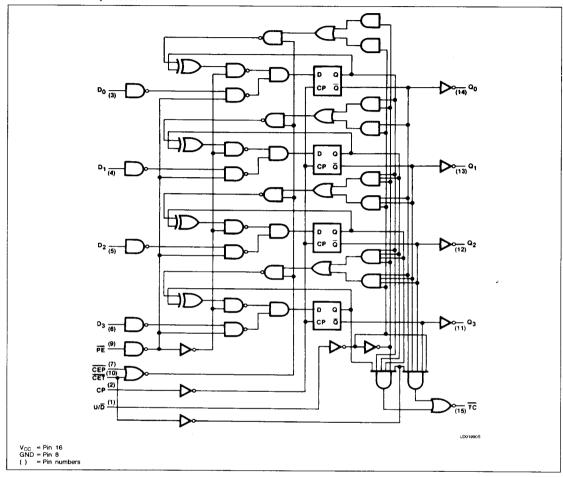

#### LOGIC DIAGRAM, '168A

December 4, 1985

5-311

# 74LS168A, 74LS169A, S168A, S169A

### LOGIC DIAGRAM, '169A

December 4, 1985

5-312

# 74LS168A, 74LS169A, S168A, S169A

### MODE SELECT - FUNCTION TABLE

| OPERATING MODE    |          |        | OUTPUTS |        |        |                |                                  |            |

|-------------------|----------|--------|---------|--------|--------|----------------|----------------------------------|------------|

|                   | СР       | U/D̄   | CEP     | CET    | PE     | D <sub>n</sub> | Qn                               | TC         |

| Parallel Load     | <b>†</b> | X<br>X | X<br>X  | X<br>X |        | í<br>h         | L<br>H                           | (1)<br>(1) |

| Count Up          | 1        | h      | ı       | I      | h      | х              | Count Up                         | (1)        |

| Count Down        | 1        | ī      | ı       | ı      | h      | х              | Count Down                       | (1)        |

| Hold (do nothing) | <b>↑</b> | X<br>X | h<br>X  | X<br>h | h<br>h | X<br>X         | q <sub>n</sub><br>q <sub>n</sub> | (1)<br>H   |

H = HIGH voltage level steady state

h = HIGH voltage level one setup time prior to the LOW-to-HIGH clock transition

L = LOW voltage level steady state

I = LOW voltage level one setup time prior to the LOW-to-HIGH clock transition

X = Don't care

${\bf q}$  = Lower case letters indicate the state of the referenced output prior to the LOW-to-HIGH clock transition  ${\bf \uparrow}$  = LOW-to-HIGH clock transition

#### NOTE:

1. The TC is LOW when CET is LOW and the counter is at Terminal Count. Terminal Count Up is (HHHH) and Terminal Count Down is (LLLL) for '169A. The TC is LOW when CET is LOW and the counter is at Terminal Count. Terminal Count Up is (HLLH) and Terminal Count Down is (LLLL) for '168A.

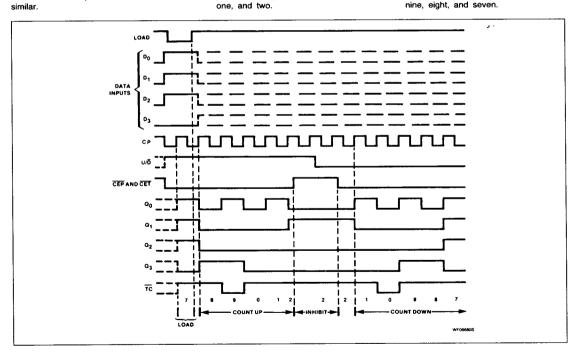

### WAVEFORM (Typical Load, Count, and Inhibit Sequences)

Illustrated below is the following sequence for

- 1. Load (preset) to BCD seven.

- the '168A. The operation of the '169A is 2. Count up to eight, nine (maximum), zero, one, and two.

- Inhibit.

- Count down to one, zero (minimum), nine, eight, and seven.

5-313

# 74LS168A, 74LS169A, S168A, S169A

# ABSOLUTE MAXIMUM RATINGS (Over operating free-air temperature range unless otherwise noted.)

|                  | PARAMETER                                      | 74LS                     | 74S                      | UNIT |

|------------------|------------------------------------------------|--------------------------|--------------------------|------|

| V <sub>CC</sub>  | Supply voltage                                 | 7.0                      | 7.0                      | V    |

| V <sub>IN</sub>  | Input voltage                                  | -0.5 to +7.0             | -0.5 to +5.5             |      |

| I <sub>IN</sub>  | Input current                                  | -30 to +1                | -30 to +5                | mA   |

| V <sub>OUT</sub> | Voltage applied to output in HIGH output state | -0.5 to +V <sub>CC</sub> | -0.5 to +V <sub>CC</sub> | V    |

| TA               | Operating free-air temperature range           | 0 to                     | 70                       | °C   |

#### RECOMMENDED OPERATING CONDITIONS

| PARAMETER       |                                |      | 74LS |       |      | 74S |       |      |

|-----------------|--------------------------------|------|------|-------|------|-----|-------|------|

|                 |                                | Min  | Nom  | Max   | Min  | Nom | Max   | UNIT |

| V <sub>CC</sub> | Supply voltage                 | 4.75 | 5.0  | 5.25  | 4.75 | 5.0 | 5.25  | V    |

| ViH             | HIGH-level input voltage       | 2.0  |      |       | 2.0  |     |       | V    |

| VIL             | LOW-level input voltage        |      |      | + 0.8 |      |     | +0.8  | V    |

| l <sub>ik</sub> | Input clamp current            |      | ,-   | -18   |      |     | -18   | mA   |

| l <sub>OH</sub> | HIGH-level output current      |      |      | -400  |      |     | -1000 | μΑ   |

| l <sub>OL</sub> | LOW-level output current       |      | -    | 8     | -    |     | 20    | mA   |

| TA              | Operating free-air temperature | 0    |      | 70    | 0    |     | 70    | °C   |

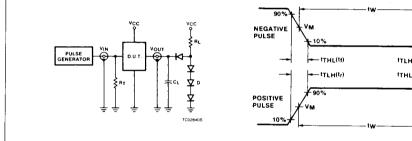

### TEST CIRCUITS AND WAVEFORMS

# Test Circuit For 74 Totem-Pole Outputs

### **DEFINITIONS**

$R_L$  = Load resistor to  $V_{CC}$ ; see AC CHARACTERISTICS for value.  $C_L$  = Load capacitance includes jig and probe capacitance;

see AC CHARACTERISTICS for value.

$\mbox{R}_{\mbox{\scriptsize T}}=\mbox{Termination}$  resistance should be equal to  $\mbox{Z}_{\mbox{\scriptsize OUT}}$  of Pulse Generators.

D = Diodes are 1N916, 1N3064, or equivalent.

$t_{\text{TLH}},\,t_{\text{THL}}$  Values should be less than or equal to the table entries.

| f           |                                 |                                     |              | - 0V      |

|-------------|---------------------------------|-------------------------------------|--------------|-----------|

| -           | + tTHL(tf)                      | tTLH(tr)                            | -            |           |

| -           | TEH(tr)                         | tTHL(ti)                            | •            |           |

| VE          | 90%                             | 90%                                 |              | - AMP (V) |

| 7           | <b>⊬</b> ∨m                     | Ym>                                 | 7            |           |

| <u>0%</u> ₩ |                                 | w                                   | 10%          | - ov      |

|             |                                 |                                     |              | WF06450S  |

|             | V <sub>M</sub> = 1.3V for 74LS; | V <sub>M</sub> ≈ 1.5V for all other | TTL families | 3.        |

### Input Pulse Definition

| FAMILY  | INPUT PULSE REQUIREMENTS |           |             |                  |                  |  |  |  |  |  |

|---------|--------------------------|-----------|-------------|------------------|------------------|--|--|--|--|--|

| TAMIL 1 | Amplitude                | Rep. Rate | Pulse Width | t <sub>TLH</sub> | t <sub>THL</sub> |  |  |  |  |  |

| 74      | 3.0V                     | 1MHz      | 500ns       | 7ns              | 7ns              |  |  |  |  |  |

| 74LS    | 3.0V                     | 1MHz      | 500ns       | 15ns             | 6ns              |  |  |  |  |  |

| 74S     | 3.0V                     | 1MHz      | 500ns       | 2.5ns            | 2.5ns            |  |  |  |  |  |

# 74LS168A, 74LS169A, S168A, S169A

# DC ELECTRICAL CHARACTERISTICS (Over recommended operating free-air temperature range unless otherwise noted.)

| PARAMETER       |                                           |                                                                        |                                  | 74L                             | 5168A, 1 | 169A             | 748  | 69A | UNIT             |      |          |

|-----------------|-------------------------------------------|------------------------------------------------------------------------|----------------------------------|---------------------------------|----------|------------------|------|-----|------------------|------|----------|

|                 |                                           | TEST CONDITIONS1                                                       |                                  |                                 | Min      | Typ <sup>2</sup> | Max  | Min | Typ <sup>2</sup> | Max  | UNII     |

| V <sub>OH</sub> | HIGH-level<br>output voltage              | V <sub>CC</sub> = MIN,<br>V <sub>IL</sub> = MAX, I                     |                                  |                                 | 2.7      | 3.4              |      | 2.7 | 3.4              |      | <b>V</b> |

|                 |                                           |                                                                        |                                  | I <sub>OL</sub> = MAX           |          | 0.35             | 0.5  |     |                  | 0.5  | <b>V</b> |

| V <sub>OL</sub> | LOW-level output voltage                  | V <sub>CC</sub> = MIN, V <sub>IH</sub> = MIN,<br>V <sub>IL</sub> = MAX |                                  | I <sub>OL</sub> = 4mA<br>(74LS) |          | 0.25             | 0.4  |     |                  |      | >        |

| V <sub>IK</sub> | Input clamp voltage                       | V <sub>CC</sub> = MIN,                                                 | I <sub>I</sub> = I <sub>IK</sub> |                                 |          |                  | -1.5 |     |                  | -1.2 | ٧        |

| l <sub>1</sub>  | Input current at maximum input voltage    |                                                                        | Vı                               | = 5.5V                          |          |                  |      |     |                  | 1.0  | mA       |

|                 |                                           | V <sub>CC</sub> = MAX                                                  | V <sub>1</sub> = 7.0V            | PE input                        |          |                  | 40   |     |                  |      | μΑ       |

|                 |                                           |                                                                        |                                  | Other inputs                    | _        |                  | 0.1  |     |                  |      | mA       |

| -               |                                           | V <sub>CC</sub> = MAX                                                  | V <sub>1</sub> = 2.7V            | PE input                        |          |                  | 0.2  |     |                  | 100  | mA       |

| I <sub>IH</sub> | HIGH-level input current                  |                                                                        |                                  | CET input                       |          |                  | 20   |     |                  | 100  | μA       |

|                 |                                           |                                                                        |                                  | Other inputs                    |          |                  | 20   |     |                  | 50   | μΑ       |

|                 |                                           |                                                                        | -                                | PE input                        |          |                  | -0.8 |     | Γ                |      | mA       |

|                 |                                           |                                                                        | $V_{\parallel} = 0.4V$           | Other inputs                    |          |                  | -0.4 |     |                  |      | mA       |

| I <sub>IL</sub> | LOW-level input current                   | V <sub>CC</sub> = MAX                                                  | 1                                | CET input                       |          |                  |      |     |                  | -4.0 | mA       |

|                 |                                           | V <sub>I</sub> = 0.5V                                                  | Other inputs                     |                                 |          |                  |      |     | -2.0             | mA   |          |

| los             | Short-circuit output current <sup>3</sup> | V <sub>CC</sub> = MAX                                                  |                                  |                                 | -20      |                  | -100 | -40 |                  | -100 | mA       |

| lcc             | Supply current <sup>4</sup> (total)       | V <sub>CC</sub> = MAX                                                  |                                  |                                 |          | 20               | 34   |     | 55               | 80   | mA       |

### NOTES:

- 1. For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions for the applicable type.

- 2. All typical values are at V<sub>CC</sub> = 5V, T<sub>A</sub> = 25°C.

- 3. IoS is tested with V<sub>OUT</sub> = +0.5V and V<sub>CC</sub> = V<sub>CC</sub> MAX + 0.5V. Not more than one output should be shorted at a time and duration of the short circuit should not exceed one second.

- 4. I<sub>CC</sub> is measured after applying a momentary 4.5V, then ground to the Clock input with all other inputs grounded and outputs open.

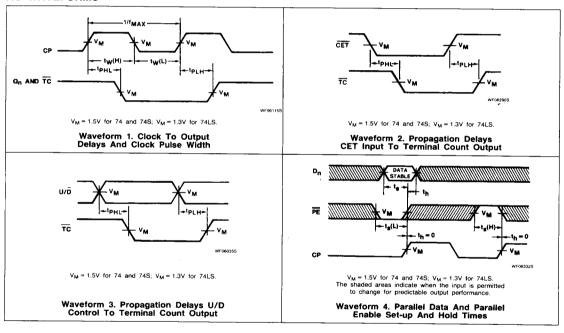

### AC ELECTRICAL CHARACTERISTICS TA = 25°C, VCC = 5.0V

|                                      |                                          |                           | 74  | 4LS                                   | 745 |                                                                |     |                                |      |

|--------------------------------------|------------------------------------------|---------------------------|-----|---------------------------------------|-----|----------------------------------------------------------------|-----|--------------------------------|------|

|                                      | PARAMETER                                | PARAMETER TEST CONDITIONS |     | IDITIONS $C_L = 15pF, R_L = 2k\Omega$ |     | $C_L$ = 15pF, $R_L$ = 280 $\Omega$<br>U/ $\overline{D}$ = HIGH |     | R <sub>L</sub> = 280Ω<br>= LOW | UNIT |

|                                      |                                          |                           | Min | Max                                   | Min | Max                                                            | Min | Max                            |      |

| f <sub>MAX</sub>                     | Maximum clock frequency                  | Waveform 1                | 25  |                                       | 40  |                                                                | 40  |                                | MHz  |

| t <sub>PLH</sub>                     | Propagation delay<br>Clock to Q output   | Waveform 1                |     | 20<br>23                              |     | 12<br>15                                                       |     | 12<br>15                       | ns   |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation delay<br>Clock to TC         | Waveform 1                |     | 35<br>35                              |     | 17<br>15                                                       |     | 15<br>25                       | ns   |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation delay                        | Waveform 2                |     | 14<br>14                              |     | 11<br>15                                                       |     | 11<br>15                       | ns   |

| t <sub>PLH</sub>                     | Propagation delay  U/D control to  TC(b) | Waveform 3                |     | 25<br>29                              |     | 15<br>15                                                       |     | 10<br>20                       | ns   |

#### NOTE

Per industry convention, f<sub>MAX</sub> is the worst case value of the maximum device operating frequency with no constraints on t, t<sub>i</sub>, pulse width or duty cycle.

December 4, 1985

b. Propagation delay time from up/down to terminal count must be measured with the counter at either a minimum or a maximum count. As the logic level of the Up/Down input is changed, the Terminal Count output will follow. If the count is minimum (0), the Terminal Count output transition will be in phase. If the count is maximum (9 for '168A or 15 for 169A, the Terminal Count output will be out of phase.

# 74LS168A, 74LS169A, S168A, S169A

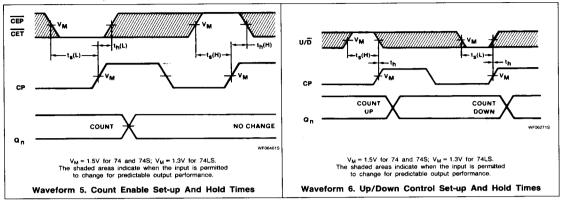

### AC SET-UP REQUIREMENTS TA = 25°C, VCC = 5.0V

|                | PARAMETER                      | TEST CONDITIONS | 74LS |     | 74S |                                                  |      |

|----------------|--------------------------------|-----------------|------|-----|-----|--------------------------------------------------|------|

|                | TATIONICIES                    | TEST CONDITIONS | Min  | Max | Min | Max                                              | UNIT |

| tw             | Clock pulse width              | Waveform 1      | 25   |     | 10  |                                                  | ns   |

| ts             | Setup time, data to clock      | Waveform 4      | 20   |     | 6   |                                                  | ns   |

| th             | Hold time, data to clock       | Waveform 4      | 0    |     | 1   |                                                  | ns   |

| ts             | Setup time, PE to clock        | Waveform 4      | 25   | -   | 9   |                                                  | ns   |

| t <sub>h</sub> | Hold time, PE to clock         | Waveform 4      | 0    |     | 0   |                                                  | ns   |

| ts             | Setup time, CEP & CET to clock | Waveform 5      | 20   |     | 16  |                                                  | ns   |

| th             | Hold time, CEP & CET to clock  | Waveform 5      | 0    |     | 0   |                                                  | ns   |

| ts             | Setup time, U/D to clock       | Waveform 6      | 30   |     | 20  | <del>                                     </del> | ns   |

| t <sub>h</sub> | Hold time, U/D to clock        | Waveform 6      | 0    |     | 0   |                                                  | ns   |

### **AC WAVEFORMS**

# 74LS168A, 74LS169A, S168A, S169A

### AC WAVEFORMS (Continued)