### **General Description**

The MAX7500/MAX7501/MAX7502 temperature sensors accurately measure temperature and provide an over-temperature alarm/interrupt/shutdown output. These devices convert the temperature measurements to digital form using a high-resolution, sigma-delta, analog-to-digital converter (ADC). Communication is through an I<sup>2</sup>C™-compatible 2-wire serial interface. The MAX7500/MAX7501/MAX7502 integrate a timeout feature that offers protection against I2C bus lockups.

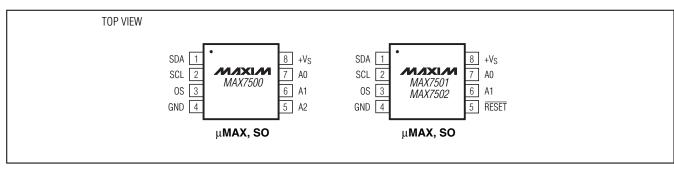

The 2-wire serial interface accepts standard write byte. read byte, send byte, and receive byte commands to read the temperature data and configure the behavior of the open-drain over-temperature shutdown output. The MAX7500 features three address select lines, while the MAX7501 and MAX7502 feature two address select lines and a RESET input. The MAX7500/MAX7501/ MAX7502s' 3.0V to 5.5V supply voltage range, low 250µA supply current, and a lockup-protected I2Ccompatible interface make them ideal for a wide range of applications, including personal computers (PCs), electronic test equipment, and office electronics.

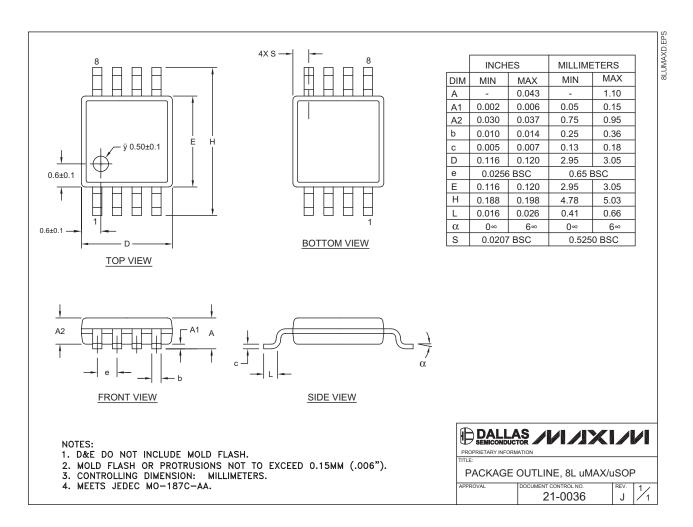

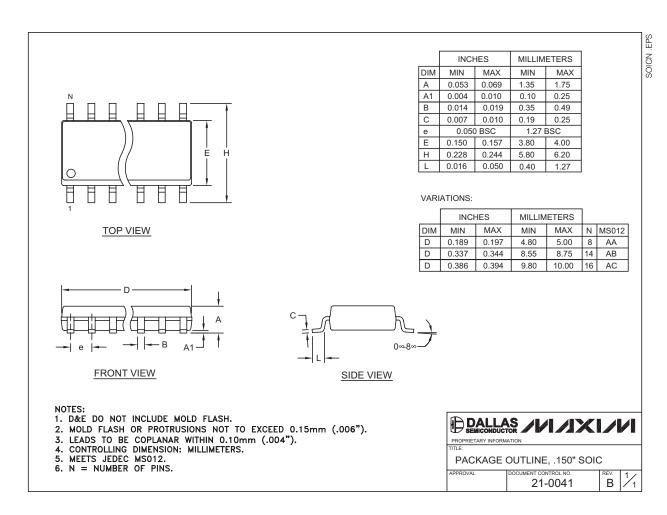

The MAX7500/MAX7501/MAX7502 are available in 8pin µMAX® and SO packages and operate over the -55°C to +125°C temperature range.

### **Applications**

**PCs**

Servers

Office Electronics

Electronic Test Equipment

Industrial Process Control

#### **Features**

- **♦ Timeout Prevents Bus Lockup**

- ♦ I<sup>2</sup>C Bus Interface

- ♦ 3.0V to 5.5V Supply Voltage Range

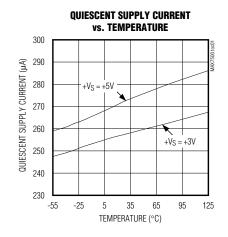

- ♦ 250µA (typ) Operating Supply Current

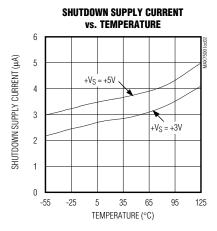

- ♦ 3µA (typ) Shutdown Supply Current

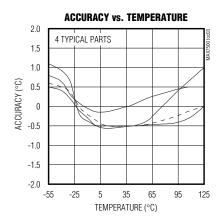

- ♦ ±2°C (max) from -25°C to +100°C Temperature Accuracy

- ♦ µMAX, SO Packages Save Space

- ♦ Separate Open-Drain OS Output Operates as Interrupt or Comparator/Thermostat Input

- ♦ Register Readback Capability

- **♦ Improved LM75 Second Source**

### **Ordering Information**

| PART        | TEMP RANGE      | PIN-PACKAGE |

|-------------|-----------------|-------------|

| MAX7500MSA  | -55°C to +125°C | 8 SO        |

| MAX7500MUA  | -55°C to +125°C | 8 µMAX      |

| MAX7501MSA* | -55°C to +125°C | 8 SO        |

| MAX7501MUA* | -55°C to +125°C | 8 µMAX      |

| MAX7502MSA* | -55°C to +125°C | 8 SO        |

| MAX7502MUA* | -55°C to +125°C | 8 µMAX      |

<sup>\*</sup>Future product—contact factory for availability.

I<sup>2</sup>C is a trademark of Philips Corp.

Purchase of I<sup>2</sup>C components of Maxim Integrated Products Inc., or one of its sublicensed Associated Companies, conveys a license under Philips I<sup>2</sup>C Patent Rights to use these components in an I<sup>2</sup>C system, provided that the system conforms to the I<sup>2</sup>C Standard Specification as defined by Philips.

µMAX is a registered trademark of Maxim Integrated Products, Inc.

## **Pin Configurations**

NIXIN

Maxim Integrated Products 1

#### **ABSOLUTE MAXIMUM RATINGS**

| (Note 1)                                                   | Conti |

|------------------------------------------------------------|-------|

| +V <sub>S</sub> to GND0.3V to +6V                          | 8-F   |

| OS, SDA, SCL to GND0.3V to +6.0V                           | 8-F   |

| All Other Pins to GND0.3V to (+Vs + 0.3V)                  | Oper  |

| Input Current at Any Pin (Note 2)+5mA                      | Junct |

| Package Input Current (Note 2)+20mA                        | Stora |

| ESD Protection (all pins, Human Body Model, Note 3) ±2000V | Lead  |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |        |

|-------------------------------------------------------|--------|

| 8-Pin μMAX (derate 4.5mW/°C above +70°C)              | 362mW  |

| 8-Pin SO (derate 5.9mW/°C above +70°C)                | 471mW  |

| Operating Temperature Range55°C to                    | +125°C |

| Junction Temperature                                  | +150°C |

| Storage Temperature Range65°C to                      | +150°C |

| Lead Temperature (soldering, 10s)                     | +300°C |

|                                                       |        |

- **Note 1:** Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. DC and AC electrical specifications do not apply when operating the device beyond its rated operating conditions.

- Note 2: When the input voltage (V<sub>I</sub>) at any pin exceeds the power supplies (V<sub>I</sub> < GND or V<sub>I</sub> > + V<sub>S</sub>), the current at that pin should be limited to 5mA. The 20mA maximum package input current rating limits the number of pins that can safely exceed the power supplies with an input current of 5mA to 4.

- **Note 3:** Human Body Model, 100pF discharged through a  $1.5k\Omega$  resistor.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

(+Vs = +3.0V to +5.5V, T<sub>A</sub> = -55°C to +125°C, unless otherwise noted. Typical values are at +Vs = +3.3V, T<sub>A</sub> = +25°C.) (Notes 4, 5)

| PARAMETER                            | SYMBOL              | CONDITIONS                        | MIN                   | TYP   | MAX                      | UNITS            |

|--------------------------------------|---------------------|-----------------------------------|-----------------------|-------|--------------------------|------------------|

| A                                    |                     | -25°C ≤ T <sub>A</sub> ≤ +100°C   |                       |       | ±2.0                     | °C               |

| Accuracy                             |                     | -55°C ≤ T <sub>A</sub> ≤ +125°C   |                       |       | ±3.0                     |                  |

| Resolution                           |                     |                                   |                       | 9     |                          | Bits             |

| Conversion Time                      |                     | (Note 6)                          |                       | 100   |                          | ms               |

|                                      |                     | I <sup>2</sup> C inactive         |                       | 0.25  | 0.5                      | mA               |

| Quiescent Supply Current             |                     | Shutdown mode, $+V_S = 3V$        |                       | 3     |                          |                  |

|                                      |                     | Shutdown mode, $+V_S = 5V$        |                       | 5     |                          | μΑ               |

| +V <sub>S</sub> Supply Voltage Range |                     |                                   | 3.0                   |       | 5.5                      | V                |

| OS Output Saturation Voltage         |                     | I <sub>OUT</sub> = 4.0mA (Note 7) |                       |       | 0.8                      | V                |

| OS Delay                             |                     | (Note 8) 1                        |                       |       | 6                        | Conver-<br>sions |

| Tos Default Temperature              | mperature (Note 9)  |                                   |                       | 80    |                          | °C               |

| THYST Default Temperature            |                     | (Note 9)                          |                       | 75    |                          | °C               |

| LOGIC (SDA, SCL, A0, A1, A2)         | •                   |                                   | <u>.</u>              |       |                          |                  |

| Input High Voltage                   | VIH                 |                                   | +V <sub>S</sub> x 0.7 |       |                          | V                |

| Input Low Voltage                    | VIL                 |                                   |                       |       | +V <sub>S</sub> x<br>0.3 | V                |

| Input High Current I <sub>IH</sub>   |                     | $V_{IN} = 5V$                     |                       | 0.005 | 1.0                      | μΑ               |

| Input Low Current I <sub>IL</sub>    |                     | V <sub>IN</sub> = 0V              |                       | 0.005 | 1.0                      | μΑ               |

| Input Capacitance                    |                     | All digital inputs                |                       | 5     |                          | рF               |

| Output High Current                  | Output High Current |                                   |                       |       | 1                        | μΑ               |

| Output Low Voltage                   |                     | I <sub>OL</sub> = 3mA             |                       |       | 0.4                      | V                |

\_\_\_ /N/XI/M

### **ELECTRICAL CHARACTERISTICS (continued)**

$(+V_S = +3.0V \text{ to } +5.5V, T_A = -55^{\circ}\text{C} \text{ to } +125^{\circ}\text{C}, \text{ unless otherwise noted.}$  Typical values are at  $+V_S = +5V, T_A = +25^{\circ}\text{C}.$ ) (Notes 4, 5)

| PARAMETER                                       | SYMBOL         | CONDITIONS                         | MIN                             | TYP                             | MAX | UNITS |

|-------------------------------------------------|----------------|------------------------------------|---------------------------------|---------------------------------|-----|-------|

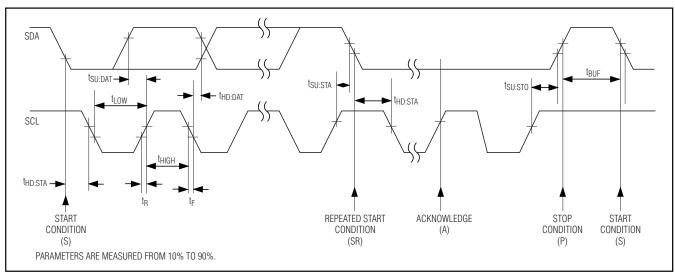

| I <sup>2</sup> C-COMPATIBLE TIMING (Note 1      | 0)             |                                    |                                 |                                 |     |       |

| Serial Clock Frequency                          | fscL           | Bus timeout inactive               | DC                              |                                 | 400 | kHz   |

| Minimum RESET Pulse Width                       |                |                                    | 1                               |                                 |     | μs    |

| Bus Free Time Between STOP and START Conditions | tBUF           |                                    | 1.3                             |                                 |     | μs    |

| START Condition Hold Time                       | thd:Sta        |                                    | 0.6                             |                                 |     | μs    |

| STOP Condition Setup Time                       | tsu:sto        | 90% of SCL to 10% of SDA           | 100                             |                                 |     | ns    |

| Clock Low Period                                | tLOW           |                                    | 1.3                             |                                 |     | μs    |

| Clock High Period                               | tHIGH          |                                    | 0.6                             |                                 |     | μs    |

| START Condition Setup Time                      | tsu:sta        | 90% of SCL to 90% of SDA           | 100                             |                                 |     | ns    |

| Data Setup Time                                 | tsu:dat        | 10% of SDA to 10% of SCL           | 100                             |                                 |     | ns    |

| Data Hold Time                                  | thd:dat        | 10% of SCL to 10% of SDA (Note 11) | 0                               |                                 | 0.9 | μs    |

| Maximum Receive SCL/SDA Rise Time               | t <sub>R</sub> |                                    |                                 | 300                             |     | ns    |

| Minimum Receive SCL/SDA Rise<br>Time            | t <sub>R</sub> | (Note 12)                          |                                 | 20 +<br>0.1 x<br>C <sub>B</sub> |     | ns    |

| Maximum Receive SCL/SDA Fall Time               | t <sub>F</sub> |                                    |                                 | 300                             |     | ns    |

| Minimum Receive SCL/SDA Fall<br>Time            | t <sub>F</sub> | (Note 12)                          |                                 | 20 +<br>0.1 x<br>C <sub>B</sub> |     | ns    |

| Transmit SDA Fall Time                          | t <sub>F</sub> | (Note 12)                          | 20 +<br>0.1 x<br>C <sub>B</sub> |                                 | 250 | ns    |

| Pulse Width of Suppressed Spike                 | tsp            | (Note 13)                          | 0                               |                                 | 50  | ns    |

| SDA Time Low for Reset of Serial Interface      | tTIMEOUT       | (Note 14)                          | 150                             |                                 | 300 | ms    |

- Note 4: All parts operate properly over the +Vs = 3V to 5V supply voltage range. The devices are tested and specified for rated accuracy at their nominal supply voltage. Accuracy typically degrades 1°C per volt of change in +Vs as it varies from the nominal value.

- **Note 5:** All parameters are measured at +25°C. Values over the temperature range are guaranteed by design.

- **Note 6:** This specification indicates how often temperature data is updated. The devices can be read at any time without regard to conversion state, while yielding the last conversion result.

- Note 7: For best accuracy, minimize output loading. Higher sink currents can affect sensor accuracy due to internal heating.

- **Note 8:** OS delay is user programmable up to six "over-limit" conversions before OS is set to minimize false tripping in noisy environments.

- Note 9: Default values set at power-up.

- **Note 10:** All timing specifications are guaranteed by design.

- **Note 11:** A master device must provide a hold time of at least 300ns for the SDA signal to bridge the undefined region of SCL's falling edge.

- **Note 12:**  $C_B$  = total capacitance of one bus line in pF. Tested with  $C_B$  = 400pF.

- Note 13: Input filters on SDA, SCL, and A\_ suppress noise spikes less than 50ns.

- **Note 14:** Holding the SDA line low for a time greater than t<sub>TIMEOUT</sub> causes the devices to reset SDA to the IDLE state of the serial bus communication (SDA set high).

### **Typical Operating Characteristics**

$(T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

### **Pin Description**

| Р       | IN                 |                 |                                                                                                                                                                        |

|---------|--------------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MAX7500 | MAX7501<br>MAX7502 | NAME            | FUNCTION                                                                                                                                                               |

| 1       | 1                  | SDA             | Serial Data Input/Output Line. Open drain. Connect SDA to a pullup resistor.                                                                                           |

| 2       | 2                  | SCL             | Serial Data Clock Input. Open drain. Connect SCL to a pullup resistor.                                                                                                 |

| 3       | 3                  | OS              | Over-Temperature Shutdown Output. Open drain. Connect OS to a pullup resistor.                                                                                         |

| 4       | 4                  | GND             | Ground                                                                                                                                                                 |

| 5       | _                  | A2              | 2-Wire Interface Address Input. Connect A2 to GND or +V <sub>S</sub> to set the desired I <sup>2</sup> C bus address. Do not leave floating. (See Table 1.)            |

| _       | 5                  | RESET           | Active-Low Reset Input. Pull RESET low for longer than the minimum reset pulse width to reset the I <sup>2</sup> C bus and all internal registers to their POR values. |

| 6       | 6                  | A1              | 2-Wire Interface Address Input. Connect A1 to GND or +V <sub>S</sub> to set the desired I <sup>2</sup> C bus address. Do not leave floating. (See Table 1.)            |

| 7       | 7                  | A0              | 2-Wire Interface Address Input. Connect A0 to GND or +V <sub>S</sub> to set the desired I <sup>2</sup> C bus address. Do not leave floating. (See Table 1.)            |

| 8       | 8                  | +V <sub>S</sub> | Positive Supply Voltage Input. Bypass to GND with a 0.1µF bypass capacitor.                                                                                            |

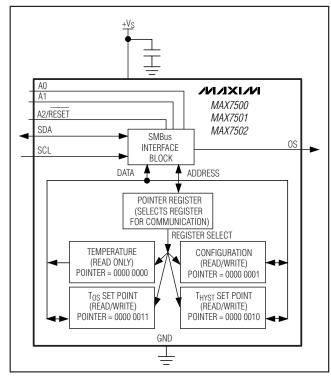

### Detailed Description

The MAX7500/MAX7501/MAX7502 temperature sensors measure temperature, convert the data into digital form using a sigma-delta ADC, and communicate the conversion results through an I<sup>2</sup>C-compatible 2-wire serial interface. These devices accept standard I<sup>2</sup>C commands to read the data, set the over-temperature

alarm (OS) trip thresholds, and configure other characteristics. The MAX7500 features three address select lines (A0, A1, A2) while the MAX7501 and MAX7502 feature two address select lines (A0, A1) and a  $\overline{\text{RESET}}$  input. The MAX7500/MAX7501/MAX7502 operate from +3.0V to +5.5V supply voltages of and consume 250µA of supply current.

Table 1. I<sup>2</sup>C Slave Addresses

| DEVICE  | BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|---------|-------|-------|-------|-------|-------|-------|-------|-------|

| MAX7500 | 1     | 0     | 0     | 1     | A2    | A1    | A0    | RD/W  |

| MAX7501 | 1     | 0     | 0     | 1     | 1     | A1    | A0    | RD/W  |

| MAX7502 | 1     | 0     | 0     | 1     | 0     | A1    | A0    | RD/W  |

Figure 1. Serial Bus Timing

#### I<sup>2</sup>C-Compatible Bus Interface

From a software perspective, the MAX7500/MAX7501/ MAX7502 appear as a set of byte-wide registers that contain temperature data, alarm threshold values, and control bits. A standard I<sup>2</sup>C-compatible 2-wire serial interface reads temperature data and writes control bits and alarm threshold data. Each device responds to its own I<sup>2</sup>C slave address, which is selected using A0, A1, and A2. See Table 1.

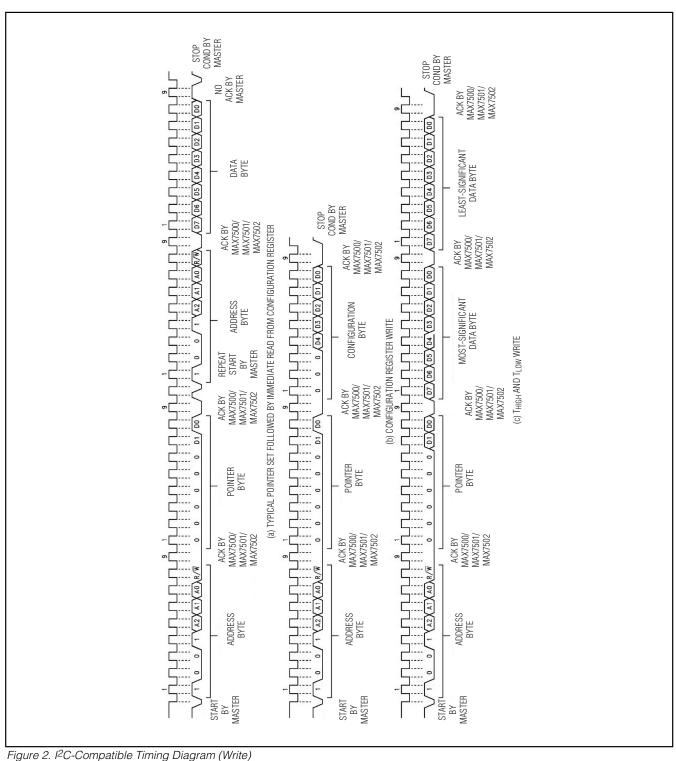

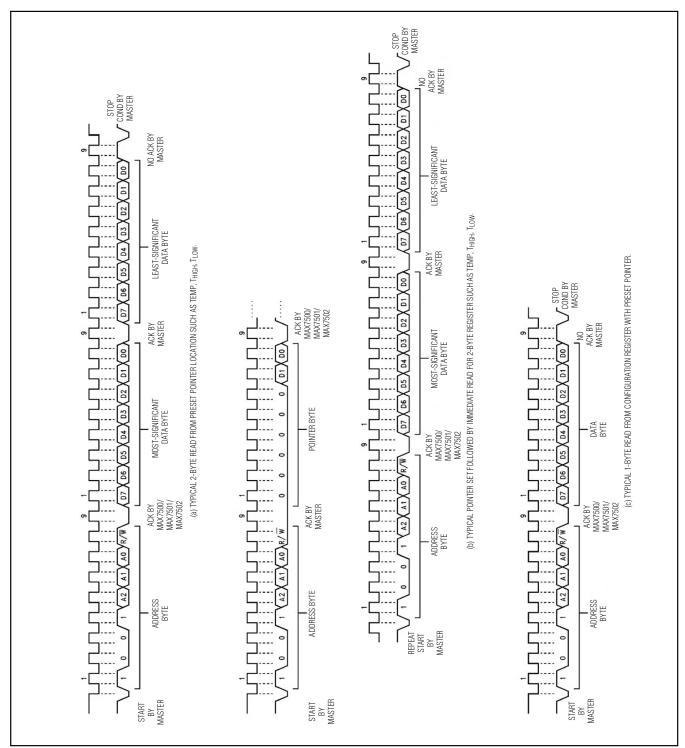

The MAX7500/MAX7501/MAX7502 employ four standard I<sup>2</sup>C protocols: write byte, read byte, send byte, and receive byte (Figures 1, 2, and 3). The shorter receive byte protocol allows quicker transfers, provided that the correct data register was previously selected

by a read-byte instruction. Use caution when using the shorter protocols in multimaster systems, as a second master could overwrite the command byte without informing the first master. The MAX7500 has eight different slave addresses available; therefore, a maximum of eight MAX7500 devices can share the same bus. The MAX7501/MAX7502 each have four different slave addresses available.

MIXIM

Figure 3. I<sup>2</sup>C-Compatible Timing Diagram (Read)

**Table 2. Register Functions**

| REGISTER NAME | ADDRESS (hex) | POR STATE (hex) | POR STATE<br>(BINARY) | POR STATE (°C) | READ/<br>WRITE |

|---------------|---------------|-----------------|-----------------------|----------------|----------------|

| Temperature   | 00            | _               | _                     | _              | Read only      |

| Configuration | 01            | 00              | 0000 0000             | _              | R/W            |

| THYST         | 02            | 4B0             | 0100 1011 0           | 75             | R/W            |

| Tos           | 03            | 500             | 0101 0000 0           | 80             | R/W            |

Table 3. Temperature Register Definition

|                                         | UPPER BYTE  |      |      |     |     |     |     |              |    |    | LO | WER B | YTE |    |    |

|-----------------------------------------|-------------|------|------|-----|-----|-----|-----|--------------|----|----|----|-------|-----|----|----|

| D15                                     | D14         | D13  | D12  | D11 | D10 | D9  | D8  | D7           | D6 | D5 | D4 | D3    | D2  | D1 | D0 |

| Sign bit<br>1= Negative<br>0 = Positive | MSB<br>64°C | 32°C | 16°C | 8°C | 4°C | 2°C | 1°C | LSB<br>0.5°C | ×  | ×  | х  | х     | ×   | ×  | х  |

X = Don't care.

#### **Register Descriptions**

The MAX7500/MAX7501/MAX7502 have an internal pnjunction-based temperature sensor whose analog output is converted to digital form using a 9-bit sigma-delta ADC. The measured temperature and temperature configurations are controlled by the temperature, configuration, THYST, and ToS registers. See Table 2.

#### Temperature Register

Read the measured temperature through the temperature register. The temperature data format is 9 bits, two's complement, and the register is read out in 2 bytes: an upper byte and a lower byte. Bit D15 is the sign bit. When bit D15 is 1, the temperature reading is negative. When bit D15 is zero, the temperature reading is positive. Bits D14–D7 contain the temperature data, with the LSB representing 0.5°C and the MSB representing 64°C (see Table 3). The MSB is transmit-

**Table 4. Temperature Data Output**

| TEMPEDATURE (00) | DIGITAL OUT         | PUT  |

|------------------|---------------------|------|

| TEMPERATURE (°C) | BINARY              | hex  |

| +125             | 0111 1101 0xxx xxxx | 7D0x |

| +25              | 0001 1001 0xxx xxxx | 190x |

| +0.5             | 0000 0000 1xxx xxxx | 008x |

| 0                | 0000 0000 0xxx xxxx | 000x |

| -0.5             | 1111 1111 1xxx xxxx | FF8x |

| -25              | 1110 0110 0xxx xxxx | E70x |

| -55              | 1100 1000 0xxx xxxx | C90x |

ted first. The last 7 bits of the lower byte, bits D6–D0, are don't cares. When reading the temperature register, bits D6–D0 must be ignored. When the measured temperature is greater than +127.5°C, the value stored in the temperature register is clipped to 7F8h. When the measured temperature is below -64°C, the value in the temperature register is clipped to BF8h.

During the time of reading the temperature register, any changes in temperature are ignored until the read is completed. The temperature register is updated upon completion of the next conversion.

Table 3 lists the temperature register definition.

#### Configuration Register

The 8-bit configuration register sets the fault queue, OS polarity, shutdown control, and whether the OS output functions in comparator or interrupt mode. When writing to the configuration register, set bits D7, D6, and D5 to zero. See Table 5.

Bits D4 and D3, the fault queue bits, determine the number of faults necessary to trigger an OS condition. See Table 6. The number of faults set in the queue must occur to trip the OS output. The fault queue prevents OS false tripping in noisy environments.

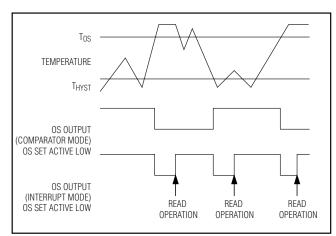

Set bit D2, the OS polarity bit, to zero to force the OS output active low. Set bit D2 to 1 to set the OS output polarity to active high. OS is an open-drain output under all conditions and requires a pullup resistor to output a high voltage. See Figure 4.

Set bit D1, the comparator/interrupt bit to zero to run the over-temperature shutdown block in comparator mode. In comparator mode, OS is asserted when the

Table 5. Configuration Register Definition

| ſ | D7 | D6 | D5 | D4          | D3          | D2          | D1                       | D0       |

|---|----|----|----|-------------|-------------|-------------|--------------------------|----------|

|   | 0  | 0  | 0  | Fault queue | Fault queue | OS polarity | Comparator/<br>interrupt | Shutdown |

Table 6. Configuration Register Fault Queue Bits

| D4 | D3 | NO. OF FAULTS |

|----|----|---------------|

| 0  | 0  | 1 (POR state) |

| 0  | 1  | 2             |

| 1  | 0  | 4             |

| 1  | 1  | 6             |

temperature rises above the  $T_{OS}$  value. OS is deasserted when the temperature drops below the  $T_{HYST}$  value. See Figure 4. Set bit D1 to 1 to run the over-temperature shutdown block in interrupt mode. OS is asserted in interrupt mode when the temperature rises above the  $T_{OS}$  value or falls below the  $T_{HYST}$  value. OS is deasserted only after performing a read operation.

Set bit D0, the shutdown bit, to zero for normal operation. Set bit D0 to 1 to shut down the MAX7500/MAX7501/MAX7502 internal blocks, dropping the supply current to 3µA. The I<sup>2</sup>C interface remains active as long as the shutdown bit is set. The Tos, Thyst, and configuration registers can still be written to and read from while in shutdown.

#### Tos and Thyst Registers

In comparator mode, the OS output behaves like a thermostat. The output asserts when the temperature rises above the limit set in the Tos register. The output deasserts when the temperature falls below the limit set in the THYST register. In comparator mode, the OS output can be used to turn on a cooling fan, initiate an emergency shutdown signal, or reduce system clock speed.

Figure 4. OS Timing Diagram

In interrupt mode, exceeding ToS also asserts OS. OS remains asserted until a read operation is performed on any of the registers. Once OS has asserted due to crossing above ToS and is then reset, it is asserted again only when the temperature drops below THYST. The output remains asserted until it is reset by a read. Putting the MAX7500/MAX7501/MAX7502 into shutdown mode also resets OS.

The Tos and THYST registers are accessed with 2 bytes, with bits D15–D7 containing the data. Bits D6–D0 are don't cares when writing to these two registers and read-back zeros when reading from these registers. The LSB represents 0.5°C while the MSB represents 64°C. See Table 7.

Table 7. Tos and Thyst Register Definitions

| COMMAND | UPPER BYTE                               |             |      |      |     |     |     |     | LOWER BYTE   |    |    |    |    |    |    |    |

|---------|------------------------------------------|-------------|------|------|-----|-----|-----|-----|--------------|----|----|----|----|----|----|----|

|         | D15                                      | D14         | D13  | D12  | D11 | D10 | D9  | D8  | D7           | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

| Write   | Sign bit<br>1 = negative<br>0 = positive | MSB<br>64°C | 32°C | 16°C | 8°C | 4°C | 2°C | 1°C | LSB<br>0.5°C | x  | X  | x  | X  | Х  | X  | x  |

| Read    | Sign bit<br>1 = negative<br>0 = positive | MSB<br>64°C | 32°C | 16°C | 8°C | 4°C | 2°C | 1°C | LSB<br>0.5°C | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

X = Don't care.

#### Shutdown

Set bit D0 in the configuration register to 1 to place the MAX7500/MAX7501/MAX7502 in shutdown mode and reduce supply current to  $3\mu$ A.

#### **Power-Up and Power-Down**

The MAX7500/MAX7501/MAX7502 power up to a known state, as indicated in Table 2. Some of these settings are summarized below:

- Comparator mode

- Tos = +80°C

- $T_{HYST} = +75^{\circ}C$

- OS active low

- Pointer = 00

#### **Internal Registers**

The MAX7500/MAX7501/MAX7502s' pointer register selects between four data registers. See Figure 5. At power-up, the pointer is set to read the temperature register at address 00. The pointer register latches the last location to which it was set. All registers are read and write, except the temperature register, which is read only.

Write to the configuration register by writing an address byte, a data pointer byte, and a data byte. If 2 data bytes are written, the second data byte overrides the first. If more than 2 data bytes are written, only the first 2 bytes are recognized while the remaining bytes are ignored. The Tos and Thyst registers require 1 address byte and 1 pointer byte and 2 data bytes. If only 1 data byte is written, it is saved in bits D15–D8 of the respective register. If more than 2 data bytes are written, only the first 2 bytes are recognized while the remaining bytes are ignored.

Read from the MAX7500/MAX7501/MAX7502 in one of two ways. If the location latched in the pointer register is set from the previous read, the new read consists of an address byte, followed by retrieving the corresponding number of data bytes. If the pointer register needs to be set to a new address, perform a read operation by writing an address byte, pointer byte, repeat start, and another address byte.

An inadvertent 8-bit read from a 16-bit register, with the D7 bit low, can cause the MAX7500/MAX7501/MAX7502 to stop in a state where the SDA line is held low. Ordinarily, this would prevent any further bus communication until the master sends nine additional clock cycles or SDA goes high. At that time, a stop condition

Figure 5. Block Diagram

resets the device. With the MAX7500/MAX7501/MAX7502, if the additional clock cycles are not generated by the master, the bus resets and unlocks after the bus timeout period has elapsed.

The MAX7501/MAX7502 can be reset by pulsing RESET low.

#### **Bus Timeout**

Communication errors sometimes occur due to noise pickup on the bus. In the worst case, such errors can cause the slave device to hold the data line low, thereby preventing other devices from communicating over the bus. The MAX7500/MAX7501/MAX7502s' internal bus timeout circuit resets the bus and releases the data line if the line is low for more than 250ms. When the bus timeout is active, the minimum serial clock frequency is limited to 6Hz.

#### RESET

The RESET input on the MAX7501/MAX7502 provides a way to reset the I<sup>2</sup>C bus and all the internal registers to their initial POR values. To reset, apply a low pulse with a duration of at least 1µs to the RESET input.

### Applications Information

#### **Digital Noise**

The MAX7500/MAX7501/MAX7502 feature an integrated lowpass filter on both the SCL and the SDA digital lines to mitigate the effects of bus noise. Although this filtering makes communication robust in noisy environments, good layout practices are always recommended. Minimize noise coupling by keeping digital traces away from switching power supplies. Ensure that digital lines containing high-speed data communications cross at right angles to the SDA and SCL lines.

Excessive noise coupling into the SDA and SCL lines on the MAX7500/MAX7501/MAX7502—specifically noise with amplitude greater than 400mV<sub>P-P</sub> (the MAX7500/MAX7501/MAX7502s' typical hysteresis), overshoot greater than 300mV above +Vs, and undershoot more than 300mV below GND—may prevent suc-

cessful serial communication. Serial bus no-acknowledge is the most common symptom, causing unnecessary traffic on the bus.

Care must be taken to ensure proper termination within a system with long PC board traces or multiple parts on the bus. Resistance can be added in series with the SDA and SCL lines to further help filter noise and ringing. If it proves to be necessary, a  $5k\Omega$  resistor should be placed in series with the SCL line, placed as close as possible to SCL. This  $5k\Omega$  resistor, with the 5pF to 10pF stray capacitance of the MAX7500/MAX7501/MAX7502 provide a 6MHz to 12MHz lowpass filter, which is sufficient filtering in most cases.

### Chip Information

**TRANSISTOR COUNT: 9611**

PROCESS: CMOS

### **Package Information**

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to <a href="https://www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>.)

### Package Information (continued)

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to <a href="https://www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>.)

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.