OCTOBER 2003

### PRODUCT NOTIFICATION

| DEVICE      | LITERATURE NO. |

|-------------|----------------|

| TLV320AIC12 | SLWS115        |

| TLV320AIC13 | SLWS139        |

| TLV320AIC14 | SLWS140        |

| TLV320AIC15 | SLWS141        |

| TLV320AIC20 | SLAS363        |

| TLV320AIC21 | SLAS365        |

| TLV320AIC24 | SLAS366        |

| TLV320AIC25 | SLAS367        |

Texas Instruments (TI) has recently identified a problem in the product models listed above related to DLL clock-generation. When a clock-generation mode is used that powers up the delay-locked-loop (DLL), the DLL may not startup properly when initiated, resulting in the audio master clock not functioning. This results in the codec in the products not functioning. This issue does not affect applications that do not enable the product's DLL.

Since this issue does not affect operation if the DLL is not enabled, customers are recommended to ensure their system does not enable the product's DLL. The DLL is enabled anytime the *P* value in control register #4 (pertaining to clock generation) is NOT set equal to 8. The DLL is used whenever the part is in *fine* sampling mode, as described in Section 3.1 of the data manual, so the recommended mode to use is the *coarse* sampling mode, which requires P=8.

At present, TI does not have a screening procedure in place to detect product with the DLL issue, but the company also realizes that many customers do not use the DLL in their systems and will be unaffected by this issue.

TI is not confident of the operation of the DLL in this product at this time. To ensure customers have been made aware of this issue, orders for these parts will only be filled upon return of a signed waiver until this issue is resolved. The company has initiated an investigation to fully understand the root cause of this problem and determine what appropriate long-term corrective action should be taken. TI recommends that all customers presently using these parts contact the company immediately, so they can receive updates on this investigation and plans for its resolution.

We apologize for the inconvenience placed upon customers in ordering this product. However, we wish to ensure that our customers are aware of the device shortcomings from the specification. We are working in earnest to remove this waiver requirement.

For further information, please contact

Neeraj Magotra

WW Strategic Marketing Manager for Voice/Audio Systems

Office: (214) 480-7486 nmagotra@ti.com

# **TLV320AIC13**

SMARTDM™ Low-Power, Low-Voltage, 1.1-V to 3.6-V I/O, 16-Bit, 26-KSPS Codec

# Data Manual

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third—party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Mailing Address:

Texas Instruments Post Office Box 655303 Dallas, Texas 75265

Copyright © 2002, Texas Instruments Incorporated

# **Contents**

| Se | ection |           | Title                                     | Page       |

|----|--------|-----------|-------------------------------------------|------------|

| 1  | Introd | luction . |                                           | 1–1        |

|    | 1.1    | Descrip   | tion                                      | 1–1        |

|    | 1.2    | Feature   | es                                        | 1–1        |

|    | 1.3    | Function  | nal Block Diagram                         | 1–3        |

| 2  | Termi  |           | criptions                                 | 2–1        |

|    | 2.1    |           | g Information                             | 2–1        |

|    | 2.2    |           | al Functions                              |            |

|    | 2.3    |           | ons and Terminology                       |            |

| 3  |        |           | scription                                 | 3–1        |

| _  | 3.1    |           | ng Frequencies                            | _          |

|    | 3.2    |           | Architecture                              |            |

|    | V      | 3.2.1     | Antialiasing Filter                       |            |

|    |        | 3.2.2     | Sigma-Delta ADC                           |            |

|    |        | 3.2.3     | Decimation Filter                         |            |

|    |        | 3.2.4     | Sigma-Delta DAC                           |            |

|    |        | 3.2.5     | Interpolation Filter                      |            |

|    |        | 3.2.6     | Analog/Digital/Side-Tone Loopback         |            |

|    |        | 3.2.7     | ADC PGA                                   |            |

|    |        | 3.2.8     | DAC PGA                                   |            |

|    | 3.3    |           | Input/Output                              | 3–2        |

|    | 0.0    | 3.3.1     | MIC Input                                 | _          |

|    |        | 3.3.2     | INP and INM Input                         |            |

|    |        | 3.3.3     | Single-Ended Analog Input                 |            |

|    |        | 3.3.4     | Analog Output                             |            |

|    | 3.4    |           | Control                                   |            |

|    | 0. 1   | 3.4.1     | Overflow Flags                            |            |

|    |        | 3.4.2     | IIR/FIR Bypass Mode                       |            |

|    | 3.5    | _         | Reset and Power Management                |            |

|    | 0.0    | 3.5.1     | Software and Hardware Reset               |            |

|    |        | 3.5.2     | Power Management                          |            |

|    | 3.6    |           | nterface                                  |            |

|    | 0.0    | 3.6.1     | Clock Source (MCLK, SCLK)                 |            |

|    |        | 3.6.2     | Serial Data Out (DOUT)                    |            |

|    |        | 3.6.3     | Serial Data In (DIN)                      |            |

|    |        | 3.6.4     | Frame-Sync FS                             |            |

|    |        | 3.6.5     | Cascade Mode and Frame-Sync Delayed (FSD) |            |

|    |        | 3.6.6     | Stand-Alone Slave                         | 3–7<br>3–7 |

|    |        | 3.6.7     |                                           |            |

|    |        | J.U.1     | Asynchronous Sampling                     | 3–7        |

|   | 3.7             | Host Po   | rt Interface                                                               | 3–8             |

|---|-----------------|-----------|----------------------------------------------------------------------------|-----------------|

|   |                 | 3.7.1     | S <sup>2</sup> C (Start-Stop Communication)                                |                 |

|   |                 | 3.7.2     | I <sup>2</sup> C                                                           |                 |

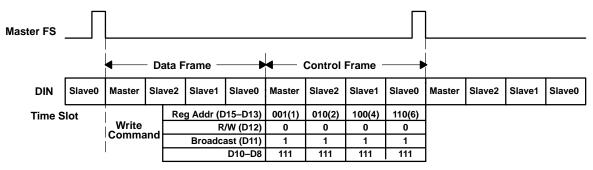

|   | 3.8             | Smart T   | ime Division Multiplexed Serial Port (SMARTDM)                             | 3–11            |

|   |                 | 3.8.1     | Programming Mode                                                           |                 |

|   |                 | 3.8.2     | Continuous Data Transfer Mode                                              |                 |

|   |                 | 3.8.3     | Turbo Operation (SCLK)                                                     | 3–13            |

|   | 3.9             | Control   | Register Programming                                                       |                 |

|   |                 | 3.9.1     | Data Frame Format                                                          |                 |

|   |                 | 3.9.2     | Control Frame Format (Programming Mode)                                    |                 |

|   |                 | 3.9.3     | Broadcast Register Write                                                   |                 |

|   |                 | 3.9.4     | Register Map                                                               |                 |

| 4 | Contr           | ol Regist | ter Content Description                                                    |                 |

|   | 4.1             | _         | Register 1                                                                 |                 |

|   | 4.2             |           | Register 2                                                                 |                 |

|   | 4.3             |           | Register 3                                                                 |                 |

|   | 4.4             |           | Register 4                                                                 |                 |

|   | 4.5             |           | Register 5A                                                                |                 |

|   | 4.6             |           | Register 5B                                                                |                 |

|   | 4.7             |           | Register 5C                                                                |                 |

|   | 4.8             |           | Register 5D                                                                |                 |

|   | 4.9             |           | Register 6                                                                 |                 |

| 5 | Electr          |           | racteristics                                                               |                 |

|   | 5.1             |           | e Maximum Ratings Over Operating Free-Air                                  |                 |

|   |                 |           | ature Range                                                                | 5–1             |

|   | 5.2             |           | nended Operating Conditions                                                | 5–1             |

|   | 5.3             |           | al Characteristics Over Recommended Operating                              |                 |

|   |                 | Free-Air  | Temperature Range, $AV_{DD} = 3.3 \text{ V}$ , $DV_{DD} = 1.8 \text{ V}$ , | <b>-</b> 0      |

|   |                 |           | = 1.1 V                                                                    | 5–2             |

|   |                 | 5.3.1     | Digital Inputs and Outputs, f <sub>S</sub> = 8 kHz, Outputs Not Loaded     | 5–2             |

|   | 5.4             | ADC Pa    | th Filter, f <sub>S</sub> = 8 kHz                                          |                 |

|   | J. <del>T</del> | 5.4.1     | FIR Filter                                                                 |                 |

|   |                 | 5.4.2     | IIR Filter                                                                 |                 |

|   | 5.5             | _         | rnamic Performance, f <sub>S</sub> = 8 kHz                                 |                 |

|   | 5.5             | 5.5.1     | ADC Signal-to-Noise                                                        |                 |

|   |                 | 5.5.2     | ADC Signal-to-Distortion                                                   |                 |

|   |                 | 5.5.3     | ADC Signal-to-Distortion + Noise                                           |                 |

|   |                 | 5.5.4     | ADC Channel Characteristics                                                |                 |

|   | 5.6             |           | th Filter, f <sub>S</sub> = 8 kHz                                          |                 |

|   | 5.0             | 5.6.1     | FIR Filter                                                                 |                 |

|   |                 | 5.6.2     | IIR Filter                                                                 |                 |

|   | 5.7             |           | rnamic Performance                                                         |                 |

|   | 5.1             | 5.7.1     | OUTP1/OUTM1 Signal-to-Noise When Load Is 600 $\Omega$                      |                 |

|   |                 | 5.7.1     | OUTP1/OUTM1 Signal-to-Distortion When Load                                 | J <del>-4</del> |

|   |                 | J.1.Z     | Is $600 \Omega \dots \dots \dots \dots \dots \dots \dots \dots \dots$      | 5–4             |

|                      | 5.7.3                    | OUTP1/OUTM1 Signal-to-Distortion + Noise When Load Is 600 Ω  | 5–4        |

|----------------------|--------------------------|--------------------------------------------------------------|------------|

|                      | 5.7.4                    | OUTP2, OUTP3 Signal-to-Noise When Load Is 16 $\Omega$        |            |

|                      | 5.7.5                    | OUTP2, OUTP3 Signal-to-Distortion When Load Is 16 $\Omega$ . |            |

|                      | 5.7.6                    | OUTP2, OUTP3 Signal-to-Distortion + Noise When               |            |

|                      | 5.7.7                    | Load Is 16 $\Omega$                                          | 5–5<br>5–5 |

| 5.8                  |                          | mplifier Characteristics                                     | 5–5<br>5–6 |

| 5.9                  |                          | / Amplifier Characteristics                                  | 5–6        |

| 5.10                 |                          | Supply Rejection                                             | 5–6        |

| 5.11                 |                          | Supply                                                       |            |

| 5.12                 |                          | Requirements                                                 |            |

| 5.13                 |                          | and Grounding Guidelines for TLV320AIC13                     |            |

|                      |                          | List of Illustrations                                        |            |

| Figure               |                          | Title                                                        | Page       |

| 3–1. Mi              | crophone I               | nterface                                                     | 3–3        |

| 3–2. IN              | P and INM                | Internal Self-Biased Circuit                                 | 3–3        |

| 3–3. Sii             | ngle-Ended               | I Input                                                      | 3–4        |

| 3–4. Ol              | JTP1/OUTI                | M1 Output                                                    | 3–4        |

| 3–5. Sii             | ngle-Ended               | I/Differential Connection of OUTP2/OUTP3 Output              | 3–4        |

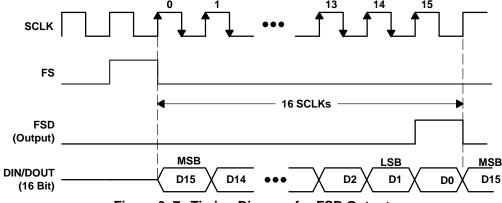

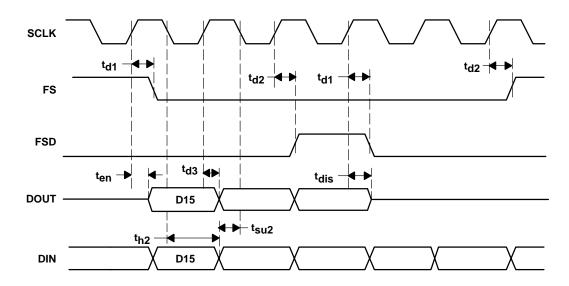

| 3–6. Tir             | ming Diagra              | am of FS                                                     | 3–7        |

| 3–7. Tir             | ming Diagra              | am for FSD Output                                            | 3–7        |

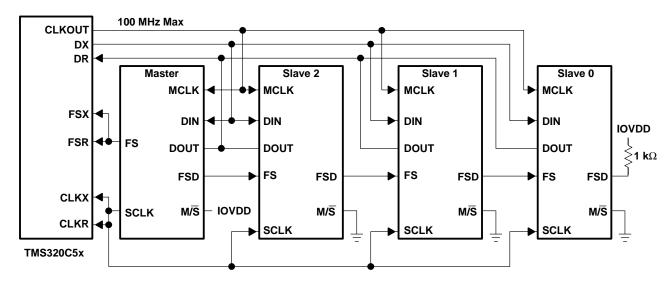

| 3–8. Ca              | ascade Con               | nnection (To DSP Interface)                                  | 3–8        |

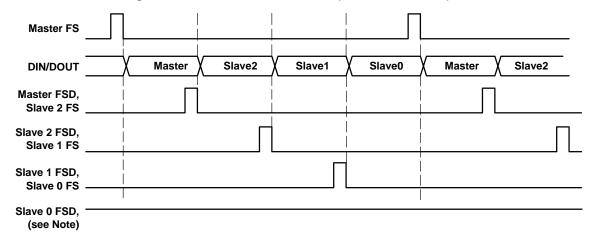

| 3–9. Ma              | aster-Slave              | Frame-Sync Timing in Continuous Data Transfer Mode           | 3–8        |

| 3–10. S              | S <sup>2</sup> C Prograi | mming                                                        | 3–9        |

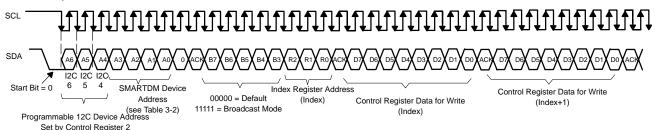

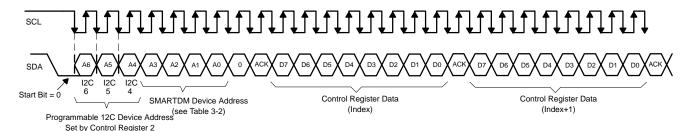

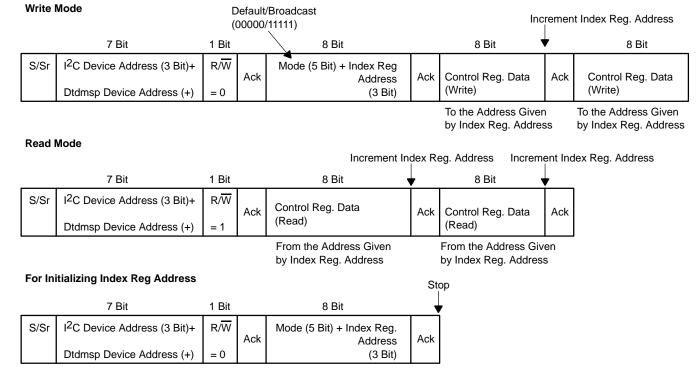

| 3–11. I <sup>2</sup> | 2C Write Se              | equence                                                      | 3–10       |

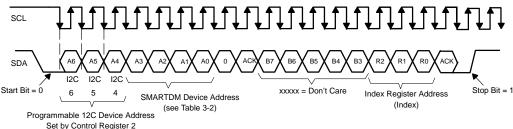

| 3–12. l <sup>2</sup> | <sup>2</sup> C Read Se   | equence                                                      | 3–10       |

|                      |                          | ter Addresses                                                |            |

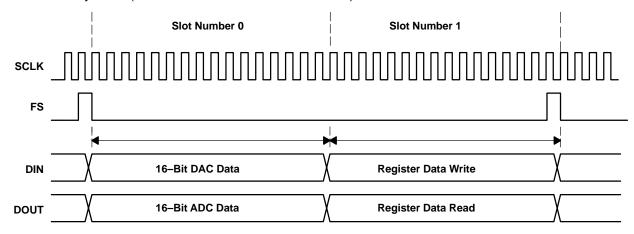

|                      | _                        | peration/Programming Mode: Stand-Alone Timing                |            |

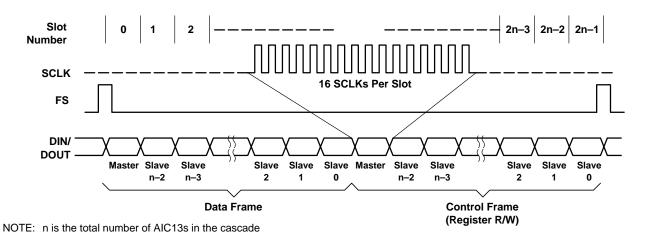

| 3–15. S              | Standard Op              | peration/Programming Mode: Master-Slave                      |            |

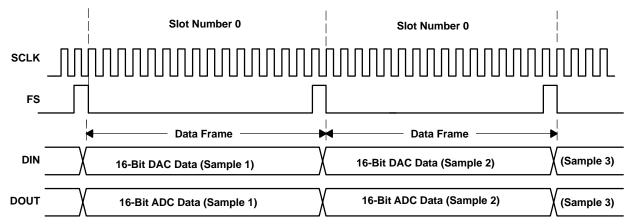

| 3–16. S              | Standard Op              | peration/Continuous Data Transfer Mode: e Timing             |            |

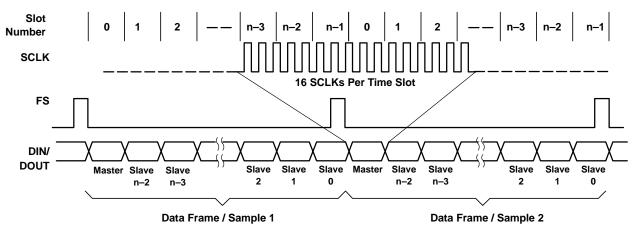

| 3–17. S              | Standard Op              | peration/Continuous Data Transfer Mode:                      |            |

|                      |                          | ram for Turbo Operation                                      |            |

|                      |                          | Format                                                       |            |

|                      |                          | ne Data Format                                               |            |

|                      |                          |                                                              |            |

|                      |                          | Register Write Example                                       |            |

| 5−1 Ha               | raware Res               | set Timing                                                   | 5–7        |

| 5–2 Serial Communication Timing                                                                                                                                                                                                                                                                                                                                                                                                                        | 5–7              |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

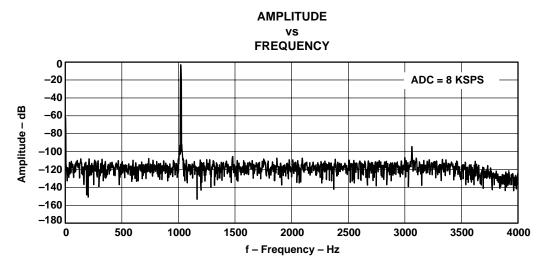

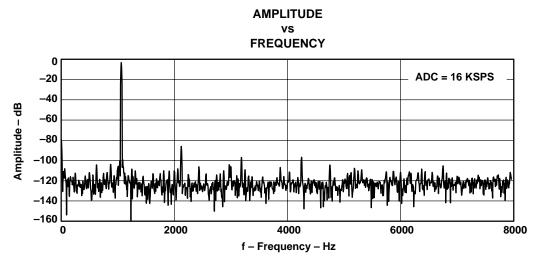

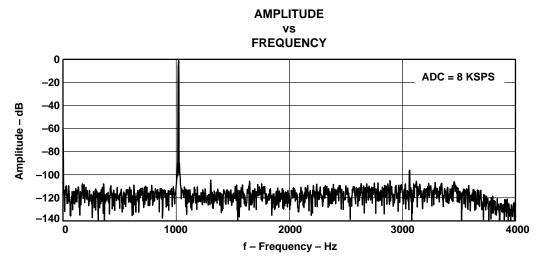

| 5–3 FFT—ADC Channel (–3 dB Input)                                                                                                                                                                                                                                                                                                                                                                                                                      | 5–8              |

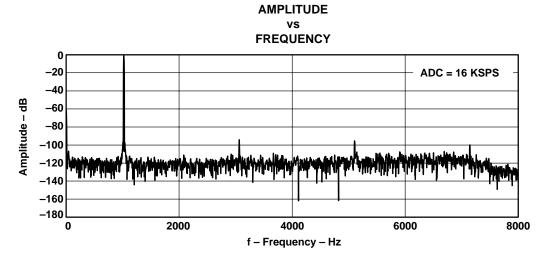

| 5–4 FFT—ADC Channel (–1 dB Input)                                                                                                                                                                                                                                                                                                                                                                                                                      | 5–8              |

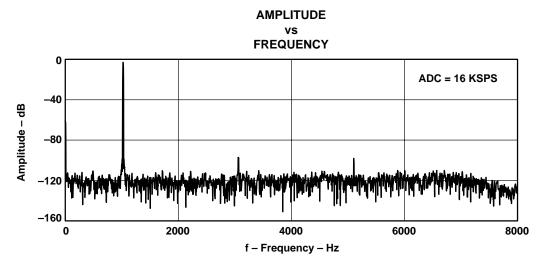

| 5–5 FFT—ADC Channel (–3 dB Input)                                                                                                                                                                                                                                                                                                                                                                                                                      | 5–8              |

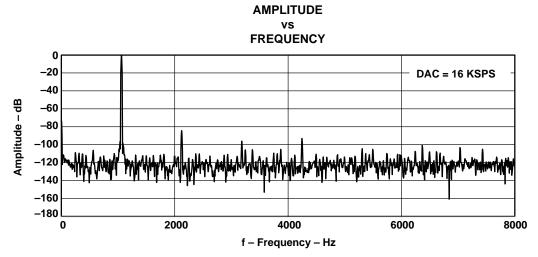

| 5–6 FFT—DAC Channel (–3 dB Input)                                                                                                                                                                                                                                                                                                                                                                                                                      | 5–9              |

| 5–7 FFT—DAC Channel (0 dB Input)                                                                                                                                                                                                                                                                                                                                                                                                                       | 5–9              |

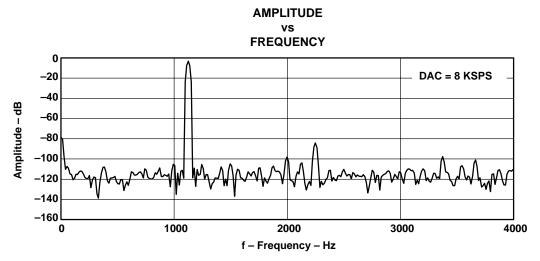

| 5–8 FFT—DAC Channel (–3 dB Input)                                                                                                                                                                                                                                                                                                                                                                                                                      | 5–9              |

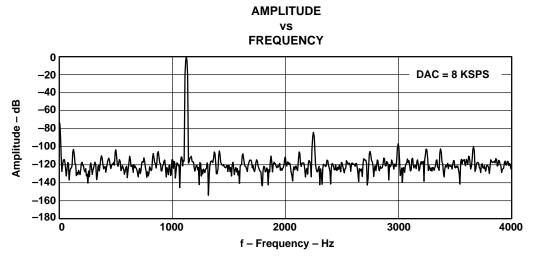

| 5–9 FFT—DAC Channel (0 dB Input)                                                                                                                                                                                                                                                                                                                                                                                                                       | 5–10             |

| 5-10 FFT-ADC Channel (-1 dB Input)                                                                                                                                                                                                                                                                                                                                                                                                                     | 5–10             |

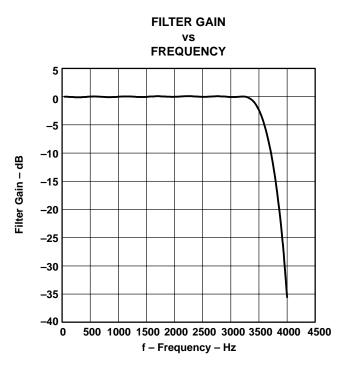

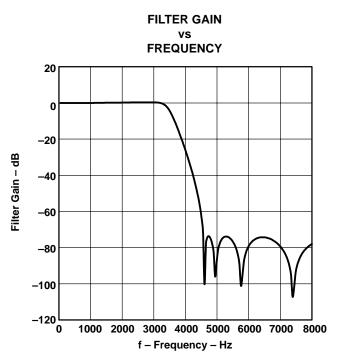

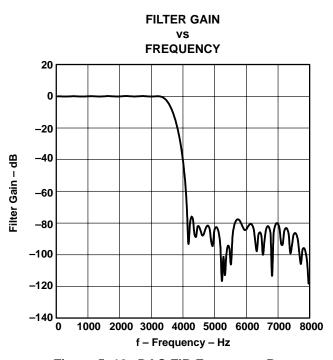

| 5–11 ADC FIR Frequency Response                                                                                                                                                                                                                                                                                                                                                                                                                        | 5–11             |

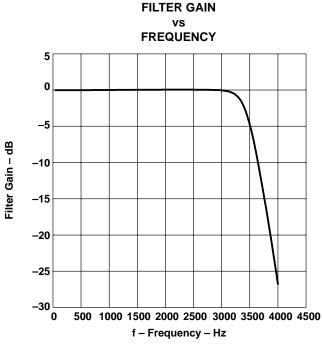

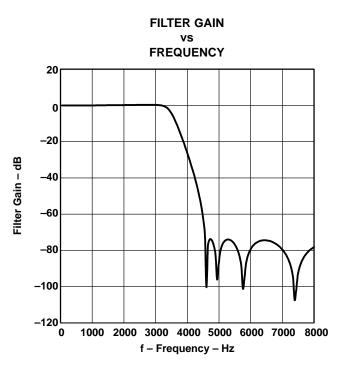

| 5–12 ADC IIR Frequency Response                                                                                                                                                                                                                                                                                                                                                                                                                        |                  |

| 5–13 DAC IIR Frequency Response (OSR = 512)                                                                                                                                                                                                                                                                                                                                                                                                            | 5–11             |

| 5–14 DAC IIR Frequency Response (OSR = 256)                                                                                                                                                                                                                                                                                                                                                                                                            | 5–11             |

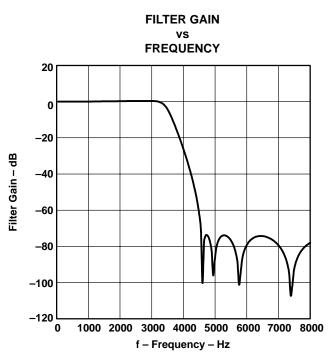

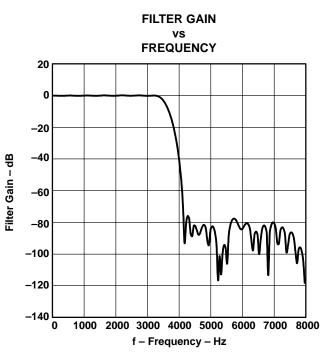

| 5–15 DAC IIR Frequency Response (OSR = 128)                                                                                                                                                                                                                                                                                                                                                                                                            | 5–12             |

| 5–16 DAC FIR Frequency Response (OSR = 512)                                                                                                                                                                                                                                                                                                                                                                                                            |                  |

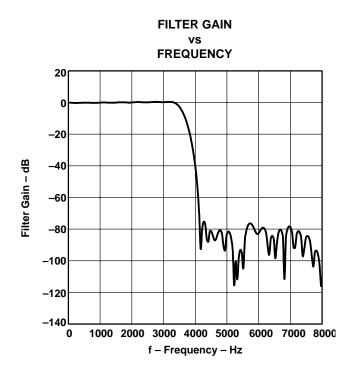

| 5–17 DAC FIR Frequency Response (OSR = 256)                                                                                                                                                                                                                                                                                                                                                                                                            | 5–12             |

| 5–18 DAC FIR Frequency Response (OSR = 128)                                                                                                                                                                                                                                                                                                                                                                                                            |                  |

| 5-19 Single-Ended Microphone Input (Internal Common Mode)                                                                                                                                                                                                                                                                                                                                                                                              | 5–13             |

| 5-19 Single-Ended Microphone Input (Internal Common Mode)                                                                                                                                                                                                                                                                                                                                                                                              |                  |

| 5–19 Single-Ended Microphone Input (Internal Common Mode) 5–20 Pseudo-Differential Microphone Input (External Common Mod                                                                                                                                                                                                                                                                                                                               |                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                  |

| 5–20 Pseudo-Differential Microphone Input (External Common Mod                                                                                                                                                                                                                                                                                                                                                                                         |                  |

| 5–20 Pseudo-Differential Microphone Input (External Common Mod<br>List of Tables                                                                                                                                                                                                                                                                                                                                                                       | le) 5–14         |

| 5–20 Pseudo-Differential Microphone Input (External Common Mod  List of Tables  Table  Title                                                                                                                                                                                                                                                                                                                                                           | le) 5–14<br>Page |

| 5–20 Pseudo-Differential Microphone Input (External Common Mod  List of Tables  Table Title  3–1 Analog Output Load Resistance                                                                                                                                                                                                                                                                                                                         | Page 3–4         |

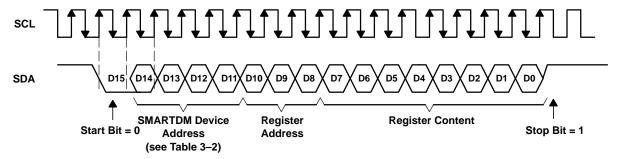

| 5–20 Pseudo-Differential Microphone Input (External Common Mod  List of Tables  Table Title  3–1 Analog Output Load Resistance 3–2 SMARTDM Device Addresses                                                                                                                                                                                                                                                                                            | Page3-43-9       |

| List of Tables  Table Title 3–1 Analog Output Load Resistance 3–2 SMARTDM Device Addresses 3–3 Serial Interface Configurations                                                                                                                                                                                                                                                                                                                         | Page             |

| List of Tables  Table Title 3–1 Analog Output Load Resistance 3–2 SMARTDM Device Addresses 3–3 Serial Interface Configurations 3–4 Register Map                                                                                                                                                                                                                                                                                                        | Page             |

| List of Tables  Table Title 3–1 Analog Output Load Resistance 3–2 SMARTDM Device Addresses 3–3 Serial Interface Configurations 3–4 Register Map 3–5 Register Addresses                                                                                                                                                                                                                                                                                 | Page             |

| List of Tables  Table Title 3–1 Analog Output Load Resistance 3–2 SMARTDM Device Addresses 3–3 Serial Interface Configurations 3–4 Register Map                                                                                                                                                                                                                                                                                                        | Page             |

| List of Tables  Table Title  3–1 Analog Output Load Resistance 3–2 SMARTDM Device Addresses 3–3 Serial Interface Configurations 3–4 Register Map 3–5 Register Addresses 4–1 Control Register 1 Bit Summary 4–2 Control Register 2 Bit Summary 4–3 Control Register 3 Bit Summary                                                                                                                                                                       | Page             |

| List of Tables  Table Title 3–1 Analog Output Load Resistance 3–2 SMARTDM Device Addresses 3–3 Serial Interface Configurations 3–4 Register Map 3–5 Register Addresses 4–1 Control Register 1 Bit Summary 4–2 Control Register 2 Bit Summary 4–3 Control Register 3 Bit Summary 4–4 Control Register 4 Bit Summary                                                                                                                                     | Page             |

| List of Tables  Table Title 3–1 Analog Output Load Resistance 3–2 SMARTDM Device Addresses 3–3 Serial Interface Configurations 3–4 Register Map 3–5 Register Addresses 4–1 Control Register 1 Bit Summary 4–2 Control Register 2 Bit Summary 4–3 Control Register 3 Bit Summary 4–4 Control Register 4 Bit Summary 4–5 Control Register 5A Bit Summary                                                                                                 | Page             |

| List of Tables  Table Title 3–1 Analog Output Load Resistance 3–2 SMARTDM Device Addresses 3–3 Serial Interface Configurations 3–4 Register Map 3–5 Register Addresses 4–1 Control Register 1 Bit Summary 4–2 Control Register 2 Bit Summary 4–3 Control Register 3 Bit Summary 4–4 Control Register 4 Bit Summary 4–5 Control Register 5A Bit Summary 4–6 A/D PGA Gain                                                                                | Page             |

| List of Tables  Table Title  3–1 Analog Output Load Resistance 3–2 SMARTDM Device Addresses 3–3 Serial Interface Configurations 3–4 Register Map 3–5 Register Addresses 4–1 Control Register 1 Bit Summary 4–2 Control Register 2 Bit Summary 4–3 Control Register 3 Bit Summary 4–4 Control Register 4 Bit Summary 4–5 Control Register 5A Bit Summary 4–6 A/D PGA Gain 4–7 Control Register 5B Bit Summary                                           | Page             |

| List of Tables  Table Title 3–1 Analog Output Load Resistance 3–2 SMARTDM Device Addresses 3–3 Serial Interface Configurations 3–4 Register Map 3–5 Register Addresses 4–1 Control Register 1 Bit Summary 4–2 Control Register 2 Bit Summary 4–3 Control Register 3 Bit Summary 4–4 Control Register 4 Bit Summary 4–5 Control Register 5A Bit Summary 4–6 A/D PGA Gain 4–7 Control Register 5B Bit Summary 4–8 D/A PGA Gain                           | Page             |

| List of Tables  Table Title 3–1 Analog Output Load Resistance 3–2 SMARTDM Device Addresses 3–3 Serial Interface Configurations 3–4 Register Map 3–5 Register Addresses 4–1 Control Register 1 Bit Summary 4–2 Control Register 2 Bit Summary 4–2 Control Register 3 Bit Summary 4–4 Control Register 4 Bit Summary 4–5 Control Register 5A Bit Summary 4–6 A/D PGA Gain 4–7 Control Register 5B Bit Summary 4–8 D/A PGA Gain 4–9 Digital Sidetone Gain | Page             |

| List of Tables  Table Title 3–1 Analog Output Load Resistance 3–2 SMARTDM Device Addresses 3–3 Serial Interface Configurations 3–4 Register Map 3–5 Register Addresses 4–1 Control Register 1 Bit Summary 4–2 Control Register 2 Bit Summary 4–3 Control Register 3 Bit Summary 4–4 Control Register 4 Bit Summary 4–5 Control Register 5A Bit Summary 4–6 A/D PGA Gain 4–7 Control Register 5B Bit Summary 4–8 D/A PGA Gain                           | Page             |

#### 1 Introduction

The TLV320AlC13 is a true low-cost low-power highly-integrated high-performance voiceband codec designed with new technological advances. The TLV320AlC13 provides high resolution signal conversion from digital-to-analog (D/A) and from analog-to-digital (A/D) using oversampling sigma-delta technology with programmable sampling rate.

#### 1.1 Description

The TLV320AlC13 implements the smart time division multiplexed serial port (SMARTDM™). This design innovation optimizes the DSP performance with an advanced synchronous serial port in TDM format for glue-free interface to popular DSPs (i.e., C5x, C6x) and microcontrollers. The SMARTDM supports both continuous data transfer mode and on-the-fly reconfiguration programming mode. The advantage of SMARTDM is to maximize the bandwidth of data transfer between the TLV320AlC13 DSP codec and the DSP. In normal operation, it automatically detects the number of codecs in the serial interface and adjusts the number of time slots to match the number of codecs so that no time slot in the TDM frame is wasted. In the turbo mode, it maintains the same number of time slots but maximizes the bit transferred rate to 25 MHz to give the DSP more bandwidth to process other tasks in the same sampling period. The SMARTDM technology allows up to 16 codec to share a single 4-wire serial bus.

The TLV320AlC13 also provides a flexible host port. The host port interface is a two-wire serial interface that can be programmed to be either an industrial standard  $I^2C$  or a simple  $S^2C$  (start-stop communication protocol).

The TLV320AlC13 also integrates all of the critical functions needed for most voice-band applications including MIC preamp, handset/headset preamps, antialiasing filter (AAF), input/output programmable gain amplifier (PGA), and selectable low-pass IIR/FIR filters.

The TLV320AlC13 implements an extensive power management; including device power-down, independent software control for turning off ADC, DAC, op-amps, and IIR/FIR filter (bypassable) to maximize system power conservation. The TLV320AlC13 consumes only 10 mW at 3 V without 16- $\Omega$  drivers.

The TLV320AIC13's low power operation from 2.7-V to 3.6-V for analog and I/O and 1.65 V to 1.95 for digital core power supplies, along with extensive power management, make it ideal for portable applications including wireless accessories, hands free car kits, VOIP, cable modem, and speech processing. Its low group delay characteristic makes it suitable for single or multichannel active control applications.

The wide range of low-voltage I/O (1.1 V–3.6 V) enables the AIC13 to interface with a single power supply, or with dual power supplies for mixed low-voltage DSP systems such as the TMS320UC54x. This feature eliminates the need for external level-shifting and reduces power consumption

The TLV320AlC13 is characterized for commercial operation from 0°C to 70°C and industrial operation from –40°C to 85°C.

#### 1.2 Features

- C54x Software Driver Available

- 16-Bit Oversampling Sigma-Delta A/D Converter

- 16-Bit Oversampling Sigma-Delta D/A Converter

- Support Maximum Master Clock of 100 MHz to Allow DSPs Output Clock to Be Used as Master Clock

- Selectable FIR/IIR Filter With Bypassing Option

SMARTDM is a trademark of Texas Instruments.

- Programmable Sampling Rate up to:

- Max 26 KSPS With On-Chip IIR/FIR Filter

- Max 104 KSPS With IIR/FIR Bypassed

- On-Chip FIR Produced 84-dB SNR for ADC and 91-dB SNR for DAC Over 13-kHz BW

- External DSPs IIR/FIR for a Final Sampling Rate of 8 Ksps (IIR/FIR Bypassed) Produced 87-dB SNR for ADC and 92-dB SNR for DAC.

- Smart Time Division Multiplexed Serial Port (SMARTDM)

- Glueless 4-Wire Interface to DSP

- Automatic Cascade Detection (ACD) Self-Generates Master/Slave Device Addresses

- Programming Mode to Allow On-the-Fly Reconfiguration

- Continuous Data Transfer Mode to Support DSP's DMA/Autobuffering Mode

- Turbo Mode to Maximize Bit Clock for Faster Data Transfer and Higher Data Bandwidth

- Total Number of Time Slots Dynamically Proportional to Number of Codecs in the Cascade to Eliminate Unused Time Slots and Optimize DSP Memory Allocation

- Allows up to 16 Codecs to Be Connected to a Single Serial Port

- Host Port

- 2-Wire Interface

- Selectable I<sup>2</sup>C or S<sup>2</sup>C

- Differential and Single-Ended Analog Input/Output

- Built-In Functions:

- Sidetone

- Antialiasing Filter (AAF)

- Programmable Input and Output Gain Control (PGA)

- Microphone/Handset/Headset Amplifiers

- Power Management With Hardware/Software Power-Down Modes 30 μW

- Separate Software Control for ADC and DAC Power Down

- Fully Compatible With TI C54x DSP Power Supplies

- 1.65-V–1.95-V Digital Core Power

- 1.1-V–3.6-V Digital I/O

- 2.7-V–3.6-V Analog

- Power Dissipation (PD) 10 mW at 3 V in Standard Operation

- Internal Reference Voltage (V<sub>ref</sub>)

- 2s Complement Data Format

- Test Mode Which Includes Digital Loopback and Analog Loopback

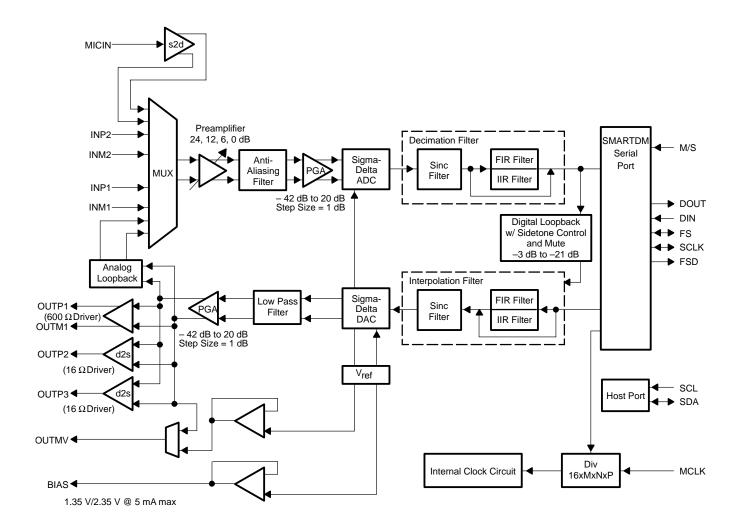

### 1.3 Functional Block Diagram

# **2 Terminal Descriptions**

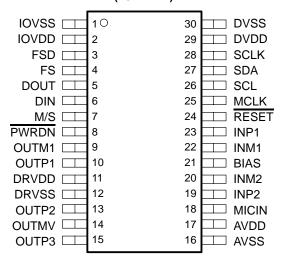

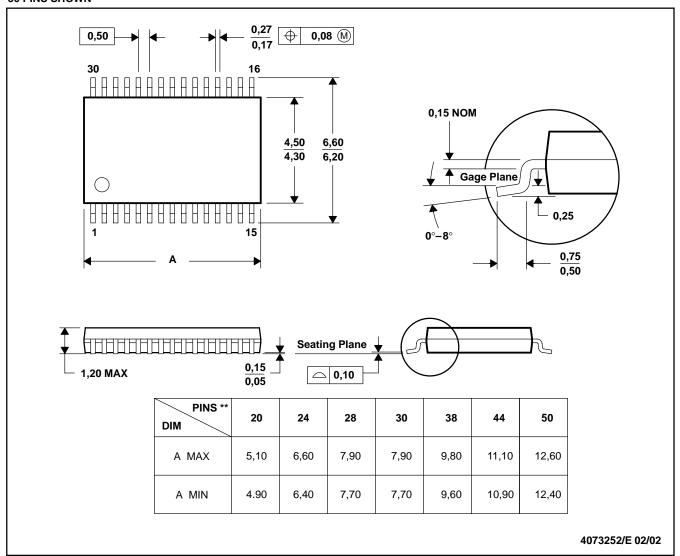

# DBT PACKAGE (TOP VIEW)

# 2.1 Ordering Information

| TA            | 30-TSSOP DBT PACKAGE |

|---------------|----------------------|

| 0°C to 70°C   | TLV320AIC13C         |

| –40°C to 85°C | TLV320AIC13I         |

#### 2.2 Terminal Functions

| TERMIN | NAL | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                    |

|--------|-----|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME   | NO. | 2   | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                    |

| AVDD   | 17  | ı   | Analog power supply                                                                                                                                                                                                                                                                                                                                            |

| AVSS   | 16  | I   | Analog ground                                                                                                                                                                                                                                                                                                                                                  |

| BIAS   | 21  | 0   | Bias output voltage is software selectable between 1.35 V and 2.35 V. Its output current is 5 mA.                                                                                                                                                                                                                                                              |

| DIN    | 6   | I   | Data input. DIN receives the DAC input data and register data from the external DSP (digital signal processor) and is synchronized to SCLK and FS. Data is latched at the falling edge of SCLK when FS is low.                                                                                                                                                 |

| DOUT   | 5   | 0   | Data output. DOUT transmits the ADC output bits and registers data, and is synchronized to SCLK and FS. Data is sent out at the rising edge of SCLK when FS is low. Outside data/control frame, DOUT is put in 3-state.                                                                                                                                        |

| DRVDD  | 11  | ı   | Analog power supply for the 16-Ω drivers OUTP2 and OUTP3                                                                                                                                                                                                                                                                                                       |

| DRVSS  | 12  | ı   | Analog ground for the 16- $\Omega$ drivers OUTP2 and OUTP3                                                                                                                                                                                                                                                                                                     |

| DVDD   | 29  | I   | Digital power supply                                                                                                                                                                                                                                                                                                                                           |

| DVSS   | 30  | ı   | Digital ground                                                                                                                                                                                                                                                                                                                                                 |

| FS     | 4   | I/O | Frame sync. When FS goes low, DIN begins receiving data bits and DOUT begins transmitting data bits. In master mode, FS is internally generated and is low during the data transmission to DIN and from DOUT. In slave mode, FS is externally generated.                                                                                                       |

| FSD    | 3   | 0   | Frame sync delayed output. The FSD output synchronizes a slave device to the frame sync of the master device. FSD is applied to the slave FS input and is the same duration as the master FS signal. This pin must be pulled low if AlC13 is a stand-alone slave. It may be pulled high if the AlC13 is a stand-alone master or the last slave in the cascade. |

| INM1   | 22  | I   | Inverting analog input 1. It must be connected to AVSS if not used.                                                                                                                                                                                                                                                                                            |

| INM2   | 20  | I   | Inverting analog input 2. It must be connected to AVSS if not used.                                                                                                                                                                                                                                                                                            |

| INP1   | 23  | I   | Noninverting analog input 1. It must be connected to AVSS if not used.                                                                                                                                                                                                                                                                                         |

| INP2   | 19  | I   | Noninverting analog input 2. It must be connected to AVSS if not used.                                                                                                                                                                                                                                                                                         |

# 2.2 Terminal Functions (Continued)

| TERMINAL |     | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                            |

|----------|-----|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME     | NO. | 2   | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                            |

| IOVDD    | 2   | -   | Digital I/O power supply                                                                                                                                                                                                                                                                                                                                                                                                               |

| IOVSS    | 1   | ı   | Digital I/O ground                                                                                                                                                                                                                                                                                                                                                                                                                     |

| MCLK     | 25  | -   | Master clock. MCLK derives the internal clocks of the sigma-delta analog interface circuit.                                                                                                                                                                                                                                                                                                                                            |

| MICIN    | 18  | ı   | MIC preamplifier input. It must be connected to AVSS if not used.                                                                                                                                                                                                                                                                                                                                                                      |

| M/S      | 7   | I   | Master/slave select input. When M/S is high, the device is the master, and when low it is a slave.                                                                                                                                                                                                                                                                                                                                     |

| OUTM1    | 9   | 0   | Inverting output of the DAC. OUTM1 is functionally identical with and complementary to OUTP1. This differential output can drive a minimum load of 600 $\Omega$ . This output can also be used alone for single-ended operation.                                                                                                                                                                                                       |

| OUTMV    | 14  | 0   | Programmable virtual ground for the output of OUTP2 and OUTP3 (see Register Map).                                                                                                                                                                                                                                                                                                                                                      |

| OUTP1    | 10  | 0   | Noninverting output of the DAC. This differential output can drive a minimum load of 600 $\Omega$ . This output can also be used alone for single-ended operation.                                                                                                                                                                                                                                                                     |

| OUTP2    | 13  | 0   | Analog output #2 from the 16- $\Omega$ driver. This output can drive a minimum load of 16 $\Omega$ and also can be configured as either single-ended output or differential output by the control register 6.                                                                                                                                                                                                                          |

| OUTP3    | 15  | 0   | Analog output #3 from the 16- $\Omega$ driver. This output can drive a minimum load of 16 $\Omega$ and also be configured as either single-ended output or differential output by the control register 6.                                                                                                                                                                                                                              |

| PWRDN    | 8   | I   | Power down. When PWRDN is pulled low, the device goes into a power-down mode, the serial interface is disabled, and most of the high-speed clocks are disabled. However, all the register values are sustained and the device resumes full-power operation without reinitialization when PWRDN is pulled high again. PWRDN resets the counters only and preserves the programmed register contents.                                    |

| RESET    | 24  | I   | Hardware reset. The reset function is provided to initialize all of the internal registers to their default values. The serial port is configured to the default state accordingly.                                                                                                                                                                                                                                                    |

| SCL      | 26  | I   | Programmable host port (I <sup>2</sup> C or S <sup>2</sup> C) clock input.                                                                                                                                                                                                                                                                                                                                                             |

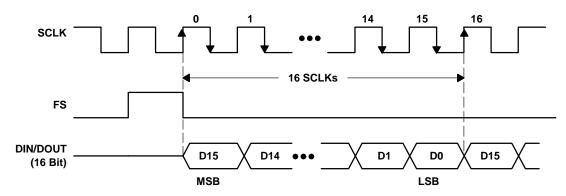

| SCLK     | 28  | I/O | Shift clock. SCLK signal clocks serial data into DIN and out of DOUT during the frame-sync interval. When configured as an output (M/S high), SCLK is generated internally by multiplying the frame-sync signal frequency by 16 and the number of codecs in cascade in standard and continuous mode. When configured as an input (M/S low), SCLK is generated externally and must be synchronous with the master clock and frame sync. |

| SDA      | 27  | I/O | Programmable host port (I <sup>2</sup> C or S <sup>2</sup> C) data line.                                                                                                                                                                                                                                                                                                                                                               |

# 2.3 Definitions and Terminology

| Data Transfer<br>Interval         | The time during which data is transferred from DOUT and to DIN. The interval is 16 shift clocks and the data transfer is initiated by the falling edge of the FS signal in standard and continuous mode.                        |

|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Signal Data                       | This refers to the input signal and all of the converted representations through the ADC channel and the signal through the DAC channel to the analog output. This is contrasted with the purely digital software control data. |

| Frame Sync                        | Frame sync refers only to the falling edge of the signal FS that initiates the data transfer interval                                                                                                                           |

| Frame Sync and<br>Sampling Period | Frame sync and sampling period is the time between falling edges of successive FS signals.                                                                                                                                      |

| $f_S$                             | The sampling frequency                                                                                                                                                                                                          |

| ADC Channel                       | ADC channel refers to all signal processing circuits between the analog input and the digital conversion result at DOUT.                                                                                                        |

| DAC channel                       | DAC channel refers to all signal processing circuits between the digital data word applied to DIN and the differential output analog signal available at OUTP1and OUTM.                                                         |

| Dxx                               | Bit position in the primary data word (xx is the bit number)                                                                                                                                                                    |

| DSxx                              | Bit position in the secondary data word (xx is the bit number)                                                                                                                                                                  |

| PGA                               | Programmable gain amplifier                                                                                                                                                                                                     |

| IIR                               | Infinite impulse response                                                                                                                                                                                                       |

| FIR                               | Finite impulse response                                                                                                                                                                                                         |

# 3 Functional Description

#### 3.1 Operating Frequencies (see Notes)

The sampling frequency is the frequency of the frame sync (FS) signal whose falling edge starts digital-data transfer for both ADC and DAC. The sampling frequency is derived from the master clock (MCLK) input by the following equations:

Coarse sampling frequency (default):

The coarse sampling is selected by programming P = 8 in the control register 4, which is the default configuration of AIC13 on power-up or reset.

```

FS = Sampling (conversion) frequency = MCLK / (16 \times M \times N \times 8)

```

• Fine sampling frequency (see Note 5):

```

FS = Sampling (conversion) frequency = MCLK/ (16 \times M \times N \times P)

```

NOTES: 1. Use control register 4 to set the following values of M, N, and P

- 2. M = 1, 2, ..., 128

- 3. N = 1, 2, ..., 16

- 4. P = 1,2,...,8

- 5. The fine sampling rate needs an on-chip Delay Lock Loop (frequency multiplier) to generate internal clocks. The DLL requires the relationship between MCLK and P to meet the following condition: 10 MHz ≤ (MCLK/P) ≤ 25 MHz

- 6. Both equations of FS require that the following conditions should be met:

- $(M \times N \times P) \ge (devnum \times mode)$  if the FIR/IIR filter is not bypassed.

- [Integer(M/4)  $\times$  N  $\times$  P]  $\geq$  (devnum  $\times$  mode) if the FIR/IIR filter is bypassed. where

devnum is the number of devices connecting in cascade

mode is equal to 1 for continuous data transfer mode and 2 for programming mode

EXAMPLE:

The MCLK comes from the DSP C5402's CLKOUT and equals to 20.48 MHz and the conversion rate of 8 kHz is desired. First, set P=1 to satisfy the condition 5 so that (MCLK/P) = 20.48 MHz/1 = 20.48 MHz. Next, pick M=10 and N=16 to satisfy condition 6 and derive 8 kHz for FS. That is,

$$FS = 20.48 \text{ MHz} / (16 \times 10 \times 16 \times 1) = 8 \text{ kHz}$$

#### 3.2 Internal Architecture

#### 3.2.1 Antialiasing Filter

The built-in antialiasing filter is a two-pole filter that has a 20-dB attenuation at 1 MHz.

#### 3.2.2 Sigma-Delta ADC

The sigma-delta analog-to-digital converter is a sigma-delta modulator with 128-x oversampling. The ADC provides high-resolution, low-noise performance using oversampling techniques. Due to the oversampling employed, only single pole R-C filters are required on the analog inputs.

#### 3.2.3 Decimation Filter

The decimation filters are either FIR filters or IIR filters selected by bit D5 of the control register 1. The FIR filter provides linear-phase output with  $17/f_S$  group delay, whereas the IIR filter generates nonlinear phase output with negligible group delay. The decimation filters reduce the digital data rate to the sampling rate. This is accomplished by decimating with a ratio of 1:128. The output of the decimation filter is a 16-bit 2s-complement data word clocking at the sample rate selected for that particular data channel. The BW of the filter is  $(0.45 \times FS)$  and scales linearly with the sample rate.

#### 3.2.4 Sigma-Delta DAC

The sigma-delta digital-to-analog converter is a sigma-delta modulator with 128/256/512-x oversampling. The DAC provides high-resolution, low-noise performance using oversampling techniques. The oversampling ratio in DAC is programmable to 256/512 using bits D4–D3 of control register 3, the default being 128. Oversampling ratio of 512 can be used when FS is a maximum of 8 Ksps and an oversampling ratio of 256 can be used when FS is a maximum of 16 Ksps. M should be a multiple of 2 for oversampling ratio of 256 and 4 for an oversampling ratio of 512.

#### 3.2.5 Interpolation Filter

The interpolation filters are either FIR filters or IIR filters selected by bit D5 of the control register 1. The FIR filter provides linear-phase output with  $18/f_s$  group delay, whereas the IIR filter generates nonlinear phase output with negligible group delay. The interpolation filter resamples the digital data at a rate of 128/256/512 times the incoming sample rate, based on the oversampling rate of DAC. The high-speed data output from the interpolation filter is then used in the sigma-delta DAC. The BW of the filter is  $(0.45 \times FS)$  and scales linearly with the sample rate.

#### 3.2.6 Analog/Digital/Side-Tone Loopback

The analog and digital loopbacks provide a means of testing the data ADC/DAC channels and can be used for in-circuit system level tests. The analog loopback always has the priority to route the DAC low pass filter output into the analog input where it is then converted by the ADC to a digital word. The digital loopback routes the ADC output to the DAC input on the device. Analog loopback is enabled by writing a 1 to bit D2 in the control register 1. Digital loopback is enabled by writing a 1 to bit D1 in control register 1. The side-tone digital loopback attenuates the ADC output and mixes it with the input of the DAC. The level of the side tone is set by DSTG, bits D5–D3 of the control register 5C.

#### 3.2.7 ADC PGA

TLV320AlC13 has a built-in PGA for controlling the signal levels at ADC outputs. ADC PGA gain setting can be selected by writing into bits D5–D0 of register 5A. The PGA range of the ADC channel is 20 dB to –42 dB in steps of 1 dB and mute. To avoid sudden jumps in signal levels with PGA changes, the gains are applied internally with zero-crossovers.

#### 3.2.8 DAC PGA

TLV320AlC13 has a built-in PGA for controlling the analog output signal levels in DAC channel. DAC PGA gain setting can be selected by writing into bits D5–D0 of register 5B. The PGA range of the DAC channel is 20 dB to –42 dB in steps of 1 dB, and mute. To avoid sudden *pop-sounds* with power-up/down and gain changes the power-up/down and gain changes for DAC channel are applied internally with zero-crossovers.

#### 3.3 Analog Input/Output

The TLV320AlC13 has three programmable analog inputs and three programmable analog outputs. Bits D2–D1 of control register 6 select the analog input source from MICIN, INP1/M1, or INP2/M2. All analog I/O is either single-ended or differential. All analog input signals are self-biased to 1.35 V. The three analog outputs are configured by bits D7, D6, D5, and D4–D3 of control register 6.

#### 3.3.1 MIC Input

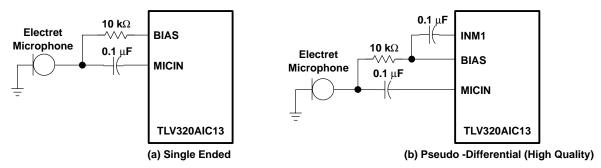

TLV320AlC13 supports single-ended microphone input. This can be used by connecting the external single-ended source through ac-coupling to the MICIN pin. This channel is selected by writing 01 or 10 into bits D2–D1 in control register 6. The single-ended input is supported in two modes.

Writing 01 into bits D2–D1 chooses self biased MICIN mode. In this mode the device internally self-biases the input at 1.35 V. For best noise performance the user must bias the microphone circuit using the BIAS voltage generated by the device as shown in Figure 5–19.

Writing 10 into bits D2–D1 chooses pseudodifferential MICIN mode. In this mode the single-ended input is connected through ac-coupling to MICIN and the bias voltage used to generate the signal is also ac-coupled to INM1 as shown in Figure 5–20. For best noise performance the MICIN and INM1 lines are routed in similar fashion from the microphone to the device for noise cancellation.

For high quality performance the single-ended signal is converted internally into differential signal before being converted. To improve the dynamic range with different types of microphones the device supports a pre-amplifier with gain settings of 0/6/12/24 dB. This can be chosen by writing into bits D1–D0 of control register 5C.

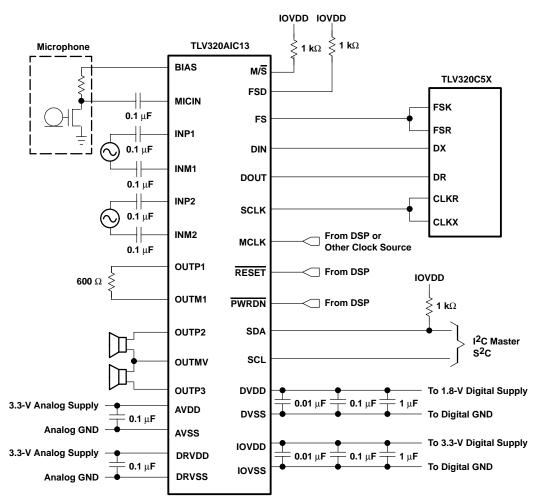

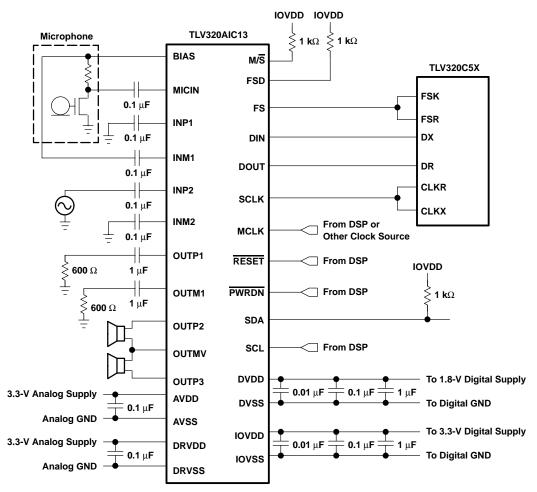

Figure 3–1. Microphone Interface

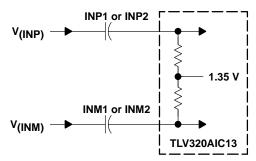

#### 3.3.2 INP and INM Input

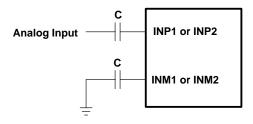

To produce common-mode rejection of unwanted signal performance, the analog signal is processed differentially until it is converted to digital data. The signal applied to the terminals INM1/2 and INP1/2 are differential to preserve device specifications (see Figure 3–2). The signal source driving analog inputs (INP1/2 and INM1/2) should have low source impedance for lowest noise performance and accuracy. To obtain maximum dynamic range, the signal must be ac-coupled to the input terminal.

Figure 3-2. INP and INM Internal Self-Biased Circuit

#### 3.3.3 Single-Ended Analog Input

The two differential inputs of (INP1/M1 and INP2/M2) can be configured to work as single-ended inputs by connecting INP to the analog input and INM to ground (see Figure 3–3).

Figure 3-3. Single-Ended Input

#### 3.3.4 Analog Output

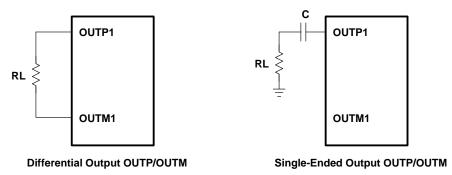

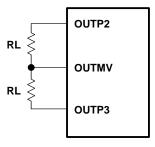

The OUTP and OUTM are differential output from the DAC channel. The OUTP1 and OUTM1 can drive a load of  $600-\Omega$  directly and be either differential or single-ended (see Figure 3–4). The OUTP2 and OUTP3 are output from two audio amplifiers to drive low-voltage speakers like those in the handset and headset. They can drive a load of  $16-\Omega$  directly and be configured as either differential output or single-ended output as by bit D7 of the control register 6 (see Figure 3–5). If OUTP2 and OUTP3 are differential output, the OUTMV pin becomes the common inverting output. Both OUTP2 and OUTP3 can be used simultaneously if each differential load  $R_L > 64~\Omega$ . This is because OUTMV amp can drive a maximum load of  $16~\Omega$  only (only one driver used) or a parallel combination of two  $32-\Omega$  loads (both drivers used). If both OUTP2 and OUTP3 are used simultaneously, they are muted at the same time if MUTE is selected.

Otherwise, the OUTMV pin is configured as the *virtual* ground for single-ended output and equal to the common mode voltage at 1.35 V.

Figure 3-4. OUTP1/OUTM1 Output

Figure 3-5. Single-Ended/Differential Connection of OUTP2/OUTP3 Output

| Table 3-1. An | alog Outpu | t Load Resis | stance |

|---------------|------------|--------------|--------|

|               |            |              |        |

| SPEAKER DRIVER CONFIGURATION | NO. OF SPEAKER DRIVERS ON | MIN LOAD |

|------------------------------|---------------------------|----------|

| Single-ended                 | 1                         | 16-Ω     |

| Single-ended                 | 2                         | 32-Ω     |

| Differential                 | 1                         | 32-Ω     |

| Differential                 | 2                         | 64-Ω     |

#### 3.4 IIR/FIR Control

#### 3.4.1 Overflow Flags

The decimation IIR/FIR filter sets an overflow flag (bit D7) of control register 1 indicating that the input analog signal has exceeded the range of internal decimation filter calculations. The interpolation IIR/FIR filter sets an overflow flag (bit D4) of control register 1 indicating that the digital input has exceeded the range of internal interpolation filter calculations. When the IIR/FIR overflow flag is set in the register, it remains set until the user reads the register. Reading this value resets the overflow flag. These flags need to be reset after power-up by reading the register. If FIR/IIR overflow occurs, the input signal is attenuated by either the PGA or some other method.

#### 3.4.2 IIR/FIR Bypass Mode

An option is provided to bypass IIR/FIR filter sections of the decimation filter and the interpolation filter. This mode is selected through bit D6 of control register 2 and effectively increases the frequency of the FS signal to four times normal output rate of the IIR/FIR-filter. For example, for a normal sampling rate of 8 Ksps (i.e., FS = 8 kHz) with IIR/FIR, if the IIR/FIR is bypassed, the frequency of FS is readjusted to  $4\times8$  kHz = 32 kHz. The sinc filters of the two paths can not be bypassed. A maximum of eight devices in cascade can be supported in the IIR/FIR bypassed mode.

In this mode, the ADC channel outputs data which has been decimated only till 4 Fs. Similarly DAC channel input needs to be pre-interpolated to 4 Fs before being given to the device. This mode allows users the flexibility to implement their own filter in DSP for decimation and interpolation. M should be a multiple of 4 during IIR/FIR Bypass mode.

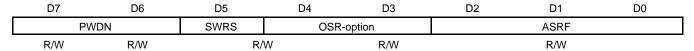

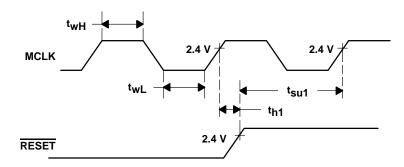

#### 3.5 System Reset and Power Management

#### 3.5.1 Software and Hardware Reset

The TLV320AIC13 resets internal counters and registers in response to either of two events:

- A low-going reset pulse is applied to terminal RESET

- A 1 is written to the programmable software reset bits (D5 of control register 3)

**NOTE:** The TLV320AlC13 requires a power-up reset applied to the RESET pin.

Either event resets the control registers and clears all sequential circuits in the device. The H/W RESET (active low) signal is at least 6 master clock periods long. As soon as the RESET input is applied, the TLV320AlC13 enters the initialization cycle that lasts for 132 MCLKs, during which the DSPs serial port is put in 3-state. For a cascaded system the rise time of H/W RESET needs to be less than the MCLK period and should satisfy setup time requirement of 2 ns with respect to MCLK rise-edge. In stand-alone-slave mode SCLK must be running during RESET. RESET must be synchronized with MCLK in all cases.

#### 3.5.2 Power Management

Most of the device (all except the digital interface) enters the power-down mode when D7 and D6, in control register 3, are set to 1. When the PWRDN pin is low, the entire device is powered down. In either case, register contents are preserved and the output of the amplifier is held at midpoint voltage to minimize pops and clicks.

The amount of power drawn during software power down is higher than during a hardware power down because of the current required to keep the digital interface active. Additional differences between software and hardware power-down modes are detailed in the following paragraphs.

#### 3.5.2.1 Software Power-Down

Data bits D7 and D6 of control register 3 are used by TLV320AlC13 to turn on or off the software power-down mode, which takes effect in the next frame FS. The ADC and DAC can be powered down individually. In the software power-down, the digital interface circuit is still active while the internal ADC and DAC channel and differential outputs OUTPx and OUTMx are disabled, and DOUT is put in 3-state in the data frame only. Register data in the control frame is still accepted via DIN, but data in the data frame is ignored. The device returns to normal operation when D7 and D6 of control register 3 are reset.

#### 3.5.2.2 Hardware Power-Down

The TLV320AlC13 requires the PWRDN signal to be synchronized with MCLK. When PWRDN is held low, the device enters hardware power-down mode. In this state, the internal clock control circuit and the differential outputs are disabled. All other digital I/Os are disabled and DIN can not accept any data input. The device can only be returned to normal operation by holding PWRDN high. When not holding the device in the hardware power-down mode, PWRDN must be tied high.

#### 3.6 Digital Interface

#### 3.6.1 Clock Source (MCLK, SCLK)

MCLK is the external master clock input. The clock circuit generates and distributes necessary clocks throughout the device. SCLK is the bit clock used to receive and transmit data synchronously. When the device is in the master mode, SCLK and FS are output and derived from MCLK in order to provide clocking the serial communications between the device and a digital signal processor (DSP). When in the slave mode, SCLK and FS are inputs. In the non-turbo mode (TURBO = 0), SCLK frequency is defined by:

$$SCLK = (16 \times FS \times \#Devices \times mode)$$

Where:

FS is the frame-sync frequency.

#Device is the number of the device in cascade.

Mode is equal to 1 for continuous data transfer mode and 2 for programming mode.

In turbo mode, see Section 3.8.3.

#### 3.6.2 Serial Data Out (DOUT)

DOUT is placed in the high-impedance state after transmission of the LSB is completed. In data frame, the data word is the ADC conversion result. In the control frame, the data is the register read results when requested by the read/write (R/W) bit. If a register read is not requested, the low eight bits of the secondary word are all zeroes. Valid data on DOUT is taken from the high-impedance state by the falling edge of frame-sync (FS). The first bit transmitted on the falling edge of FS is the MSB of valid data.

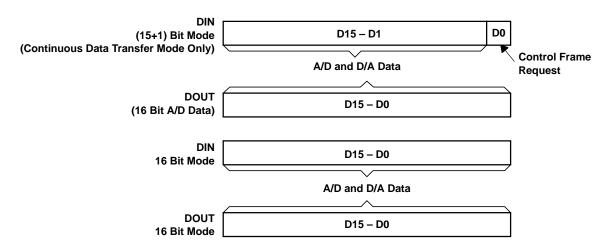

#### 3.6.3 Serial Data In (DIN)