### **Features**

- DC to DC Step Down 1.2 A, 0.9V (Dynamically Adjustable to 0.87V/1.1V/1.2V)

- DC to DC step Down 1.2 A, 1.2V (Dynamically Adjustable to 1.0V/1.1V/1.3V) or 1.75V (Dynamically Adjustable 1.65V/1.70V/1.80V)

- DC to DC Step Down 1.2 A, 1.8V (Dynamically Adjustable to 1.70V/1.75V/1.85V) or 2.5V (Dynamically Adjustable 2.3V/2.4V/2.6V)

- DC to DC Step Up/Down 520 mA, 3.3V (Dynamically Adjustable to 3.0V/3.1V/3.4V)

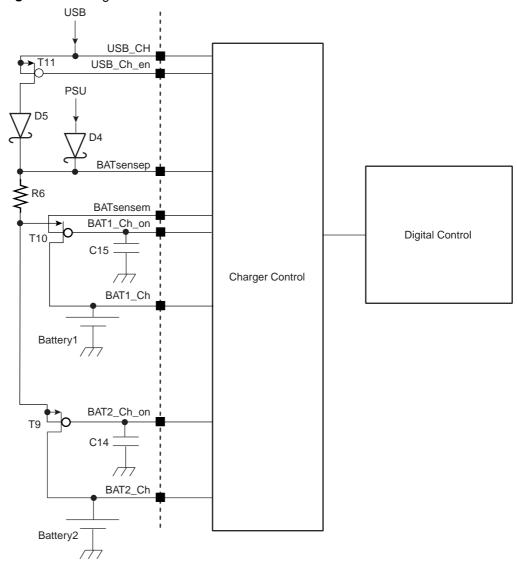

- Dual Battery Chargers: Li+ Precharge, Fast Charge, Top-up Charge, 4.1V (or Adjustable), Processor Tuned Algorithms

- USB Trickle Charge: Precharge Flat Battery from USB Pre-enumeration, then Autowake of Processor at 3.8V Battery Level

- Battery Charge Select: 25 mA to 500 mA

- Real-time Charge Inhibit: Allows Charge Suspend (e.g. During TX Slots)

- Supply Monitor of Four Power Sources: Thermistors, Temperature, DC/DC Rails, all Supplied with Out-of-regulation Threshold Detection

- SIM Interface: SIM / USIM, 1.8V / 3.0V Standards, Integrated TX and RX Data FIFO

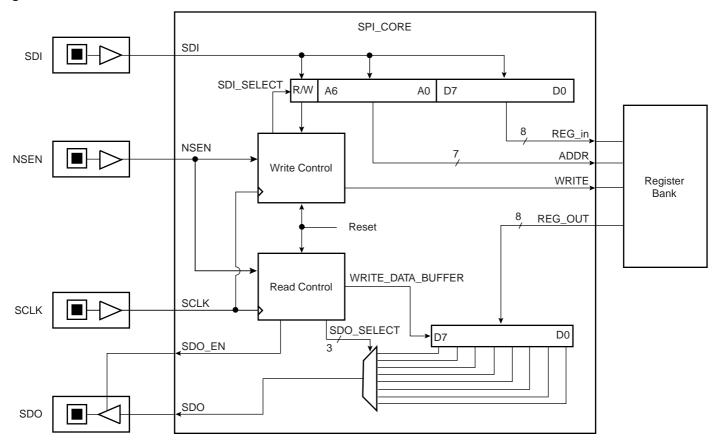

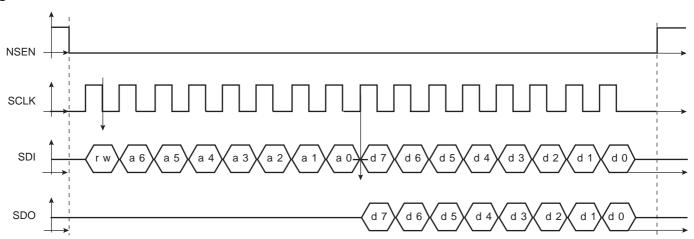

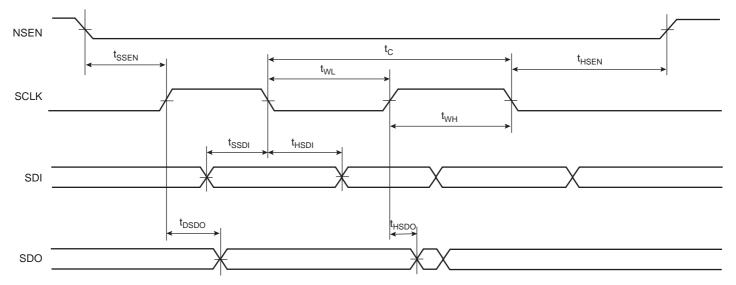

- SPI Control Interface: Up to 13 MHz; Tuned for SA1110/PXA250/PXA255 1.2 MHz SPI, 128 8-bit Registers

- Power on Reset: For SA1110/PXA250/PXA255 Architectures plus Additional Sequenced System Level Resets

- Voltage and Temperature Supervision

- Calibrated Voltage Reference

- 8-bit ADC with 5-input Multiplexer

- Integrated Oscillator, Start-up and Self-protection Circuitry

- Off Power: 60 µA with External "Button Select" for Restart

- Applications Include: PDAs, PCMCIA Cards, SMART Phones, Pocket PCs, 3G Applications, Intel<sup>®</sup> XScale<sup>™</sup> Powered Applications

### **Description**

The AT73C203 device provides an integrated solution to portable and handheld applications built around microprocessors requiring "smart" power management functions, such as PDAs, Palmtop computers, point-of-sales terminals, 3G modems, etc.

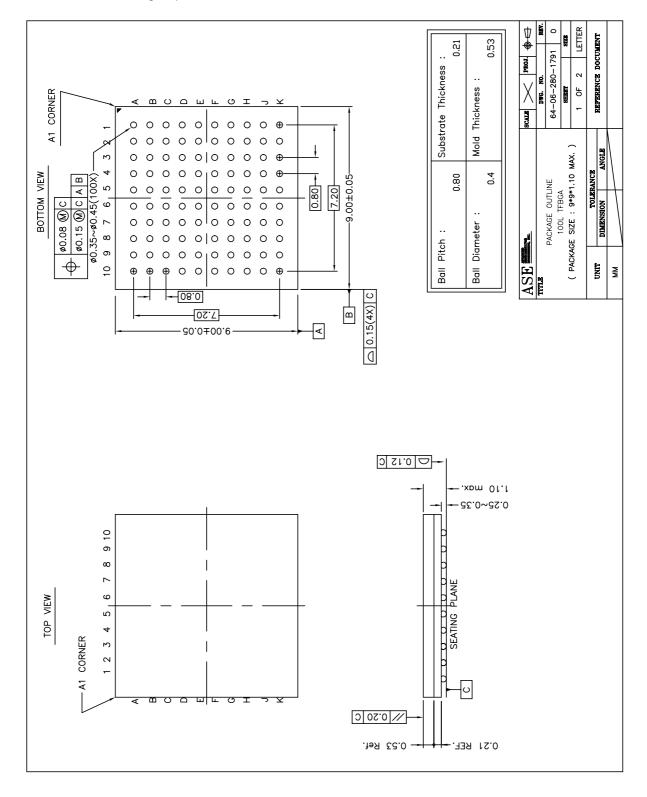

Its compact package outline and small size of external components make the AT73C203 suitable for PCMCIA card power management as well.

The AT73C203 integrates a power switch controller that, when connected to an external power switch, may be used for automatically selecting one of four possible power sources:

- Internal battery

- External battery

- Plugtop power supply unit 5V (PSU)

- PC Host USB supply

The power switch output (VDD-PSU line) is connected directly to external auxiliary components such as a radio or any other "current hungry" module.

The AT73C203 is also equipped with four digital rails from VDD-PSU to supply a base-band chip, a reset generator for the baseband chip, and a SPI interface to control the AT73C203 via an internal register set. The USIM interface allows the application processor to communicate with and control a USIM card. Charge control enables the application processor to charge the battery from the PSU or USB. A state machine can also determine whether to charge the internal battery through USB at start-up. Additionally, hardware monitoring gives information to the application processor when a voltage drop occurs (programmed via internal registers).

# Power Management

AT73C203

Power

Management IC

for Datacom

Platforms

2742B-PMGMT-03/04

### **Functional Diagram**

Figure 1. AT73C203 Functional Diagram

### **Pin Description**

Table 1. AT73C203 Pin Description

| Signal Name         | Pin Type | Pack Pin | Level           | ESD Protection | Comments        |  |

|---------------------|----------|----------|-----------------|----------------|-----------------|--|

| AVSS                | A-I      | A1       | AVSS            |                | ESD Ground      |  |

| SELDC175            | D-I      | B2       | gnddig - vsauv  | avss - vswin   | Digital control |  |

| SELDC25             | D-I      | B1       | gnddig - vsauv  | avss - vswin   | Digital control |  |

| nEN_RAIL3           | D-I/O    | А3       | gnddig - vsauv  | avss - vswin   | Digital control |  |

| nEN_RAIL4           | D-I/O    | A2       | gnddig - vsauv  | avss - vswin   | Digital control |  |

| nASIC_RESET         | D-O      | C3       | gnddig - vout3  | avss - vout3   | RESET           |  |

| nBOARD_RESET        | D-O      | C1       | gnddig - vout3  | avss - vout3   | RESET           |  |

| BOARD_RESET         | D-O      | C2       | gnddig - vout3  | avss - vout3   | RESET           |  |

| nPROC_RESET         | D-O      | D4       | gnddig - vout3  | avss - vout3   | RESET           |  |

| nPROC_RESET_OUT     | D-I      | D3       | gnddig - vout3  | avss - vout3   | RESET           |  |

| nASIC_RESET_REQUEST | D-I      | D1       | gnddig - vout3  | avss - vout3   | RESET           |  |

| POWER_EN            | D-I      | D2       | gnddig - vout3  | avss - vout3   | Digital control |  |

| SYST_CLK            | D-I      | A4       | gnddig - vout3  | avss - vout3   | Digital control |  |

| nUSIM_INT           | D-O      | E1       | gnddig - vout3  | avss - vout3   | Digital control |  |

| nINT                | D-O      | E2       | gnddig - vout3  | avss - vout3   | Digital control |  |

| BUTTON_OUT          | D-O      | E3       | gnddig - vout3  | avss - vout3   | Digital control |  |

| CHG_INHIBIT         | D-I      | F1       | gnddig - vout3  | avss - vout3   | Digital control |  |

| TEST1               | D-I/O    | F2       | gnddig - vsauv  | avss – vsauv   | TEST            |  |

| TEST2               | D-I/O    | F3       | gnddig - vsauv  | avss - vsauv   | TEST            |  |

| IDBITS3             | D-I/O    | G1       | gnddig - vout3  | avss - vout3   | Digital control |  |

| IDBITS2             | D-I/O    | F4       | gnddig - vout3  | avss - vout3   | Digital control |  |

| IDBITS1             | D-I/O    | G2       | gnddig - vout3  | avss - vout3   | Digital control |  |

| IDBITS0             | D-I/O    | H1       | gnddig - vout3  | avss - vout3   | Digital control |  |

| SDO                 | D-I/O    | G3       | gnddig - vout3  | avss - vout3   | SPI             |  |

| SDI                 | D-I      | H2       | gnddig - vout3  | avss - vout3   | SPI             |  |

| SCLK                | D-I      | J1       | gnddig - vout3  | avss - vout3   | SPI             |  |

| nSEN                | D-I      | E5       | gnddig - vout3  | avss - vout3   | SPI             |  |

| GNDDIG              | A-I      | K1       | GND             | avss - gnddig  | Digital ground  |  |

| VOUT3               | A-I      | K2       | gnddc3 - vout3  | avss - vboost  | DCDC rail3      |  |

| VBOOST              | A-I      | J2       | gnddc3 - vddpsu | PCboost        | DCDC rail3      |  |

| DH3                 | A-O      | K3       | gnddc3 - vddpsu | avss - vboost  | DCDC rail3      |  |

| GNDDC3              | A-I      | H3       | GND             | avss - gnddc3  | DCDC rail3      |  |

| DL3                 | A-O      | J3       | gnddc3 - vddpsu | avss - PCmax   | DCDC rail3      |  |

| VDDPSU3             | A-I      | G4       | gnddc3 - vddpsu | avss - PCmax   | DCDC rail3      |  |

Table 1. AT73C203 Pin Description (Continued)

| Signal Name                  | Pin Type                               | Pack Pin          | Level                        | ESD Protection | Comments      |

|------------------------------|----------------------------------------|-------------------|------------------------------|----------------|---------------|

| DCSENSE3                     | A-I                                    | H4                | gnddc3 - vddpsu avss - PCmax |                | DCDC rail3    |

| VOUT2                        | A-I                                    | K4                |                              |                | DCDC rail2    |

| DCSENSE2                     | A-I                                    | H5                | gnddc2 - vddpsu avss - PCmax |                | DCDC rail2    |

| DH2                          | A-O                                    | K5                | gnddc2 - vddpsu              | avss - PCmax   | DCDC rail2    |

| VDDPSU2                      | A-I                                    | G5                | gnddc2 - vddpsu              | avss - PCmax   | DCDC rail2    |

| GNDDC2                       | A-I                                    | J4                | GND                          | avss - gnddc2  | DCDC rail2    |

| DL2                          | A-O                                    | J5                | gnddc2 - vddpsu              | avss - PCmax   | DCDC rail2    |

| VOUT1                        | A-I                                    | K6                | gnddc1 - vout1               | avss - PCmax   | DCDC rail1    |

| DCSENSE1                     | A-I                                    | H6                | gnddc1 - vddpsu              | avss - PCmax   | DCDC rail1    |

| DH1                          | A-O                                    | K7                | gnddc1 - vddpsu              | avss - PCmax   | DCDC rail1    |

| VDDPSU1                      | A-I                                    | G6                | gnddc1 - vddpsu              | avss - PCmax   | DCDC rail1    |

| GNDDC1                       | A-I                                    | J6                | GND                          | avss - gnddc1  | DCDC rail1    |

| DL1                          | A-O                                    | J7                | gnddc1 - vddpsu              | avss - PCmax   | DCDC rail1    |

| VOUT4                        | A-I                                    | J10               | gnddc4 - vout4               | avss - PCmax   | DCDC rail4    |

| DCSENSE4                     | A-I                                    | K9                | gnddc4 - vddpsu              | avss - PCmax   | DCDC rail4    |

| DH4                          | A-O                                    | K8                | gnddc4 - vddpsu              | avss - PCmax   | DCDC rail4    |

| VDDPSU4                      | A-I                                    | K10               | gnddc4 - vddpsu              | avss - PCmax   | DCDC rail4    |

| GNDDC4                       | A-I                                    | J9                | GND                          | avss - gnddc4  | DCDC rail4    |

| DL4                          | A-O                                    | J8                | gnddc4 - vddpsu              | avss - PCmax   | DCDC rail4    |

| SIM_CLK                      | D-O                                    | H10               | gnddig - vsim                | avss - PCmax   | SIM           |

| SIM_RESET                    | D-O                                    | H9                | gnddig - vsim                | avss - PCmax   | SIM           |

| SIM_IO                       | D-I/O                                  | G7                | gnddig - vsim                | avss - PCmax   | SIM           |

| SIM_VCC                      | A-O                                    | G8                | gnddig - vsim                | avss - PCmax   | SIM regulator |

| GND_CH                       | A-I                                    | E6                | GND                          | avss - gndch   | Charger       |

| BAT2_CH                      | A-I                                    | F7                | gndch - maxsupply            | avss - PCmax   | Charger       |

| BAT1_CH                      | A-I                                    | F10               | gndch - maxsupply            | avss - PCmax   | Charger       |

| BAT2_CH_ON                   | A-O                                    | F9                | gndch - maxsupply            | avss - PCmax   | Charger       |

| BAT1_CH_ON                   | A-O                                    | F8                | gndch - maxsupply            | avss - PCmax   | Charger       |

| BATSENSEM                    | A-I                                    | E10               | gndch - maxsupply            | avss - PCmax   | Charger       |

| BATSENSEP                    | A-I                                    | E9                | gndch - maxsupply            | avss - PCmax   | Charger       |

| USB_CH_EN                    | A-O                                    | E8                | gndch - maxsupply            | avss - PCmax   | Charger       |

| USB_CH                       | A-I D10 gndch - maxsupply avss - PCmax |                   | Charger                      |                |               |

| GABAT1                       | D-O E7 gnda1 - maxsupply avss - PCmax  |                   | avss - PCmax                 | Power switch   |               |

| GABAT2                       | D-O                                    | D9                | gnda1 - maxsupply            | avss - PCmax   | Power switch  |

| GAPSU D-O C10 gnda1 - maxsup |                                        | gnda1 - maxsupply | avss - PCmax                 | Power switch   |               |

| VDDPSU                       | A-I                                    | G10               | gnda1 - vddpsu               | avss - PCmax   | Power switch  |

Table 1. AT73C203 Pin Description (Continued)

| Signal Name  | Pin Type | Pack Pin | Level             | ESD Protection | Comments            |  |

|--------------|----------|----------|-------------------|----------------|---------------------|--|

| BAT1_PIO     | A-I      | D8       | gnda1 - bat1      | avss - PCmax   | Power switch        |  |

| BAT2_PIO     | A-I      | C9       | gnda1 - bat2      | avss - PCmax   | Power switch        |  |

| PSU_PIO      | A-I      | B10      | gnda1 - psu       | avss - PCmax   | Power switch        |  |

| USB_PIO      | A-I      | D6       | gnda1 - usb       | avss - PCmax   | Power switch        |  |

| MAXSUPPLY    | A-O      | A10      | gnda1 - maxsupply | PCmax          | Power switch        |  |

| GND_PIO      | A-I      | В9       | GND               | avss - gnda1   | Power switch        |  |

| VREFFUSE     | A-I      | A9       | avss - 5.5v       | avss-vswin     | FUSES               |  |

| VBIAS        | A-O      | C8       | gnda - vsauv      | avss - vswin   | Reference generator |  |

| CREF         | A-O      | A8       | gnda - vsauv      | avss - vswin   | Reference generator |  |

| VMES         | A-O      | B8       | gnda - vsauv      | avss - vswin   | Measurement bridge  |  |

| PORTEST      | D-O      | D7       | gnda - vsauv      | avss - vswin   | Power on reset      |  |

| THERM1       | A-O      | C7       | gnda - vsauv      | avss - vswin   | Current generator   |  |

| THERM2       | A-O      | A7       | gnda - vsauv      | avss - vswin   | Current generator   |  |

| GNDA         | A-I      | В7       | GND               | avss - gnda    | Internal regulator  |  |

| VSAUV        | A-O      | C6       | gnda - vsauv      | avss - vswin   | Internal regulator  |  |

| VSW          | A-I      | A6       | gnda - vswin      | avss - vswin   | Internal regulator  |  |

| VSWIN        | A-I      | B6       | gnda - vswin      | PCvswin        | Internal regulator  |  |

| SCAN_TEST_MD | D-I/O    | C4       | gnddig - vsauv    | avss - vswin   | TEST                |  |

| SCAN_ENABLE  | D-I/O    | A5       | gnddig - vsauv    | avss - vswin   | TEST                |  |

| nSHUTDOWN    | D-I      | B5       | gnddig - vsauv    | avss - vswin   | Digital control     |  |

| PCMCIA       | D-I      | C5       | gnddig - vsauv    | avss - vswin   | Digital control     |  |

| SIM_PRES     | D-I      | G9       | gnddig - vsauv    | avss - vswin   | Digital control     |  |

| BUTTON_IN    | D-I      | D5       | gnddig - vsauv    | avss - vswin   | Digital control     |  |

| NC           |          | B4       |                   |                | Not Connected       |  |

| NC           |          | E4       |                   |                | Not Connected       |  |

| NC           |          | H8       |                   |                | Not Connected       |  |

| NC           |          | H7       |                   |                | Not Connected       |  |

| NC           |          | F5       |                   |                | Not Connected       |  |

| NC           |          | В3       |                   |                | Not Connected       |  |

| NC           |          | F6       |                   |                | Not Connected       |  |

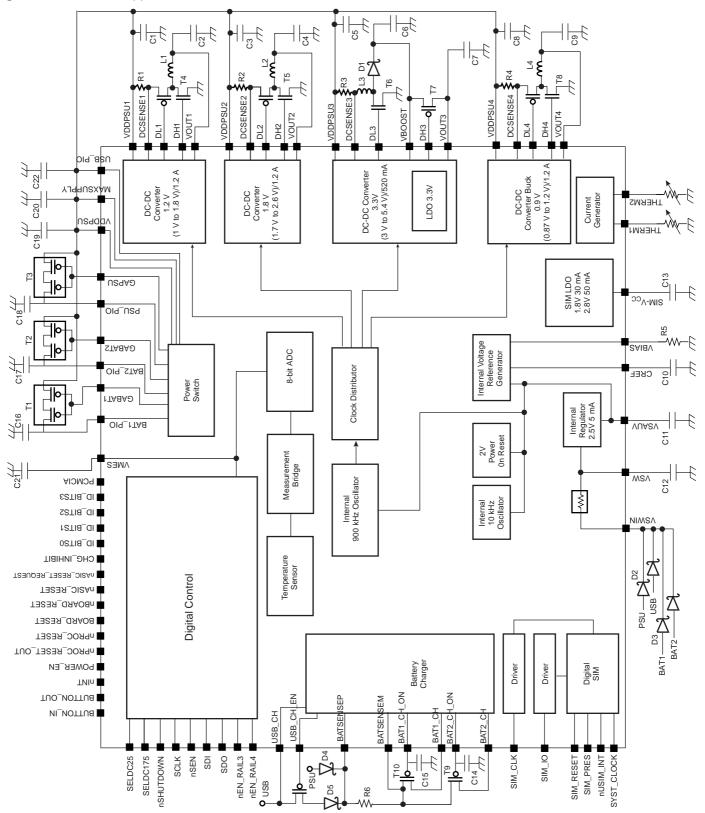

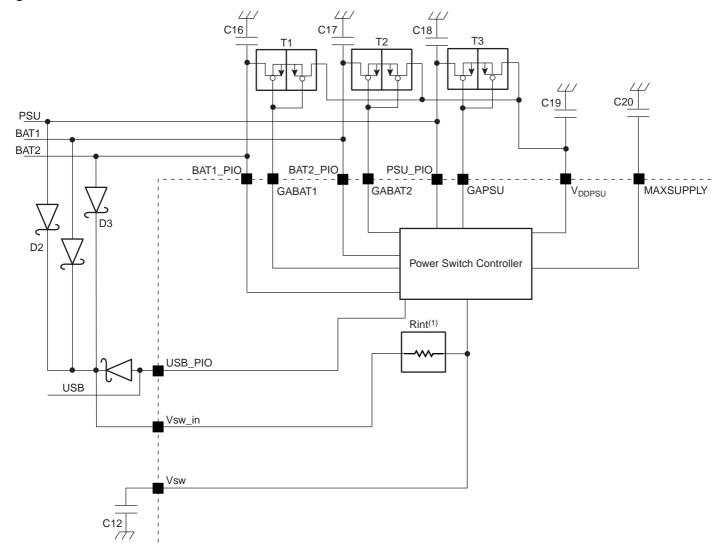

### **Application Schematic**

Figure 2. AT73C203 Application Schematic

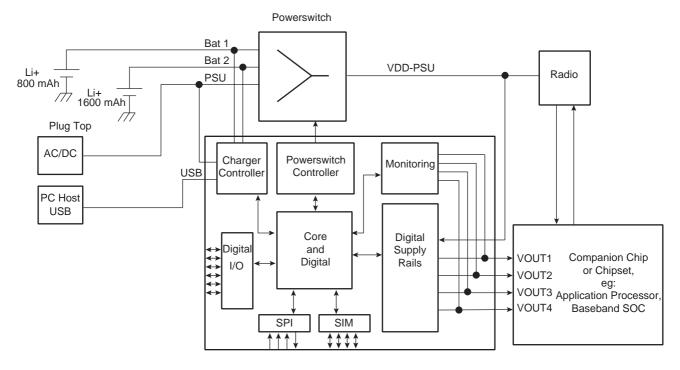

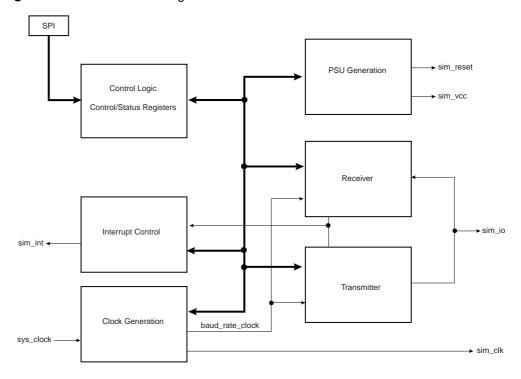

### **Architecture Overview**

Figure 3. AT73C203 Architecture Overview

## System Level Description

Several power sources may be used to power the AT73C203 circuitry including an internal or external battery, external PSU or USB. The internal battery is always physically present in the unit, but any or all of the other sources may be connected or disconnected at any time.

The AT73C203 enables one application to be powered up from the correct source of up to four possible power sources under hardware control. When powered, the external processor can monitor the input power sources and initiate battery charging as required via the SPI. The application processor is also able to enable/disable the circuit power rails and configure a low power sleep state.

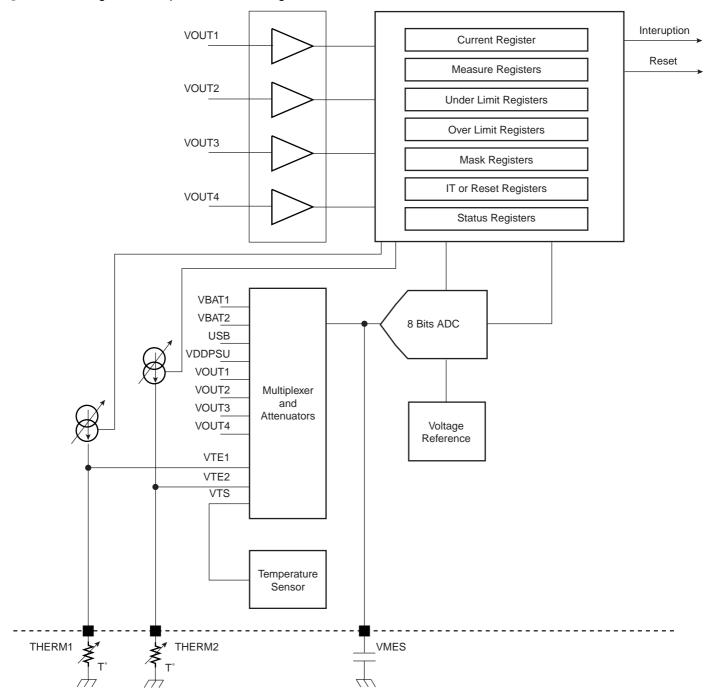

An input-multiplexed 8-bit ADC is available that allows the application processor to monitor the presence of and measure the voltage of the power sources, batteries and rails. An associated threshold and comparator circuit may be used to indicate to the processor that an out-of limit event has occurred.

The battery charging circuitry is designed to allow charging from the PSU input and to allow current-limited 'supplement' charging from the USB input. In both cases, the chargers operate under processor control and monitoring with hardware safety lockout.

When the PSU is present, a power path is selected (e.g. from a DC jack) through the power switching circuitry to the external components (e.g. radio and companion chips or chipset, baseband chip etc.) This power path enables the application processor to boot up. A parallel path exists from the PSU input (e.g. jack) through current limiting devices to two battery chargers. The current switches only block reverse current when disabled so care must be taken when controlling them.

When a USB input is powered, a single power path exists through the current limiting devices to the two battery chargers. The hardware defaults to a current limit of 100 mA

but the application processor may set 500 mA after negotiation with the PC. This power should always be used to charge the batteries in the absence of the PSU power source.

SIM/USIM interface hardware is provided, allowing the application processor to communicate and control a SIM/USIM card according to the required analog and digital specifications.

Most of the blocks are switched on or off by the digital control block (not all the control lines are drawn on the block diagram).

Only the supply monitor, digital control, power on reset, 10 kHz internal oscillator and internal regulator are always on.

All these blocks are designed to have very low power consumption, capable of achieving three months standby time for the application.

### **Functional Integration**

The AT73C203 integrates the following functions:

**Supply Monitor**

The supply monitor block enables the AT73C203 to correctly switch the four main supplies (two batteries, PSU and USB). All the outputs are sent to the digital control.

**Internal Regulator**

The internal regulator is a low drop out regulator generating  $V_{SAUV}$  at 2.5V with a maximum load of 5 mA. Its input is  $V_{SW}$ .

**Power-on Reset**

The internal power-on reset is supplied by  $V_{\text{SAUV}}$  and resets the AT73C203 digital circuitry at 2V.

10 kHz Internal Oscillator

The 10 kHz low power oscillator is the clock source for the AT73C203 digital circuitry.  $V_{\text{SALIV}}$  supplies it.

**Digital Control**

The digital block controls each block and drives the SPI interface and the different interrupts (external and internal). The controls, inputs and outputs are level shifted when necessary and protected to avoid current flowing between the blocks (not represented in the block diagram). A state machine controls the AT73C203 circuitry according the supplies and inputs states. A table of registers is accessible via SPI to command or read status of the AT73C203.

**Reference Generator**

The reference generator provides the AT73C203 with a precise bandgap voltage ( $V_{REF}$ ) and current bias ( $I_{REF}$ ) used by all analog blocks (DC/DC, ADC, charger) except the core blocks. It is turned off under digital control when necessary and is  $V_{SAUV}$  supplied.

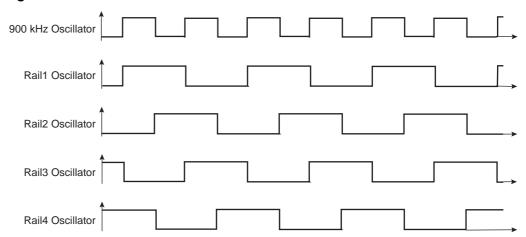

900 kHz Oscillator and Clock Distribution

The 900 kHz oscillator provides the clock to all DC/DC converters. The clock distributor provides phased clocks to the DC/DC converters to avoid switching at the same time. The frequency of the oscillator is trimmed during production to optimize the DC/DC efficiency.

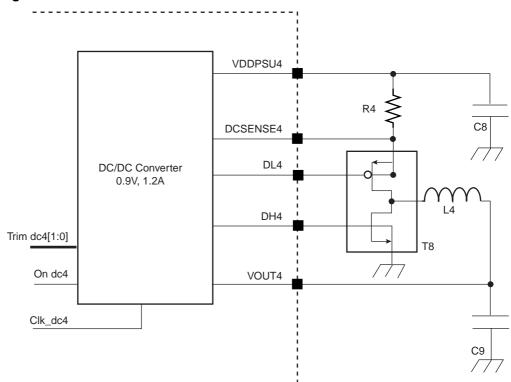

DC to DC Step Down 1.2 A, 0.9V

The DC to DC step Down 1.2A, 0.9V (dynamically adjustable to 0.87V/0.9V/1.1V/ 1.2V) is a programmable buck DC/DC converter dedicated to advanced sub-micron processors and SoC ASIC logic cores requiring dynamic power management at low voltages and high currents.

The default voltage is 0.9V for which the device is optimized.

The external components needed include a current sensing resistor, a dual PMOS-NMOS, an inductor and an output capacitor.

The application processor can change the output voltage via registers accessible by SPI.

When the cell is off, the output is in high impedance state.

If not used, this section can be permanently deactivated.

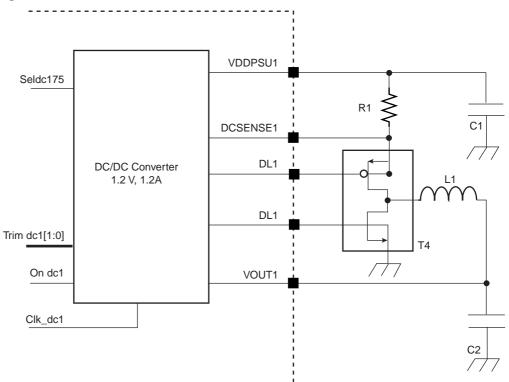

### DC to DC Step Down 1.2A, 1.2V OR 1.75V

The DC to DC step Down 1.2A, 1.2V (dynamically adjustable to 1.0V/1.1V/1.2V/1.3V) is a programmable buck synchronous DC/DC converter dedicated to the application processor core and/or a "companion" ASIC SoC Processor Core. The default voltage is 1.2V. An external pin can select 1.75V output voltage with tuning: 1.80V, 1.70V or 1.65V. The entire cell is optimized for 1.2V. The application processor can change the output voltage as described above via registers accessible by SPI.

The external components needed include a current sensing resistor, a dual PMOS-NMOS, one inductor and one output capacitor.

When the cell is off, the output is pulled to ground.

If not used, this section can be permanently deactivated

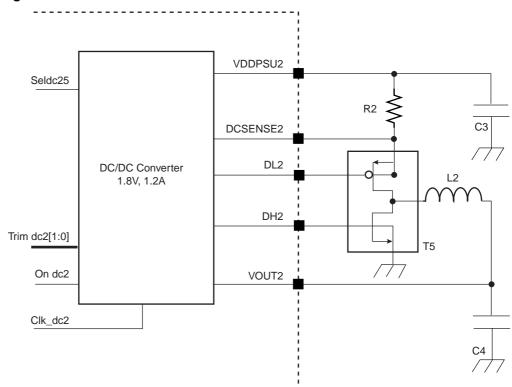

### DC to DC Step Down 1.2A, 1.8V OR 2.5V

The DC to DC step Down 1.2A, 1.8V (dynamically adjustable to 1.70V/1.75V/1.80V/1.85V) is a programmable buck synchronous DC/DC converter dedicated to the supply of recent and future Flash and SDRAM memories and their associated buses on the application processor I/O section as well as additional memory extension modules such as CF cards, MMCards, Memory Stick, etc. The default voltage is 1.8V. An external pin can select 2.5V output voltage with tuning: 2.6V, 2.4V and 2.3V. The entire cell is optimized for 1.8V. The application processor can change the output voltage as described above via registers accessible by SPI.

The external components needed include a current sensing resistor, a dual PMOS-NMOS, an inductor and an output capacitor.

A low quiescent current mode is implemented when a very low standby current is needed with a parallel voltage regulator.

When the cell is off, the output is in high impedance state.

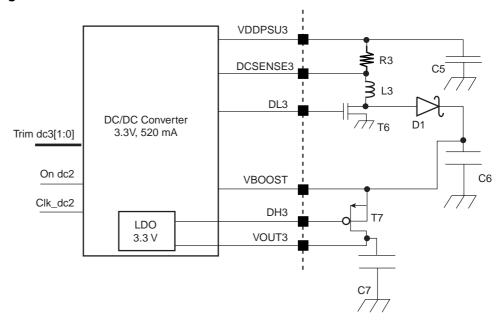

### DC to DC Step Up/ Down 520 mA, 3.3V

The DC to DC step Up/Down 520 mA, 3.3V (dynamically adjustable to 3.0V/3.1V/3.4V) is a boost DC/DC 3.6V converter followed by a linear drop out regulator. It is intended to supply 3.3V I/Os needed in the application (Audio Codec, LCD, Memories).

The external components needed include a current sensing resistor, an NMOS, a Schottky diode, an inductor and an output capacitor.

The default value of the LDO is 3.3V but three other values can be programmed: 3.1V, 3.2V and 3.4V. The entire cell is optimized for 3.3V. The application processor can change the output voltage as described above via registers accessible by SPI.

When the cell is off, the output is pulled to ground.

### **Power Switch Controller**

The power switch controller drives an external PMOS switch to multiplex VDD-PSU from the internal or external battery or USB. The purpose of this cell is to guarantee a sufficient supply for VDD-PSU and to limit voltage drops even during switchover. In-rush current and current flow between the inputs must be avoided.

When this cell is off, VDD-PSU is left in high impedance.

### **Current Generators**

Two accurate current generators allow the measurement of the resistance of two external battery thermistors. The outputs  $V_{THE1}$  and  $V_{THE2}$  go to the measurement bridge. The

current generators are supplied by  $V_{\text{SAUV}}$  and controlled by the digital control for use during battery charging.

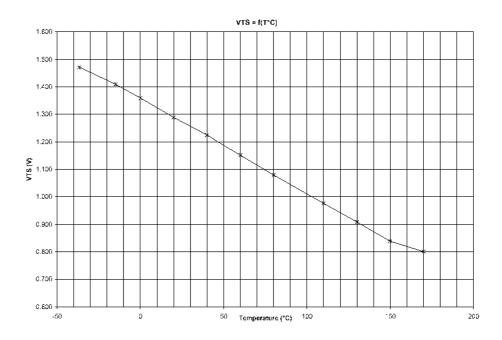

#### **Temperature Sensor**

The temperature sensor voltage output depends linearly on temperature. It is supplied by  $V_{\text{SAUV}}$  and driven by the digital control. The temperature seen by the sensor is directly related to the chip activity and the power internally dissipated. To get a good indication of the ambient temperature, the software must take into account this offset.

### Measurement Bridge/ Multiplexer

The measurement bridge provides adapted voltages of the internal and external batteries, DC/DC converter outputs, USB, VDD-PSU,  $V_{THE1}$  and  $V_{THE2}$  to the multiplexed input of the serial analog to digital converter.

### **Analog to Digital Converter**

An 8-bit analog to digital converter is integrated into the AT73C203 to give information about voltage and temperature to the application processor via the SPI interface.

### Li-Ion/Battery Chargers

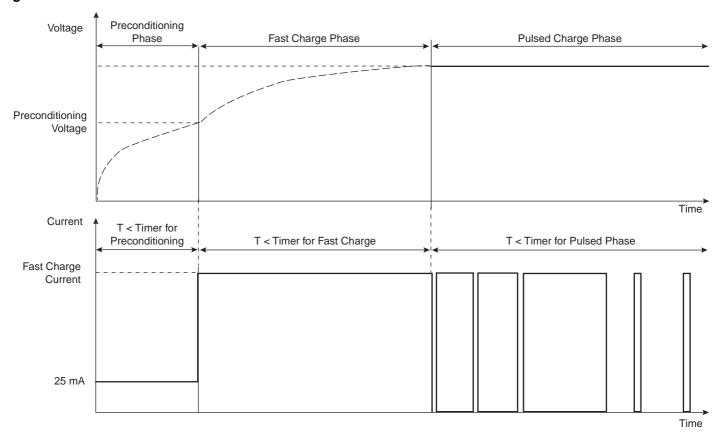

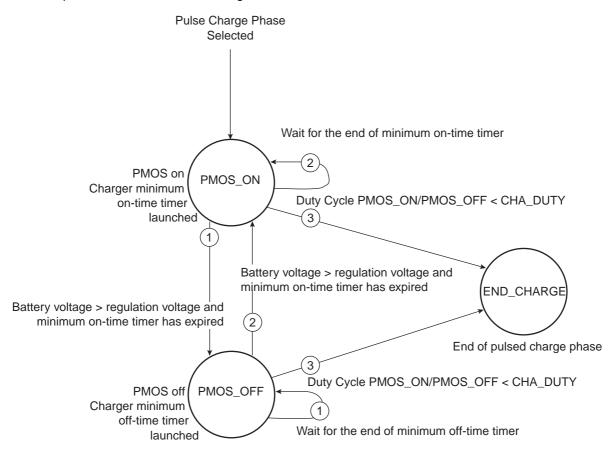

The battery chargers both have stand-alone constant current (CC) precharge and micro-processor-controlled CC fast charge as well as top-off mode end-of-charge algorithm.

The digital block controls this cell. All current and voltage settings are programmable via registers.

The charger controller is divided into two similar parts, one for the internal battery and one for the external battery. Each charger multiplexes the source (USB or PSU) and limits the programmable current charge (via sense resistor). An external PMOS and a Schottky diode are needed for each charger.

The application processor must check that the temperature allows charging via the current generator, measurement bridge and ADC.

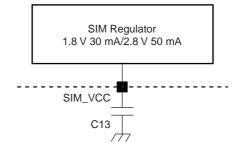

#### **USIM Voltage Regulator**

A regulator is provided to power up the USIM card. It is supplied directly from VDD\_PSU. One of two different voltages can be selected:

- 2.8V (50 mA)

- 1.8V (30 mA)

By default, the regulator is in power-down mode.

The pins connected to the USIM (SIM\_CLK, SIM\_IO, SIM\_PWR) must have driver specification according to ETS TS 102 221.

#### **USIM Digital Section**

The main part of the USIM digital section is an ISO7816 UART compatible interface.

#### **Reset Generation**

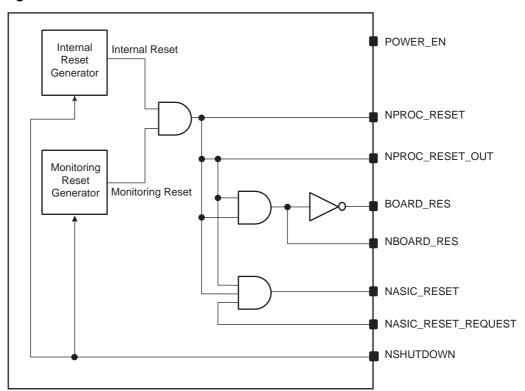

A reset is generated via the internal state machine. The timer for this internal reset generator is 150 ms (typical). The application processor can set the AT73C203 to off mode via the POWER\_EN pin. The "internal" reset is active at low level.

Another way to generate a reset is to program it through the monitoring function (ADC with measurement bridge and data registers). The "monitoring" reset is active at low level.

A logical AND of the "internal" and the "monitoring" reset drives the reset of the external application processor (NPROC\_RESET pin).

Other pins are used to generate separated resets for external "companion" chips such as baseband chips.

NSHUTDOWN forces the AT73C203 internal digital block to the reset state. This turns all the supplies off and then restarts the internal state machine.

### **Recommended External Components**

Table 2. Recommended External Components

| Schematic Reference                | Component Reference                                   |

|------------------------------------|-------------------------------------------------------|

| C1, C3, C5, C8, C16, C17, C18, C19 | 22 μF ceramic                                         |

| C2, C4, C6, C7, C9                 | 47 μF tantalum low ESR TPSW476M010R0150 or equivalent |

| C10, C20                           | 100 nF XR5 ±10%                                       |

| C11, C13, C22                      | 2.2 µF X5R ± 10%                                      |

| C12                                | 330 nF X5R ± 10%                                      |

| C14, C15                           | 10 nF X5R ± 10%                                       |

| C21                                | 100 pF X5R ± 10%                                      |

| L1, L4                             | 4.7µH SMT3106-471M (Gowanda®) or equivalent           |

| L2, L3                             | 10 μH SMT3106-102M (Gowanda) or equivalent            |

| D2, D3                             | Bat54C                                                |

| D4, D5, D1                         | MBRA120LT3 (ON Semiconductor®) or equivalent          |

| R1, R2, R4                         | 100 mΩ± 2% 250mW                                      |

| R3                                 | 100 mΩ ± 2% 250mW                                     |

| R5                                 | 220 kΩ ± 1%                                           |

| R6                                 | 200 mΩ ± 2% 50mW                                      |

| T1, T2, T3                         | Si4965DY                                              |

| T4, T5, T8                         | Si5513DC                                              |

| Т6                                 | Si1400DL                                              |

| T7, T9, T10                        | Si8401DL                                              |

| T11                                | Si1405DL                                              |

### **Absolute Maximum Ratings**

| Operating Ambient Temperature40°C to +85°C                   |

|--------------------------------------------------------------|

| Storage Temperature55°C to + 150°C                           |

| BAT1_PIO, BAT2_PIO, PSU_PIO, USB_PIO,                        |

| USB_CH, BAT1_CH, BAT2_CH, VSW_IN to ground Pins0.3V to +6.5V |

\*NOTICE:

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **Recommended Operating Conditions**

Table 3. Recommended Operating Conditions

| Parameter                     | Conditions                                                             | Min  | Max  | Unit |

|-------------------------------|------------------------------------------------------------------------|------|------|------|

| Operating Ambient Temperature |                                                                        | -40  | +85  | °C   |

| Storage Temperature           |                                                                        | -55  | +150 | °C   |

| Signal to Ground Pins         | BAT1_PIO, BAT2_PIO, PSU_PIO, USB_PIO, USB_CH, BAT1_CH, BAT2_CH, VSW_IN | -0.3 | +5.5 | V    |

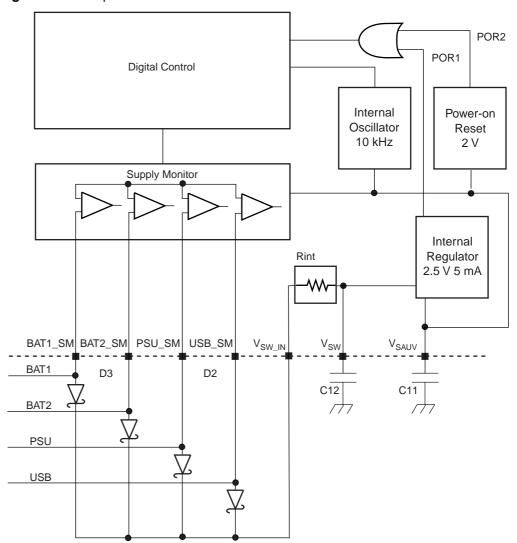

### **System Overview**

### Startup and Off Mode

Most of the blocks are switched on or off by the digital block. Only the supply monitor, digital control, power-on reset, internal 10kHz oscillator and internal regulator are always on.

Figure 4. Start-up Overview

The system has two modes: Off and Active.

**Off Mode:** All the cells are off except the supply monitor, digital control, power-on reset, internal 10 kHz oscillator and internal regulator. These blocks are designed to consume very little power in order to achieve an off time of three months from a 600 mA fully charged battery.

**Active Mode:** The power switch and all the DC/DC controllers are on. All the other cells are controlled by software (via internal registers).

#### **Startup Description**

V<sub>SW\_IN</sub> is an analog OR of BAT1, BAT2, USB and PSU implemented using four external Schottky diodes. Schottky diodes are used to minimize the power source to the AT73C203 voltage drop in order to maximize battery life. See Figure 4 on page 13.

When at least one of these supplies are present,  $V_{SW\_IN}$  tracks the highest voltage of the four inputs. An internal resistor (Rint) between  $V_{SW}$  and  $V_{SW\_IN}$  limits the current flowing through the diodes and C12.

$V_{SW}$  is the input of the internal regulator, which delivers the supply for the digital, oscillators, power-on reset, measurement bridge, reference generator, AD converter, temperature sensor, current generator and supply monitor blocks. Only a small current is supplied from  $V_{SW-IN}$  which minimizes the voltage drop across the Schottky diodes.

#### **Power-on-reset Protection**

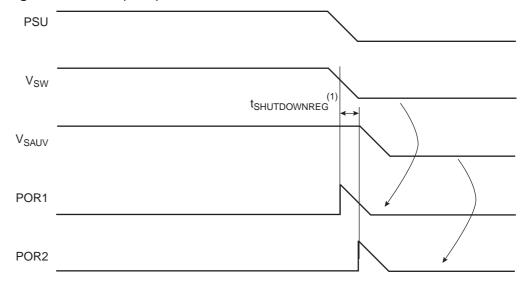

Figure 5 below and Figure 6 on page 15 illustrate the start-up sequence of the AT73C203 under the following conditions.

- One supply is present (PSU), the others are connected to ground or not present.

- POR1 supervises V<sub>SW</sub>. It goes to low level after the start-up time of the internal regulator.

- POR2 supervises V<sub>SAUV</sub>. It goes to low after V<sub>SAUV</sub> reaches the correct value for the digital core to run.

- Both V<sub>SW</sub> and V<sub>SAUV</sub> must be stable for the digital block to operate correctly.

- The reset for the digital core is the logical OR of POR1 and POR2.

PSU

V<sub>SW</sub>

V<sub>SAUV</sub>

POR1

POR2

Figure 5. PSU Rising Sequence

Note: 1.  $t_{STARTUPREG} = Startup$  time of the internal regulator.

Figure 6. PSU Drop Sequence

Note: 1.  $t_{SHUTDOWNREG} = Shutdown time of the internal regulator.$

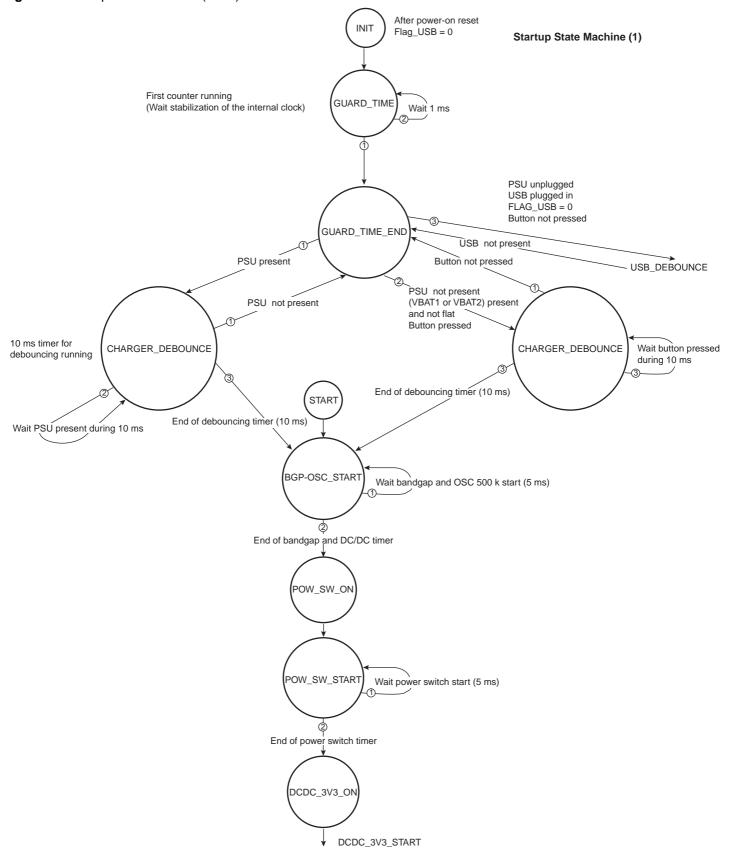

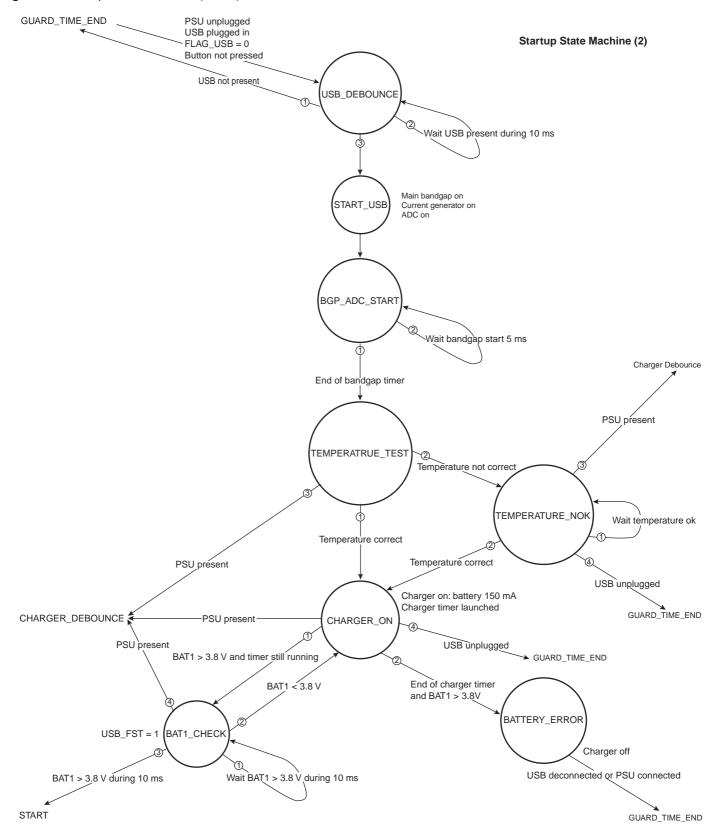

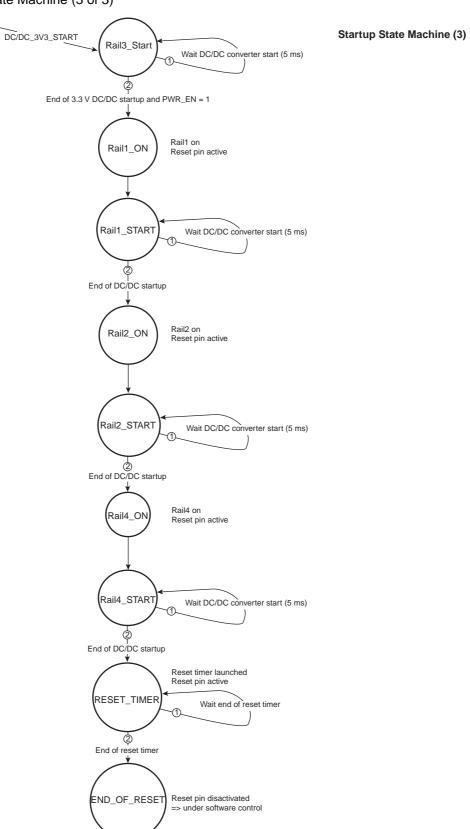

#### **State Machine Description**

State machines for the start-up and off modes are described in the following pages.

The state machine is completely synchronous to the internal 10 kHz oscillator and all the signals connected to the analog blocks are level shifted as necessary and protected to allow a reliable level.

USB\_FST is a digital flag. By default USB\_FST is set at 0. If the digital core begins to precharge battery 1 from USB at startup, USB\_FST is set to 1 by the internal digital block. The application processor can reset it to 0 via the SPI if needed by setting the USB\_FCR flag. This flag acts to avoid digital oscillation when the charge through USB is the start condition. It is also used to inform the application processor that the AT73C203 has charged the internal battery from USB with a minimal amount of charge.

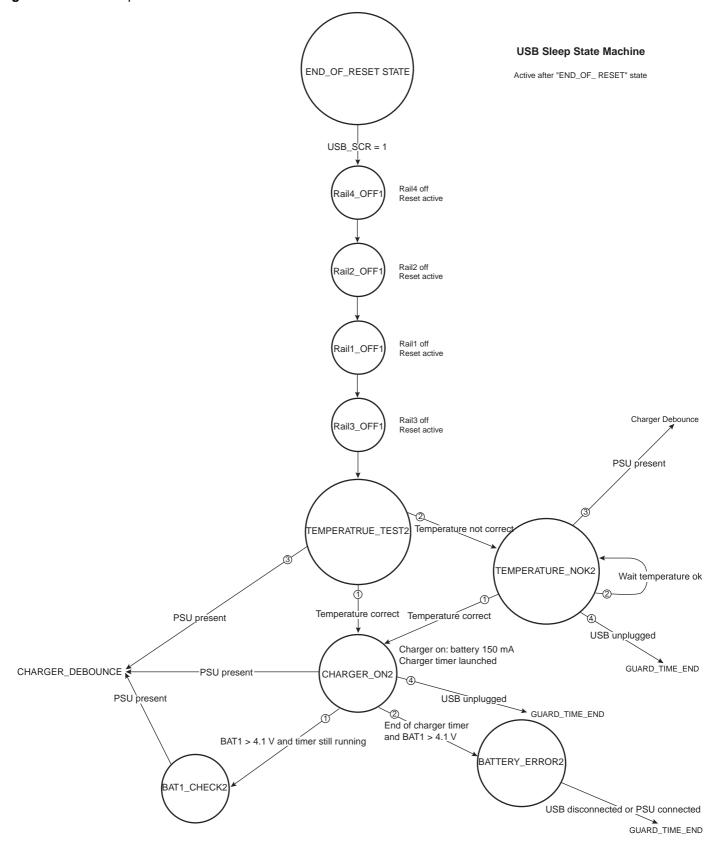

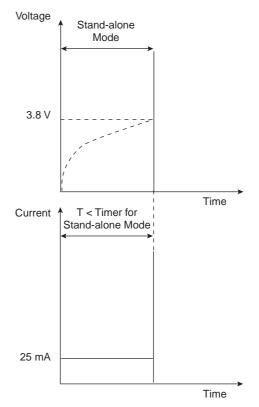

The digital core can also put the AT73C203 via USB\_SCR register into a mode where the digital core is off and battery1 is charged (25 mA) through USB up to 4.1V. In this mode (see Figure 10 on page 19) and when battery1 is precharged by USB (see Figure 8 on page 17), a CTN thermistor must be connected to therm1. The CTN thermistor used must be equivalent to the thermistor 103JT-025 from SEMITEC<sup>®</sup>.

- Temperature to allow precharging through USB: 0°C to 60°C.

- Safety timer for the USB stand alone mode: 1 hour

- Safety timer for the USB Sleep mode: 24 hours

Figure 7. Startup State Machine (1 of 3)

Figure 8. Startup State Machine (2 of 3)

Figure 9. Startup State Machine (3 of 3)

Figure 10. USB Sleep State Machine

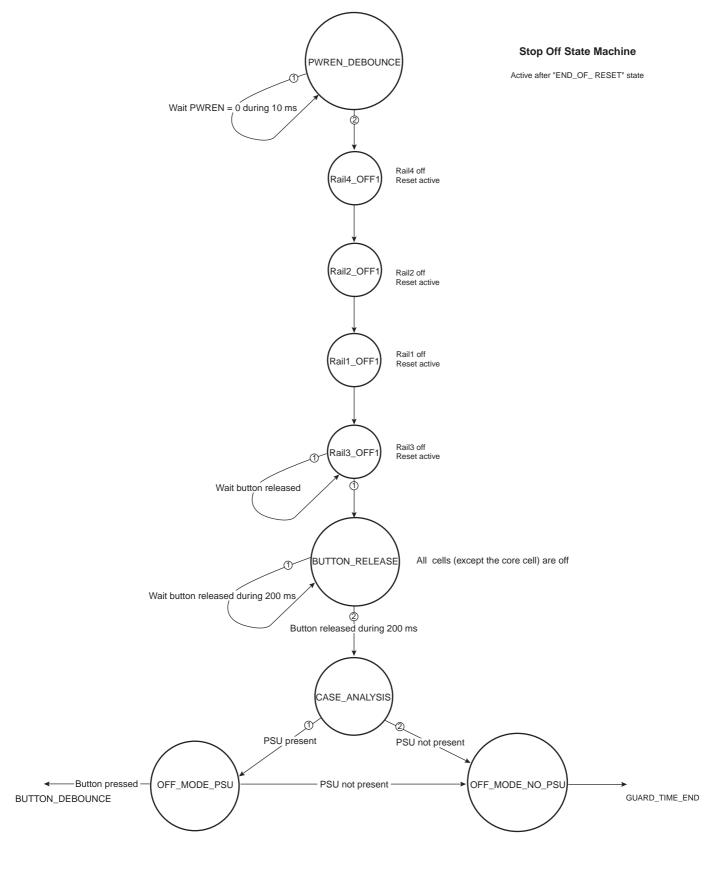

Figure 11. Stop Off State Machine

#### **Reset Generation**

A reset is generated via the internal state machine as described in Figure 7 on page 16, Figure 8 on page 17, Figure 9 on page 18 and Figure 11 on page 20. The timer for the internal reset generator is 150 ms (typical).

The application processor can set the AT73C203 to off mode via the POWER\_EN pin (Figure 11 on page 20). This "internal" reset is active at low level.

Another way to generate a reset is to program it through the monitoring function. The "monitoring" reset is active at low level.

An logical AND of the "internal" reset and the "monitoring" reset drives the reset of the external microprocessor. It is connected to the NPROC\_RESET pin and directly drives the external microprocessor.

Additional pins are used to generate separated resets for the baseband chips (see Figure 12 below).

NSHUTDOWN forces the AT73C203 internal digital block to the reset state. This turns all the supplies off and then restarts the internal state machine.

Power-on reset resets the internal state machine. nPROC\_RESET resets all other digital parts, with the exception of the USIM interface which is reset via the nBOARD\_RES pin.

Figure 12. Reset Generation Architecture

### AT73C203 User Interface

Table 4. AT73C203 User Interface

| Address     | Register        | Name                                         | Access     | Reset State |

|-------------|-----------------|----------------------------------------------|------------|-------------|

|             |                 | General-purpose Registers                    |            |             |

| 0x48        | GP_IDENT        | Chip Identification                          | Read-only  | 0xA0        |

| 0x4B        | GP_GPIO_READ    | GPIO status                                  | Read-only  | -           |

| 0x4A        | GP_GPIO_WRITE   | GPIO control                                 | Read/Write | 0x00        |

| 0x49        | DC_TRIM         | Digital rails trimming                       | Read/Write | 0x00        |

| 0x4C        | PWS_CR          | Power switch control                         | Read/Write | 0x00        |

| 0x4D        | PWS_SR          | Power switch status                          | Read-only  | -           |

| 0x4F        | USB_FST         | USB flag status                              | Read-only  | -           |

| 0x4E        | USB_FCR         | USB flag control                             | Write-only | -           |

|             |                 | USIM Interface Registers                     |            |             |

| 0x32        | SIM_CSR         | USIM channel status                          | Read-only  | -           |

| 0x34        | SIM_BSR         | USIM buffer status                           | Read-only  | 0x00        |

| 0x36        | SIM_MSR         | USIM miscellaneous status                    | Read-only  | -           |

| 0x37        | SIM_IMR1        | USIM interrupt mask 1                        | Read/Write | 0x00        |

| 0x39        | SIM_IMR2        | USIM interrupt mask 2                        | Read/Write | 0x00        |

| 0x35        | SIM_MR          | M_MR USIM mode                               |            | 0x80        |

| 0x33        | SIM_CR          | USIM control                                 | Write-only | -           |

| 0x3F        | SIM_AR          | USIM activation                              | Read/Write | 0x00        |

| 0x38        | SIM_RHR         | USIM receiver holding                        | Read-only  | -           |

| 0x31        | SIM_THR         | USIM transmitter holding                     | Write-only | -           |

| 0x3A        | SIM_BDR         | USIM baud divisor                            | Read/Write | 0x0C        |

| 0x3E        | SIM_CDR         | USIM clock divisor                           | Read/Write | 0x00        |

| 0x3B - 0x3C | SIM_RTOR        | USIM receiver time-out                       | Read/Write | 0x00        |

| 0x3D        | SIM_TTGR        | USIM transmitter time guard                  | Read/Write | 0x00        |

| 0x30        | SIM_NER         | USIM number of errors                        | Read-only  | 0x00        |

|             |                 | Voltage and Temperature Monitoring Registers |            |             |

| 0x29        | MON_CR          | Monitoring Control                           | Read/Write | 0x00        |

| 0x00        | MON_VBAT1_MEAS  | Monitoring VBAT1 measure                     | Read-only  | 0x00        |

| 0x01        | MON_VBAT2_MEAS  | Monitoring VBAT2 measure                     | Read-only  | 0x00        |

| 0x02        | MON_USB_MEAS    | Monitoring USB measure                       | Read-only  | 0x00        |

| 0x03        | MON_VDDPSU_MEAS | Monitoring VDDPSU measure                    | Read-only  | 0x00        |

| 0x04        | MON_VOUT1_MEAS  | Monitoring VOUT1 measure                     | Read-only  | 0x00        |

| 0x05        | MON_VOUT2_MEAS  | Monitoring VOUT2 measure                     | Read-only  | 0x00        |

| 0x06        | MON_VOUT3_MEAS  | Monitoring VOUT3 measure                     | Read-only  | 0x00        |

Table 4. AT73C203 User Interface (Continued)

| Address | Register                              | Name                                    | Access     | Reset State |

|---------|---------------------------------------|-----------------------------------------|------------|-------------|

| 0x07    | MON_VOUT4_MEAS                        | Monitoring VOUT4 measure                | Read-only  | 0x00        |

| 0x08    | MON_VTE1_MEAS                         | Monitoring VTE1 measure                 | Read-only  | 0x00        |

| 0x09    | MON_VTE2_MEAS Monitoring VTE2 measure |                                         | Read-only  | 0x00        |

| 0x0A    | MON_VTS_MEAS                          | Monitoring VTS measure                  | Read-only  | 0x00        |

| 0x16    | MON_VBAT1_UNDL                        | Monitoring VBAT1 under limit            | Read/Write | 0x00        |

| 0x0B    | MON_VBAT1_OVL                         | Monitoring VBAT1 over limit             | Read/Write | 0x00        |

| 0x17    | MON_VBAT2_UNDL                        | Monitoring VBAT2 under limit            | Read/Write | 0x00        |

| 0x0C    | MON_VBAT2_OVL                         | Monitoring VBAT2 over limit             | Read/Write | 0x00        |

| 0x18    | MON_USB_ UNDL                         | Monitoring USB under limit              | Read/Write | 0x00        |

| 0x0D    | MON_USB_OVL                           | Monitoring USB over limit               | Read/Write | 0x00        |

| 0x19    | MON_VDDPSU_ UNDL                      | Monitoring VDDPSU under limit           | Read/Write | 0x00        |

| 0x0E    | MON_VDDPSU_OVL                        | Monitoring VDDPSU over limit            | Read/Write | 0x00        |

| 0x1A    | MON_VOUT1_UNDL                        | Monitoring VOUT1 under limit            | Read/Write | 0x00        |

| 0x0F    | MON_VOUT1_OVL                         | Monitoring VOUT1 over limit             | Read/Write | 0x00        |

| 0x1B    | MON_VOUT2_UNDL                        | Monitoring VOUT2 under limit            | Read/Write | 0x00        |

| 0x10    | MON_VOUT2_OVL                         | Monitoring VOUT2 over limit             | Read/Write | 0x00        |

| 0x1C    | MON_VOUT3_UNDL                        | Monitoring VOUT3 under limit            | Read/Write | 0x00        |

| 0x11    | MON_VOUT3_OVL                         | Monitoring VOUT3 over limit             | Read/Write | 0x00        |

| 0x1D    | MON_VOUT4_UNDL                        | Monitoring VOUT4 under limit            | Read/Write | 0x00        |

| 0x12    | MON_VOUT4_OVL                         | N_VOUT4_OVL Monitoring VOUT4 over limit |            | 0x00        |

| 0x1E    | MON_VTE1_UNDL                         | Monitoring VTE1 under limit             | Read/Write | 0x00        |

| 0x13    | MON_VTE1_OVL                          | Monitoring VTE1 over limit              | Read/Write | 0x00        |

| 0x1F    | MON_VTE2_UNDL                         | Monitoring VTE2 under limit             | Read/Write | 0x00        |

| 0x14    | MON_VTE2_OVL                          | Monitoring VTE2 over limit              | Read/Write | 0x00        |

| 0x20    | MON_VTS_UNDL                          | Monitoring VTS under limit              | Read/Write | 0x00        |

| 0x15    | MON_VTS_OVL                           | Monitoring VTS over limit               | Read/Write | 0x00        |

| 0x21    | MON_MR1                               | Monitoring Interrupt/reset mask 1       | Read/Write | 0x00        |

| 0x22    | MON_MR2                               | Monitoring Interrupt/reset mask 2       | Read/Write | 0x00        |

| 0x23    | MON_IR1                               | Monitoring Interrupt/reset selection 1  | Read/Write | 0x00        |

| 0x24    | MON_IR2                               | Monitoring Interrupt/reset selection 2  | Read/Write | 0x00        |

| 0x25    | MON_SR1                               | Monitoring Status 1                     | Read-only  | 0x00        |

| 0x26    | MON_SR2                               | Monitoring Status 2                     | Read-only  | 0x00        |

| 0x27    | MON_VTE1_CURR                         | Monitoring current DAC thermistor 1     | Read/Write | 0x00        |

| 0x28    | MON_VTE2_CURR                         | Monitoring current DAC thermistor 2     | Read/Write | 0x00        |

|         |                                       | Charge Control Registers                |            |             |

| 0x47    | CHA_MR                                | Charge mode                             | Write-only | 0x00        |

Table 4. AT73C203 User Interface (Continued)

| Address | Register    | Name                         | Access     | Reset State |

|---------|-------------|------------------------------|------------|-------------|

| 0x41    | CHA_SR      | Charger status               | Read-only  | 0x00        |

| 0x40    | CHA_CR      | Charge control               | Write-only | 0x00        |

| 0x42    | CHA_STR_CR  | Charger safety timer control | Write-only | 0x00        |

| 0x43    | CHA_STR_SR  | Charger safety timer status  | Read-only  | 0x00        |

| 0x44    | CHA_TMINON  | Charger minimum on time      | Read/Write | 0x00        |

| 0x45    | CHA_TMINOFF | Charger minimum off time     | Read/Write | 0x00        |

| 0x46    | CHA_TR      | Charger trimming             | Read/Write | 0x00        |

### **General-purpose Registers**

### **Chip Identification Register**

Name: GP\_IDENT Access: Read-only

| 7 | 6   | 5      | 4 | 3 | 2     | 1      | 0 |

|---|-----|--------|---|---|-------|--------|---|

|   | ATM | FI II) |   |   | VERSI | ION_ID |   |

### • VERSION\_ID: Version Identification

These four bits correspond to device version.

For the first version,  $VERSION_ID = 0x0$ .

### • ATMEL\_ID: ATMEL Identification

These four bits give the company identification.

$ATMEL_ID = 0xA$

Note that GP\_IDENT can only be changed by metal mask.

For 56H05A and 56H05B,  $GP_IDENT = 0xA0$ .

For 56H05C,  $GP_IDENT = 0xA2$ .

### **GPIO Status Register**

Name: GP\_GPIO\_READ

Access: Read-only

| 7 | 6 | 5 | 4 | 3         | 2         | 1         | 0         |

|---|---|---|---|-----------|-----------|-----------|-----------|

| - | - | - | - | GPIO_RD_3 | GPIO_RD_2 | GPIO_RD_1 | GPIO_RD_0 |

#### • GPIO\_RD\_0: Value of ID\_BITS0 pin

0: ID BITS0 = 0

1: ID\_BITS0 = 1

• GPIO\_RD\_1: Value of ID\_BITS1 pin

0: ID\_BITS1 = 0

1: ID BITS1 = 1

• GPIO\_RD\_2: Value of ID\_BITS2 pin

0: ID\_BITS2 = 0

1: ID\_BITS2 = 1

• GPIO\_RD\_3: Value of ID\_BITS3 pin

$0: ID_BITS3 = 0$

1: ID\_BITS3 = 1

### **GPIO Control Register**

Name: GP\_GPIO\_WRITE

Access: Read/Write

7 6 5 4 3 2 1 0 | GPIO\_DO\_3 | GPIO\_DO\_2 | GPIO\_DO\_1 | GPIO\_DO\_0 | GPIO\_OE\_3 | GPIO\_OE\_2 | GPIO\_OE\_1 | GPIO\_OE\_0

• GPIO\_OE\_0: Output enable for ID\_BITS0 pin

0: ID\_BITS0 pin configures as input

1: ID\_BITS0 pin configures as output

• GPIO\_OE\_1: Output enable for ID\_BITS1 pin

0: ID\_BITS1 pin configures as input

1: ID\_BITS1 pin configures as output

• GPIO OE 2: Output enable for ID BITS2 pin

0: ID\_BITS2 pin configures as input

1: ID\_BITS2 pin configures as output

• GPIO\_OE\_3: Output enable for ID\_BITS3 pin

0: ID\_BITS3 pin configures as input

1: ID\_BITS3 pin configures as output

• GPIO\_DO\_0: Output data for ID\_BITS0 pin

0: ID\_BITS0 pin sets to 0 (if GPIO\_OE\_0 = 1)

1: ID BITS0 pin sets to 1 (if GPIO OE 0 = 1)

• GPIO\_DO\_1: Output data for ID\_BITS1 pin

0: ID\_BITS1 pin sets to 0 (if GPIO\_OE\_1 = 1)

1: ID\_BITS1 pin sets to 1 (if GPIO\_OE\_1 = 1)

• GPIO\_DO\_2: Output data for ID\_BITS2 pin

0: ID\_BITS2 pin sets to 0 (if GPIO\_OE\_2 = 1)

1: ID\_BITS2 pin sets to 1 (if GPIO\_OE\_2 = 1)

• GPIO\_DO\_3: Output data for ID\_BITS3 pin

0: ID\_BITS3 pin sets to 0 (if GPIO\_OE\_3 = 1)

1: ID\_BITS3 pin sets to 1 (if GPIO\_OE\_3 = 1)

### **Digital Rail Trimming Register**

Name: DC \_TRIM Access: Read/Write

|   | 7         | 6 | 5         | 4 | 3         | 2 | 1         | 0 |

|---|-----------|---|-----------|---|-----------|---|-----------|---|

| ĺ | DC_TRIM_4 |   | DC_TRIM_3 |   | DC_TRIM_2 |   | DC_TRIM_1 |   |

### • DC\_TRIM\_1: Trimming for rail 1 output voltage

If SELDC175 = 0:

| DC_TRIM_1 |   |                                              |

|-----------|---|----------------------------------------------|

| 0 0       |   | Rail 1 output voltage = 1.2V (default value) |

| 0         | 1 | Rail 1 output voltage = 1.3V                 |

| 1         | 0 | Rail 1 output voltage = 1.1V                 |

| 1         | 1 | Rail 1 output voltage = 1.5V                 |

### If SELDC175 = 1:

| DC_TRIM_1 |   |                                               |

|-----------|---|-----------------------------------------------|

| 0 0       |   | Rail 1 output voltage = 1.75V (default value) |

| 0         | 1 | Rail 1 output voltage = 1.80V                 |

| 1         | 0 | Rail 1 output voltage = 1.70V                 |

| 1         | 1 | Rail 1 output voltage = 1.65V                 |

### • DC\_TRIM\_2: Trimming for rail 2 output voltage

If SELDC25 = 0:

| DC_TRIM_2 |   |                                               |

|-----------|---|-----------------------------------------------|

| 0 0       |   | Rail 2 output voltage = 1.80V (default value) |

| 0         | 1 | Rail 2 output voltage = 1.85V                 |

| 1         | 0 | Rail 2 output voltage = 1.75V                 |

| 1         | 1 | Rail 2 output voltage = 1.70V                 |

### If SELDC25 = 1:

| DC_T | RIM_2 |                                               |

|------|-------|-----------------------------------------------|

| 0 0  |       | Rail 2 output voltage = 2.50V (default value) |

| 0    | 1     | Rail 2 output voltage = 2.60V                 |

| 1    | 0     | Rail 2 output voltage = 2.40V                 |

| 1    | 1     | Rail 2 output voltage = 2.30V                 |

### • DC\_TRIM\_3: Trimming for rail 3 output voltage

| DC_TRIM_3 |   |                                              |

|-----------|---|----------------------------------------------|

| 0 0       |   | Rail 3 output voltage = 3.3V (default value) |

| 0         | 1 | Rail 3 output voltage = 3.1V                 |

| 1         | 0 | Rail 3 output voltage = 3.2V                 |

| 1         | 1 | Rail 3 output voltage = 3.4V                 |

### • DC\_TRIM\_4: Trimming for rail 4 output voltage

| DC_TRIM_4 |   |                                              |

|-----------|---|----------------------------------------------|

| 0 0       |   | Rail 4 output voltage = 0.9V (default value) |

| 0         | 1 | Rail 4 output voltage = 1.20V                |

| 1         | 0 | Rail 4 output voltage = 0.87V                |

| 1         | 1 | Rail 4 output voltage = 1.10V                |

### **Power Switch Control Register**

Name: PWS \_CR (0x4C)

Access: Read/Write

| _ | 7 | 6 | 5 | 4 | 3          | 2          | 1 0       |

|---|---|---|---|---|------------|------------|-----------|

|   | - | - | - | - | PWS_ENBAT2 | PWS_ENBAT1 | PWS_FORCE |

With PWS\_FORCE, the microprocessor can force selection of an input source. This may be used to test the AT73C203 or by the microprocessor to force use of one of the batteries.

PWS\_FORCE: Force an input source to be selected

| PWS_FORCE |   | Input Selected                                 |

|-----------|---|------------------------------------------------|

| 0 0       |   | Power switch runs automatically (default mode) |

| 0         | 1 | PSU                                            |

| 1         | 0 | Battery 2                                      |

| 1         | 1 | Battery 1                                      |

• PWS\_ENBAT1: Reset FLATBAT1 (refer to "Power Switch Status Register" on page 30)

0: No action (default value)

1: FLATBAT1 is reset to 0

• PWS\_ENBAT2: Reset FLATBAT2 (refer to "Power Switch Status Register" on page 30)

0: No action (default value)

1: FLATBAT2 is reset to 0

### **Power Switch Status Register**

Name: PWS \_SR Access: Read-only

| 7 | 6 | 5 | 4 | 3        | 2        | 1     | 0     |

|---|---|---|---|----------|----------|-------|-------|

| - | - | - | - | FLATBAT2 | FLATBAT1 | PWS_S | TATUS |

#### PWS\_STATUS: Status of the power switch

| PWS_S | STATUS | Input Selected                        |  |  |  |

|-------|--------|---------------------------------------|--|--|--|

| 0     | 0      | Power switch off or no input selected |  |  |  |

| 0     | 1      | PSU                                   |  |  |  |

| 1     | 0      | Battery 2                             |  |  |  |

| 1     | 1      | Battery 1                             |  |  |  |

With PWS\_STATUS (bits accessible via SPI), the microprocessor can read which supply is currently selected by the AT73C203.

#### • FLATBAT1: BAT1 flat threshold indication

0: Default and reset value

1: Bat1 voltage has reached flat threshold during selection (latched value). Bat1 cannot be used as input source (until reset by the microprocessor)

#### • FLATBAT2: BAT2 flat threshold indication

0: Default and reset value

1: Bat2 voltage has reached flat threshold during selection (latched value). Bat2 cannot be used as input source (until reset by the microprocessor)

### **USB Flag Status**

Name: USB\_FST Access: Read-only

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0       |

|---|---|---|---|---|---|---|---------|

| - | - | - | - | - | - | • | USB_FST |

### USB\_FST: USB flag status

0: USB has not been used to precharge (stand alone mode)

1: USB has been used to precharge (stand alone mode)

Refer to "State Machine Description" on page 15.

### **USB Flag Control**

Name: USB\_FCR (0x4E)

Access: Write-only

| 7 | 6 | 5 | 4 | 3 | 2 | 1       | 0       |

|---|---|---|---|---|---|---------|---------|

| - | - | - | - | - | - | USB_SCR | USB_FCR |

• USB\_FCR: USB flag control

0: No action

1: Resets USB\_FST to 0

• USB\_SCR: USB sleep control

0: No action

1: Enter in "USB SLEEP STATE MACHINE"

Refer to "State Machine Description" on page 15.

### **USIM Interface Registers**

### **Channel Status Register**

Name: SIM\_CSR (0x32)

Access: Read-only

| 7 | 6      | 5       | 4     | 3    | 2    | 1      | 0     |

|---|--------|---------|-------|------|------|--------|-------|

| - | TXNACK | TXEMPTY | TXRDY | PARE | OVRE | RXFULL | RXRDY |

### RXRDY: Receiver Ready

0: The receiver FIFO is empty.

1: At least one complete character has been received.

RXFULL: Receiver Full

0: The receiver FIFO is not full.

1: The receiver FIFO is full.

OVRE: Overrun Error

0: No byte has been transferred from the Receive Shift Register to the receiver FIFO when RXFULL was asserted since the last Reset Status Bits command.

1: At least one byte has been transferred from the Receive Shift Register to the receiver FIFO when RXFULL was asserted since the last Reset Status Bits command.

• PARE: Parity Error

0: No parity bit has been detected as false since the last Reset Status Bits command.

1: At least one parity bit has been detected as false since the last Reset Status Bits command.

TXRDY: Transmitter Ready

0: The transmitter FIFO is full.

1: The transmitter FIFO is not full.

• TXEMPTY: Transmitter Empty

0: There are characters in either the transmitter FIFO or the Transmit Shift Register.

1: There are no characters in either the transmitter FIFO or the Transmit Shift Register. TXEMPTY is 1 after Parity, Stop Bit and Time-guard have been transmitted. TXEMPTY is 1 after stop bit has been sent, or after Time-guard has been sent if SIM\_TTGR is not 0.

#### TXNACK: Non Acknowledge

0: A Non Acknowledge has not been detected during a transmission

1: A Non Acknowledge has been detected during a transmission.

### **Buffer Status Register**

Name: SIM\_BSR Access: Read-only

| 7 | 6   | 5   | 4 | 3 | 2   | 1  | 0 |

|---|-----|-----|---|---|-----|----|---|

|   | TXF | PTR |   |   | RXP | TR |   |

### • RXPTR: Receiver buffer pointer

Indicates the number of characters waiting to be read in the receiver FIFO. If RXPTR = 15 then if RXFULL is set, there are 16 characters in the FIFO, otherwise there are 15.

#### • TXPTR: Transmitter buffer pointer

Indicates the number of characters waiting to be transmitted from the transmitter FIFO. If TXPTR = 15 then if TXRDY is set, there are 15 characters in the FIFO, otherwise 16.

### Miscellaneous Status Register

Name: SIM\_MSR Access: Read-only

| 7 | 6 | 5 | 4 | 3 | 2    | 1         | 0       |

|---|---|---|---|---|------|-----------|---------|

| - | - | - | - | - | PRES | ITERATION | TIMEOUT |

#### • TIMEOUT: Receiver Time-out

0: There has not been a time-out since the last Start Time-out command or the Time-out Register is 0.

1: There has been a time-out since the last Start Time-out command.

#### • ITERATION: Max number of Repetitions Reached

Note: This bit will operate only in Protocol T: 0.

0: Max number of repetitions has not been reached.

1: Max number of repetitions has been reached.

A repetition consists of transmitted characters or successive NACK.

### • PRES: SIM card presence

0: The SIM card is not present.

1: The SIM card is present.

### **Interrupt Mask Register 1**

Name: SIM\_IMR1 (0x37)

Access: Read/Write

|   | 7 | 6      | 5       | 4     | 3    | 2    | 1      | 0     |

|---|---|--------|---------|-------|------|------|--------|-------|

| ſ | - | TXNACK | TXEMPTY | TXRDY | PARE | OVRE | RXFULL | RXRDY |

#### • RXRDY: Enable RXRDY Interrupt

0: Disables RXRDY Interrupt.

1: Enables RXRDY Interrupt.

• RXFULL: Enable RXFULL Interrupt

0: Disables RXFULL Interrupt.

1: Enables RXFULL Interrupt.

• OVRE: Enable Overrun Error Interrupt

0: Disables Overrun Error Interrupt.

1: Enables Overrun Error Interrupt.

• PARE: Enable Parity Error Interrupt

0: Disables Parity Error Interrupt.

1: Enables Parity Error Interrupt.

• TXRDY: Enable TXRDY Interrupt

0: Disables TXRDY Interrupt.

1: Enables TXRDY Interrupt.

• TXEMPTY: Enable TXEMPTY Interrupt

0: Disables TXEMPTY Interrupt.

1: Enables TXEMPTY Interrupt.

• TXNACK: Enable Non Acknowledge Interrupt

0: Disables Non Acknowledge Interrupt.

1: Enables Non Acknowledge Interrupt

### **Interrupt Mask Register 2**

Name: SIM\_IMR2 (0x39)

Access: Read/Write

| 7 | 6 | 5 | 4      | 3      | 2    | 1         | 0       |

|---|---|---|--------|--------|------|-----------|---------|

| - | - | - | TXHALF | RXHALF | PRES | ITERATION | TIMEOUT |

#### • TIMEOUT: Enable Time-out Interrupt

0: Disables reception time-out interrupt.

1: Enables reception time-out interrupt.

### • ITERATION: Enable Iteration Interrupt

Note: This will operate only in Protocol T: 0.

0: Disables ITERATION interrupt.

1: Enables ITERATION interrupt.

• PRES: Enable Presence Interrupt

0: Disables card presence interrupt.

1: Enables card presence interrupt.

• RXHALF: Enable Reception Buffer Half Full Interrupt

0: Disables reception buffer half full interrupt.

1: Enables reception buffer half full interrupt.

• TXHALF: Enable Transmission Buffer Half Full Interrupt

0: Disables transmission buffer half full interrupt.

1: Enables transmission buffer half full interrupt.

### **Mode Register**

Name: SIM\_MR (0x35)

Access: Read/Write

| 7        | 6         | 5 | 4             | 3 | _ 2     | 1       | 0     |

|----------|-----------|---|---------------|---|---------|---------|-------|

| POLARITY | BIT_ORDER |   | MAX_ITERATION | ١ | DSRNACK | IRXNACK | TMODE |

• TMODE: Protocol Mode

0: Protocol T: 0 1: Protocol T: 1

IRXNACK: Inhibit Reception Non Acknowledge

0: The NACK is generated

1: The NACK is not generated

Note: This bit will be used only in protocol T: 0 receiver.

• DSRXNACK: Disable Successive Reception NACK

0: NACK is sent on the IO line as soon as a parity error occurs in the received character (unless IRXNACK is set).

1: Successive parity errors are counted up to the value specified in the MAX\_ITERATION field. These parity errors generate a NACK on the IO line. As soon as this value is reached, no additional NACK is sent on the IO line. The flag ITERATION is asserted.

• MAX\_ITERATION: Number of Repetitions

0 - 7 This will operate in Protocol T: 0 only

• BIT\_ORDER

0: LSB first (direct convention)

1: MSB first (inverse convention)

• POLARITY: Polarity

0: Odd parity (odd number of 1 on character + parity bit) (inverse convention)

1: Even parity (even number of 1 on character + parity bit) (direct convention)

## **Control Register**

Name: SIM\_CR

Access: Write-only

| 7     | 6     | 5       | 4    | 3       | _ 2   | 1    | 0      |

|-------|-------|---------|------|---------|-------|------|--------|

| RSTTX | RSTRX | RSTPRES | RETT | RSTNACK | RSTIT | STTO | RSTSTA |

#### · RSTSTA: Reset Status Bits

0: No effect.

1: Resets the status bits PARE AND OVRE in the SIM\_CSR.

• STTO: Start Time-out

0: No effect

1: Start. waiting for a character before clocking the time-out counter.

• RSTIT: Reset Iterations

0: No effect.

1: Resets the status bit Iteration.

• RSTNACK: Reset Non Acknowledge

0: No effect

1: Resets the status bit TXNACK.

• RETTO: Rearm Time-out

0: No effect

1: Restart. Time-out

• RSTPRES: Reset Presence Interrupt

0: No effect

1: Reset. SIM card presence interrupt.

• RSTRX: Reset Receiver

0: No effect

1: The receiver logic is reset and the receiver FIFO is emptied.

• RSTTX: Reset Transmitter

0: No effect

1: The transmitter logic is reset and the transmitter FIFO is emptied.

## **Activation Register**

Name: SIM\_AR (0x3F)

Access: Read/Write

| 7 | 6 | 5 | 4  | 3   | 2      | 1     | 0      |

|---|---|---|----|-----|--------|-------|--------|

| - | - | - | VS | SEL | ACTIVE | CLKEN | SRESET |

• SRESET: SIM Reset Pin

0: SIM Reset pin: 0.1: SIM Reset pin: 1.

• CLKEN: SIM Clock Enable

0: SIM clock disabled (grounded).

1: SIM clock enabled.

• ACTIVE: IO Line Activation

0: IO line at ground.

1: IO line enabled.

• VSEL: SIM Voltage Selection

00: Disabled01: Disabled

10: Regulator output equals 1.8V

11: Regulator output equals 2.8V

## **Receiver Holding Register**

Name: SIM\_RHR (0x38)

Access: Read-only

7 6 5 4 3 2 1 0 RHR

First character received if RXRDY is set.

## **Transmitter Holding Register**

Name: SIM\_THR (0x31)

Access: Write-only

7 6 5 4 3 2 1 0 THR

Next character to be transmitted. If transmitter FIFO is full, the last character is overwritten.

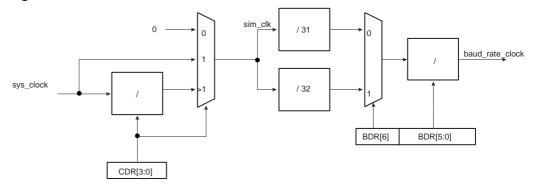

## **Baud Divisor Register**

Name: SIM\_BDR (0x3A)

Access: Read/Write

7 6 5 4 3 2 1 0 - BDR

The baud rate =  $f/(div1 \times div2)$  where f is the SIM clock frequency.

div1 is coded on BDR[6].

| BDR[6] | 0  | 1  |

|--------|----|----|

| div1   | 31 | 32 |

div2 is coded on BDR[5:0].

| BDR[5:0] | 0  | 1 - 63   |

|----------|----|----------|

| div2     | 64 | BDR[5:0] |

BDR reset value = b0001100. Initial baud rate = 372.

## **Clock Divisor Register**

Name: SIM\_CDR (0x3E)

Access: Read/Write

| 7 | 6 | 5 | 4 | 3 | 2  | 1 | 0 |

|---|---|---|---|---|----|---|---|

| - | - | - | - |   | CD | R |   |

The SIM clock is generated through a programmable divider. The division factor can be modified in this register.

| CDR[3:0]              | 0000     | 0001 to 1111 |

|-----------------------|----------|--------------|

| Clock division factor | No clock | CDR[3:0]     |

CDR reset value = 0000.

## **Receiver Time-out Register**

Name: SIM\_RTOR (0x3B and 0x3C)

Access: Read/Write

| 15 | 14   | 13 | 12 | 11   | 10 | 9 | 8 |  |  |

|----|------|----|----|------|----|---|---|--|--|

|    | RTOR |    |    |      |    |   |   |  |  |

| 7  | 6    | 5  | 4  | 3    | 2  | 1 | 0 |  |  |

|    |      |    | Г  | RTOR |    |   |   |  |  |

0: Disables the RX Time-out function.

1 - 65535: The Time-out counter is loaded with RTOR (16 bits) when the Start Time-out command is given or when each new data character is received (after reception has started).

## **Transmitter Time Guard Register**

Name: SIM\_TTGR (0x3D)

Access: Read/Write

Time-guard duration = TG x Bit Period

0: Disables the TX Time-guard function.

1 - 255: IO line is inactive high after the transmission of each character for the time-guard duration.

## **Number of Errors Register**

Name: SIM\_NER (0x30)

Access: Read-only

| 7 | 6 | 5 | 4 | 3   | 2 | 1 | 0 |

|---|---|---|---|-----|---|---|---|

|   |   |   |   | NER |   |   |   |

NB\_ERRORS: Error number during transfers

This 8-bit register presents the total amount of errors that occurred during a transfer. It is a read-only register and it is reset by reading the register.

## **Voltage and Temperature Monitoring Registers**

## **Control Register**

Name: MON\_CR (0x29)

Access: Read/Write

| 7 | 6 | 5 | 4 | 3 | 2 | 1        | 0      |

|---|---|---|---|---|---|----------|--------|

| - | - | - | - | - | - | IT_RESET | MON_ON |

• MON\_ON: Enable bit of the monitoring function

0: Monitoring function disabled

1: Monitoring function enabled

• IT\_RESET: Reset of the status register

0: No action

1: Reset the status registers MON\_SR1 and MON\_SR2

**VBAT1 Measure Register**

Name: MON\_VBAT1\_MEAS (0x00)

Access: Read-only

7 6 5 4 3 2 1 0 MON\_VBAT1\_MEAS

**VBAT2 Measure Register**

Name: MON\_VBAT2\_MEAS (0x01)

Access: Read-only

7 6 5 4 3 2 1 0 MON\_VBAT2\_MEAS

**USB Measure Register**

Name: MON\_USB\_MEAS (0x02)

Access: Read-only

7 6 5 4 3 2 1 0 MON\_USB\_MEAS

**VDDPSU Measure Register**

Name: MON\_VDDPSU\_MEAS (0x03)

Access: Read-only

7 6 5 4 3 2 1 0 MON\_VDDPSU\_MEAS

**VOUT1 Measure Register**

Name: MON\_VOUT1\_MEAS (0x04)

Access: Read-only

7 6 5 4 3 2 1 0 MON\_VOUT1\_MEAS

**VOUT2 Measure Register**

Name: MON\_VOUT2\_MEAS (0x05)

Access: Read-only

7 6 5 4 3 2 1 0 MON\_VOUT2\_MEAS

**VOUT3 Measure Register**

Name: MON\_VOUT3\_MEAS (0x06)

Access: Read-only

7 6 5 4 3 2 1 0 MON\_VOUT3\_MEAS

**VOUT4 Measure Register**

Name: MON\_VOUT4\_MEAS (0x07)

Access: Read-only

7 6 5 4 3 2 1 0 MON\_VOUT4\_MEAS **VTE1 Measure Register**

Name: MON\_VTE1\_MEAS (0x08)

Access: Read-only

7 6 5 4 3 2 1 0 MON\_VTE1\_MEAS

**VTE2 Measure Register**

Name: MON\_VTE2\_MEAS (0x09)

Access: Read-only

7 6 5 4 3 2 1 0 MON\_VTE2\_MEAS

**VTS Measure Register**

Name: MON\_VTS\_MEAS (0x0A)

Access: Read-only

7 6 5 4 3 2 1 0 MON\_VTS\_MEAS

**VBAT1 Under Limit Register**

Name: MON\_VBAT1\_UNDL (0x16)

Access: Read/write

7 6 5 4 3 2 1 0 MON\_VBAT1\_UNDL

**VBAT1 Over Limit Register**

Name: MON\_VBAT1\_OVL (0x1B)

Access: Read/write

7 6 5 4 3 2 1 0 MON VBAT1 OVL

**VBAT2 Under Limit Register**

Name: MON\_VBAT2\_UNDL (0x17)

Access: Read/write

7 6 5 4 3 2 1 0 MON\_VBAT2\_UNDL

**VBAT2 Over Limit Register**

Name: MON\_VBAT2\_OVL (0x0C)

Access: Read/write

7 6 5 4 3 2 1 0 MON\_VBAT2\_OVL **USB Under Limit Register**

Name: MON\_USB\_UNDL (0x18)

Access: Read/write

7 6 5 4 3 2 1 0 MON\_USB\_UNDL

**USB Over Limit Register**

Name: MON\_USB\_OVL (0x1D)

Access: Read/write

7 6 5 4 3 2 1 0 MON USB OVL

**VDDPSU Under Limit Register**

Name: MON\_VDDPSU\_UNDL (0x19)

Access: Read/write

7 6 5 4 3 2 1 0 MON\_VDDPSU\_UNDL

**VDDPSU Over Limit Register**

Name: MON\_VDDPSU\_OVL (0x0E)

Access: Read/write

7 6 5 4 3 2 1 0 MON\_VDDPSU\_OVL

**VOUT1 Under Limit Register**

Name: MON\_VOUT1\_UNDL (0x1A)

Access: Read/write

7 6 5 4 3 2 1 0 MON\_VOUT1\_UNDL

**VOUT1 Over Limit Register**

Name: MON\_VOUT1\_OVL (0x1F)

Access: Read/write

7 6 5 4 3 2 1 0 MON VOUT1 OVL

**VOUT2 Under Limit Register**

Name: MON\_VOUT2\_UNDL (0x1B)

Access: Read/write

7 6 5 4 3 2 1 0 MON\_VOUT2\_UNDL

**VOUT2 Over Limit Register**

Name: MON\_VOUT2\_OVL (0x10)

Access: Read/write

7 6 5 4 3 2 1 0 MON\_VOUT2\_OVL

| VOUT3 | Under  | Limit | Red  | ister  |

|-------|--------|-------|------|--------|

| 10010 | Oliaci |       | 1109 | 113661 |

Name: MON\_VOUT3\_UNDL (0x1C)

Access: Read/write

7 6 5 4 3 2 1 0 MON\_VOUT3\_UNDL

## **VOUT3 Over Limit Register**

Name: MON\_VOUT3\_OVL (0x11)

Access: Read/write

7 6 5 4 3 2 1 0 MON\_VOUT3\_OVL

## **VOUT4 Under Limit Register**

Name: MON\_VOUT4\_UNDL (0x1D)

Access: Read/write

7 6 5 4 3 2 1 0 MON\_VOUT4\_UNDL

## **VOUT4 Over Limit Register**

Name: MON\_VOUT4\_OVL (0x12)

Access: Read/write

7 6 5 4 3 2 1 0 MON\_VOUT4\_OVL

**VTE1 Under Limit Register**

Name: MON\_VTE1\_UNDL (0x1E)

Access: Read/write

7 6 5 4 3 2 1 0 MON\_VTE1\_UNDL

**VTE1 Over Limit Register**

Name: MON\_VTE1\_OVL (0x13)

Access: Read/write

7 6 5 4 3 2 1 0 MON\_VTE1\_OVL

**VTE2 Under Limit Register**

Name: MON\_VTE2\_UNDL (0x1F)

Access: Read/write

7 6 5 4 3 2 1 0 MON\_VTE2\_UNDL

**VTE2 Over Limit Register**

Name: MON\_VTE2\_OVL (0x14)

Access: Read/write

7 6 5 4 3 2 1 0 MON VTE2 OVL

**VTS Under Limit Register**

Name: MON\_VTS\_UNDL (0x20

Access: Read/write

7 6 5 4 3 2 1 0 MON\_VTS\_UNDL

**VTS Over Limit Register**

Name: MON\_VTS\_OVL (0x15)

Access: Read/write

7 6 5 4 3 2 1 0 MON\_VTS\_OVL

### Interrupt/ Reset Mask Register 1

Name: MON\_MR1 (0x21)

Access: Read/Write

| 7     | 6     | 5     | 4     | 3      | _ 2 | 1     | 0     |

|-------|-------|-------|-------|--------|-----|-------|-------|

| VOUT4 | VOUT3 | VOUT2 | VOUT1 | VDDPSU | USB | VBAT2 | VBAT1 |

#### VBAT1: Enable VBAT1 Interrupt or Reset

0: Disables VBAT1 interrupt or global reset.

1: Enables VBAT1 interrupt or global reset.

#### • VBAT2: Enable VBAT2 Interrupt

0: Disables VBAT2 interrupt or global reset.

1: Enables VBAT2 interrupt or global reset.

#### • USB: Enable USB Interrupt

0: Disables USB interrupt or global reset.

1: Enables USB interrupt or global reset.

#### VDDPSU: Enable VDDPSU Interrupt

0: Disables VDDPSU interrupt or global reset.

1: Enables VDDPSU interrupt or global reset.

#### • VOUT1: Enable VOUT1 Interrupt

0: Disables VOUT1 interrupt or global reset.

1: Enables VOUT1 interrupt or global reset.

#### • VOUT2: Enable VOUT2 Interrupt

0: Disables VOUT2 interrupt or global reset.

1: Enables VOUT2 interrupt or global reset.

#### VOUT3: Enable VOUT3 Interrupt

0: Disables VOUT3 interrupt or global reset.

1: Enables VOUT3 interrupt or global reset.

#### • VOUT4: Enable VOUT4 Interrupt

0: Disables VOUT4 interrupt or global reset.

1: Enables VOUT4 interrupt or global reset.

## Interrupt/ Reset Mask Register 2

Name: MON\_MR2 (0x22)

Access: Read/Write

7 6 5 4 3 2 1 0

- VOUT4COMP VOUT3COMP VOUT2COMP VOUT1COMP VTS VTE2 VTE1

#### • VTE1: Enable VTE1 Interrupt or Reset

0: Disables VTE1 interrupt or global reset.

1: Enables VTE1 interrupt or global reset.

#### • VTE2: Enable VTE2 Interrupt

0: Disables VTE2 interrupt or global reset.

1: Enables VTE2 interrupt or global reset.

#### • VTS: Enable VTS Interrupt

0: Disables VTS interrupt or global reset.

1: Enables VTS interrupt or global reset.

### • VOUT1COMP: Enable VOUT1COMP Interrupt or Reset

0: Disables VOUT1COMP interrupt or global reset.

1: Enables VOUT1COMP interrupt or global reset.

• VOUT2COMP: Enable VOUT2COMP Interrupt or Reset

0: Disables VOUT2COMP interrupt or global reset.

1: Enables VOUT2COMP interrupt or global reset.

• VOUT3COMP: Enable VOUT3COMP Interrupt or Reset

0: Disables VOUT3COMP interrupt or global reset.

1: Enables VOUT3COMP interrupt or global reset.

• VOUT4COMP: Enable VOUT4COMP Interrupt or Reset

0: Disables VOUT4COMP interrupt or global reset.

1: Enables VOUT4COMP interrupt or global reset.

## Interrupt/ Reset Selection Register 1

Name: MON\_IR1 (0x23)

Access: Read/Write

| 7     | 6     | 5     | 4     | _ 3    | 2   | 1     | 0     |

|-------|-------|-------|-------|--------|-----|-------|-------|

| VOUT4 | VOUT3 | VOUT2 | VOUT1 | VDDPSU | USB | VBAT2 | VBAT1 |

#### • VBAT1: Select for VBAT1 Interrupt or Reset

0: Interrupt selected for VBAT1

1: Global reset selected for VBAT1.

VBAT2: Select for VBAT2 Interrupt or Reset

0: Interrupt selected for VBAT2

1: Global reset selected for VBAT2.

• USB: Select for USB Interrupt or Reset

0: Interrupt selected for USB

1: Global reset selected for USB.

VDDPSU: Select for VDDPSU Interrupt or Reset

0: Interrupt selected for VDDPSU

1: Global reset selected for VDDPSU.

VOUT1: Select for VOUT1 Interrupt or Reset

0: Interrupt selected for VOUT1

1: Global reset selected for VOUT1.

• VOUT2: Select for VOUT2 Interrupt or Reset

0: Interrupt selected for VOUT2

1: Global reset selected for VOUT2.

VOUT3: Select for VOUT3 Interrupt or Reset

0: Interrupt selected for VOUT3

1: Global reset selected for VOUT3.

VOUT4: Select for VOUT4 Interrupt or Reset

0: Interrupt selected for VOUT4

1: Global reset selected for VOUT4.

## Interrupt/ Reset Selection Register 2

Name: MON\_IR2 (0x24)

Access: Read/Write

7 6 5 4 3 2 1 0

- VOUT4COMP VOUT3COMP VOUT2COMP VOUT1COMP VTS VTE2 VTE1

#### • VTE1: Select for VTE1 Interrupt or Reset

0: Interrupt selected for VTE1

1: Global reset selected for VTE1.

VTE2: Select for VTE2 Interrupt or Reset

0: Interrupt selected for VTE2

1: Global reset selected for VTE2.

• VTS: Select for VTS Interrupt or Reset

0: Interrupt selected for VTS

1: Global reset selected for VTS.

• VOUT1COMP: Select for VOUT1COMP Interrupt or Reset

0: Interrupt selected for VOUT1COMP

1: Global reset selected for VOUT1COMP.

• VOUT2COMP: Select for VOUT2COMP Interrupt or Reset

0: Interrupt selected for VOUT2COMP

1: Global reset selected for VOUT2COMP.

• VOUT3COMP: Select for VOUT3COMP Interrupt or Reset

0: Interrupt selected for VOUT3COMP

1: Global reset selected for VOUT3COMP.

• VOUT4COMP: Select for VOUT4COMP Interrupt or Reset

0: Interrupt selected for VOUT4COMP

1: Global reset selected for VOUT4COMP.

### Status Register 1

Name: MON\_SR1 (0x25)

Access: Read-only