### MS7200L/7201AL/7202AL 256 x 9, 512 x 9, 1K x 9 CMOS FIFO

#### Features

- First-In/First-Out static RAM based dual port memory

- Three densities in a x9 configuration

- Low power versions

- Includes empty, full, and half full status flags

- Direct replacement for industry standard Mostek and IDT

- Ultra high-speed 30 MHz FIFOs available with 33 ns cycle times.

- Fully expandable in both depth and width

- Simultaneous and asynchronous read and write

- Auto retransmit capability

- TTL compatible interface, single 5V ± 10% power supply

- Available in 28 pin 300 mil and 600 mil plastic DIP, 32 Pin PLCC and 330 mil SOG

# Pin Configurations 28-PIN PDIP

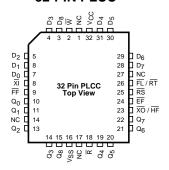

#### 32-PIN PLCC

### **Descriptions**

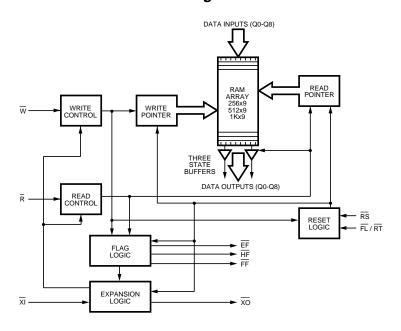

The MS7200L/7201AL/7202AL are dual-port static RAM based CMOS First-In/First-Out (FIFO) memories organized in nine-bit wide words. The devices are configured so that data is read out in the same sequential order that it was written in. Additional expansion logic is provided to allow for unlimited expansion of both word size and depth.

The dual-port RAM array is internally sequenced by independent Read and Write pointers with no external addressing needed. Read and write operations are fully asynchronous and may occur simultaneously, even with the device operating at full speed. Status flags are provided for full, empty, and half-full conditions to eliminate data underflow and overflow. The x9 architecture provides an additional bit which may be used as a parity or control bit. In addition, the devices offer a retransmit capability which resets the Read pointer and allows for retransmission from the beginning of the data.

The MS7200L/7201AL/7202AL are available in a range of frequencies from 10 to 30 MHz (33 - 100 ns cycle times). A low power version with a 500µA power down supply current is available. They are manufactured on Mosel-Vitelic's high performance 1.2µ CMOS process and operate from a single 5V power supply.

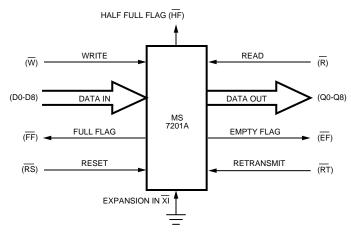

### **Block Diagram**

### MS7200L/7201AL/7202AL

### Signal Descriptions

#### INPUTS:

### Data In $(D_0 - D_8)$

These data inputs accept 9-bit data words for sequential storage in the FIFO during write operations.

### **CONTROLS:**

#### Reset (RS)

The reset input is active LOW. When asserted, the device is asynchronously reset, and both the read and write internal pointers are set to the first location in the FIFO. A Reset is required after power-up before a write operation can occur. Both Read Enable  $(\overline{\mathbb{R}})$  and Write Enable  $(\overline{\mathbb{W}})$  must be HIGH during Reset.

### Read Enable (R)

The read enable input is active LOW. As long as the Empty Flag ( $\overline{EF}$ ) is not set, the read cycle is started on the falling edge of this signal. The data is accessed on a First-In/First-Out basis, independent of any write activity, and is presented on the Data Output pins (Q0 - Q8). When  $\overline{R}$  goes HIGH the Data Output pins return to the high impedance state, and the read pointer is incremented. When the FIFO is empty or all of the data has been read, the Empty Flag will be set and further read operations are inhibited until a valid write operation has been performed.

### Write Enable (W)

The write enable input is active LOW. As long as the Full Flag ( $\overline{\text{FF}}$ ) is not set, the write cycle is started on the falling edge of this signal. The data present on the Data Input pins (D0 - D8) is stored sequentially, independent of any read activity. When  $\overline{\text{W}}$  goes HIGH the write cycle is terminated and the write pointer is incremented. When the maximum capacity of the FIFO has been reached the Full Flag will be set, and further write operations are inhibited until a valid read operation has been performed.

#### Expansion In $(\overline{XI})$

This input pin serves two purposes. When grounded, it indicates that the device is being operated in the single device mode. In Depth Expansion mode, this pin is connected to the Expansion Out Output  $(\overline{XO})$  of the previous device.

### First Load/Retransmit (FL/RT)

This is a dual-purpose input. In single device mode (when Expansion In  $(\overline{XI})$  is grounded) this pin acts as the retransmit input. A LOW pulse on this will reset the read pointer to the first memory location of the FIFO. The write pointer is unaffected. Both the read enable  $(\overline{R})$  and write enable  $(\overline{W})$  inputs must remain HIGH during the retransmit cycle.

In Depth Expansion mode this pin acts as a first load indicator. It must be grounded on the first device in the chain to indicate which device is the first to receive data.

#### **OUTPUTS:**

### Data Output (Q<sub>0</sub> - Q<sub>8</sub>)

A 9 bit data word from the FIFO is output on these pins during read operations. They are in the high impedance state whenever  $\overline{R}$  is HIGH.

### Empty Flag (EF)

This output is active LOW. When all of the data has been read from the FIFO (defined as when the Read pointer is one location behind the Write pointer) this flag will be set. The Data Output pins will be forced into the high impedance state, and all further read operations will be inhibited until a valid write operation has been performed (which will reset this flag).

### Full Flag (FF)

This output is active LOW. To prevent data overflow, when the maximum capacity of the FIFO has been reached (defined as when the Write pointer is one location behind the Read pointer) this flag will be set. All further write operations will be inhibited until a valid read operation has been performed (which will reset this flag).

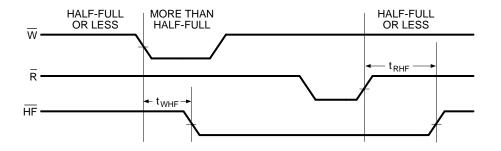

### Expansion Out/Half Full Flag (XO/HF)

This dual-purpose output is active LOW. In single device mode (when Expansion In  $(\overline{XI})$  is grounded) this flag will be set at the falling edge of the next write operation after the FIFO has reached one-half of its maximum capacity. This flag will remain set as long as the difference between the read pointer and the write pointer is greater than one-half of the maximum capacity of the FIFO.

In Depth Expansion mode, this output is connected to the Expansion In Input of the next device in the chain. The Expansion Out pin provides a pulse to the next device in the chain when the last memory location has been reached.

### MS7200L/7201AL/7202AL

### Absolute Maximum Ratings(1)

| Symbol            | Parameter                           | Condition    | Unit |

|-------------------|-------------------------------------|--------------|------|

| $V_{TERM}$        | Terminal Voltage with Repect to GND | -0.5 to +7.0 | V    |

| T <sub>BIAS</sub> | Temperature Under Bias              | -10 to +125  | ℃    |

| T <sub>STG</sub>  | Storage Temperature                 | -60 to +150  | ℃    |

| P <sub>T</sub>    | Power Dissipation                   | 1.0          | W    |

| I <sub>OUT</sub>  | DC Output Current                   | 20           | mA   |

Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

### **Operating Range**

| Range      | Ambient<br>Temperature | Vcc      |

|------------|------------------------|----------|

| Commercial | 0°C to + 70°C          | 5V ± 10% |

## **Capacitance**(1) $T_A = 25$ °C, f = 1.0MHz

| Symbol          | Parameter          | Condition     | Max. | Unit |

|-----------------|--------------------|---------------|------|------|

| C <sub>IN</sub> | Input Capacitance  | $V_{IN} = 0V$ | 4    | рF   |

| C <sub>Q</sub>  | Output Capacitance | $V_{DQ} = 0V$ | 6    | рF   |

DC Electrical Characteristics (over the commercial operating range)

| Test                 |                                                     | MS7200L/7201AL<br>7202AL<br>(-25, -35)                                                                                                                               |      | MS72<br>7<br>(- |      |      |      |      |       |

|----------------------|-----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----------------|------|------|------|------|-------|

| Parameter            | Parameter                                           | Test Conditions                                                                                                                                                      | Min. | Тур.            | Max. | Min. | Тур. | Max. | Units |

| V <sub>IL</sub>      | Input Low Voltage                                   |                                                                                                                                                                      | -    | -               | 0.8  | -    |      | 0.8  | V     |

| V <sub>IH</sub>      | Input High Voltage                                  |                                                                                                                                                                      | 2.0  | -               | -    | 2.0  | -    | -    | V     |

| I <sub>IL</sub>      | Input Leakage Current                               | V <sub>CC</sub> = Max, V <sub>IN</sub> = 0Vto V <sub>CC</sub>                                                                                                        | -1   |                 | 1    | -1   |      | 1    | μΑ    |

| I <sub>OL</sub>      | Output Leakage Current                              | $V_{CC} = Max, R = V_{IH}, V_{IN} = 0V \text{ to} V_{CC}$                                                                                                            | -10  |                 | 10   | -10  |      | 10   | μА    |

| V <sub>OL</sub>      | Output Low Voltage                                  | V <sub>CC</sub> = Min, I <sub>OL</sub> = 8mA                                                                                                                         | -    | -               | 0.4  | -    | -    | 0.4  | V     |

| $V_{OH}$             | Output High Voltage                                 | V <sub>CC</sub> = Min, I <sub>OH</sub> = -2mA                                                                                                                        | 2.4  | -               | -    | 2.4  |      | -    | V     |

| $I_{CC1}$            | Operating Power Supply Current                      | $V_{CC} = Max, I_{I/O} = 0mA, F = F_{max}$                                                                                                                           | -    | -               | 125  | -    | 50   | 80   | mA    |

| I <sub>CC2</sub>     | Average Standby Current                             | $V_{CC} = Max, \overline{R} = \overline{W} = \overline{RS} = \overline{FL} / \overline{RT} = V_{IH},$ $I_{I/O} = 0mA$                                                | -    | -               | 15   | -    | 5    | 8    | mA    |

| I <sub>CCSB(S)</sub> | Power Down Power Supply<br>Current (Standard Power) | $V_{CC}$ = Max, $\overline{R}$ = $\overline{W}$ = $\overline{RS}$ = $\overline{FL}$ / $\overline{RT}$ > $V_{CC}$ -0.2V, $V_{IN}$ > $V_{CC}$ -0.2V or $V_{IN}$ < 0.2V | -    | -               | 5    | -    | -    | 5    | mA    |

| I <sub>CCSB(L)</sub> | Power Down Power Supply<br>Current (Low Power)      | $V_{CC} = Max$ , $\overline{R} = \overline{W} = \overline{RS} = \overline{FL}/\overline{RT} > V_{CC}$ -0.2V, $V_{IN} > V_{CC}$ -0.2V or $V_{IN} < 0.2V$              | -    | -               | 500  | -    | -    | 500  | μА    |

### **Truth Tables**

### Single Device Configuration/Width Expansion Mode

| Mode       |    | Inputs |    | Interna       | l Status      | Outputs |    |    |  |

|------------|----|--------|----|---------------|---------------|---------|----|----|--|

|            | RS | RT     | Χī | Read Pointer  | Write Pointer | ĒF      | FF | HF |  |

| Reset      | 0  | Х      | 0  | Location Zero | Location Zero | 0       | 1  | 1  |  |

| Retransmit | 1  | 0      | 0  | Location Zero | Unchanged     | Х       | Х  | Х  |  |

| Read/Write | 1  | 1      | 0  | Increment (1) | Increment (1) | Х       | Х  | Х  |  |

NOTE: 1. Pointer will increment if flag is high.

### Depth Expansion/Compound Expansion Mode

| Mode                    | Inputs |    |     | Internal      | Status        | Outputs |    |  |

|-------------------------|--------|----|-----|---------------|---------------|---------|----|--|

|                         | RS     | FL | Χī  | Read Pointer  | Write Pointer | ĒĒ      | FF |  |

| Reset-First Device      | 0      | 0  | (1) | Location Zero | Location Zero | 0       | 1  |  |

| Reset all Other Devices | 0      | 1  | (1) | Location Zero | Unchanged     | 0       | 1  |  |

| Read/Write              | 1      | Х  | (1) | Х             | Х             | Х       | Х  |  |

NOTE:

1.  $\overline{XI}$  is connected to  $\overline{XO}$  of previous device. See Figure 15.  $\overline{RS}$  = Reset Input.  $\overline{FL/RT}$  = First Load/Retransmit.  $\overline{EF}$  = Empty Flag Output.  $\overline{FF}$  Full Flag Output.  $\overline{XI}$  = Expansion Input.

### MS7200L/7201AL/7202AL

# AC Electrical Characteristics (over the commercial operating range)

|                                   |                                       | 1    |      |          |                    | MS7200L-50<br>MS7201AL-50 |                  | MS7200L-80<br>MS7201AL-80 |      |       |

|-----------------------------------|---------------------------------------|------|------|----------|--------------------|---------------------------|------------------|---------------------------|------|-------|

| Parameter                         |                                       |      |      |          | )1AL-50<br>)2AL-50 | 1                         | 1AL-80<br>2AL-80 |                           |      |       |

| Name                              | Parameter                             | Min. | Max. | Min.     | Max.               | Min.                      | Max.             | Min.                      | Max. | Units |

| $f_{\mathbb{S}}$                  | Shift Frequency                       | -    | 30   | -        | 22.2               | -                         | 15               | -                         | 10   | MHz   |

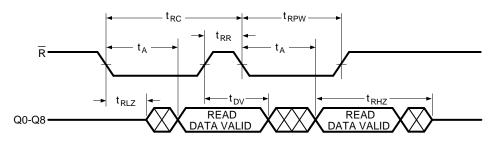

| Read Cycle                        |                                       |      |      |          |                    |                           |                  |                           |      |       |

| t <sub>RC</sub>                   | Read Cycle Time                       | 33   |      | 45       |                    | 65                        | _                | 100                       | _    | ns    |

| t <sub>A</sub>                    | Access Time                           | _    | 25   | _        | 35                 | -                         | 50               | _                         | 80   | ns    |

| t <sub>RPW</sub>                  | Read Pulse Width                      | 25   | _    | 35       | _                  | 50                        | _                | 80                        | _    | ns    |

| t <sub>RR</sub>                   | Read Recovery Time                    | 8    |      | 10       |                    | 15                        | _                | 20                        | _    | ns    |

| t <sub>RL 7</sub> (2)             | Read Pulse Low to Data Bus at Low Z   | 5    | -    | 5        | -                  | 10                        | -                | 10                        | -    | ns    |

| t <sub>RHZ</sub> (2,3)            | Read Pulse High to Data Bus at High Z | -    | 18   | -        | 20                 | -                         | 30               | -                         | 30   | ns    |

| t <sub>DV</sub>                   | Data Valid from Read Pulse High       | 5    | _    | 5        | _                  | 5                         | _                | 5                         | _    | ns    |

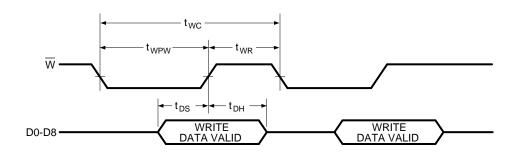

| Write Cycle                       | e                                     |      |      |          |                    |                           |                  |                           |      |       |

| t <sub>WC</sub>                   | Write Cycle Time                      | 33   | -    | 45       | _                  | 65                        | -                | 100                       | -    | ns    |

| t <sub>WPW</sub> <sup>(1)</sup>   | Write Pulse Width                     | 25   | -    | 35       | _                  | 50                        | _                | 80                        | -    | ns    |

| $t_{WR}$                          | Write Recovery Time                   | 8    | _    | 10       | _                  | 15                        | _                | 20                        | -    | ns    |

| t <sub>DS</sub>                   | Data Setup Time                       | 15   | -    | 18       | -                  | 30                        | -                | 40                        | -    | ns    |

| t <sub>DH</sub>                   | Data Hold Time                        | 0    | _    | 0        | _                  | 5                         | -                | 10                        | -    | ns    |

| t <sub>WLZ</sub> <sup>(2,3)</sup> | Write Pulse High to Data Bus at Low Z | 5    | _    | 10       | _                  | 15                        | _                | 20                        | _    | ns    |

| Flag Timing                       | g                                     | _    |      |          |                    | _                         |                  |                           |      |       |

| t <sub>REF</sub>                  | Read Low to Empty Flag Low            | _    | 25   | _        | 30                 | -                         | 45               | _                         | 60   | ns    |

| t <sub>RHF</sub>                  | Read High to Half Full Flag High      | -    | 33   | -        | 45                 | -                         | 65               | -                         | 100  | ns    |

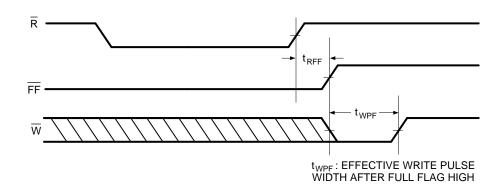

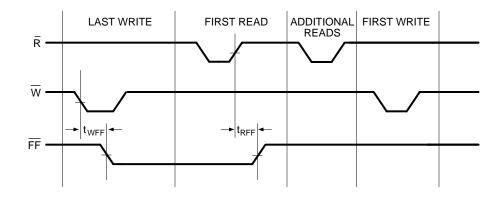

| t <sub>RFF</sub>                  | Read High to Full Flag High           | -    | 25   | -        | 30                 | -                         | 45               | -                         | 60   | ns    |

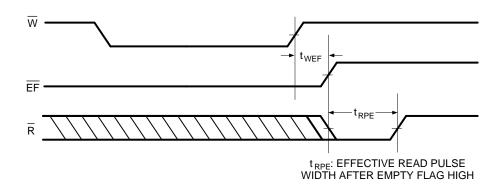

| t <sub>WEF</sub>                  | Write High to Empty Flag High         | -    | 25   | -        | 30                 | -                         | 45               | -                         | 60   | ns    |

| t <sub>WFF</sub>                  | Write Low to Full Flag Low            | -    | 25   | -        | 30                 | -                         | 45               | -                         | 60   | ns    |

| t <sub>WHF</sub>                  | Write Low to Half Full Flag Low       | _    | 33   | _        | 45                 | -                         | 65               | _                         | 100  | ns    |

| t <sub>RPE</sub>                  | Read Pulse Width After EF High        | 25   | _    | 35       |                    | 50                        | -                | 80                        | _    | ns    |

| t <sub>WPF</sub>                  | Write Pulse Width After FF High       | 25   |      | 35       | _                  | 50                        | _                | 80                        | _    | ns    |

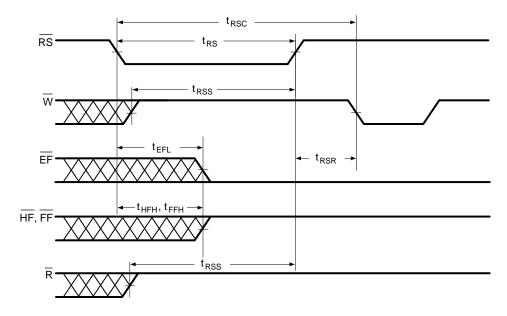

| Reset Timi                        | -                                     |      |      |          | _                  |                           |                  |                           |      |       |

| t <sub>RSC</sub>                  | Reset Cycle Time                      | 33   |      | 45       | _                  | 65                        |                  | 100                       |      | ns    |

| t <sub>RS</sub> (1)               | Reset Pulse Width                     | 25   |      | 35       |                    | 50                        |                  | 80                        |      | ns    |

| t <sub>RSS</sub>                  | Reset Set Up Time                     | 25   |      | 35       | _                  | 50                        | _                | 80                        |      | ns    |

| t <sub>RSR</sub>                  | Reset Recovery Time                   | 8    |      | 10       |                    | 15                        |                  | 20                        |      | ns    |

| t <sub>EFL</sub>                  | Reset to Empty Flag Low               | -    | 33   | <u> </u> | 45                 | -                         | 65               |                           | 100  | ns    |

| t <sub>HFH</sub>                  | Reset to Half Full Flag High          | -    | 33   |          | 45                 | -                         | 65               |                           | 100  | ns    |

| t <sub>FFH</sub>                  | Reset to Full Flag High               | -    | 33   |          | 45                 | -                         | 65               | _                         | 100  | ns    |

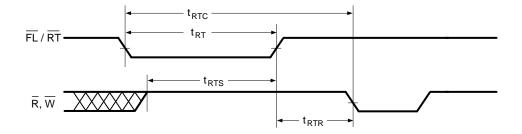

| Retransmit                        | -                                     |      |      |          |                    |                           |                  |                           |      | _     |

| t <sub>RTC</sub>                  | Retransmit Cycle Time                 | 33   |      | 45       |                    | 65                        |                  | 100                       |      | ns    |

| t <sub>RT</sub> <sup>(1)</sup>    | Retransmit Pulse Width                | 25   |      | 35       |                    | 50                        |                  | 80                        |      | ns    |

| t <sub>RTS</sub>                  | Retransmit Set up Time                | 25   |      | 35       |                    | 50                        | -                | 80                        |      | ns    |

| t <sub>RTR</sub>                  | Retransmit Recovery Time              | 8    |      | 10       |                    | 15                        |                  | 20                        |      | ns    |

| Expansion                         |                                       |      |      |          |                    | 1                         |                  |                           | - 00 |       |

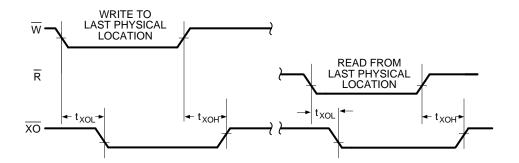

| t <sub>XOL</sub>                  | Read/Write to XO Low                  | -    | 25   | -        | 35                 | -                         | 50               |                           | 80   | ns    |

| t <sub>XOH</sub>                  | Read/Write to XO High                 | -    | 25   | -        | 35                 | -                         | 50               | -                         | 80   | ns    |

| t <sub>XI</sub>                   | XI Pulse Width                        | 25   | -    | 35       |                    | 50                        |                  | 80                        | -    | ns    |

| t <sub>XIS</sub>                  | XI Set up Time                        | 15   |      | 15       |                    | 15                        |                  | 15                        | -    | ns    |

| t <sub>XIR</sub>                  | XI Recovery Time                      | 8    | -    | 10       | -                  | 10                        | -                | 10                        | -    | ns    |

### NOTES:

- 1. Pulse widths less than minimum value are not allowed.

- 2. Values guaranteed by design, not currently tested.

- 3. Only applies to read data flow-through mode.

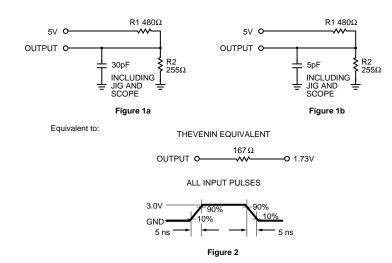

### **AC Test Conditions**

| Input Pulse Levels        | 0V~ 3.0V |

|---------------------------|----------|

| Input Rise and Fall Times | 5 ns     |

| Timing Reference Level    | 1.5V     |

### AC Test Loads and Waveforms

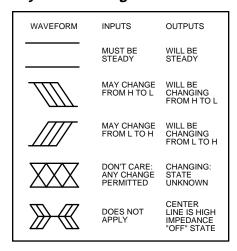

# MS7200L/7201AL/7202AL Key to Switching Waveforms

### **Timing Waveforms**

### **RESET**

### **ASYNCHRONOUS READ OPERATION**

# Timing Waveforms

### **ASYNCHRONOUS WRITE OPERATION**

### **RETRANSMIT**

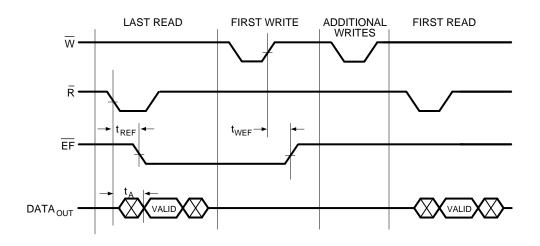

### **EMPTY FLAG TIMING**

### MS7200L/7201AL/7202AL

## **Timing Waveforms**

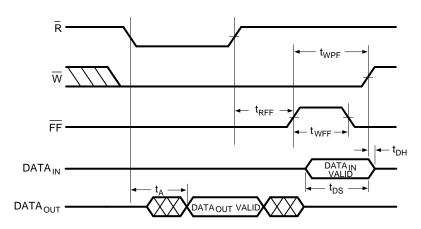

### **FULL FLAG TIMING**

### **HALF-FULL FLAG TIMING**

### **FULL FLAG FROM LAST WRITE TO FIRST READ**

## Timing Waveforms

### **EMPTY FLAG FROM LAST READ TO FIRST WRITE**

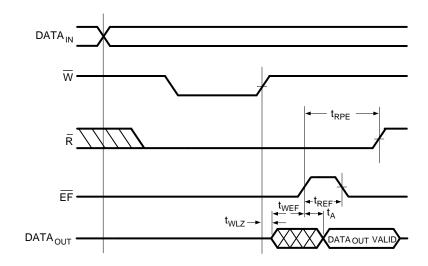

### **READ DATA FLOW-THROUGH MODE**

### WRITE DATA FLOW-THROUGH MODE

MS7200L/01AL/02AL Rev. 1.0 January 1995

# **Timing Waveforms**

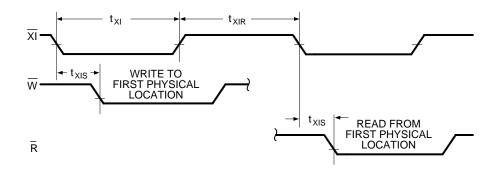

### **EXPANSION IN**

#### **EXPANSION OUT**

### Operating Modes:

(Note: The7201A Lis used as example - these figures apply to all three devices, MS7200L/7201AL/7202AL

### **Single Device Mode**

When one MS7201AL is used standalone in Single Device Mode, the Expansion In  $(\overline{XI})$  control input pin must be grounded. See Figure 3.

Figure 3. Single Device Mode

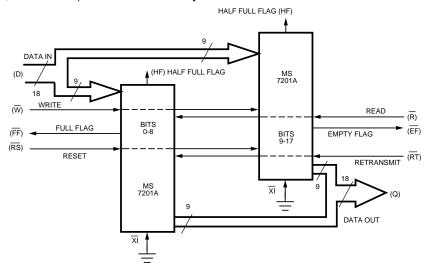

### Width Expansion Mode

Word width may be expanded by connecting the corresponding control input signals of multiple devices together. The EMPTY, HALF FULL and FULL FLAGS (EE, HF and FF) can be detected by

any particular device. Figure 4 shows an 18 bit wide configuration using two devices. They may be configured to any word width in this manner.

Figure 4. Width Expansion Mode

NOTES:

Flag detection is accomplished by monitoring the  $\overline{\text{EF}}$ ,  $\overline{\text{HF}}$  and  $\overline{\text{EF}}$  pins on the device used in the Width Expansion Mode. Do not connect output control signals together.

### Depth Expansion (Daisy Chain) Mode

Word depths may be expanded in multiples of 512 words by Daisy Chaining the devices together as follows:

- 1. The FIRST LOAD (FL) control signal of the first device must be grounded. This FIFO represents word 1-512.

- 2. All other devices in the Daisy Chain must have the FIRST LOAD  $(\overline{FL})$  control signal tied to  $V_{CC}$  in the inactive-high state.

- 3. The EXPANSION OUT (XO) pin of each device must be connected to the EXPANSION IN (XI) pin of the next device as shown in Figure 5.

- External logic is required to generate a common FULL FLAG (FF) and EMPTY FLAG (EF) signal by ORing all of the FFs together and ORing all of the EFs together.

- 5. The RETRANSMIT (RT) fuction and HALF FULL FLAG (HF) are not available in Daisy Chain Mode.

Figure 5. Diagram of a 1536 x 9 FIFO in Depth Expansion Mode

MS7200L/01AL/02AL Rev. 1.0 January 1995

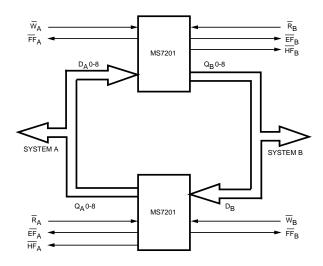

### **Bidirectional Mode**

Data buffering between two systems can be achieved by pairing two FIFO arrays as shown in Figure 6. This allows each system to READ and WRITE shared data. The FULL FLAG ( $\overline{\text{FF}}$ ) must be monitored on the FIFO where WRITE ENABLE ( $\overline{\text{W}}$ ) is used and the EMPTY FLAG ( $\overline{\text{EF}}$ ) must be monitored on the FIFO where READ ENABLE ( $\overline{\text{R}}$ ) is used. Both Width Expansion and Depth Expansion

Modes may be used in combination with Bidirectional Mode.

### Compound Expansion Mode:

Both Width Expansion Mode and Depth Expansion (Daisy Chain) Mode can be used together to configure a large FIFO array (See Figure 4 and 5).

Figure 6. BiDirectional FIFO Mode

### **Ordering Information**

| Speed (ns) | C           | ordering Part Numb | er            | Package                        | Temperature<br>Range |

|------------|-------------|--------------------|---------------|--------------------------------|----------------------|

| 25         |             | MS7201AL-25PC      | MS7202AL-25PC | 28 Pin Plastic DIP - 600 mil   | 0°C to +70°C         |

| 25         | MS7200-25NC | MS7201AL-25NC      | MS7202AL-25NC | 28 Pin Plastic DIP - 300 mil   | 0°C to +70°C         |

| 25         | MS7200-25JC | MS7201AL-25JC      | MS7202AL-25JC | 32 Pin Plastic PLCC            | 0°C to +70°C         |

| 25         | MS7200-25FC | MS7201AL-25FC      | MS7202AL-25FC | 28 Pin Small Outline - 330 mil | 0°C to +70°C         |

| 35         |             | MS7201AL-35PC      | MS7202AL-35PC | 28 Pin Plastic DIP - 600 mil   | 0°C to +70°C         |

| 35         | MS7200-35NC | MS7201AL-35NC      | MS7202AL-35NC | 28 Pin Plastic DIP - 300 mil   | 0°C to +70°C         |

| 35         | MS7200-35JC | MS7201AL-35JC      | MS7202AL-35JC | 32 Pin Plastic PLCC            | 0°C to +70°C         |

| 35         | MS7200-35FC | MS7201AL-35FC      | MS7202AL-35FC | 28 Pin Small Outline - 330 mil | 0°C to +70°C         |

| 50         |             | MS7201AL-50PC      | MS7202AL-50PC | 28 Pin Plastic DIP - 600 mil   | 0°C to +70°C         |

| 50         | MS7200-50NC | MS7201AL-50NC      | MS7202AL-50NC | 28 Pin Plastic DIP - 300 mil   | 0°C to +70°C         |

| 50         | MS7200-50JC | MS7201AL-50JC      | MS7202AL-50JC | 32 Pin Plastic PLCC            | 0°C to +70°C         |

| 50         | MS7200-50FC | MS7201AL-50FC      | MS7202AL-50FC | 28 Pin Small Outline - 330 mil | 0°C to +70°C         |

| 80         |             | MS7201AL-80PC      | MS7202AL-80PC | 28 Pin Plastic DIP - 600 mil   | 0°C to +70°C         |

| 80         | MS7200-80NC | MS7201AL-80NC      | MS7202AL-80NC | 28 Pin Plastic DIP - 300 mil   | 0°C to +70°C         |

| 80         | MS7200-80JC | MS7201AL-80JC      | MS7202AL-80JC | 32 Pin Plastic PLCC            | 0°C to +70°C         |

| 80         | MS7200-80FC | MS7201AL-80FC      | MS7202AL-80FC | 28 Pin Small Outline - 330 mil | 0°C to +70°C         |