## TMS320F28PLC84, TMS320F28PLC83

SPRS802 - SEPTEMBER 2014

# TMS320F28PLC8x Power Line Communications (PLC) Processors

## 1 Device Overview

## 1.1 Features

- · System-on-Chip for Power Line Communications

- Supports PLC Networks Using G3-PLC, PRIME, IEEE-1901.2, ITU G.9903, ITU G.9904

Standards in the CENELEC Frequency Band (35 kHz-90 kHz)

- Designed to Operate With the AFE031 Analog Front End (AFE) for PLC

- Supports Texas Instruments PLC Software

- IEEE 1901.2

- ITU G.9903

- ITU G.9904

- PRIME

- G3-PLC

- TMS320F28PLC84 Includes Key G3-PLC Firmware Routines Loaded into On-chip ROM

- Opens On-chip Flash Memory for Future Firmware Enhancements

- 32-Bit C28x CPU Architecture Optimized for Orthogonal Frequency-Division Multiplex (OFDM) Communications

- Viterbi/Complex Math Unit (VCU)

- 90 MHz

- On-chip Memory

- 256KB of Flash

- 100KB of RAM

- Boot ROM

- 1.2 Applications

- Electric Meters

- Power Line Communications Data Concentrators

- · Power Supply

- Single 3.3-V Power Supply

- Option to Disable On-chip Low-Dropout (LDO) Regulator and Supply 1.8-V Core Voltage With External Regulator

- Communications Peripherals

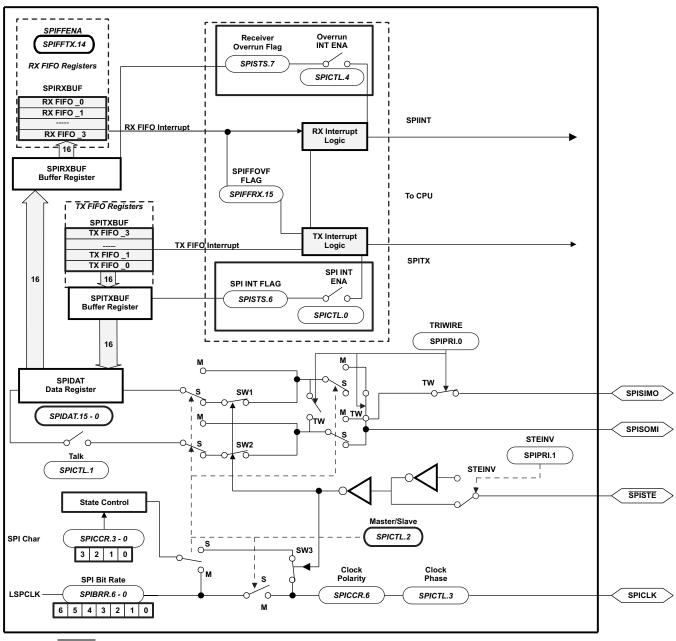

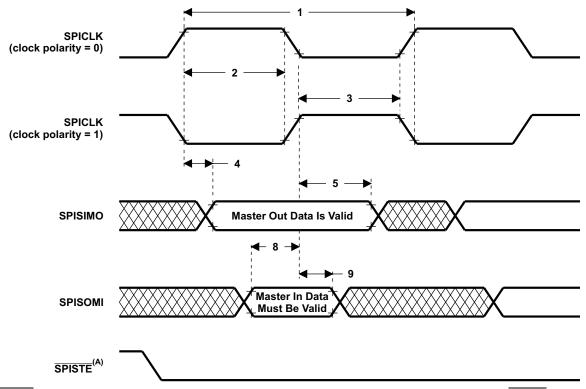

- Two Serial Peripheral Interface (SPI) Ports

- Two Serial Communications Interface (SCI) Ports

- One Multichannel Buffered Serial Port (McBSP)

- · McBSP Port can Also be Used as SPI

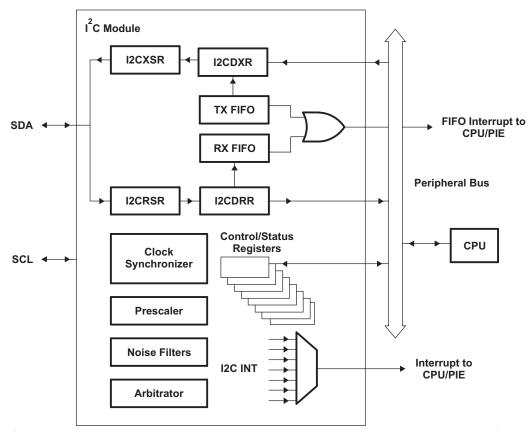

- One Inter-Integrated-Circuit (I<sup>2</sup>C) Port

- Analog Subsystem

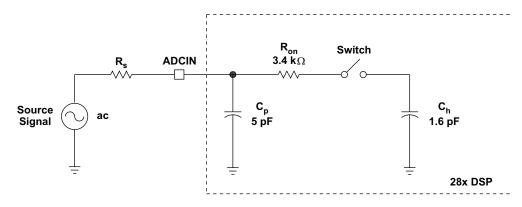

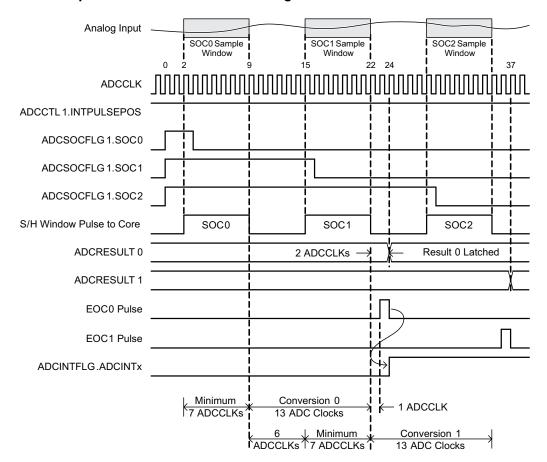

- 12-Bit Analog-to-Digital Converters (ADCs), Each With Dual Sample-and-Hold (S/H)

- ADC Operates at 3.4 MSPS

- 128-Bit Security Key and Lock

- Protects Secure Memory Blocks

- Prevents Firmware Reverse Engineering

- Blocks JTAG Access When Enabled

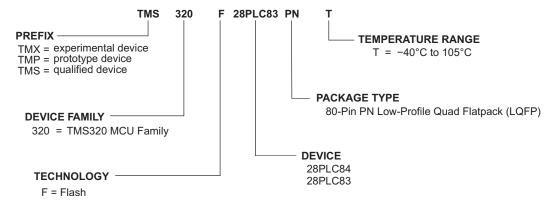

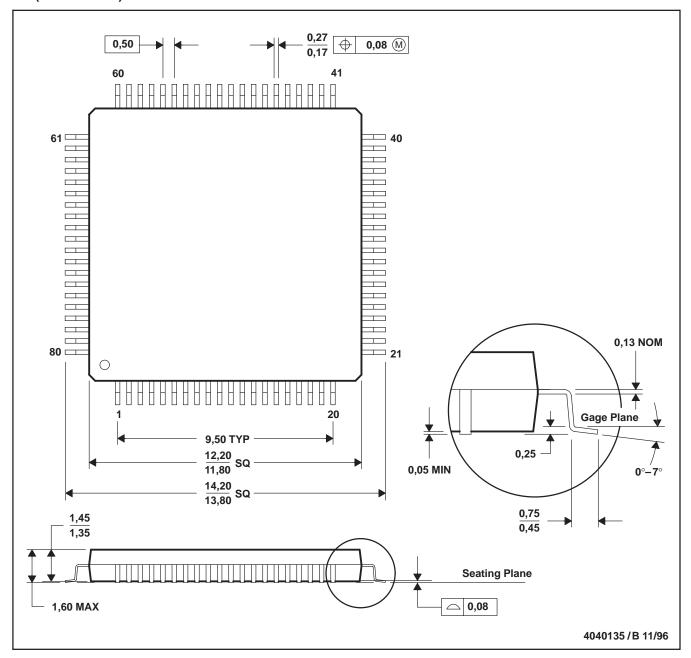

- 80-Pin PN Low-Profile Quad Flatpack (LQFP)

- Industrial Temperature Range: –40°C to 105°C

Solar Inverters

## 1.3 Description

The Texas Instruments TMS320F28PLC8x PLC processors are optimized to meet the requirements for AMI networks in Smart Grid installations that will use narrowband power line communications in the CENELEC frequency band. The CENELEC band is defined to be 35 kHz to 90 kHz.

The F28PLC8x processors are designed to execute the entire PLC protocol stack for the supported industry standards. TI supplies these firmware libraries to execute on the F28PLC8x processors with no additional license fees or royalties.

The F28PLC8x processors are also used in PLC data concentrators, which act as neighborhood-area collectors of electricity usage information from multiple end nodes.

The F28PLC8x processors are optimized to work with the AFE031 analog front end for PLC. The AFE031 is an integrated analog front end for narrowband PLC that is capable of driving a transformer-coupled connection to the AC Mains power line. It is ideal for driving high-current, low-impedance lines driving up to 1.9 A into reactive loads. The AFE031 is compliant to CENELEC A, B, C, and D (EN50065-1, -2, -3, -7) frequency bands.

See Section 7.1.1.2 for a list of reference designs, starter kits, and tools.

## Device Information<sup>(1)</sup>

| PART NUMBER      | PACKAGE   | BODY SIZE         |

|------------------|-----------|-------------------|

| TMS320F28PLC84PN | LQFP (80) | 12.0 mm × 12.0 mm |

| TMS320F28PLC83PN | LQFP (80) | 12.0 mm × 12.0 mm |

For more information on these devices, see Section 8, Mechanical Packaging and Orderable Information.

SPRS802-SEPTEMBER 2014 www.ti.com

#### **Functional Block Diagram** 1.4

**ISTRUMENTS**

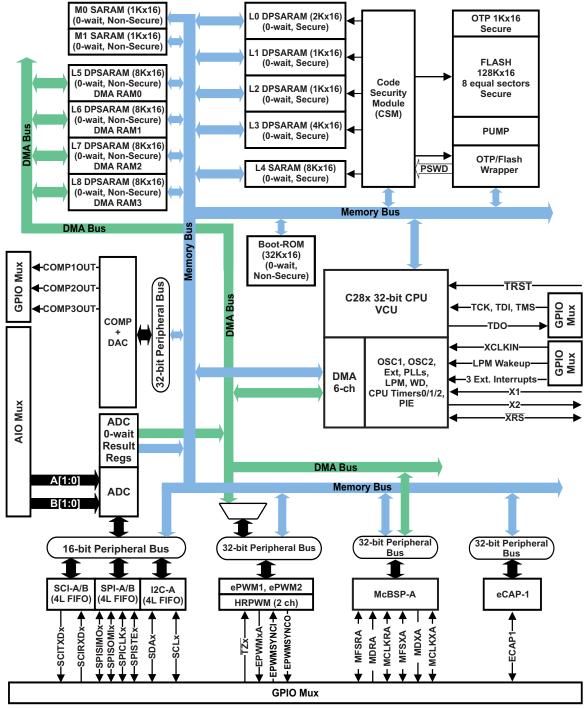

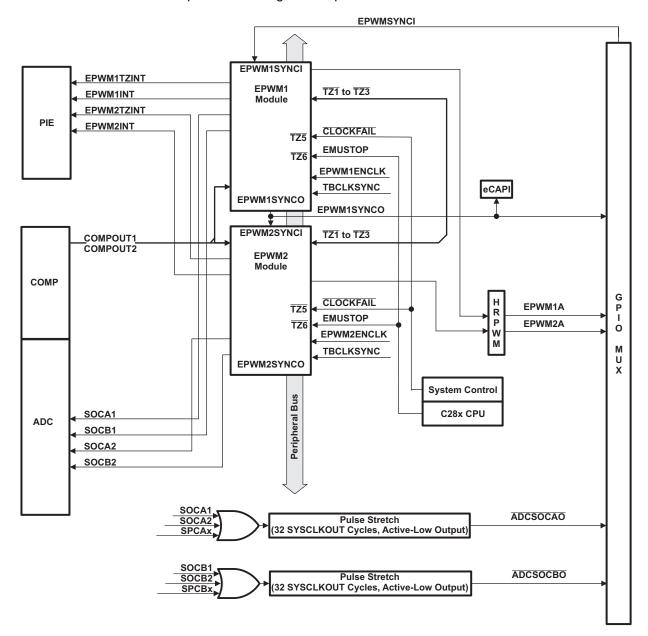

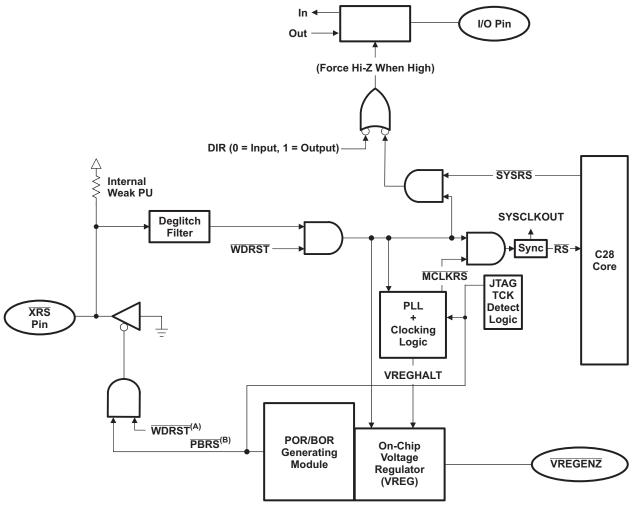

Figure 1-1 shows a functional block diagram of the device.

Not all peripheral pins are available at the same time due to multiplexing.

Figure 1-1. Functional Block Diagram

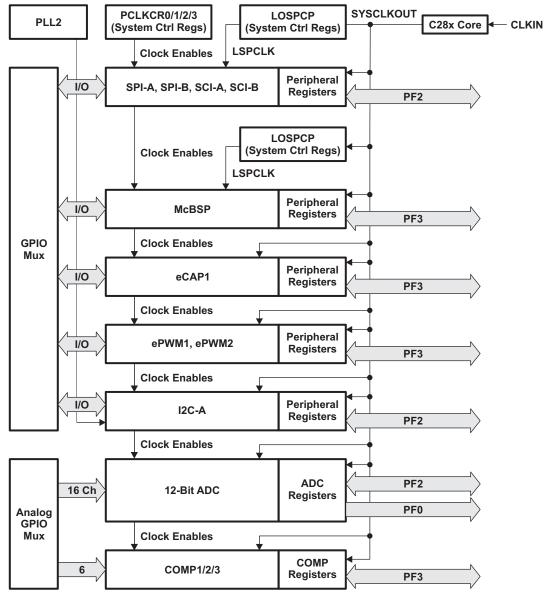

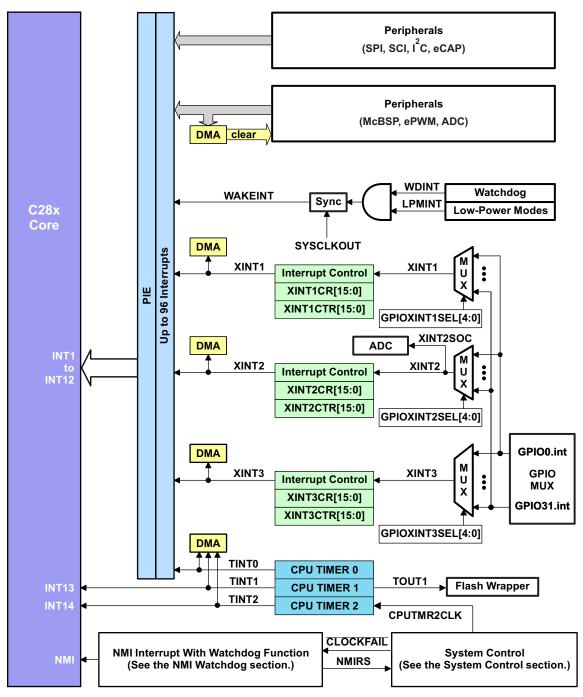

## 1.5 Additional Block Diagrams

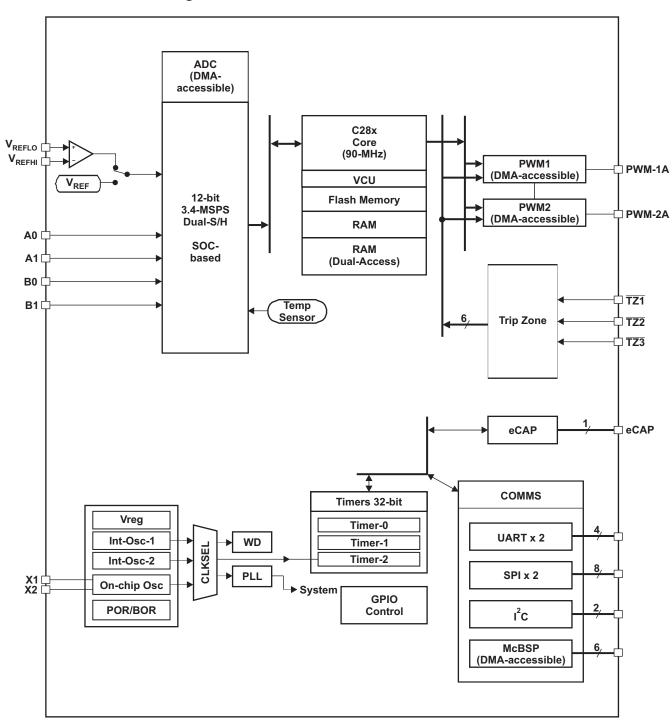

Figure 1-2. Peripheral Blocks

# **Table of Contents**

| 1 | Devi | ce Overview <u>1</u>                           |   | 5.8   | Current Consumption             | <u>96</u>  |

|---|------|------------------------------------------------|---|-------|---------------------------------|------------|

|   | 1.1  | Features <u>1</u>                              |   | 5.9   | Parameter Information           | <u>99</u>  |

|   | 1.2  | Applications <u>1</u>                          |   | 5.10  | Test Load Circuit               | . 99       |

|   | 1.3  | Description                                    |   | 5.11  | Flash Timing                    | 100        |

|   | 1.4  | Functional Block Diagram 3                     | 6 | Deta  | iled Description                | 102        |

|   | 1.5  | Additional Block Diagrams 4                    |   | 6.1   | Overview                        | 102        |

| 2 | Revi | sion History <u>6</u>                          |   | 6.2   | Memory                          | <u>118</u> |

| 3 | Devi | ce Comparison 7                                |   | 6.3   | Identification                  | 123        |

| 4 | Term | ninal Configuration and Functions              | 7 | Devi  | ce and Documentation Support    | 124        |

|   | 4.1  | Signal Descriptions 9                          |   | 7.1   | Device Support                  | 124        |

|   | 4.2  | Pin Multiplexing 15                            |   | 7.2   | Documentation Support           | 126        |

| 5 | Spec | cifications <u>17</u>                          |   | 7.3   | Related Links                   | 126        |

|   | 5.1  | Absolute Maximum Ratings 17                    |   | 7.4   | Community Resources             | 127        |

|   | 5.2  | Handling Ratings                               |   | 7.5   | Trademarks                      | 127        |

|   | 5.3  | Recommended Operating Conditions               |   | 7.6   | Electrostatic Discharge Caution | 127        |

|   | 5.4  | Electrical Characteristics                     |   | 7.7   | Glossary                        | 127        |

|   | 5.5  | Thermal Resistance Characteristics for PN      | 8 |       | nanical Packaging and Orderable |            |

|   |      | Package <u>19</u>                              |   | Infor | mation                          | 128        |

|   | 5.6  | Thermal Design Considerations 19               |   | 8.1   | Packaging Information           | 128        |

|   | 5.7  | Timing and Switching Characteristics <u>20</u> |   |       |                                 |            |

|   |      |                                                |   |       |                                 |            |

SPRS802 - SEPTEMBER 2014

## 2 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| DATE           | REVISION | NOTES           |

|----------------|----------|-----------------|

| September 2014 | *        | Initial Release |

# 3 Device Comparison

Table 3-1 lists the features of the F28PLC8x devices.

## NOTE

The F28PLC84 device has the same hardware features as the F28PLC83 device. The only difference is that the F28PLC84 has a new ROM code with additional PLC software included.

**Table 3-1. Device Comparison**

|                                | FEATURE                                          | TYPE <sup>(1)</sup> | F28PLC84<br>F28PLC83<br>(90 MHz) |

|--------------------------------|--------------------------------------------------|---------------------|----------------------------------|

| Package Type                   |                                                  |                     | 80-Pin PN                        |

| Instruction cycle              |                                                  | _                   | 11.11 ns                         |

| VCU                            |                                                  |                     | Yes                              |

| 6-Channel Direct Memory Acc    | cess (DMA)                                       | 0                   | Yes                              |

| On-chip Flash (16-bit word)    |                                                  | -                   | 128K                             |

| On-chip SARAM (16-bit word)    |                                                  | -                   | 50K                              |

| Code security for on-chip Flas | h, SARAM, and One-time programmable (OTP) blocks | -                   | Yes                              |

| Boot ROM (32K x 16)            |                                                  | -                   | Yes                              |

| OTP ROM (16-bit word)          |                                                  | -                   | 1K                               |

| Enhanced Pulse Width Modul     | ator (ePWM) channels                             | 1                   | 2                                |

| High-resolution ePWM channel   | els                                              | 1                   | 2                                |

| Enhanced Capture (eCAP) inp    | outs                                             | 0                   | 1                                |

| Watchdog timer                 |                                                  | -                   | Yes                              |

|                                | MSPS                                             |                     | 3.4                              |

|                                | Conversion Time                                  | 3                   | 289 ns                           |

| 12-Bit ADC                     | Channels                                         |                     | 4                                |

|                                | Temperature Sensor                               |                     | Yes                              |

|                                | Dual Sample-and-Hold                             |                     | Yes                              |

| 32-Bit CPU timers              |                                                  | -                   | 3                                |

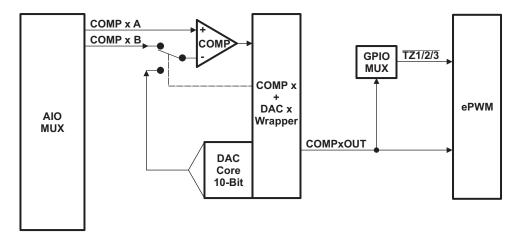

| Comparators with Integrated I  | DACs                                             | 0                   | 3                                |

| I <sup>2</sup> C               |                                                  | 0                   | 1                                |

| McBSP                          |                                                  | 1                   | 1                                |

| SPI                            |                                                  | 1                   | 2                                |

| SCI                            |                                                  | 0                   | 2                                |

| 2-pin Oscillator               |                                                  |                     | 1                                |

| 0-pin Oscillator               |                                                  |                     | 2                                |

| 1/0 = 1 = 1 = 1                | General-Purpose Input/Output (GPIO)              | -                   | 40                               |

| I/O pins (shared)              | Analog Input/Output (AIO)                        | -                   | 6                                |

| External interrupts            |                                                  | -                   | 3                                |

| Supply voltage (nominal)       |                                                  | _                   | 3.3 V                            |

| Temperature options            | T: -40°C to 105°C                                | _                   | Yes                              |

| Product status <sup>(2)</sup>  |                                                  | _                   | TMS                              |

<sup>(1)</sup> A type change represents a major functional feature difference in a peripheral module. Within a peripheral type, there may be minor differences between devices that do not affect the basic functionality of the module. These device-specific differences are listed in the TMS320x28xx, 28xxx DSP Peripheral Reference Guide (SPRU566) and in the peripheral reference guides.

<sup>(2)</sup> See Section 7.1.2, Device and Development Support Tool Nomenclature, for descriptions of device stages. The "TMS" product status denotes a fully qualified production device.

# TEXAS INSTRUMENTS

## 4 Terminal Configuration and Functions

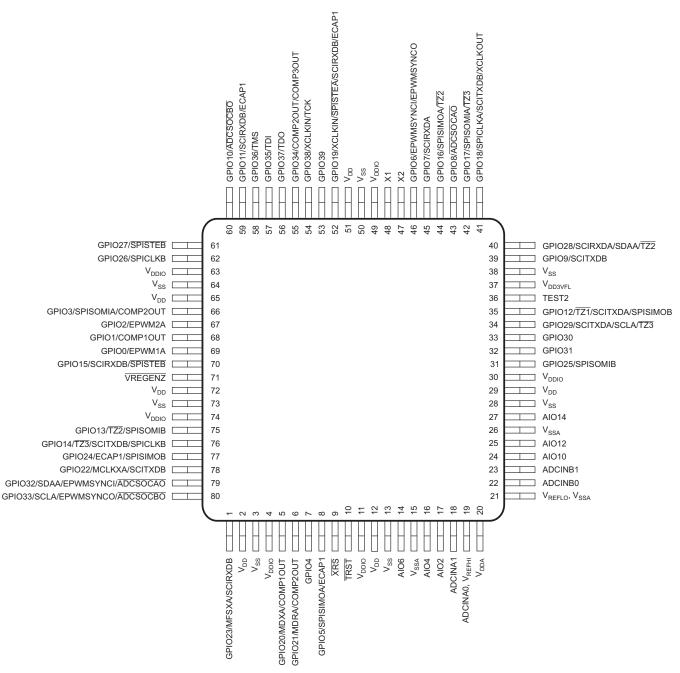

Figure 4-1 shows the pin assignments on the 80-pin PN package.

A. Pin 19: V<sub>REFHI</sub> and ADCINA0 share the same pin on the 80-pin PN device and their use is mutually exclusive to one another.

Pin 21:  $V_{\text{REFLO}}$  is always connected to  $V_{\text{SSA}}$  on the 80-pin PN device.

Figure 4-1. 80-Pin PN Package (Top View)

## 4.1 Signal Descriptions

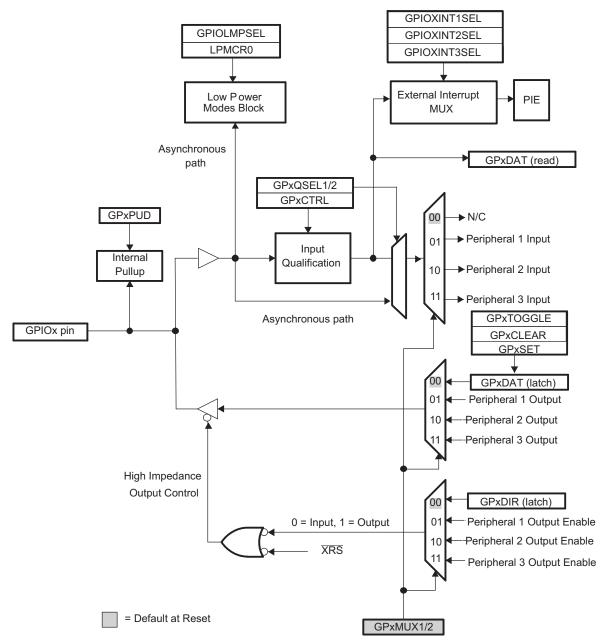

Table 4-1 describes the signals. With the exception of the JTAG pins, the GPIO function is the default at reset, unless otherwise mentioned. The peripheral signals that are listed under them are alternate functions. Inputs are not 5-V tolerant. All GPIO pins are I/O/Z and have an internal pullup, which can be selectively enabled or disabled on a per-pin basis. This feature only applies to the GPIO pins. The pullups on the PWM pins are not enabled at reset. The pullups on other GPIO pins are enabled upon reset. The AIO pins do not have an internal pullup.

**NOTE:** When the on-chip voltage regulator (VREG) is used, the GPIO19, GPIO34, GPIO35, GPIO36, GPIO37, and GPIO38 pins could glitch during power up. If this behavior is unacceptable in an application, 1.8 V could be supplied externally. There is no power-sequencing requirement when using an external 1.8-V supply. However, if the 3.3-V transistors in the level-shifting output buffers of the I/O pins are powered prior to the 1.9-V transistors, it is possible for the output buffers to turn on, causing a glitch to occur on the pin during power up. To avoid this behavior, power the  $V_{DD}$  pins prior to or simultaneously with the  $V_{DDIO}$  pins, ensuring that the  $V_{DD}$  pins have reached 0.7 V before the  $V_{DDIO}$  pins reach 0.7 V.

Table 4-1. Signal Descriptions<sup>(1)</sup>

| TERMINAL                |                 |     |                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

|-------------------------|-----------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| NAME                    | NAME PN PIN NO. |     | DESCRIPTION                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

|                         | JTAG            |     |                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

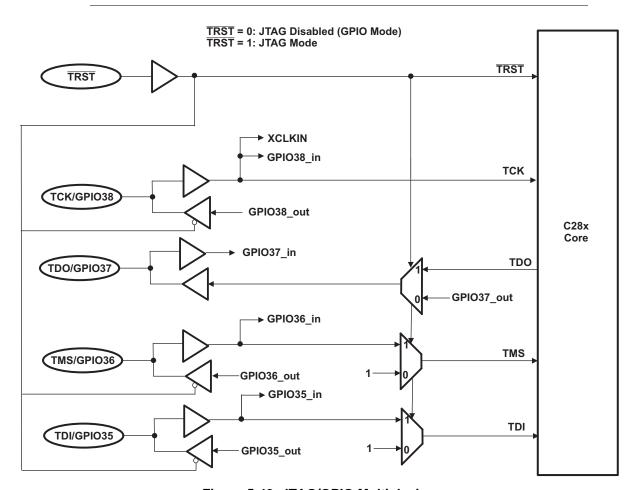

| TRST                    | 10              | I   | JTAG test reset with internal pulldown. $\overline{TRST}$ , when driven high, gives the scan system control of the operations of the device. If this signal is not connected or driven low, the device operates in its functional mode, and the test reset signals are ignored. |  |  |  |  |  |  |

| тск                     | See<br>GPIO38   | I   | See GPIO38. JTAG test clock with internal pullup. (↑)                                                                                                                                                                                                                           |  |  |  |  |  |  |

| TMS                     | See<br>GPIO36   | I   | See GPIO36. JTAG test-mode select (TMS) with internal pullup. This serial control input is clocked into the TAP controller on the rising edge of TCK. (↑)                                                                                                                       |  |  |  |  |  |  |

| TDI                     | See<br>GPIO35   | I   | See GPIO35. JTAG test data input (TDI) with internal pullup. TDI is clocked into the selected register (instruction or data) on a rising edge of TCK. (↑)                                                                                                                       |  |  |  |  |  |  |

| TDO See O/Z (instructio |                 | O/Z | See GPIO37. JTAG scan out, test data output (TDO). The contents of the selected register (instruction or data) are shifted out of TDO on the falling edge of TCK. (8-mA drive)                                                                                                  |  |  |  |  |  |  |

|                         | FLASH           |     |                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

| V <sub>DD3VFL</sub>     | 37              |     | 3.3-V Flash Core Power Pin. This pin should be connected to 3.3 V at all times.                                                                                                                                                                                                 |  |  |  |  |  |  |

| TEST2                   | 36              | I/O | Test Pin. Reserved for TI. Must be left unconnected.                                                                                                                                                                                                                            |  |  |  |  |  |  |

<sup>(1)</sup> I = Input, O = Output, Z = High Impedance, OD = Open Drain, ↑ = Pullup, ↓ = Pulldown

| TERMINAL |                                                                          |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

|----------|--------------------------------------------------------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| NAME     | NAME PN PIN NO.                                                          |      | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

|          | CLOCK                                                                    |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

| XCLKOUT  | See<br>GPIO18                                                            | O/Z  | See GPIO18. Output clock derived from SYSCLKOUT. XCLKOUT is either the same frequency, one-half the frequency, or one-fourth the frequency of SYSCLKOUT. The value of XCLKOUT is controlled by bits 1:0 (XCLKOUTDIV) in the XCLK register. At reset, XCLKOUT = SYSCLKOUT/4. The XCLKOUT signal can be turned off by setting XCLKOUTDIV to 3. The mux control for GPIO18 must also be set to XCLKOUT for this signal to propogate to the pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

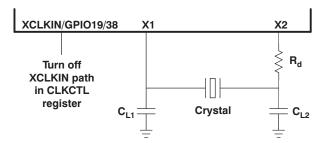

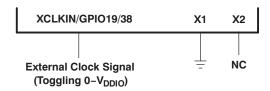

| XCLKIN   | See<br>GPIO19<br>and<br>GPIO38                                           | I    | See GPIO19 and GPIO38. External oscillator input. Pin source for the clock is controlled by the XCLKINSEL bit in the XCLK register, GPIO38 is the default selection. This pin feeds a clock from an external 3.3-V oscillator. In this case, the X1 pin, if available, must be tied to GND and the on-chip crystal oscillator must be disabled via bit 14 in the CLKCTL register. If a crystal/resonator is used, the XCLKIN path must be disabled by bit 13 in the CLKCTL register. NOTE: Designs that use the GPIO38/XCLKIN/TCK pin to supply an external clock for normal device operation may need to incorporate some hooks to disable this path during debug using the JTAG connector. This action is to prevent contention with the TCK signal, which is active during JTAG debug sessions. The zero-pin internal oscillators may be used during this time to clock the device.                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

| X1       | 48 I must be connected across X1 and X2. In this case, the XCLKIN path m |      | On-chip crystal-oscillator input. To use this oscillator, a quartz crystal or a ceramic resonator must be connected across X1 and X2. In this case, the XCLKIN path must be disabled by bit 13 in the CLKCTL register. If this pin is not used, this pin must be tied to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| X2       | 47                                                                       | 0    | On-chip crystal-oscillator output. A quartz crystal or a ceramic resonator must be connected across X1 and X2. If X2 is not used, X2 must be left unconnected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

|          | ·                                                                        |      | RESET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

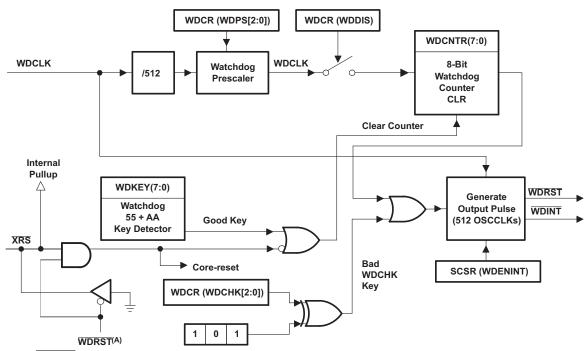

| XRS      | 9                                                                        | I/OD | Device Reset (in) and Watchdog Reset (out). The F28PLC8x device has a built-in power-on reset (POR) and brown-out reset (BOR) circuitry. During a power-on or brown-out condition, this pin is driven low by the device. An external circuit may also drive this pin to assert a device reset. This pin is also driven low by the device when a watchdog reset occurs. During watchdog reset, the $\overline{XRS}$ pin is driven low for the watchdog reset duration of 512 OSCCLK cycles. A resistor between $2.2 \text{ k}\Omega$ and $10 \text{ k}\Omega$ should be placed between $\overline{XRS}$ and $V_{DDIO}$ . If a capacitor is placed between $2.2 \text{ k}\Omega$ and $10 \text{ k}\Omega$ should be placed between $100 \text{ n}$ F or smaller. These values will allow the watchdog to properly drive the $100 \text{ n}$ for smaller. These values will allow the watchdog reset is asserted. Regardless of the source, a device reset causes the device to terminate execution. The program counter points to the address contained at the location $100 \text{ n}$ for this pin is an open-drain with an internal pullup. (†) |  |  |  |  |  |  |

| TERMINAL           |               |       |                                                                                                                                                                                                                                     |  |  |

|--------------------|---------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME               | PN<br>PIN NO. | I/O/Z | DESCRIPTION                                                                                                                                                                                                                         |  |  |

|                    |               |       | ADC, COMPARATOR, ANALOG I/O                                                                                                                                                                                                         |  |  |

| AIO6               | 14            | I/O   | Digital AIO 6                                                                                                                                                                                                                       |  |  |

| AIO4               | 16            | I/O   | Digital AIO 4                                                                                                                                                                                                                       |  |  |

| AIO2               | 17            | I/O   | Digital AIO 2                                                                                                                                                                                                                       |  |  |

| ADCINA1            | 18            | I     | ADC Group A, Channel 1 input                                                                                                                                                                                                        |  |  |

| ADCINA0            | 19            | I     | ADC Group A, Channel 0 input. <b>NOTE:</b> V <sub>REFHI</sub> and ADCINA0 share the same pin on the 80-pin PN device and their use is mutually exclusive to one another.                                                            |  |  |

| $V_{REFHI}$        | 19            |       | ADC External Reference – only used when in ADC external reference mode. See Section 5.7.4.1.1.  NOTE: V <sub>REFHI</sub> and ADCINA0 share the same pin on the 80-pin PN device and their use is mutually exclusive to one another. |  |  |

| AIO14              | 27            | I/O   | Digital AIO 14                                                                                                                                                                                                                      |  |  |

| AIO12              | 25            | I/O   | Digital AIO12                                                                                                                                                                                                                       |  |  |

| AIO10              | 24            | I/O   | Digital AIO 10                                                                                                                                                                                                                      |  |  |

| ADCINB1            | 23            | I     | ADC Group B, Channel 1 input                                                                                                                                                                                                        |  |  |

| ADCINB0            | 22            | I     | ADC Group B, Channel 0 input                                                                                                                                                                                                        |  |  |

| V <sub>REFLO</sub> | 21            |       | NOTE: V <sub>REFLO</sub> is always connected to V <sub>SSA</sub> on the 80-pin PN device.                                                                                                                                           |  |  |

|                    |               |       | CPU AND I/O POWER                                                                                                                                                                                                                   |  |  |

| $V_{DDA}$          | 20            |       | Analog Power Pin. Tie with a 2.2-µF capacitor (typical) close to the pin.                                                                                                                                                           |  |  |

| V <sub>SSA</sub>   | 15            |       |                                                                                                                                                                                                                                     |  |  |

| V <sub>SSA</sub>   | 21            |       | Analog Ground Pin.  NOTE: V <sub>REFLO</sub> is always connected to V <sub>SSA</sub> on the 80-pin PN device.                                                                                                                       |  |  |

| V <sub>SSA</sub>   | 26            |       | 35A                                                                                                                                                                                                                                 |  |  |

| $V_{DD}$           | 2             |       |                                                                                                                                                                                                                                     |  |  |

| $V_{DD}$           | 12            |       |                                                                                                                                                                                                                                     |  |  |

| $V_{DD}$           | 29            |       | CPU and Logic Digital Power Pins. When using internal VREG, place one 1.2-μF capacitor                                                                                                                                              |  |  |

| $V_{DD}$           | 51            |       | between each V <sub>DD</sub> pin and ground. Higher value capacitors may be used.                                                                                                                                                   |  |  |

| $V_{DD}$           | 65            |       |                                                                                                                                                                                                                                     |  |  |

| $V_{DD}$           | 72            |       |                                                                                                                                                                                                                                     |  |  |

| $V_{DDIO}$         | 4             |       |                                                                                                                                                                                                                                     |  |  |

| $V_{DDIO}$         | 11            |       |                                                                                                                                                                                                                                     |  |  |

| $V_{DDIO}$         | 30            |       | ☐ Digital I/O and Flash Power Pin – Single Supply source when VREG is enabled.                                                                                                                                                      |  |  |

| V <sub>DDIO</sub>  | 49            |       | Digital 1/O and hash hower him - Single Supply Source when VICEO is enabled.                                                                                                                                                        |  |  |

| $V_{DDIO}$         | 63            |       |                                                                                                                                                                                                                                     |  |  |

| $V_{DDIO}$         | 74            |       |                                                                                                                                                                                                                                     |  |  |

| V <sub>SS</sub>    | 3             |       |                                                                                                                                                                                                                                     |  |  |

| V <sub>SS</sub>    | 13            |       |                                                                                                                                                                                                                                     |  |  |

| V <sub>SS</sub>    | 28            |       |                                                                                                                                                                                                                                     |  |  |

| V <sub>SS</sub>    | 38            |       | Digital Ground Pins                                                                                                                                                                                                                 |  |  |

| V <sub>SS</sub>    | 50            |       |                                                                                                                                                                                                                                     |  |  |

| V <sub>SS</sub>    | 64            |       |                                                                                                                                                                                                                                     |  |  |

| V <sub>SS</sub>    | 73            |       |                                                                                                                                                                                                                                     |  |  |

|                    |               |       | VOLTAGE REGULATOR CONTROL SIGNAL                                                                                                                                                                                                    |  |  |

| VREGENZ            | 71            | I     | Internal VREG Enable/Disable – pull low to enable VREG, pull high to disable VREG.                                                                                                                                                  |  |  |

| TERMINAL  |               |       |                                                                                  |  |  |

|-----------|---------------|-------|----------------------------------------------------------------------------------|--|--|

| NAME      | PN<br>PIN NO. | I/O/Z | DESCRIPTION                                                                      |  |  |

|           |               |       | GPIO AND PERIPHERAL SIGNALS (1)                                                  |  |  |

| GPIO0     | 60            | I/O/Z | General-purpose input/output 0                                                   |  |  |

| EPWM1A    | 69            | 0     | Enhanced PWM1 Output A and High-resolution Pulse Width Modulator (HRPWM) channel |  |  |

| GPIO1     | 60            | I/O/Z | General-purpose input/output 1                                                   |  |  |

| COMP1OUT  | 68            | 0     | Direct output of Comparator 1                                                    |  |  |

| GPIO2     | 67            | I/O/Z | General-purpose input/output 2                                                   |  |  |

| EPWM2A    | 67            | 0     | Enhanced PWM2 Output A and HRPWM channel                                         |  |  |

| GPIO3     |               | I/O/Z | General-purpose input/output 3                                                   |  |  |

| SPISOMIA  | 66            | I/O   | SPI-A slave out, master in                                                       |  |  |

| COMP2OUT  |               | 0     | Direct output of Comparator 2                                                    |  |  |

| GPIO4     | 7             | I/O/Z | General-purpose input/output 4                                                   |  |  |

| GPIO5     |               | I/O/Z | General-purpose input/output 5                                                   |  |  |

| SPISIMOA  | 8             | I/O   | SPI-A slave in, master out                                                       |  |  |

| ECAP1     |               | I/O   | Enhanced Capture input/output 1                                                  |  |  |

| GPIO6     |               | I/O/Z | General-purpose input/output 6                                                   |  |  |

| EPWMSYNCI | 46            | 1     | External ePWM sync pulse input                                                   |  |  |

| EPWMSYNCO |               | 0     | External ePWM sync pulse output                                                  |  |  |

| GPI07     | 45            | I/O/Z | General-purpose input/output 7                                                   |  |  |

| SCIRXDA   | 45            | 1     | SCI-A receive data                                                               |  |  |

| GPIO8     | 1/O/Z<br>43 – |       | General-purpose input/output 8                                                   |  |  |

| Reserved  |               |       | Reserved                                                                         |  |  |

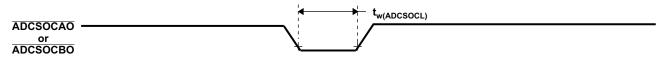

| ADCSOCAO  |               | 0     | ADC start-of-conversion A                                                        |  |  |

| GPIO9     |               | I/O/Z | General-purpose input/output 9                                                   |  |  |

| SCITXDB   | 39            | 0     | SCI-B transmit data                                                              |  |  |

| GPIO10    |               | I/O/Z | General-purpose input/output 10                                                  |  |  |

| Reserved  | 60            | _     | Reserved                                                                         |  |  |

| ADCSOCBO  |               | 0     | ADC start-of-conversion B                                                        |  |  |

| GPIO11    |               | I/O/Z | General-purpose input/output 11                                                  |  |  |

| SCIRXDB   | 59            | 1     | SCI-B receive data                                                               |  |  |

| ECAP1     |               | I/O   | Enhanced Capture input/output 1                                                  |  |  |

| GPIO12    |               | I/O/Z | General-purpose input/output 12                                                  |  |  |

| TZ1       | 25            | 1     | Trip Zone input 1                                                                |  |  |

| SCITXDA   | 35            | 0     | SCI-A transmit data                                                              |  |  |

| SPISIMOB  |               | I/O   | SPI-B slave in, master out                                                       |  |  |

| GPIO13    |               | I/O/Z | General-purpose input/output 13                                                  |  |  |

| TZ2       | 75            | 1     | Trip Zone input 2                                                                |  |  |

| Reserved  |               |       | Reserved                                                                         |  |  |

| SPISOMIB  |               |       | SPI-B slave out, master in                                                       |  |  |

| GPIO14    |               | I/O/Z | General-purpose input/output 14                                                  |  |  |

| TZ3       | 70            | 1     | Trip zone input 3                                                                |  |  |

| SCITXDB   | 76            | 0     | SCI-B transmit data                                                              |  |  |

| SPICLKB   |               | I/O   | SPI-B clock input/output                                                         |  |  |

<sup>(1)</sup> The GPIO function (shown in bold italics) is the default at reset. The peripheral signals that are listed under them are alternate functions. For JTAG pins that have the GPIO functionality multiplexed, the input path to the GPIO block is always valid. The output path from the GPIO block and the path to the JTAG block from a pin is enabled or disabled based on the condition of the TRST signal.

| TERMINAL   |               |       |                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|------------|---------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME       | PN<br>PIN NO. | I/O/Z | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| GPIO15     |               | I/O/Z | General-purpose input/output 15                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| SCIRXDB    | 70            | 1     | SCI-B receive data                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| SPISTEB    |               | I/O   | SPI-B slave transmit enable input/output                                                                                                                                                                                                                                                                                                                                                                                         |  |

| GPIO16     |               | I/O/Z | General-purpose input/output 16                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| SPISIMOA   | 4.4           | I/O   | SPI-A slave in, master out                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| Reserved   | 44            | -     | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| TZ2        |               | 1     | Trip Zone input 2                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| GPIO17     |               | I/O/Z | General-purpose input/output 17                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| SPISOMIA   | 40            | I/O   | SPI-A slave out, master in                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| Reserved   | 42            | _     | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| TZ3        |               | 1     | Trip zone input 3                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| GPIO18     |               | I/O/Z | General-purpose input/output 18                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| SPICLKA    |               | I/O   | SPI-A clock input/output                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| SCITXDB    |               | 0     | SCI-B transmit data                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| XCLKOUT 41 |               | O/Z   | Output clock derived from SYSCLKOUT. XCLKOUT is either the same frequency, one-half the frequency, or one-fourth the frequency of SYSCLKOUT. The value of XCLKOUT is controlled by bits 1:0 (XCLKOUTDIV) in the XCLK register. At reset, XCLKOUT = SYSCLKOUT/4. The XCLKOUT signal can be turned off by setting XCLKOUTDIV to 3. The mux control for GPIO18 must also be set to XCLKOUT for this signal to propagate to the pin. |  |

| GPIO19     |               | I/O/Z | General-purpose input/output 19                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| XCLKIN     | 52            | I     | External Oscillator Input. The path from this pin to the clock block is not gated by the mux function of this pin. Care must be taken not to enable this path for clocking if this path is being used for the other peripheral functions.                                                                                                                                                                                        |  |

| SPISTEA    | 52            | I/O   | SPI-A slave transmit enable input/output                                                                                                                                                                                                                                                                                                                                                                                         |  |

| SCIRXDB    |               | 1     | SCI-B receive data                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| ECAP1      |               | I/O   | Enhanced Capture input/output 1                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| GPIO20     |               | I/O/Z | General-purpose input/output 20                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| MDXA       | 5             | 0     | McBSP transmit serial data                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| COMP1OUT   |               | 0     | Direct output of Comparator 1                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| GPIO21     |               | I/O/Z | General-purpose input/output 21                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| MDRA       | 6             | 1     | McBSP receive serial data                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| COMP2OUT   |               | 0     | Direct output of Comparator 2                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| GPIO22     |               | I/O/Z | General-purpose input/output 22                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| MCLKXA     | 78            | I/O   | McBSP transmit clock                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| SCITXDB    |               | 0     | SCI-B transmit data                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| GPIO23     |               | I/O/Z | General-purpose input/output 23                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| MFSXA      | 1             | I/O   | McBSP transmit frame synch                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| SCIRXDB    |               |       | SCI-B receive data                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| GPIO24     | I/O/Z         |       | General-purpose input/output 24                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| ECAP1      | 77            | I/O   | Enhanced Capture input/output 1                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| SPISIMOB   |               | I/O   | SPI-B slave in, master out                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| GPIO25     |               | I/O/Z | General-purpose input/output 25                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| SPISOMIB   | 31            | I/O   | SPI-B slave out, master in                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| TERMINAL  |               |       |                                                                                                                                                                                                                                |  |  |  |

|-----------|---------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME      | PN<br>PIN NO. | I/O/Z | DESCRIPTION                                                                                                                                                                                                                    |  |  |  |

| GPIO26    | 60            | I/O/Z | General-purpose input/output 26                                                                                                                                                                                                |  |  |  |

| SPICLKB   | 62            | I/O   | SPI-B clock input/output                                                                                                                                                                                                       |  |  |  |

| GPIO27    | 04            | I/O/Z | General-purpose input/output 27                                                                                                                                                                                                |  |  |  |

| SPISTEB   | 61            | I/O   | SPI-B slave transmit enable input/output                                                                                                                                                                                       |  |  |  |

| GPIO28    |               | I/O/Z | General-purpose input/output 28                                                                                                                                                                                                |  |  |  |

| SCIRXDA   | 40            | 1     | SCI-A receive data                                                                                                                                                                                                             |  |  |  |

| SDAA      | 40            | I/OD  | I <sup>2</sup> C data open-drain bidirectional port                                                                                                                                                                            |  |  |  |

| TZ2       |               | 1     | Trip zone input 2                                                                                                                                                                                                              |  |  |  |

| GPIO29    |               | I/O/Z | General-purpose input/output 29                                                                                                                                                                                                |  |  |  |

| SCITXDA   | 34            | 0     | SCI-A transmit data                                                                                                                                                                                                            |  |  |  |

| SCLA      | 34            | I/OD  | I <sup>2</sup> C clock open-drain bidirectional port                                                                                                                                                                           |  |  |  |

| TZ3       |               | 1     | Trip zone input 3                                                                                                                                                                                                              |  |  |  |

| GPIO30    | 33            | I/O/Z | General-purpose input/output 30                                                                                                                                                                                                |  |  |  |

| GPIO31    | 32            | I/O/Z | General-purpose input/output 31                                                                                                                                                                                                |  |  |  |

| GPIO32    |               | I/O/Z | General-purpose input/output 32                                                                                                                                                                                                |  |  |  |

| SDAA      | 70            | I/OD  | I <sup>2</sup> C data open-drain bidirectional port                                                                                                                                                                            |  |  |  |

| EPWMSYNCI | 79            | 1     | Enhanced PWM external sync pulse input                                                                                                                                                                                         |  |  |  |

| ADCSOCAO  |               | 0     | ADC start-of-conversion A                                                                                                                                                                                                      |  |  |  |

| GPIO33    |               | I/O/Z | General-purpose input/output 33                                                                                                                                                                                                |  |  |  |

| SCLA      | 80            | I/OD  | I <sup>2</sup> C clock open-drain bidirectional port                                                                                                                                                                           |  |  |  |

| EPWMSYNCO | 00            | 0     | Enhanced PWM external synch pulse output                                                                                                                                                                                       |  |  |  |

| ADCSOCBO  |               | 0     | ADC start-of-conversion B                                                                                                                                                                                                      |  |  |  |

| GPIO34    |               | I/O/Z | General-purpose input/output 34                                                                                                                                                                                                |  |  |  |

| COMP2OUT  | 55            | 0     | Direct output of Comparator 2                                                                                                                                                                                                  |  |  |  |

| COMP3OUT  |               | 0     | Direct output of Comparator 3                                                                                                                                                                                                  |  |  |  |

| GPIO35    |               | I/O/Z | General-purpose input/output 35                                                                                                                                                                                                |  |  |  |

| TDI       | 57            | I     | JTAG test data input with internal pullup. TDI is clocked into the selected register (instruction or data) on a rising edge of TCK.                                                                                            |  |  |  |

| GPIO36    |               | I/O/Z | General-purpose input/output 36                                                                                                                                                                                                |  |  |  |

| TMS       | 58            | I     | JTAG test-mode select with internal pullup. This serial control input is clocked into the TAP controller on the rising edge of TCK.                                                                                            |  |  |  |

| GPIO37    |               | I/O/Z | General-purpose input/output 37                                                                                                                                                                                                |  |  |  |

| TDO       | 56            | O/Z   | JTAG scan out, test data output. The contents of the selected register (instruction or data) are shifted out of TDO on the falling edge of TCK (8 mA drive).                                                                   |  |  |  |

| GPIO38    |               | I/O/Z | General-purpose input/output 38                                                                                                                                                                                                |  |  |  |

| XCLKIN    | 54            | I     | External Oscillator Input. The path from this pin to the clock block is not gated by the mux function of this pin. Care must be taken to not enable this path for clocking if this path is being used for the other functions. |  |  |  |

| TCK       |               | 1     | JTAG test clock with internal pullup                                                                                                                                                                                           |  |  |  |

| GPIO39    | 53            | I/O/Z | General-purpose input/output 39                                                                                                                                                                                                |  |  |  |

# 4.2 Pin Multiplexing

Table 4-2. GPIOA MUX<sup>(1)</sup> (2)

|                          | DEFAULT AT RESET<br>PRIMARY I/O<br>FUNCTION | PERIPHERAL<br>SELECTION 1 | PERIPHERAL<br>SELECTION 2 | PERIPHERAL<br>SELECTION 3 |

|--------------------------|---------------------------------------------|---------------------------|---------------------------|---------------------------|

| GPAMUX1 REGISTER<br>BITS | (GPAMUX1 BITS = 00)                         | (GPAMUX1 BITS = 01)       | (GPAMUX1 BITS = 10)       | (GPAMUX1 BITS = 11)       |

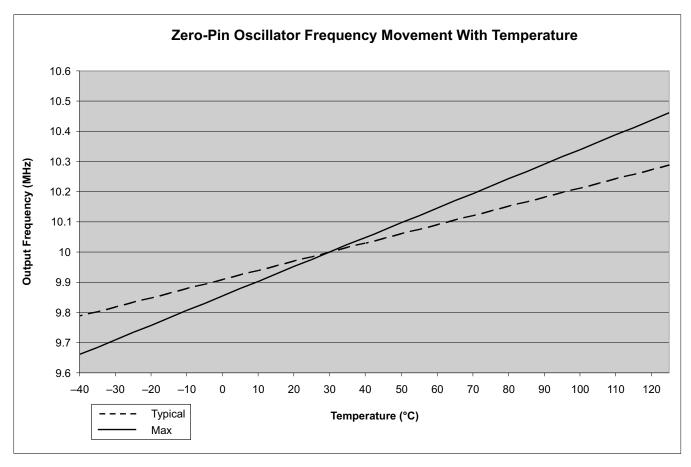

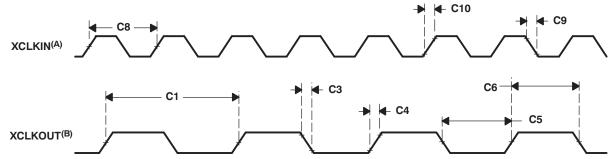

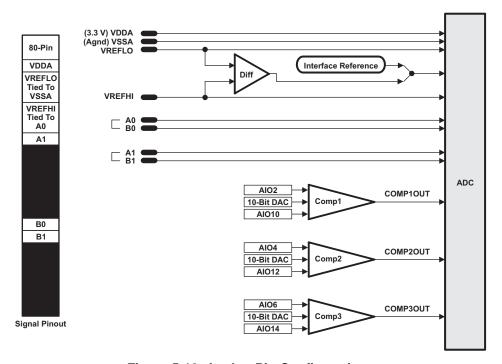

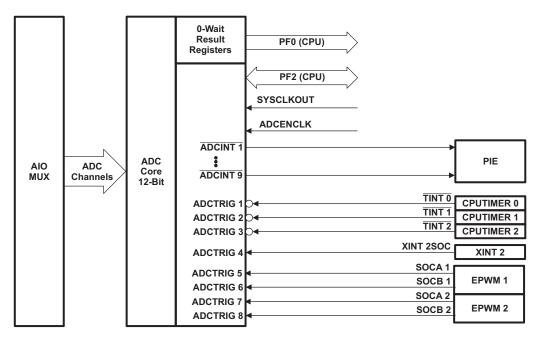

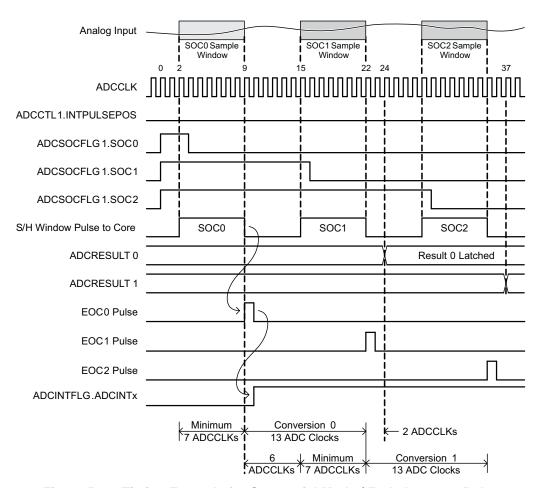

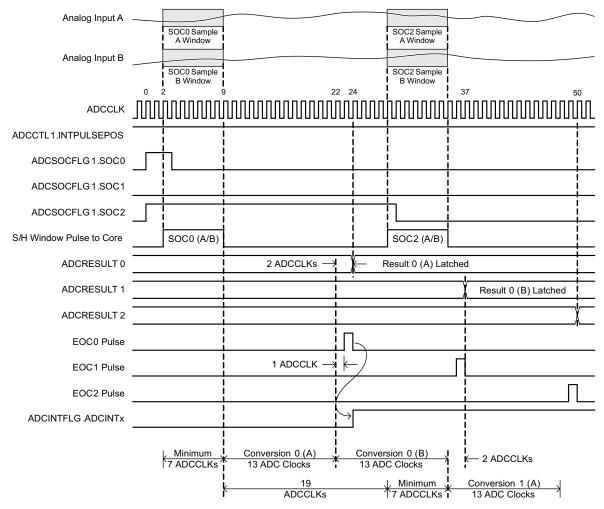

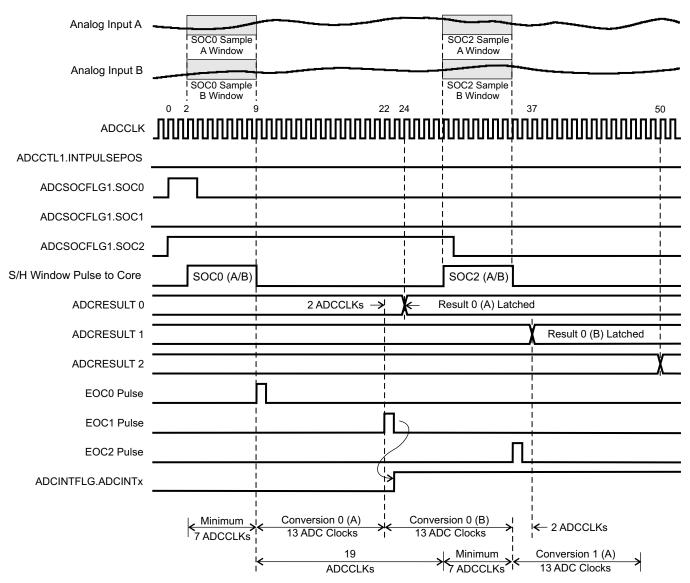

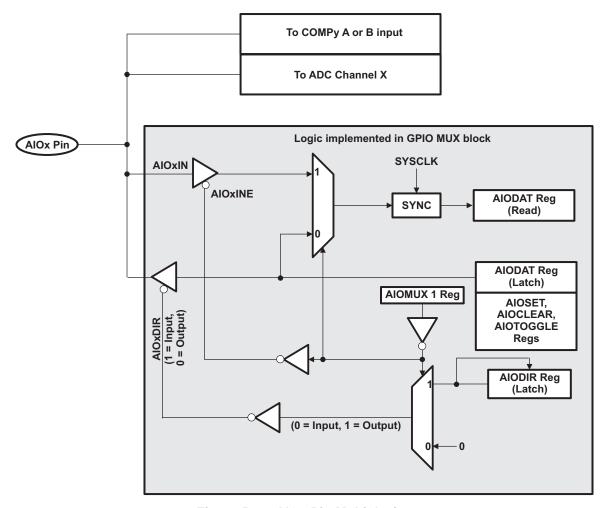

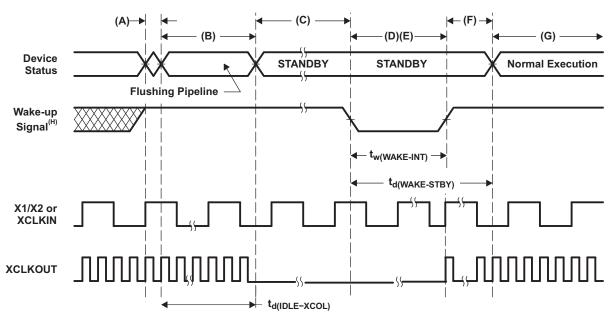

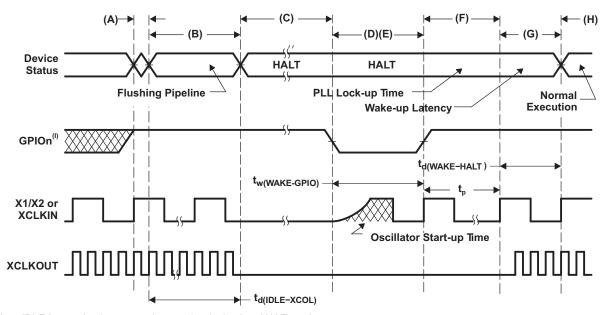

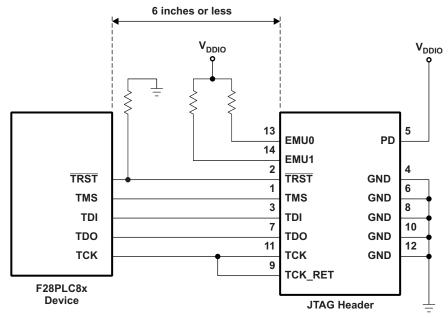

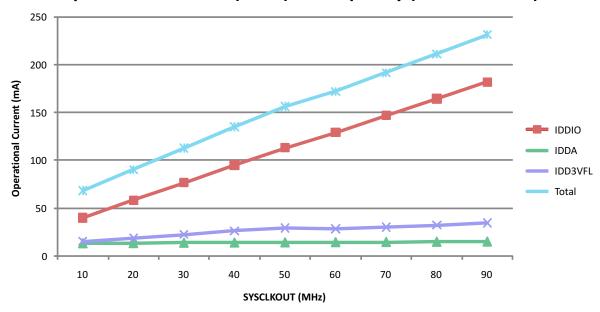

| 1-0                      | GPIO0                                       | EPWM1A (O)                | Reserved                  | Reserved                  |