# SIEMENS

## ICs for Communications

ISDN Echocancellation Circuit

IEC-Q

PEB 2091 Version 5.3

PEF 2091 Version 5.3

Delta Sheet 09.98

DS 1

**PEB/F 2091****Revision History:****Original Version: 09.98**

Previous Version:

| Point<br>(in previous<br>Version) | Point<br>(in new<br>Version) | Subjects (major changes since last revision) |

|-----------------------------------|------------------------------|----------------------------------------------|

|                                   |                              |                                              |

IOM®, IOM®-1, IOM®-2, SICOFI®, SICOFI®-2, SICOFI®-4, SICOFI®-4µC, SLICOFI®, ARCOFI®, ARCOFI®-BA, ARCOFI®-SP, EPIC®, EPIC®-S, ELIC®, IPAT®, ITAC®, ISAC®, ISAC®-S TE, ISAC®-P, ISAC®-P TE, IDEC®, SICAT®, OCTAT®, QUAT®, QUAT®-S are registered trademarks of Siemens AG.

MUSAC™-A, FALC™54, IWE™, SARE™, UTPT™, ASM™, ASP™, DigiTape™ are trademarks of Siemens AG.

For questions on technology, delivery and prices please contact the Semiconductor Group Offices in Germany or the Siemens Companies and Representatives worldwide: see our webpage at <http://www.siemens.de/semiconductor/communication>.

**Edition 09.98**

**Published by Siemens AG,

HL SP,

Balanstraße 73,

81541 München**

© Siemens AG 3.9.98.

All Rights Reserved.

**Attention please!**

As far as patents or other rights of third parties are concerned, liability is only assumed for components, not for applications, processes and circuits implemented within components or assemblies.

The information describes the type of component and shall not be considered as assured characteristics.

Terms of delivery and rights to change design reserved.

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Siemens Office, Semiconductor Group.

Siemens AG is an approved CECC manufacturer.

**Packing**

Please use the recycling operators known to you. We can also help you – get in touch with your nearest sales office. By agreement we will take packing material back, if it is sorted. You must bear the costs of transport.

For packing material that is returned to us unsorted or which we are not obliged to accept, we shall have to invoice you for any costs incurred.

**Components used in life-support devices or systems must be expressly authorized for such purpose!**

Critical components<sup>1</sup> of the Semiconductor Group of Siemens AG, may only be used in life-support devices or systems<sup>2</sup> with the express written approval of the Semiconductor Group of Siemens AG.

- 1 A critical component is a component used in a life-support device or system whose failure can reasonably be expected to cause the failure of that life-support device or system, or to affect its safety or effectiveness of that device or system.

- 2 Life support devices or systems are intended (a) to be implanted in the human body, or (b) to support and/or maintain and sustain human life. If they fail, it is reasonable to assume that the health of the user may be endangered.

---

|          | <b>Table of Contents</b>                                  | <b>Page</b> |

|----------|-----------------------------------------------------------|-------------|

| <b>1</b> | <b>Overview</b> .....                                     | <b>7</b>    |

| 1.1      | Features .....                                            | 8           |

| 1.2      | Pin Configuration .....                                   | 9           |

| 1.3      | Pin Definitions and Functions .....                       | 10          |

| 1.3.1    | Pin Definition in Stand Alone Mode .....                  | 10          |

| 1.3.1.1  | Mode Selection Pins .....                                 | 10          |

| 1.3.1.2  | Power Supply Pins .....                                   | 11          |

| 1.3.1.3  | IOM®-2 Pins .....                                         | 11          |

| 1.3.1.4  | IOM®-2 Control Pins .....                                 | 12          |

| 1.3.1.5  | U-Interface Pins .....                                    | 12          |

| 1.3.1.6  | Power Controller Pins .....                               | 13          |

| 1.3.1.7  | Clocks .....                                              | 14          |

| 1.3.1.8  | Miscellaneous Pins .....                                  | 15          |

| 1.3.1.9  | Test Pins .....                                           | 16          |

| 1.3.2    | Pin Definition in Microprocessor Mode .....               | 17          |

| 1.3.2.1  | Mode Selection Pins .....                                 | 17          |

| 1.3.2.2  | Data, Address and µP Selection Pins .....                 | 17          |

| 1.3.2.3  | µP Control Pins .....                                     | 19          |

| 1.3.2.4  | Power Supply Pins .....                                   | 20          |

| 1.3.2.5  | IOM®-2 Pins .....                                         | 21          |

| 1.3.2.6  | U-Interface Pins .....                                    | 21          |

| 1.3.2.7  | Power Controller Pins .....                               | 22          |

| 1.3.2.8  | Clocks .....                                              | 22          |

| 1.3.2.9  | Miscellaneous Pins .....                                  | 23          |

| 1.3.2.10 | Test Pin .....                                            | 24          |

| 1.4      | Microprocessor Bus Interface (Overview) .....             | 25          |

| 1.5      | System Integration .....                                  | 26          |

| 1.5.1    | Repeater .....                                            | 26          |

| 1.5.2    | Wireless Local Loop .....                                 | 27          |

| 1.5.3    | Dual Mode U and S Terminals and PC Cards .....            | 28          |

| <b>2</b> | <b>Functional Description</b> .....                       | <b>29</b>   |

| 2.1      | Control of Single Bits Indications .....                  | 29          |

| 2.2      | Undervoltage Detection .....                              | 33          |

| 2.3      | Power On Reset (POR) .....                                | 34          |

| 2.4      | Upstream Wake-Up Indication in the LT Repeater Mode ..... | 35          |

| 2.5      | Master Clock on Pin CLS in NT Repeater Mode .....         | 36          |

| 2.6      | IOM®-2 Clock Disable .....                                | 37          |

| 2.7      | Superframe Marker Enable in µP Mode .....                 | 38          |

---

| <b>Table of Contents</b>                                                 | <b>Page</b> |

|--------------------------------------------------------------------------|-------------|

| 2.8 Activation in the $\mu$ P-NT Mode .....                              | 39          |

| 2.9 Selectable Polarity of S/G Bit .....                                 | 40          |

| 2.10 Indication of S/G Bit Status on Pin SG .....                        | 47          |

| 2.11 Activation Attempt Initiated by NT in NT-Auto Mode .....            | 47          |

| 2.12 Schmitt Trigger in Reset Path .....                                 | 48          |

| <b>3 Cleared Errata .....</b>                                            | <b>49</b>   |

| 3.1 Improved: Higher IOM Jitter in NT Mode Reduced .....                 | 49          |

| 3.2 Undervoltage Detection .....                                         | 49          |

| 3.3 Cleared: Bit Errors on the U-Interface in LT Burst Mode .....        | 49          |

| 3.4 Dropped: Monitor Channel Receive Constraints .....                   | 49          |

| 3.5 Data Propagation Time from the LT-IOM to the NT-IOM .....            | 49          |

| 3.6 Cleared: Bit Errors and Corrupted Single Pulses in LT Modes .....    | 50          |

| 3.7 Cleared: Warm Start Time Requirement not Met in LT Mode .....        | 50          |

| 3.8 Constant Propagation Delay in Wireless Local Loop Applications ..... | 50          |

| 3.9 Activation in NT Mode by $\mu$ C .....                               | 50          |

| <b>4 Register Description .....</b>                                      | <b>51</b>   |

| 4.1 ADF-Register .....                                                   | 51          |

| 4.2 ADF2-Register .....                                                  | 52          |

| 4.3 CIWU-Register .....                                                  | 53          |

| <b>5 Electrical Characteristics .....</b>                                | <b>54</b>   |

| 5.1 Power Consumption .....                                              | 54          |

| 5.2 DC Characteristics .....                                             | 54          |

| 5.3 AC Characteristics .....                                             | 55          |

| 5.3.1 Microprocessor Interface Timing in Parallel Mode .....             | 55          |

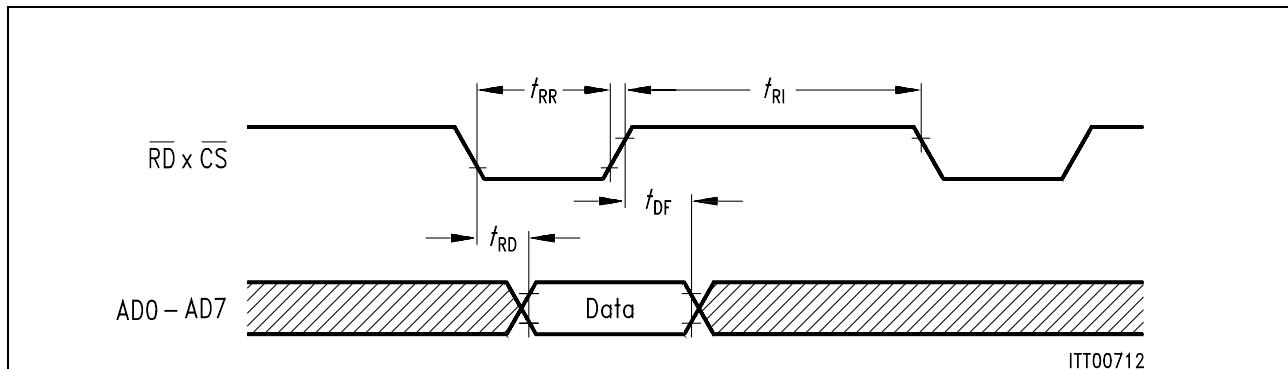

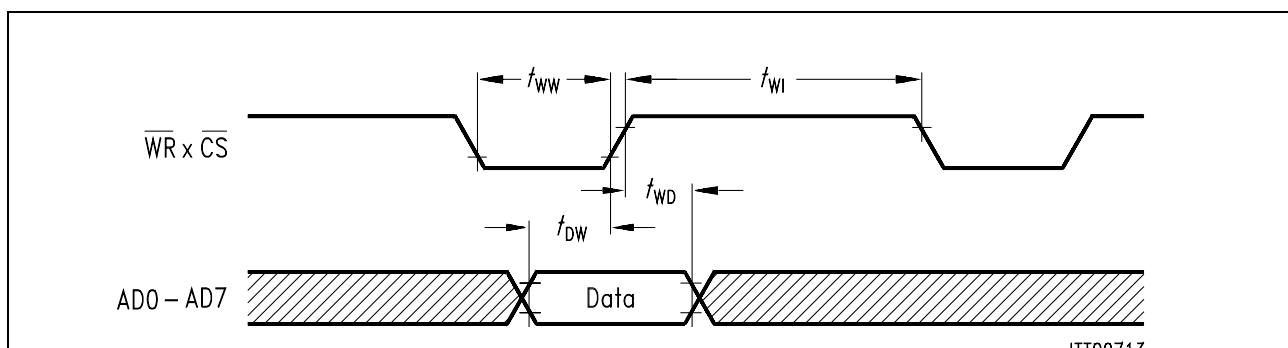

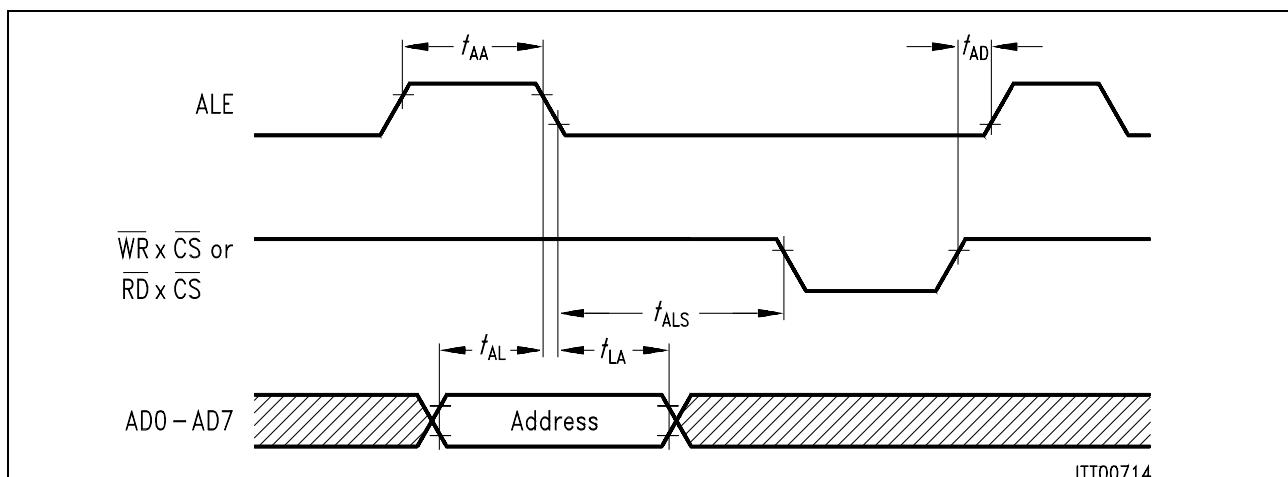

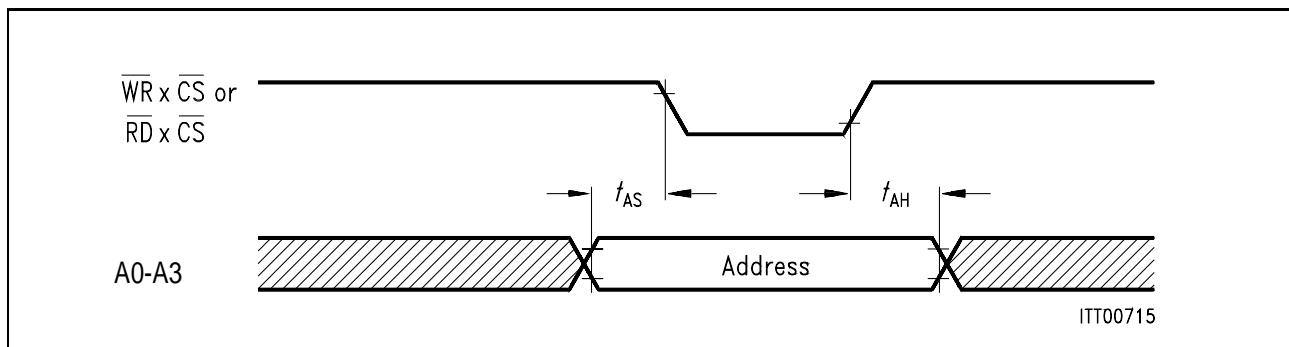

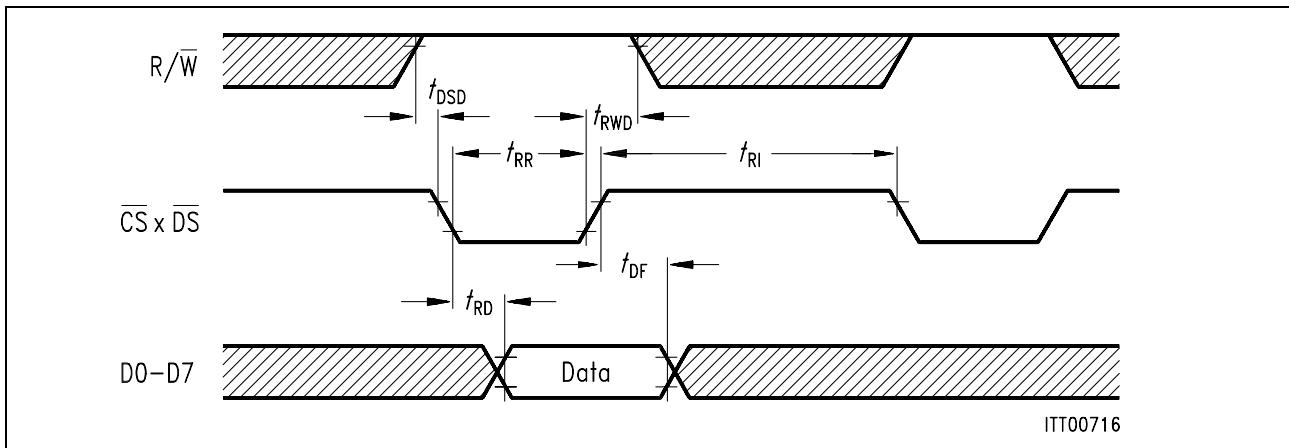

| 5.3.1.1 Siemens/Intel Bus Mode .....                                     | 56          |

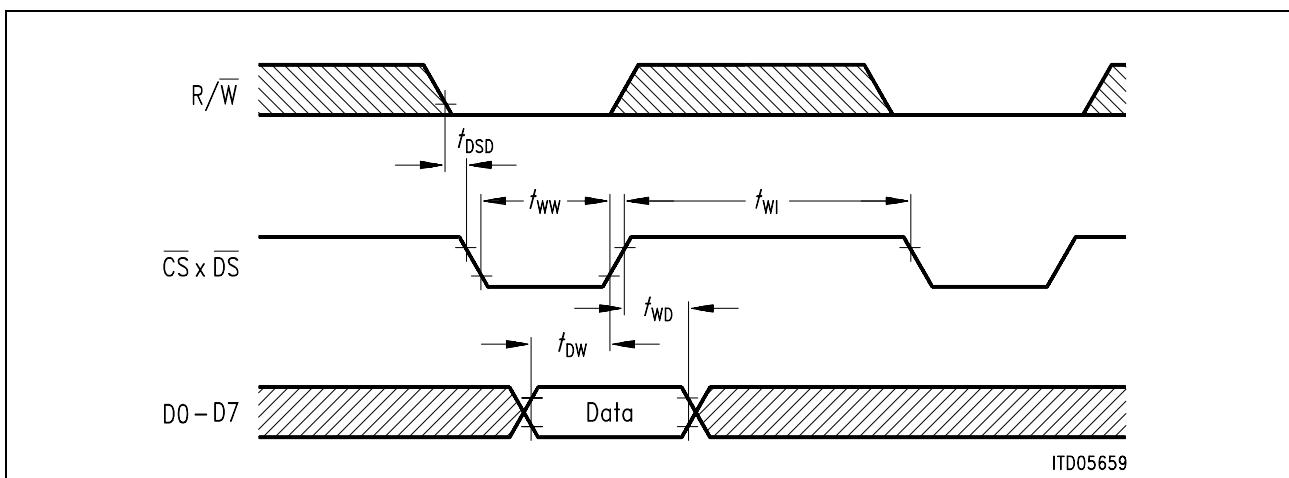

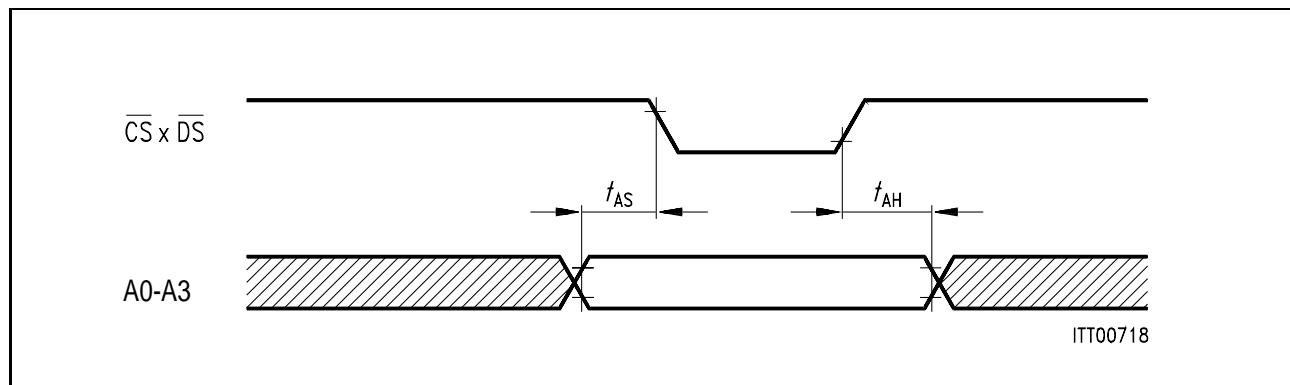

| 5.3.1.2 Motorola Bus Mode .....                                          | 57          |

| 5.3.1.3 Timing Values of the $\mu$ P Interface in Parallel Mode .....    | 58          |

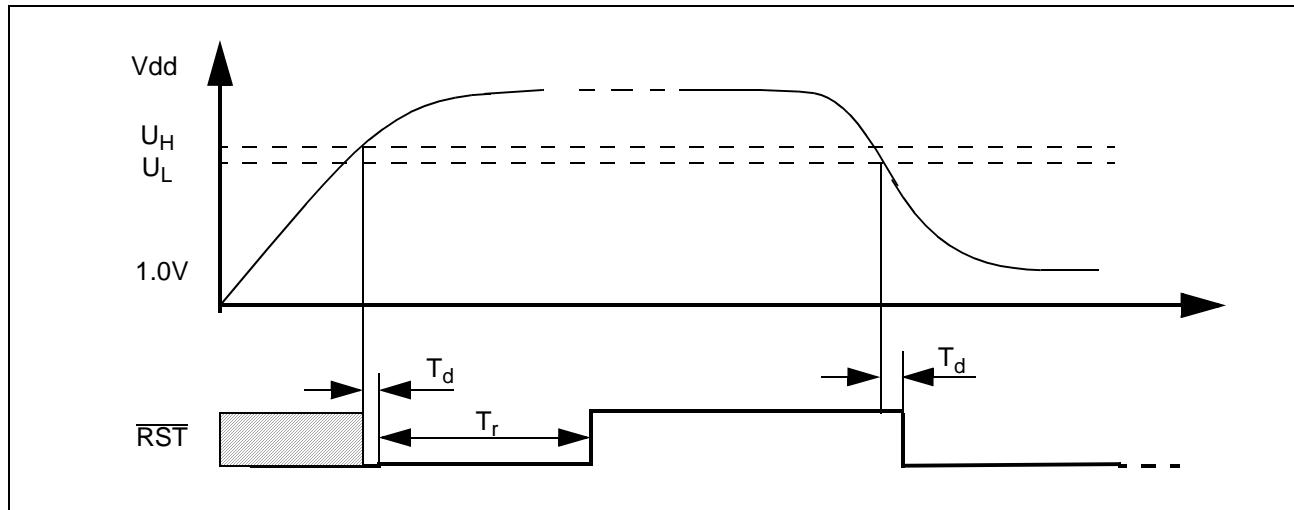

| 5.3.2 Undervoltage Detection Timing .....                                | 59          |

| 5.3.3 Timing Properties of CLS in NT Repeater Mode .....                 | 60          |

| 5.3.4 Timing Properties of Pin SG in TE Mode .....                       | 61          |

| <b>6 Package Outlines .....</b>                                          | <b>62</b>   |

---

| <b>List of Figures</b>                                                              | <b>Page</b> |

|-------------------------------------------------------------------------------------|-------------|

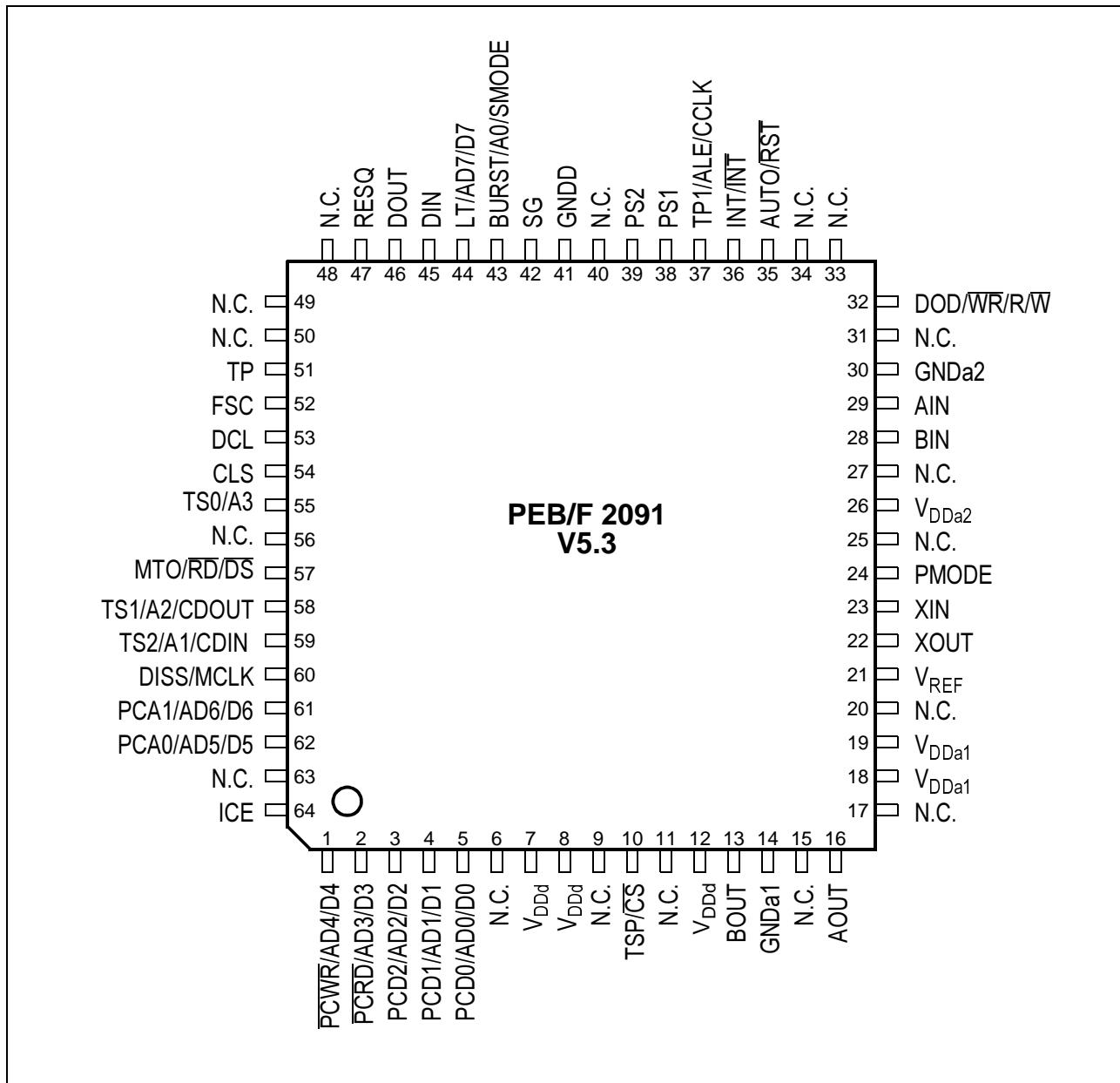

| Figure 1: Pin Configuration for M-QFP-64 and T-QFP-64 Packages (top view) . . . . . | 9           |

| Figure 2: Architecture of Repeater Application . . . . .                            | 26          |

| Figure 3: Architecture of the Wireless Local Loop Base Station . . . . .            | 27          |

| Figure 4: Dual Mode PC Adapter Card . . . . .                                       | 28          |

| Figure 5: UVD Control of Pin RST . . . . .                                          | 34          |

| Figure 6: Wake Up Indication in Repeater Power Down . . . . .                       | 36          |

| Figure 7: DIN Control via CIWU:SPU in NT $\mu$ P Mode . . . . .                     | 39          |

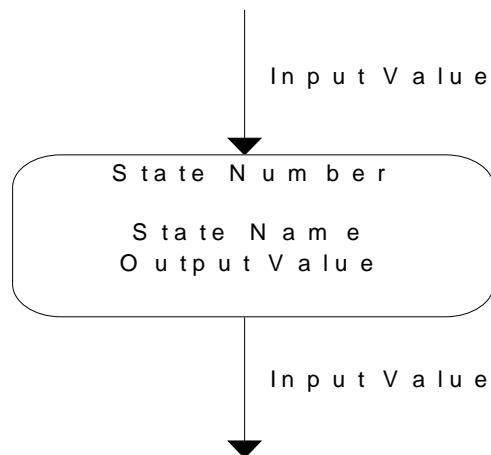

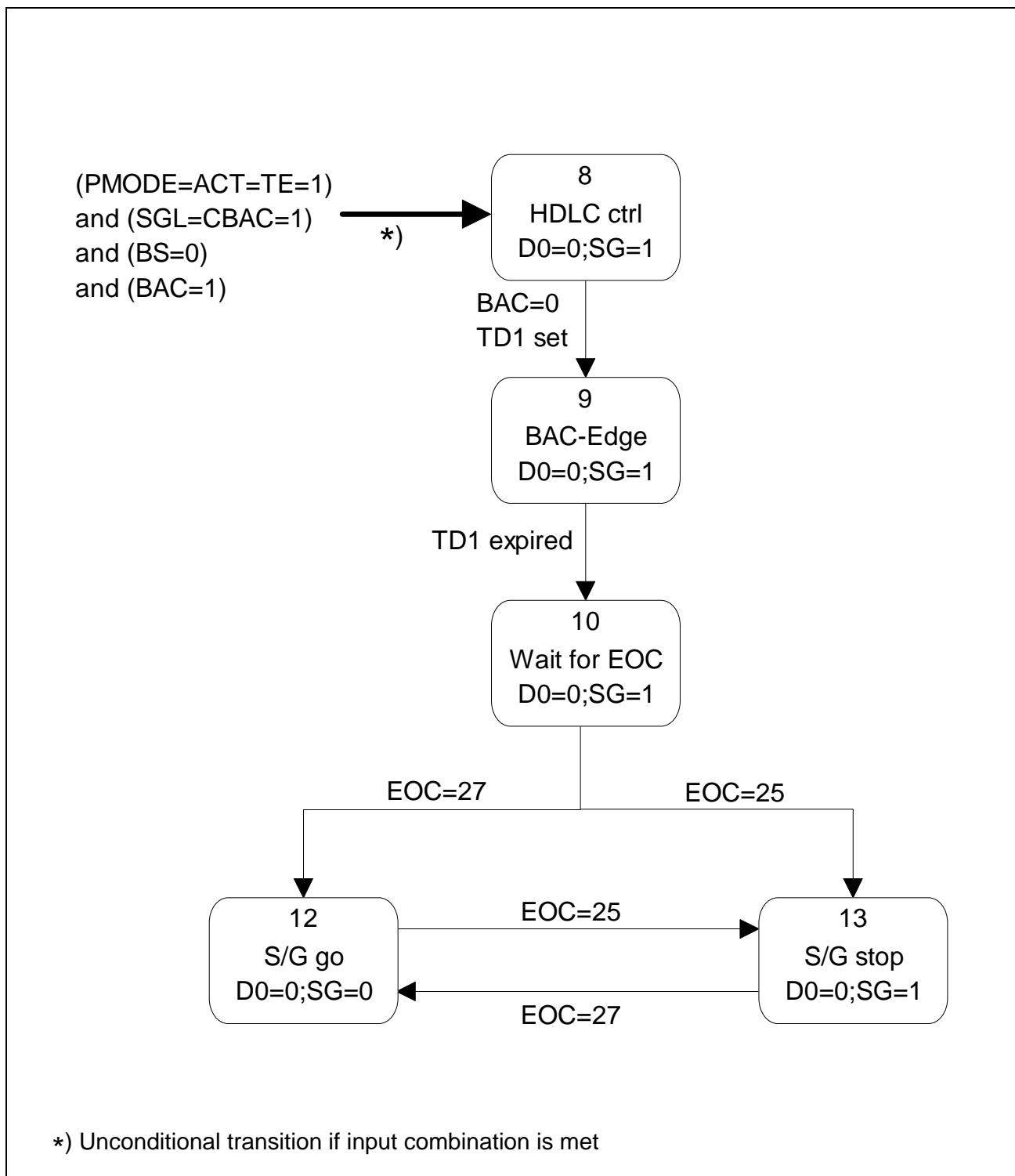

| Figure 8: State Machine Notation for S/G Bit Control . . . . .                      | 42          |

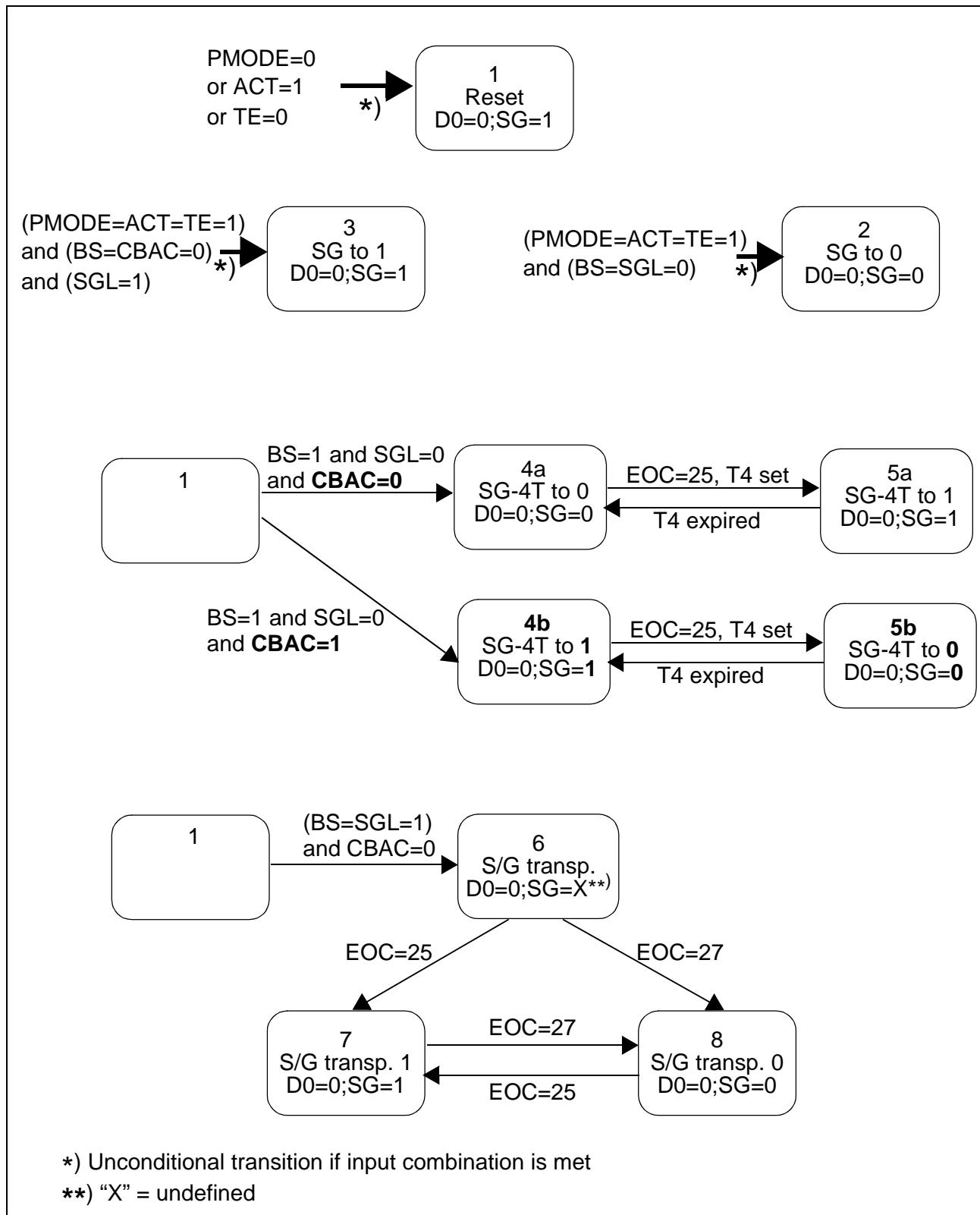

| Figure 9: State Machine for S/G Bit Control (part 1) . . . . .                      | 43          |

| Figure 10: State Machine for S/G Bit Control (part 2) . . . . .                     | 44          |

| Figure 11: State Machine for S/G Bit Control (Part 3) . . . . .                     | 45          |

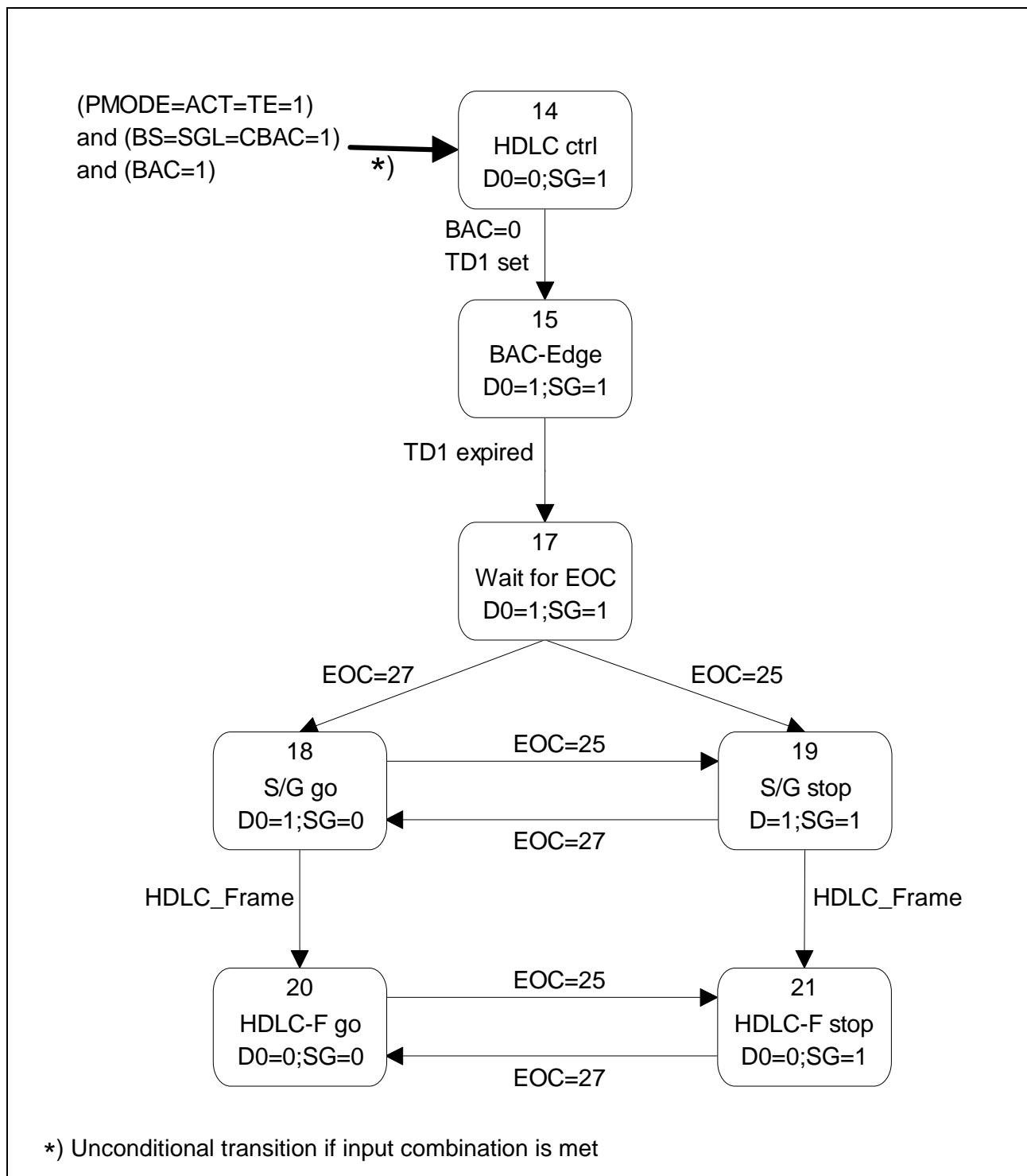

| Figure 12: S/G Bit Status on Pin S/G . . . . .                                      | 47          |

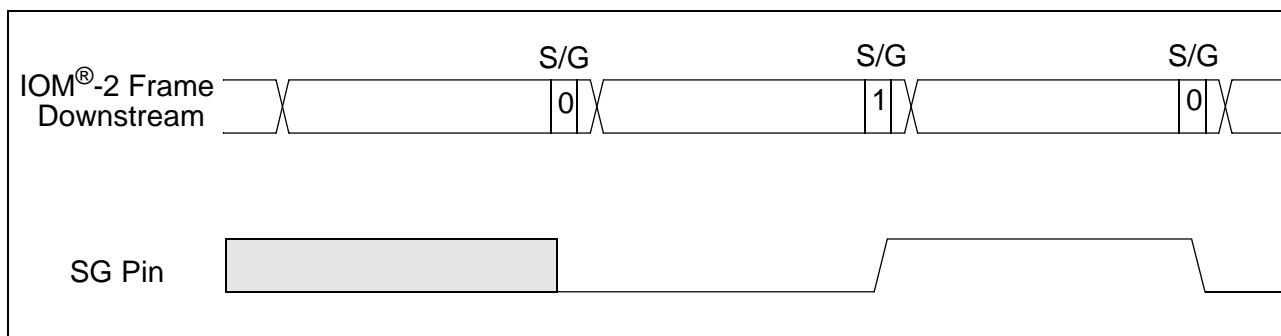

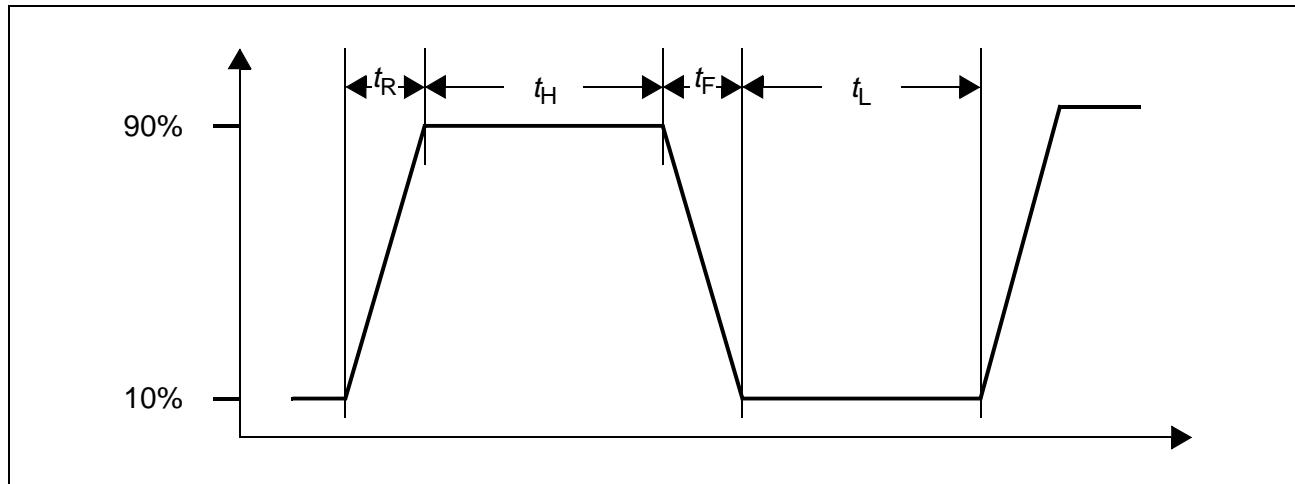

| Figure 13: Input/Output Wave Form for AC Tests . . . . .                            | 55          |

| Figure 14: Siemens/Intel Read Cycle . . . . .                                       | 56          |

| Figure 15: Siemens/Intel Write Cycle . . . . .                                      | 56          |

| Figure 16: Siemens/Intel Multiplexed Address Timing . . . . .                       | 56          |

| Figure 17: Siemens/Intel Non-Multiplexed Address Timing . . . . .                   | 57          |

| Figure 18: Motorola Read Timing . . . . .                                           | 57          |

| Figure 19: Motorola Write Cycle . . . . .                                           | 57          |

| Figure 20: Motorola Non-Multiplexed Address Timing . . . . .                        | 58          |

| Figure 21: UVD Timing Characteristics . . . . .                                     | 59          |

| Figure 22: Dynamic Characteristics of CLS in NT-RP Mode . . . . .                   | 60          |

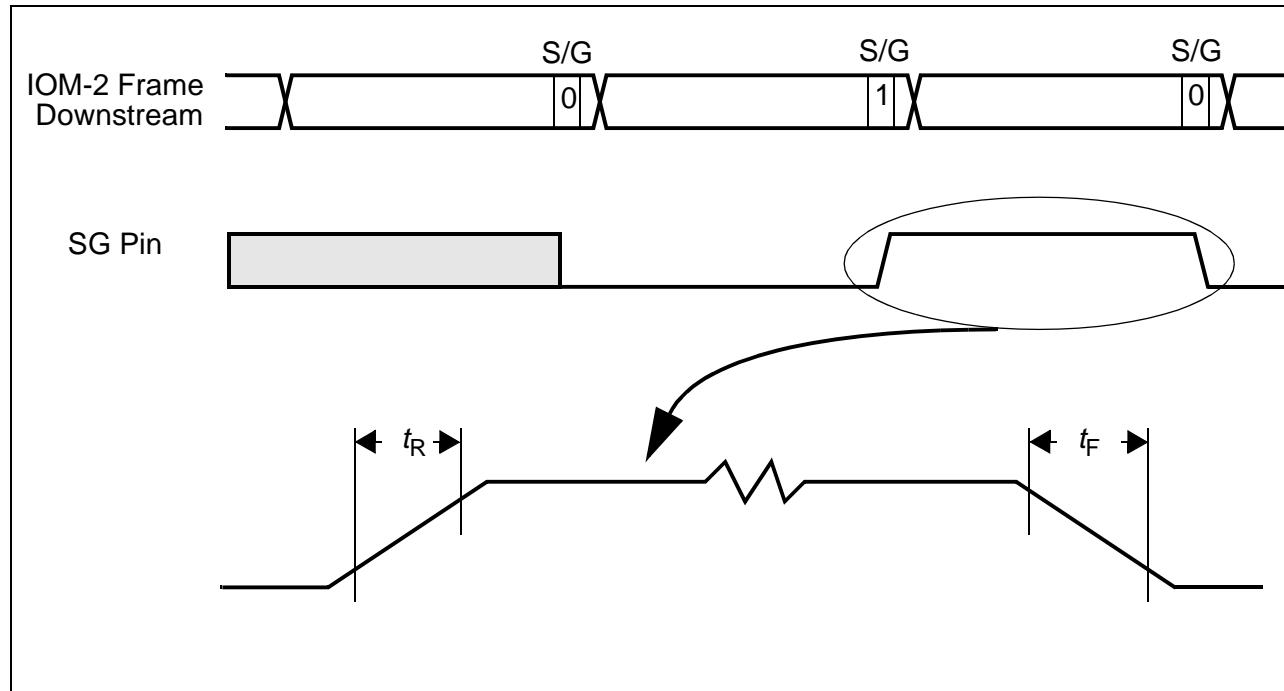

| Figure 23: Dynamic Characteristics of Pin SG . . . . .                              | 61          |

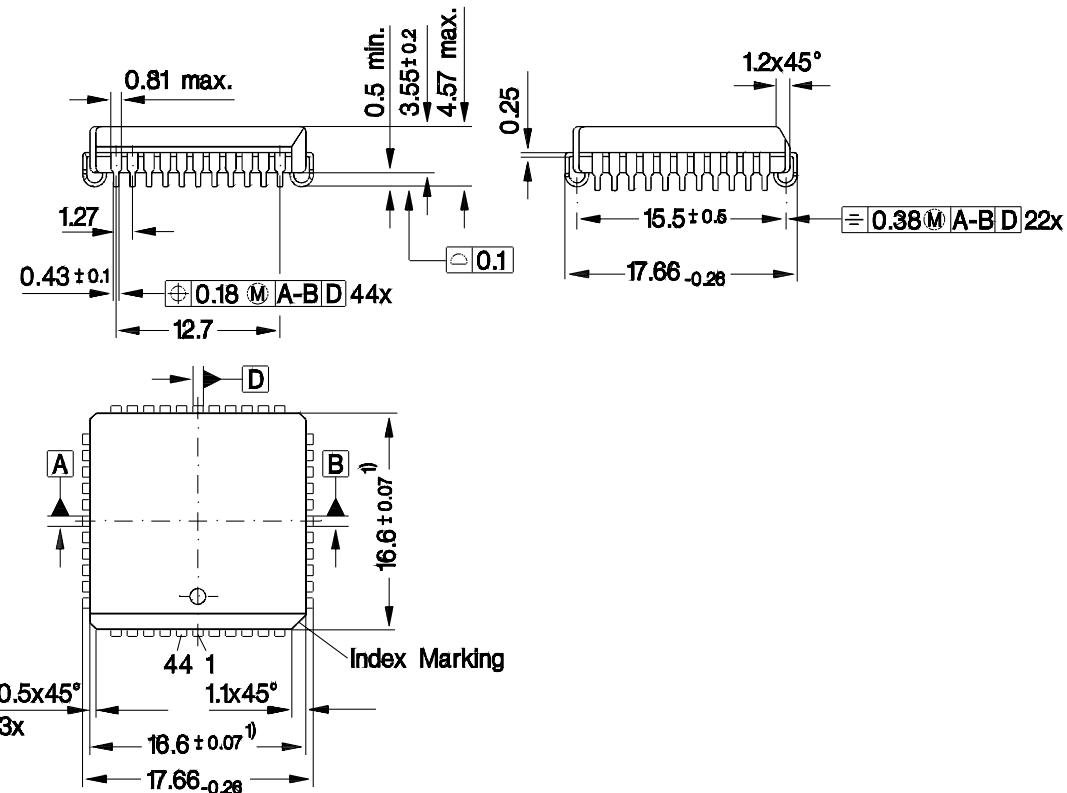

| Figure 24: Package Outline for P-LCC-44 . . . . .                                   | 62          |

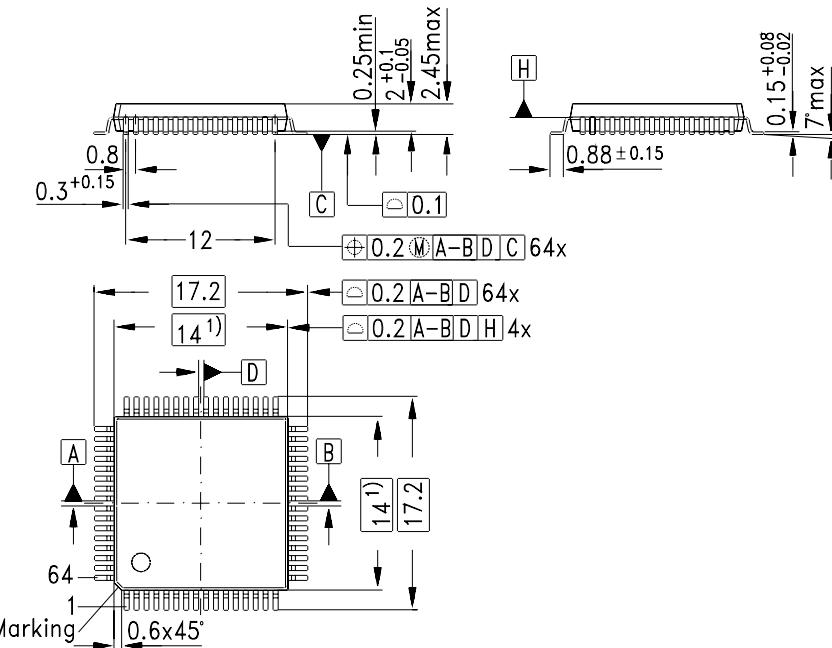

| Figure 25: Package Outline for M-QFP-64 . . . . .                                   | 63          |

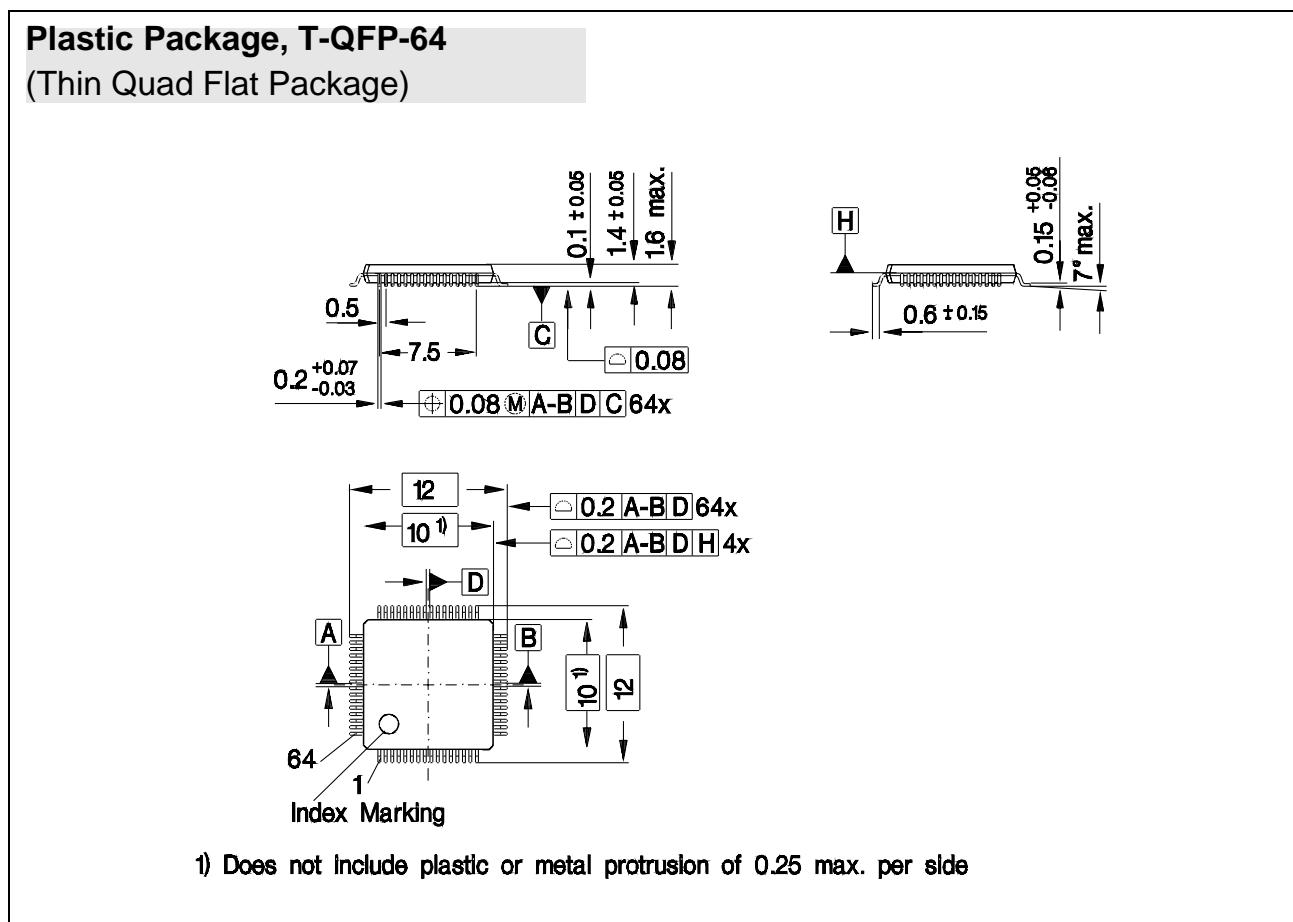

| Figure 26: Package Outline for T-QFP-64 . . . . .                                   | 64          |

---

| <b>List of Tables</b>                                                              | <b>Page</b> |

|------------------------------------------------------------------------------------|-------------|

| Table 1: Microprocessor Bus Interface . . . . .                                    | 25          |

| Table 2: Format of MON-8-Messages . . . . .                                        | 30          |

| Table 3: U-Frame Structure . . . . .                                               | 31          |

| Table 4: Setting Filtering Method for M4 Bits . . . . .                            | 32          |

| Table 5: Setting Filtering Method for Additional Overhead Bits . . . . .           | 32          |

| Table 6: IOM®-2 Clock Disable Overview (Only in the IOM®-2 Master Modes) . . . . . | 38          |

| Table 7: Function of the Register Bits: SWST:BS, SWST:SGL and ADF:CBAC . . . . .   | 40          |

| Table 8: Timing Parameters of UVD Function . . . . .                               | 59          |

| Table 9: Output Characteristics of CLS in NT-RP Mode . . . . .                     | 60          |

| Table 10: Output Characteristics of Pin S/G. . . . .                               | 61          |

## 1 Overview

The PEB/F 2091, IEC-Q Version 5.3 is an optimized version of the IEC-Q which offers

- new features to support applications gaining increasing importance in the marketplace,

- improved electrical behavior and functions, as well as

- full compatibility to previous IEC-Q versions.

### New Features

New features are introduced to support applications such as Wireless Local Loop, U interface repeaters, Dual Mode S and U Terminals and PC cards.

### Improved Characteristics

Electrical Characteristics, such as power consumption, ESD immunity, and dynamic characteristics of the Microprocessor interface have been significantly improved.

Some functions were improved to achieve more flexibility and comply with various customers needs.

All errata with significance to function or service have been cleared.

### Compatibility

Version 5.3 is compatible to all previous versions of PEB/F 2091 and PSB/F 21910 up to Version 5.2. This Delta Sheet refers to Version 5.1 of PEB/F 2091<sup>1)</sup>. It can also serve as Delta Sheet compared with versions 5.2 if points 3.6, page 50, 3.7, page 50 and 5.1, page 54 are ignored. These points have been implemented in Version 5.2. For differences in default settings between Version 5.3 and versions 5.1 and 5.2 see Footnote 2, page 29 and Note, page 38.

---

<sup>1</sup> Related documents: User's Manual 02.95 of the PEB 2091 Version 4.3, Delta Sheet of the PEB/F 2091 Version 4.4 and Delta Sheet of the PEB/F 2091 Version 5.1.

## Version 5.3

**CMOS**

### 1.1 Features

- All functions of PEB/F 2091 and PSB/F 21910

- Compatible with all PEB/F 2091 and PSB/F 21910 versions up to Version 5.2

- Significant reduction in power consumption compared with all versions up to Version 5.1

- Significant improvement in ESD immunity

- Accelerated microprocessor interface in parallel mode

- Reduced Jitter of the IOM®-2 interface in all NT and TE modes

- Internal undervoltage detection control

- User defined control of Single Bits indication and filtering

- A Schmitt Trigger has been introduced in the Hardware Reset path

- Available in three packages: P-LCC-44, M-QFP-64 and T-QFP-64

#### In µP mode:

- User defined enable or disable of the superframe marker function

- Wake-up function in NT Mode without IOM®-2 interface

- Selectable polarity of the S/G bit

- Indication of S/G bit status on pin SG (available only in M-QFP-64 and TQFP-64 packages)

#### In repeater applications:

- Upstream wake-up indication in LT Repeater mode

- 15.36 MHz master clock available on pin CLS in NT Repeater mode

**P-LCC-44**

**M-QFP-64**

**T-QFP-64**

## 1.2 Pin Configuration

Figure 1 Pin Configuration for M-QFP-64 and T-QFP-64 Packages (top view)

## 1.3 Pin Definitions and Functions

The following tables group the pins according to their functions. They include pin name, pin number, type and a brief description of the function. Changes compared with versions 5.1 and 5.2 will be written in bold type style.

### 1.3.1 Pin Definition in Stand Alone Mode

(i.e. PMODE="0" or unconnected)

| Pin No.<br>P-LCC-44 | Pin No.<br>T-QFP64<br>M-QFP64 | Symbol | Input (I)<br>Output (O) | Function |

|---------------------|-------------------------------|--------|-------------------------|----------|

|                     |                               |        |                         |          |

#### 1.3.1.1 Mode Selection Pins

|    |    |       |     |                                                                                                                                                                                                                          |

|----|----|-------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12 | 24 | PMODE | I   | Processor Interface Enable: Setting PMODE to "1" enables the Processor Interface (Multiplexed, demultiplexed and serial modes). Tie to GND or do not connect to select stand alone mode. Internal pull down.             |

| 28 | 47 | RESQ  | I   | <b>Reset:</b> Low active, must be (0) at least for <b>30</b> ns. The reset in the LT and NT-PBX mode will be carried out only after the on IOM®-2 clock have been applied to the IEC-Q. Tie to VDD if not used.          |

| 3  | 10 | TSP   | I   | Single pulse test mode: For activation refer to table 2 on page 48 in the User's Manual 02.95 of the PEB 2091 Version 4.3. When active, alternating 2.5 V pulses are issued in 1.5 ms intervals. Tie to GND if not used. |

| 25 | 44 | LT    | I/O | LT-modes: Selects LT, COT 512/1536, LT-RP (1) and non LT modes NT, TE, NT-PBX, NT-RP (0).                                                                                                                                |

| 24 | 43 | BURST | I   | Selection of burst modes (LT, NT-PBX) with (1) and non-burst modes (NT, TE, COT-512/1536, LT/NT-RP) with (0).                                                                                                            |

## Overview

| Pin No.<br>P-LCC-44 | Pin No.<br>T-QFP64<br>M-QFP64 | Symbol | Input (I)<br>Output (O) | Function                                                                                             |

|---------------------|-------------------------------|--------|-------------------------|------------------------------------------------------------------------------------------------------|

| 33                  | 55                            | TS0    | I                       | Time-slot: IOM®-2 channel selection for burst mode. LSB, active high.                                |

| 35                  | 58                            | TS1    | I/O                     | Time-slot: IOM®-2 channel selection for burst mode. Active high.                                     |

| 36                  | 59                            | TS2    | I                       | Time-slot: IOM®-2 channel selection for burst mode. MSB, active high.                                |

| 18                  | 35                            | AUTO   | I/O                     | Auto mode: Selection between auto- and transparent mode for EOC channel processing. (Automode = (1)) |

## 1.3.1.2 Power Supply Pins

|      |          |            |   |                                                                              |

|------|----------|------------|---|------------------------------------------------------------------------------|

| 1, 2 | 7, 8, 12 | $V_{DDD}$  | I | 5 V ± 5% digital supply voltage                                              |

| 5    | 14       | $GNDA1$    | I | 0 V analog                                                                   |

| 7, 8 | 18, 19   | $V_{DDA1}$ | I | 5 V ± 5% analog supply voltage                                               |

| 9    | 21       | $V_{REF}$  | O | VREF pin to buffer internally generated voltage with capacitor 100 nF vs GND |

| 13   | 26       | $V_{DDA2}$ | I | 5 V ± 5% analog supply voltage                                               |

| 16   | 30       | $GNDA2$    | I | 0 V analog                                                                   |

| 23   | 41       | $GNDD$     | I | 0 V digital                                                                  |

## 1.3.1.3 IOM®-2 Pins

|    |    |     |     |                                                                                                                                                                                                               |

|----|----|-----|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31 | 53 | DCL | I/O | Data clock: Clock range 512 kHz to 4096 kHz, depending on mode.                                                                                                                                               |

| 30 | 52 | FSC | I/O | Frame synchronization clock: The start of the B1-channel in time-slot 0 is marked. FSC = (1) for one DCL-period indicates a superframe marker. FSC = (1) for at least two DCL-periods marks a standard frame. |

| <b>Pin No.<br/>P-LCC-44</b> | <b>Pin No.<br/>T-QFP64<br/>M-QFP64</b> | <b>Symbol</b> | <b>Input (I)<br/>Output (O)</b> | <b>Function</b>                                                                                                                                |

|-----------------------------|----------------------------------------|---------------|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| 26                          | 45                                     | DIN           | I                               | Data in: Input of IOM®-2 data synchronous to DCL-clock. Corresponds to DD (data downstream) in LT and DU (data upstream) in NT-applications.   |

| 27                          | 46                                     | DOUT          | O                               | Data out: Output of IOM®-2 data synchronous to DCL-clock. Corresponds to DD (data downstream) in NT and DU (data upstream) in LT-applications. |

**1.3.1.4 IOM®-2 Control Pins**

|    |    |     |   |                                                                                                                       |

|----|----|-----|---|-----------------------------------------------------------------------------------------------------------------------|

| 17 | 32 | DOD | I | DOUT open drain: Select open drain with DOD = (1) (external pull-up resistor required) and tristate with DOD = (0).   |

| 34 | 57 | MTO | I | Monitor procedure time-out: Disables the internal 6 ms monitor time-out when set to (1). Internal pull-down resistor. |

**1.3.1.5 U-Interface Pins**

|    |    |      |   |                                                     |

|----|----|------|---|-----------------------------------------------------|

| 15 | 29 | AIN  | I | Differential U-Interface input: Connect to hybrid.  |

| 14 | 28 | BIN  | I | Differential U-Interface input: Connect to hybrid.  |

| 6  | 16 | AOUT | O | Differential U-Interface output: Connect to hybrid. |

| 4  | 13 | BOUT | O | Differential U-Interface output: Connect to hybrid. |

| Pin No.<br>P-LCC-44 | Pin No.<br>T-QFP64<br>M-QFP64 | Symbol | Input (I)<br>Output (O) | Function |

|---------------------|-------------------------------|--------|-------------------------|----------|

|                     |                               |        |                         |          |

**1.3.1.6 Power Controller Pins**

|    |    |      |     |                                                                                                                                                                                                  |

|----|----|------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 44 | 5  | PCD0 | I/O | Data bus of power controller interface: LSB. Do not connect if not used. Internal pull-up.                                                                                                       |

| 43 | 4  | PCD1 | I/O | Data bus of power controller interface: Do not connect if not used. Internal pull-up.                                                                                                            |

| 42 | 3  | PCD2 | I/O | Data bus of power controller interface: MSB. Do not connect if not used. Internal pull-up.                                                                                                       |

| 39 | 62 | PCA0 | I/O | Address bus of power controller interface.                                                                                                                                                       |

| 38 | 61 | PCA1 | I/O | Address bus of power controller interface.                                                                                                                                                       |

| 41 | 2  | PCRD | I/O | Power controller interface read request: Low active.                                                                                                                                             |

| 40 | 1  | PCWR | I/O | Power controller interface write request: Low active.                                                                                                                                            |

| 19 | 36 | INT  | I/O | Interrupt: Change-sensitive. After a change of level has been detected the C/I code "INT" will be issued on IOM®-2. Tie to GND during operation.                                                 |

| 37 | 60 | DISS | O   | Disable power supply: Different function in LT and NT modes. LT: the DISS pin is set to (1) with the C/I command "LTD". NT: the DISS pin is set to (1) after receipt of MON-0 LBBD in auto-mode. |

| <b>Pin No.<br/>P-LCC-44</b> | <b>Pin No.<br/>T-QFP64<br/>M-QFP64</b> | <b>Symbol</b> | <b>Input (I)<br/>Output (O)</b> | <b>Function</b>                                                                                                                                                                                                                                                                                         |

|-----------------------------|----------------------------------------|---------------|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 21                          | 38                                     | PS1           | I                               | Power status (primary): Different function in LT- and NT-mode. LT: (1) indicates that the remote power is switched off. (1) on PS1 results in C/I message "HI". Clamp to low if not used. NT: (1) indicates that prim. Power supply is OK. The pin value is identical to the overhead bit "PS1" value.  |

| 22                          | 39                                     | PS2           | I                               | Power status (secondary): Different function in LT- and NT-mode. LT: the current feed value is transmitted (8 bit serially) from a power controller. Read the value with MON-8 "RPFC". NT: (1) indicates that secondary power supply is OK. The pin value is identical to the overhead bit "PS2" value. |

### **1.3.1.7      Clocks**

|    |    |      |   |                                                                                                                                                                                                                                        |

|----|----|------|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10 | 22 | XOUT | O | Crystal OUT: 15.36-MHz crystal is connected. Suitable load capacitances should be connected in parallel. Their value depends on the crystal chosen and board Layout. Leave open if not used.                                           |

| 11 | 23 | XIN  | I | Crystal IN: External 15.36-MHz clock signal or 15.36-MHz crystal is connected. In case a crystal is connected, suitable load capacitances should be connected in parallel. Their value depends on the crystal chosen and board Layout. |

| Pin No.<br>P-LCC-44 | Pin No.<br>T-QFP64<br>M-QFP64 | Symbol | Input (I)<br>Output (O) | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|---------------------|-------------------------------|--------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 32                  | 54                            | CLS    | O                       | <p>Clock Signal: In the NT-Modes this clock is synchronized to U-Interface. Used to synchronize external PLL or to clock S-Interface devices. In the NT-, NT-Auto, COT- and TE-, modes a 7.68 MHz clock is provided on this pin. In the PBX- and in the LT-RP modes a 512 kHz is provided.</p> <p><b>In the NT-RP mode a 15.36 MHz clock is provided (not synchronized to U-Interface).</b></p> <p>In the LT- mode the clock on CLS is not defined.</p> |

### 1.3.1.8 Miscellaneous Pins

|               |    |     |   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|---------------|----|-----|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Not available | 64 | ICE | I | <p><b>IOM®-2 Clocks Enable</b></p> <p>0: no FSC and DCL clocks are output. Clocks may be applied to pins FSC and DCL. However, they are ignored by the IEC-Q. Data on pin DIN is ignored. Pin DOUT is 'floating'.</p> <p>1: Behavior as in former versions of the IEC-Q. The IOM®-2 clocks FSC and DCL are output on the corresponding pins.</p> <p>Due to the 100kOhm pull-up resistor this is the default configuration after reset if pin ICE is not connected.</p> <p>This pin can be overridden by the bit ADF2:ICEC. For more information see "IOM®-2 Clock Disable", page 37.</p> <p><b>Internal pull up.</b></p> |

|---------------|----|-----|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

---

**Overview**

| Pin No.<br>P-LCC-44 | Pin No.<br>T-QFP64<br>M-QFP64 | Symbol | Input (I)<br>Output (O) | Function                                                                                                                                                                                      |

|---------------------|-------------------------------|--------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Not available       | 42                            | SG     | O                       | <b>Stop/Go Bit Status Pin</b><br>Gives the status of the S/G bit in TE mode if the S/G bit control function is being used, see "Indication of S/G Bit Status on Pin SG", page 47 for details. |

**1.3.1.9 Test Pins**

|    |    |     |   |                                                                               |

|----|----|-----|---|-------------------------------------------------------------------------------|

| 29 | 51 | TP  | I | Test pin: Not available to user. Do not connect. Internal pull-down resistor. |

| 20 | 37 | TP1 | I | Test pin: Not available to user. Do not connect. Internal pull-down resistor. |

### 1.3.2 Pin Definition in Microprocessor Mode

(i.e. PMODE="1")

| Pin No.<br>P-LCC-44 | Pin No.<br>T-QFP64<br>M-QFP64 | Symbol | Input (I)<br>Output (O) | Function |

|---------------------|-------------------------------|--------|-------------------------|----------|

|                     |                               |        |                         |          |

#### 1.3.2.1 Mode Selection Pins

|    |    |       |   |                                                                                                                                                                                                                  |

|----|----|-------|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12 | 24 | PMODE | I | Processor Interface Enable: Setting PMODE to "1" enables the Processor Interface (Multiplexed, demultiplexed and serial modes). Tie to GND or do not connect to select stand alone mode. Internal pull down.     |

| 28 | 47 | RESQ  | I | <b>Reset:</b> Low active, must be (0) at least for <b>30 ns</b> . The reset in the LT and NT-PBX mode will be carried out only after the on IOM®-2 clock have been applied to the IEC-Q. Tie to VDD if not used. |

#### 1.3.2.2 Data, Address and µP Selection Pins

|    |    |                        |     |                                                                                                                                             |

|----|----|------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------|

| 24 | 43 | SMODE<br>A0            | I   | Serial mode pin: SMODE = 1 selects serial mode, SMODE = 0 enables the multiplexed mode.<br>Address bus pin (Demultiplexed mode)             |

| 36 | 59 | CDIN<br>A1<br>not used | I   | Controller Data In (Serial mode): CCLK determines the data rate.<br>Address bus pin (Demultiplexed mode).<br>(Multiplexed mode) tie to GND. |

| 35 | 58 | CDOUT                  | I/O | Controller Data Out (Serial mode): CCLK determines the data rate.<br>CDOUT is "high Z" if no data is transmitted.                           |

**Overview**

| <b>Pin No.<br/>P-LCC-44</b> | <b>Pin No.<br/>T-QFP64<br/>M-QFP64</b> | <b>Symbol</b>              | <b>Input (I)<br/>Output (O)</b> | <b>Function</b>                                                                                            |

|-----------------------------|----------------------------------------|----------------------------|---------------------------------|------------------------------------------------------------------------------------------------------------|

| 35                          | 58                                     | A2<br>not used             | I/O                             | Address bus pin (Demultiplexed mode).<br>(Multiplexed mode) tie to GND.                                    |

| 33                          | 55                                     | not used<br>A3<br>not used | I                               | (Serial mode) tie to GND.<br>Address bus pin (Demultiplexed mode).<br>(Multiplexed mode) tie to GND.       |

| 44                          | 5                                      | not used<br>D0<br>AD0      | I/O                             | (Serial mode) tie to GND.<br>Data bus pin (Demultiplexed mode)<br>Address/Data bus pin (Multiplexed mode)  |

| 43                          | 4                                      | not used<br>D1<br>AD1      | I/O                             | (Serial mode) tie to GND.<br>Data bus pin (Demultiplexed mode)<br>Address/Data bus pin (Multiplexed mode)  |

| 42                          | 3                                      | not used<br>D2<br>AD2      | I/O                             | (Serial mode) tie to GND.<br>Data bus pin (Demultiplexed mode)<br>Address/Data bus pin (Multiplexed mode)  |

| 41                          | 2                                      | not used<br>D3<br>AD3      | I/O                             | (Serial mode) tie to GND.<br>Data bus pin (Demultiplexed mode)<br>Address/Data bus pin (Multiplexed mode)  |

| 40                          | 1                                      | not used<br>D4<br>AD4      | I/O                             | (Serial mode) tie to GND.<br>Data bus pin (demultiplexed modes)<br>Address/Data bus pin (Multiplexed mode) |

**Overview**

| <b>Pin No.<br/>P-LCC-44</b> | <b>Pin No.<br/>T-QFP64<br/>M-QFP64</b> | <b>Symbol</b>         | <b>Input (I)<br/>Output (O)</b> | <b>Function</b>                                                                                            |

|-----------------------------|----------------------------------------|-----------------------|---------------------------------|------------------------------------------------------------------------------------------------------------|

| 39                          | 62                                     | not used<br>D5<br>AD5 | I/O                             | (Serial mode) tie to GND.<br>Data bus pin (demultiplexed modes)<br>Address/Data bus pin (Multiplexed mode) |

| 38                          | 61                                     | not used<br>D6<br>AD6 | I/O                             | (Serial mode) tie to GND.<br>Data bus pin (demultiplexed modes)<br>Address/Data bus pin (Multiplexed mode) |

| 25                          | 44                                     | not used<br>D7<br>AD7 | I/O                             | (Serial mode) tie to GND.<br>Data bus pin (demultiplexed modes)<br>Address/Data bus pin (Multiplexed mode) |

**1.3.2.3       $\mu$ P Control Pins**

|    |    |                       |     |                                                                                                                                                                                                                                 |

|----|----|-----------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 19 | 36 | INT                   | I/O | Interrupt line (Multiplexed, demultiplexed and serial modes): Low active.                                                                                                                                                       |

| 3  | 10 | CS                    | I   | Chip select (Multiplexed, demultiplexed and serial modes): Low active.                                                                                                                                                          |

| 17 | 32 | not used<br>WR<br>R/W | I   | (Serial mode) tie to GND.<br>Write (Siemens/Intel multiplexed and demultiplexed modes): indicates a write operation, active low.<br>Read/Write (Motorola demultiplexed mode): indicates a read (high) or write (low) operation. |

**Overview**

| Pin No.<br>P-LCC-44 | Pin No.<br>T-QFP64<br>M-QFP64 | Symbol               | Input (I)<br>Output (O) | Function                                                                                                                                                                                                                                                                                                                                                                                                |

|---------------------|-------------------------------|----------------------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 34                  | 57                            | not used<br>RD<br>DS | I                       | (Serial mode) tie to GND.<br>Read (Siemens/Intel multiplexed and demultiplexed modes): indicates a read operation, active low.<br>Data Strobe (Motorola demultiplexed mode): indicates a data transfer, active low.                                                                                                                                                                                     |

| 20                  | 37                            | CCLK<br>ALE<br>ALE   | I                       | Controller data clock (Serial mode): Shifts data from or to the device.<br>Address Latch Enable (Demultiplexed mode): ALE tied to GND selects the Siemens/Intel type. ALE tied to VDD selects the Motorola type.<br>Address Latch Enable (Multiplexed mode): In the Siemens/Intel $\mu$ P interface modes a high indicates an address on the AD0..3 pins which is latched with the falling edge of ALE. |

**1.3.2.4 Power Supply Pins**

|      |          |            |   |                                                                                   |

|------|----------|------------|---|-----------------------------------------------------------------------------------|

| 1, 2 | 7, 8, 12 | $V_{DDD}$  | I | 5 V $\pm$ 5% digital supply voltage                                               |

| 5    | 14       | $GND_A1$   | I | 0 V analog                                                                        |

| 7, 8 | 18, 19   | $V_{DDA1}$ | I | 5 V $\pm$ 5% analog supply voltage                                                |

| 9    | 21       | $V_{REF}$  | O | $V_{REF}$ pin to buffer internally generated voltage with capacitor 100 nF vs GND |

| 13   | 26       | $V_{DDA2}$ | I | 5 V $\pm$ 5% analog supply voltage                                                |

| 16   | 30       | $GND_A2$   | I | 0 V analog                                                                        |

| 23   | 41       | $GND_D$    | I | 0 V digital                                                                       |

| Pin No.<br>P-LCC-44 | Pin No.<br>T-QFP64<br>M-QFP64 | Symbol | Input (I)<br>Output (O) | Function |

|---------------------|-------------------------------|--------|-------------------------|----------|

|                     |                               |        |                         |          |

**1.3.2.5 IOM®-2 Pins**

|    |    |      |     |                                                                                                                                                                                                               |

|----|----|------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31 | 53 | DCL  | I/O | Data clock: Clock range 512 kHz to 4096 kHz, depending on mode.                                                                                                                                               |

| 30 | 52 | FSC  | I/O | Frame synchronization clock: The start of the B1-channel in time-slot 0 is marked. FSC = (1) for one DCL-period indicates a superframe marker. FSC = (1) for at least two DCL-periods marks a standard frame. |

| 26 | 45 | DIN  | I   | Data in: Input of IOM®-2 data synchronous to DCL-clock. Corresponds to DD (data downstream) in LT and DU (data upstream) in NT-applications.                                                                  |

| 27 | 46 | DOUT | O   | Data out: Output of IOM®-2 data synchronous to DCL-clock. Corresponds to DD (data downstream) in NT and DU (data upstream) in LT-applications.                                                                |

**1.3.2.6 U-Interface Pins**

|    |    |      |   |                                                     |

|----|----|------|---|-----------------------------------------------------|

| 15 | 29 | AIN  | I | Differential U-Interface input: Connect to hybrid.  |

| 14 | 28 | BIN  | I | Differential U-Interface input: Connect to hybrid.  |

| 6  | 16 | AOUT | O | Differential U-Interface output: Connect to hybrid. |

| 4  | 13 | BOUT | O | Differential U-Interface output: Connect to hybrid. |

| Pin No.<br>P-LCC-44 | Pin No.<br>T-QFP64<br>M-QFP64 | Symbol | Input (I)<br>Output (O) | Function |

|---------------------|-------------------------------|--------|-------------------------|----------|

|                     |                               |        |                         |          |

**1.3.2.7 Power Controller Pins**

|    |    |     |   |                                                                                                                                                                                                                                                                                                          |

|----|----|-----|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 21 | 38 | PS1 | I | Power status (primary): Different function in LT- and NT-mode. LT: (1) indicates that the remote power is switched off. (1) on PS1 results in C/I message "HI". Clamp to low if not used. NT: (1) indicates that primary power supply is OK. The pin value is identical to the overhead bit "PS1" value. |

| 22 | 39 | PS2 | I | Power status (secondary): Different function in LT- and NT-mode. LT: the current feed value is transmitted (8 bit serially) from a power controller. Read the value with MON-8 "RPFC". NT: (1) indicates that secondary power supply is OK. The pin value is identical to the overhead bit "PS2" value.  |

**1.3.2.8 Clocks**

|    |    |      |   |                                                                                                                                                                                                                                        |

|----|----|------|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10 | 22 | XOUT | O | Crystal OUT: 15.36-MHz crystal is connected. Suitable load capacitances should be connected in parallel. Their value depends on the crystal chosen and board Layout. Leave open if not used.                                           |

| 11 | 23 | XIN  | I | Crystal IN: External 15.36-MHz clock signal or 15.36-MHz crystal is connected. In case a crystal is connected, suitable load capacitances should be connected in parallel. Their value depends on the crystal chosen and board Layout. |

## Overview

| Pin No.<br>P-LCC-44 | Pin No.<br>T-QFP64<br>M-QFP64 | Symbol | Input (I)<br>Output (O) | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|---------------------|-------------------------------|--------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 32                  | 54                            | CLS    | O                       | <p>Clock Signal: In the NT-Modes this clock is synchronized to U-Interface. Used to synchronize external PLL or to clock S-Interface devices. In the NT-, NT-Auto, COT- and TE-, modes a 7.68 MHz clock is provided on this pin. In the PBX- and in the LT-RP modes a 512 kHz is provided.</p> <p><b>In the NT-RP mode a 15.36 MHz clock is provided (not synchronized to U-Interface).</b></p> <p>In the LT- mode the clock on CLS is not defined.</p> |

| 37                  | 60                            | MCLK   | O                       | Microprocessor clock output (Multiplexed, demultiplexed and serial modes): provided with four programmable clock rates: 7.68 MHz, 3.84 MHz, 1.92 MHz and 0.96 MHz.                                                                                                                                                                                                                                                                                      |

## 1.3.2.9 Miscellaneous Pins

|               |    |     |   |                                                                                                                                                                                                                                                                          |

|---------------|----|-----|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 18            | 35 | RST | O | Reset output (Multiplexed, demultiplexed and serial modes): Low active.                                                                                                                                                                                                  |

| Not available | 42 | SG  | O | <p><b>Stop/Go Bit Status Pin</b><br/> <b>Gives the status of the S/G bit in TE mode if the S/G bit control function is being used, see "Indication of S/G Bit Status on Pin SG", page 47 for details.</b></p> <p><b>In all other modes the SG pin is set to "1".</b></p> |

## Overview

| Pin No.<br>P-LCC-44 | Pin No.<br>T-QFP64<br>M-QFP64 | Symbol | Input (I)<br>Output (O) | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|---------------------|-------------------------------|--------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Not available       | 64                            | ICE    | I                       | <p><b>IOM®-2 Clocks Enable</b></p> <p>0: no FSC and DCL clocks are output. Clocks may be applied to pins FSC and DCL. However, they are ignored by the IEC-Q. Data on pin DIN is ignored. Pin DOUT is 'floating'.</p> <p>1: Behavior as in former versions of the IEC-Q. The IOM®-2 clocks FSC and DCL are output on the corresponding pins.</p> <p>Due to the 100kOhm pull-up resistor this is the default configuration after reset if pin ICE is not connected.</p> <p>This pin can be overridden by the bit ADF2:ICEC. For more information see "IOM®-2 Clock Disable", page 37.</p> <p><b>Internal pull up.</b></p> |

## 1.3.2.10 Test Pin

|    |    |    |   |                                                                               |

|----|----|----|---|-------------------------------------------------------------------------------|

| 29 | 51 | TP | I | Test pin: Not available to user. Do not connect. Internal pull-down resistor. |

|----|----|----|---|-------------------------------------------------------------------------------|

**1.4 Microprocessor Bus Interface (Overview)**

The table below gives an overview of the different microprocessor bus modes.

**Table 1 Microprocessor Bus Interface**

| <b>Pin Number</b> |                       | <b>Stand Alone Mode</b> | <b>Symbol in Processor Mode</b> |                             |                       |         |

|-------------------|-----------------------|-------------------------|---------------------------------|-----------------------------|-----------------------|---------|

| P-LCC-44          | T-QFP-64 and M-QFP-64 |                         | Siemens/ Intel multiplexed      | Siemens/ Intel demultiplex. | Motorola demultiplex. | Serial  |

| 12                | 24                    | PMODE = 0               | PMODE = 1                       |                             |                       |         |

| 44                | 5                     | PCD0                    | AD0                             | D0                          | D0                    | n.c.    |

| 43                | 4                     | PCD1                    | AD1                             | D1                          | D1                    | n.c.    |

| 42                | 3                     | PCD2                    | AD2                             | D2                          | D2                    | n.c.    |

| 41                | 2                     | PCRD                    | AD3                             | D3                          | D3                    | n.c.    |

| 40                | 1                     | PCWR                    | AD4                             | D4                          | D4                    | n.c.    |

| 39                | 62                    | PCA0                    | AD5                             | D5                          | D5                    | n.c.    |

| 38                | 61                    | PCA1                    | AD6                             | D6                          | D6                    | n.c.    |

| 25                | 44                    | LT                      | AD7                             | D7                          | D7                    | n.c.    |

| 19                | 36                    | INT                     | INT                             | INT                         | INT                   | INT     |

| 24                | 43                    | BURST                   | SMODE=0                         | A0                          | A0                    | SMODE=1 |

| 36                | 59                    | TS2                     | n.c.                            | A1                          | A1                    | CDIN    |

| 35                | 58                    | TS1                     | n.c.                            | A2                          | A2                    | CDOUT   |

| 33                | 55                    | TS0                     | n.c.                            | A3                          | A3                    | n.c.    |

| 20                | 37                    | TP1                     | ALE                             | ALE=0                       | ALE=1                 | CCLK    |

| 34                | 57                    | MTO                     | RD                              | RD                          | DS                    | n.c.    |

| 17                | 32                    | DOD                     | WR                              | WR                          | R/W                   | n.c.    |

| 3                 | 10                    | TSP                     | CS                              | CS                          | CS                    | CS      |

| 37                | 60                    | DISS                    | MCLK                            |                             |                       |         |

| 18                | 35                    | AUTO                    | RST                             |                             |                       |         |

## 1.5 System Integration

The PEB/F 2091 can be combined with a variety of other devices to fit in numerous applications. Some of them are described in the User's Manual 02.95 of the PEB 2091 Version 4.3, page 35 ff. Version 5.3, with its new features, offers various possibilities to achieve significant cost and power reduction in some applications, as well as introducing new applications. Some of these possibilities are sketched briefly below.

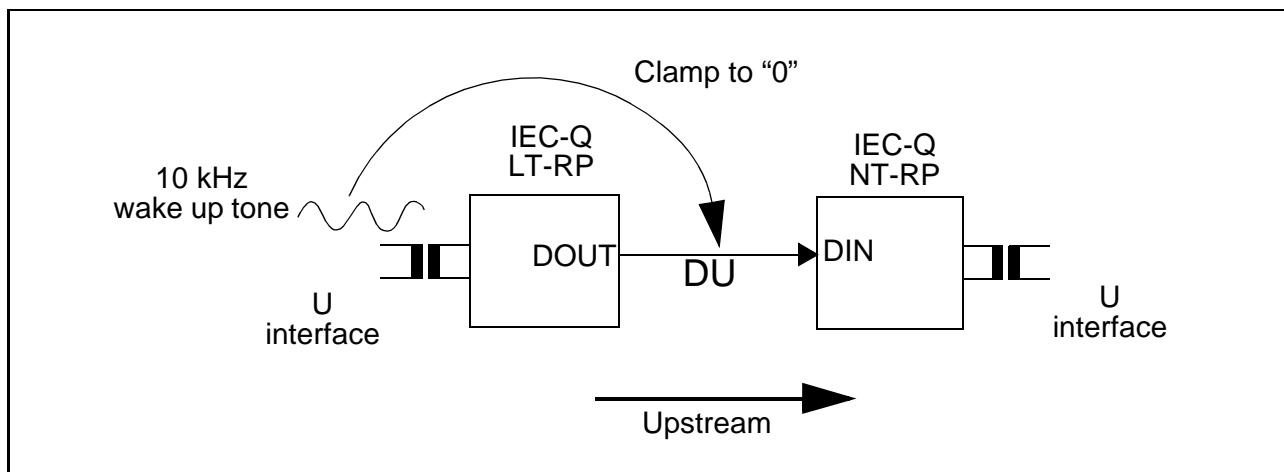

### 1.5.1 Repeater

New repeater features have been implemented in this version:

- A wake-up tone from downstream is indicated directly on DOUT. No special circuit for wake tone detection is needed any more. See "Upstream Wake-Up Indication in the LT Repeater Mode", page 35.

- A master clock is delivered on pin CLS in the NT Repeater mode. This clock will be available in both power-up and power-down states. This allows reducing power consumption to a minimum in power down. Furthermore, PLL architecture can be simplified. See "Master Clock on Pin CLS in NT Repeater Mode", page 36.

- The undervoltage detection function can be used to detect power supply level drops on the board and reduce external reset circuitry. See "Undervoltage Detection", page 33.

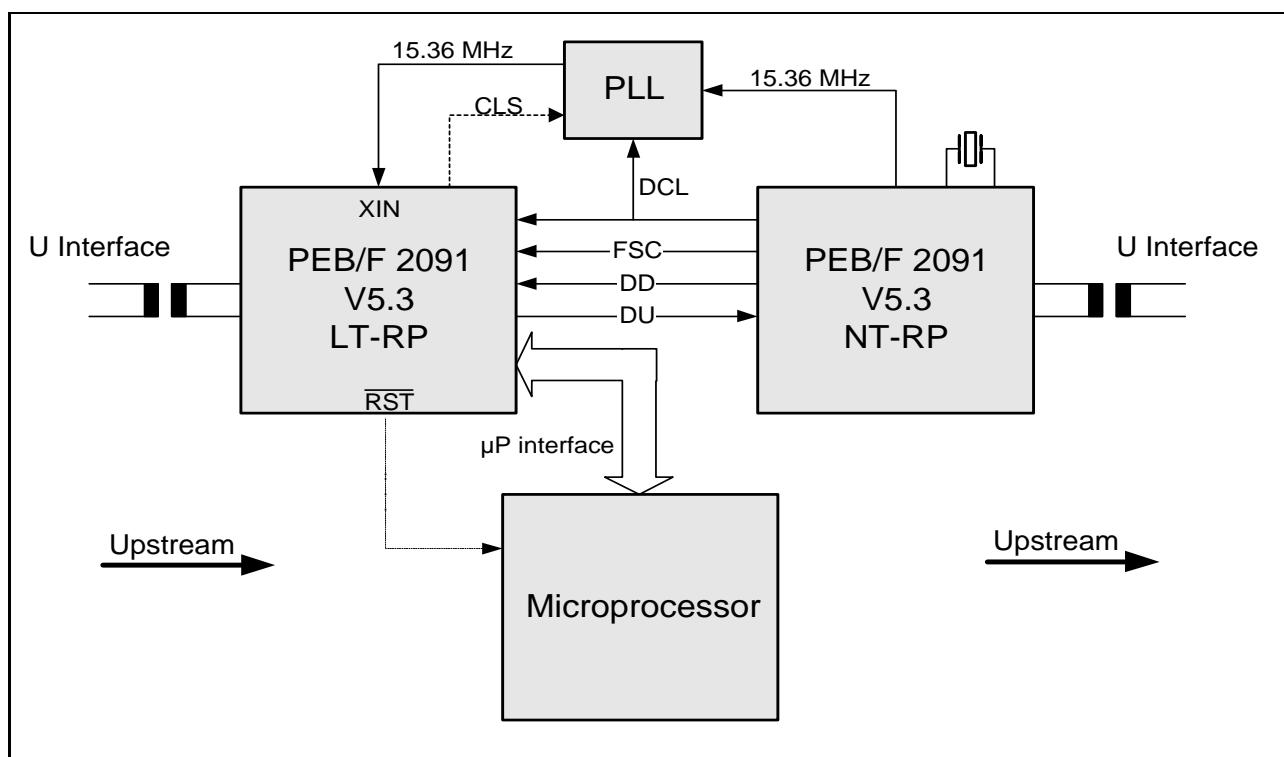

**Figure 2 Architecture of Repeater Application**

### 1.5.2 Wireless Local Loop

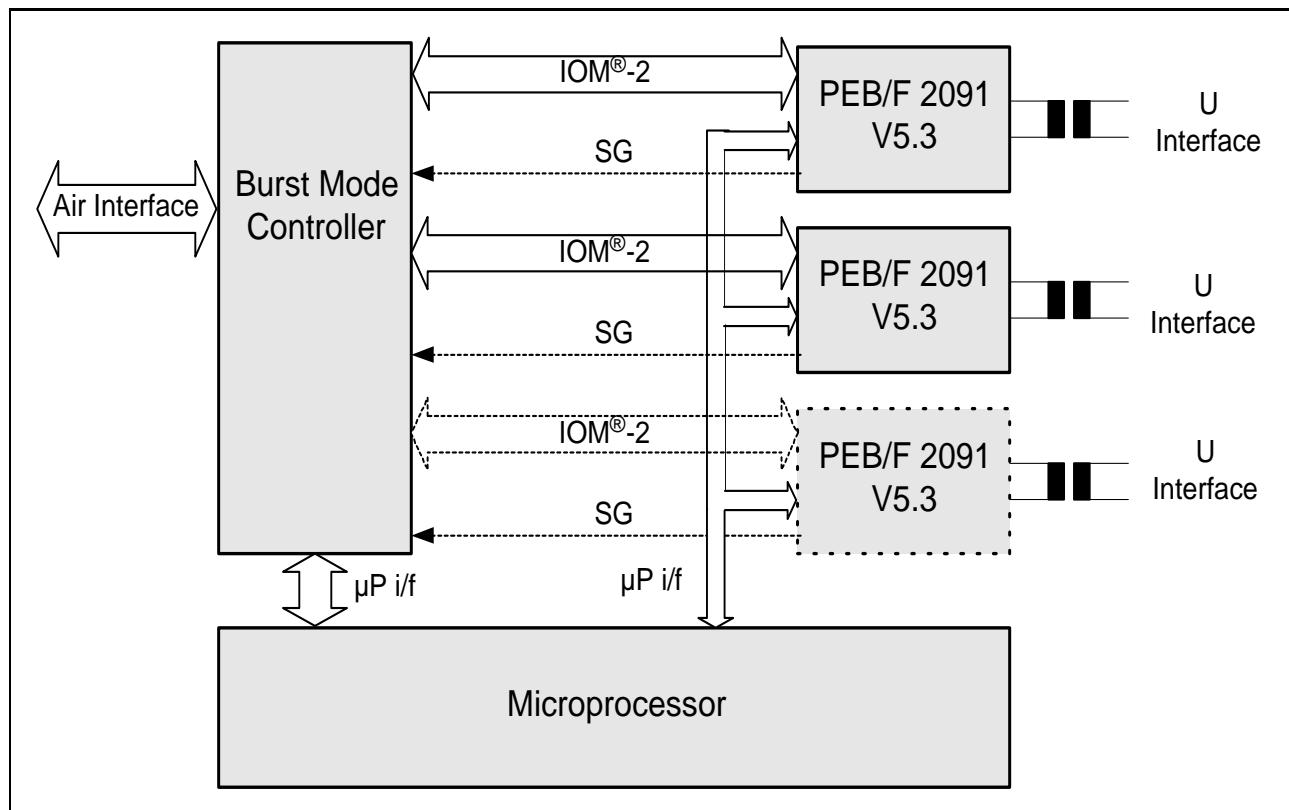

In Figure 3 a possible Base Station configuration is sketched. The PEB/F 2091 Version 5.3 is designed to suit to PEB 24911/PEB 24902 (DFE-Q/AFE) in the linecard, and to the PMB 2727 (Multichannel Burst Mode Controller) in the base station. The two new features of Version 5.3 concerning the Stop/Go function (see "Selectable Polarity of S/G Bit", page 40, and "Indication of S/G Bit Status on Pin SG", page 47) allow flexible and cost effective construction of Base Station boards without the need for external circuitry for S/G bit evaluation. Like the S/G bit, the S/G pin can be used for transmitting a common synchronization pulse to the burst mode controller. Moreover the undervoltage detection feature (see "Undervoltage Detection", page 33) can be used to simplify control of power supply level on the board.

**Figure 3** Architecture of the Wireless Local Loop Base Station

### 1.5.3 Dual Mode U and S Terminals and PC Cards

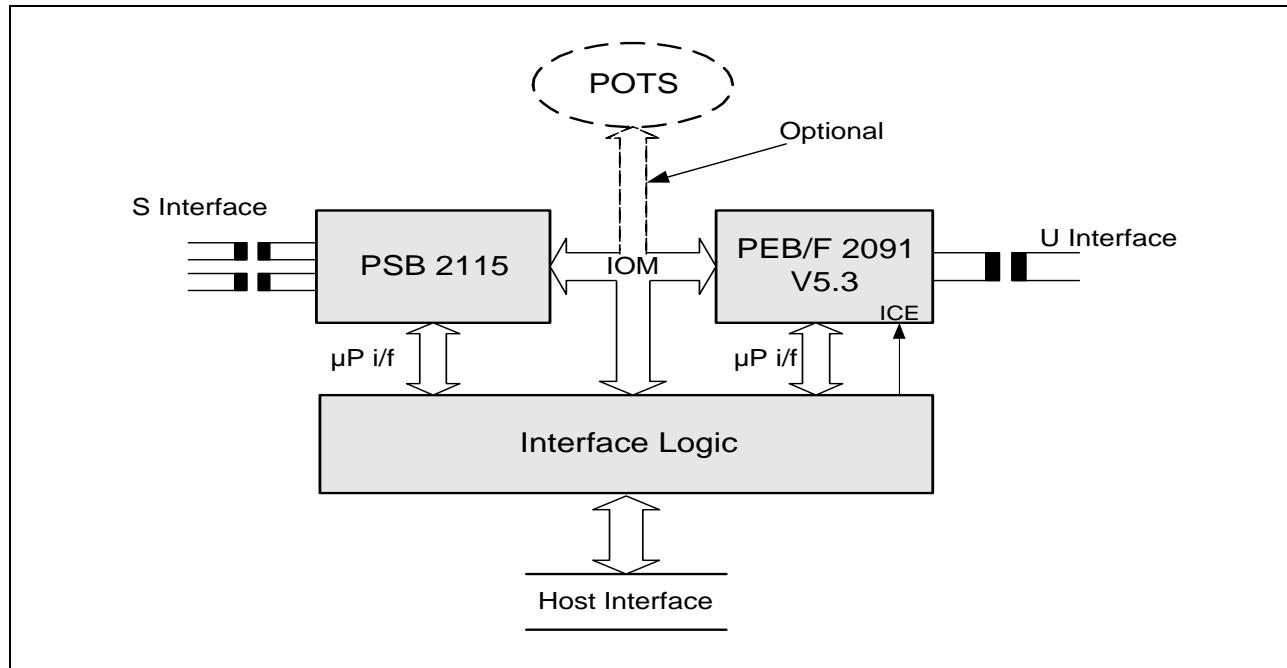

In this version of PEB/F 2091 the IOM®-2 interface can be set to tristate when the IOM®-2 master mode is used. This allows introduction of Dual Mode terminals and PC adapter cards using e.g. IPAC without external glue logic. See 2.6, page 37 for details.

**Figure 4** Dual Mode PC Adapter Card

## 2 Functional Description

### 2.1 Control of Single Bits Indications

The received Single Bits of the U Interface (see page 30 for definition) have to be forwarded via MON-2 messages to the controller unit<sup>1)</sup> to allow higher layer evaluation of this data. In all PEB/F 2091 versions up to Version 5.2 this Single Bits will be forwarded in the following way:

- In Repeater modes a MON-2 message containing all 12 Single Bits will be issued every 12 ms (see User's Manual 02.95 of the PEB 2091 Version 4.3, page 129).

- In all other modes the conditions for issuing the MON-2 message, containing all 12 Single Bits, depend on the version used:

In Version 5.1: A MON-2 is issued if the polarity of at least one of the Single Bits, other than FEBE, has been changed (see corresponding point of Errata Sheet of the PEB/F 2091 V5.1).

In all other versions: The MON-2 message will be issued only if in addition no CRC violations have been detected in the completed last two superframes (for details, see User's Manual 02.95 of the PEB 2091 Version 4.3, page 129).

Version 5.3 has been improved to allow almost free control of the conditions for Single Bits verification.

For compatibility, Version 5.3 can be configured to function either like Version 5.1 or alternatively like all other versions<sup>2)</sup>.

Furthermore, verification of Single Bits changes can be chosen to be controlled by a triple last look processor. Choosing this filtering method will imply that a change in a Single Bit will be issued via MON-2 message only if an identical bit value has been received for three consecutive superframes. This setting for the M4 bits complies with ANSI T1.601 without need for further software efforts. Note that this is the default setting for the M4 bits in all non repeater modes (see Table 4). Note also that this filtering method setting can be combined with the CRC filtering method.

In addition, verification of the M4 bits is completely independent of verification of bits M51, M52 and M61. This allows using the M4 bits in compliance with ANSI T1.601 (Triple Last Look), and still retain the freedom to use bits M51, M52 and M61 for other purposes (i.e. control functions, or even very low rate data transmission).

Control of the Single Bits is mode independent. This allows more flexibility, e.g. in repeater applications.

Selection of the filtering method is controlled via MON-8 messages. It is therefore available in stand alone mode as well as in  $\mu$ P mode.

1) Upstream in the LT modes and downstream in the NT modes

2) Note however that the default setting of Version 5.3 is different than all previous versions. The default setting of Version 5.3 is given in Table 4, page 32 and Table 5, page 32.

**Definitions**

As selection of the verification method for Single Bits is done via MON-8 messages, it is convenient to recall the format of MON-8 messages, which is given in Table 2 below. For more details on MON-8 messages, refer to User's Manual 02.95 of the PEB 2091 Version 4.3, page 129 ff.

**Table 2 Format of MON-8-Messages**

| <b>1. Byte</b> |                  | <b>2. Byte</b>               |

|----------------|------------------|------------------------------|

| 1 0 0 0        | r   0 0 0        | D7 D6 D5 D4 D3 D2 D1 D0      |

| MON-8          | Register   Addr. | Local Command (Message/Data) |

r: Register address – 0 = local function register

– 1 = internal register

D0...7 Local command – 00 ... FF<sub>H</sub> = local function code

– 00 ... FF<sub>H</sub> = internal register address

The MON-8 commands used to control the verification method are all local functions. The Register bit "r" should therefore be set to "0" in this case.

The Single Bits in the U frame are defined to be bits M41 to M48 (eight bits) in addition to the three bits M51, M52 and M61 and the FEBE bit. These bits are highlighted in Table 3, which gives the general structure of the U frame. In the following section Bits M41 to M48 are referred to as *M4 Bits*. Bits M51, M52 and M61 are referred to as *Additional Overhead Bits*.

**Table 3 U-Frame Structure**

|                  |                | Framing   | 2B + D   | Overhead Bits (M1 – M6) |       |       |           |                  |       |  |

|------------------|----------------|-----------|----------|-------------------------|-------|-------|-----------|------------------|-------|--|

|                  | Quat Positions | 1 – 9     | 10 – 117 | 118                     | 118   | 119   | 119       | 120              | 120   |  |

|                  | Bit Positions  | 1 – 18    | 19 – 234 | 235                     | 236   | 237   | 238       | 239              | 240   |  |

| Super Frame #    | Basic Frame #  | Sync Word | 2B + D   | M1                      | M2    | M3    | M4        | M5               | M6    |  |

| 1                | 1              | ISW       | 2B + D   | EOCa1                   | EOCa2 | EOCa3 | ACT/ ACT  | 1                | 1     |  |

|                  | 2              | SW        | 2B + D   | EOC d/m                 | EOCi1 | EOCi2 | DEA / PS1 | 1                | FEBE  |  |

|                  | 3              | SW        | 2B + D   | EOCi3                   | EOCi4 | EOCi5 | 1/ PS2    | CRC1             | CRC2  |  |

|                  | 4              | SW        | 2B + D   | EOCi6                   | EOCi7 | EOCi8 | 1/ NTM    | CRC3             | CRC4  |  |

|                  | 5              | SW        | 2B + D   | EOCa1                   | EOCa2 | EOCa3 | 1/ CSO    | CRC5             | CRC6  |  |

|                  | 6              | SW        | 2B + D   | EOC d/m                 | EOCi1 | EOCi2 | 1         | CRC7             | CRC8  |  |

|                  | 7              | SW        | 2B + D   | EOCi3                   | EOCi4 | EOCi5 | UOA / SAI | CRC9             | CRC10 |  |

|                  | 8              | SW        | 2B + D   | EOCi6                   | EOCi7 | EOCi8 | AIB / NIB | CRC11            | CRC12 |  |

| 2,3...           |                |           |          |                         |       |       |           |                  |       |  |

| LT- to NT dir. > |                |           |          |                         |       |       | /         | < NT- to LT dir. |       |  |

- ISW Inverted Synchronization Word (quad):

- SW Synchronization Word (quad):

- CRC Cyclic Redundancy Check

- EOC Embedded Operation Channel

- ACT Activation bit

- DEA Deactivation bit

- CSO Cold Start Only

- UOA U-Only Activation

- SAI S-Activity Indicator

- FEBE Far-end Block Error

- PS1 Power Status Primary Source

- PS2 Power Status Secondary Source

- NTM NT-Test Mode

- AIB Alarm Indication Bit

- NIB Network Indication Bit

|      |                                                    |

|------|----------------------------------------------------|

| a    | = address bit                                      |

| d/m  | = data / message bit                               |

| i    | = information (data / message)                     |

| ACT  | = (1) -> Layer 2 ready for communication           |

| DEA  | = (0) -> LT informs NT that it will turn off       |

| CSO  | = (1) -> NT-activation with cold start only        |

| UOA  | = (0) -> U-only activated                          |

| SAI  | = (0) -> S-interface is deactivated                |

| FEBE | = (0) -> Far-end block error occurred              |

| PS1  | = (1) -> Primary power supply OK                   |

| PS2  | = (1) -> Secondary power supply OK                 |

| NTM  | = (0) -> NT busy in test mode                      |

| AIB  | = (0) -> Interruption (according to ANSI)          |

| NIB  | = (1) -> no function<br>(reserved for network use) |

**Verification Control for M4 Bits**

Table 4 gives the available settings for M4 Bits filtering via MON-8 command.

**Table 4 Setting Filtering Method for M4 Bits**

| <b>Code<br/>D7-D0 (Bin)<sup>1)</sup></b> | <b>Symbol</b>               | <b>Function</b>                                                                                                                                                                                                         |

|------------------------------------------|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1000 1110                                | TLL<br>(Default,<br>not RP) | A change in at least one of the M4 Bits will be passed via MON-2 only after valid triple last look.<br>This is the default setting after reset in all non repeater modes                                                |

| 1000 1101                                | CRC<br>(Default,<br>RP)     | A change in at least one of the M4 Bits will be passed via MON-2 only if the CRC is valid for the last two superframes, not including the current one.<br>This is the default setting after reset in the repeater modes |

| 1000 1111                                | TLL,<br>CRC                 | A change in at least one of the M4 Bits will be passed via MON-2 only after valid triple last look, and if the CRC is valid for the last two superframes, not including the current one                                 |

| 1000 1100                                | On<br>Change                | Every change in at least one of the M4 Bits will be passed via MON-2                                                                                                                                                    |

1) see Table 2 for definition

**Verification Control for Additional Overhead Bits**

Table 5 gives the available settings for Additional Overhead Bits (M51, M52, M61) filtering via MON-8 command.

**Table 5 Setting Filtering Method for Additional Overhead Bits**

| <b>Code<br/>D7-D0 (Bin)<sup>1)</sup></b> | <b>Symbol</b>               | <b>Function</b>                                                                                                                                                                                                                          |

|------------------------------------------|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1000 1010                                | TLL<br>(Default,<br>not RP) | A change in at least one of the Additional Overhead Bits will be passed via MON-2 only after valid triple last look.<br>This is the default setting after reset in all non repeater modes                                                |

| 1000 1001                                | CRC<br>(Default,<br>RP)     | A change in at least one of the Additional Overhead Bits will be passed via MON-2 only if the CRC is valid for the last two superframes, not including the current one.<br>This is the default setting after reset in the repeater modes |

**Table 5 Setting Filtering Method for Additional Overhead Bits**

| Code<br>D7-D0 (Bin) <sup>1)</sup> | Symbol       | Function                                                                                                                                                                                                 |

|-----------------------------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1000 1011                         | TLL,<br>CRC  | A change in at least one of the Additional Overhead Bits will be passed via MON-2 only after valid triple last look, and if the CRC is valid for the last two superframes, not including the current one |

| 1000 1000                         | On<br>Change | Every change in at least one of the Additional Overhead Bits will be passed via MON-2                                                                                                                    |

1) see Table 2 for definition

### Reset behavior

MON-2 messages will be issued only if the receiver is synchronized. This is done to avoid meaningless MON-2 messages if data transmission is not synchronized.

In other words, MON-2 messages will be issued **only** in the following states (page numbers refer to User's Manual 02.95 of the PEB 2091 Version 4.3):

*In LT Mode (page 165):* "Line Active", "Pend. Transparent", "S/T Deactivated", "Pend. Deactivation" and "Transparent".

*In NT Mode (page 175):* "Synchronized 1", "Synchronized 2", "Wait for Act", "Transparent", "ERROR S/T", "Pend. Deact. S/T", "Pend. Deact. U" and "Analog Loop Back".

*In LT-Repeater Mode (page 185):* "Pend. Transparent", "Transparent", "Pend. Deactivation".

*In NT-Repeater Mode (page 186):* "Synchronized", "Transparent", "ERROR", "Pend. Deact." and "Analog Loop Back".

Mode setting via MON-8 will be reset only if the "Test" state is entered (see User's Manual 02.95 of the PEB 2091 Version 4.3, pages 165, 175, 185 and 186), e.g. after Hardware Reset, Software Reset or Power-On Reset.

## 2.2 Undervoltage Detection

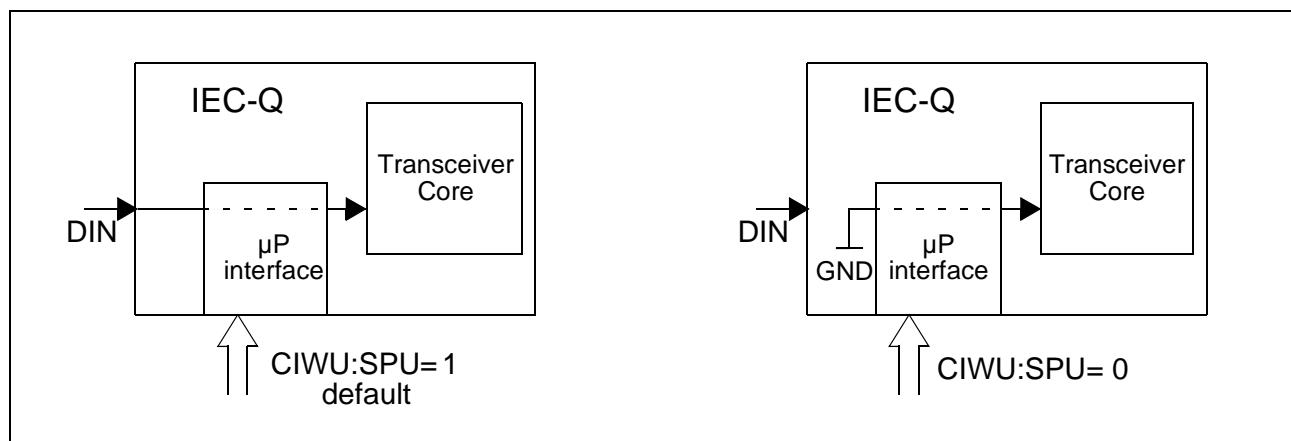

**Note:** This feature is only available in the microprocessor mode (PMODE = "1").

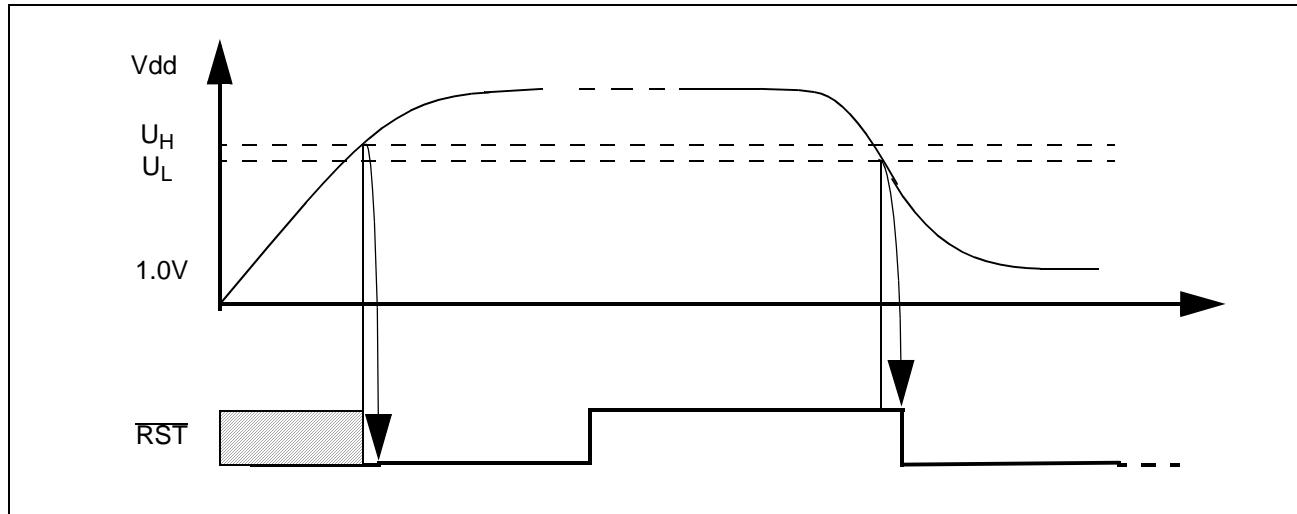

The undervoltage detector is enabled by setting the ADF:UVF bit to "1", see "ADF-Register", page 51. Note that the default setting of this bit after power on will be "1", i.e. the undervoltage detection feature will be activated. It activates the reset signal if the supply voltage drops below the threshold  $U_L$  (typically 4.21 V, see Figure 5 below and "Undervoltage Detection Timing", page 59).

## Functional Description

It also acts as power on reset by creating a reset pulse on pin  $\overline{RST}$  if the supply voltage rises above  $U_H$  (typically 4.30 V). It then stays inactive until the supply voltage drops again below the threshold level  $U_L$  (see also "Power On Reset (POR)", page 34, for more information).

Figure 5 UVD Control of Pin  $\overline{RST}$