April 1992 Revised November 1999

#### 74ABT646

### Octal Transceivers and Registers with 3-STATE Outputs

#### **General Description**

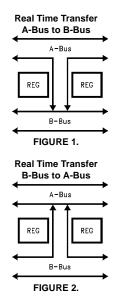

The ABT646 consists of bus transceiver circuits with 3-STATE, D-type flip-flops, and control circuitry arranged for multiplexed transmission of data directly from the input bus or from the internal registers. Data on the A or B bus will be clocked into the registers as the appropriate clock pin goes to a high logic level. Control  $\overline{\text{OE}}$  and direction pins are provided to control the transceiver function. In the transceiver mode, data present at the high impedance port may be stored in either the A or the B register or in both. The select controls can multiplex stored and real-time (transparent mode) data. The direction control determines which bus will receive data when the enable control  $\overline{\text{OE}}$  is Active LOW. In the isolation mode (control  $\overline{\text{OE}}$  HIGH), A data may be stored in the B register and/or B data may be stored in the A register.

#### **Features**

- Independent registers for A and B buses

- Multiplexed real-time and stored data

- A and B output sink capability of 64 mA, source capability of 32 mA

- Guaranteed output skew

- Guaranteed multiple output switching specifications

- Output switching specified for both 50 pF and 250 pF loads

- Guaranteed simultaneous switching noise level and dynamic threshold performance

- Guaranteed latchup protection

- High impedance glitch free bus loading during entire power up and power down cycle

- Nondestructive hot insertion capability

#### **Ordering Code:**

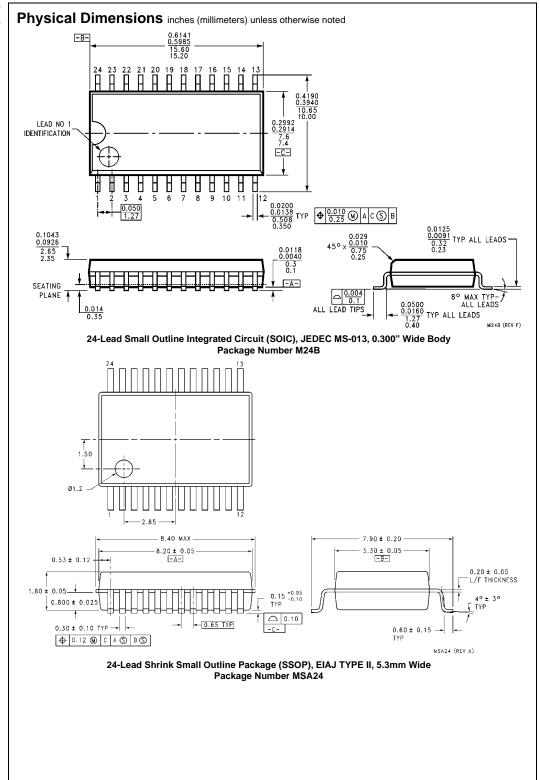

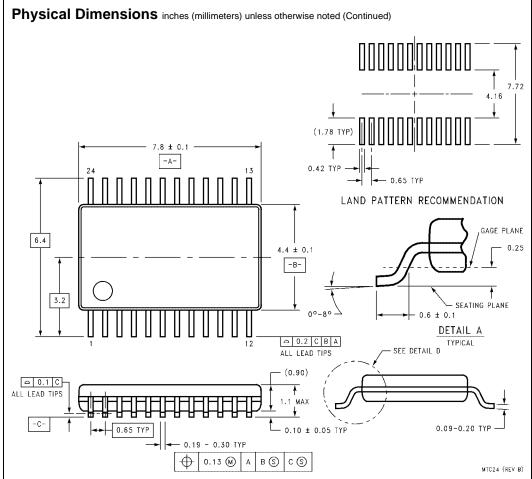

| Order Number | Package Number | Package Description                                                         |

|--------------|----------------|-----------------------------------------------------------------------------|

| 74ABT646CSC  | M24B           | 24-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-153, 4.4mm Wide   |

| 74ABT646CMSA | MSA24          | 24-Lead Shrink Small Outline Package (SSOP), EIAJ TYPE II, 5.3mm Wide       |

| 74ABT646CMTC | MTC24          | 24-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm Wide |

Device also available in Tape and Reel. Specify by appending suffix letter "X" to the ordering code.

#### **Connection Diagram**

#### **Pin Descriptions**

| Pin Names                      | Description                            |

|--------------------------------|----------------------------------------|

| A <sub>0</sub> -A <sub>7</sub> | Data Register A Inputs/3-STATE Outputs |

| B <sub>0</sub> -B <sub>7</sub> | Data Register B Inputs/3-STATE Outputs |

| CPAB, CPBA                     | Clock Pulse Inputs                     |

| SAB, SBA                       | Select Inputs                          |

| OE                             | Output Enable Input                    |

| DIR                            | Direction Control Input                |

#### **Truth Table**

|    |     | Inp    | uts    |     |     | Data I/O<br>(Note 1)           |                                | Function                                                               |  |

|----|-----|--------|--------|-----|-----|--------------------------------|--------------------------------|------------------------------------------------------------------------|--|

| OE | DIR | СРАВ   | СРВА   | SAB | SBA | A <sub>0</sub> -A <sub>7</sub> | B <sub>0</sub> -B <sub>7</sub> |                                                                        |  |

| Н  | Х   | H or L | H or L | Х   | Х   |                                |                                | Isolation                                                              |  |

| Н  | Χ   | ~      | Χ      | Χ   | Χ   | Input                          | Input                          | Clock A <sub>n</sub> Data into A Register                              |  |

| Н  | Χ   | Χ      | ~      | Χ   | Χ   |                                |                                | Clock B <sub>n</sub> Data into B Register                              |  |

| L  | Н   | Х      | Х      | L   | Х   |                                |                                | A <sub>n</sub> to B <sub>n</sub> —Real Time (Transparent Mode)         |  |

| L  | Н   | ~      | Χ      | L   | Χ   | Input                          | Output                         | Clock A <sub>n</sub> Data into A Register                              |  |

| L  | Н   | H or L | Χ      | Н   | Χ   |                                |                                | A Register to B <sub>n</sub> (Stored Mode)                             |  |

| L  | Н   | ~      | Χ      | Н   | Χ   |                                |                                | Clock A <sub>n</sub> Data into A Register and Output to B <sub>n</sub> |  |

| L  | L   | Х      | Χ      | Х   | L   |                                |                                | B <sub>n</sub> to A <sub>n</sub> —Real Time (Transparent Mode)         |  |

| L  | L   | X      | ~      | Χ   | L   | Output                         | Input                          | Clock B <sub>n</sub> Data into B Register                              |  |

| L  | L   | Χ      | H or L | Х   | Н   |                                |                                | B Register to A <sub>n</sub> (Stored Mode)                             |  |

| L  | L   | Х      | ~      | Х   | Н   |                                |                                | Clock B <sub>n</sub> Data into B Register and Output to A <sub>n</sub> |  |

H = HIGH Voltage Level

Note 1: The data output functions may be enabled or disabled by various signals at the  $\overline{\text{OE}}$  and DIR inputs. Data input functions are always enabled; i.e., data at the bus pins will be stored on every LOW-to-HIGH transition of the appropriate clock inputs.

L = LOW Voltage Level X = Immaterial

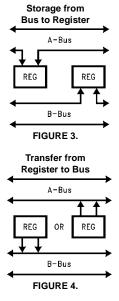

## Logic Diagram

Please note that this diagram is provided only for the understanding of logic operations and should not be used to estimate propagation delays.

#### Absolute Maximum Ratings(Note 2)

$\begin{array}{lll} \mbox{Storage Temperature} & -65^{\circ}\mbox{C to } +150^{\circ}\mbox{C} \\ \mbox{Ambient Temperature under Bias} & -55^{\circ}\mbox{C to } +125^{\circ}\mbox{C} \\ \mbox{Junction Temperature under Bias} & -55^{\circ}\mbox{C to } +150^{\circ}\mbox{C} \\ \end{array}$

$V_{CC}$  Pin Potential to Ground Pin -0.5V to +7.0V

Input Voltage (Note 3) -0.5V to +7.0V Input Current (Note 3) -30 mA to +5.0 mA

Voltage Applied to Any Output

in the Disable or

Power-Off State -0.5V to +5.5V

in the HIGH State -0.5 V to  $\text{V}_{\text{CC}}$

Current Applied to Output

in LOW State (Max)  ${\rm twice\ the\ rated\ I_{OL}\ (mA)}$  DC Latchup Source Current  ${\rm -500\ mA}$

Over Voltage Latchup (I/O) 10V

# Recommended Operating Conditions

Free Air Ambient Temperature -40°C to +85°C Supply Voltage +4.5V to +5.5V

Minimum Input Edge Rate ( $\Delta V/\Delta t$ )

Data Input

50 mV/ns

Enable Input

20 mV/ns

Clock Input

100 mV/ns

Note 2: Absolute maximum ratings are values beyond which the device may be damaged or have its useful life impaired. Functional operation

under these conditions is not implied.

Note 3: Either voltage limit or current limit is sufficient to protect inputs.

#### **DC Electrical Characteristics**

| Symbol                             | Parameter                         | Min  | Тур | Max  | Units  | V <sub>CC</sub> | Conditions                                        |

|------------------------------------|-----------------------------------|------|-----|------|--------|-----------------|---------------------------------------------------|

| V <sub>IH</sub>                    | Input HIGH Voltage                | 2.0  |     |      | V      |                 | Recognized HIGH Signal                            |

| V <sub>IL</sub>                    | Input LOW Voltage                 |      |     | 0.8  | V      |                 | Recognized LOW Signal                             |

| V <sub>CD</sub>                    | Input Clamp Diode Voltage         |      |     | -1.2 | V      | Min             | I <sub>IN</sub> = -18 mA (Non I/O Pins)           |

| V <sub>OH</sub>                    | Output HIGH Voltage               | 2.5  |     |      |        |                 | $I_{OH} = -3 \text{ mA}, (A_n, B_n)$              |

|                                    |                                   | 2.0  |     |      |        |                 | $I_{OH} = -32 \text{ mA}, (A_n, B_n)$             |

| V <sub>OL</sub>                    | Output LOW Voltage                |      |     | 0.55 |        |                 | $I_{OL} = 64 \text{ mA}, (A_n, B_n)$              |

| V <sub>ID</sub>                    | Input Leakage Test                | 4.75 |     |      | V      | 0.0             | I <sub>ID</sub> = 1.9 μA, (Non-I/O Pins)          |

|                                    |                                   |      |     |      |        |                 | All Other Pins Grounded                           |

| I <sub>IH</sub>                    | Input HIGH Current                |      |     | 1    | μА     | Max             | V <sub>IN</sub> = 2.7V (Non-I/O Pins) (Note 4)    |

|                                    |                                   |      |     | 1    | P** *  |                 | V <sub>IN</sub> = V <sub>CC</sub> (Non-I/O Pins)  |

| I <sub>BVI</sub>                   | Input HIGH Current                |      |     | 7    | μА     | Max             | V <sub>IN</sub> = 7.0V (Non-I/O Pins)             |

|                                    | Breakdown Test                    |      |     |      |        |                 | IIV - (                                           |

| I <sub>BVIT</sub>                  | Input HIGH Current                |      |     | 100  | μА     | Max             | $V_{IN} = 5.5V (A_n, B_n)$                        |

|                                    | Breakdown Test (I/O)              |      |     |      |        |                 |                                                   |

| I <sub>IL</sub>                    | Input LOW Current                 |      |     | -1   | μА     | Max             | V <sub>IN</sub> = 0.5V (Non-I/O Pins) (Note 4)    |

|                                    |                                   |      |     | -1   |        |                 | V <sub>IN</sub> = 0.0V (Non-I/O Pins)             |

| I <sub>IH</sub> + I <sub>OZH</sub> | Output Leakage Current            |      |     | 10   | μΑ     | 0V-5.5V         | $V_{OUT} = 2.7V (A_n, B_n); \overline{OE} = 2.0V$ |

| $I_{IL} + I_{OZL}$                 | Output Leakage Current            |      |     | -10  | μΑ     | 0V-5.5V         | $V_{OUT} = 0.5V (A_n, B_n); \overline{OE} = 2.0V$ |

| Ios                                | Output Short-Circuit Current      | -100 |     | -275 | mA     | Max             | $V_{OUT} = 0V (A_n, B_n)$                         |

| I <sub>CEX</sub>                   | Output HIGH Leakage Current       |      |     | 50   | μΑ     | Max             | $V_{OUT} = V_{CC} (A_n, B_n)$                     |

| I <sub>ZZ</sub>                    | Bus Drainage Test                 |      |     | 100  | μΑ     | 0.0V            | $V_{OUT} = 5.5V (A_n, B_n);$                      |

|                                    |                                   |      |     |      |        |                 | All Others GND                                    |

| I <sub>CCH</sub>                   | Power Supply Current              |      |     | 250  | μΑ     | Max             | All Outputs HIGH                                  |

| I <sub>CCL</sub>                   | Power Supply Current              |      |     | 30   | mA     | Max             | All Outputs LOW                                   |

| I <sub>CCZ</sub>                   | Power Supply Current              |      |     | 50   | μΑ     | Max             | Outputs 3-STATE; All Others GND                   |

| I <sub>CCT</sub>                   | Additional I <sub>CC</sub> /Input |      |     | 2.5  | mA     | Max             | $V_I = V_{CC} - 2.1V$                             |

|                                    |                                   |      |     |      |        |                 | All Other Outputs at V <sub>CC</sub> or GND       |

| I <sub>CCD</sub>                   | Dynamic I <sub>CC</sub> No        | Load |     |      |        |                 | Outputs OPEN                                      |

|                                    | (Note 4)                          |      |     | 0.18 | mA/MHz | Max             | OE and DIR = GND,                                 |

|                                    |                                   |      |     |      |        |                 | Non-I/O = GND or V <sub>CC</sub> (Note 5)         |

|                                    |                                   |      |     |      |        |                 | One Bit toggling, 50% duty cycle                  |

Note 4: Guaranteed but not tested.

Note 5: For 8-bit toggling,  $I_{\mbox{\scriptsize CCD}} < 1.4$  mA/MHz.

#### **DC Electrical Characteristics**

| Symbol           | Parameter                                    | Min  | Тур  | Max | Units | v <sub>cc</sub> | Conditions $\mathbf{C_L} = 50 \; \mathbf{pF}, \; \mathbf{R_L} = 500 \Omega$ |

|------------------|----------------------------------------------|------|------|-----|-------|-----------------|-----------------------------------------------------------------------------|

| V <sub>OLP</sub> | Quiet Output Maximum Dynamic V <sub>OL</sub> |      | 0.6  | 0.8 | V     | 5.0             | T <sub>A</sub> = 25°C (Note 6)                                              |

| V <sub>OLV</sub> | Quiet Output Minimum Dynamic V <sub>OL</sub> | -1.2 | -0.9 |     | V     | 5.0             | T <sub>A</sub> = 25°C (Note 6)                                              |

| V <sub>OHV</sub> | Minimum HIGH Level Dynamic Output Voltage    | 2.5  | 3.0  |     | V     | 5.0             | T <sub>A</sub> = 25° (Note 7)                                               |

| V <sub>IHD</sub> | Minimum HIGH Level Dynamic Input Voltage     | 2.2  | 1.8  |     | V     | 5.0             | T <sub>A</sub> = 25°C (Note 8)                                              |

| V <sub>ILD</sub> | Maximum LOW Level Dynamic Input Voltage      |      | 0.8  | 0.5 | V     | 5.0             | T <sub>A</sub> = 25°C (Note 8)                                              |

Note 6: Max number of outputs defined as (n). n – 1 data inputs are driven 0V to 3V. One output at LOW. Guaranteed, but not tested.

$\textbf{Note 7:} \ \text{Max number of outputs defined as (n).} \ n-1 \ \text{data inputs are driven 0V to 3V}. \ \text{One output HIGH. Guaranteed, but not tested.}$

Note 8: Max number of data inputs (n) switching. n – 1 inputs switching 0V to 3V. Input-under-test switching: 3V to threshold (V<sub>ILD</sub>), 0V to threshold (V<sub>IHD</sub>). Guaranteed, but not tested

#### **AC Electrical Characteristics**

(SOIC and SSOP package)

|                  |                                                |                         | T <sub>A</sub> = +25°C |          | T <sub>A</sub> = -55°0 | C to +125°C           | $T_A = -40^\circ$                                | C to +85°C             |       |

|------------------|------------------------------------------------|-------------------------|------------------------|----------|------------------------|-----------------------|--------------------------------------------------|------------------------|-------|

| Symbol           | Parameter                                      | V <sub>CC</sub> = +5.0V |                        | <i>l</i> | $V_{CC}=4$             | .5V-5.5V              | $\mathbf{V_{CC}} = \mathbf{4.5V} \mathbf{-5.5V}$ |                        | Units |

| Symbol           |                                                |                         | $C_L = 50 \text{ pF}$  |          | C <sub>L</sub> =       | $C_L = 50 \text{ pF}$ |                                                  | C <sub>L</sub> = 50 pF |       |

|                  |                                                | Min                     | Тур                    | Max      | Min                    | Max                   | Min                                              | Max                    |       |

| f <sub>MAX</sub> | Maximum Clock Frequency                        | 200                     |                        |          | 200                    |                       | 200                                              |                        | MHz   |

| t <sub>PLH</sub> | Propagation Delay                              | 1.7                     | 3.0                    | 5.6      | 2.2                    | 8.8                   | 1.7                                              | 5.6                    | ns    |

| t <sub>PHL</sub> | Clock to Bus                                   | 1.7                     | 3.4                    | 5.6      | 1.7                    | 8.8                   | 1.7                                              | 5.6                    | 115   |

| t <sub>PLH</sub> | Propagation Delay                              | 1.5                     | 2.6                    | 4.8      | 1.5                    | 7.9                   | 1.5                                              | 4.8                    | ns    |

| t <sub>PHL</sub> | Bus to Bus                                     | 1.5                     | 3.0                    | 4.8      | 1.5                    | 7.9                   | 1.5                                              | 4.8                    | 115   |

| t <sub>PLH</sub> | Propagation Delay                              | 1.5                     | 3.0                    | 5.9      | 1.5                    | 8.1                   | 1.5                                              | 5.9                    | ns    |

| t <sub>PHL</sub> | SBA or SAB to A <sub>n</sub> to B <sub>n</sub> | 1.5                     | 3.4                    | 5.9      | 1.5                    | 8.9                   | 1.5                                              | 5.9                    | 115   |

| t <sub>PZH</sub> | Enable Time                                    | 1.5                     | 3.2                    | 6.3      | 1.0                    | 7.3                   | 1.5                                              | 6.3                    |       |

| $t_{PZL}$        | OE to A <sub>n</sub> or B <sub>n</sub>         | 1.5                     | 3.5                    | 6.3      | 1.9                    | 8.8                   | 1.5                                              | 6.3                    | ns    |

| t <sub>PHZ</sub> | Disable Time                                   | 1.5                     | 3.7                    | 6.0      | 1.5                    | 9.3                   | 1.5                                              | 6.0                    |       |

| $t_{PLZ}$        | OE to A <sub>n</sub> or B <sub>n</sub>         | 1.5                     | 3.2                    | 6.0      | 1.5                    | 9.3                   | 1.5                                              | 6.0                    | ns    |

| t <sub>PZH</sub> | Enable Time                                    | 1.5                     | 3.4                    | 6.3      | 1.0                    | 7.7                   | 1.5                                              | 6.3                    | 20    |

| $t_{PZL}$        | DIR to A <sub>n</sub> or B <sub>n</sub>        | 1.5                     | 3.7                    | 6.3      | 2.2                    | 9.5                   | 1.5                                              | 6.3                    | ns    |

| t <sub>PHZ</sub> | Disable Time                                   | 1.5                     | 3.8                    | 6.0      | 1.5                    | 8.7                   | 1.5                                              | 6.0                    | 20    |

| t <sub>PLZ</sub> | DIR to A <sub>n</sub> or B <sub>n</sub>        | 1.5                     | 3.2                    | 6.0      | 1.5                    | 9.2                   | 1.5                                              | 6.0                    | ns    |

### **AC Operating Requirements**

| Symbol             | Parameter           | $T_A = +25^{\circ}C$ $V_{CC} = +5.0V$ $C_L = 50 \text{ pF}$ |     | $V_{CC} = +5.0V$ $V_{CC} = 4.5V-5.5V$ $C_L = 50 \text{ pF}$ $C_L = 50 \text{ pF}$ |     | $T_A = -40$ °C to +85°C<br>$V_{CC} = 4.5V-5.5V$<br>$C_L = 50$ pF |     | Units |

|--------------------|---------------------|-------------------------------------------------------------|-----|-----------------------------------------------------------------------------------|-----|------------------------------------------------------------------|-----|-------|

|                    |                     | Min                                                         | Max | Min                                                                               | Max | Min                                                              | Max |       |

| t <sub>S</sub> (H) | Setup Time, HIGH    | 1.5                                                         |     | 1.5                                                                               | 3.0 | 1.5                                                              |     | ns    |

| t <sub>S</sub> (L) | or LOW Bus to Clock | 1.5                                                         |     | 1.5                                                                               | 3.0 | 1.5                                                              |     | 113   |

| t <sub>H</sub> (H) | Hold Time, HIGH     | 1.0                                                         |     | 1.0                                                                               | 1.0 | 1.0                                                              |     | ns    |

| t <sub>H</sub> (L) | or LOW Bus to Clock | 1.0                                                         |     | 1.0                                                                               | 1.0 | 1.0                                                              |     | 115   |

| t <sub>W</sub> (H) | Pulse Width,        | 3.0                                                         |     | 3.0                                                                               | 4.0 | 3.0                                                              |     | 20    |

| t <sub>W</sub> (L) | HIGH or LOW         | 3.0                                                         |     | 3.0                                                                               | 4.0 | 3.0                                                              |     | ns    |

#### **Extended AC Electrical Characteristics**

(SOIC Package)

| Symbol           | Parameter                                                  | $T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}$ $V_{CC} = 4.5\text{V} - 5.5\text{V}$ $C_L = 50 \text{ pF}$ 8 Outputs Switching (Note 9) |     | $T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}$ $V_{CC} = 4.5\text{V} - 5.5\text{V}$ $C_L = 250 \text{ pF}$ 1 Output Switching (Note 10) |     | $T_A = -40^{\circ}\text{C to} +85^{\circ}\text{C}$ $V_{CC} = 4.5\text{V} -5.5\text{V}$ $C_L = 250 \text{ pF}$ 8 Outputs Switching (Note 11) |      | Units |    |

|------------------|------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------|------|-------|----|

|                  |                                                            |                                                                                                                                             |     |                                                                                                                                              |     |                                                                                                                                             |      |       |    |

|                  |                                                            | Min                                                                                                                                         | Max | Min                                                                                                                                          | Max | Min                                                                                                                                         | Max  |       |    |

| t <sub>PLH</sub> | Propagation Delay                                          | 1.5                                                                                                                                         | 5.5 | 2.0                                                                                                                                          | 7.5 | 2.5                                                                                                                                         | 10.0 | ns    |    |

| t <sub>PHL</sub> | Clock to Bus                                               | 1.5                                                                                                                                         | 5.5 | 2.0                                                                                                                                          | 7.5 | 2.5                                                                                                                                         | 10.0 | 115   |    |

| t <sub>PLH</sub> | Propagation Delay                                          | 1.5                                                                                                                                         | 6.0 | 2.0                                                                                                                                          | 7.0 | 2.5                                                                                                                                         | 9.5  | ns    |    |

| t <sub>PHL</sub> | Bus to Bus                                                 | 1.5                                                                                                                                         | 6.0 | 2.0                                                                                                                                          | 7.0 | 2.5                                                                                                                                         | 9.5  | 115   |    |

| t <sub>PLH</sub> | Propagation Delay                                          | 1.5                                                                                                                                         | 6.0 | 2.0                                                                                                                                          | 7.5 | 2.5                                                                                                                                         | 10.0 | ns    |    |

| t <sub>PHL</sub> | SBA or SAB to A <sub>n</sub> or B <sub>n</sub>             | 1.5                                                                                                                                         | 6.0 | 2.0                                                                                                                                          | 7.5 | 2.5                                                                                                                                         | 10.0 |       |    |

| t <sub>PZH</sub> | Output Enable Time                                         | 1.5                                                                                                                                         | 6.0 | 2.0                                                                                                                                          | 8.0 | 2.5                                                                                                                                         | 10.5 |       |    |

| $t_{PZL}$        | OE <sub>n</sub> or DIR to A <sub>n</sub> or B <sub>n</sub> | 1.5                                                                                                                                         | 6.0 | 2.0                                                                                                                                          | 8.0 | 2.5                                                                                                                                         | 10.5 | ns    |    |

| t <sub>PHZ</sub> | Output Disable Time                                        | 1.5                                                                                                                                         | 6.0 | (Note 12)                                                                                                                                    |     | (Note 42) (Note 42)                                                                                                                         |      | 0.12) | ns |

| $t_{PLZ}$        | OE <sub>n</sub> or DIR to A <sub>n</sub> or B <sub>n</sub> | 1.5                                                                                                                                         | 6.0 |                                                                                                                                              |     | (Note 12)                                                                                                                                   |      | 115   |    |

Note 9: This specification is guaranteed but not tested. The limits apply to propagation delays for all paths described switching in phase (i.e., all LOW-to-HIGH, HIGH-to-LOW, etc.).

Note 10: This specification is guaranteed but not tested. The limits represent propagation delay with 250 pF load capacitors in place of the 50 pF load capacitors in the standard AC load. This specification pertains to single output switching only.

Note 11: This specification is guaranteed but not tested. The limits represent propagation delays for all paths described switching in phase (i.e., all LOW-to-HIGH, HIGH-to-LOW, etc.) with 250 pF load capacitors in place of the 50 pF load capacitors in the standard AC load.

Note 12: The 3-STATE delays are dominated by the RC network (500\Omega, 250 pF) on the output and has been excluded from the datasheet.

#### Skew

(SOIC Package)

| Symbol                      | Parameter                                | T <sub>A</sub> = -40°C to +85°C  V <sub>CC</sub> = 4.5V-5.5V  C <sub>L</sub> = 50 pF  8 Outputs Switching  (Note 13) | T <sub>A</sub> = -40°C to +85°C  V <sub>CC</sub> = 4.5V-5.5V  C <sub>L</sub> = 250 pF  8 Outputs Switching  (Note 14)  Max | Units |

|-----------------------------|------------------------------------------|----------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|-------|

| t <sub>OSHL</sub> (Note 15) | Pin to Pin Skew, HL Transitions          | 1.3                                                                                                                  | 2.5                                                                                                                        | ns    |

| t <sub>OSLH</sub> (Note 15) | Pin to Pin Skew, LH Transitions          | 1.0                                                                                                                  | 2.0                                                                                                                        | ns    |

| t <sub>PS</sub> (Note 16)   | Duty Cycle, LH-HL Skew                   | 2.0                                                                                                                  | 4.0                                                                                                                        | ns    |

| t <sub>OST</sub> (Note 15)  | Pin to Pin Skew, LH/HL Transitions       | 2.0                                                                                                                  | 4.0                                                                                                                        | ns    |

| t <sub>PV</sub> (Note 17)   | Device to Device Skew, LH/HL Transitions | 2.5                                                                                                                  | 4.5                                                                                                                        | ns    |

Note 13: This specification is guaranteed but not tested. The limits apply to propagation delays for all paths described switching in phase (i.e., all LOW-to-HIGH, HIGH-to-LOW, etc.).

Note 14: This specification is guaranteed but not tested. The limits represent propagation delays with 250 pF load capacitors in place of the 50 pF load capacitors in the standard AC load.

Note 15: Skew is defined as the absolute value of the difference between the actual propagation delays for any two separate outputs of the same device. The specification applies to any outputs switching HIGH-to-LOW (t<sub>OSHL</sub>), LOW-to-HIGH (t<sub>OSLH</sub>), or any combination switching LOW-to-HIGH and/or HIGH-to-LOW (t<sub>OST</sub>). This specification is guaranteed but not tested.

Note 16: This describes the difference between the delay of the LOW-to-HIGH and the HIGH-to-LOW transition on the same pin. It is measured across all the outputs (drivers) on the same chip, the worst (largest delta) number is the guaranteed specification. This specification is guaranteed but not tested.

Note 17: Propagation delay variation for a given set of conditions (i.e., temperature and V<sub>CC</sub>) from device to device. This specification is guaranteed but not tested

#### Capacitance

| Symbol                     | Parameter          | Тур | Units | Conditions<br>T <sub>A</sub> = 25°C |

|----------------------------|--------------------|-----|-------|-------------------------------------|

| C <sub>IN</sub>            | Input Capacitance  | 5   | pF    | V <sub>CC</sub> = 0V (non I/O pins) |

| C <sub>I/O</sub> (Note 18) | Output Capacitance | 11  | pF    | $V_{CC} = 5.0V (A_n, B_n)$          |

Note 18:  $C_{I\!/O}$  is measured at frequency, f = 1 MHz, per MIL-STD-883, Method 3012.

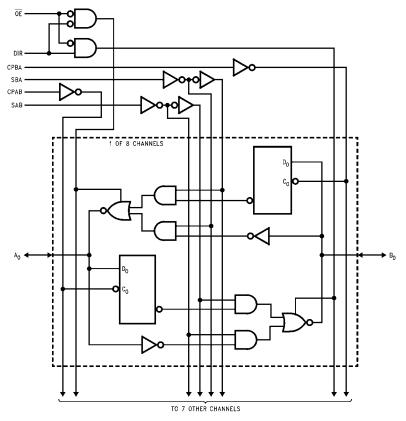

#### **AC Loading**

FIGURE 5. Standard AC Test Load

FIGURE 6. Test Input Signal Levels

Input Pulse Requirements

| Amplitude | Rep. Rate | t <sub>W</sub> | t <sub>r</sub> | t <sub>f</sub> |

|-----------|-----------|----------------|----------------|----------------|

| 3.0V      | 1 MHz     | 500 ns         | 2.5 ns         | 2.5 ns         |

FIGURE 7. Test Input Signal Requirements

#### **AC Waveforms**

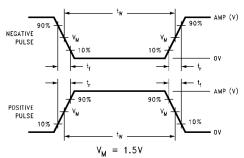

FIGURE 8. Propagation Delay Waveforms for Inverting and Non-Inverting Functions

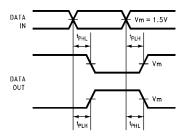

FIGURE 9. Propagation Delay, Pulse Width Waveforms

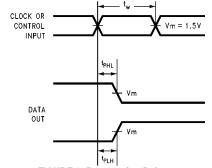

FIGURE 10. 3-STATE Output HIGH and LOW Enable and Disable Times

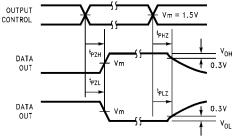

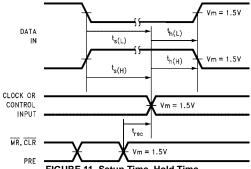

FIGURE 11. Setup Time, Hold Time and Recovery Time Waveforms

24-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm Wide Package Number MTC24

Fairchild does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and Fairchild reserves the right at any time without notice to change said circuitry and specifications.

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component in any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

www.fairchildsemi.com

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

### Fairchild Semiconductor:

74ABT646CMSAX 74ABT646CSC 74ABT646CMSA 74ABT646CSCX 74ABT646CMTCX 74ABT646CMTC