### INTEGRATED CIRCUITS

# DATA SHEET

## 80CL410/83CL410

Low voltage/low power single-chip 8-bit microcontroller with I<sup>2</sup>C

Product specification

1995 Jan 20

IC20 Data Handbook

## Low voltage/low power single-chip 8-bit microcontroller with I<sup>2</sup>C

#### 80CL410/83CL410

#### **DESCRIPTION**

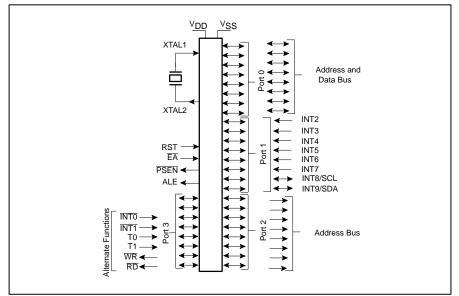

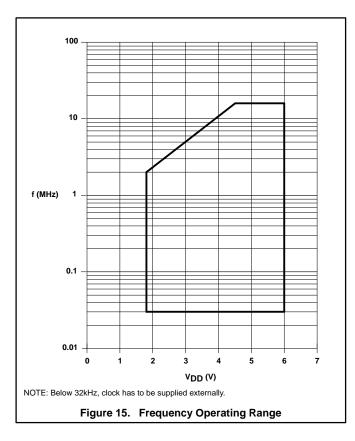

The 80CL410/83CL410 (hereafter generically referred to as 8XCL410) is manufactured in an advanced CMOS process that allows the part to operate at supply voltages down to 1.8V and oscillator frequencies down to DC. The 8XCL410 has the same instruction set as the 80C51.

The 8XCL410 features a 4k byte ROM (83CL410), 128 bytes RAM (both ROM and RAM are externally expandable to 64k bytes), four 8-bit ports, two 16-bit timer/counters, an I<sup>2</sup>C serial interface, a thirteen source, two priority level nested interrupt structure, and on-chip oscillator circuitry suitable for quartz crystal, ceramic resonator, RC, or LC.

The 8XCL410 has two reduced power modes that are the same as those on the standard 80C51. The special reduced power feature of this part is that it can be stopped and then restarted. Running from an external clock source, the clock can be stopped and after a period of time restarted. The 8XCL410 will resume operation from where it was when the code stopped with no loss of internal state, RAM contents, or Special Function Register contents. If the internal oscillator is used the part cannot be stopped and started, but the power-down mode, which can be terminated via an interrupt, can be used to achieve similar power savings and then restart without loss of on-chip RAM and Special Function Register values.

#### **FEATURES**

- Single supply voltage 1.8V to 6.0V

- Frequency from DC to 12MHz

- 80C51 based architecture

- 4k × 8 ROM (64k external)

- 128 × 8 RAM (64k external)

- 120 / 0 10 mm (0 m 0/m

- Four 8-bit I/O ports

- Two 16-bit timer/counters

- A thirteen-source, two-level, nested priority interrupt structure

- 10 external interrupts

- Fully static 80C51 CPU

- I<sup>2</sup>C Serial Interface

- Two power control modes

- Idle mode

- Power-down mode can be terminated by reset or external interrupt

- Wake-up via external interrupts at port 1

- Single supply voltage 1.8V to 6.0V

- Frequency range of DC to 12MHz

- On-chip oscillator (quartz crystal, ceramic resonator, RC, LC)

- Very low power consumption

- Operating temperature range: -40 to +85°C

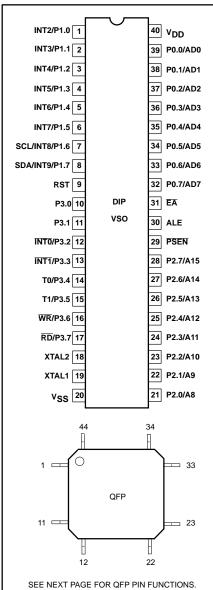

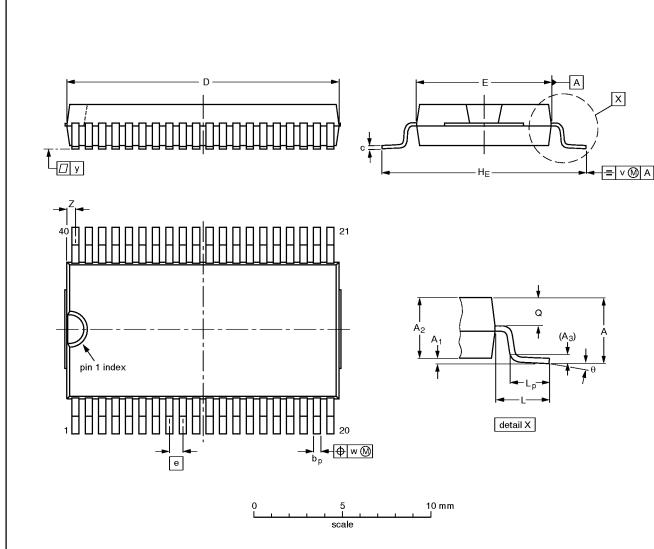

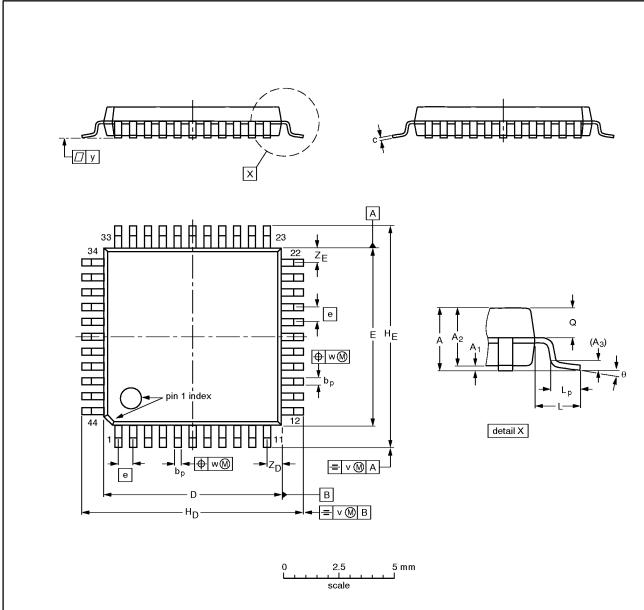

#### PIN CONFIGURATION

#### ORDERING CODE

| PHILIPS PART O | RDER NUMBER<br>ARKING | PHILIPS NORTH AMERICA<br>PART ORDER NUMBER <sup>1</sup> |              | TEMPERATURE °C                                              |                | Drawing<br>Number |

|----------------|-----------------------|---------------------------------------------------------|--------------|-------------------------------------------------------------|----------------|-------------------|

| ROMless        | ROM                   | ROMIess                                                 | ROM          | AND PACKAGE                                                 | FREQUENCY      | Number            |

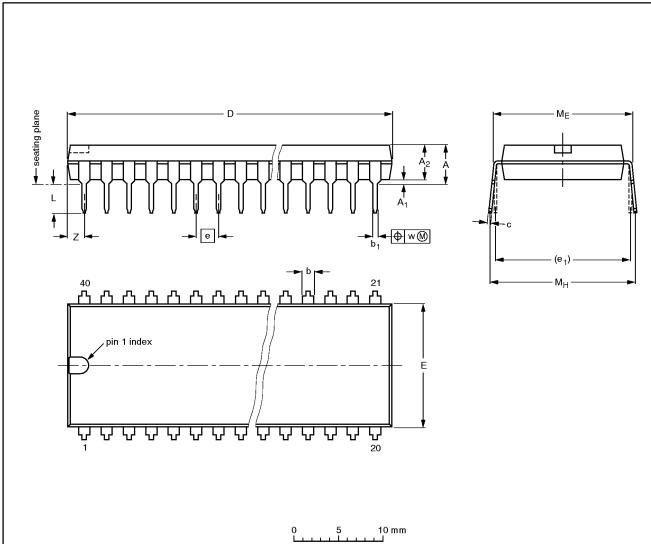

| P80CL410HFP    | P83CL410HFP           | P80CL410HF N                                            | P83CL410HF N | -40 to +85,<br>40-Pin Plastic Dual In-line Package          | 32kHZ to 12MHz | SOT129-1          |

| P80CL410HFT    | P83CL410HFT           | P80CL410HF D                                            | P83CL410HF D | –40 to +85,<br>40-Pin Plastic Very Small Outline<br>Package | 32kHZ to 12MHz | SOT158-1          |

|                | P83CL410HFH           |                                                         |              | –40 to +85,<br>44-Pin Plastic Quad Flat Pack                | 32kHZ to 12MHz | SOT307-2          |

#### NOTE:

For emulation purposes, the P85CL000 (Piggyback version) with 256 bytes of RAM is recommended.

<sup>1.</sup> Parts ordered by the Philips North America part number will be marked with the Philips part marking.

## Low voltage/low power single-chip 8-bit microcontroller with I<sup>2</sup>C

### 80CL410/83CL410

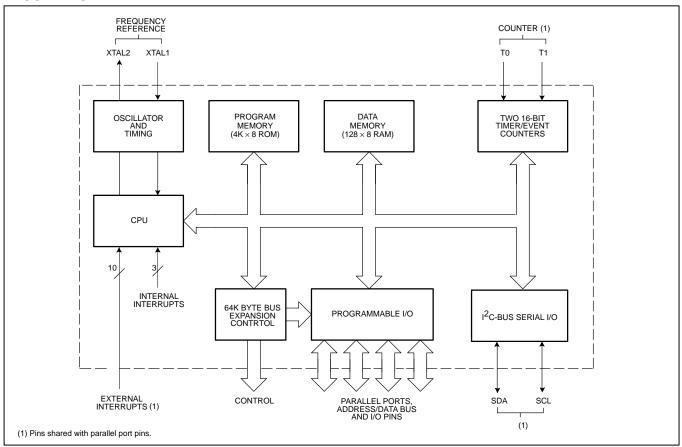

## PLASTIC QUAD FLAT PACK PIN FUNCTIONS

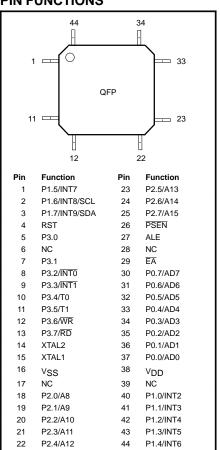

#### **LOGIC SYMBOL**

## 80CL410/83CL410

#### **BLOCK DIAGRAM**

## Low voltage/low power single-chip 8-bit microcontroller with I<sup>2</sup>C

## 80CL410/83CL410

### **PIN DESCRIPTION**

|           | PIN          | NO.             |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----------|--------------|-----------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MNEMONIC  | QFP          | DIL40/<br>VSO40 | TYPE | NAME AND FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| $V_{SS}$  | 16           | 20              | I    | Ground: 0V reference.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| $V_{DD}$  | 38           | 40              | ı    | <b>Power Supply:</b> This is the power supply voltage for normal, idle, and power-down operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| P0.0-0.7  | 30–37        | 39–32           | I/O  | <b>Port 0:</b> Port 0 is an open-drain, bidirectional I/O port. Port 0 pins that have 1s written to them float and can be used as high-impedance inputs. Port 0 is also the multiplexed low-order address and data bus during accesses to external program and data memory. In this application, it uses strong internal pull-ups when emitting 1s.                                                                                                                                                                                                                                                                                                                                                                                                                |

| P1.0–P1.7 | 40–44<br>1–3 | 1–8             | I/O  | <b>Port 1:</b> Port 1 is an 8-bit bidirectional I/O port with internal pull-ups. Port 1 pins that have 1s written to them are pulled high by the internal pull-ups and can be used as inputs. As inputs, port 1 pins that are externally pulled low will source current because of the internal pull-ups. (See DC Electrical Characteristics: I <sub>IL</sub> ). Additional functions include:                                                                                                                                                                                                                                                                                                                                                                     |

|           |              | 7               | I/O  | SCL (P1.6): I <sup>2</sup> C serial bus clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|           |              | 8               | I/O  | SDA (P1.7): I <sup>2</sup> C serial bus data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|           |              | 1–8             | 1    | INT2-INT9 (P1.0-P1.7): Additional external interrupts.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

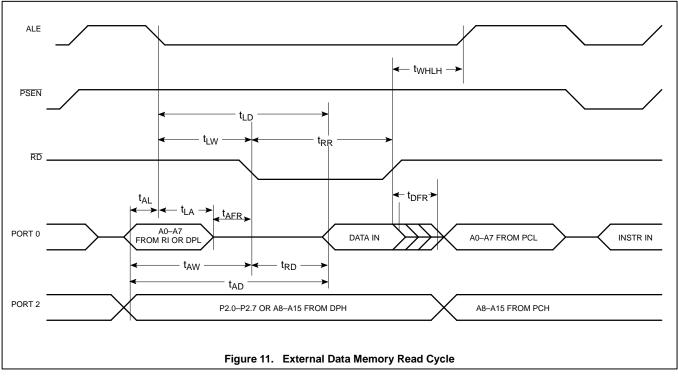

| P2.0-P2.7 | 18–25        | 21–28           | I/O  | <b>Port 2:</b> Port 2 is an 8-bit bidirectional I/O port with internal pull-ups. Port 2 pins that have 1s written to them are pulled high by the internal pull-ups and can be used as inputs. As inputs, port 2 pins that are externally being pulled low will source current because of the internal pull-ups. (See DC Electrical Characteristics: I <sub>IL</sub> ). Port 2 emits the high-order address byte during fetches from external program memory and during accesses to external data memory that use 16-bit addresses (MOVX @DPTR). In this application, it uses strong internal pull-ups when emitting 1s. During accesses to external data memory that use 8-bit addresses (MOV @Ri), port 2 emits the contents of the P2 special function register. |

| P3.0-P3.7 | 5, 7–13      | 10–17           | I/O  | <b>Port 3:</b> Port 3 is an 8-bit bidirectional I/O port with internal pull-ups. Port 3 pins that have 1s written to them are pulled high by the internal pull-ups and can be used as inputs. As inputs, port 3 pins that are externally being pulled low will source current because of the pull-ups. (See DC Electrical Characteristics: I <sub>IL</sub> ). Port 3 also serves the special features of the 80C51 family, as listed below:                                                                                                                                                                                                                                                                                                                        |

|           | 8            | 12              | l ı  | INTO (P3.2): External interrupt 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|           | 9            | 13              | ı    | INT1 (P3.3): External interrupt 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|           | 10           | 14              | 1    | T0 (P3.4): Timer 0 external input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|           | 11           | 15              | 1    | T1 (P3.5): Timer 1 external input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|           | 12           | 16              | 0    | WR (P3.6): External data memory write strobe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|           | 13           | 17              | 0    | RD (P3.7): External data memory read strobe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

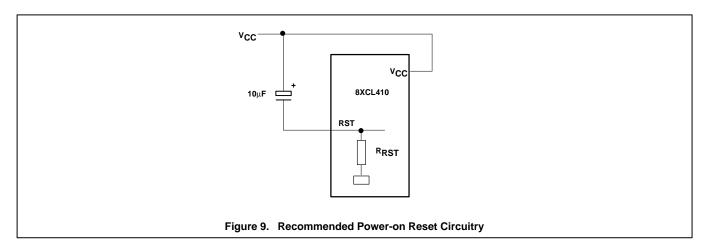

| RST       | 4            | 9               | I    | <b>Reset:</b> A high on this pin for two machine cycles while the oscillator is running, resets the device. An internal diffused resistor to $V_{SS}$ permits a power-on reset using only an external capacitor to $V_{DD}$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

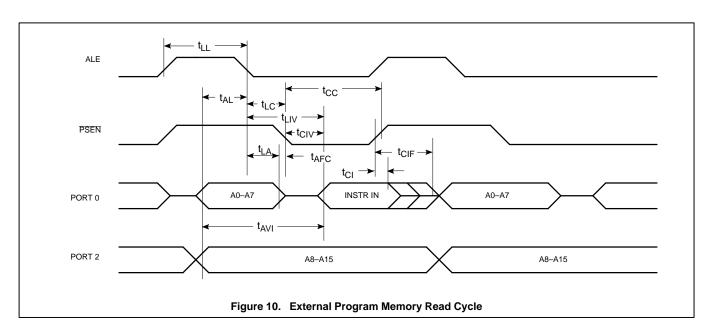

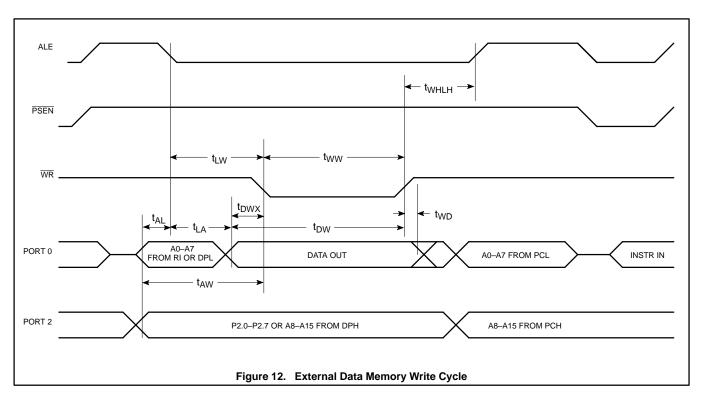

| ALE       | 27           | 30              | 0    | Address Latch Enable: Output pulse for latching the low byte of the address during an access to external memory. In normal operation, ALE is emitted at a constant rate of 1/6 the oscillator frequency, and can be used for external timing or clocking. Note that one ALE pulse is skipped during each access to external data memory.                                                                                                                                                                                                                                                                                                                                                                                                                           |

| PSEN      | 26           | 29              | 0    | Program Store Enable: The read strobe to external program memory. When the device is executing code from the external program memory, PSEN is activated twice each machine cycle, except that two PSEN activations are skipped during each access to external data memory. PSEN is not activated during fetches from internal program memory.                                                                                                                                                                                                                                                                                                                                                                                                                      |

| EA        | 29           | 31              | l    | <b>External Access Enable:</b> $\overline{EA}$ must be externally held low to enable the device to fetch code from external program memory locations 0000H to 0FFFH. If $\overline{EA}$ is held high, the device executes from internal program memory unless the program counter contains an address greater than 0FFFH.                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| XTAL1     | 15           | 19              | I    | Crystal 1: Input to the inverting oscillator amplifier and input for an external clock source.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| XTAL2     | 14           | 18              | 0    | Crystal 2: Output from the inverting oscillator amplifier.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

80CL410/83CL410

Table 1. 8XCL410 Special Function Registers

| Table 1.     | 8XCL410 Special                         | DIRECT     | <u> </u> |            | SS SYME       | SOL OR A   | ALTERNAT   | LIVE BUB. | T FUNCTI  | ON        | RESET            |

|--------------|-----------------------------------------|------------|----------|------------|---------------|------------|------------|-----------|-----------|-----------|------------------|

| SYMBOL       | DESCRIPTION                             | ADDRESS    | MSB      | I ADDRE    | .33, 3 i ivie | SOL, OK A  | ALIEKNAI   | IIVE POR  | PONCTI    | LSB       | VALUE            |

| ACC*         | Accumulator                             | E0H        | E7       | E6         | E5            | E4         | E3         | E2        | E1        | E0        | 00H              |

| B*           | B register                              | F0H        | F7       | F6         | F5            | F4         | F3         | F2        | F1        | F0        | 00H              |

| DPTR:<br>DPH | Data pointer<br>(2 bytes):<br>High byte | 83H        |          |            |               |            |            |           |           |           | 00H              |

| DPL          | Low byte                                | 82H        |          |            |               |            |            |           |           |           | 00H              |

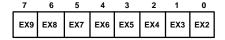

| IP0*#        | Into recent priority (                  | DOLL       | BF       | BE<br>_    | BD<br>PS1     | BC         | BB<br>PT1  | BA<br>PX1 | B9<br>PT0 | B8<br>PX0 | xx000000B        |

| IPU #        | Interrupt priority 0                    | B8H        | FF       | FE         | FD            | FC         | FB         | FA        | F9        | F8        | XXUUUUUUB        |

| IP1*#        | Interrupt priority 1                    | F8H        | PX9      | PX8        | PX7           | PX6        | PX5        | PX4       | PX3       | PX2       | 00H              |

|              |                                         |            |          | •          |               |            |            |           |           |           | 1                |

|              |                                         |            | AF       | AE         | AD            | AC         | AB         | AA        | A9        | A8        | _                |

| IEN0*#       | Interrupt enable 0                      | A8H        | EA       | _          | ES1           | _          | ET1        | EX1       | ET0       | EX0       | 00H              |

|              |                                         |            | EF       | EE         | ED            | EC         | EB         | EA        | E9        | E8        | 4                |

| IEN1*#       | Interrupt enable 1                      | E8H        | EX9      | EX8        | EX7           | EX6        | EX5        | EX4       | EX3       | EX2       | 00H              |

|              |                                         |            | C7       | C6         | C5            | C4         | C3         | C2        | C1        | C0        | 1                |

| IRQ1*#       | Interrupt request flag                  | C0H        | IQ9      | IQ8        | IQ7           | IQ6        | IQ5        | IQ4       | IQ3       | IQ2       | 00H              |

| IX1#         | Interrupt polarity                      | E9H        |          |            |               |            |            |           |           |           | 00H              |

| P0*          | Port 0                                  | 80H        | 87       | 86         | 85            | 84         | 83         | 82        | 81        | 80        | FFH              |

| P1*          | Port 1                                  | 90H        | 97       | 96         | 95            | 94         | 93         | 92        | 91        | 90        | FFH              |

| P2*          | Port 2                                  | A0H        | A7       | A6         | A5            | A4         | А3         | A2        | A1        | Α0        | FFH              |

| P3*          | Port 3                                  | ВОН        | B7       | B6         | B5            | B4         | В3         | B2        | B1        | В0        | FFH              |

| PCON         | Power control                           | 87H        | SMOD     | _          | _             | _          | GF1        | GF0       | PD        | IDL       | 0xxx0000B        |

|              |                                         |            | D7       | D6         | D5            | D4         | D3         | D2        | D1        | D0        |                  |

| PSW*         | Program status word                     | D0H        | CY       | AC         | F0            | RS1        | RS0        | OV        |           | P         | 00H              |

|              |                                         |            |          | •          |               |            | •          |           |           |           | 1                |

| S1ADR#       | Slave address                           | DBH        | DE       | DE         | DD            | <b>D</b> O | <b>D</b> D | D.4       | Do        | Do        | 00H              |

| S1CON*#      | Serial control                          | D8H        | DF<br>-  | DE<br>ENS1 | DD<br>STA     | DC<br>STO  | DB<br>SI   | DA<br>AA  | D9<br>CR1 | D8<br>CR0 | x0000000B        |

| S1DAT#       | Serial data                             | DAH        |          | LINOT      | OIA           | 010        |            | AA        | OKT       | ONO       | 00H              |

| S1STA#<br>SP | Serial status Stack pointer             | D9H<br>81H |          |            |               |            |            |           |           |           | 11111000B<br>07H |

| O.           | Clack pointor                           | 0111       | 8F       | 8E         | 8D            | 8C         | 8B         | 8A        | 89        | 88        |                  |

| TCON*        | Timer/counter con-<br>trol              | 88H        | TF1      | TR1        | TF0           | TR0        | IE1        | IT1       | IE0       | IT0       | 00H              |

| TMOD         | Timer/counter mode                      | 89H        | GATE     | C/T        | M1            | МО         | GATE       | C/T       | M1        | МО        | 00Н              |

| TH0          | Timer/counter mode Timer 0 high byte    | 8CH        | GAIE     | L C/ I     | IVII          | IVIU       | J GAIE     | C/ I      | IVII      | IVIU      | 00H              |

|              | Timer 1 high byte                       | l .        |          |            |               |            |            |           |           |           |                  |

| TH1          | 1                                       | 8DH<br>8AH |          |            |               |            |            |           |           |           | 00H<br>00H       |

| TL0          | Timer 0 low byte                        |            |          |            |               |            |            |           |           |           |                  |

| TL1          | Timer 1 low byte                        | 8BH        |          |            |               |            |            |           |           |           | 00H              |

<sup>\*</sup> SFRs are bit addressable.

<sup>#</sup> SFRs are modified from or added to the 80C51 SFRs.

## Low voltage/low power single-chip 8-bit microcontroller with I<sup>2</sup>C

#### 80CL410/83CL410

#### **PORT OPTIONS**

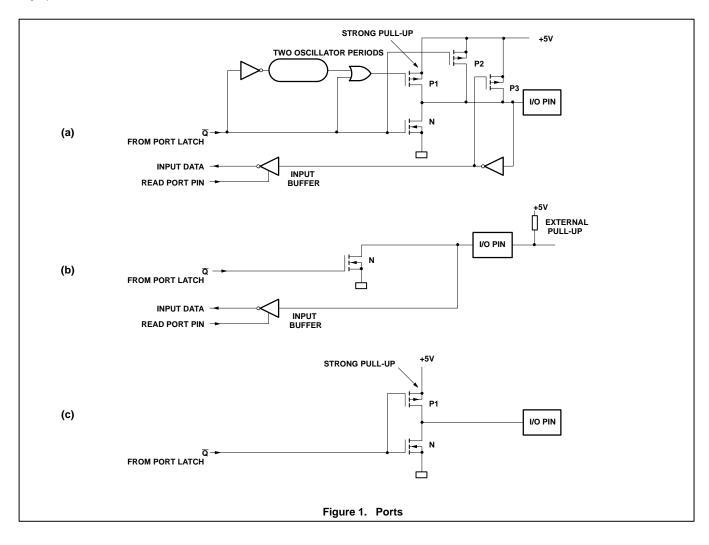

The pins of port 1 (not P1.6/SCL or P1.7/SDA), port 2, and port 3 may be individually configured with one of the following port options (see Figure 1):

Option 1: Standard Port-

quasi-bidirectional I/O with pull-up. The strong booster pull-up p1 is turned on for two oscillator periods after a 0-to-1 transition in the port latch. See Figure 1(a).

Option 2: **Open Drain**—quasi-bidirectional I/O with n-channel open drain output. Use as an output requires the connection of an external pull-up resistor. See Figure 1(b).

Option 3: **Push-Pull**—output with drive capability in both polarities. Under this option, pins can only be used as outputs. See Figure 1(c).

The definition of port options for port 0 is slightly different.

Two cases have to be examined. First, accesses to external memory (EA = 0 or access above the built-in memory boundary), and second, I/O accesses.

#### **External Memory Accesses**

Option 1: True 0 and 1 are written as address to the external memory (strong pull-up is used).

Option 2: An external pull-up resistor is needed for external accesses.

Option 3: Not allowed for external memory accesses as the port can only be used as output.

#### I/O Accesses

Option 1: When writing a 1 to the port latch, the strong pull-up p1 will be on for two oscillator periods. No weak pull-up exists. Without an external pull-up, this option can be used as a high-impedance input.

Option 2: Open drain—quasi-bidirectional I/O with n-channel open drain output. Use as an output requires the connection of an external pull-up resistor. See Figure 1(c).

Option 3: Push-Pull—output with drive capability in both polarities. Under this option, pins can only be used as outputs.

Individual mask selection of the post-reset state is available on any of the above pins. Make your selection by appending "S" or "R" to option 1, 2, or 3 above (e.g., 1S for a standard I/O to be set after RESET or 2R for an open-drain I/O to be reset after RESET.

Option S: **Set**—after reset, this pin will be initialized High.

Option R: **Reset**—after reset, this pin will be initialized I ow.

### Low voltage/low power single-chip 8-bit microcontroller with I<sup>2</sup>C

#### 80CL410/83CL410

#### **POWER-DOWN MODE**

The instruction setting PCON.1 is the last executed prior to going into the power-down mode. In power-down mode, the oscillator is stopped. The contents of the the on-chip RAM and SFRs are preserved. The port pins output the values held by their respective SFRs. ALE and PSEN are held low.

In the power-down mode, V<sub>DD</sub> may be reduced to minimize power consumption. However, the supply voltage must not be reduced until the power-down mode is active, and must be restored before the hardware reset is applied and frees the oscillator. Reset must be held active until the oscillator has restarted and stabilized.

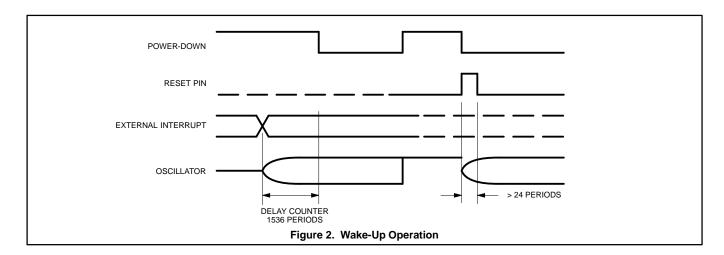

From the power-down mode the part can be restarted by using either the wake-up mode or the Reset Mode.

#### Wake-Up Mode

Setting both PD and IDL bits in the PCON register forces the controller into the power-down mode. Setting both bits enable the controller to be woken-up from the power-down mode via either an enabled external interrupt INT2–INT9, or a reset operation.

An external interrupt for an enabled interrupt INT2–INT9 at port 1 starts both the oscillator and the delay counter. To ensure that the oscillator is stable before the controller restarts, the internal clock will remain inactive for 1536 oscillator periods after the interrupt

is detected. This is controlled by the on-chip delay counter. After this, the PD flag will be reset, the controller is now in the Idle mode and the interrupt will be handled in the normal way.

#### **Reset Mode**

Setting only the PD bit in the PCON register again forces the controller into the power-down mode, but in this case it can only be restored to normal operation with a direct reset operation.

To restore normal operation, the RESET pin has to be kept High for a minimum of 24 oscillator periods. The on-chip delay counter is inactive. The user has to insure that the oscillator is stable before any operation is attempted. Figure 2 illustrates the two possibilities for wake-up.

#### **IDLE MODE**

The instruction that sets PCON.0 is the last instruction executed before going into idle mode. In idle mode, the internal clock is stopped for the CPU, but not for the interrupt, timer, and serial port functions. The CPU status is preserved along with the stack pointer, program counter, program status word and accumulator. The RAM and all other registers maintain their data during idle mode. The port pins retain the logical states they held at idle mode activation. ALE and PSEN hold at the logic high level.

There are two methods used to terminate the idle mode. Activation of any interrupt will cause PCON to be cleared by hardware; terminating idle mode. The interrupt is serviced, and following the instruction RETI, the next instruction to be executed will be the one following the instruction that put the device in the the idle mode.

Flag bits GF0 and GF1 can be used to determine whether the interrupt was received during normal execution or idle mode. For example, the instruction that writes to PCON.0 can also set or clear one or both flag bits. When idle mode is terminated by an interrupt, the service routine can examine the status of the flag bits.

The second method of terminating the idle mode is with an external hardware reset. Since the oscillator is still running, the hardware reset is required to be active for only two machine cycles to complete the reset operation. Reset redefines all SFRs, but does not affect the state of the on-chip RAM.

The status of the external pins during idle and power-down mode is shown in Table 2. If the power-down mode is activated while accessing external memory, port data held in the special function register P2 is restored to port 2. If the data is a logic 1, the port pin is held high during the power-down mode.

Table 2.

External Pin Status During Idle and Power-Down Modes

| MODE       | PROGRAM MEMORY | ALE | PSEN | PORT 0   | PORT 1 | PORT 2  | PORT 3 |

|------------|----------------|-----|------|----------|--------|---------|--------|

| Idle       | Internal       | 1   | 1    | Data     | Data   | Data    | Data   |

| Idle       | External       | 1   | 1    | Floating | Data   | Address | Data   |

| Power-down | Internal       | 0   | 0    | Data     | Data   | Data    | Data   |

| Power-down | External       | 0   | 0    | Floating | Data   | Data    | Data   |

## Low voltage/low power single-chip 8-bit microcontroller with I<sup>2</sup>C

#### 80CL410/83CL410

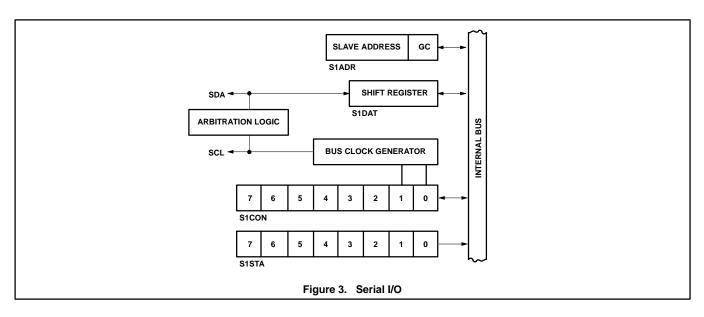

#### I<sup>2</sup>C-BUS SERIAL I/O

The serial port supports the twin line I<sup>2</sup>C-bus. The I<sup>2</sup>C-bus consists of a data line (SDA) and a clock line (SCL). These lines also function as I/O port lines P1.7 and P1.6 respectively. The system is unique because data transport, clock generation, address recognition and bus control arbitration are all controlled by hardware. The I<sup>2</sup>C-bus serial I/O has complete autonomy in byte handling and operates in four modes:

- Master transmitter

- Master receiver

- Slave transmitter

- Slave receiver

These functions are controlled by the S1CON register. S1STA is the status register whose contents may also be used as a vector to various service routines. S1DAT is the data shift register and S1ADR the slave address register. Slave address recognition is performed by hardware.

#### S1CON (D8H) Serial control register

| CR2 ENS1 STA STO SI AA CR1 CF |

|-------------------------------|

|-------------------------------|

#### CR0, CR1, CR2

These three bits determine the serial clock frequency when SIO is in a master mode.

AA

SI

Assert acknowledge bit. When the AA flag is set, an acknowledge (low level to SDA) will be returned during the acknowledge clock pulse on the SCL line when:

- own slave address is received

- general call address is received (S1ADR.0 = 1)

- data byte received while device is programmed as master

- data byte received while device is selected slave

With AA = 0, no acknowledge will be returned. Consequently, no interrupt is requested when the "own slave address" or general call address is received.

SIO interrupt flag. When the SI flag is set, an acknowledge is returned after any one of the following conditions:

- a start condition is generated in master mode

- own slave address received during AA = 1

- general call address received while S1ADR.0 and AA = 1

- data byte received or transmitted in master mode (even if arbitration is lost)

- data byte received or transmitted as selected slave

- stop or start condition received as selected slave receiver or transmitter

STO

STOP flag. With this bit set while in master mode, a STOP condition is generated. When a STOP condition is detected on the bus, the SIO hardware clears the STO flag. In the slave mode, the STO flag may also be set to recover from an error condition. In this case, no STOP condition is transmitted to the I<sup>2</sup>C-bus. However, the SIO hardware behaves as if a STOP condition has been received and releases SDA and SCL. The SIO then switches to the "not addressed" slave receiver mode. The STO flag is automatically cleared by hardware.

STA

START flag. When the STA bit is set in slave mode, the SIO hardware checks the status of the I<sup>2</sup>C-bus and generates a START condition if the bus is free. If STA is set while the SIO is in master mode, SIO transmits a repeated START condition.

ENS<sub>1</sub>

When ENS1 = 0, the SIO is disabled. The SDA and SCL outputs are in a high-impedance state; P1.6 and P1.7 function as open drain ports.

When ENS1 = 1, the SIO is enabled. The P1.6 and P1.7 port latches must be set to logic 1.

## Low voltage/low power single-chip 8-bit microcontroller with I<sup>2</sup>C

#### 80CL410/83CL410

#### S1STA (D9H) Status register

S1STA is an 8-bit read-only special function register. S1STA.3–S1STA.7 hold a status code. S1STA.0–S1STA.2 are held LOW. The contents of S1STA may be used as a vector to a service routine. This optimizes response time of the software and consequently that of the I<sup>2</sup>C-bus.

The following is a list of the status codes:

#### Abbreviations used:

SLA: 7-bit slave address

R: Read bit W: Write bit

ACK: Acknowledgement (acknowledge

bit = 0

ACK: Not Acknowledge (acknowledge

bit = 1)

DATA: 8-bit byte to or from the I<sup>2</sup>C-bus

MST: Master SLV: Slave TRX: Transmitter REC: Receiver

#### MST/TRX mode

S1STA value

08H – a START condition has been transmitted

10H – a repeated START condition has been transmitted

18H – SLA and W have been transmitted, ACK received

20H – SLA and W have been transmitted, ACK received

28H – DATA of S1DAT has been transmitted, ACK received

30H – DATA of S1DAT has been transmitted, ACK received

38H - Arbitration lost in SLA, R/W or DATA

#### MST/REC mode

S1STA value

08H – a START condition has been transmitted

10H – a repeated START condition has been transmitted

38H - Arbitration lost while returning ACK

40H – SLA and R have been transmitted, ACK received

48H – SLA and R have been transmitted, ACK received

50H – DATA has been received, ACK returned

58H – DATA has been received, ACK returned

#### SLV/REC mode

S1STA value

60H – Own SLA and W have been received, ACK returned

68H – Arbitration lost in SLA, R/W as MST. Own SLA and W have been received, ACK returned

70H - General CALL has been received, ACK returned

78H – Arbitration lost in SLA, R/W as MST. General CALL has been received

80H – Previously addressed with own SLA.

DATA byte received, ACK returned

88H – Previously addressed with own SLA.

DATA byte received, ACK returned

90H – Previously addressed with general CALL. DATA byte has been received, ACK has been returned

98H – Previously addressed with general CALL. DATA byte has been received, ACK has been returned

A0H – A STOP condition or repeated START condition has been received while still addressed as SLV/REC or SLV/TRX

#### SLV/TRX mode

S1STA value

A8H - Own SLA and R have been received, ACK returned

B0H – Arbitration lost in SLA, R/W as MST. Own SLA and R have been received, ACK returned

B8H – DATA byte has been transmitted, ACK received

COH – DATA byte has been transmitted, ACK received

C8H – Last DATA byte has been transmitted (AA = logic 0), ACK received

#### Miscellaneous

S1STA value

00H – Bus error during MST mode or selected SLV mode, due to an erroneous START or STOP condition

F8H – No relevant state interruption available, SI = 0.

## S1DAT (DAH) Data Shift Register

| Data Gillit Hogistor |   |   |   |   |   |   |   |

|----------------------|---|---|---|---|---|---|---|

| 7                    | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

#### Data shift register S1DAT

This register contains the serial data to be transmitted or data that has just been received. Bit 7 is transmitted or received first, i.e., data is shifted from left to right.

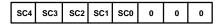

## S1ADR (DBH) Slave Address Register

| Olave Address Register |   |   |   |   |   |   |   |  |

|------------------------|---|---|---|---|---|---|---|--|

| 7                      | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

S1ADR.0, GC: 0 = general CALL address is not recognized

1 = general CALL address is recognized

S1ADR.7-1: own slave address

This 8-bit register may be loaded with the 7-bit slave address, to which the controller will respond when programmed as a slave receiver/transmitter. The LSB bit (GC) is used to determine whether the general CALL address is recognized.

Table 3. SCL Frequency

|     |     |     |                             |         | BIT RATE (kHz) at foso | ;     |

|-----|-----|-----|-----------------------------|---------|------------------------|-------|

| CR2 | CR1 | CR0 | f <sub>OSC</sub> DIVIDED BY | 3.58MHz | 6MHz                   | 12MHz |

| 0   | 0   | 0   | 256                         | 14.0    | 23.4                   | 46.9  |

| 0   | 0   | 1   | 224                         | 16.0    | 26.8                   | 53.6  |

| 0   | 1   | 0   | 192                         | 18.6    | 31.3                   | 62.5  |

| 0   | 1   | 1   | 160                         | 22.4    | 37.5                   | 75.0  |

| 1   | 0   | 0   | 960                         | 3.73    | 6.25                   | 12.5  |

| 1   | 0   | 1   | 120                         | 29.8    | 50                     | 100   |

| 1   | 1   | 0   | 60                          | 59.7    | 100                    | -     |

| 1   | 1   | 1   | not allowed                 | -       | _                      | -     |

## Low voltage/low power single-chip 8-bit microcontroller with I<sup>2</sup>C

### 80CL410/83CL410

#### INTERRUPT SYSTEM

External events and the real-time-driven on-chip peripherals require service by the CPU asynchronous to the execution of any particular section of code. To tie the asynchronous activities of these functions to normal program execution, a multiple-source, two-priority level, nested interrupt system is provided. The 8XCL410 acknowledges interrupt requests from thirteen sources, as follows:

- INT0 and INT1

- Timer 0 and timer 1

- I<sup>2</sup>C-bus serial I/O interrupt

- INT2 to INT9 (port 1)

Each interrupt vectors to a separate location in program memory for its service routine. Each source can be individually enabled or disabled by corresponding bits in the internal enable registers (IEN0, IEN1) The priority level is selected via the interrupt priority register (IP0, IP1). All enabled sources can be globally disabled or enabled.

#### **External Interrupts INT2-INT9**

Port 1 lines serve an alternative purpose as eight additional interrupts INT2–INT9. When enabled, each of these lines can "wake-up" the device from power-down mode. Using the IX1 register, each pin may be initialized to either active high or low. IRQ1 is the interrupt request flag register. Each flag, if the interrupt is enabled, will be set on an interrupt request but it must be cleared by software.

#### IEN0 (A8H) Interrupt enable register

| 7  | 6 | 5   | 4 | 3   | 2   | 1   | 0   |

|----|---|-----|---|-----|-----|-----|-----|

| EA | _ | ES1 | - | ET1 | EX1 | ET0 | EX0 |

| Bit    | Symbol | Function                              |

|--------|--------|---------------------------------------|

| IEN0.7 | EEA    | General enable/disable                |

|        |        | control                               |

|        |        | 0 = no interrupt is enabled           |

|        |        | 1 = any individually enabled          |

|        |        | interrupt will be                     |

|        |        | accepted                              |

| IEN0.6 | _      | (unused)                              |

| IEN0.5 | ES1    | Enable I <sub>2</sub> C SIO interrupt |

| IEN0.4 | _      | (unused)                              |

| IEN0.3 | ET1    | Enable Timer T1 interrupt             |

| IEN0.2 | EX1    | Enable external interrupt 1           |

| IEN0.1 | ET0    | Enable Timer T0 interrupt             |

| IEN0.0 | EX0    | Enable external interrupt 0           |

#### IEN1 (E8H) Interrupt enable register

| Bit    | Symbol | Function                    |

|--------|--------|-----------------------------|

| IEN1.7 | EX9    | Enable external interrupt 9 |

| IEN1.6 | EX8    | Enable external interrupt 8 |

| IEN1.5 | EX7    | Enable external interrupt 7 |

| IEN1.4 | EX6    | Enable external interrupt 6 |

| IEN1.3 | EX5    | Enable external interrupt 5 |

| IEN1.2 | EX4    | Enable external interrupt 4 |

| IEN1.1 | EX3    | Enable external interrupt 3 |

| IEN1.0 | EX2    | Enable external interrupt 2 |

where 0 = interrupt disabled 1 = interrupt enabled

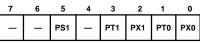

#### IP0 (B8H) Interrupt priority register

| Bit   | Symbol | Function                       |

|-------|--------|--------------------------------|

| IP0.7 | _      | (unused)                       |

| IP0.6 | _      | (unused)                       |

| IP0.5 | PS1    | I <sub>2</sub> C SIO interrupt |

|       |        | priority level                 |

| IP0.4 | _      | (unused)                       |

| IP0.3 | PT1    | Timer 1 interrupt              |

|       |        | prioity level                  |

| IP0.2 | PX1    | External interrupt 1           |

|       |        | priority level                 |

| IP0.1 | PT0    | Timer 0 interrupt              |

|       |        | prioity level                  |

| IP0.0 | PX0    | External interrupt 0           |

|       |        | priority level                 |

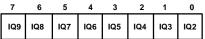

#### IP1 (F8H) Interrupt priority register

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|

| PX9 | PX8 | PX7 | PX6 | PX5 | PX4 | PX3 | PX2 |

| Bit   | Symbol | Function                            |

|-------|--------|-------------------------------------|

| IP1.7 | PX9    | External interrupt 9 priority level |

| IP1.6 | PX8    | External interrupt 8 priority level |

| IP1.5 | PX7    | External interrupt 7 priority level |

| IP1.4 | PX6    | External interrupt 6 priority level |

| IP1.3 | PX5    | External interrupt 5 priority level |

| IP1.2 | PX4    | External interrupt 4 priority level |

| IP1.1 | PX3    | External interrupt 3 priority level |

| IP1.0 | PX2    | External interrupt 2 priority level |

Interrupt priority is as follows:

0 - low priority

1 - high priority

#### IX1 (E9H) Interrupt polarity register

| _ 7 | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|

| IL9 | IL8 | IL7 | IL6 | IL5 | IL4 | IL3 | IL2 |

| Bit   | Symbol | Function                            |

|-------|--------|-------------------------------------|

| IX1.7 | ĬL9    | External interrupt 9 polarity level |

| IX1.6 | IL8    | External interrupt 8 polarity level |

| IX1.5 | IL7    | External interrupt 7 polarity level |

| IX1.4 | IL6    | External interrupt 6 polarity level |

| IX1.3 | IL5    | External interrupt 5 polarity level |

| IX1.2 | IL4    | External interrupt 4 polarity level |

| IX1.1 | IL3    | External interrupt 3 polarity level |

| IX1.0 | IL2    | External interrupt 2 polarity level |

Writing either a "1" or "0" to an IX1 register bit sets the priority level of the corresponding external interrupt to active High or Low, respectively.

## Low voltage/low power single-chip 8-bit microcontroller with I<sup>2</sup>C

#### 80CL410/83CL410

#### IRQ1 (C0H) Interrupt request flag register

| Bit    | Symbol | Function                          |

|--------|--------|-----------------------------------|

| IRQ1.7 | IQ9    | External interrupt 9 request flag |

| IRQ1.6 | IQ8    | External interrupt 8 request      |

| IRQ1.5 | IQ7    | flag External interrupt 7 request |

| IRQ1.4 | IQ6    | flag External interrupt 6 request |

| IRQ1.3 | IQ5    | flag External interrupt 5 request |

| IRQ1.2 | IQ4    | flag External interrupt 4 request |

| IRQ1.1 | IQ3    | flag External interrupt 3 request |

| IRQ1.0 | IQ2    | flag                              |

| IKQ1.0 | IQZ    | External interrupt 2 request flag |

|              | ilag   |                       |

|--------------|--------|-----------------------|

| Priority     | Vector | Source                |

| X0 (highest) | 0003H  | External 0            |

| S1           | 002BH  | I <sup>2</sup> C port |

| X5           | 0053H  | External 5            |

| T0           | 000BH  | Timer 0               |

| X6           | 005BH  | External 6            |

| X1           | 0013H  | External 1            |

| X2           | 003BH  | External 2            |

| X7           | 0063H  | External 7            |

| T1           | 001BH  | Timer 1               |

| X3           | 0043H  | External 3            |

| X8           | 006BH  | External 8            |

| X4           | 004BH  | External 4            |

| X9 (lowest)  | 0073H  | External 9            |

| Registe |                                         | SFR<br>Address |

|---------|-----------------------------------------|----------------|

| IX1     | Interrupt polarity register             | E9H            |

| IRQ1    | Interrupt request flag<br>register      | C0H            |

| IEN0    | Interrupt enable register               | A8H            |

| IEN1    | Interrupt enable register (INT2–INT9)   | E8H            |

| IP0     | Interrupt priority register             | B8H            |

| IP1     | Interrupt priority register (INT2–INT9) | F8H            |

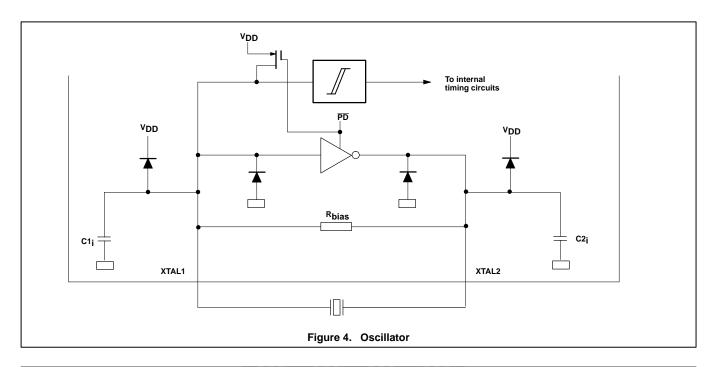

#### OSCILLATOR CIRCUITRY

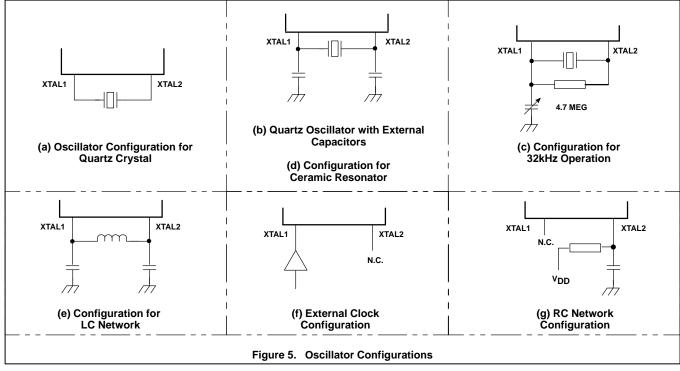

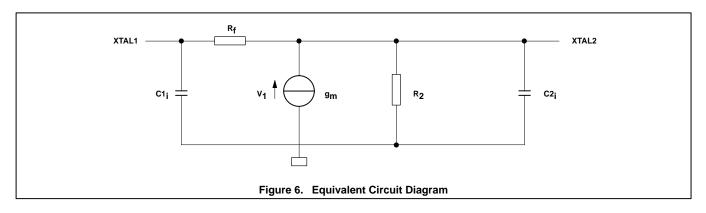

The on-chip oscillator circuitry of the 8XCL410 is a single stage inverting amplifier biased by an internal feedback resistor. (See Figure 4.) The oscillator can be operated with a quartz crystal, ceramic resonator, LC network or RC network. See Figure 5 for different configurations. When ordering parts, it is necessary to specify an oscillator option. The options are: RC when an RC network will be used, OSC 2 for oscillator operation below 4MHz, OSC 3 for oscillator operation from 4MHz to 10MHz, OSC 4 for oscillator operation above 10MHz, and 32kHz if 32kHz to 400kHz operation is desired.

For operation as a standard quartz oscillator, no external components are needed (except at 32KHz). When using external capacitors, ceramic resonators, coils, and RC networks to drive the oscillator, five different configurations are supported (see Figure 5 and Table 4).

In the power-down mode the oscillator is stopped and XTAL1 is pulled high. The oscillator inverter is switched off to ensure no current will flow. To drive the device with an external clock source, apply the external clock signal to XTAL1, and leave XTAL2 to float, as shown in Figure 5(f). There are no requirements on the duty cycle of the external clock, since the input to the internal clocking circuitry is split using a flip-flop.

The following options are provided for optimum on-chip oscillator performance. Please state option when ordering:

Osc.1: Figure 5(c). An option for 32kHz clock applications with external trimmer for frequency adjustment.

A 4.7M $\Omega$  bias resistor must be connected in parallel with the crystal.

Osc.2: Figure 5(e). An option for low-power, low-frequency operations using LC components or quartz.

Osc.3: An option for medium frequency range applications.

Osc.4: An option for high frequency range applications.

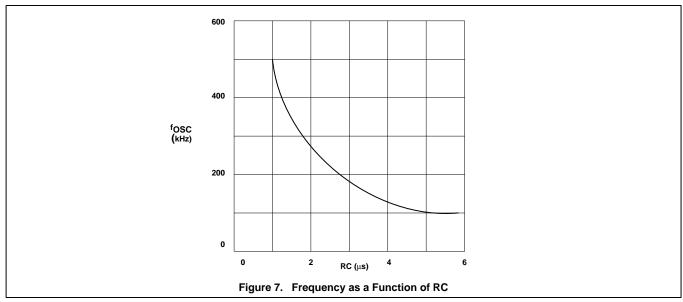

RC: Figure 5(g). An option for an RC oscillator.

The equivalent circuit data of the internal oscillator compares with that of matched crystals.

The externally adjustable RC oscillator has a frequency range from 100kHz to 500kHz. (See Figure 7.)

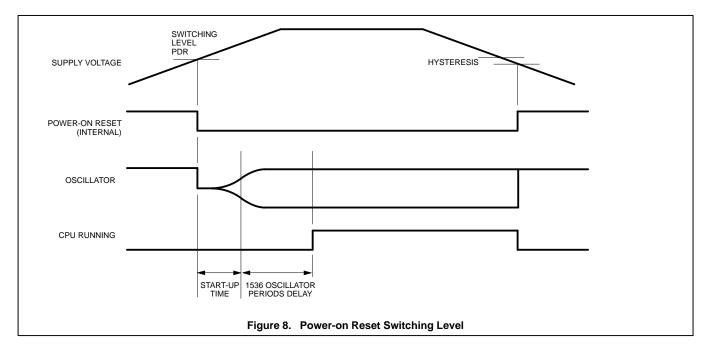

#### **Power-on Reset**

The 8XCL410 contains on-chip circuitry which switch the port pins to the customer-defined logic level as soon as V<sub>DD</sub> exceeds 1.3V if the mask option "ON" has been chosen (see Figures 8 and 9). As soon as the minimum supply voltage is reached, the oscillator will start up. However, to ensure that the oscillator is stable before the controller starts, the clock signals are gated away from the CPU for a further 1536 oscillator periods.

An hysteresis of approximately 50mV at a typical power-on switching level of 1.3V will ensure correct operation.

The on-chip power—on reset circuitry can also be switched off via the mask option "OFF". This option reduces the power-down current to typically 800µA and can be chosen if external reset circuitry is used. For applications not requiring the internal reset, option "OFF" should be chosen.

An automatic reset can be obtained at power-on by connecting the RST pin to  $V_{DD}$  via a  $10\mu F$  capacitor. At power-on, the voltage on the RST pin is equal to  $V_{DD}$  minus the capacitor voltage, and decreases from  $V_{DD}$  as the capacitor discharges through the internal resistor  $R_{RST}$  to ground. The larger the capacitor, the more slowly  $V_{RST}$  decreases.  $V_{RST}$  must remain above the lower threshold of the Schmitt trigger long enough to effect a complete reset. The time required is the oscillator start-up time, plus 2 machine cycles.

#### P80CL410: ROM-less VERSION OF P83CL410

The P80CL410 is a low voltage ROMless version of the P83CL410. The mask options on the P80CL410 are fixed as follows:

Port Options:

All ports except P16/P17 have option "1S", i.e., standard port, High after reset. The ports P16/P17 have option "2S", i.e., open drain, High after reset.

Oscillator option: OSC3

Power-on Reset option: OFF

## 80CL410/83CL410

# Low voltage/low power single-chip 8-bit microcontroller with I<sup>2</sup>C

80CL410/83CL410

Table 4. Oscillator Type Selection Guide

|           |         |        | C1  | EXT. | C2 EXT. |     | MAXIMUM RESONATOR                                               |

|-----------|---------|--------|-----|------|---------|-----|-----------------------------------------------------------------|

| RESONATOR | f (MHz) | OPTION | MIN | MAX  | MIN     | MAX | SERIES RESISTANCE                                               |

| Quartz    | 0.032   | Osc.1  | 5   | 15   | 0       | 0   | 15kΩ <sup>1</sup>                                               |

| Quartz    | 1.0     | Osc.2  | 0   | 30   | 0       | 30  | 600Ω                                                            |

| Quartz    | 3.58    | Osc.2  | 0   | 15   | 0       | 15  | 100Ω                                                            |

| Quartz    | 4.0     | Osc.2  | 0   | 20   | 0       | 20  | 75Ω                                                             |

| Quartz    | 6.0     | Osc.3  | 0   | 10   | 0       | 10  | 60Ω                                                             |

| Quartz    | 10.0    | Osc.4  | 0   | 15   | 0       | 15  | 60Ω                                                             |

| Quartz    | 12.0    | Osc.4  | 0   | 10   | 0       | 10  | 40Ω                                                             |

| Quartz    | 16.0    | Osc.4  | 0   | 15   | 0       | 15  | 20Ω                                                             |

| PXE       | 0.455   | Osc.2  | 40  | 50   | 40      | 50  | 10Ω                                                             |

| PXE       | 1.0     | Osc.2  | 15  | 50   | 15      | 50  | 100Ω                                                            |

| PXE       | 3.58    | Osc.2  | 0   | 40   | 0       | 40  | 10Ω                                                             |

| PXE       | 4.0     | Osc.2  | 0   | 40   | 0       | 40  | 10Ω                                                             |

| PXE       | 6.0     | Osc.2  | 0   | 20   | 0       | 20  | 5Ω                                                              |

| PXE       | 10.0    | Osc.3  | 0   | 15   | 0       | 15  | 6Ω                                                              |

| PXE       | 12.0    | Osc.4  | 10  | 40   | 10      | 40  | 6Ω                                                              |

| LC        |         | Osc.2  | 20  | 90   | 20      | 90  | $10\mu H = 1\Omega$<br>$100\mu H = 5\Omega$<br>$1mH = 75\Omega$ |

#### NOTE:

Table 5. Oscillator Equivalent Circuit Parameters (see Figure 6)

| PARAMETER          | OPTION                           | SYMBOL                                                                   | CONDITION                                                                                                                                        | MIN                     | TYP                       | MAX                        | UNIT                 |

|--------------------|----------------------------------|--------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|---------------------------|----------------------------|----------------------|

| Transconductance   | Osc.1<br>Osc.2<br>Osc.3<br>Osc.4 | 9m<br>9m<br>9m<br>9m                                                     | T = +25°C; V <sub>DD</sub> = 4.5V<br>T = +25°C; V <sub>DD</sub> = 4.5V<br>T = +25°C; V <sub>DD</sub> = 4.5V<br>T = +25°C; V <sub>DD</sub> = 4.5V | -<br>200<br>400<br>1000 | 15<br>600<br>1500<br>4000 | -<br>1000<br>4000<br>10000 | μs<br>μs<br>μs<br>μs |

| Input capacitance  | Osc.1<br>Osc.2<br>Osc.3<br>Osc.4 | c1 <sub>i</sub><br>c1 <sub>i</sub><br>c1 <sub>i</sub><br>c1 <sub>i</sub> |                                                                                                                                                  | -<br>-<br>-<br>-        | 3.0<br>8.0<br>8.0<br>8.0  | -<br>-<br>-<br>-           | pF<br>pF<br>pF<br>pF |

| Output capacitance | Osc.1<br>Osc.2<br>Osc.3<br>Osc.4 | c2 <sub>i</sub><br>c2 <sub>i</sub><br>c2 <sub>i</sub><br>c2 <sub>i</sub> |                                                                                                                                                  | -<br>-<br>-<br>-        | 23.0<br>8.0<br>8.0<br>8.0 | -<br>-<br>-                | pF<br>pF<br>pF<br>pF |

| Output resistance  | Osc.1<br>Osc.2<br>Osc.3<br>Osc.4 | R2<br>R2<br>R2<br>R2                                                     |                                                                                                                                                  | -<br>-<br>-<br>-        | 3800<br>65<br>18<br>5.0   |                            | kΩ<br>kΩ<br>kΩ<br>kΩ |

<sup>1.</sup> 32kHz quartz crystals with a series resistance higher than 15k $\Omega$  will reduce the guaranteed supply voltage range to 2.5 to 3.5V.

## 80CL410/83CL410

## Low voltage/low power single-chip 8-bit microcontroller with I<sup>2</sup>C

### 80CL410/83CL410

#### **ABSOLUTE MAXIMUM RATINGS 1, 2, 3**

| PARAMETER                           | RATING                       | UNIT |

|-------------------------------------|------------------------------|------|

| Supply voltage                      | -0.5 to +6.5                 | V    |

| All input voltages                  | −0.5 to V <sub>DD</sub> +0.5 | V    |

| DC current into any input or output | 5                            | mA   |

| Total power dissipation             | 300                          | mW   |

| Storage temperature range           | -65 to +150                  | °C   |

| Operating ambient temperature range | -40 to +85                   | °C   |

| Operating junction temperature      | 125                          | °C   |

#### NOTES:

- Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any conditions other than those described in the AC and DC Electrical Characteristics section of this specification is not implied.

- 2. This product includes circuitry specifically designed for the protection of its internal devices from the damaging effects of excessive static charge. Nonetheless, it is suggested that conventional precautions be taken to avoid applying greater than the rated maxima.

- 3. Parameters are valid over operating temperature range unless otherwise specified. All voltages are with respect to V<sub>SS</sub> unless otherwise noted

### Low voltage/low power single-chip 8-bit microcontroller with I<sup>2</sup>C

80CL410/83CL410

#### DC ELECTRICAL CHARACTERISTICS

$T_{amb} = -40^{\circ}C \text{ to } +85^{\circ}C, V_{SS} = 0V$

|                  |                                                                                                                                                                                                                    | TEST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | LIM                |                                                               |                                              |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|---------------------------------------------------------------|----------------------------------------------|--|

| SYMBOL           | PARAMETER                                                                                                                                                                                                          | CONDITIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | MIN MAX            |                                                               | UNIT                                         |  |

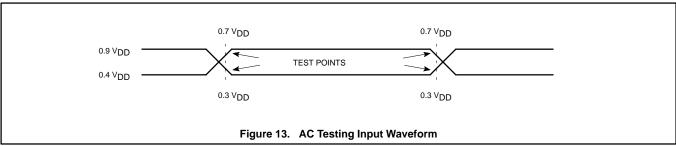

| $V_{DD}$         | Supply voltage<br>RAM retention voltage in power-down mode                                                                                                                                                         | f <sub>CLK</sub> (see Figure 13)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1.8<br>1.0         | 6.0<br>—                                                      | V<br>V                                       |  |

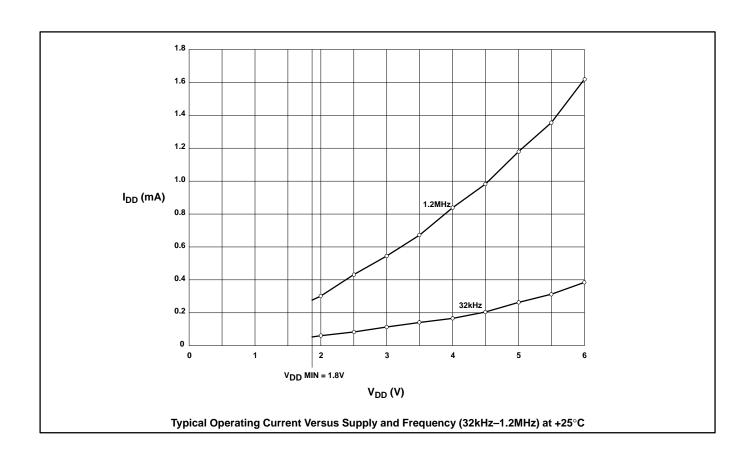

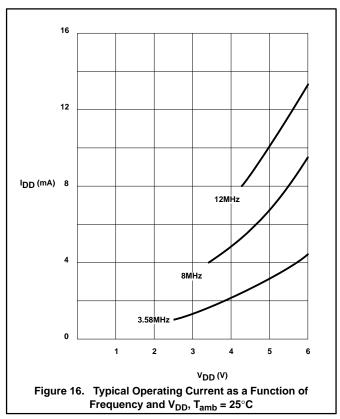

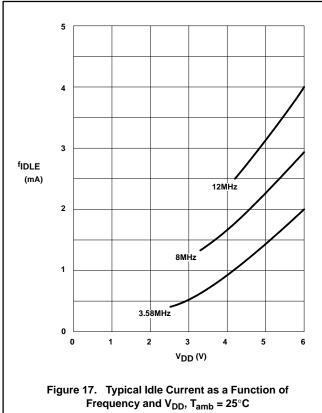

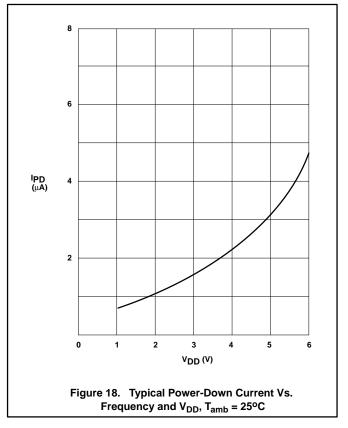

| I <sub>DD</sub>  | Power supply current: Operating <sup>1</sup> OSC 1 option OSC 2 option OSC 2 option OSC 3 option OSC 4 option Idle mode <sup>2</sup> OSC 1 option OSC 2 option OSC 2 option OSC 2 option OSC 3 option OSC 4 option | $\begin{split} f_{CLK} = 32 \text{kHz},  V_{DD} = 1.8 \text{V},  T_{amb} = +25^{\circ}\text{C} \\ f_{CLK} = 3.58 \text{MHz},  V_{DD} = 3 \text{V} \\ f_{CLK} = 10 \text{MHz},  V_{DD} = 5 \text{V} \\ f_{CLK} = 12 \text{MHz},  V_{DD} = 5 \text{V} \\ f_{CLK} = 12 \text{MHz},  V_{DD} = 5 \text{V} \end{split}$ $f_{CLK} = 32 \text{kHz},  V_{DD} = 1.8 \text{V},  T_{amb} = +25^{\circ}\text{C} \\ f_{CLK} = 3.58 \text{MHz},  V_{DD} = 3 \text{V} \\ f_{CLK} = 10 \text{MHz},  V_{DD} = 5 \text{V} \\ f_{CLK} = 12 \text{MHz},  V_{DD} = 5 \text{V} \\ f_{CLK} = 12 \text{MHz},  V_{DD} = 5 \text{V} \end{split}$ |                    | 50<br>2.5<br>14<br>16<br>20<br>25<br>1.0<br>5.0<br>7.0<br>8.5 | μΑ<br>mA<br>mA<br>mA<br>μΑ<br>mA<br>mA<br>mA |  |

|                  | Power-down mode <sup>3</sup>                                                                                                                                                                                       | $V_{DD} = 1.8V, T_{amb} = +25^{\circ}C$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | _                  | 10                                                            | μΑ                                           |  |

| $V_{IL}$         | Input low voltage                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | $V_{SS}$           | 0.3V <sub>DD</sub>                                            | V                                            |  |

| V <sub>IH</sub>  | Input high voltage                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0.7V <sub>DD</sub> | $V_{DD}$                                                      | V                                            |  |

| I <sub>OL</sub>  | Output sink current, except SDA, SCL                                                                                                                                                                               | $V_{DD} = 5V, V_{OL} = 0.4V$<br>$V_{DD} = 2.5V, V_{OL} = 0.4V$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1.6<br>0.7         |                                                               | mA<br>mA                                     |  |

| I <sub>OL1</sub> | Output sink current, SDA, SCL                                                                                                                                                                                      | V <sub>DD</sub> = 5V, V <sub>OL</sub> = 0.4V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 3.0                |                                                               | mA                                           |  |

| I <sub>OH</sub>  | Output source current (push-pull options only)                                                                                                                                                                     | $V_{DD} = 5V, V_{OH} = V_{DD} - 0.4V$<br>$V_{DD} = 2.5V, V_{OH} = V_{DD} - 0.4V$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1.6<br>0.7         |                                                               | mA<br>mA                                     |  |

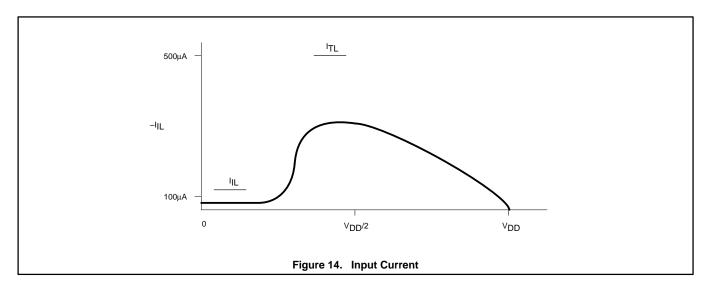

| I <sub>IL</sub>  | Logical 0 input current, ports 1, 2, 3                                                                                                                                                                             | $V_{DD} = 5V, V_{IN} = 0.4V$<br>$V_{DD} = 2.5V, V_{IN} = 0.4V$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                    | –100<br>–50                                                   | μΑ<br>μΑ                                     |  |

| I <sub>TL</sub>  | Logical 1-to-0 transition current, ports 1, 2, 3                                                                                                                                                                   | $V_{DD} = 5V, V_{IN} = V_{DD}/2$<br>$V_{DD} = 2.5V, V_{IN} = V_{DD}/2$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                    | -1.0<br>-500                                                  | mA<br>μA                                     |  |