# TC9327BFG

## DTS Microcontroller (DTS-21)

The TC9327BFG is a 4-bit CMOS microcontroller for single-chip digital tuning systems, featuring a built-in 230-MHz prescaler, PLL, and LCD drivers.

The CPU has 4-bit parallel addition and subtraction instructions (e.g., AI, SI), logic operation instructions (e.g., OR, AN), composite decision and comparison instructions (e.g., TM, SL), and time-base functions.

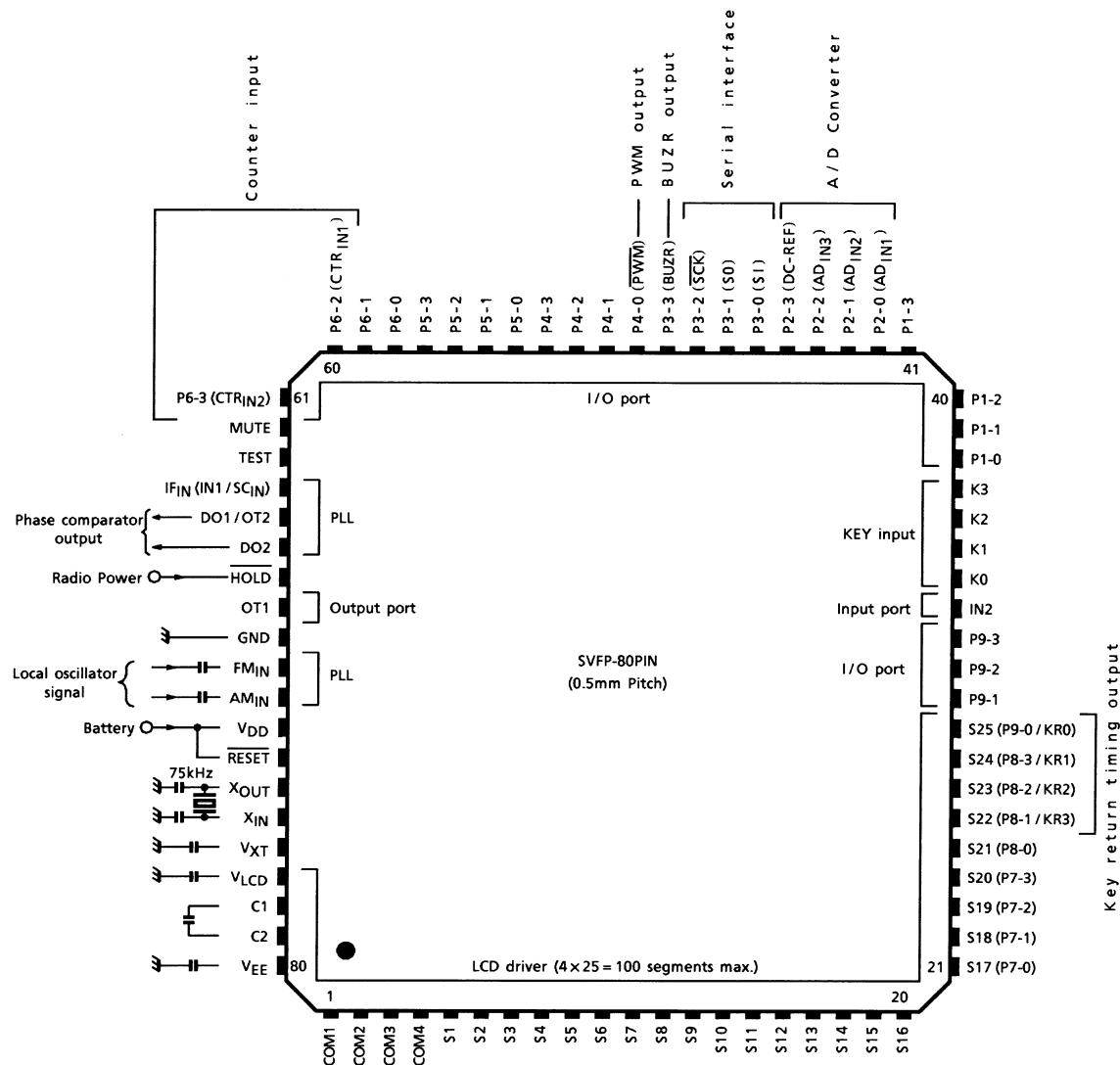

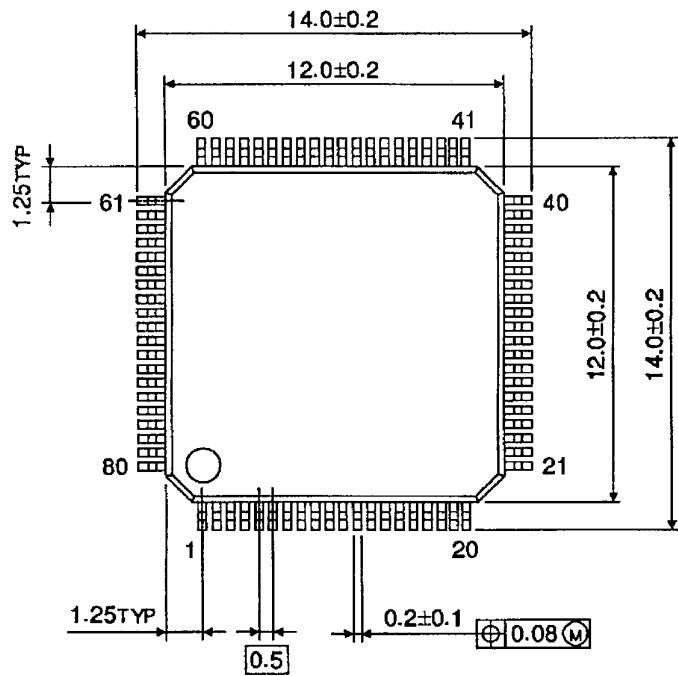

The package is an 80-pin, 0.5 mm-pitch compact package. In addition to various input/output ports and a dedicated key-input port, which are controlled by powerful input/output instructions (IN1 to 3, OUT1 to 3), there are many dedicated LCD pins, a PWM output port, a BUZR port, a 6-bit A/D converter, a serial interface, and an IF counter, etc.

Low-voltage and low-current consumption make this microcontroller suitable for portable DTS equipment.

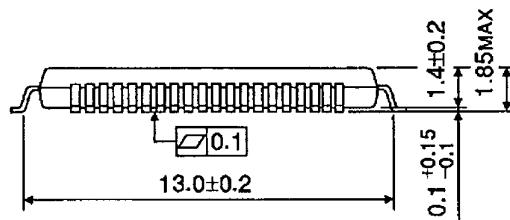

LQFP80-P-1212-0.50A

Weight: 0.45 g (typ.)

## Features

- 4 bit microcontroller for single-chip digital tuning systems.

- Operating voltage  $V_{DD} = 1.8$  to  $3.6$  V, with low current consumption due to CMOS circuitry (with only the CPU operating when  $V_{DD} = 3$  V,  $I_{DD} = 100 \mu A$  max)

- Built-in prescaler (1/2 fixed divider +2 modulus prescaler:  $f_{max} \geq 230$  MHz)

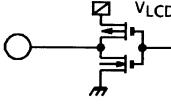

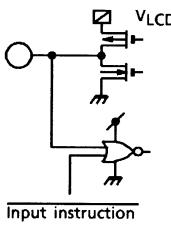

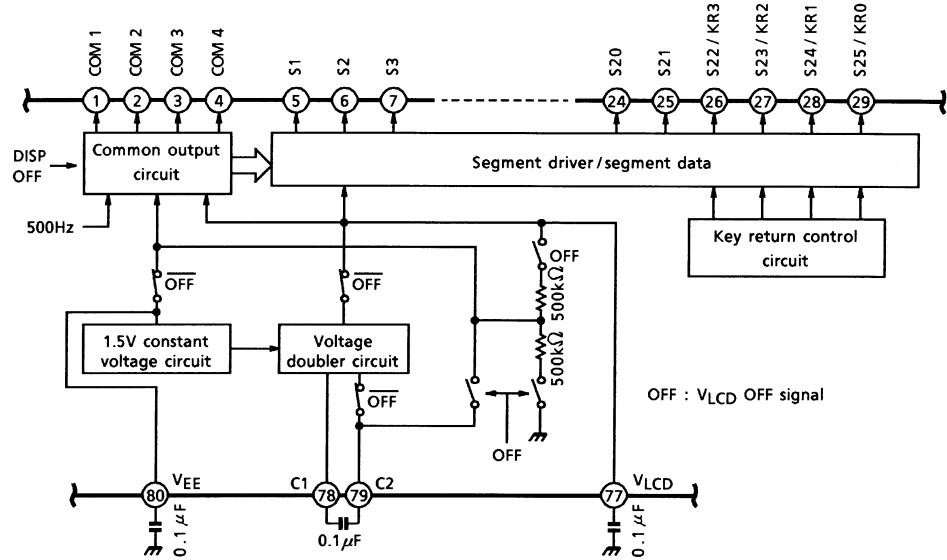

- Features built-in 1/4-duty, 1/2-bias LCD drivers and a built-in 3 V booster circuit for the display.

- Data memory (RAM) and ports are easily backed up.

- Program memory (ROM):  $16$  bit  $\times 7168$  steps

- Data memory (RAM): 4 bit  $\times 256$  words

- 62-instruction set (all one-word instructions)

- Instruction execution time: 40  $\mu s$  (with 75-kHz crystal) (MVGS, DAL instructions: 80  $\mu s$ )

- Many addition and subtraction instructions (12 types each addition and subtraction)

- Powerful composite decision instructions (TMTR, TMFR, TMT, TMF, TMTN, TMFN)

- Data can be transmitted between addresses on the same row.

- Register indirect transfer available (MVGD, MVGS instructions).

- 16 powerful general registers (located in RAM)

- Stack levels: 2

- Free branching (JUMP instructions) is allowed in the 7168 steps of program memory (ROM) as there are no pages or fields.

- 16 bits of any address in the 1024 program memory steps (ROM) can be referenced (DAL instructions).

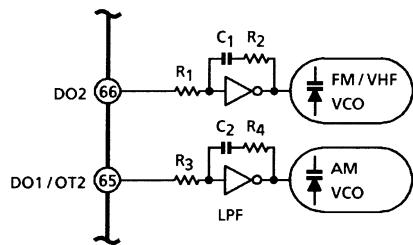

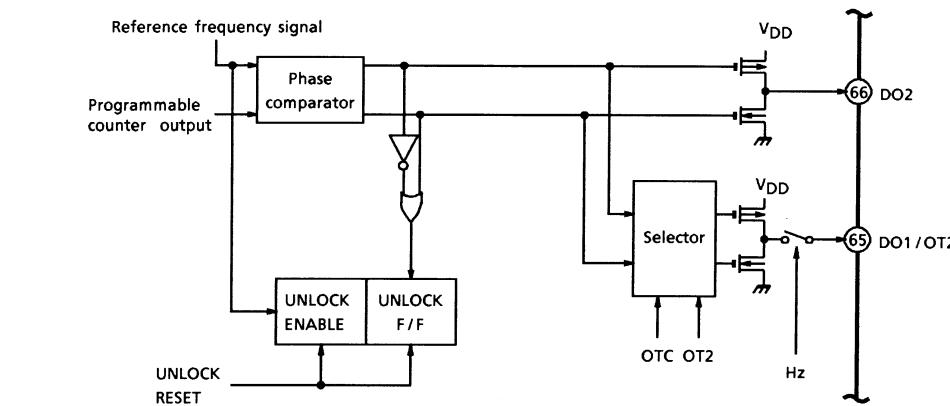

- Features independent frequency input pins (FMIN and AMIN) and two (DO1 and DO2) phase comparator outputs for FM/VHF and AM.

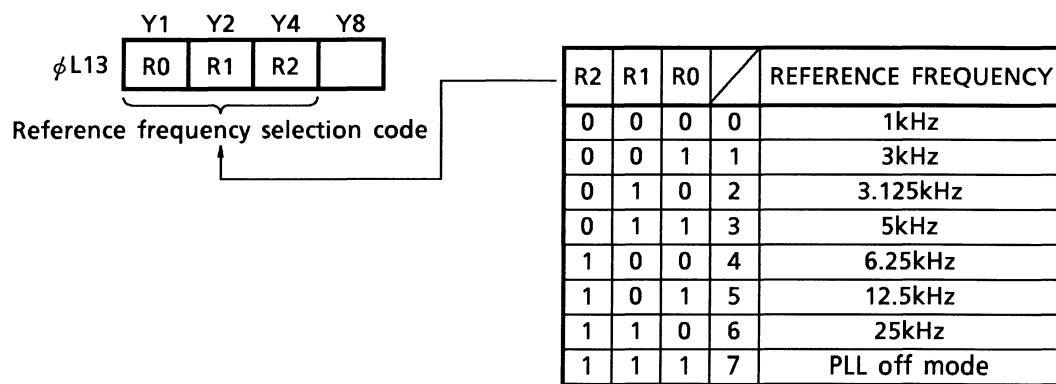

- Seven kinds of reference frequencies can be selected via software.

- Powerful input/output instructions (IN1 to 3, OUT1 to 3).

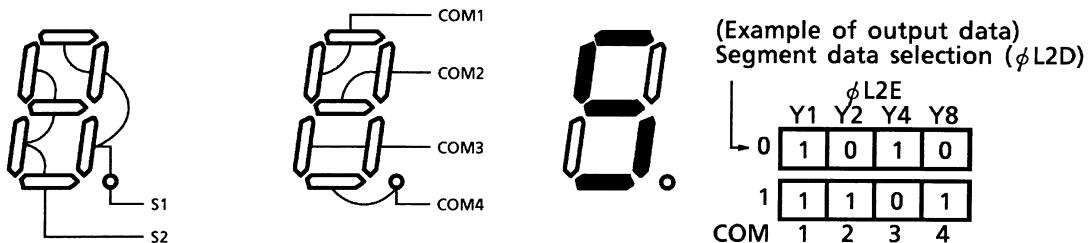

- Dedicated input ports (K0 to K3) for key input, 29 LCD drive pins (100 segments maximum) available.

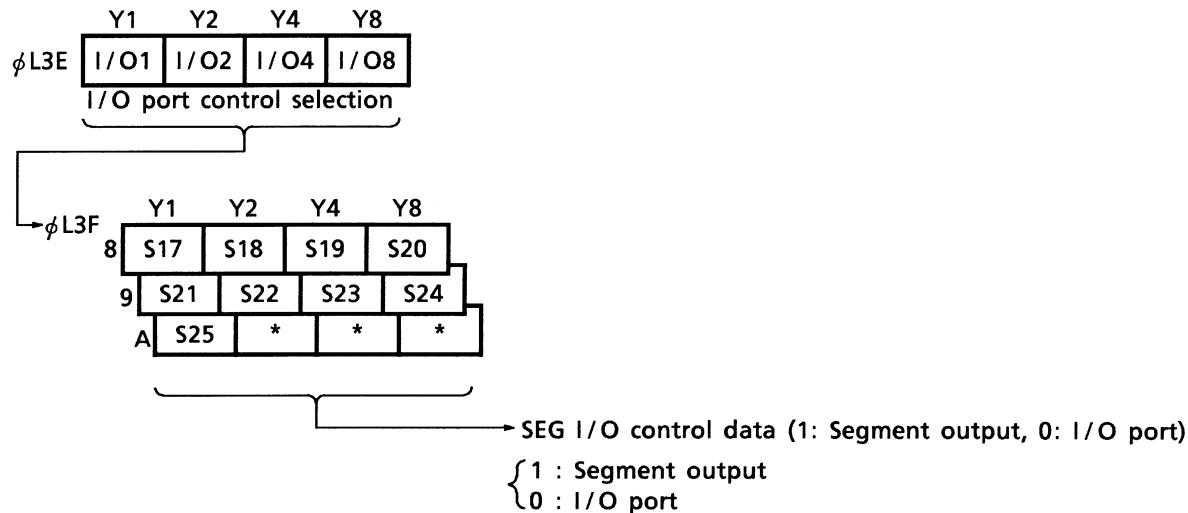

- 29 I/O ports: 27 input/output programmable in 1-bit units, 1 output-only port, and 1 input-only port. The 2 IFIN, and DO1 pins can be switched by instruction to IN1 (input-only) or OT2 (output-only). In addition, 9 output LCD output pins for S17 to S25 can be switched to I/O port in 1-bit units.

- Three backup modes available by instruction: Only CPU operation, crystal oscillation only, clock stop.

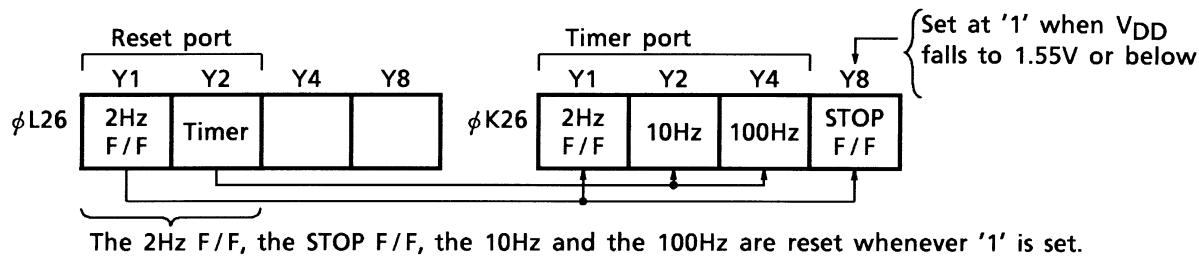

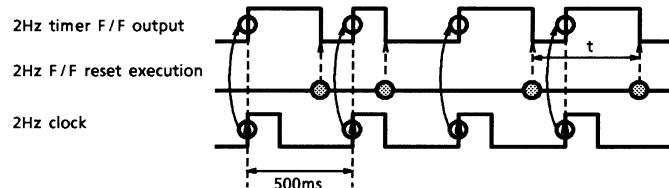

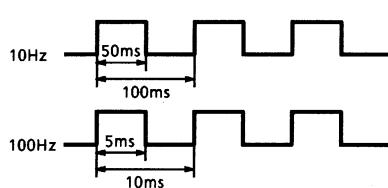

- Features a built-in 2-Hz timer F/F and a built-in 10/100 Hz interval pulse outputs (internal port for time base).

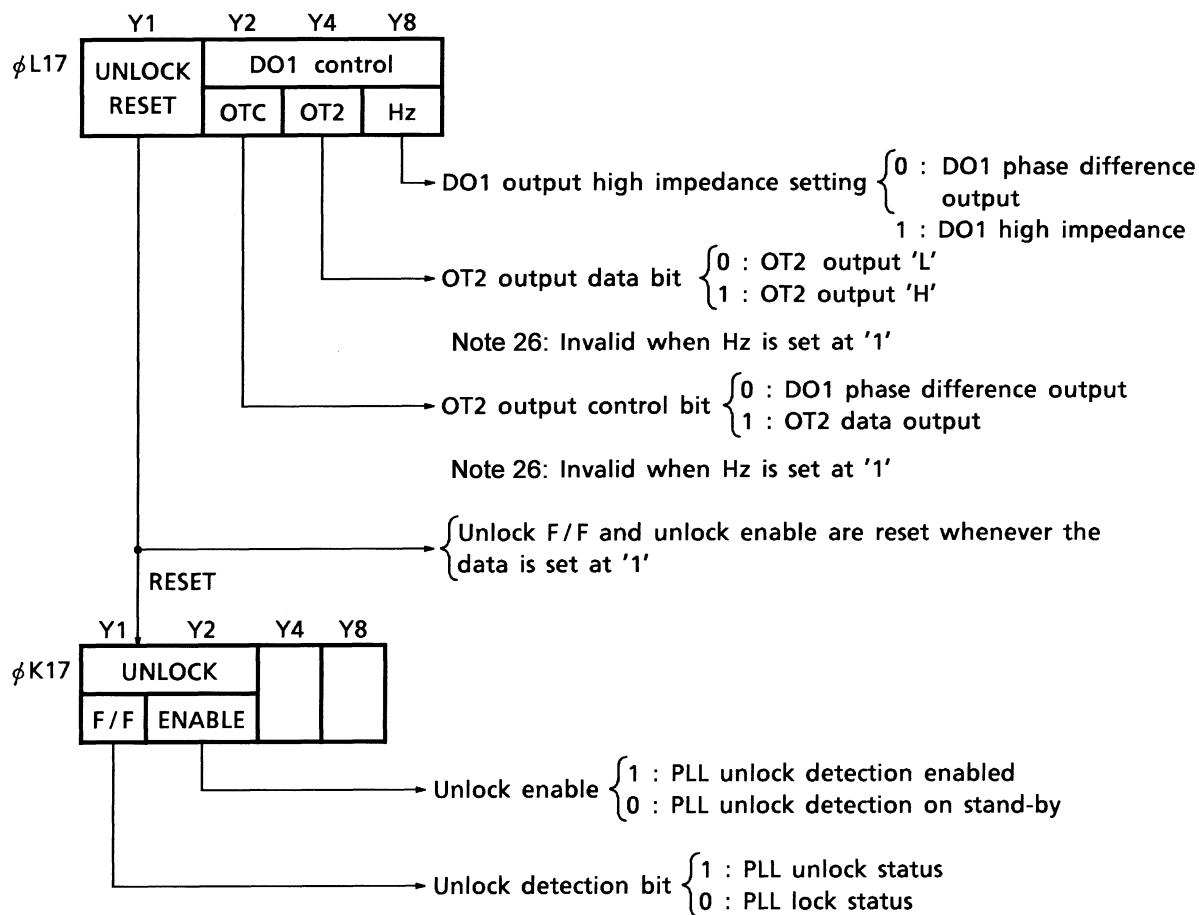

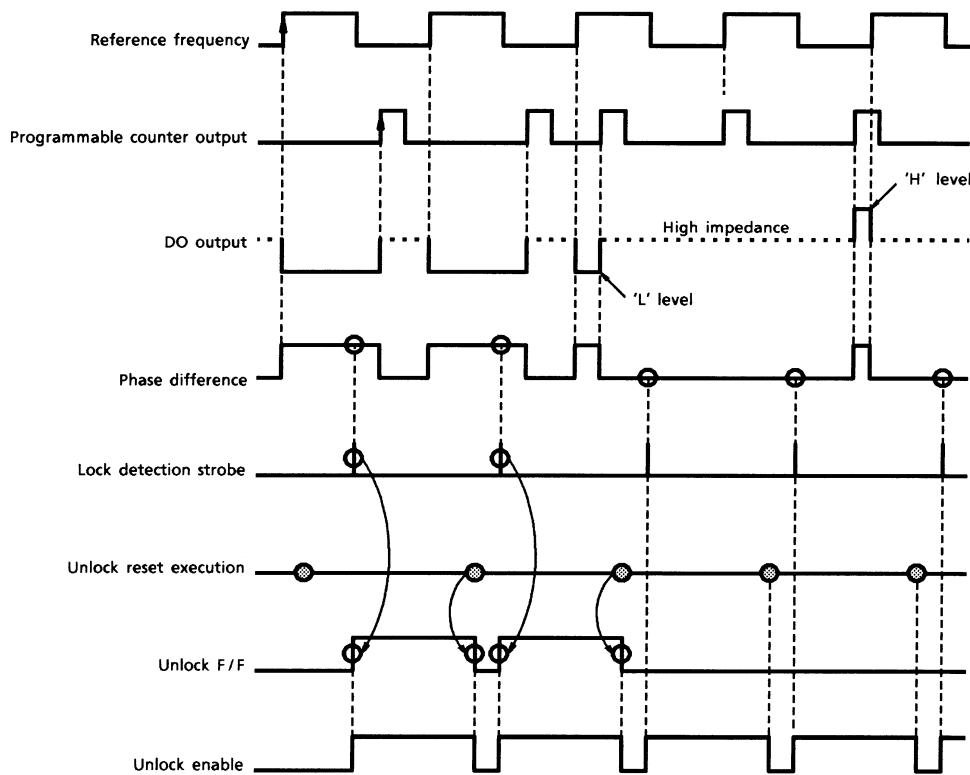

- Allows PLL lock status detection.

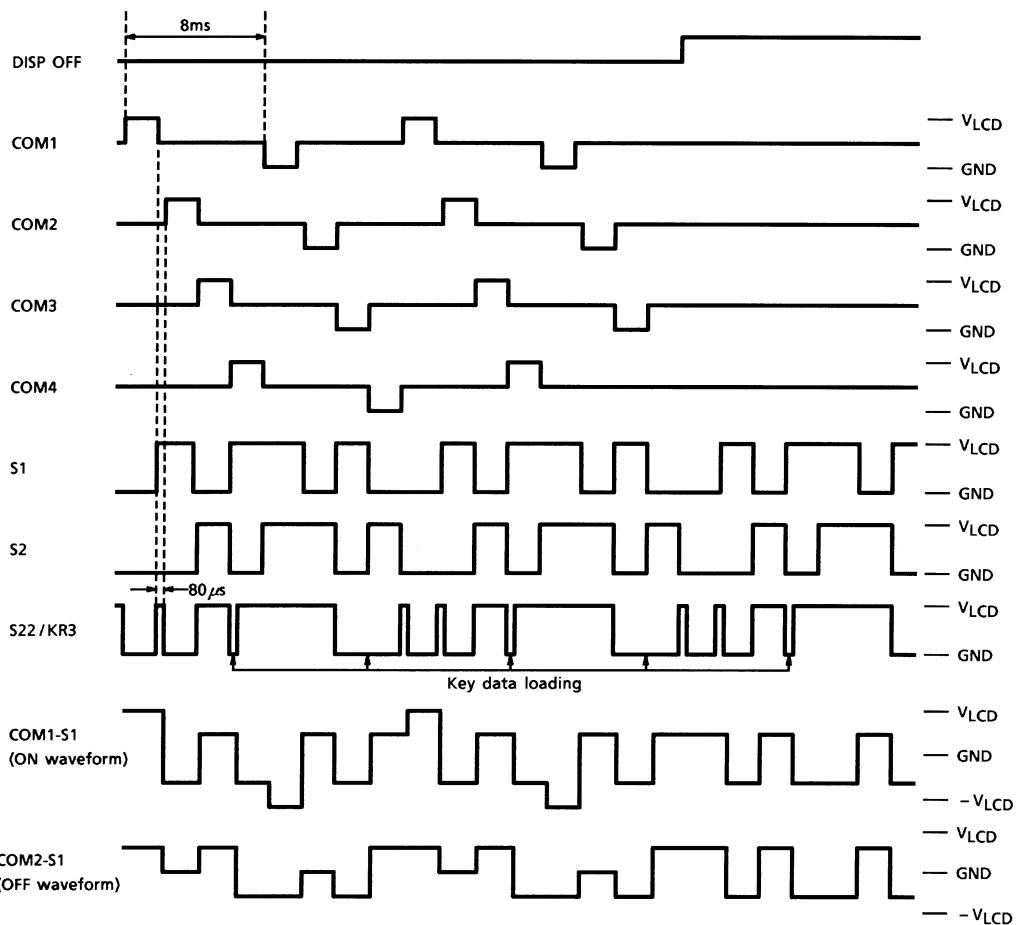

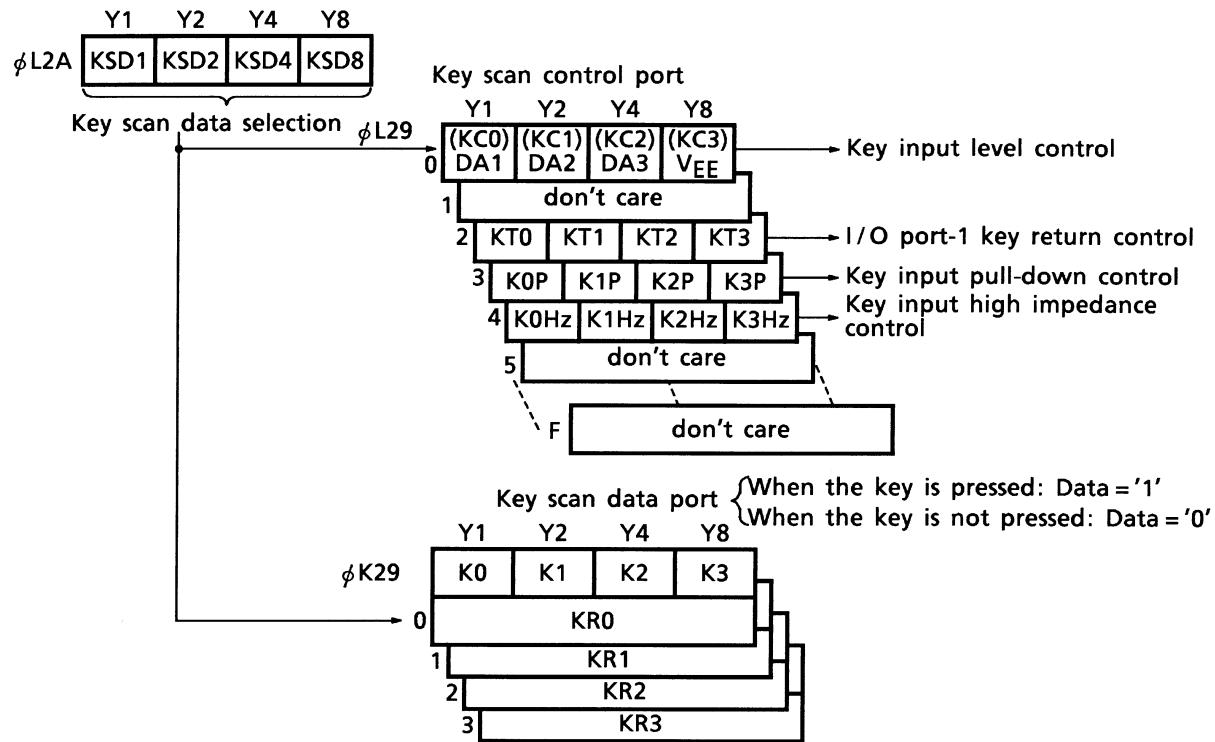

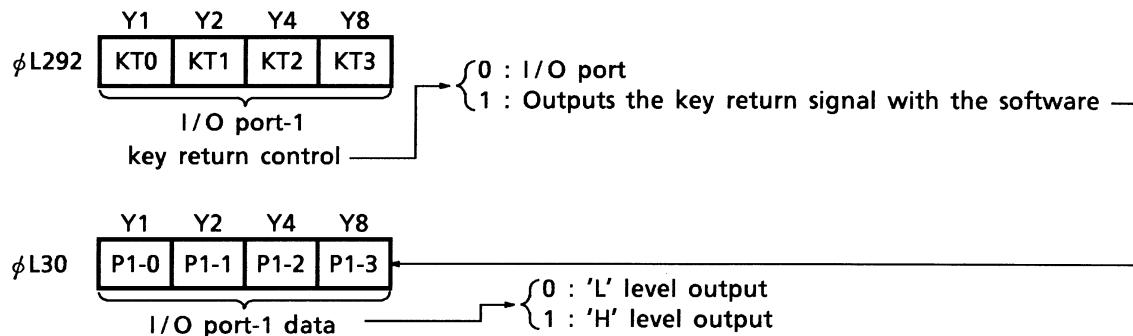

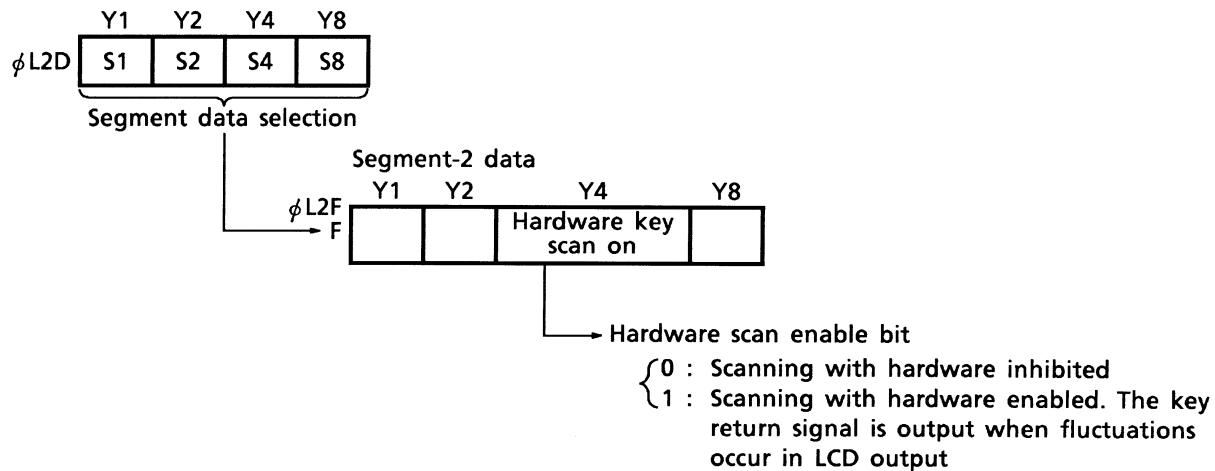

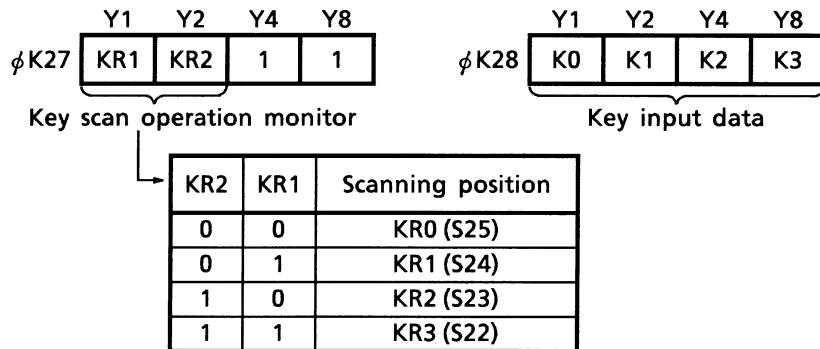

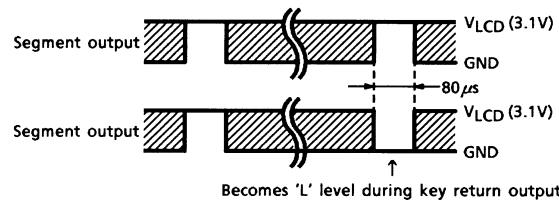

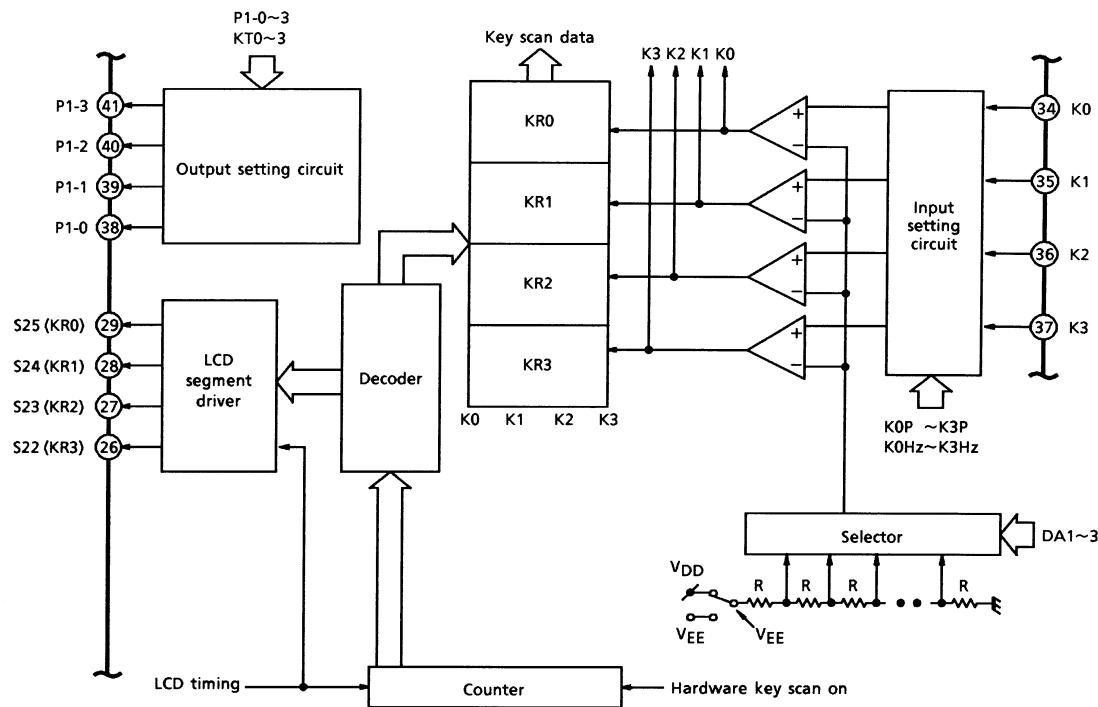

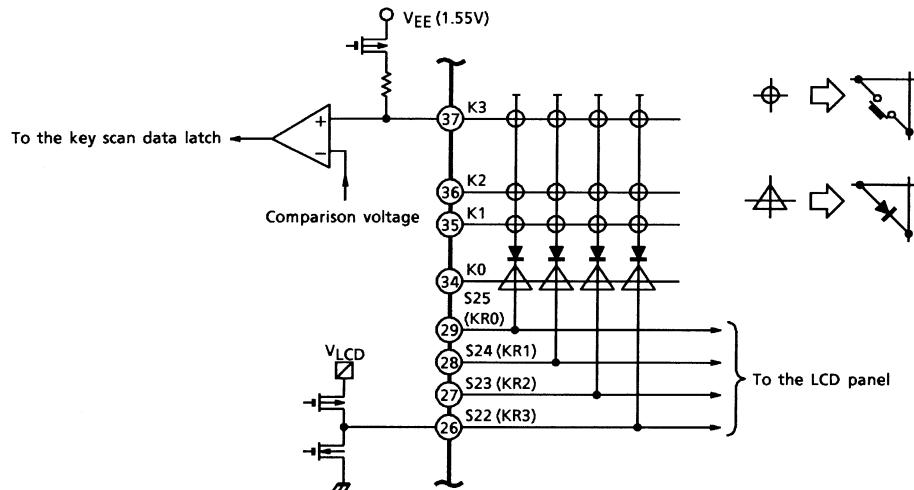

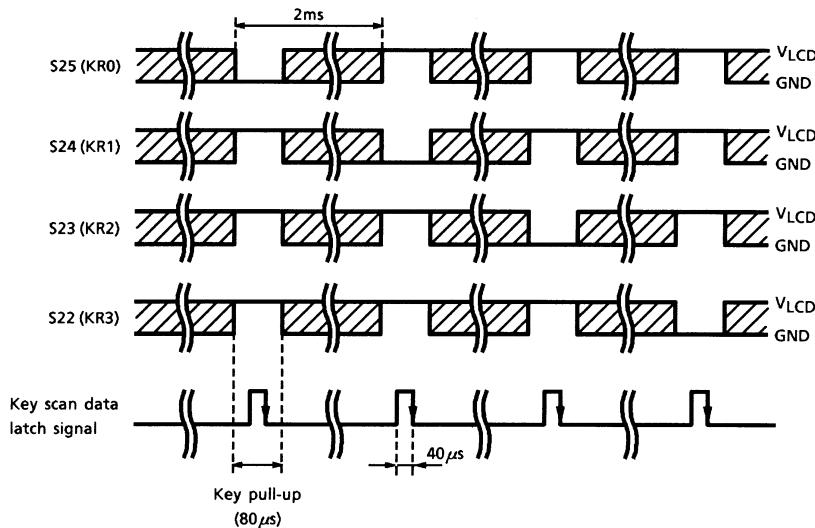

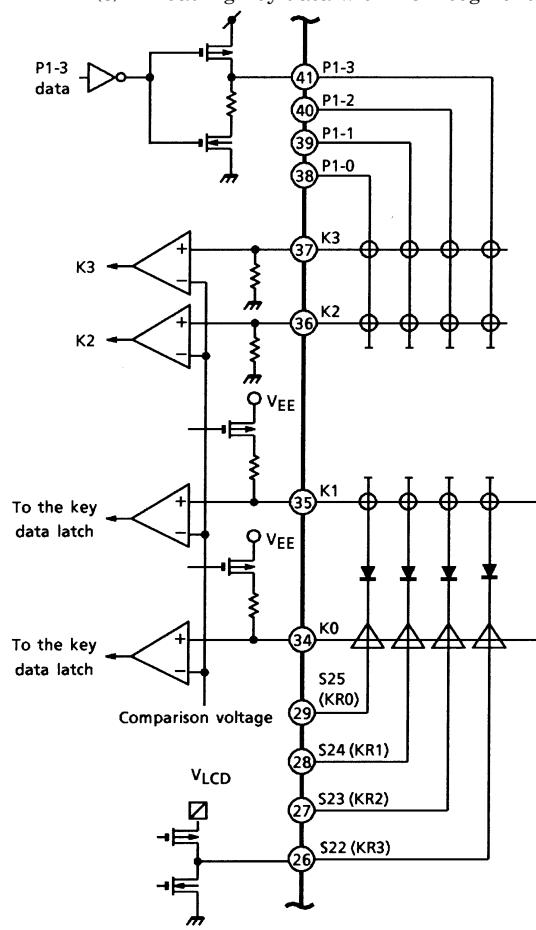

- Four of the LCD segment outputs (S22 to S25) can also operate as key return timing outputs (KR0 to KR3). The I/O ports are not dedicated for key return timing outputs but can have other uses as well.

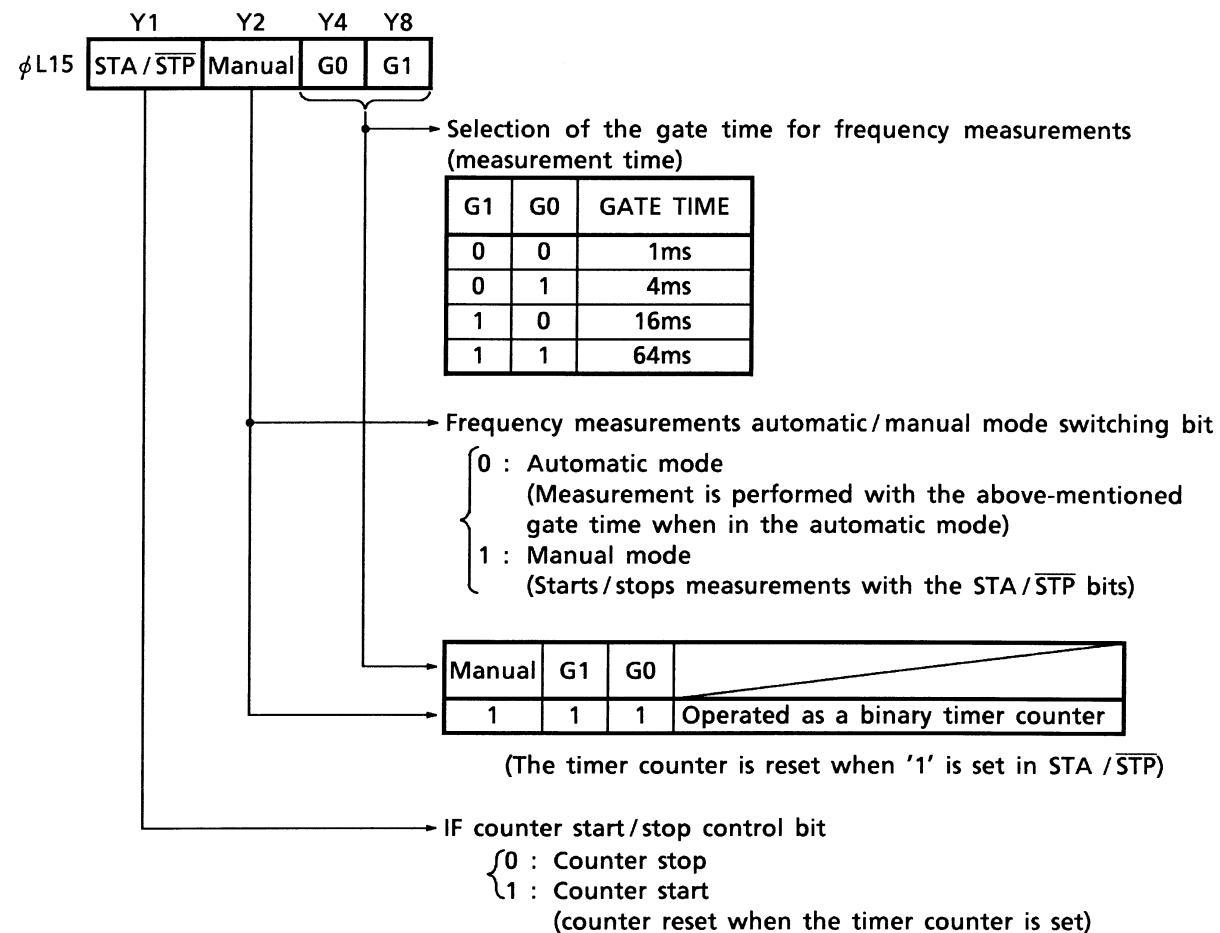

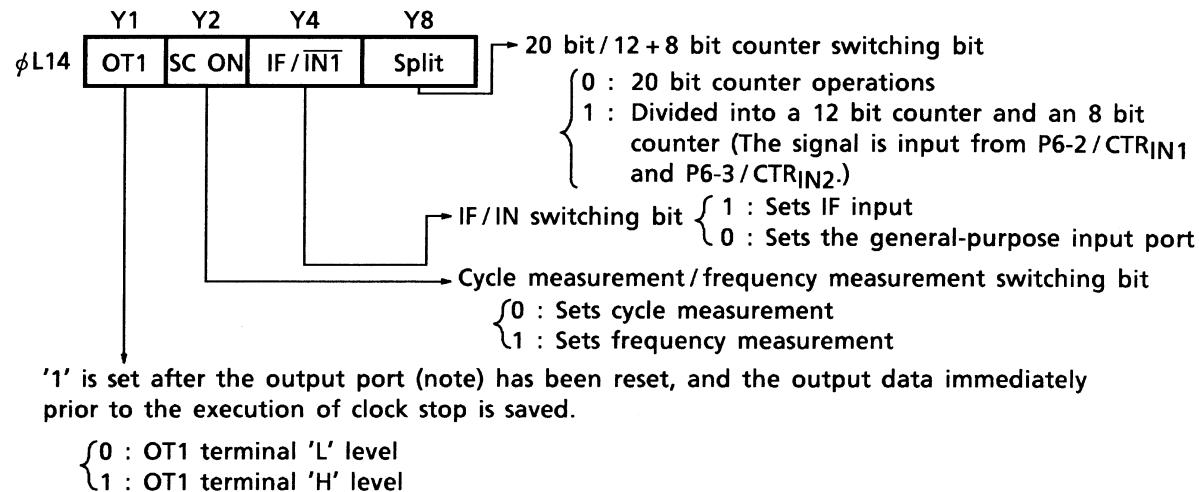

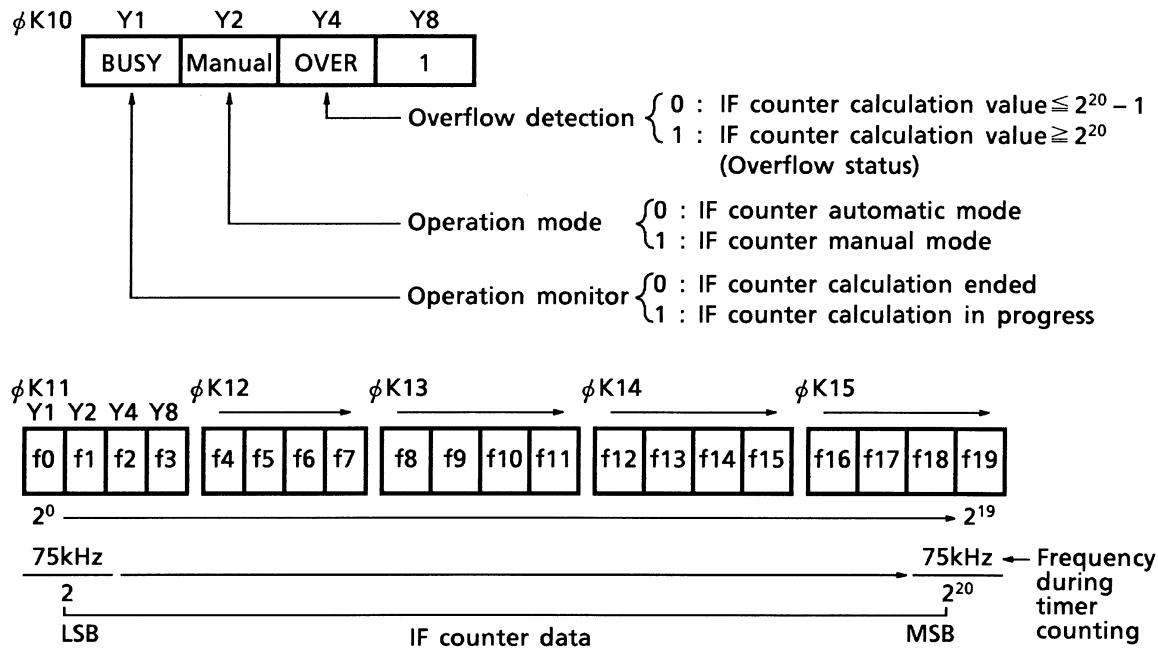

- Built-in 20-bit, general-purpose IF counters can detect stations during auto-tuning by counting the intermediate frequencies of each band.

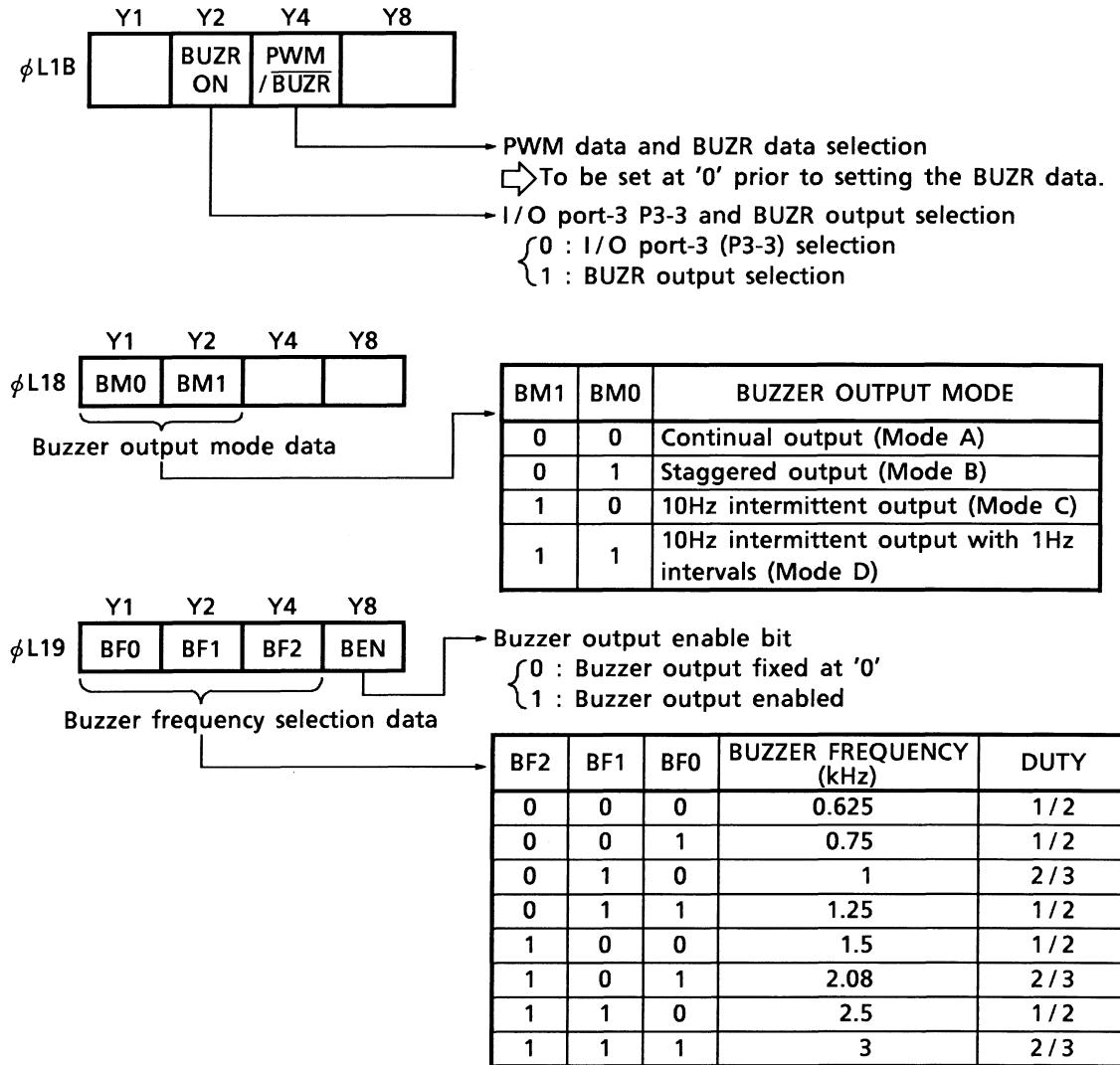

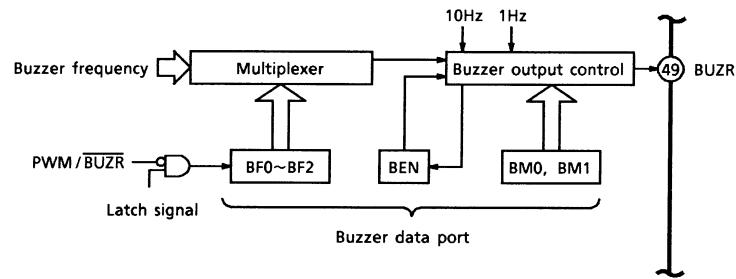

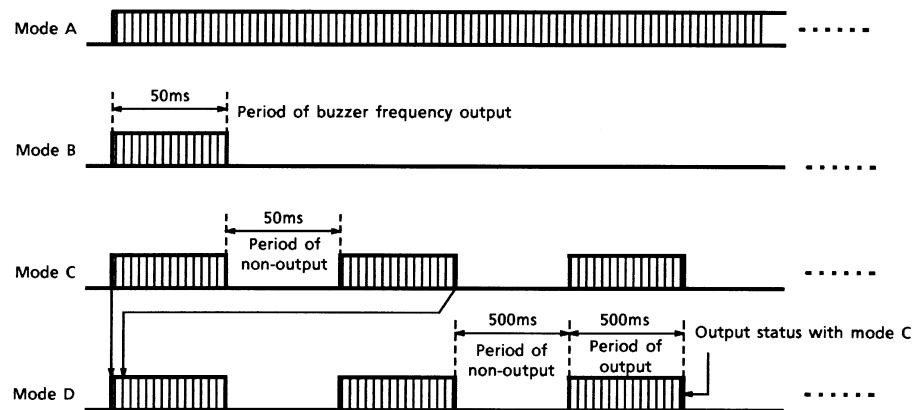

- Built-in buzzer output circuit can output 8 kinds of frequencies in 4 modes: Continuous output, single-shot output, 10-Hz intermittent output, and 10-Hz intermittent 1-Hz interval output.

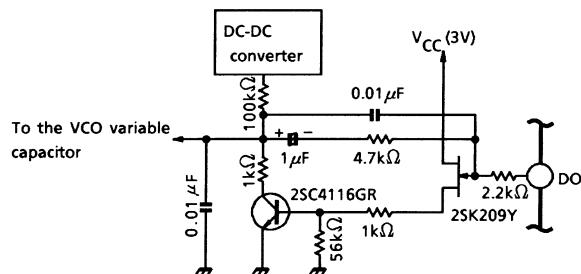

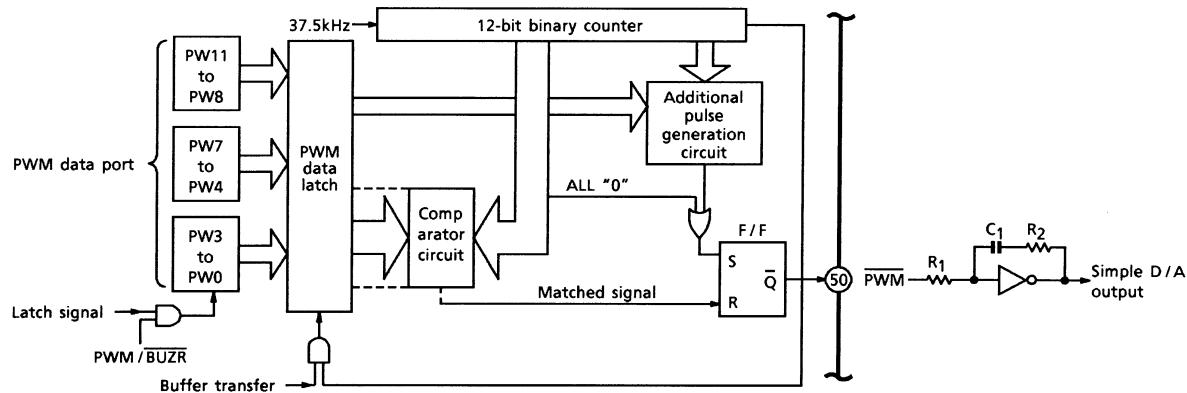

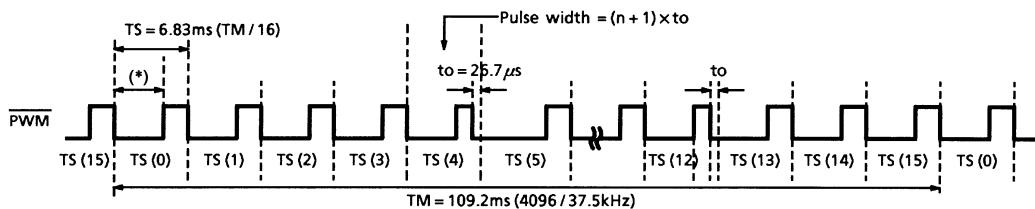

- Features built-in 12-bit PWM circuit usable for easy-to-use D/A converter.

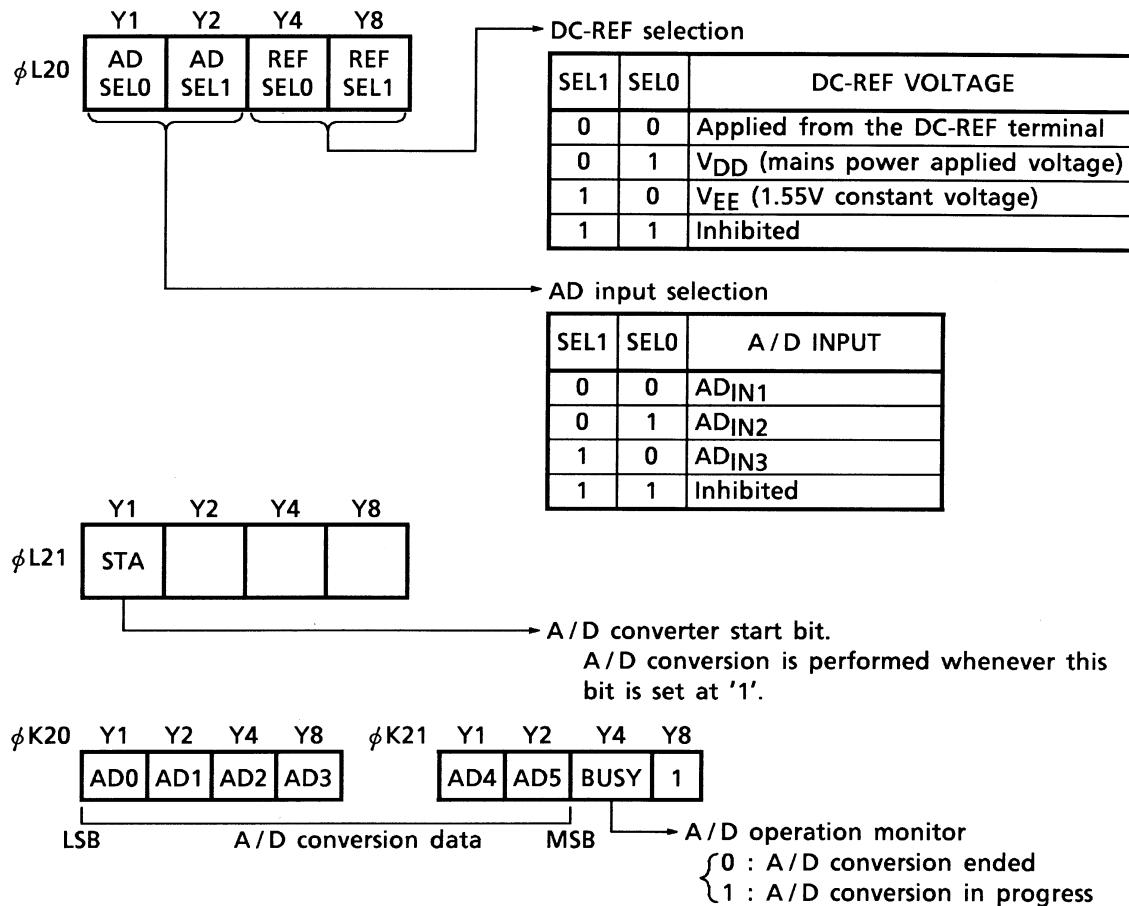

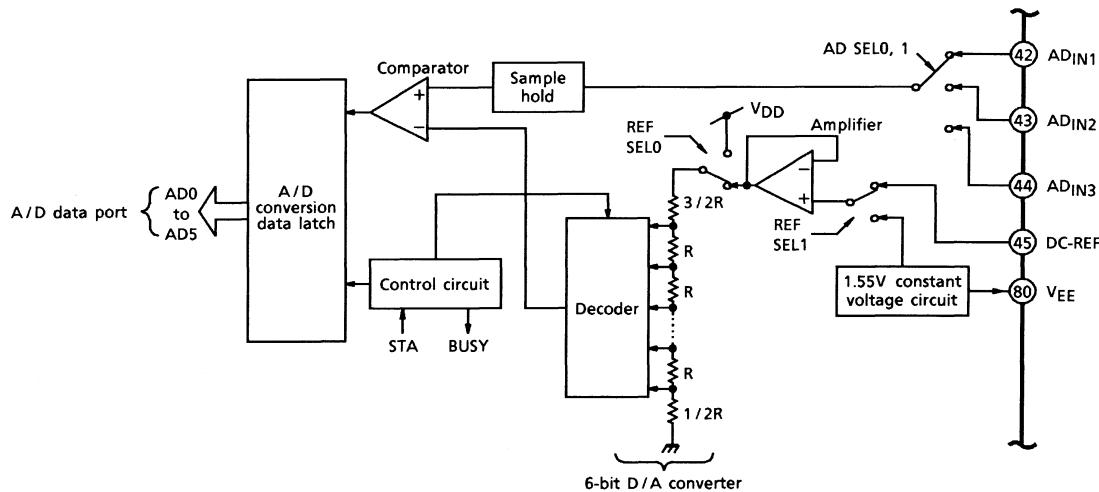

- Features a built-in 3-channel, 6-bit A/D converter.

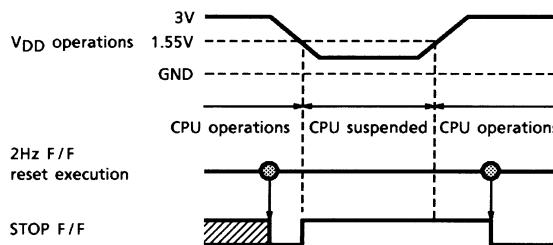

- To prevent CPU malfunction, a built-in supply voltage drop detection circuit shuts down the CPU when the voltage falls below 1.55 V.

## Pin Assignment

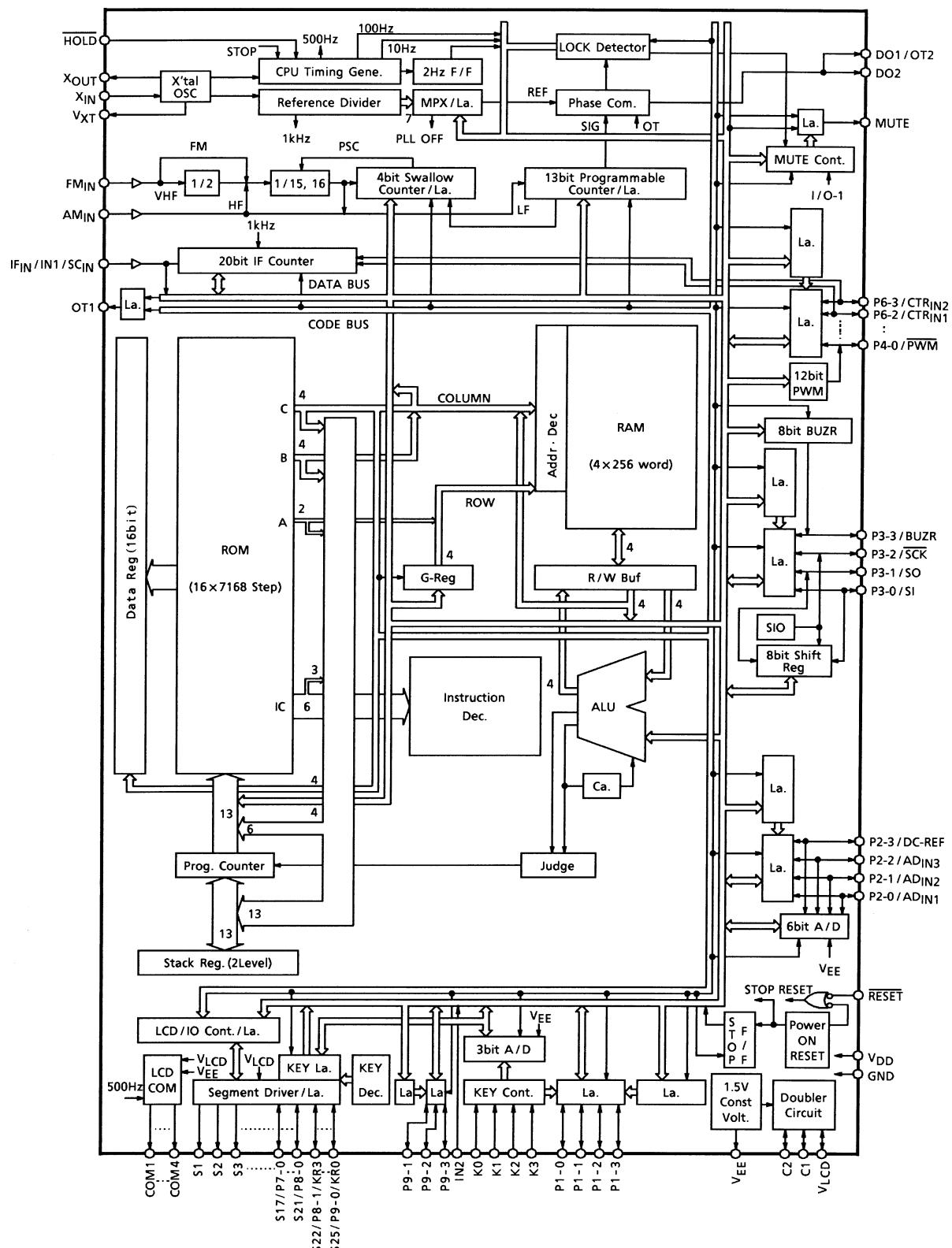

## Block Diagram

## Description of Pin Function

| Pin No. | Symbol                    | Pin Name                                             | Function and Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Remarks                                                                               |

|---------|---------------------------|------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|

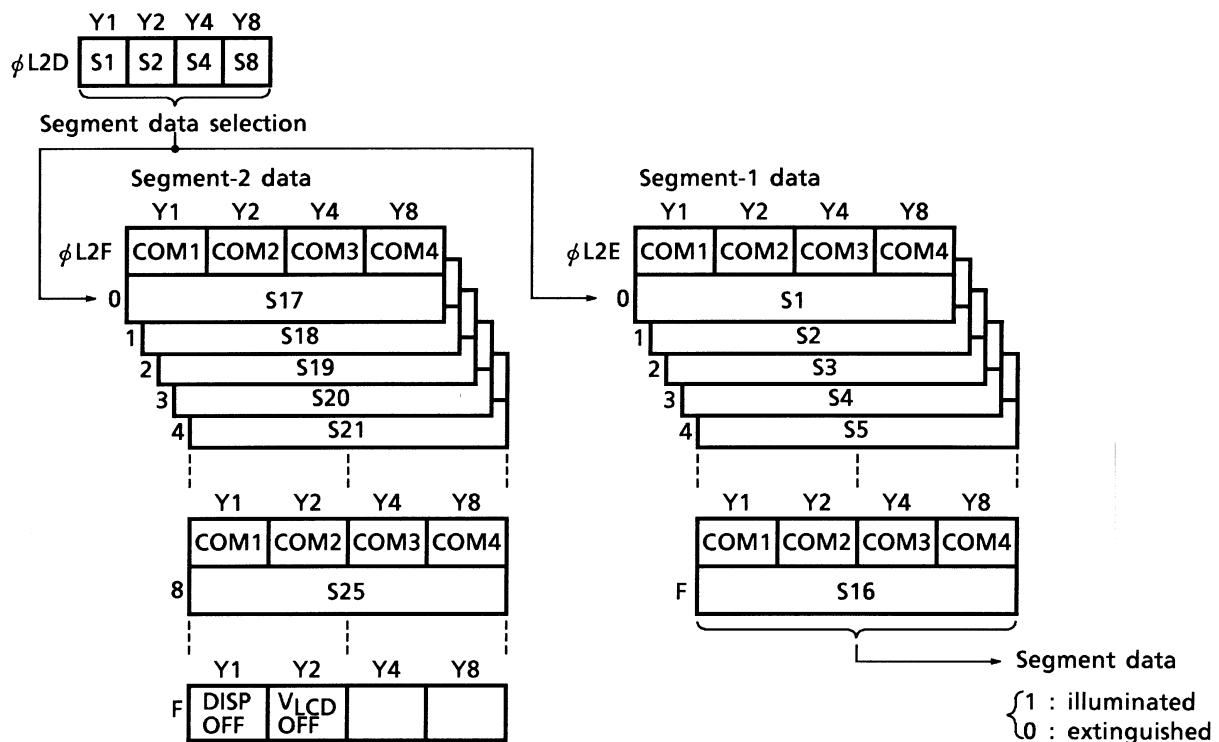

| 1       | COM1                      | LCD common output                                    | Output common signals to LCD panels. Through a matrix with pins S1 to S25, a maximum 100 segments can be displayed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |

| 2       | COM2                      |                                                      | Three levels, $V_{LCD}$ , $V_{EE}$ , and GND, are output at 62.5 Hz every 2 ms.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                       |

| 3       | COM3                      |                                                      | $V_{EE}$ is output after system reset and CLOCK STOP are released, and a common signal is output after the DISP OFF bit is set to "0".                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                       |

| 4       | COM4                      |                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                       |

| 5~20    | S1~S16                    | LCD segment output                                   | Segment signal output terminals for LCD panel. Together with COM1 to COM4, a matrix is formed that can display a maximum of 100 segments.                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

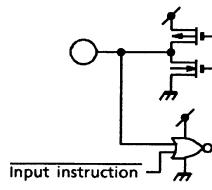

| 21~25   | S17/P7-0~S21/P8-0         | LCD segment output/I/O port                          | S17 to S25 are usable as I/O port by program. Signals for key matrix and the segment signals from pins S22/KR3 to S25/KR0 are output on a time sharing basis. $4 \times 4 = 16$ key matrix can be created in conjunction with key input ports K0 to K3.                                                                                                                                                                                                                                                                                                                                                               |    |

| 26~29   | S22/P8-1/KR3~S25/P9-0/KR0 | LCD segment output/I/O port/key return timing output |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                       |

| 30~32   | P9-1~P9-3                 | I/O port 9                                           | 3-bit I/O port, capable of input/output setup for each bit via software.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| 33      | IN2                       | Input port 2                                         | 1-bit input port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

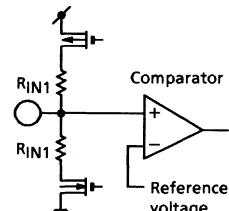

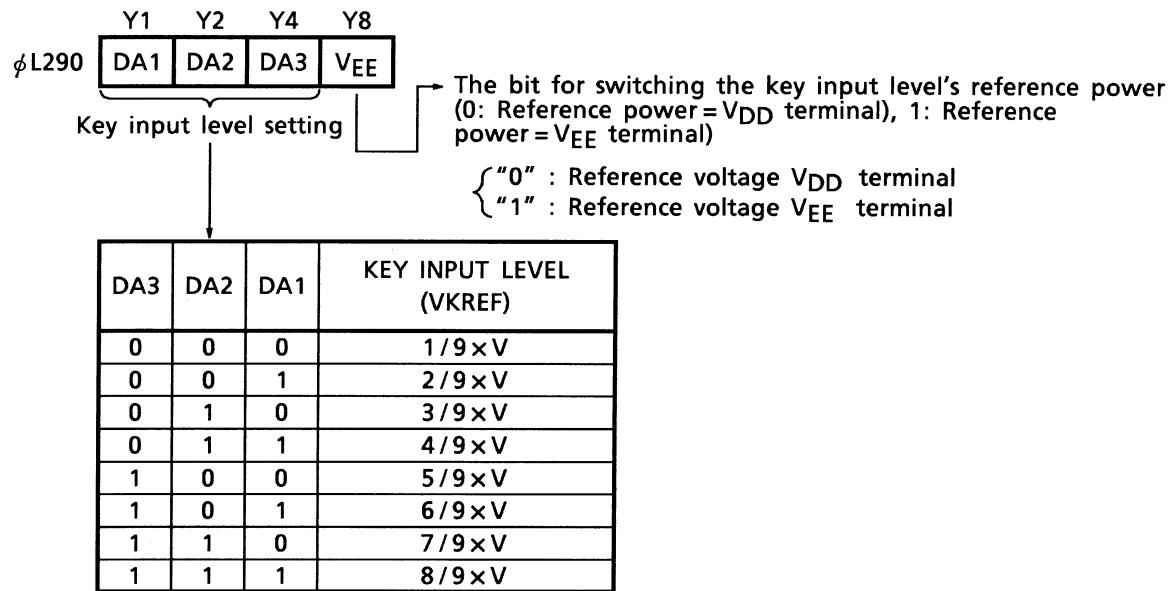

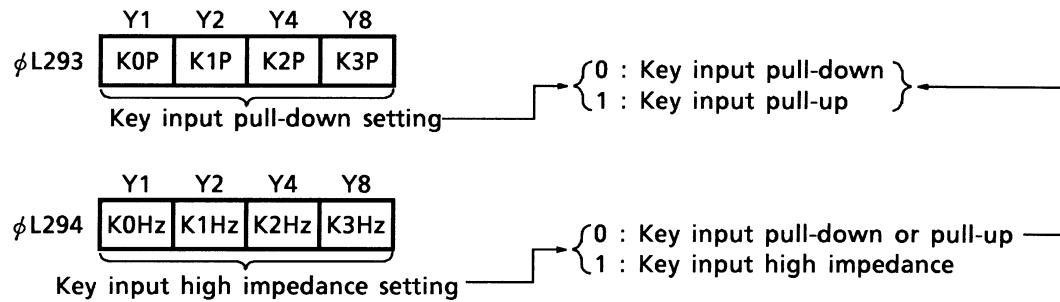

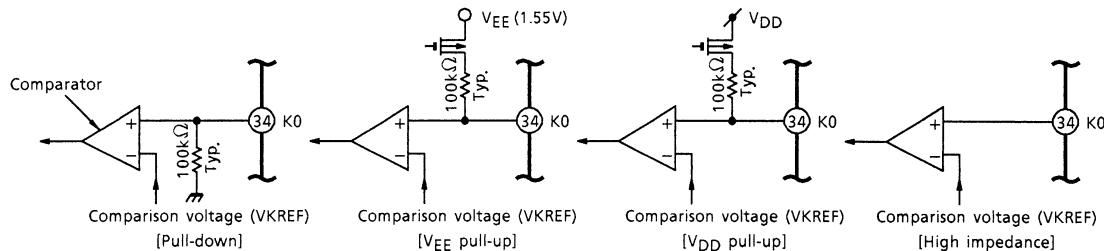

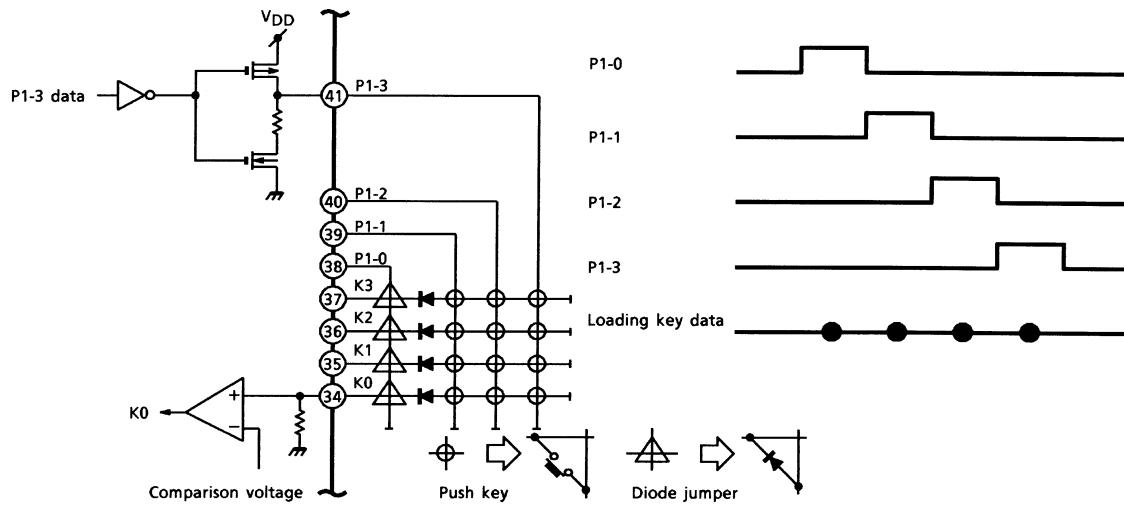

| 34~37   | K0~K3                     | Key input port                                       | 4-bit input port for key matrix input, capable of inputting a maximum of $4 \times 4 = 16$ key data in combination with the key return timing outputs (KR0 to KR3) of an LCD segment pin. Comprises an A/D comparator making it possible to select high impedance with pull-down and pull-up pins for inputs, and to perform programming with a 3-bit input threshold. This allows various key matrices to be formed. Also usable as a 4-channel 3-bit A/D converter with a successive comparison formula via software. When an "H" level is applied in key input ports set to pull-down mode, WAIT mode is canceled. |  |

| Pin No. | Symbol                                                    | Pin Name                                                                                                                   | Function and Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Remarks |

|---------|-----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

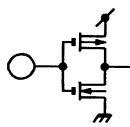

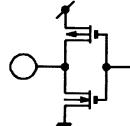

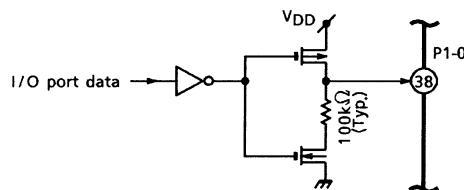

| 38~41   | P1-0~P1-3                                                 | I/O port 1                                                                                                                 | <p>The input and output of these 4-bit I/O ports can be programmed in 1-bit units. This pin is capable of outputting timing signals for the key matrix by program.</p> <p>It contains load resistance in N-ch, and can form the matrix for a push-key needing no diode for the key matrix.</p> <p>By altering the input of I/O ports set to input, the CLOCK STOP mode or the WAIT mode can be released, and the MUTE bit of the MUTE pin can be set to "1".</p>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |

| 42~45   | P2-0/ADIN1<br>P2-1/ADIN2<br>P2-2/ADIN3<br>P2-3/<br>DC-REF | I/O port 2<br>/AD analog voltage input<br>/AD analog voltage input<br>/AD analog voltage input<br>/Reference voltage input | <p>4-bit I/O ports, allowing input and output to be programmed in 1-bit units.</p> <p>Pins P2-0 to P2-2 can also be used for analog input to the built-in 6-bit, 3-channel A/D converter.</p> <p>The conversion time of the built-in A/D converter using the successive comparison method is 280 <math>\mu</math>s. The necessary pin can be programmed to AD analog input in 1-bit units, and P2-3 can be set to the reference voltage input. Internal power supply (<math>V_{DD}</math>) or constant voltage (<math>V_{EE}</math>) can be used as the reference voltage. So battery voltage, etc., can be easily detected. The reference voltage input, for which a built-in operational amp. is used, has high impedance.</p> <p>The A/D converter and all associated controls are performed via software.</p>                                                                                                                                                        |         |

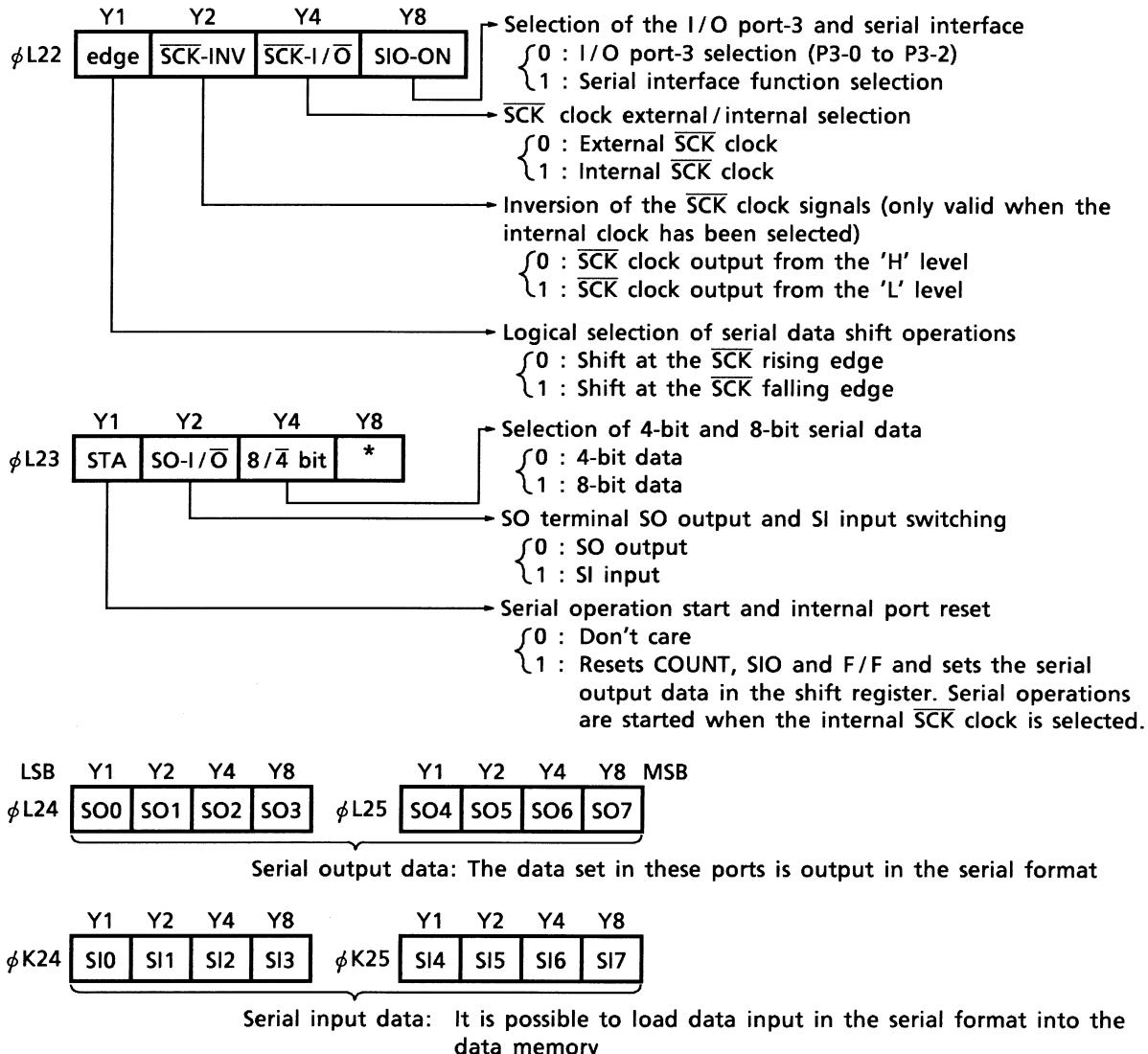

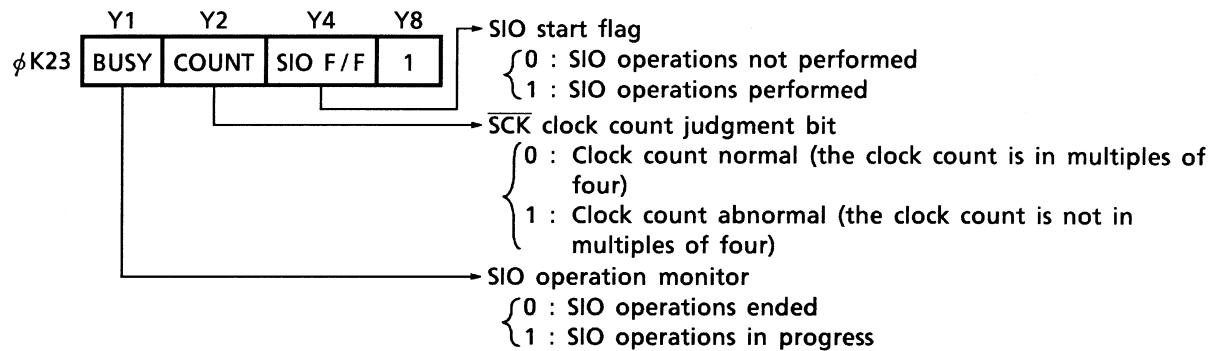

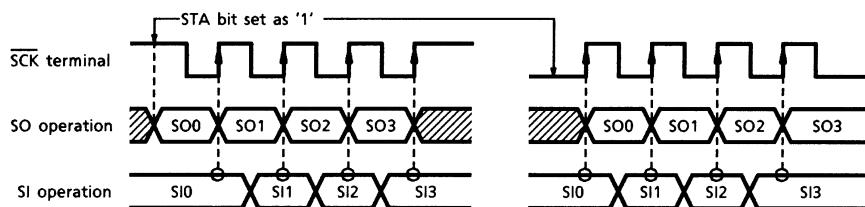

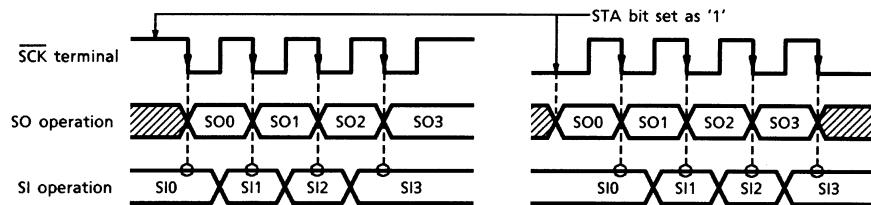

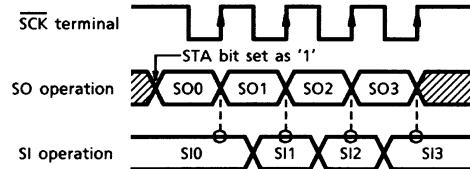

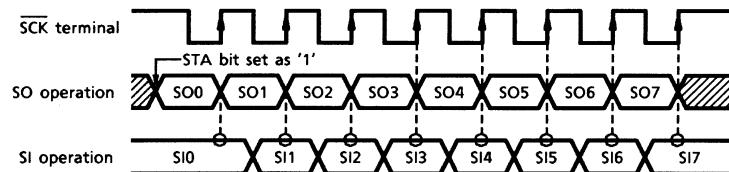

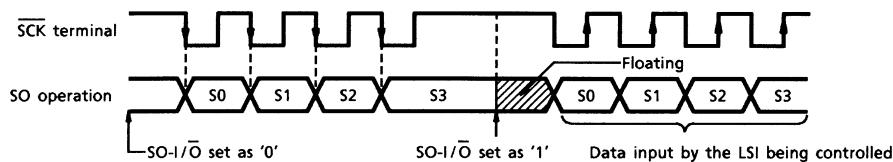

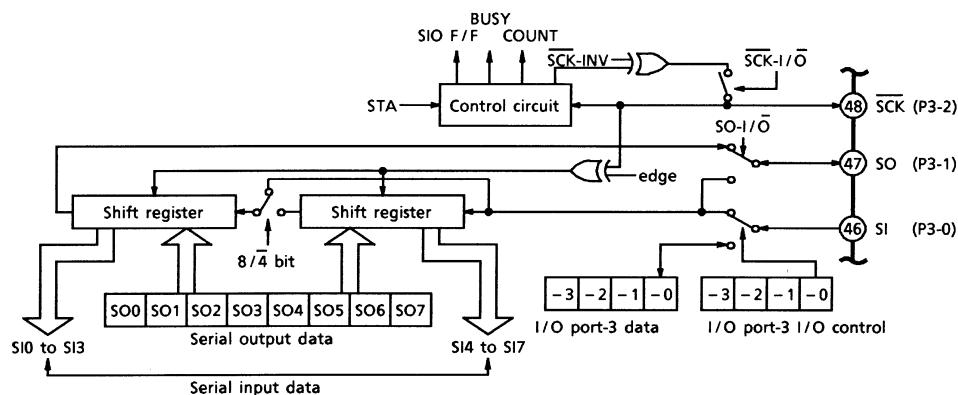

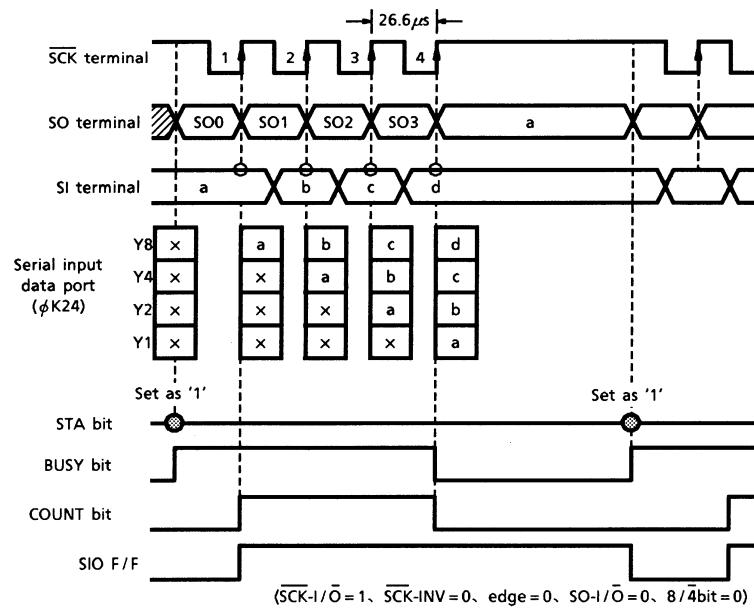

| 46~49   | P3-0/SI<br>P3-1/SO<br>P3-2/SCK<br>P3-3/BUZR               | I/O port 3<br>/Serial data input<br>/Serial data output<br>/Serial clock I/O<br>/Buzzer output                             | <p>4-bit I/O ports, allowing input and output to be programmed in 1-bit units. Pins P3-0 to P3-2 can also be used for the I/O terminals of serial interface circuits (SIO).</p> <p>SIO functions for 4-bit or 8-bit serial data inputs from the SI pin and outputs from the SO pin at the SCK pin clock edge.</p> <p>The clock for serial operation (SCK) is capable of internal/external options and rise/fall shift options. The SO pin is also capable of switching to serial inputs (SI), facilitating the control of various LSI's and communication between controllers. All SIO inputs use built-in Schmitt circuits.</p> <p>P3-3 pins also functions as the output for a built-in buzzer. The buzzer output can select 8 kinds of 0.625 to 3 kHz frequencies with 4 modes: continuous output, single-shot output, 10-Hz intermittent output, and 10-Hz intermittent 1-Hz interval output.</p> <p>SIO, buzzer, and all associated controls can be programmed.</p> |         |

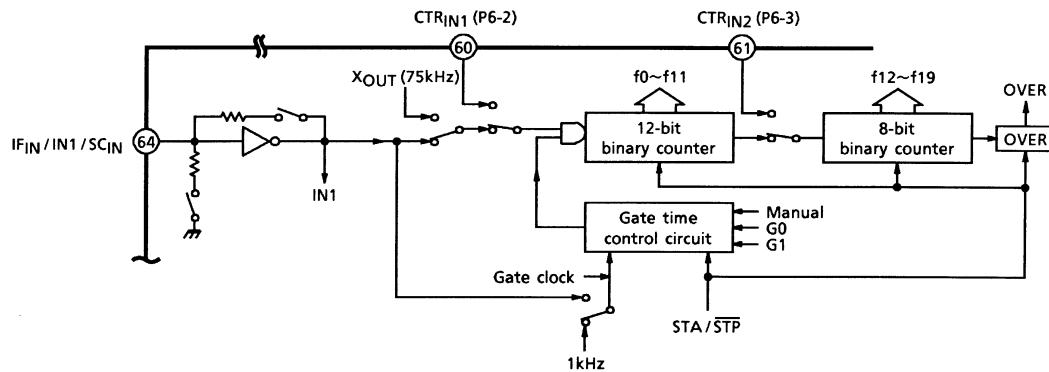

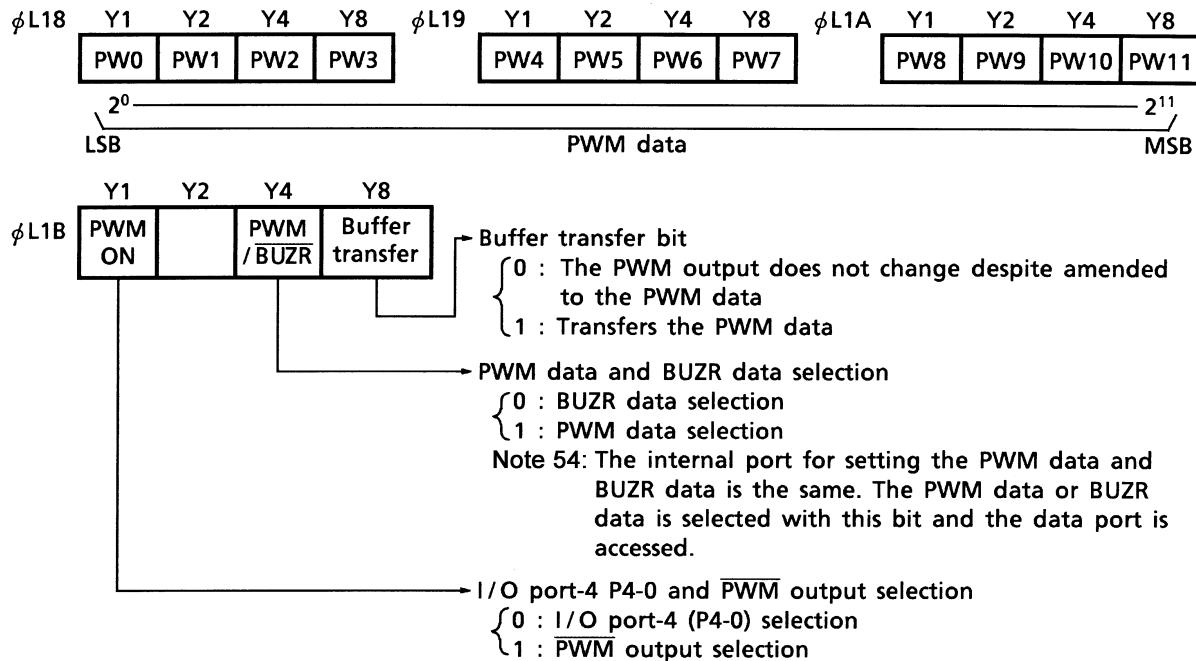

| 50~61   | P4-0/PWM<br>P4-1~<br>P6-2/CTRIN1<br>P6-3/CTRIN2           | I/O port 4<br>/PWM output<br>I/O port 4~<br>I/O port 6<br>/Counter input                                                   | <p>16-bit I/O ports, allowing input and output to be programmed in 1-bit units.</p> <p>The P4-0 pin is also used for built-in 12-bit PWM outputs. The PWM outputs pulse continuously at 73.26 Hz, and can change the duty of the pulses to 256 steps (8 bits), causing the added pulses to be output using 4 bits for 16 cycles (218.5 ms).</p> <p>The P6-2 and P6-3 pins are also used for input purposes when using 20-bit IF counters as 12-bit and 8-bit binary counters.</p> <p>The P6-2 pin can be used for 12-bit binary counter inputs, and the P6-3 pin for 8-bit binary counter inputs.</p> <p>PWM outputs, counter inputs, and all associated controls can be programmed.</p>                                                                                                                                                                                                                                                                                 |         |

| Pin No. | Symbol                                  | Pin Name                                             | Function and Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Remarks |

|---------|-----------------------------------------|------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

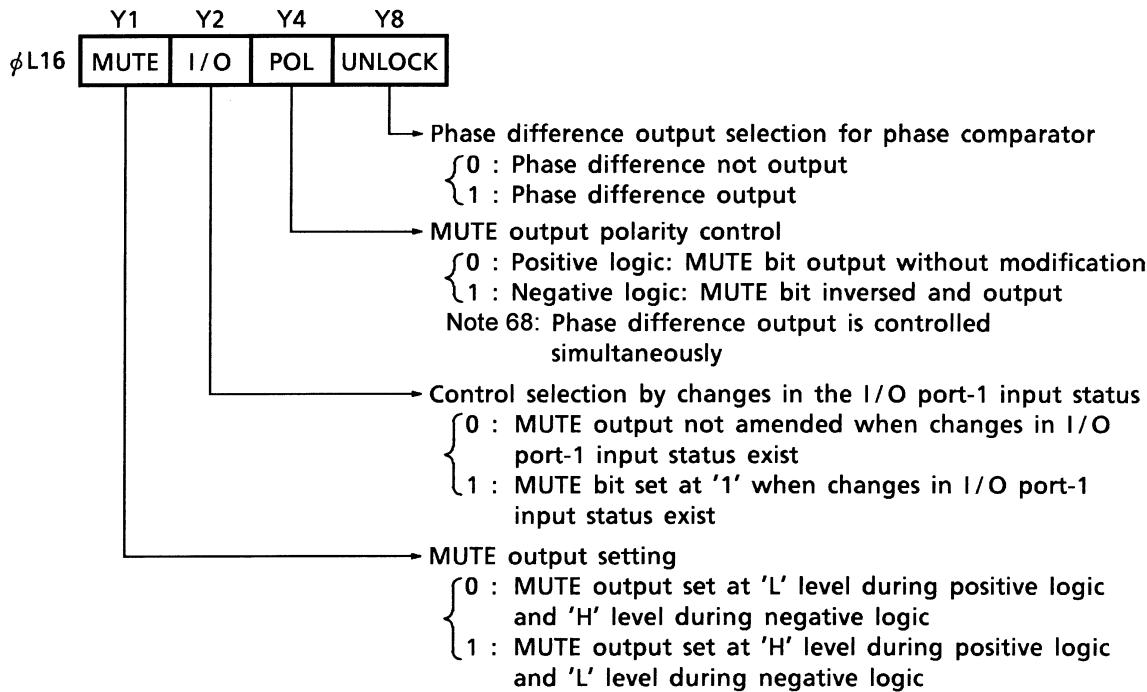

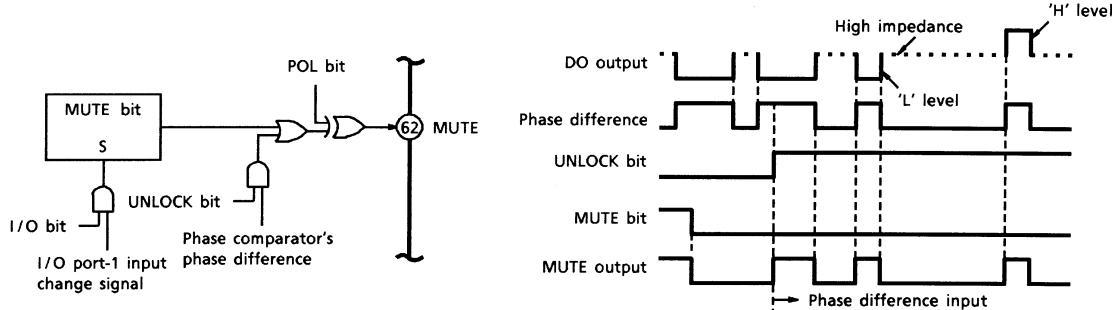

| 62      | MUTE                                    | Muting output port                                   | 1-bit output port, normally used for muting control signal output.<br><br>This pin can set the internal MUTE bit to "1" according to a change in the input of I/O port 1. MUTE bit output logic can be changed: PLL phase difference can also be output using this pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |

| 63      | TEST                                    | Test mode control input                              | Input pin used for controlling TEST mode.<br>"H" (high) level indicates TEST mode, while "L" (low) indicates normal operation.<br><br>The pin is normally used at low level or in NC (no connection) state. (a pull-down resistor is builtin).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |

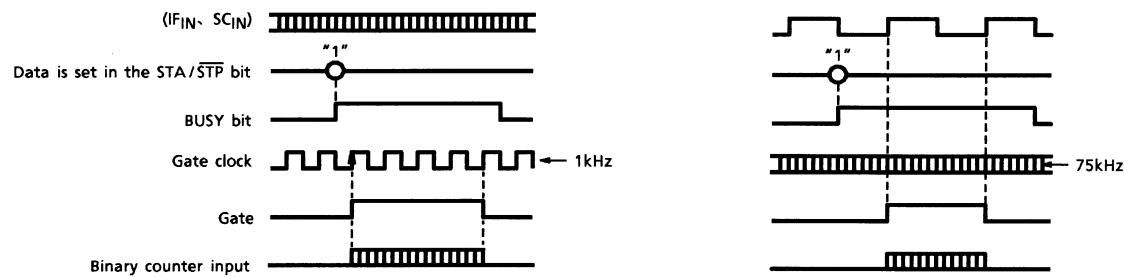

| 64      | IF <sub>IN</sub> /IN1 /SC <sub>IN</sub> | IF signal input /Input port /Cycle measurement input | IF signal input pin for the IF counter to count the IF signals of the FM and AM bands and to detect the automatic stop position.<br><br>The input frequency is between 0.35 to 12 MHz (0.2 V <sub>p-pmin</sub> ). A built-in input amp. and C coupling allow operation at low-level input.<br><br>The IF counter is a 20 bit counter with optional gate times of 1, 4, 16 and 64 ms. 20 bits of data can be readily stored in memory. This counter is used as a timer when the IF counter is not used.<br><br>The input pin can be programmed for use as an input port (IN port). CMOS input is used when the pin is set as an IN port.<br><br>Note: To set SC <sub>IN</sub> , use the pin with DC coupling and rectangular wave input. |         |

| 65      | DO1/OT2                                 | Phase comparator output /Output port                 | PLL phase comparator output pins.<br><br>When the prescaler output of the programmable counter is higher than the reference frequency, output is at high level. When output is lower than the reference frequency, output is at low level.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |

|         |                                         |                                                      | When output equals the reference frequency, high impedance output is obtained. Because DO1 and DO2 are output in parallel, optional filter constants can be designed for the FM/VHF and AM bands.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |

| 66      | DO2                                     | Phase comparator output                              | Pin DO1 can be programmed to high impedance or programmed as an output port (OT2). Thus, the pins can be used to improve lock-up time or used as output ports.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |

| Pin No. | Symbol          | Pin Name                | Function and Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Remarks                                                                               |

|---------|-----------------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|

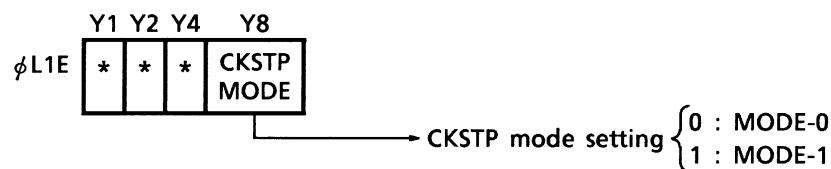

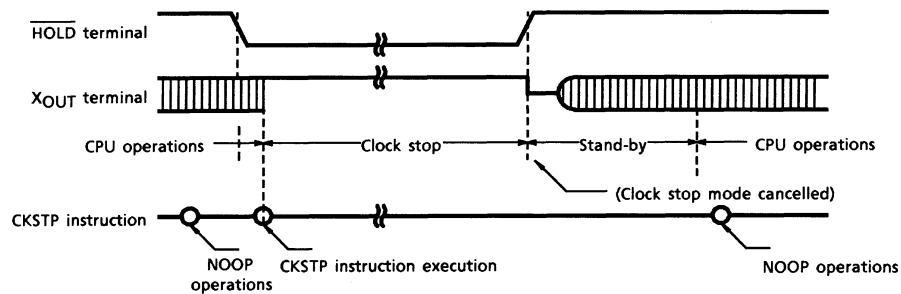

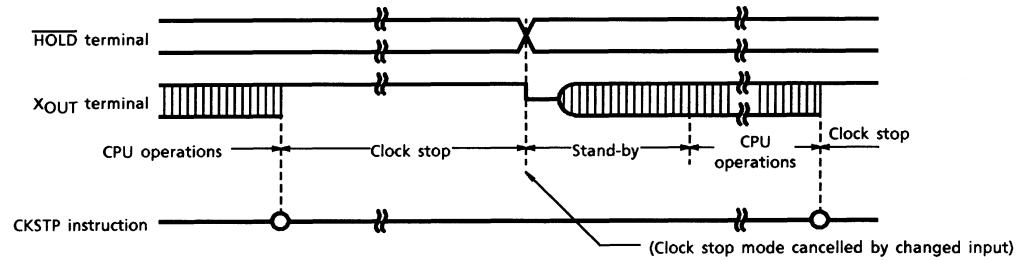

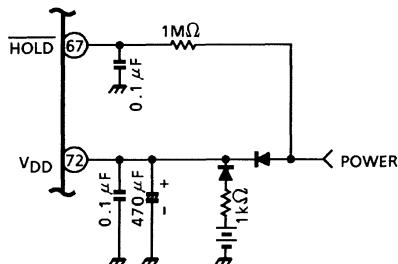

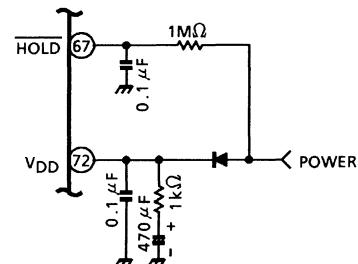

| 67      | <u>HOLD</u>     | Hold mode control input | <p>Input pin for request/release hold mode.</p> <p>Normally, this pin is used to input radio mode selection signals or battery detection signals.</p> <p>Hold mode includes CLOCK STOP mode (stops crystal oscillation) and WAIT mode (halts CPU). Setting is implemented with the CKSTP instruction or the WAIT instruction. When the CKSTP instruction is executed, request/release of the hold mode depends on the internal MODE bit. If the MODE bit is "0" (MODE-0), executing the CKSTP instruction while the <u>HOLD</u> pin is at low level stops the generator and the CPU and changes to memory back-up mode. If the MODE bit is "1" (MODE-1), executing the CKSTP instruction enters memory back-up mode regardless of the level of the <u>HOLD</u> pin. Memory back-up is released when the <u>HOLD</u> pin goes high in MODE-0, or when the <u>HOLD</u> pin input changes in MODE-1.</p> <p>When memory back-up mode is entered by executing a WAIT instruction, any change in the <u>HOLD</u> pin input releases the mode.</p> <p>In memory back-up mode, current consumption is low (below 10 <math>\mu</math>A), and all the output pins (e.g., display output, output ports) are automatically set to low level.</p> |    |

| 68      | OT1             | Output port             | <p>1-bit output port.</p> <p>Note: This output goes high after reset, and internal latch data is output as is even when CLOCK STOP is being executed.</p>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| 72      | V <sub>DD</sub> | Power-supply pins       | <p>Pins to which power is applied.</p> <p>Normally, V<sub>DD</sub> = 1.8 to 3.6 V is applied.</p> <p>In back-up mode (when CKSTP instructions are being executed), voltage can be lowered to 1.0 V. If voltage falls below 1.55 V while the CPU is operating, the CPU stops to prevent malfunction (STOP mode). When the voltage rises above 1.55 V, the CPU restarts.</p> <p>STOP mode can be detected by checking the STOP F/F bit. If necessary, execute initialization or adjust clock by program.</p>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| 69      | GND             |                         | <p>When detecting or preventing CPU malfunctions using an external circuit, STOP mode can be invalidated and rendered non-operative by program. In that case, all four bits of the internal TEST port should be set to "1".</p> <p>If more than 1.8 V is applied when the pin voltage is 0, the device system is reset and the program starts from address "0". (power on reset)</p> <p>Note: To operate the power on reset, the power supply should start up in 10 to 100 ms.</p>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| Pin No. | Symbol           | Pin Name                         | Function and Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Remarks |

|---------|------------------|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

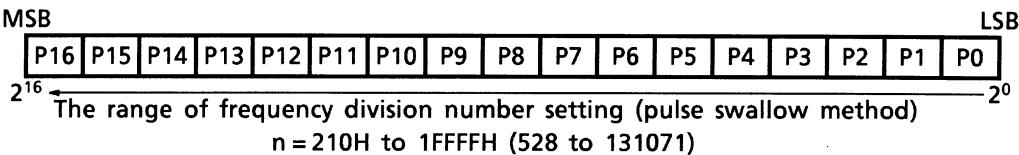

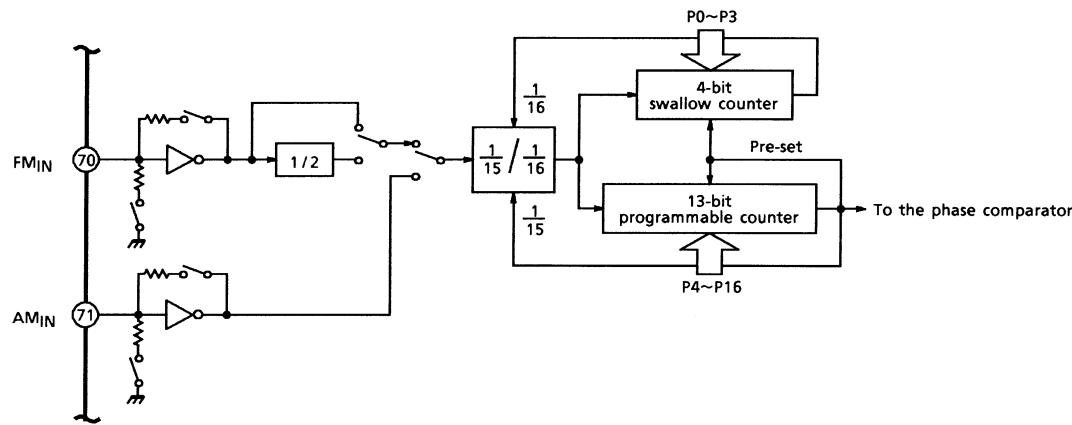

| 70      | FM <sub>IN</sub> | FM local oscillator signal input | <p>Using programmable counter input pins for FM, VHF band.</p> <p>The 1/2 + pulse swallow system (VHF mode) and the pulse swallow system (FM mode) are freely selectable by program.</p> <p>At the VHF mode, local oscillation output (VCO output) of 50 to 230 MHz [0.3 V<sub>p-p</sub> (min)] is input, and at the FM mode, that of 40 to 130 MHz [0.2 V<sub>p-p</sub> (min)] is input.</p> <p>A built-in input amp. and C coupling allow operation at low-level input.</p> <p>Note: When in the PLL OFF mode or when set to AM<sub>IN</sub> input, the input is pulled down.</p> |         |

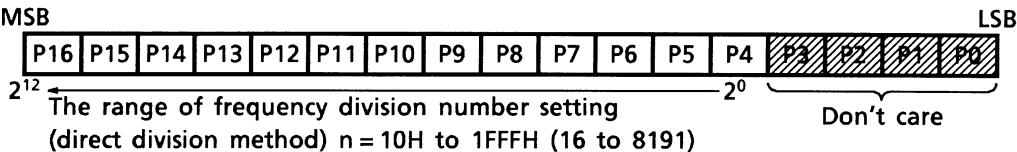

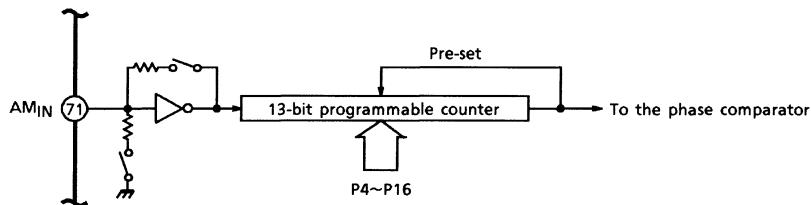

| 71      | AM <sub>IN</sub> | AM local oscillator signal input | <p>Programmable counter input pin for AM band.</p> <p>The pulse swallow system (HF mode) and direct dividing system (LF mode) are freely selectable by program. At the HF mode, local oscillation output (VCO output) of 1 to 45 MHz [0.2 V<sub>p-p</sub> (min)] is input, and at the LF mode, 0.5 to 12 MHz [0.2 V<sub>p-p</sub> (min)] is input.</p> <p>Built-in input amp. operates with low-level input using a C coupling.</p> <p>Note: When in PLL OFF mode or when set to FM<sub>IN</sub> input, the input is pulled down.</p>                                               |         |

| 73      | RESET            | Reset input                      | <p>Input pin for system reset signals.</p> <p>RESET takes place while at low level; at high level, the program starts from address "0".</p> <p>Normally, if more than 1.8 V is supplied to V<sub>DD</sub> when the voltage is 0, the system is reset (power on reset).</p> <p>Accordingly, this pin should be set to high level during operation.</p>                                                                                                                                                                                                                               |         |

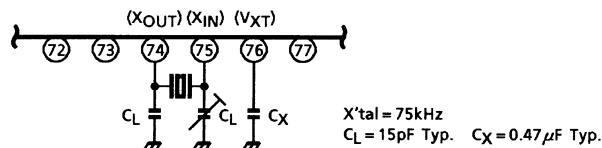

| 74      | X <sub>OUT</sub> | Crystal oscillator pin           | Crystal oscillator pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |

| 75      | X <sub>IN</sub>  |                                  | A reference 75-kHz crystal resonator is connected to the X <sub>IN</sub> and X <sub>OUT</sub> pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |

| 76      | V <sub>XT</sub>  |                                  | The oscillator stops oscillating during CKSTP instruction execution.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |

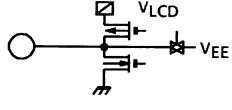

| 77      | V <sub>LCD</sub> | Voltage doubler boosting pin     | <p>The V<sub>XT</sub> pin is the power supply for the crystal oscillator. A stabilizing capacitor (0.47 <math>\mu</math>F typ.) is connected.</p>                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |

| 78      | C1               |                                  | Voltage doubler boosting pin to drive the LCD. A capacitor (0.1 to 3.3 $\mu$ F typ.) is connected to boost the voltage.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |

| 79      | C2               |                                  | <p>The V<sub>LCD</sub> pin outputs voltage (3.1 V), which has been doubled from the constant voltage (V<sub>EE</sub>: 1.55 V) using the capacitor connected between C1 and C2. This potential is supplied to the LCD driver.</p> <p>If the internal V<sub>LCD</sub> OFF bit is set to "1" by program, an external supply can be input through the V<sub>LCD</sub> pin to drive the LCD.</p> <p>At this time, the V<sub>LCD</sub>/2 potential, whose V<sub>LCD</sub> voltage divided using resistors, is output from the C2 pin.</p>                                                 |         |

| Pin No. | Symbol   | Pin Name                    | Function and Operation                                                                                                                                                                                                           | Remarks |

|---------|----------|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| 80      | $V_{EE}$ | Constant voltage supply pin | 1.55 V constant voltage supply pin to drive the LCD.<br>A stabilizing capacitor (0.47 $\mu$ F typ.) is connected. This is a reference voltage for the A/D converter, key input, and the bias potential of the LCD common output. | —       |

Note 1: When the device is reset ( $V_{DD} = 0$  V  $\rightarrow$  1.8 V or higher or  $\overline{RESET} = "L"$   $\rightarrow$  "H") I/O ports are set to input, the pins for both LCD output and I/O ports and additional functions (e.g., SIO, A/D converter) are set to I/O port input pins, while the  $IF_{IN}/IN1/SC_{IN}$  pins become IF input pins.

Note 2: When in PLL OFF mode (when the four bits in the internal reference ports are all set to "1"), the  $IF_{IN}/SC_{IN}$  and  $FM_{IN}$ ,  $AM_{IN}$  pins are pulled down, and DO1 and DO2 are at high impedance.

Note 3: When in CLOCK STOP mode (during execution of CKSTP instruction), the output ports (excluding OT1 output) and LCD output pins are all at low level, while the constant voltage circuit ( $V_{EE}$ ), the voltage doubler circuit ( $V_{LCD}$ ), and the power supply for the crystal oscillator ( $V_{XT}$ ) are at  $V_{DD}$  level.

Note 4: When the device is being reset, the contents of the output ports and internal ports are undefined and must be initialized via software.

Note 5: When the pins for both LCD output and I/O ports are set to the I/O port,  $V_{LCD}$  potential is used as the power supply for the output, so the  $V_{LCD}$  level is output at "H" level. In addition, the input power supply is at  $V_{DD}$  level, so it can be used in the same way as for the other I/O port inputs.

## Description of Operations

### CPU

The CPU consists of a program counter, a stack register, ALU, a program memory, a data memory, a G-register, a data register, a carry F/F and a judgment circuit.

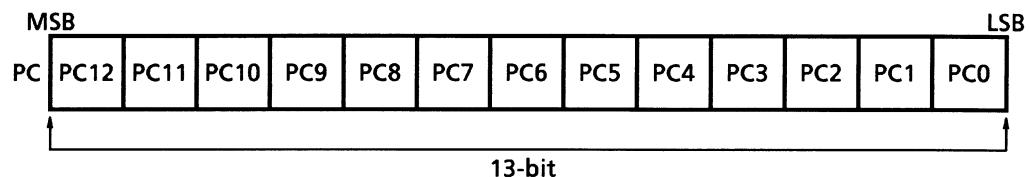

#### 1. Program Counter (PC)

The program counter consists of a 13-bit binary up-counter and addresses the program memory (ROM). The counter is cleared when the system is reset and the programs start from the 0 address.

Under normal conditions, the counter is increased in increments of one whenever an instruction is executed, but the address specified in the instruction operand is loaded when a JUMP instruction or CALL instruction is executed.

Also, when an instruction that is equipped with the skip function (AIS, SLTI, TMT, RNS instructions, etc.) is executed and the result of this includes a skip condition, the program counter is increased in increments of two and the subsequent instruction is skipped.

#### 2. Stack Register (STACK)

A register consisting of  $2 \times 13$  bits which stores the contents of the program counter +1 (the return address) when a sub-routine call instruction is executed. The contents of the stack register are loaded into the program counter when the return instruction (RN or RNS instruction) is executed.

There are two stack levels available and nesting occurs with both levels.

#### 3. ALU

ALU is equipped with binary 4-bit parallel add/subtract functions, logical operation, comparison and multiple bit judgment functions.

This CPU is not equipped with an accumulator, and all operations are handled directly within the data memory.

#### 4. Program Memory (ROM)

The program memory consists of 16 bits  $\times$  7168 steps and is used for storing programs. The usable address range consists of 7168 steps between address 0000H and address 1BFFH.

The program memory is divided into 7168 separate steps and consists of pages 0 to 6. The JUMP instruction can be freely used throughout all 7168 steps. However, the range of use for the CALL instruction is limited to addresses 400H to 7FFH (page 1). It is also possible to use address 000H to 3FFH (page 0) in the program memory as a data area, and the 16-bit contents of this can be loaded into the data register by executing the DAL instruction.

Note 6: An address outside of the program loop must be set when establishing a data area within the program memory.

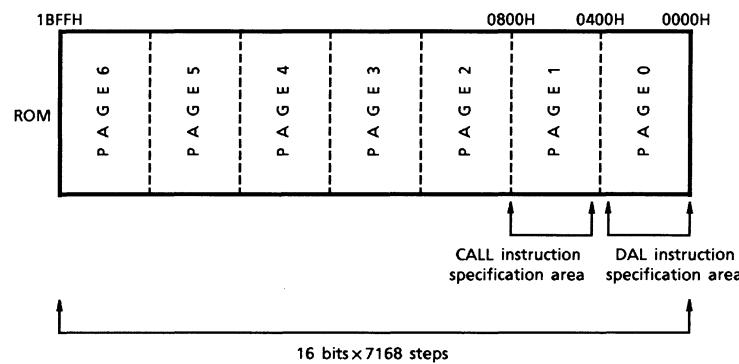

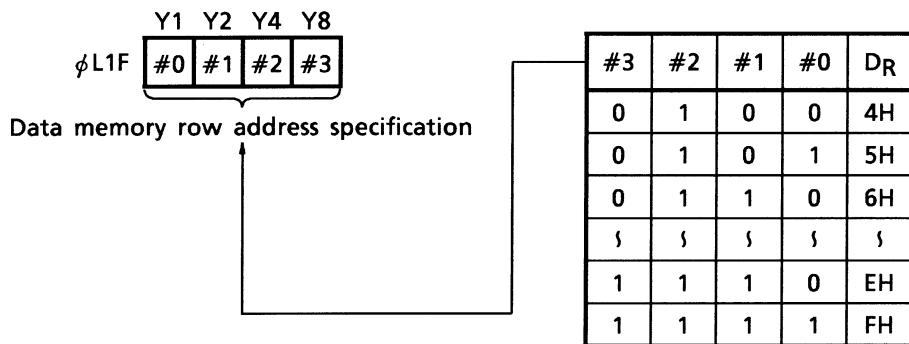

## 5. Data Memory (RAM)

The data memory consists of  $4 \text{ bits} \times 256 \text{ words}$  and is used for storing data. These 256 words are expressed in row addresses (4 bits) and column addresses (4 bits). 192 words (row address = addresses 4H to FH) within the data memory are addressed indirectly by the G-register. Owing to this, it is necessary to specify the row address with the G-register before the data in this area can be processed.

The addresses 00H to 0FH within the data memory are known as general registers, and these can be used simply by specifying the relevant column addresses (4 bit). These sixteen general registers can be used for operations and transfers with the data memory, and may also be used as normal data memories.

Note 7: The column address (4 bit) that specifies the general register is the register number of the general register.

Note 8: All row addresses (addresses 0H to FH) can be specified indirectly with the G-register.

Note 9: The indirect specification of row addresses = 0H to FH is also possible

## 6. G-Register (G-REG)

The G-register is a 4 bit register used for addressing the row addresses (DR = 4H to FH addresses) of the data memory's 192 words.

The contents of this register are validated when the MVGD instruction or MVGS instruction are executed, and are not affected through the execution of any other instructions. This register is used as one of the ports, and the contents are set when the OUT1 instruction from amongst the I/O instructions is executed. (→ refer to section #1 in register ports.)

## 7. Data Register (DATA REG)

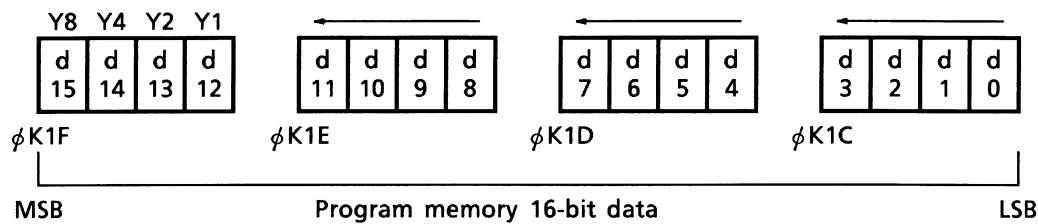

The data register consists of  $1 \times 16$  bits and loads 16 bits of optional address data from amongst addresses 000H to 3FFH in the program memory when the DAL instruction is executed. This register is used as one of the ports, and the contents are loaded into the data memory in units of 4 bits when the IN1 instruction from amongst the I/O instructions is executed. (→ refer to section #2 in register ports.)

## 8. Carry F/F (CF/F)

This is set when either CARRY or BORROW are issued in the result of calculation instruction execution and is reset if neither of these are issued.

The contents of carry F/F can only be amended through the execution of addition or subtraction instructions and are not affected by the execution of any other instruction.

## 9. Judgment Circuit (J)

This circuit judges the skip conditions when an instruction equipped with the skip function is executed. The program counter is increased in increments of two when the skip conditions are satisfied, and the subsequent instruction is skipped.

There are 29 instructions equipped with a wide variety of skip functions available. (→ refer to the items marked with a “\*” symbol in the table of instruction functions and operational instructions in section 11.)

## 10. Instruction Set Table

A total of 62 instruction sets are available, and all of these are single-word instructions. These instructions are expressed with 6-bit instruction codes.

| High Order 2-Bit |   | 00        | 01          | 10         | 11                           |

|------------------|---|-----------|-------------|------------|------------------------------|

| Low Order 4-Bit  |   | 0         | 1           | 2          | 3                            |

| 0000             | 0 | AI M, I   | AD r, M     | TMTR r, M  | SLTI M, I                    |

| 0001             | 1 | AIS M, I  | ADS r, M    | TMFR r, M  | SGEI M, I                    |

| 0010             | 2 | AIN M, I  | AND r, M    | SEQ r, M   | SEQI M, I                    |

| 0011             | 3 | AIC M, I  | AC r, M     | SNE r, M   | SNEI M, I                    |

| 0100             | 4 | AICS M, I | ACS r, M    | LD r, M    | TMTN M, N                    |

| 0101             | 5 | AICN M, I | ACN r, M    | ST M, r    | TMT M, N                     |

| 0110             | 6 | ORIM M, I | ORR r, M    | MVGD r, M  | TMFN M, N                    |

| 0111             | 7 | ANIM M, I | ANDR r, M   | MVGS M, r  | TMF M, N                     |

| 1000             | 8 | SI M, I   | SU r, M     | JUMP ADDR1 | IN1 M, C                     |

| 1001             | 9 | SIS M, I  | SUS r, M    |            | IN2 M, C                     |

| 1010             | A | SIN M, I  | SUN r, M    |            | IN3 M, C                     |

| 1011             | B | SIB M, I  | SB r, M     |            | OUT1 C, M                    |

| 1100             | C | SIBS M, I | SBS r, M    |            | OUT2 C, M                    |

| 1101             | D | SIBN M, I | SBN r, M    |            | OUT3 C, M                    |

| 1110             | E | XORI M, I | XORR r, M   |            | DAL ADDR3, r                 |

| 1111             | F | MVIM M, I | MVSR M1, M2 | CALL ADDR2 | RN, RNS, WAIT<br>CKSTP, NOOP |

**11. Table of Instruction Functions and Operational Instructions

(description of the symbols used in the table)**

M: Data memory address. Generally one of the addresses from amongst addresses 00H to 3FH in the data memory.

r: General register

One of the addresses from amongst addresses 00H to 0FH in the data memory.

PC: Program counter (13 bits)

STACK: Stack register (13 bits)

G: G-register (4 bits)

DATA: Data register (16 bits)

I: Immediate data (4 bits)

N: Bit position (4 bits)

—: ALL "0"

C: Port code No. (4 bits)

CN: Port code No. (4 bits)

RN: General register No. (4 bits)

ADDR1: Program memory address (13 bits)

ADDR2: Program memory address within page 1 (10 bits)

ADDR3: High order 6 bit of the program memory address within page 0

Ca: Carry

b: Borrow

IN1-IN3: The ports used during the execution of instructions IN1 to IN3

OUT1-OUT3: The ports used during the execution of instructions OUT1 to OUT3

( ): Contents of the register or data memory

[ ] C: Contents of the port indicating code No.C (4 bits)

[ ]: Contents of the data memory indicating the contents of the register or data memory

[ ] P: Contents of the program memory (16 bits)

IC: Instruction code (6 bits)

\*: Commands equipped with the skip function

DC: Data memory column address (4 bits)

DR: Data memory row address (2 bits)

| Instruction Group     | Mnemonic | Skip Function | Function Description | Operation Description                                             | Machine Language (16 bits)                         |            |                |                |                |

|-----------------------|----------|---------------|----------------------|-------------------------------------------------------------------|----------------------------------------------------|------------|----------------|----------------|----------------|

|                       |          |               |                      |                                                                   | IC (6 bits)                                        | A (2 bits) | B (4 bits)     | C (4 bits)     |                |

| ADDITION INSTRUCTIONS | AI       | M, I          | —                    | Add immediate data to memory                                      | $M \leftarrow (M) + I$                             | 000000     | D <sub>R</sub> | D <sub>C</sub> | I              |

|                       | AIS      | M, I          | *                    | Add immediate data to memory, then skip if carry                  | $M \leftarrow (M) + I$<br>Skip if carry            | 000001     | D <sub>R</sub> | D <sub>C</sub> | I              |

|                       | AIN      | M, I          | *                    | Add immediate data to memory, then skip if not carry              | $M \leftarrow (M) + I$<br>Skip if not carry        | 000010     | D <sub>R</sub> | D <sub>C</sub> | I              |

|                       | AIC      | M, I          | —                    | Add immediate data to memory with carry                           | $M \leftarrow (M) + I + ca$                        | 000011     | D <sub>R</sub> | D <sub>C</sub> | I              |

|                       | AICS     | M, I          | *                    | Add immediate data to memory with carry, then skip if carry       | $M \leftarrow (M) + I + ca$<br>Skip if carry       | 000100     | D <sub>R</sub> | D <sub>C</sub> | I              |

|                       | AICN     | M, I          | *                    | Add immediate data to memory with carry, then skip if not carry   | $M \leftarrow (M) + I + ca$<br>Skip if not carry   | 000101     | D <sub>R</sub> | D <sub>C</sub> | I              |

|                       | AD       | r, M          | —                    | Add memory to general register                                    | $r \leftarrow (r) + (M)$                           | 010000     | D <sub>R</sub> | D <sub>C</sub> | R <sub>N</sub> |

|                       | ADS      | r, M          | *                    | Add memory to general register, then skip if carry                | $r \leftarrow (r) + (M)$<br>Skip if carry          | 010001     | D <sub>R</sub> | D <sub>C</sub> | R <sub>N</sub> |

|                       | ADN      | r, M          | *                    | Add memory to general register, then skip if not carry            | $r \leftarrow (r) + (M)$<br>Skip if not carry      | 010010     | D <sub>R</sub> | D <sub>C</sub> | R <sub>N</sub> |

|                       | AC       | r, M          | —                    | Add memory to general register with carry                         | $r \leftarrow (r) + (M) + ca$                      | 010011     | D <sub>R</sub> | D <sub>C</sub> | R <sub>N</sub> |

|                       | ACS      | r, M          | *                    | Add memory to general register with carry, then skip if carry     | $r \leftarrow (r) + (M) + ca$<br>Skip if carry     | 010100     | D <sub>R</sub> | D <sub>C</sub> | R <sub>N</sub> |

|                       | ACN      | r, M          | *                    | Add memory to general register with carry, then skip if not carry | $r \leftarrow (r) + (M) + ca$<br>Skip if not carry | 010101     | D <sub>R</sub> | D <sub>C</sub> | R <sub>N</sub> |

| Instruction Group        | Mnemonic | Skip Function | Function Description | Operation Description                                                      | Machine Language (16 bits)                         |            |                |                |                |

|--------------------------|----------|---------------|----------------------|----------------------------------------------------------------------------|----------------------------------------------------|------------|----------------|----------------|----------------|

|                          |          |               |                      |                                                                            | IC (6 bits)                                        | A (2 bits) | B (4 bits)     | C (4 bits)     |                |

| SUBTRACTION INSTRUCTIONS | SI       | M, I          | —                    | Subtract immediate data from memory                                        | $M \leftarrow (M) - I$                             | 001000     | D <sub>R</sub> | D <sub>C</sub> | I              |

|                          | SIS      | M, I          | *                    | Subtract immediate data from memory, then skip if borrow                   | $M \leftarrow (M) - I$<br>Skip if borrow           | 001001     | D <sub>R</sub> | D <sub>C</sub> | I              |

|                          | SIN      | M, I          | *                    | Subtract immediate data from memory, then skip if not borrow               | $M \leftarrow (M) - I$<br>Skip if not borrow       | 001010     | D <sub>R</sub> | D <sub>C</sub> | I              |

|                          | SIB      | M, I          | —                    | Subtract immediate data from memory with borrow                            | $M \leftarrow (M) - I - b$                         | 001011     | D <sub>R</sub> | D <sub>C</sub> | I              |

|                          | SIBS     | M, I          | *                    | Subtract immediate data from memory with borrow, then skip if borrow       | $M \leftarrow (M) - I - b$<br>Skip if borrow       | 001100     | D <sub>R</sub> | D <sub>C</sub> | I              |

|                          | SIBN     | M, I          | *                    | Subtract immediate data from memory with borrow, then skip if not borrow   | $M \leftarrow (M) - I - b$<br>Skip if not borrow   | 001101     | D <sub>R</sub> | D <sub>C</sub> | I              |

|                          | SU       | r, M          | —                    | Subtract memory from general register                                      | $r \leftarrow (r) - (M)$                           | 011000     | D <sub>R</sub> | D <sub>C</sub> | R <sub>N</sub> |

|                          | SUS      | r, M          | *                    | Subtract memory from general register, then skip if borrow                 | $r \leftarrow (r) - (M)$<br>Skip if borrow         | 011001     | D <sub>R</sub> | D <sub>C</sub> | R <sub>N</sub> |

|                          | SUN      | r, M          | *                    | Subtract memory from general register, then skip if not borrow             | $r \leftarrow (r) - (M)$<br>Skip if not borrow     | 011010     | D <sub>R</sub> | D <sub>C</sub> | R <sub>N</sub> |

|                          | SB       | r, M          | —                    | Subtract memory from general register with borrow                          | $r \leftarrow (r) - (M) - b$                       | 011011     | D <sub>R</sub> | D <sub>C</sub> | R <sub>N</sub> |

| COMPARISON INSTRUCTIONS  | SBS      | r, M          | *                    | Subtract memory from general register with borrow, then skip if borrow     | $r \leftarrow (r) - (M) - b$<br>Skip if borrow     | 011100     | D <sub>R</sub> | D <sub>C</sub> | R <sub>N</sub> |

|                          | SBN      | r, M          | *                    | Subtract memory from general register with borrow, then skip if not borrow | $r \leftarrow (r) - (M) - b$<br>Skip if not borrow | 011101     | D <sub>R</sub> | D <sub>C</sub> | R <sub>N</sub> |

|                          | SLTI     | M, I          | *                    | Skip if memory is less than immediate data                                 | Skip if $(M) < I$                                  | 110000     | D <sub>R</sub> | D <sub>C</sub> | I              |

|                          | SGEI     | M, I          | *                    | Skip if memory is greater than or equal to immediate data                  | Skip if $(M) \geq I$                               | 110001     | D <sub>R</sub> | D <sub>C</sub> | I              |

|                          | SEQI     | M, I          | *                    | Skip if memory is equal to immediate data                                  | Skip if $(M) = I$                                  | 110010     | D <sub>R</sub> | D <sub>C</sub> | I              |

|                          | SNEI     | M, I          | *                    | Skip if memory is not equal to immediate data                              | Skip if $(M) \neq I$                               | 110011     | D <sub>R</sub> | D <sub>C</sub> | I              |

| COMPARISON INSTRUCTIONS  | SEQ      | r, M          | *                    | Skip if general register is equal to memory                                | Skip if $(r) = (M)$                                | 100010     | D <sub>R</sub> | D <sub>C</sub> | R <sub>N</sub> |

|                          | SNE      | r, M          | *                    | Skip if general register is not equal to memory                            | Skip if $(r) \neq (M)$                             | 100011     | D <sub>R</sub> | D <sub>C</sub> | R <sub>N</sub> |

| Instruction Group              | Mnemonic | Skip Function | Function Description | Operation Description                                                          | Machine Language (16 bits)               |            |                |                 |                 |

|--------------------------------|----------|---------------|----------------------|--------------------------------------------------------------------------------|------------------------------------------|------------|----------------|-----------------|-----------------|

|                                |          |               |                      |                                                                                | IC (6 bits)                              | A (2 bits) | B (4 bits)     | C (4 bits)      |                 |

| TRANSFER INSTRUCTIONS          | LD       | r, M          | —                    | Load memory to general register                                                | $r \leftarrow (M)$                       | 100100     | D <sub>R</sub> | D <sub>C</sub>  | R <sub>N</sub>  |

|                                | ST       | M, r          | —                    | Store general register to memory                                               | $M \leftarrow (r)$                       | 100101     | D <sub>R</sub> | D <sub>C</sub>  | R <sub>N</sub>  |

|                                | MVSR     | M1, M2        | —                    | Move memory to memory in the same row                                          | $(D_R, D_{C1}) \leftarrow (D_R, D_{C2})$ | 011111     | D <sub>R</sub> | D <sub>C1</sub> | D <sub>C2</sub> |

|                                | MVIM     | M, I          | —                    | Move immediate data to memory                                                  | $M \leftarrow I$                         | 001111     | D <sub>R</sub> | D <sub>C</sub>  | I               |

|                                | MVGD     | r, M          | —                    | Move memory to destination memory referring to G-register and general register | $[(G), (r)] \leftarrow (M)$              | 100110     | D <sub>R</sub> | D <sub>C</sub>  | R <sub>N</sub>  |

|                                | MVGS     | M, r          | —                    | Move source memory referring to G-register and general register to memory      | $M \leftarrow [(G), (r)]$                | 100111     | D <sub>R</sub> | D <sub>C</sub>  | R <sub>N</sub>  |

| I/O INSTRUCTIONS               | IN1      | M, C          | —                    | Input IN1 port data to memory                                                  | $M \leftarrow [IN1] C$                   | 111000     | D <sub>R</sub> | D <sub>C</sub>  | C <sub>N</sub>  |

|                                | OUT1     | C, M          | —                    | Output contents of memory to OUT1 port                                         | $[OUT1] C \leftarrow (M)$                | 111011     | D <sub>R</sub> | D <sub>C</sub>  | C <sub>N</sub>  |

|                                | IN2      | M, C          | —                    | Input IN2 port data to memory                                                  | $M \leftarrow [IN2] C$                   | 111001     | D <sub>R</sub> | D <sub>C</sub>  | C <sub>N</sub>  |

|                                | OUT2     | C, M          | —                    | Output contents of memory to OUT2 port                                         | $[OUT2] C \leftarrow (M)$                | 111100     | D <sub>R</sub> | D <sub>C</sub>  | C <sub>N</sub>  |

|                                | IN3      | M, C          | —                    | Input IN3 port data to memory                                                  | $M \leftarrow [IN3] C$                   | 111010     | D <sub>R</sub> | D <sub>C</sub>  | C <sub>N</sub>  |

|                                | OUT3     | C, M          | —                    | Output contents of memory to OUT3 port                                         | $[OUT3] C \leftarrow (M)$                | 111101     | D <sub>R</sub> | D <sub>C</sub>  | C <sub>N</sub>  |

| LOGICAL OPERATION INSTRUCTIONS | ORR      | r, M          | —                    | Logical OR of general register and memory                                      | $r \leftarrow (r) \vee (M)$              | 010110     | D <sub>R</sub> | D <sub>C</sub>  | R <sub>N</sub>  |

|                                | ANDR     | r, M          | —                    | Logical AND of general register and memory                                     | $r \leftarrow (r) \wedge (M)$            | 010111     | D <sub>R</sub> | D <sub>C</sub>  | R <sub>N</sub>  |

|                                | ORIM     | M, I          | —                    | Logical OR of memory and immediate data                                        | $M \leftarrow (M) \vee I$                | 000110     | D <sub>R</sub> | D <sub>C</sub>  | I               |

|                                | ANIM     | M, I          | —                    | Logical AND of memory and immediate data                                       | $M \leftarrow (M) \wedge I$              | 000111     | D <sub>R</sub> | D <sub>C</sub>  | I               |

|                                | XORIM    | M, I          | —                    | Logical exclusive OR of memory and immediate data                              | $M \leftarrow (M) \oplus I$              | 001110     | D <sub>R</sub> | D <sub>C</sub>  | I               |

|                                | XORR     | r, M          | —                    | Logical exclusive OR of general register and memory                            | $r \leftarrow (r) \oplus (M)$            | 011110     | D <sub>R</sub> | D <sub>C</sub>  | R <sub>N</sub>  |

| Instruction Group         | Mnemonic     | Skip Function | Function Description                                                                                                                              | Operation Description                                         | Machine Language (16 bits) |                 |                |                |

|---------------------------|--------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|----------------------------|-----------------|----------------|----------------|

|                           |              |               |                                                                                                                                                   |                                                               | IC (6 bits)                | A (2 bits)      | B (4 bits)     | C (4 bits)     |

| BIT JUDGMENT INSTRUCTIONS | TMTR r, M    | *             | Test general register bits by memory bits, then skip if all bits specified are true                                                               | Skip if r [N (M)] = all "1"                                   | 100000                     | D <sub>R</sub>  | D <sub>C</sub> | R <sub>N</sub> |

|                           | TMFR r, M    | *             | Test general register bits by memory bits, then skip if all bits specified are false                                                              | Skip if r [N (M)] = all "0"                                   | 100001                     | D <sub>R</sub>  | D <sub>C</sub> | R <sub>N</sub> |

|                           | TMT M, N     | *             | Test memory bits, then skip if all bits specified are true                                                                                        | Skip if M (N) = all "1"                                       | 110101                     | D <sub>R</sub>  | D <sub>C</sub> | N              |

|                           | TMF M, N     | *             | Test memory bits, then skip if all bits specified are false                                                                                       | Skip if M (N) = all "0"                                       | 110111                     | D <sub>R</sub>  | D <sub>C</sub> | N              |

|                           | TMTN M, N    | *             | Test memory bits, then not skip if all bits specified are true                                                                                    | Skip if M (N) = not all "1"                                   | 110100                     | D <sub>R</sub>  | D <sub>C</sub> | N              |

|                           | TMFN M, N    | *             | Test memory bits, then not skip if all bits specified are false                                                                                   | Skip if M (N) = not all "0"                                   | 110110                     | D <sub>R</sub>  | D <sub>C</sub> | N              |

| SUBROUTINE INSTRUCTIONS   | CALL ADDR2   | —             | Call subroutine                                                                                                                                   | STACK $\leftarrow$ (PC) + 1 and PC $\leftarrow$ ADDR2 + 400 H | 101111                     | ADDR2 (10 bits) |                |                |

|                           | RN           | —             | Return to main routine                                                                                                                            | PC $\leftarrow$ (STACK)                                       | 111111                     | 00              | —              | —              |

|                           | RNS          | *             | Return to main routine and skip unconditionally                                                                                                   | PC $\leftarrow$ (STACK) and skip                              | 111111                     | 01              | —              | —              |

| JUMP INSTRUCTIONS         | JUMP ADDR1   | —             | Jump to the address specified                                                                                                                     | PC $\leftarrow$ ADDR1                                         | 101                        | ADDR1 (13 bits) |                |                |

|                           | DAL ADDR3, r | —             | Load program memory in page 0 to DATA register                                                                                                    | DATA $\leftarrow$ [ADDR3 + (r)] P in page 0                   | 111110                     | ADDR3 (6 bits)  |                | R <sub>N</sub> |

| OTHER INSTRUCTIONS        | WAIT P       | —             | At P = "0" H, the condition is CPU waiting (soft wait mode)<br>At P = "1" H, except for clock generator, all function is waiting (hard wait mode) | Wait at condition P                                           | 111111                     | 10              | 0000           | P              |

|                           | CKSTP        | —             | Clock generator stop                                                                                                                              | Stop clock generator in <u>HOLD</u> = "0"                     | 111111                     | 10              | 1000           | —              |

|                           | NOOP         | —             | No operation                                                                                                                                      | —                                                             | 111111                     | 11              | —              | —              |

Note 10: The four low order bits of the program memory's 10-bit address specified with the DAL instruction are addressed indirectly with the contents of the general register.

The execution time for the DAL instruction is 80  $\mu$ s (two machine cycles).

Note 11: The execution time for the MVGS instruction is 80  $\mu$ s (two machine cycles).

## I/O Map

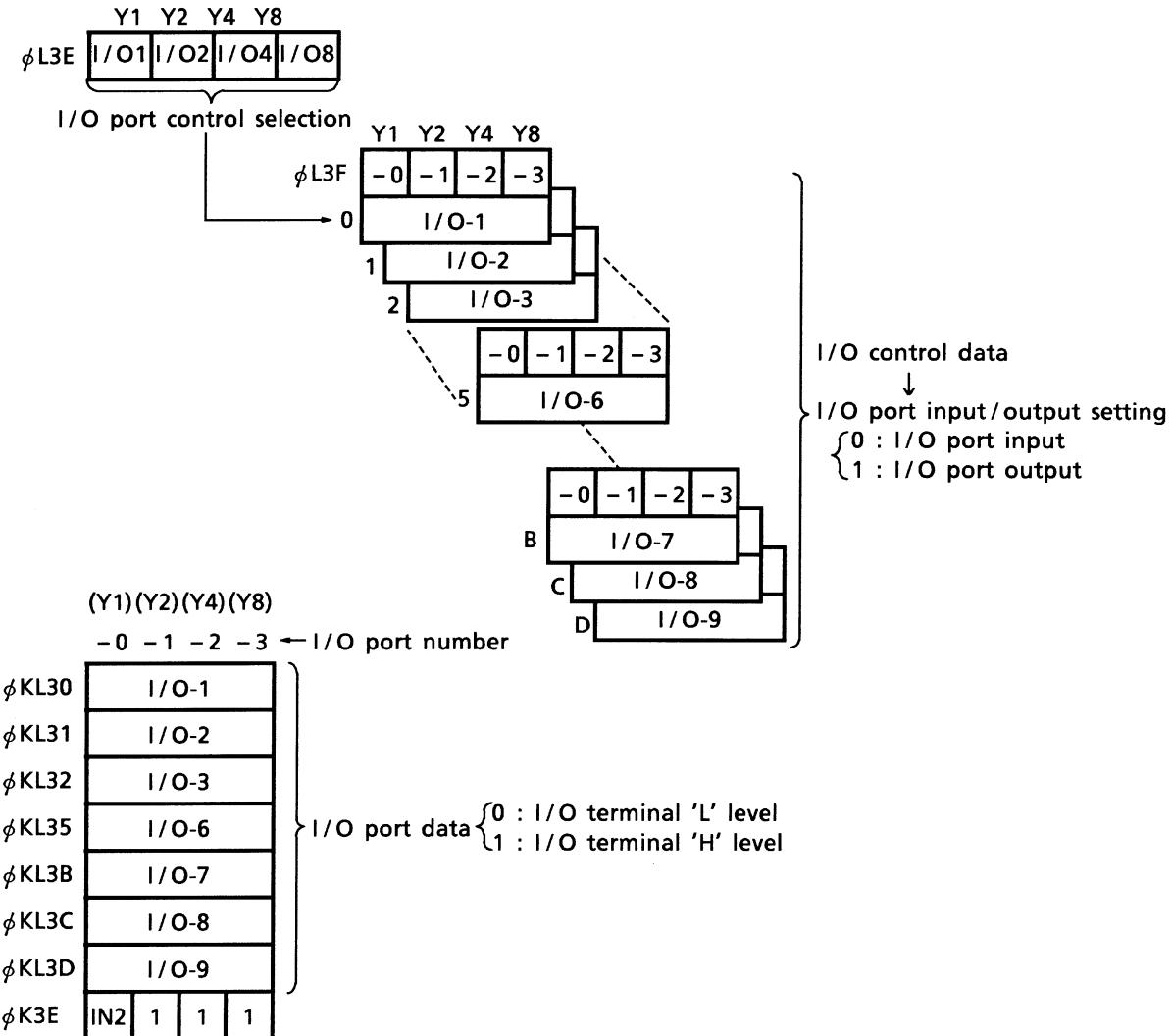

All of the ports within the device are expressed with a matrix of six I/O instructions (OUT 1 to 3 instructions and IN 1 to 3 instructions) and a 4-bit code number.

The allocation of these ports is shown on the following page in the form of an I/O map. The ports used in the execution of the various I/O instructions on the horizontal axis of the I/O map are allocated to the port code numbers indicated on the vertical axis. The G-register and data register are also used as ports.

The OUT 1 to 3 instructions are specified as output ports and the IN 1 to 3 instructions are specified as input ports.

Note 12: The ports indicated by the angled lines on the I/O map do not actually exist within the device.

The contents of other ports and data memories are not affected when data is output to a non-existent output port with the execution of the output instruction. The data loaded from data memories when a non-existent input port has been specified with the execution of an input instruction becomes '1'.

Note 13: The output ports marked with an asterisk (\*) on the I/O map are not used. Data output to these ports assume the 'don't care' status.

Note 14: The Y1 contents of the ports expressed in 4 bits correspond to the data memory data's low order bits and the Y8 contents correspond to the high order bits.

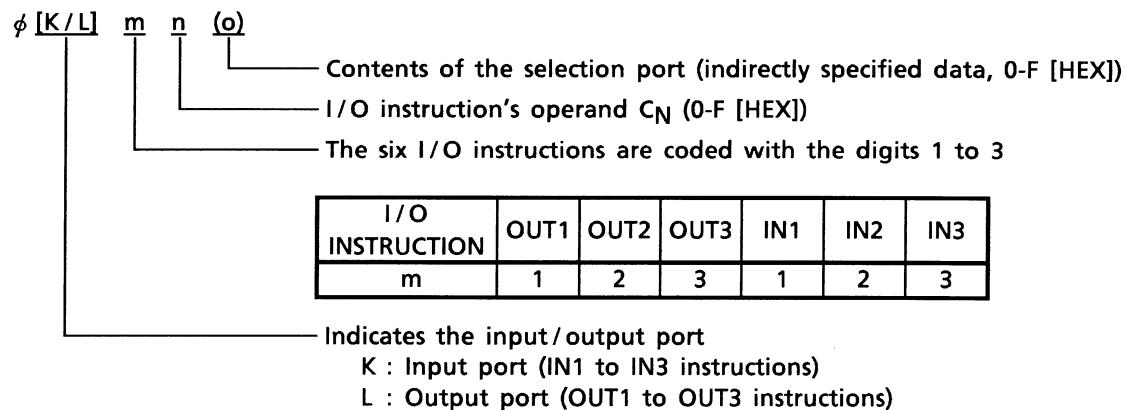

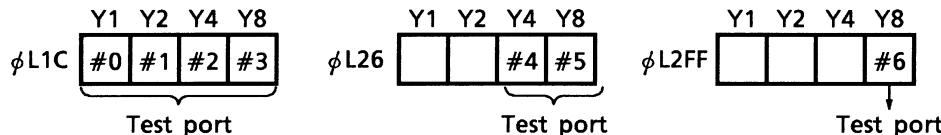

The ports specified with the six I/O instructions and code No.C are coded in the following manner:

(example) The setting for the G-register is allocated to code 'F' in the OUT1 instruction. The encoded expression at this time becomes 'φL1F'.

## I/O Map

| I/O<br>Code | φL1                            |             |                 |                   | φL2                     |                  |                   |          | φL3                   |            |       |       | φK1             |         |      |      | φK2             |                |                  |        | φK3             |            |            |    |    |  |  |  |  |  |

|-------------|--------------------------------|-------------|-----------------|-------------------|-------------------------|------------------|-------------------|----------|-----------------------|------------|-------|-------|-----------------|---------|------|------|-----------------|----------------|------------------|--------|-----------------|------------|------------|----|----|--|--|--|--|--|

|             | OUT1 Instruction               |             |                 |                   | OUT2 Instruction        |                  |                   |          | OUT3 Instruction      |            |       |       | IN1 Instruction |         |      |      | IN2 Instruction |                |                  |        | IN3 Instruction |            |            |    |    |  |  |  |  |  |

|             | Y1                             | Y2          | Y4              | Y8                | Y1                      | Y2               | Y4                | Y8       | Y1                    | Y2         | Y4    | Y8    | Y1              | Y2      | Y4   | Y8   | Y1              | Y2             | Y4               | Y8     | Y1              | Y2         | Y4         | Y8 |    |  |  |  |  |  |

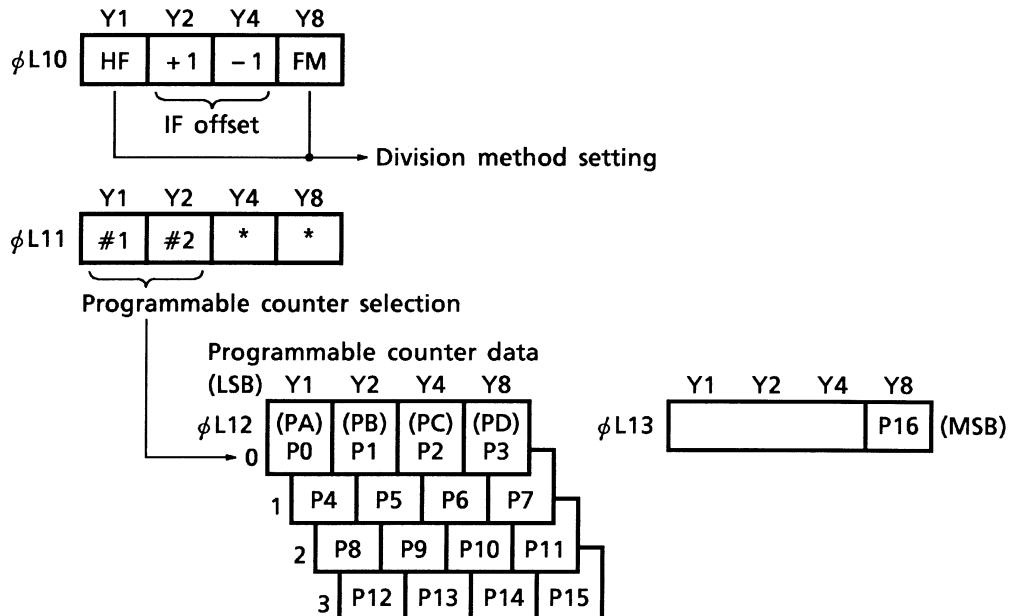

| 0           | HF                             | IF offset   |                 | FM                | A/D control             |                  |                   |          | I/O-1 data            |            |       |       | IF control data |         |      |      | 1               | A/D data       |                  |        |                 | I/O-1 data |            |    |    |  |  |  |  |  |

|             |                                | +1          | -1              |                   | AD SEL0                 | AD SEL1          | REF SEL0          | REF SEL1 | -0                    | -1         | -2    | -3    | BUSY            | Manual  | OVER | 1    | AD0             | AD1            | AD2              | AD3    | -0              | -1         | -2         | -3 |    |  |  |  |  |  |

| 1           | Programmable counter selection |             |                 |                   | A/D control             |                  |                   |          | I/O-2 data            |            |       |       | IF data         |         |      |      | 1               | A/D data       |                  |        |                 | I/O-2 data |            |    |    |  |  |  |  |  |