# 2.5" PATA-SSD Datasheet

# **CONTENTS**

| 1. Overview                                                                                                                                                                                                                                                                                                                                                                                        |    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Features General Description Pin Assignment and Description 4.1 2.5" PATA-SSD Interface Pin Assignments 4.2 2.5" PATA-SSD Pin Descriptions Identify Drive Information Power Management 6.1 Power Saving Flow ATA Command Set System Power Consumption Electrical Specifications D. DC Characters 1. AC Characters 11.1 PIO Data Transfer 11.2 Multi Word DMA 11.3 Ultra DMA. 2. Physical Dimension | 5  |

|                                                                                                                                                                                                                                                                                                                                                                                                    |    |

| •                                                                                                                                                                                                                                                                                                                                                                                                  |    |

| 4.1 2.5" PATA-SSD Interface Pin Assignments                                                                                                                                                                                                                                                                                                                                                        | 9  |

| 4.2 2.5" PATA-SSD Pin Descriptions                                                                                                                                                                                                                                                                                                                                                                 | 10 |

| 5. Identify Drive Information                                                                                                                                                                                                                                                                                                                                                                      | 11 |

| 6. Power Management                                                                                                                                                                                                                                                                                                                                                                                | 13 |

| 6.1 Power Saving Flow                                                                                                                                                                                                                                                                                                                                                                              | 14 |

| 7. ATA Command Set                                                                                                                                                                                                                                                                                                                                                                                 |    |

| 8. System Power Consumption                                                                                                                                                                                                                                                                                                                                                                        | 19 |

| 9. Electrical Specifications                                                                                                                                                                                                                                                                                                                                                                       | 19 |

|                                                                                                                                                                                                                                                                                                                                                                                                    |    |

|                                                                                                                                                                                                                                                                                                                                                                                                    |    |

|                                                                                                                                                                                                                                                                                                                                                                                                    |    |

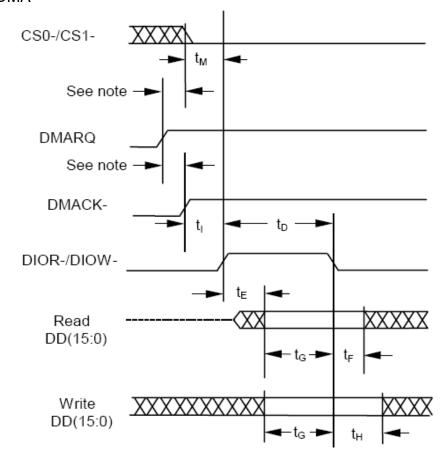

| 11.2 Multi Word DMA                                                                                                                                                                                                                                                                                                                                                                                | 22 |

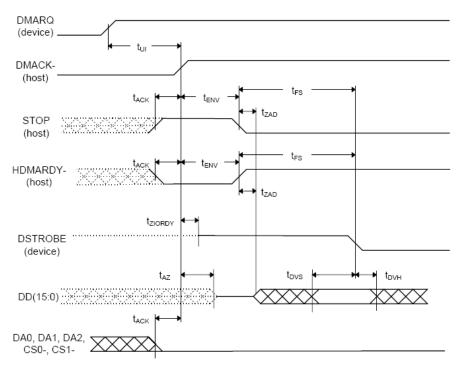

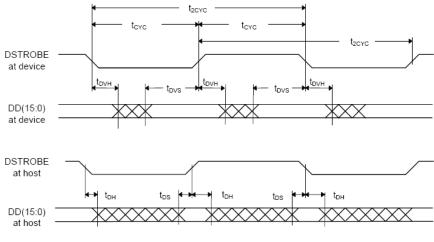

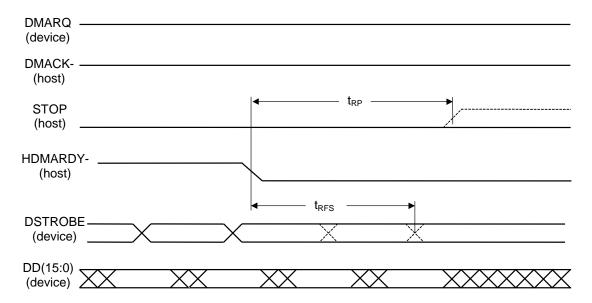

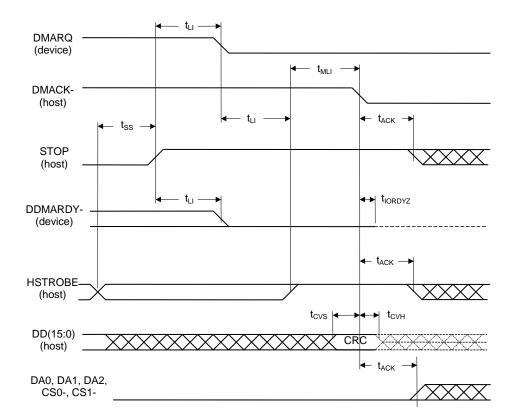

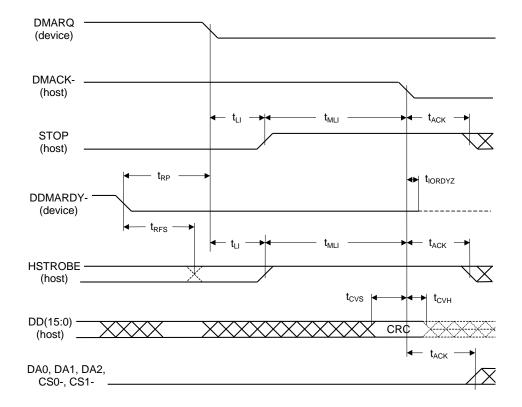

| 11.3 Ultra DMA                                                                                                                                                                                                                                                                                                                                                                                     | 24 |

| 12. Physical Dimension                                                                                                                                                                                                                                                                                                                                                                             | 31 |

| Appendix: Part Number Table                                                                                                                                                                                                                                                                                                                                                                        |    |

|                                                                                                                                                                                                                                                                                                                                                                                                    |    |

# **Revision History**

| Rev. | Date       | History                                    |

|------|------------|--------------------------------------------|

| 0.1  | 2009/3/25  | 1. 1 <sup>st</sup> draft                   |

| 0.2  | 2009/3/30  | Modify description                         |

| 0.3  | 2009/4/16  | Increase testing information               |

| 0.4  | 2009/6/25  | Increase extended temperature product line |

| 0.5  | 2009/7/14  | Fixed the data transfer mode information.  |

| 0.6  | 2009/7/29  | Define form template                       |

| 1.0  | 2010/11/25 | Update Emb'Core Logo & PN List             |

|      |            |                                            |

Advantech reserves the right to make changes without further notice to any products or data herein to improve reliability, function, or design. Information furnished by Advantech is believed to be accurate and reliable. However, Advantech does not assure any liability arising out of the application or use of this information, nor the application or use of any product or circuit described herein, neither does it convey any license under its patent rights or the rights of others.

SQFlash 2.5" PATA-SSD

# 1. Overview

Advantech SQFlash 2.5" PATA-SSD (Solid State Drive) is a non-volatile, solid state data storage system. Due to rapid reduction of flash media, Solid State Drive becomes more and more popular storage media to replace conventional Hard Disk Drive. Free of any mechanical components, 2.5" PATA-SSD provides more robust and cost effective storage solution for embedded application. Offering standard ATA interface, which is fully compatible with traditional HDD, 2.5" PATA-SSD offers the designer an easy solution to implement in PC-based systems.

Advantech SQFlash 2.5" PATA-SSD is one of the most popular cards today based on its high performance, good reliability and wide compatibility.

# 2. Features

- Standard 2.5" PATA Form Factor

- Operating Voltage: 3.3V \ 5.0V

- Standard ATA/IDE Bus Interface

- 512 Bytes/Sector

- ATA command set compatible

- Selectable Master/Slave Setting

# Capacities

- SLC type: 4GB, 8GB, 16GB, 32GB, 64GB

- MLC type: 8GB, 16GB, 32GB, 64GB, 128GB

# Data Transfer mode

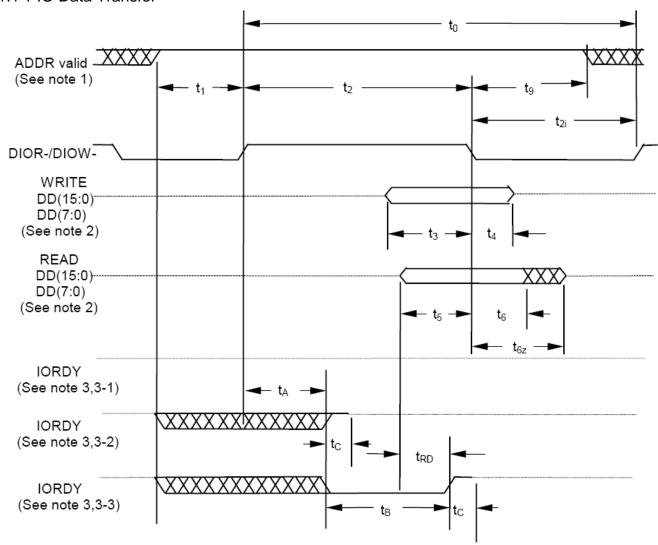

- Support Data Transfer up to PIO mode 4

- Support Data Transfer up to Multiword DMA mode 2

- Support Data Transfer up to Ultra DMA mode 4

### Performance

- SLC type

- Sustain Read Speed up to 65 MB/s

- Sustain Write Speed up to 55 MB/s

- MLC type

- Sustain Read Speed up to 63 MB/s

- Sustain Write Speed up to 28 MB/s

# ■ Temperature Ranges

- Commercial Temperature

- 0°C to 70°C for operating

- -25°C to 85°C for storage

- Extended Temperature

- -40°C to 85°C for operating

- -55°C to 125°C for storage

# Mechanical Specification

Shock: 2,500G / 0.5ms

Vibration: 20G / 80~2,000Hz

# ■ Humidty

Operating Humidity: 5% ~ 95%

Non-Operating Humidity: 5% ~ 95%

### **■** Flash Endurance

SLC type: 100,000 Program/Erase Cycle

MLC type: 5,000 Program/Erase Cycle

# MTBF

2,000,000 hours

# Data Retention

SQFlash 2.5" PATA-SSD

10 years

# ■ Intelligent ATA/IDE Module

- Built-in Embedded Flash File System

- Implements dynamic wear-leveling algorithms and static wear-leveling algorithms to increase endurance of flash media

- This algorithm can correct up to 12 random bits per 512bytes area.

- Acquired RoHS \ CE \ FCC Certificate

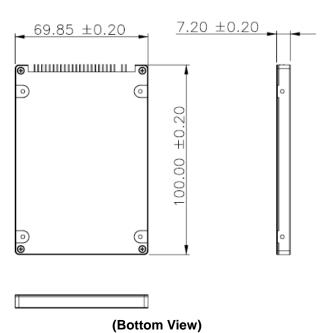

- Dimension: 100mm x 69.85mm x 7.2 mm

# 3. **General Description**

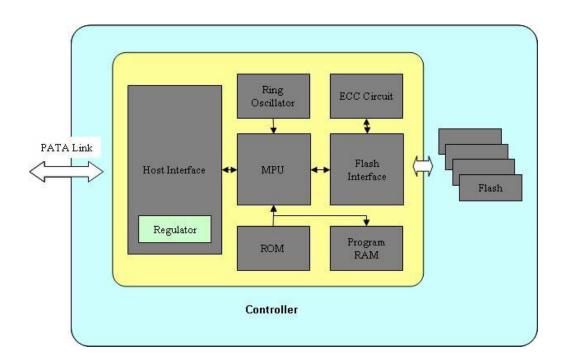

### Advanced NAND Flash Controller

Advantech SQFlash 2.5" PATA-SSD includes Bad Block Management Algorithm, Wear Leveling Algorithm and Error Detection / Correction Code (EDC/ECC) Algorithm.

# Bad Block Management

Bad blocks are blocks that contain one or more invalid bits of which the reliability is not guaranteed. Bad blocks may be representing when flash is shipped and may developed during life time of the device.

Advantech SQFlash 2.5" PATA-SSD implement an efficient bad block management algorithm to detect the factory produced bad blocks and manages any bad blocks that may develop over the life time of the device. This process is completely transparent to the user, user will not aware of the existence of the bad blocks during operation.

# Wear Leveling

NAND Type flash have individually erasable blocks, each of which can be put through a finite number of erase cycles before becoming unreliable. It means after certain cycles for any given block, errors can be occurred in a much higher rate compared with typical situation. Unfortunately, in the most of cases, the flash media will not been used evenly. For certain area, like file system, the data gets updated much frequently than other area. Flash media will rapidly wear out in place without any rotation.

Wear leveling attempts to work around these limitations by arranging data so that erasures and re-writes are distributed evenly across the full medium. In this way, no single sector prematurely fails due to a high concentration of program/erase cycles.

Advantech SQFlash 2.5" PATA-SSD provides advanced wear leveling algorithm, which can efficiently spread out the flash usage through the whole flash media area. By implement both dynamic and static wear leveling algorithms, the life expectancy of the flash media can be improved significantly.

### Error Detection / Correction

Advantech SQFlash 2.5" PATA-SSD utilizes BCH ECC Algorithm which offers one of the most powerful ECC algorithms in the industry. This algorithm can correct up to 12 random bits per 512bytes area.

# Sophisticate Product Management Systems

Since industrial application require much more reliable devices compare with consumer product, a more sophisticated product management system become necessary for industrial customer requirement. The key to providing reliable devices is product traceability and failure analysis system. By implement such systems end customer can expect much more reliable product.

# Block Diagram

REV 1.0 Page 7 of 32 Nov. 25, 2010

# ■ LBA、Cylinders、Heads、Sectors value

| Density | LBA (K bytes) | Cylinders | Heads | Sectors |

|---------|---------------|-----------|-------|---------|

| 4 GB    | 7,880,544     | 7,818     | 16    | 63      |

| 8 GB    | 15,072,624    | 14,953    | 16    | 63      |

| 16 GB   | 30,146,256    | 16,383    | 16    | 63      |

| 32 GB   | 61,078,752    | 16,383    | 16    | 63      |

| 64 GB   | 122,158,512   | 16,383    | 16    | 63      |

| 128 GB  | 249,822,720   | 16,383    | 16    | 63      |

# 4. Pin Assignment and Description

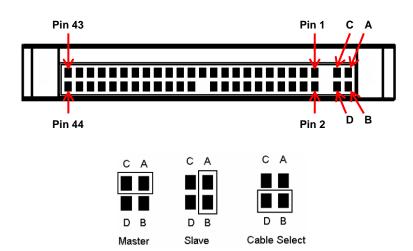

# 4.1 2.5" PATA-SSD Interface Pin Assignments

| Pin# | Signal Name           | Pin Type | Pin# | Signal Name   | Pin Type |

|------|-----------------------|----------|------|---------------|----------|

| 1    | -RESET                | I        | 2    | GND           | -        |

| 3    | DD7                   | I/O      | 4    | DD8           | I/O      |

| 5    | DD6                   | I/O      | 6    | DD9           | I/O      |

| 7    | DD5                   | I/O      | 8    | DD10          | I/O      |

| 9    | DD4                   | I/O      | 10   | DD11          | I/O      |

| 11   | DD3                   | I/O      | 12   | DD12          | I/O      |

| 13   | DD2                   | I/O      | 14   | DD13          | I/O      |

| 15   | DD1                   | I/O      | 16   | DD14          | I/O      |

| 17   | DD0                   | I/O      | 18   | DD15          | I/O      |

| 19   | GND                   | -        | 20   | KEY_PIN(OPEN) |          |

| 21   | DMARQ                 | 0        | 22   | GND           | -        |

| 23   | -DIOW:STOP            | I        | 24   | GND           | -        |

| 25   | -DIOR:-HDMARDY:HSTOBE | 0        | 26   | GND           | -        |

| 27   | IORDY:DDMARDY:DSTROBE |          | 28   | CSEL          | I        |

| 29   | -DMACK                | I        | 30   | GND           | -        |

| 31   | INTRQ                 | 0        | 32   | IOIS16        | 0        |

| 33   | DA1                   | I        | 34   | -PDIAG:-CBLID | I/O      |

| 35   | DA0                   | I        | 36   | DA2           | I        |

| 37   | -CS0                  | I        | 38   | -CS1          | I        |

| 39   | -DASP                 | I/O      | 40   | GND           | -        |

| 41   | VCC                   | Р        | 42   | VCC           | Р        |

| 43   | GND                   | -        | 44   | NC            |          |

### \*Note:

"I": An input from the host system to the device.

"O" : An output from the device to the host system.

"I/O": An input/output (bi-direction) common.

"P": Power supply.

# 4.2 2.5" PATA-SSD Pin Descriptions

| Pin #                                                         | Signal Name                                | Pin Type | Description                                                                                                                                                                                                                                                                             |

|---------------------------------------------------------------|--------------------------------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                                                             | -RESET                                     | I        | Hardware reset signal from the host                                                                                                                                                                                                                                                     |

| 17, 15, 13, 11, 9,<br>7, 5, 3, 4, 6, 8,<br>10, 12, 14, 16, 18 | DD0~DD15<br>(Device Data)                  | I/O      | 16-bit bi-direction Data Bus. DD (7:0) are used for 8-bit register transfers.                                                                                                                                                                                                           |

| 21                                                            | DMARQ<br>(DMA Request)                     | 0        | For DMA data transfers. Device will assert DMARQ when the device is ready to transfer data to or from the host.                                                                                                                                                                         |

| 23                                                            | -DIOW<br>(I/O Write)<br>STOP               | . 1      | This is the strobe signal used by the host to write to the device register or Data port  The host assert this signal during an UDMA                                                                                                                                                     |

|                                                               | (Stop UDMA Burst)                          |          | burst to stop the DMA burst                                                                                                                                                                                                                                                             |

|                                                               | IORDY<br>(I/O channel ready)               |          | This signal is used to temporarily stop the host register access (read or write) when the device is not ready to respond to a data transfer request.                                                                                                                                    |

| 25                                                            | DDMARDY<br>(UDMA ready)                    | 0        | The device will assert this signal to indicate that the device is ready to receive UDMA data-out burst.                                                                                                                                                                                 |

|                                                               | DSTROBE<br>(UDMA data strobe)              |          | When UDMA mode DMA Read is active, this signal is the data-in strobe generated by the device.                                                                                                                                                                                           |

| 28                                                            | CSEL<br>(Cable select)                     | 1        | This pin is used to configure this device as Device 0 or Device 1.                                                                                                                                                                                                                      |

| 29                                                            | -DMACK<br>(DMA acknowledge)                | I        | This signal is used by the host in respond to DMARQ to initiate DMA transfer.                                                                                                                                                                                                           |

| 31                                                            | INTRQ<br>(Interrupt)                       | 0        | When this device is selected, this signal is the active high Interrupt Request to the host                                                                                                                                                                                              |

| 32                                                            | IOIS16                                     | 0        | During PIO transfer mode0, 1 or 2, this pin indicates to the host the 16-bit data port has been addressed and the device is prepared to send or receive a 16-bit data word. When transferring in DMA mode, the host must use a 16-bit DMA channel and this signal will not be asserted. |

| 35, 33, 36                                                    | DA0~DA2<br>(Device Address)                | I        | This is 3-bit binary coded Address Bus.                                                                                                                                                                                                                                                 |

| 34                                                            | -PDIAG<br>(Passed diagnostics)             | I/O      | This signal will be asserted by Device 1 to indicate to Device 0 that Device 1 has completed diagnostics,                                                                                                                                                                               |

|                                                               | -CBLID (Cable assembly type identify)      |          |                                                                                                                                                                                                                                                                                         |

| 37, 38                                                        | -CS0, -CS1<br>(Chip select)                | I        | These signals are used to select the Command Block and Control Block registers. When –DMACK is asserted, -Cs0 and –Cs1 shall be negated and transfers shall be 16-bit wide.                                                                                                             |

| 39                                                            | -DASP<br>(Device active, Device 1 present) | I/O      | During the reset protocol, -DASP shall be asserted by Device 1 to indicate that the device is present.                                                                                                                                                                                  |

| 41, 42                                                        | VCC                                        | Р        | Power supply                                                                                                                                                                                                                                                                            |

| 2, 19, 22, 24, 26,<br>30, 40, 43                              | GND                                        |          | Ground.                                                                                                                                                                                                                                                                                 |

REV 1.0 Page 10 of 32 Nov. 25, 2010

# 5. Identify Drive Information

The Identity Drive Command enables Host to receive parameter information from the device. The parameter words in the buffer have the arrangement and meanings defined in below table. All reserve bits or words are zero

| Word Address | Default Value | Total Bytes | Data Field Type Information                                                        |

|--------------|---------------|-------------|------------------------------------------------------------------------------------|

| 0            | 044Ah         | 2           | General configuration – bit significant for                                        |

|              |               |             | Non-removable device                                                               |

| 1            | xxxxh         | 2           | Default number of cylinders                                                        |

| 2            | 0000h         | 2           | Reserved                                                                           |

| 3            | xxxxh         | 2           | Default number of heads                                                            |

| 4            | 7E00h         | 2           | Retired                                                                            |

| 5            | 0200h         | 2           | Retired                                                                            |

| 6            | xxxxh         | 2           | Default number of sectors per track                                                |

| 7 - 8        | xxxxh         | 4           | Number of sectors per device                                                       |

| 9            | 0000h         | 2           | Retired                                                                            |

| 10 - 19      | xxxxh         | 20          | Serial Number in ASCII                                                             |

| 20           | 0002h         | 2           | Retired                                                                            |

| 21           | 0002h         | 2           | Retired                                                                            |

| 22           | 0004h         | 2           | Number of ECC Bytes passed on Read/Write Long Commands                             |

| 23 - 26      | aaaah         | 8           | Firmware revision in ASCII                                                         |

| 27 - 46      | xxxxh         | 40          | Model number in ASCII                                                              |

| 47           | 8001h         | 2           | Maximum number of sector that shall be transferred on Read/Write Multiple commands |

| 48           | 0000h         | 2           | Reserved                                                                           |

| 49           | 2B00h         | 2           | Capabilities-LBA/DMA Supported                                                     |

| 50           | 4000h         | 2           | Reserved                                                                           |

| 51           | 0200h         | 2           | PIO data transfer cycle timing mode 2                                              |

| 52           | 0000h         | 2           | Retired                                                                            |

| 53           | 0007h         | 2           | Word 54 - 58, 64 - 70 and 88 are valid                                             |

| 54           | xxxxh         | 2           | Current numbers of cylinders                                                       |

| 55           | xxxxh         | 2           | Current numbers of heads                                                           |

| 56           | xxxxh         | 2           | Current sectors per track                                                          |

| 57 - 58      | xxxxh         | 4           | Current capacity in sectors (LBAs)(Word 57= LSW, Word 58= MSW)                     |

| 59           | 0101h         | 2           | Multiple sector setting is valid                                                   |

| 60 - 61      | xxxxh         | 4           | Total number of sectors addressable in LBA Mode                                    |

| 62           | 0000h         | 2           | Retired                                                                            |

| 63           | 0007h         | 2           | Multiword DMA mode 2 and below are supported                                       |

| 64           | 0003h         | 2           | Advance PIO transfer modes supported                                               |

| 65           | 0078h         | 2           | Minimum Multiword DMA transfer cycle time 120nsec                                  |

| 66           | 0078h         | 2           | Manufacturer's recommended Multiword DMA transfer cycle time 120nsec               |

| 67           | 0078h         | 2           | Minimum PIO transfer cycle time without flow control 120nsec                       |

| 68           | 0078h         | 2           | Minimum PIO transfer cycle time with IORDY flow control 120 nsec                   |

| 69 - 79      | 0000h         | 26          | Reserved                                                                           |

| 80           | 0030h         |             | Major version number                                                               |

| 81           | 0000h         |             | Reserved                                                                           |

| 82           | 7009h         | 2           | Supports Security Mode feature set                                                 |

| 83           | 5004h         | 2           | Reserved                                                                           |

| Word Address | Default Value | Total Bytes | Data Field Type Information                                 |

|--------------|---------------|-------------|-------------------------------------------------------------|

| 84           | 4000h         |             |                                                             |

| 85           | 7009h         |             | Feature Setting                                             |

| 86           | 1004h         |             | Feature Setting                                             |

| 87           | 4000h         |             | Feature Setting                                             |

| 88           | 203Fh         | 2           | Ultra DMA mode 5 and below are supported, UDMA mode5 select |

| 89 - 92      | 0000h         | 8           | Reserved                                                    |

| 93           | xxxxh         |             |                                                             |

| 94 - 128     | 0000h         | 2           | Enhanced security erase supported                           |

| 129 - 159    | 0000h         | 62          | Reserved vendor unique bytes                                |

| 160 - 255    | 0000h         | 192         | Reserved                                                    |

\*Note:

"a": Vender Specific Configuration"n": Host Selectable Configuration

# 6. Power Management

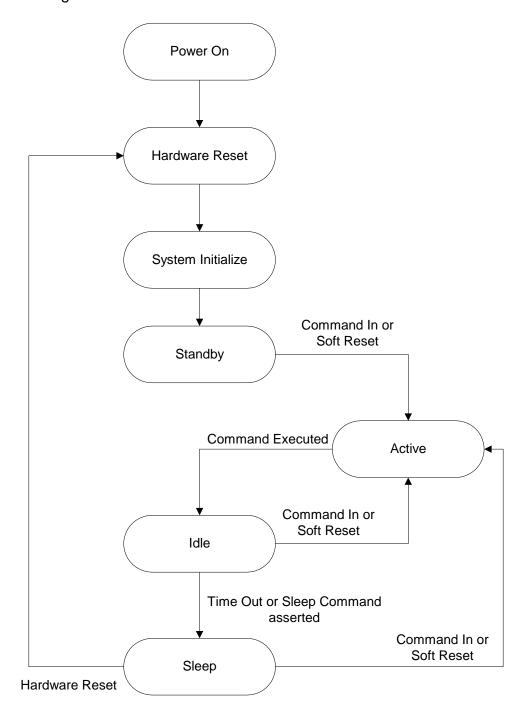

2.5" PATA-SSD provides automatic power saving mode. There are four modes on this system.

Standby Mode: When 2.5" PATA-SSD finishes the initialization routine after power reset, it goes into

Standby Mode and wait for Command In or Soft Reset.

Active Mode: If 2.5" PATA-SSD received any Command In or Soft Reset, it goes into Active Mode.

In Active Mode, it is capable to execute any ATA commands. The power consumption

is the greatest in this mode.

Idle Mode: After 2.5" PATA-SSD executed any ATA Commands or Soft Reset, it goes into Idle

Mode. Power consumption is reduced from Active Mode.

Sleep Mode: The 2.5" PATA-SSD will enter Sleep Mode if there is no Command In or Soft Reset

from the host. Sleep Mode provides the lowest power consumption. During Sleep Mode, the system main clock is stopped. This mode can be waked up from hardware

reset, software reset or any ATA command asserted.

# 6.1 Power Saving Flow

# 7. ATA Command Set

[Command Set List]

| No.   Command set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     | [Command Set List]             |         |     |    |    |    |    |    |     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--------------------------------|---------|-----|----|----|----|----|----|-----|

| EXECUTE DEVICE DIAGNOSTIC   90h   N   N   N   N   N   N   N   N   N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | No. | Command set                    | Code    | FR  | SC | SN | CY | DR | HD | LBA |

| 3   IDENTIFY DEVICE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1   | CHECK POWER MODE               | 98h,E5h | N   | N  | N  | N  | Υ  | N  | N   |

| IDLE   97h,E3h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2   | EXECUTE DEVICE DIAGNOSTIC      | 90h     | N   | N  | N  | N  | Ν  | N  | N   |

| DILE IMMEDIATE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3   | IDENTIFY DEVICE                | Ech     | N   | N  | N  | N  | Υ  | N  | N   |

| 6         INITIALIZE DEVICE PARAMETERS         91h         N         Y         N         N         Y         N         N         Y         N         N         Y         N         N         Y         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y <td< td=""><td>4</td><td>IDLE</td><td>97h,E3h</td><td>N</td><td>Υ</td><td>N</td><td>N</td><td>Υ</td><td>N</td><td>N</td></td<>                               | 4   | IDLE                           | 97h,E3h | N   | Υ  | N  | N  | Υ  | N  | N   |

| 7         NOP         O0h         N         N         N         N         Y         N         N           8         READ BUFFER         E4h         N         N         N         N         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y                                                                                                                                                                         | 5   | IDLE IMMEDIATE                 | 95h,E1h | N   | N  | N  | N  | Υ  | N  | N   |

| 8         READ BUFFER         E4h         N         N         N         Y         N         N         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         <                                                                                                                                                           | 6   | INITIALIZE DEVICE PARAMETERS   | 91h     | N   | Υ  | N  | N  | Υ  | Υ  | N   |

| 9         READ DMA         C8h,C9h         N         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y                                                                                                                                                                    | 7   | NOP                            | 00h     | N   | N  | N  | Ν  | Υ  | Ν  | N   |

| 10   READ MULTIPLE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 8   | READ BUFFER                    | E4h     | N   | N  | N  | Ν  | Υ  | Ν  | N   |

| READ NATIVE MAX ADDRESS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 9   | READ DMA                       | C8h,C9h | N   | Υ  | Υ  | Υ  | Υ  | Υ  | Υ   |

| 12         READ LONG SECTOR         22h,23h         N         N         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         N         N         N         N         N         N         N         N         N         N         N         N         N         N                                                                                                                                                           | 10  | READ MULTIPLE                  | C4h     | N   | Υ  | Υ  | Υ  | Υ  | Υ  | Y   |

| 13         READ SECTOR(S)         20h,21h         N         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N                                                                                                                                                             | 11  | READ NATIVE MAX ADDRESS        | F8h     | N   | N  | N  | N  | Υ  | N  | Υ   |

| 14         READ VERIFY SECTOR(S)         40h,41h         N         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N                                                                                                                                                      | 12  | READ LONG SECTOR               | 22h,23h | N   | N  | Υ  | Υ  | Υ  | Υ  | Y   |

| 15         RECALIBRATE         1Xh         N         N         N         Y         N         N           16         SECURITY DISABLE PASSWORD         F6h         N         N         N         N         Y         N         N           17         SECURITY ERASE PREPARE         F3h         N         N         N         N         Y         N         N           18         SECURITY ERASE UNIT         F4h         N         N         N         N         Y         N         N           19         SECURITY ERASE UNIT         F4h         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N <t< td=""><td>13</td><td>READ SECTOR(S)</td><td>20h,21h</td><td>N</td><td>Υ</td><td>Υ</td><td>Υ</td><td>Υ</td><td>Υ</td><td>Y</td></t<>                 | 13  | READ SECTOR(S)                 | 20h,21h | N   | Υ  | Υ  | Υ  | Υ  | Υ  | Y   |

| 16         SECURITY DISABLE PASSWORD         F6h         N         N         N         Y         N         N           17         SECURITY ERASE PREPARE         F3h         N         N         N         N         Y         N         N           18         SECURITY ERASE UNIT         F4h         N         N         N         N         Y         N         N           19         SECURITY ERASE UNIT         F4h         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N                                                                                                                                                    | 14  | READ VERIFY SECTOR(S)          | 40h,41h | N   | Υ  | Υ  | Υ  | Υ  | Υ  | Y   |

| 17         SECURITY ERASE PREPARE         F3h         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N <td>15</td> <td>RECALIBRATE</td> <td>1Xh</td> <td>N</td> <td>N</td> <td>N</td> <td>N</td> <td>Υ</td> <td>N</td> <td>N</td>                              | 15  | RECALIBRATE                    | 1Xh     | N   | N  | N  | N  | Υ  | N  | N   |

| 18         SECURITY ERASE UNIT         F4h         N         N         N         Y         N         N           19         SECURITY FREEZE LOCK         F5h         N         N         N         N         Y         N         N           20         SECURITY SET PASSWORD         F1h         N         N         N         N         Y         N         N           21         SECURITY UNLOCK         F2h         N         N         N         N         Y         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N<                                                                                                                                                   | 16  | SECURITY DISABLE PASSWORD      | F6h     | N   | N  | N  | N  | Υ  | N  | N   |

| 19         SECURITY FREEZE LOCK         F5h         N         N         N         Y         N         N           20         SECURITY SET PASSWORD         F1h         N         N         N         N         Y         N         N           21         SECURITY UNLOCK         F2h         N         N         N         Y         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N <td>17</td> <td>SECURITY ERASE PREPARE</td> <td>F3h</td> <td>N</td> <td>N</td> <td>N</td> <td>N</td> <td>Υ</td> <td>N</td> <td>N</td>                 | 17  | SECURITY ERASE PREPARE         | F3h     | N   | N  | N  | N  | Υ  | N  | N   |

| 20         SECURITY SET PASSWORD         F1h         N         N         N         Y         N         N           21         SECURITY UNLOCK         F2h         N         N         N         N         Y         N         N           22         SEEK         7Xh         N         N         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N                                                                                                                                                             | 18  | SECURITY ERASE UNIT            | F4h     | N   | N  | N  | N  | Υ  | N  | N   |

| 21         SECURITY UNLOCK         F2h         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N                                                                                                                                                                | 19  | SECURITY FREEZE LOCK           | F5h     | N   | N  | N  | N  | Υ  | N  | N   |

| 22         SEEK         7Xh         N         N         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N </td <td>20</td> <td>SECURITY SET PASSWORD</td> <td>F1h</td> <td>N</td> <td>N</td> <td>N</td> <td>N</td> <td>Υ</td> <td>N</td> <td>N</td>                       | 20  | SECURITY SET PASSWORD          | F1h     | N   | N  | N  | N  | Υ  | N  | N   |

| 23         SET FEATURE         EFh         Y         Y         Y         Y         Y         Y         Y         Y         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N                                                                                                                                                                    | 21  | SECURITY UNLOCK                | F2h     | N   | N  | N  | N  | Υ  | N  | N   |

| 24         SET MULTIPLE         C6h         N         Y         N         N         Y         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N                                                                                                                                                                   | 22  | SEEK                           | 7Xh     | N   | N  | Υ  | Υ  | Υ  | Υ  | Y   |

| 25         SLEEP         99h,E6h         N         N         N         N         Y         N         N           26         SMART ENABLE/DISABLE AUTO SAVE         B0h         D2h         Y         N         Y         Y         N         N           27         SMART ENABLE OPERATION         B0h         D8h         N         N         Y         Y         N         N           28         SMART DISABLE OPERATION         B0h         D9h         N         N         Y         Y         N         N           29         SMART RETURN STATUS         B0h         DAh         N         N         Y         Y         N         N           30         STANDBY         96h,E2h         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N                                                                                                                                               | 23  | SET FEATURE                    | EFh     | Υ   | Υ  | Υ  | Υ  | Υ  | Υ  | N   |

| 26         SMART ENABLE/DISABLE AUTO SAVE         B0h         D2h         Y         N         Y         Y         N         N           27         SMART ENABLE OPERATION         B0h         D8h         N         N         Y         Y         N         N           28         SMART DISABLE OPERATION         B0h         D9h         N         N         Y         Y         N         N           29         SMART RETURN STATUS         B0h         DAh         N         N         Y         Y         N         N           30         STANDBY         96h,E2h         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N                                                                                                                                                  | 24  | SET MULTIPLE                   | C6h     | N   | Υ  | N  | N  | Υ  | N  | N   |

| 27         SMART ENABLE OPERATION         B0h         D8h         N         N         Y         Y         N         N           28         SMART DISABLE OPERATION         B0h         D9h         N         N         Y         Y         N         N           29         SMART RETURN STATUS         B0h         DAh         N         N         Y         Y         N         N           30         STANDBY         96h,E2h         N         N         N         N         Y         N         N         N           31         STANDBY IMMEDIATE         94h,E0h         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         Y         Y         Y         Y         Y         Y                                                                                                                                                   | 25  | SLEEP                          | 99h,E6h | N   | N  | Ν  | N  | Υ  | N  | N   |

| 28         SMART DISABLE OPERATION         B0h         D9h         N         N         Y         Y         N         N           29         SMART RETURN STATUS         B0h         DAh         N         N         Y         Y         N         N           30         STANDBY         96h,E2h         N         N         N         N         Y         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y </td <td>26</td> <td>SMART ENABLE/DISABLE AUTO SAVE</td> <td>B0h</td> <td>D2h</td> <td>Υ</td> <td>N</td> <td>Υ</td> <td>Υ</td> <td>N</td> <td>N</td> | 26  | SMART ENABLE/DISABLE AUTO SAVE | B0h     | D2h | Υ  | N  | Υ  | Υ  | N  | N   |

| 29         SMART RETURN STATUS         B0h         DAh         N         N         Y         Y         N         N           30         STANDBY         96h,E2h         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N                                                                                                                                                               | 27  | SMART ENABLE OPERATION         | B0h     | D8h | N  | N  | Υ  | Υ  | Ν  | N   |

| 30         STANDBY         96h,E2h         N         N         N         Y         N         N           31         STANDBY IMMEDIATE         94h,E0h         N         N         N         N         Y         N         N           32         WRITE BUFFER         E8h         N         N         N         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         <                                                                                                                                                         | 28  | SMART DISABLE OPERATION        | B0h     | D9h | N  | N  | Υ  | Υ  | N  | N   |

| 31         STANDBY IMMEDIATE         94h,E0h         N         N         N         Y         N         N           32         WRITE BUFFER         E8h         N         N         N         N         Y         N         N           33         Write DMA         CAh,CBh         N         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y                                                                                                                                                                 | 29  | SMART RETURN STATUS            | B0h     | DAh | N  | N  | Υ  | Υ  | N  | N   |

| 32         WRITE BUFFER         E8h         N         N         N         Y         N         N           33         Write DMA         CAh,CBh         N         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y         Y <td< td=""><td>30</td><td>STANDBY</td><td>96h,E2h</td><td>N</td><td>N</td><td>N</td><td>N</td><td>Υ</td><td>N</td><td>N</td></td<>                                   | 30  | STANDBY                        | 96h,E2h | N   | N  | N  | N  | Υ  | N  | N   |