# VSC3304 8.5 Gbps 4 × 4 Asynchronous Crosspoint Switch

Datasheet

VMDS-10236 Revision 4.0 December 2008 Vitesse Corporate Headquarters 741 Calle Plano Camarillo, California 93012 United States

www.vitesse.com

Copyright© 2006–2008 by Vitesse Semiconductor Corporation

Vitesse Semiconductor Corporation ("Vitesse") retains the right to make changes to its products or specifications to improve performance, reliability or manufacturability. All information in this document, including descriptions of features, functions, performance, technical specifications and availability, is subject to change without notice at any time. While the information furnished herein is held to be accurate and reliable, no responsibility will be assumed by Vitesse for its use. Furthermore, the information contained herein does not convey to the purchaser of microelectronic devices any license under the patent right of any manufacturer.

Vitesse products are not intended for use in life support products where failure of a Vitesse product could reasonably be expected to result in death or personal injury. Anyone using a Vitesse product in such an application without express written consent of an officer of Vitesse does so at their own risk, and agrees to fully indemnify Vitesse for any damages that may result from such use or sale.

Vitesse Semiconductor Corporation is a registered trademark. All other products or service names used in this publication are for identification purposes only, and may be trademarks or registered trademarks of their respective companies. All other trademarks or registered trademarks mentioned herein are the property of their respective holders.

# **Contents**

| Rev | ision | History                                            | 7  |

|-----|-------|----------------------------------------------------|----|

| 1   | Pro   | oduct Overview                                     | 11 |

|     | 1.1   | Features                                           |    |

|     | 1.2   | Block Diagram                                      |    |

|     | 1.3   | Applications                                       |    |

|     | 1.5   | Applications                                       |    |

| 2   |       | nctional Descriptions                              |    |

|     | 2.1   | Reset                                              |    |

|     | 2.2   | Initialization                                     |    |

|     | 2.3   | Page-Based Programming                             |    |

|     | 2.4   | Two-Wire Serial Interface                          |    |

|     | 2.5   | Four-Wire Serial Bus (Serial Peripheral Interface) |    |

|     | 2.6   | Crosspoint Connections                             | 18 |

|     | 2.7   | Reconfigurable Ports                               | 18 |

|     | 2.8   | Input Configuration                                |    |

|     |       | 2.8.1 Input Signal Equalization (ISE)              |    |

|     |       | 2.8.2 Input Port Termination                       |    |

|     |       | 2.8.3 Input Port Disable                           |    |

|     |       | 2.8.4 Input Signal Invert                          |    |

|     |       | 2.8.5 Input LOS                                    |    |

|     | 2.9   | Output Configuration                               |    |

|     | ,     | 2.9.1 Output Pre-Emphasis                          |    |

|     |       | 2.9.2 Output Power Level                           |    |

|     |       | 2.9.3 Output Signal Suppression and Inversion      |    |

|     |       | 2.9.4 Out of Band Signal Forwarding                |    |

|     | 2 10  | ) Status Bits                                      |    |

|     |       | Channel Status                                     |    |

|     |       | 2 Global Programming                               |    |

|     | 2.12  | Clobal Frogramming                                 | 24 |

| 3   | Reg   | gisters                                            | 26 |

|     | 3.1   | Individual Register Map                            | 26 |

|     | 3.2   | Global Register Map                                | 27 |

|     | 3.3   | Individual Registers                               | 28 |

|     |       | 3.3.1 Connection                                   | 28 |

|     |       | 3.3.2 Input ISE                                    | 28 |

|     |       | 3.3.3 Input State                                  |    |

|     |       | 3.3.4 Input LOS                                    |    |

|     |       | 3.3.5 Output Pre Long                              |    |

|     |       | 3.3.6 Output Pre Short                             |    |

|     |       | 3.3.7 Output Level                                 |    |

|     |       | 3.3.8 Output State                                 |    |

|     |       | 3.3.9 Channel Status                               |    |

|     |       |                                                    |    |

|     |       | 3.3.10 Status 0 Configuration                      |    |

|     |       | 3.3.11 Status 1 Configuration                      |    |

|     |       | 3.3.12 Status State                                |    |

|     | 3.4   | Global Registers                                   |    |

|     |       | 3.4.1 Global Input ISE                             |    |

|     |       | 3.4.2 Global Input State                           |    |

|     |       | 3.4.3 Global Input LOS                             |    |

|     |       | 3 4 4 Global Output Pre Long                       | 37 |

|   |     | 3.4.5    | Global Output Pre Short       | 37 |

|---|-----|----------|-------------------------------|----|

|   |     | 3.4.6    | Global Output Level           |    |

|   |     | 3.4.7    | Global Output State           |    |

|   |     | 3.4.8    | Global Status 0 Configuration |    |

|   |     | 3.4.9    | Global Status 1 Configuration |    |

|   |     | 3.4.10   | Serial Address                |    |

|   |     | 3.4.11   | Interface Mode                |    |

|   |     | 3.4.12   |                               |    |

|   |     | 3.4.13   | Current Page                  |    |

| 4 | Ele | ctrical  | Specifications                | 42 |

|   | 4.1 | DC Cha   | aracteristics                 | 42 |

|   |     | 4.1.1    | High-Speed Data Inputs        | 42 |

|   |     | 4.1.2    | High-Speed Data Outputs       | 42 |

|   |     | 4.1.3    | LVTTL/CMOS Input Signals      | 44 |

|   |     | 4.1.4    | LVTTL/CMOS Output Signals     | 44 |

|   |     | 4.1.5    | Power Supply Requirements     | 44 |

|   | 4.2 | AC Cha   | racteristics                  | 45 |

|   |     | 4.2.1    | High-Speed Data Inputs        |    |

|   |     | 4.2.2    | High-Speed Data Outputs       |    |

|   |     | 4.2.3    | Two-Wire Serial Interface     |    |

|   |     | 4.2.4    | Four-Wire Serial Interface    |    |

|   | 4.3 |          | ing Conditions                |    |

|   | 4.4 | Stress   | Ratings                       | 49 |

| 5 | Pin | Descr    | iptions                       | 50 |

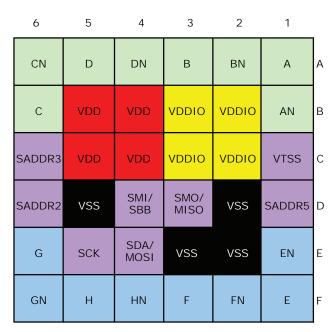

|   | 5.1 | Pin Dia  | gramgram                      | 50 |

|   | 5.2 | Pin Ide  | ntifications                  | 50 |

|   |     | 5.2.1    | High-Speed Data Pins          |    |

|   |     | 5.2.2    | Control Pins                  |    |

|   |     | 5.2.3    | Power Supplies                | 52 |

| 6 | Pac | _        | Information                   |    |

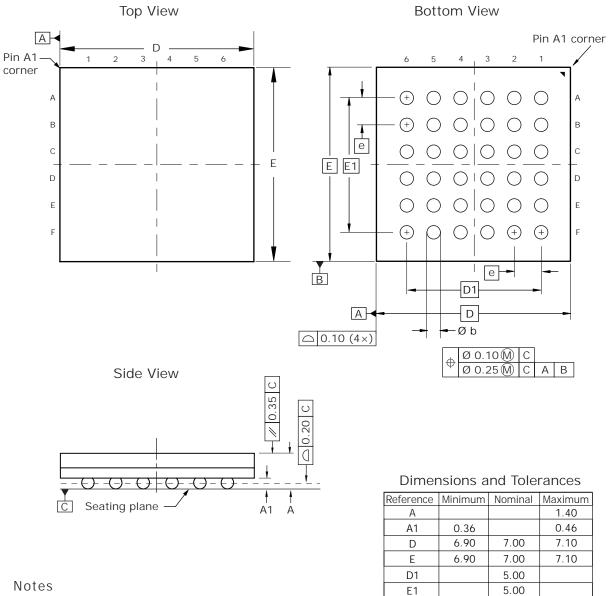

|   | 6.1 |          | e Drawing                     |    |

|   | 6.2 |          | al Specifications             |    |

|   | 6.3 | Moistur  | e Sensitivity                 | 55 |

| 7 | Des | sign Co  | onsiderations                 | 56 |

| R | 0   | lorine ' | Information                   | 57 |

| ~ |     |          | Intormation                   | 7  |

# **Figures**

| Figure 1. | Block Diagram                            | 13 |

|-----------|------------------------------------------|----|

| Figure 2. |                                          |    |

| Figure 3. | Register Map for Global Registers        |    |

|           | Two-Wire Serial Interface Timing Diagram |    |

| -         | Four-Wire Interface Operation            |    |

| Figure 6. | Pin Diagram                              | 50 |

| Figure 7. | Package Drawing                          | 54 |

# **Tables**

| Table 1.  | Features and Benefits                                |    |

|-----------|------------------------------------------------------|----|

| Table 2.  | Device Address vs. Address Pin State                 | 16 |

| Table 3.  | Global Registers and Associated Pages                | 24 |

| Table 4.  | Connection                                           |    |

| Table 5.  | Input ISE                                            |    |

| Table 6.  | Input State                                          |    |

| Table 7.  | Input LOS                                            | 29 |

| Table 8.  | Output Pre Long                                      | 30 |

| Table 9.  | Output Pre Short                                     | 30 |

| Table 10. | Output Level                                         | 31 |

| Table 11. | Output State                                         | 32 |

| Table 12. | Channel Status                                       | 32 |

| Table 13. | Status 0 Configuration                               |    |

| Table 14. | Status 1 Configuration                               | 33 |

| Table 15. | Status State                                         | 34 |

| Table 16. | Global Input ISE                                     | 35 |

| Table 17. | Global Input State                                   | 35 |

| Table 18. | Global Input LOS                                     | 36 |

| Table 19. | Global Output Pre Long                               | 37 |

| Table 20. | Global Output Pre Short                              | 37 |

| Table 21. | Global Output Level                                  | 38 |

| Table 22. | Global Output State                                  | 38 |

| Table 23. | Global Status 0 Configuration                        | 39 |

| Table 24. | Global Status 1 Configuration                        |    |

| Table 25. | Serial Address                                       | 39 |

| Table 26. | Interface Mode                                       | 40 |

| Table 27. | Initial Setup                                        | 40 |

| Table 28. | Current Page                                         | 41 |

| Table 29. | High-Speed Data Inputs                               |    |

| Table 30. | High-Speed Data Outputs                              |    |

| Table 31. | LVTTL/CMOS Input Signals                             |    |

| Table 32. | LVTTL/CMOS Output Signals                            | 44 |

| Table 33. | Power Supply Requirements                            |    |

| Table 34. | High-Speed Data Inputs                               |    |

| Table 35. | High-Speed Data Outputs                              |    |

| Table 36. | Two-Wire Serial Interface AC Signal Characteristics  |    |

| Table 37. | Four-Wire Serial Interface AC Signal Characteristics | 48 |

| Table 38. | Recommended Operating Conditions                     |    |

| Table 39. | Stress Ratings                                       |    |

| Table 40. | High-Speed Data Pins                                 |    |

| Table 41. | Control Pins                                         |    |

| Table 42. | Power Supplies                                       |    |

| Table 43. | Thermal Resistances                                  |    |

| Table 44  |                                                      | 57 |

# **Revision History**

This section describes the changes that were implemented in this document. The changes are listed by revision, starting with the most current publication.

### **Revision 4.0**

Revision 4.0 of this datasheet was published in December 2008. The following is a summary of the changes implemented in the datasheet:

- In the register map for the individual registers, the functionality of bits 2:0 (LOS threshold) in the Input LOS register was corrected to be consistent with the register. For more information, see Figure 2, page 26.

- The moisture sensitivity is now specified as level 4.

- For reference purposes, typical ranges are now provided for long and short preemphasis levels and pre-emphasis decay settings. For more information, see Table 8, page 30, Table 9, page 30, Table 19, page 37, and Table 20, page 37.

- The reset value for output power levels, bits 3:0 in the individual and global Output Level registers, was corrected from 0000 to 0001.

- The recommended operating temperature was changed to -40 °C to 110 °C for 6.5 Gbps operation and -40 °C to 100 °C for 8.5 Gbps operation, based on characterization results. For more information, see "Operating Conditions," page 49.

- As a result of final characterization, the input voltage swing parameter was updated, based on the operating conditions stated earlier in this section. For more information, see Table 29, page 42, Table 34, page 45, and Table 35, page 46.

- Power dissipation values for nominal and maximum drive levels were also updated based on final characterization. For more information, see Table 33, page 44.

- The typical value for the propagation delay was changed from 450 ps to 420 ps.

- A design consideration was added about using the OOB forwarding feature with SAS or SATA applications. For more information, see "Design Considerations," page 56.

- Information about the Software Reset register was removed, because the same information is provided in the Initial Setup register.

# **Revision 2.2**

Revision 2.2 of this datasheet was published in August 2008. The following is a summary of the changes implemented in the datasheet:

- Electrostatic discharge (ESD) voltage was added. For human body model (HBM), it is Class 2. For charged device model (CDM), it is ±750 V.

- The power-on reset sequence was clarified to state that if an external controller is connected to a power supply other than VDD, VDD must be powered up first. The

- power-on reset circuitry sequence was also modified to include the VDDIO supply as well as the VDD supply.

- It is recommended that an external heatsink be used for higher power level configurations.

- Theta JB is now specified as 28 °C/W.

- The maximum case operating temperature was extended from 85 °C to 110 °C.

- Package dimensions and tolerances were modified. The most significant modification was the maximum package height, which changed from 1.44 mm to 1.40 mm.

- The first write operation when configuring the device was modified to include the SPI interface in proper format.

- Restrictions on I/O configurations and output level and pre-emphasis settings were added to ensure that the device does not exceed maximum power dissipation specifications.

- In the individual and global Input LOS registers, the input loss-of-signal (LOS) threshold bit settings (bits 2:0) were updated.

- The minimum value for the input voltage swing, differential drive, changed from 100 mV to 200 mV.

- The serial data output voltage swing levels were updated based on characterization results.

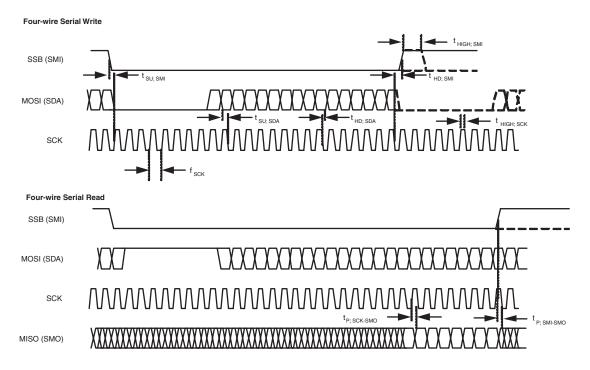

- Four-wire serial timing has been fully characterized and is now supported.

- In the Stress Ratings, the potential to ground rating was separated into two specifications to clarify the maximum value for each power supply. For  $V_{DD}$ , the maximum value is 3.0 V, and for  $V_{DDIO}$ , the maximum value is 3.8 V. For both parameters, the minimum value remains at -0.5 V. Additionally, the maximum value for the TTL DC input voltage applied changed from  $V_{DD}\,+\,1.0$  V to  $V_{DD}\,+\,0.5$  V.

- For clarification purposes, the output common-mode voltage was updated to include the V<sub>DDIO</sub> 2.5 V condition, with values of 0.5 V minimum, 1.1 V typical, and 1.7 V maximum. For the 3.3 V condition, the minimum value changed from 1.9 V to 1.3 V, the typical value changed from 2.1 V to 1.9 V, and the maximum value changed from 2.3 V to 2.5 V.

- For the LVTTL/CMOS input signals, the maximum value for the input HIGH voltage changed from  $V_{DD}$  + 0.7 V to  $V_{DD}$  + 0.5 V. Additionally, the input HIGH current and the input LOW current changed from  $\pm 10$  mA to  $\pm 150$   $\mu$ A.

- A pull-up resistor is required on the SDA pin for the LVTTL/CMOS output signals.

- References to "any input A" and "any output Y" and their associated symbols were removed, because they do not apply to this device.

- The minimum and maximum values for the propagation delay were removed; the typical value remains at 450 ps. The minimum and maximum values for the output channel-to-channel delay skew parameter were also removed, and a typical value of 50 ps was added.

- The parameter name of the serial output data jitter specification changed to "Serial output data total added random jitter" to reflect the type of jitter specified, and a condition of BER = 10<sup>-12</sup> was added. The typical value changed from 20 ps to 6 ps, and a maximum value of 14 ps was added. For the serial data output rise and fall time parameter, the minimum value of 50 ps was removed, a typical value of 45 ps was added, and the maximum value changed from 100 ps to 70 ps.

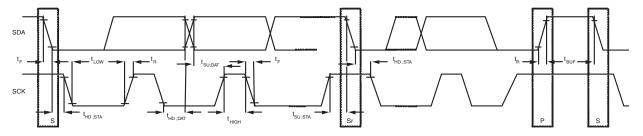

- For the two-wire serial interface AC specifications, a setup time of 0.6 µs minimum for the START condition was added. The setup time for the STOP condition parameter was removed, because it is not supported.

- The serial data input rise time and fall time and the serial data output duty cycle parameters for the high-speed outputs were removed.

- Information about the Software Reset register was missing in previous revisions of the datasheet. The information has been added.

- The bus load parameter for the two-wire interface was updated to differentiate between resistor and active pull-up devices; the maximum value for the resistive pull-up is 200 pF, and the maximum value for the active pull-up (3 mA maximum) is 400 pF.

### **Revision 2.1**

Revision 2.1 of this datasheet was published in November 2007. The following is a summary of the changes implemented in the datasheet:

- The initialization sequence was changed by adding a second operation, which is to write 06th to register 7Ath. This configures the addressing mode for bi-directional ports A through H. This reconfiguration also changes the numerical addressing associated with the input and output ports (matching the bi-directional port addressing for the device). This change was necessary to correct for a programming logic error.

- The data rate was corrected from 6 Gbps to 8.5 Gbps.

- The naming convention for the ports was modified to reflect that they are bidirectional ports. The following pins have been renamed:

E and EN (formally A0 and ANO)

F and FN (formally A1 and AN1)

G and GN (formally A2 and AN2)

H and HN (formally A3 and AN3)

A and AN (formally YO and YNO)

B and BN (formally Y1 and YN1)

C and CN (formally Y2 and YN2)

- D and DN (formally Y3 and YN3)

- In the last release of this datasheet, the pin numbers for the G and H (formerly A2 and A3) signals were inadvertently switched. In this datasheet release, the pin numbers were corrected: pin E6 is G, and pin F5 is H. In addition, the pin number for signal D was corrected to A5.

- Throughout this datasheet, references to the latched LOS condition were removed, because it is not supported.

- The power-up sequence was clarified. If the external controller uses 3.3 V logic, VDD should be powered up before VDDIO.

- Bit 4 of the Output Level register (individual address 22'h and global address 56'h)

was corrected from reserved to "terminate to VDDIO 0.7 V."

- Bit 2 of the Input State register (individual page address 11'h and global address 52'h) was corrected from "terminate to VDD" to reserved.

- The previous release of the datasheet incorrectly referenced the input port termination to  $V_{DD}$  0.8 V. It has been corrected to reference  $V_{DDIO}$  0.7 V.

- In the Global Register Map table, the bit description for bit 0 in the Interface Mode register was corrected to match the register bit description.

- In the DC specifications for the high-speed data inputs, the maximum value for the input common-mode voltage was corrected from  $V_{DD}$  to  $V_{DDIO}$  0.7 V. For the LVTTL and CMOS input signals, the maximum value for the input HIGH voltage parameter was corrected from  $V_{DD}$  + 0.6 V to  $V_{DD}$  + 0.7 V.

- For the input voltage swing, differential drive parameter, the minimum value was changed from 100 mV to 200 mV.

- In the AC specifications, the measurement conditions for the high-speed data serial data input and output rise and fall times were corrected.

- In the recommended operating conditions, the minimum and maximum values for the VDDIO power supply voltage were added.

- The 1.8 V power supply option was removed, because it is not supported.

- Design improvements resolved the CMOS I/O operation issue; the control pins SADDR, SDA, SCK, SMI, SMO, and VTSS[3:2] now have internal pull-down resistors.

- In the pin description for the VDDIO power supply, the voltage range was updated to include 2.5 V.

- In the Status State registers, the descriptions for bit 1 and bit 0 were corrected.

# **Revision 2.0**

Revision 2.0 of this datasheet was published in September 2006. This was the first publication of the document.

# 1 Product Overview

The VSC3304 is a low-cost, low-power asynchronous crosspoint switch capable of data rates up to 8.5 Gbps. The VSC3304 finds purpose not only as a switch, but also as a buffer that simplifies the design of high-speed signal paths by providing signal equalization at both inputs and outputs to reduce or reverse signal degradation due to transmission line effects.

The VSC3304 has a total of eight ports. All eight may be configured as either inputs or outputs without restriction. This provides the flexibility of using the device as a standard  $4 \times 4$  crosspoint, or anything between a 1:7 to a 7:1 multiplexer, as well as other combinations.

Featuring programmable input signal equalization and output pre-emphasis (each with multiple time constants), the VSC3304 is also ideal for countering signal degradation over a wide variety of transmission media types and lengths.

Typical power consumption for the device is 200 mW per active channel, and unused channels may be deactivated to save the power associated with those ports. Further power savings can be realized by setting the output level settings to the minimum effective value for a specific application.

The VSC3304 has a loss of signal (LOS) detector on every input port with programmable thresholds. The LOS status can be directed to either of two status registers. The LOS signal is also switched to each connected output monitored through the high-speed switching core. Out of band (OOB) signal forwarding can be enabled for each of the outputs, which causes the outputs to be squelched in response to an LOS detect at the corresponding input, thereby propagating an OOB envelope through the switch.

Programming of the VSC3304 is performed through a two-wire or a four-wire serial interface. The two-wire serial interface address can be hardwired using the three address pins or a proprietary two-wire serial interface that allows for address selection after power-up. Functions such as ResetB and Status states are accessible using the registers to ensure maximum flexibility.

# 1.1 Features

The following table lists the key aspects of the VSC3304 functionality and design along with the corresponding benefits to Vitesse customers.

#### **Table 1.** Features and Benefits

| Feature                                                               | Benefit                                                                                                                       |

|-----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| 8.5 Gbps operation                                                    | Supports latest high speed protocols                                                                                          |

| Flexible switching options: multicast, loopback, and snoop capability | Allows great flexibility in routing and fanning signals in distributed and centralized architectures                          |

| Two-wire serial bus                                                   | Simple programming interface                                                                                                  |

| High-speed four-wire serial programming interface                     | Allows complete reassignment of all switch connections in less than 14 µs, which is suitable for video switching applications |

| Asynchronous operation                                                | Data agnostic transfers allow each lane to run speed independent without an external reference clock                          |

| User-programmable input and output signal equalization                | Flexibility in correcting transmission line effects in a variety of media                                                     |

| Fully reconfigurable high-speed I/O ports                             | Optimizes signal routing and board design                                                                                     |

| LOS detection and forwarding                                          | Supports signal monitoring and OOB signal forwarding for SAS and SATA applications                                            |

| Optional output signal squelch on a per-channel basis                 | Supports OOB signal forwarding for SAS and SATA applications                                                                  |

# 1.2 Block Diagram

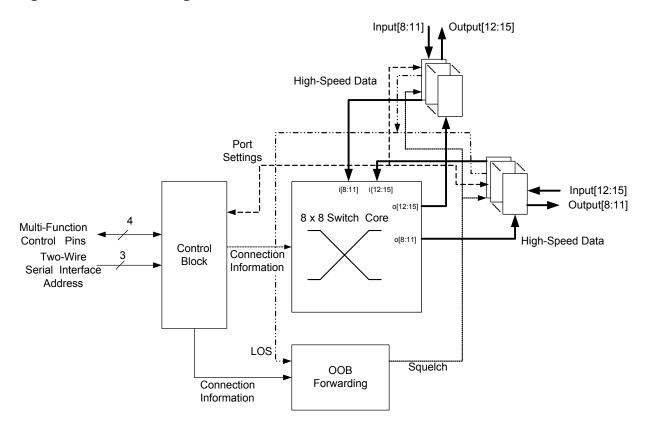

The following illustration shows the primary functional blocks of the VSC3304 device.

Figure 1. Block Diagram

# 1.3 Applications

Some of the applications for the VSC3304 device are:

- Wideband signal switching and clean-up

- Line driver or receiver

- Backplane signal fanout, driver, or receiver

- · Copper cable driver or receiver

- PCB signal enhancement

# 2 Functional Descriptions

This section provides descriptions of the functions and features of VSC3304.

### 2.1 Reset

The VSC3304 can be reset either by writing 1 to the Reset bit or by using the internal power-on reset circuit. The power-on reset circuit is linked to both the VDD and VDDIO supplies.

The reset state is released by energizing the VDD supply. The reset register bit is self-clearing. In general, the power-on reset circuit ensures that the VSC3304 powers up correctly. However, if any of the control pins are connected to a power supply other than VDD, either through a resistor or through an external controller, then the VDD supply should be energized before the other supply.

The minimum threshold for the power-on reset circuit is approximately 2.2 V. Therefore, it is important that there is sufficient decoupling on the circuit board to ensure that the VDD and the VDDIO supply voltage at the pins of the package does not drop below this value when multiple connection paths on the VSC3304 are energized simultaneously. Using the global programming registers can cause multiple paths to transition from an off state to an on state simultaneously.

### 2.2 Initialization

On reset, the VSC3304 is in low-power state. Initialization requires two consecutive register writes. The first required operation is to select the serial interface mode. Upon reset, the device monitors the pins required for the two-wire and four-wire serial interfaces for a properly formatted write in either mode. To select the two-wire serial interface, the first command must write the value 02'h to address 79'h in correct two-wire format. To select the four-wire interface, the first command must write the value 01'h to address 79'h in proper SPI format. For more information, see "Two-Wire Serial Interface," page 15 or "Four-Wire Serial Bus (Serial Peripheral Interface)," page 17.

Upon reset, all inputs, outputs, and bias generators are in an off state to reduce the power consumption. Before any connections can be activated, setting the appropriate registers bits energizes these circuits.

# 2.3 Page-Based Programming

The VSC3304 uses page-based register programming to configure the features and functions of the device. Pages are grouped according to function and each page typically has a maximum of 8 addresses but has a potential address space of 128 8-bit words. The register address within each page corresponds to the number of the input or output that it controls. A specific page is selected by programming the value for the desired page into the Current Page register at address 7F'h.

The Current Page register and all other registers that have an address of 50'h or higher are not linked to a specific page and can be programmed regardless of the value in the Current Page register (address 7F'h). These registers are used to set features and functions of the VSC3304 globally by either setting all 8 registers in an associated page

with a single programming step or by setting a configuration that affects the operation of the entire device. For more information about the registers and their functions, see "Registers," page 26.

### 2.4 Two-Wire Serial Interface

The VSC3304 supports a slave mode two-wire serial interface where an external master device controls the VSC3304 slave device. The two-wire serial interface operates in both standard mode (up to 100 kbps) and fast mode (up to 400 kbps) data transfer rates.

A master device generates a start condition <S> by transitioning SDA HIGH to LOW while SCK is HIGH. Data is then transferred on the SDA line with the most significant bit (MSB) first and the SCK line clocking each bit. Data transitions occur when the SCK is low and is valid (read) or stable (write) when on the HIGH to LOW transition of the SCK. Data transfers are acknowledged (ACK or <A>) by the receiving device (VSC3304 for data writes and the master device for data reads) by holding the SDA signal low while strobing SCK HIGH, then LOW. The master generates a stop condition <P> (terminates the data transfer) with a LOW to HIGH transition on the SDA signal while SCK is HIGH. For more information, see Figure 4, page 47.

**Serial Write** A serial write starts with the master sending a byte to the VSC3304. The first seven bits represent the serial interface address, and the eighth must be a 0 to indicate a write operation. The VSC3304 compares its serial interface address (set by the SADDR[5, 3:2] or the Serial Address register) to the one transmitted. An acknowledge is generated only if they match.

Without issuing a start or stop condition, the master then sends a second byte to the VSC3304. The VSC3304 interprets this byte as the register address. Finally, the master sends a third byte to the VSC3304. This is interpreted as the data for the register write. At this point, the write has taken effect.

The following is an example of the write sequence (assuming the serial interface address is set to 00'h):

One Byte Write: <S><00'h><A><Address><A><Data><A><P>

**Serial Read** A read cycle starts out similarly to the serial write, but immediately after the desired register address (the second byte) is sent, a stop condition is issued. The master then sends the serial interface address again but this time uses a 1 in the LSB to indicate a read operation. After the acknowledge cycle from the VSC3304, the master stops driving the SDA line. At this point, the VSC3304 outputs one bit at a time on the falling edge of SCK, transmitting the MSB first until eight bits are transmitted. After the eighth falling edge of the SCK, the VSC3304 releases control of the SDA bus and the master issues the clock for the acknowledge cycle. After the master issues the acknowledge cycle, the master issues a stop condition, which signals the end of the transmission.

The following is an example sequence (assuming the serial interface address is set to 00'h):

Read: <S><00'h><A><Address><A><P>

The VSC3304 two-wire serial interface supports a 7-bit slave address. This address may be set either of two ways. The first is to hardwire the appropriate SADDR[5, 3:2] pins

to VDD or VSS. Although the VSC3304 has a 7-bit chip address space, only three address pins are actually brought out of the package, limiting the hard-wired addressing to eight addresses. The accessible pins are labeled SADR5, SADR3, and SADR2. Of the remaining four bits, bit 0 is internally tied HIGH, bit 6 is tied LOW, bit 4 is tied to bit 5, and bit 1 is tied to bit 2. These are described in the following table. Note that all 7 bits must appear in the serial device address.

Table 2. Device Address vs. Address Pin State

| (SADR6) | SADR5 <sup>(1)</sup><br>(SADR4) | SADR3 <sup>(1)</sup> | SADR2 <sup>(1)</sup><br>(SADR1) | (SADRO) | CHP_ADDR in Binary | CHP_ADDR in Hex |

|---------|---------------------------------|----------------------|---------------------------------|---------|--------------------|-----------------|

| 0       | 0                               | 0                    | 0                               | 1       | 0000001            | 1′h             |

| 0       | 0                               | 0                    | 1                               | 1       | 0000111            | 7′h             |

| 0       | 0                               | 1                    | 0                               | 1       | 0001001            | 9′h             |

| 0       | 0                               | 1                    | 1                               | 1       | 0001111            | F'h             |

| 0       | 1                               | 0                    | 0                               | 1       | 0110001            | 31'h            |

| 0       | 1                               | 0                    | 1                               | 1       | 0110111            | 37′h            |

| 0       | 1                               | 1                    | 0                               | 1       | 0111001            | 39′h            |

| 0       | 1                               | 1                    | 1                               | 1       | 0111111            | 3F'h            |

|         | •                               | •                    | •                               | •       |                    |                 |

<sup>1.</sup> Only these three address bits are connected to external pins. The remaining four bits are either tied to fixed levels or to adjacent address pins as shown.

The second addressing method uses a proprietary interface that requires two additional signal wires (SMI and SMO) and permits the address to be programmed on initialization. On reset, the address of the VSC3304 is read from the SADDR[5, 3:2] pins. If no address is programmed into the Serial Address register, then the pin voltages define the permanent address for the device. When a value other than all zeros is programmed into the Serial Address register, then that new value overrides the value on the SADDR[5, 3:2] pins. The SMI pin must be held HIGH to program the Serial Address register.

The Serial Address register does not latch a programmed value unless the SMI pin is held HIGH concurrent with the programming instruction. Also, the MSB (bit 7) of the Serial Address register controls the state of the SMO pin. Therefore, by chaining the SMO of one VSC3304 to the SMI pin of the next, it is possible to change the address of up to 64 different devices connected to the same SCK and SDA lines even if they all initially have identical addresses. Writing an address to the first device with the SMI pin held HIGH changes the address of that device, but the remaining devices all have their SMI pins LOW, so they do not latch the address.

When the address is written to the first device, the state of the SMO can be set HIGH, which sets the SMI pin of the next device HIGH. Now the first device has a different address from the remaining devices, and the SMI pin of the second device is HIGH. The first device does not acknowledge the programming instruction to write to the Serial Address register, and only the second device latches the new address. This process is repeated until all of the devices on the serial bus are defined.

The first programming instruction to the VSC3304 is used to enable the two-wire serial interface. The programming instruction is in the standard format and sets the address 79'h to the value 02'h.

# 2.5 Four-Wire Serial Bus (Serial Peripheral Interface)

Accessing the VSC3304 registers by means of the SPI interface re-assigns the pins used in the two-wire serial interface as follows:

| SPI  | Two-Wire |

|------|----------|

| SSB  | SMI      |

| SCK  | SCK      |

| MOSI | SDA      |

| MISO | SMO      |

The four-wire serial bus, or serial peripheral interface (SPI), is designed for applications where higher data transfer rates are required. The four-wire interface has a maximum data transfer rate of 30 Mbps. Unlike the two-wire serial interface, chip selection is accomplished through an active LOW serial select signal, SSB(SMI). When the VSC3304 is reset, the VSC3304 is not in a dedicated serial interface mode. To place the VSC3304 in the four-wire SPI mode, the first command to the device must be to write the value 01'h to the register address 79'h. After this command, the MISO(SMO) pin acts as an output when SSB is LOW, and reverts to high impedance when SSB is HIGH. Prior to the initial command to select the four-wire SPI, the MISO pin will always be an active output.

When SSB is LOW, the VSC3304 responds as a slave device. Raising SSB at any time during a read or write terminates that transaction and resets the interface.

**SPI Write** A write sequence for the SPI interface of the VSC3304 is comprised of three consecutive 8-bit words. Each bit value applied to MOSI(SDA) is latched on the falling edge of SCK. The first word of the sequence indicates whether the command is a write or a read. For a write these first 8-bits are all zero. The next eight bits indicate which register address will be changed, and the last eight bits contain the value to be written to the selected register address. Both the address and data words are transmitted MSB first. SSB must be set LOW to initiate the write sequence and held LOW throughout the sequence. SSB can remain LOW for multiple write operations, but the entire three-byte sequence must be transmitted for each write. There is no sequential or burst mode for the SPI interface.

**SPI Read** The read sequence for the SPI interface of the VSC3304 requires 32 consecutive cycles of the SCK signal. The first eight bits of the MOSI signal are set to all ones to indicate that it is a read operation. The next eight bits set the register address from which data is to be read. During the third and fourth sets of eight bits, the MOSI signal can be of any value. The third set of eight clock cycles are used to allow the address value and the associated data to propagate between the register and the serial interface. The bits read from MISO during these clock cycles can be discarded. During the fourth and last eight clock cycles of the read sequence, the requested data is clocked out on the MISO pin on each rising edge of SCK. The address, data, and read data are all transmitted MSB first. The SSB pin must be set LOW to begin the sequence and held LOW throughout each sequence. SSB can remain LOW for multiple read operations, but the entire four-byte sequence must be followed for each read. There is no sequential mode for the SPI interface.

# 2.6 Crosspoint Connections

A complete connection through the VSC3304 requires that the inputs and outputs be properly energized and configured. This section provides the necessary steps to create a complete connection.

The first step is to program a connection through the switch core. The connection page is on page 00'h. Therefore, the first step is to set the current page in the Current Page register (7F'h = 00'h). Next, the value of the desired output port is the value that is used as the address in the connection programming instruction. The data value in the programming instruction is the number of the input port to be connected. The connection register also controls the on and off state of an output. When bit 4 is a 1, the output is disabled and the power used by that output is also turned off.

Consequently, when programming an input value to an output address, bit 4 must be set to 0 for the output to be enabled. The default state for an output is minimum swing and no pre-emphasis. For more information about configuring the output, see "Output Configuration," page 21.

The next step is to configure the selected input correctly. By default, all inputs are turned off to save power on start-up. To turn on the power for a given input, the correct page in the register map must be selected. The Input State Register is in page 11'h. Programming the Current Page register 7F'h to 11'h selects the Input State register page. Bit 1 of this register controls the on and off state of the input. On reset, this bit is set to 1 to turn off the input. To turn the input on, this bit must be set to 0. The selected input becomes the value for the address on this register page, and the value to be written for a basic connection is 0. For more information about configuring the input to optimize performance, see "Input Configuration," page 19.

# 2.7 Reconfigurable Ports

The standard pin designators identify eight re-programmable ports as inputs or outputs (designated as A, B, C, D, E, F, G, and H). Consequently, the VSC3304 can be set up in a variety of configurations from 1:7 to 7:1 inputs to outputs, depending on the application.

The output circuit sharing a port must be turned off before valid data can be received at the shared input. To turn off a reconfigurable output, write 1 in the bit 4 location of the address for the desired output on page 00'h of the memory map.

The following input and output pairs share the same physical ports:

- A is input 12 or output 8.

- B is input 13 or output 9.

- C is input 14 or output 10.

- D is input 15 or output 11.

- E is input 8 or output 12.

- F is input 9 or output 13.

- G is input 10 or output 14.

H is input 11 or output 15.

For instance, if using A as in input rather than an output, the first step is to write a 1 to bit 4 of address 08'h on page 00'h, turning off the A output function. Next, turn on input A by writing a 0 to bit 1 of address 0C'h on page 11'h. Finally, make a connection between A and the desired output by writing a 0C'h into the address of the desired output on page 00'h. For more information, see "Two-Wire Serial Interface," page 15.

# 2.8 Input Configuration

Each input has three sets of registers that are used to configure the various features associated with it. Each of the three sets of registers are on three separate pages of the memory map. Setting the Current Page register (address 7F'h) to 10'h, 11'h, or 12'h provides access to the three pages named Input ISE (Input Signal Equalization), Input State, or Input LOS respectively.

There are a total of eight input ports. Inputs 8 through 11 share physical ports with outputs 12 through 15, respectively. Inputs 12 through 15 share physical ports with outputs 8 through 11, respectively. Enabling the inputs requires additional current. Therefore to reduce the power consumption, it is recommended that any input sharing a port with an output be disabled (which is the default start-up state) before using that port as an output. For more information, see "Reconfigurable Ports," page 18 and "Input Port Disable," page 20.

# 2.8.1 Input Signal Equalization (ISE)

The input signal equalization on the VSC3304 helps to combat the intersymbol interference (ISI) of high-speed data as it passes through lossy media. This is accomplished by increasing the sensitivity of the receive circuits to the high frequency components of the data edges and works to reverse, in part or in whole, the degradation of signal quality due to propagation through the transmission media.

Discontinuities and losses in the transmission media act as low-pass filters and attenuate the high frequency components of a signal. The cut-off frequency and slope of the filter depend on the specifics of the discontinuities and the losses of the data path. Typically, discontinuities that are small in electrical terms, such as solder pads and connectors, have a high cutoff frequency. Lossy media, such as transmission lines or backplanes, have a lower cutoff frequency bandwidth. The electrical length of the transmission line or the size of a discontinuity affects the magnitude of the attenuation.

The VSC3304 provides flexibility in correcting for transmission losses by providing three independent ISE stages. Each stage has a different time constant (long, medium, and short) associated with it. These designations correspond to the size of the discontinuities described in the previous paragraph. The short time constant ISE is best suited to small discontinuities. The long time constant ISE is well-suited to reducing ISI over long lossy transmission lines. Each ISE stage can be de-activated or set to one of three levels, depending on the magnitude of the signal filtering that occurred during propagation. The bits that control the ISE settings are in the input ISE register (address 10'h). For more information about the registers, see "Input ISE," page 28.

# 2.8.2 Input Port Termination

Each input is terminated to a 100  $\Omega$  differential impedance. The VSC3304 offers eight bidirectional high-speed ports that can be configured as either inputs or outputs. The termination for these ports is shared for both inputs and outputs. In this case, the input is terminated to a supply of  $V_{DDIO}-0.7$  V. Connecting the input port termination to  $V_{DDIO}-0.7$  V on a bidirectional port is set by writing a 1 into bit 4 of the output associated with the desired input. The mapping is as follows:

- To connect the termination for input E to V<sub>DDIO</sub> 0.7 V, write a 1 into bit 4 of register address OC'h on page 22'h.

- To connect the termination for input F to V<sub>DDIO</sub> 0.7 V, write a 1 into bit 4 of register address 0D'h on page 22'h.

- To connect the termination for input G to V<sub>DDIO</sub> 0.7 V, write a 1 into bit 4 of register address 0E'h on page 22'h.

- To connect the termination for input H to V<sub>DDIO</sub> 0.7 V, write a 1 into bit 4 of register address 0F'h on page 22'h.

- To connect the termination for input A to V<sub>DDIO</sub> 0.7 V, write a 1 into bit 4 of register address 08'h on page 22'h.

- To connect the termination for input B to  $V_{DDIO}$  0.7 V, write a 1 into bit 4 of register address 09'h on page 22'h.

- To connect the termination for input C to V<sub>DDIO</sub> 0.7 V, write a 1 into bit 4 of register address 0A'h on page 22'h.

- To connect the termination for input D to  $V_{DDIO}$  0.7 V, write a 1 into bit 4 of register address 0B'h on page 22'h.

For more information, see "Output Level," page 31.

# 2.8.3 Input Port Disable

Each input port must be enabled before it forwards received data to the switching core. The on and off control bit for the inputs is located on page 11'h. Each address on this page refers to the number of the corresponding input. When bit 1 is set to 1, then the input port is disabled and the power associated with that port is conserved. When the part is reset, this bit is set to a 1 by default. Therefore, any inputs that are used must be enabled before use. For more information about these registers, see "Input State," page 29.

# 2.8.4 Input Signal Invert

The VSC3304 incorporates the ability to invert the signal at the input to simplify the design of high-speed boards and interconnect.

Bit 0 of the registers on the input state page (11'h) selects whether the input is inverted or normal. Each register address on the input state page corresponds to the like numbered input. For more information about the register settings, see "Input State," page 29.

### 2.8.5 Input LOS

Each input has an LOS (loss of signal) detector associated with it that sets a bit HIGH whenever the signal level drops below a selected value. Although there is a time component to the detection, the primary metric for asserting the LOS signal is the signal amplitude. This amplitude is selectable in the registers on the input LOS page (12'h). For more information about the amplitude settings, see "Input LOS," page 29.

The LOS signal is asserted upon a loss of signal or deasserted when a signal is present for more than 2 ns from when the signal level again exceeds the threshold.

This signal can be read from the registers on the channel status page.

This signal is also forwarded to any output that is connected to the corresponding input and can be used to squelch a transmitted signal when the connected input goes into an LOS state.

# 2.9 Output Configuration

Each output has four sets of registers that are used to configure the various features associated with the selected output. Each of the four registers is on a separate page of the memory map. Setting the Current Page register (address 7F'h) to 20'h, 21'h, 22'h, or 23'h provides access to the four pages named Output Pre Long, Output Pre Short, Output Level, or Output State, respectively.

The sum of all the levels for the amplitude and the long and short pre-emphasis must not exceed a total of 15. For example, if the output level is set to 8 and the short pre-emphasis amplitude is set to 5, then the amplitude setting for the long pre-emphasis should not exceed 2. If only one of the pre-emphasis time constants is required, then the sum of 15 need only be divided between the output level and the pre-emphasis setting of the selected time constant. If no pre-emphasis is used, then there is no restriction on the output amplitude. To maximize flexibility in configuring the output equalization at low output amplitude settings, there are equalization settings that are excessive at high output amplitudes. It is possible to select the large equalization amplitudes even with the higher output levels, but these stress the limits of the output driver. The result is a deformed output waveform rather than one that has been properly equalized, accompanied by excessive power dissipation.

There are a total of eight output ports. Outputs 8 through 11 share physical ports with inputs 12 through 15, respectively. Outputs 12 through 15 share physical ports with inputs 8 through 11, respectively. Enabling the inputs requires additional current. Therefore to reduce the power consumption, it is recommended that any input sharing a port with an output be disabled (which is the default start-up state) before using that port as an output.

The output ports must be configured in such a way as to not exceed power limits of the device. For information about the power requirements, see "Power Supply Requirements," page 44.

# 2.9.1 Output Pre-Emphasis

The output pre-emphasis function of the VSC3304 helps to combat the intersymbol interference (ISI) of high-speed data as it passes through lossy media. This is accomplished by shaping the output waveform to boost the magnitude of those

frequency components of the transmitted signal that are most susceptible to attenuation as it propagates through the transmission media.

Discontinuities and losses in the transmission media act as low-pass filters and attenuate the high-frequency components of a signal. The cutoff frequency and slope of the filter depend on the specifics of the discontinuities and the losses as the signal propagates through the discontinuities or media. Typically, discontinuities that are small in electrical terms, such as solder pads and connectors, have a high cutoff frequency. Lossy media, such as transmission lines or backplanes, have a lower cutoff frequency bandwidth. The electrical length of the transmission line or the size of a discontinuity affects the magnitude of the attenuation.

The VSC3304 provides flexibility in correcting for transmission losses with two independent pre-emphasis stages that are additive. Each stage has a different time constant (long and short) associated with it. The short time constant pre-emphasis is best suited to small discontinuities and electrically short transmission lines. The long time constant pre-emphasis is well suited to reducing ISI over long lossy transmission lines.

Each pre-emphasis stage can be deactivated or set to one of 15 levels, depending on the magnitude of the signal filtering that occurred during propagation. Additionally, each of the pre-emphasis stages permits the bandwidth of the boosted signal to be adjusted. Both the long and short pre-emphasis stages have eight bandwidth settings. The bandwidth settings adjust the lower limit of the signal boost and have a single pole roll-off. The uppermost frequency of the signal boost is limited by the slew rate of the output amplifier.

The bits that control the pre-emphasis settings are in the Output Pre Long and Output Pre Short registers (address 20'h and 21'h). For more information about these settings and registers, see "Output Pre Long," page 30 and "Output Pre Short," page 30.

# 2.9.2 Output Power Level

The VSC3304 provides a selection of 13 power levels that enable compliance with most popular transmission standards. The output level is selectable using bits [3:0] in the registers on the output level page (address 22'h). The register address within the page is used to identify the number of the output that it controls.

The output ports must be configured in such a way as to not exceed power limits of the device. For information about the power requirements, see "Power Supply Requirements," page 44.

The uppermost level setting is only available when the  $V_{DDIO}$  supply is connected to a 3.3 V supply. All other levels are available with a 2.5 V supply connected to  $V_{DDIO}$ .

For more information about the specific output levels and the values used to select them, see "Output Level," page 31.

# 2.9.3 Output Signal Suppression and Inversion

The VSC3304 can be configured to selectively invert any output to simplify the design of high-speed boards and interconnects.

It is also possible to suppress an output signal to reduce signal noise in a system. When the output signal is suppressed, the true and complement values are driven to the common mode value. This signal level is stable and maintains a DC level that is within  $\pm 50$  mV.

Both of these functions are controlled by bits [4:1] of the registers on the output state page 23'h. For more information about the bit values that set the state of the output for normal, inverted, or suppressed operations, see "Output State," page 32.

# 2.9.4 Out of Band Signal Forwarding

As mentioned previously, VSC3304 has the ability to suppress the output signal in response to an LOS assertion at the connected input. For more information, see "Input LOS," page 21. The purpose of this feature is to propagate out of band (OOB) signaling information through the VSC3304 and is compatible with SAS and SATA operation. For information about SAS and SATA compatibility, see "Design Considerations," page 56.

The VSC3304 features an OOB forwarding switch core that duplicates the connections in the high-speed switch core. This core is used to switch the LOS detect signal. With bit 0 of an Output State Register set to 1, the selected output is suppressed whenever the connected input asserts an LOS condition. This overrides the current output state for as long as the LOS from the input remains asserted. After the LOS condition is removed and the LOS is deasserted, the output assumes whatever state is set in bits [4:1] for that output.

It takes approximately 4 ns for the LOS condition to be propagated from the input to the output.

For more information about controlling this function, see "Output State," page 32.

# 2.10 Status Bits

The VSC3304 provides two status bits (STAT0 and STAT1) that permit monitoring of LOS conditions of one or more selected inputs. LOS signals from one or more of the inputs can be OR'ed together to generate the final state of either of these status bits.

There is a separate page for both STATO and STAT1. The registers on the Status 0 page (80'h) control STATO, and the registers on the Status 1 page (81'h) control STAT1. Each address on each page refers to the input with the same number. Bit 0 connects the LOS condition for the selected input to the status bit associated with the page that is being programmed. For more information about the term LOS, see "Channel Status," page 24.

For example, when the value 01'h is programmed to address 08'h and the value 01'h is programmed to address 09'h (both located on page 80'h), the value of STATO bit 1 is equal to 1 whenever input 8 or input 9 detects an LOS condition. When neither input 8 nor input 9 detects an LOS position, then STATO bit 1 is equal to 0.

The state of STATO and STAT1 can be monitored using the programming interface. The Status register is located on the Channel Status page (F0'h) at register address 10'h. The two LSBs of this register show the current state of STATO and STAT1. Bit 0 reflects the state of STATO, and bit 1 reflects the state of STAT1.

This provides a convenient and efficient way of polling the VSC3304 for the LOS conditions of multiple inputs by using a single register read. The LOS condition of each of the inputs can be assigned to one STAT bit or divided between STAT0 and STAT1 using the registers on the Status 0 and Status 1 pages. When the value is nonzero, then more detailed polling of each of the registers on the Channel Status page reveals which input exhibited the LOS condition. If the LOS conditions of the inputs are split among STAT0 and STAT1, fewer reads are required to locate the input with the LOS condition.

For more information about these registers, see "Status State," page 34. For more information about STATO and STAT1 in the registers, see "Status O Configuration," page 33 and "Status 1 Configuration," page 33.

### 2.11 Channel Status

The VSC3304 has a register associated with each input that reflects its LOS status. These registers are located on the channel status page (address F0'h) and the address of each register corresponds to the number value of the input that it represents.

Bit 0 is described as the LOS bit. This is the bit that reflects the current LOS state for the input as identified by the address that is read. For more information about these registers, see "Channel Status," page 32.

# 2.12 Global Programming

The VSC3304 provides the convenience of Global Programming registers to reduce the number of instructions required to initialize the device. A global programming register is associated with each page of registers with the exception of the one read-only page (F0'h) that contains the Channel Status and Pin Status registers. A single programming instruction to one of the global programming registers copies the same value to all the registers on the associated page. The global programming registers are assigned to each page as shown in the following table.

#### Table 3. Global Registers and Associated Pages

| Global Register Name    | Address      | Page of Registers | Address |

|-------------------------|--------------|-------------------|---------|

| Global Input ISE        | 51'h         | Input ISE         | 10'h    |

| Global Input State      | 52'h         | Input State       | 11'h    |

| Global Input LOS        | 53′h         | Input LOS         | 12'h    |

| Global Output Pre Long  | 54' <b>h</b> | Output Pre Long   | 20'h    |

| Global Output Pre Short | 55'h         | Output Pre Short  | 21'h    |

| Global Output Level     | 56'h         | Output Level      | 22'h    |

| Global Output State     | 57′h         | Output State      | 23'h    |

| Global Status 0         | 58' <b>h</b> | Status 0          | 80'h    |

| Global Status 1         | 59'h         | Status 1          | 81'h    |

Caution should be exercised when using the global programming registers to change values on input state pages. Because this programs all 8 inputs simultaneously, it either turns all of them on or all of them off as well. This may cause a connection to be

broken, or may cause data corruption if an input is turned on for a bidirectional port currently being used as an output.

Turning on additional inputs does not affect the signal quality of the output on a bidirectional port, but it does use additional power. Turning on all inputs simultaneously also generates an instantaneous current spike. If there is insufficient decoupling capacitance connected to the package pins, the instantaneous power supply voltage may drop below the minimum level required to trip the device power-on reset that would change the device configuration.

# 3 Registers

This section contains information about the software interface. The purpose of this section is to provide information about the programming interface, register maps, register descriptions, and register tables.

# 3.1 Individual Register Map

This section provides a register map containing summary descriptions for the individual registers. For more information about setting the individual registers, see "Individual Registers," page 28.

Figure 2. Register Map for the Individual Registers

|      | Address      | Register            |                         |           |                                 |                                             |                                        |            |                          |                             |

|------|--------------|---------------------|-------------------------|-----------|---------------------------------|---------------------------------------------|----------------------------------------|------------|--------------------------|-----------------------------|

| Page | Range        | Name                | Bit 7                   | Bit 6     | Bit 5                           | Bit 4                                       | Bit 3                                  | Bit 2      | Bit 1                    | Bit 0                       |

| 00′h | 08'h to 0F'h | Connection          | Reserved -              | read only |                                 | Output off                                  | Input to o                             | connect (0 | to 7)                    |                             |

| 10′h | 08'h to 0F'h | Input ISE           | Reserved -              | read only | ISE - Short<br>constant         | t time                                      | ISE - me<br>constant                   | dium time  | ISE - Ion<br>constant    | g time                      |

| 11′h | 08'h to 0F'h | Input State         | Reserved -              | read only | •                               | Reserved -                                  | do not pro                             | gram       | Input off                | Invert input                |

| 12′h | 08'h to 0F'h | Input LOS           | Reserved -              | read only |                                 | •                                           |                                        | LOS three  | shold                    | •                           |

| 20'h | 08'h to 0F'h | Output<br>Pre Long  | Reserved -<br>read only | Long time | e constant p                    | re-emphasis                                 | level                                  |            | e constant<br>nasis deca |                             |

| 21′h | 08'h to 0F'h | Output<br>Pre Short | Reserved -<br>read only | Short tim | e constant p                    | ore-emphasis                                | Short time constant pre-emphasis decay |            | -                        |                             |

| 22'h | 08'h to 0F'h | Output<br>Level     | Reserved -              | read only | Reserved -<br>do not<br>program | Terminate<br>to VDDIO –<br>0.7 V<br>(Input) |                                        | ower level |                          |                             |

| 23′h | 08'h to 0F'h | Output<br>State     | Reserved -              | read only |                                 | Output Ope                                  | ration mod                             | de         |                          | Enable<br>LOS<br>forwarding |

| 80'h | 08'h to 0F'h | Status Pin 0        | Reserved -              | read only |                                 | •                                           |                                        |            |                          | LOS                         |

| 81'h | 08'h to 0F'h | Status Pin 1        | Reserved -              | read only |                                 |                                             |                                        |            |                          | LOS                         |

| A0'h | 08'h to 0F'h | Reserved            | Reserved -              | do not pr | ogram                           |                                             |                                        |            |                          |                             |

| F0′h | 08'h to 0F'h | Channel<br>Status   | Reserved -              | read only |                                 |                                             |                                        |            |                          | LOS                         |

| F0′h | 10'h         | Status<br>State     | Reserved -              | read only |                                 |                                             |                                        |            | STAT1                    | STAT0                       |

| FF'h | 00'h         | Reserved            | Reserved -              | read only |                                 |                                             |                                        |            |                          | -                           |

# 3.2 Global Register Map

This section provides a register map containing summary descriptions for the global registers. For information about setting the global registers, see "Global Registers," page 35.

Figure 3. Register Map for Global Registers

| Address | Register<br>Name           | Bit 7                                                   | Bit 6                     | Bit 5                           | Bit 4                             | Bit 3              | Bit 2                  | Bit 1               | Bit 0        |  |

|---------|----------------------------|---------------------------------------------------------|---------------------------|---------------------------------|-----------------------------------|--------------------|------------------------|---------------------|--------------|--|

| 50'h    | Reserved                   | Reserved -                                              | do not pro                | gram                            |                                   |                    | <u> </u>               |                     |              |  |

| 51'h    | Global Input<br>ISE        | Reserved -                                              | read only                 | ISE - shor constant             | t time                            |                    |                        | ISE - long constant | -            |  |

| 52'h    | Global Input<br>State      | Reserved -                                              | read only                 |                                 | Reserved                          | - do not pi        | rogram                 | Input off           | Invert input |  |

| 53'h    | Global Input<br>LOS        | Reserved -                                              | read only                 |                                 |                                   |                    | LOS thresh             | old                 |              |  |

| 54'h    | Global Output<br>Pre Long  | Reserved -<br>read only                                 | Long time                 | constant pr                     | e-emphasis                        | s level            | Long time of pre-empha |                     |              |  |

| 55'h    | Global Output<br>Pre Short | Reserved -<br>read only                                 | Short time                | constant p                      | re-emphas                         | is level           | Short time decay       | constant pr         | e-emphasis   |  |

| 56'h    | Global Output<br>Level     | Reserved -                                              | read only                 | Reserved<br>– do not<br>program | Terminate inputs to VDDIO – 0.7 V | VDDIO –            |                        |                     |              |  |

| 57'h    | Global Output<br>State     | Reserved - read only Output operation mode              |                           |                                 |                                   |                    | Enable LOS forwarding  |                     |              |  |

| 58'h    | Global<br>Status 0 Pin     | Reserved -                                              | Reserved - read only      |                                 |                                   |                    |                        |                     | LOS          |  |

| 59'h    | Global<br>Status 1 Pin     | Reserved -                                              | Reserved - read only      |                                 |                                   |                    |                        |                     | LOS          |  |

| 74'h    | Reserved                   | Reserved -                                              | do not pro                | gram                            |                                   |                    |                        |                     | •            |  |

| 75'h    | Reserved                   | Reserved -                                              | do not pro                | gram                            |                                   |                    |                        |                     |              |  |

| 78'h    | Serial Address             | SMO value                                               | Serial por                | t address                       |                                   |                    |                        |                     |              |  |

| 79'h    | Interface<br>Mode          | Reserved - read only  Reserved - Two-wir do not program |                           |                                 |                                   | Two-wire<br>serial | Four-wire<br>serial    |                     |              |  |

| 7A'h    | Initial Setup              | Reserved - do not program RESET Address range setting   |                           |                                 |                                   | •                  |                        |                     |              |  |

| 7B'h    | Reserved                   | Reserved -                                              | Reserved - do not program |                                 |                                   |                    |                        |                     |              |  |

| 7C'h    | Reserved                   | Reserved - do not program                               |                           |                                 |                                   |                    |                        |                     |              |  |

| 7D'h    | Reserved                   | Reserved - do not program                               |                           |                                 |                                   |                    |                        |                     |              |  |

| 7E'h    | Reserved                   | Reserved -                                              | Reserved - do not program |                                 |                                   |                    |                        |                     |              |  |

| 7F'h    | Current Page               | Current pa                                              | ge address                | i                               |                                   |                    |                        |                     |              |  |

# 3.3 Individual Registers

This section contains information about the individual registers.

### 3.3.1 Connection

The settings in these registers make connections and enable outputs.

Register name: Connection

Page address: 00'h

Register address: 08'h - 0F'h

Register type: R/W

#### Table 4. Connection

| Bit | Bit Label       | Description                                           | Access | Reset |

|-----|-----------------|-------------------------------------------------------|--------|-------|

| 7:5 | Reserved        | Reserved - Read only                                  | R      | 000   |

| 4   | Turn off output | 0 = Output enabled<br>1 = Output off                  | R/W    | 1     |

| 3:0 | Input number    | Number of the input to connect to the selected output | R/W    | 0000  |

# 3.3.2 Input ISE

This register configures the input signal equalization for the selected input.

Register name: Input ISE

Page address: 10'h

Register address: 08'h - 0F'h

Register type: R/W

### Table 5. Input ISE

| Bit | Bit Label                     | Description                                               | Access | Reset |

|-----|-------------------------------|-----------------------------------------------------------|--------|-------|

| 7:6 | Reserved                      | Reserved - Read only                                      | R      | 00    |

| 5:4 | ISE – short time constant     | 00 = Off<br>01 = Minimum<br>10 = Moderate<br>11 = Maximum | R/W    | 00    |

| 3:2 | ISE – medium time<br>constant | 00 = Off<br>01 = Minimum<br>10 = Moderate<br>11 = Maximum | R/W    | 00    |

| 1:0 | ISE – long time<br>constant   | 00 = Off<br>01 = Minimum<br>10 = Moderate<br>11 = Maximum | R/W    | 00    |

# 3.3.3 Input State

This register defines the input enable, polarity, and terminations settings for the selected input.

Register name: Input State

Page address: 11'h

Register address: 08'h - 0F'h

Register type: R/W

### Table 6. Input State

| Bit | Bit Label              | Description                | Access | Reset |

|-----|------------------------|----------------------------|--------|-------|

| 7:5 | Reserved               | Reserved - Read only       | R      | 000   |

| 4:2 | Reserved               | Reserved - Do not program  | R/W    | 001   |

| 1   | Input power off        | 0 = On<br>1 = Off          | R/W    | 1     |

| 0   | Invert signal at input | 0 = Normal<br>1 = Inverted | R/W    | 0     |

# 3.3.4 Input LOS

This register configures the input LOS threshold value for the selected input.

Register name: Input LOS

Page address: 12'h

Register address: 08'h - 0F'h

Register type: R/W

### Table 7. Input LOS

| Bit | Bit Label                                                           | Description                                                                                                                  | Access | Reset |

|-----|---------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|--------|-------|

| 7:3 | Reserved                                                            | Reserved - Read only                                                                                                         | R      | 00000 |

| 2:0 | LOS threshold<br>settings<br>(peak-to-peak<br>differential voltage) | 111 = Unused<br>110 = Unused<br>101 = Unused<br>100 = Unused<br>011 = Unused<br>010 = 400 mV<br>001 = 200 mV<br>000 = Unused | R/W    | 100   |

# 3.3.5 Output Pre Long

This register sets the long time constant pre-emphasis for selected output.

Register name: Output Pre Long

Page address: 20'h

Register address: 08'h - 0F'h

Register type: R/W

### **Table 8.** Output Pre Long

| Bit | Bit Label          | Description                                                                          | Access | Reset |

|-----|--------------------|--------------------------------------------------------------------------------------|--------|-------|

| 7   | Reserved           | Reserved - Read only                                                                 | R      | 0     |