# Spartan-3A/3AN FPGA Starter Kit Board User Guide

UG334 (v1.1) June 19, 2008

Xilinx is disclosing this Document and Intellectual Property (hereinafter "the Design") to you for use in the development of designs to operate on, or interface with Xilinx FPGAs. Except as stated herein, none of the Design may be copied, reproduced, distributed, republished, downloaded, displayed, posted, or transmitted in any form or by any means including, but not limited to, electronic, mechanical, photocopying, recording, or otherwise, without the prior written consent of Xilinx. Any unauthorized use of the Design may violate copyright laws, trademark laws, the laws of privacy and publicity, and communications regulations and statutes.

Xilinx does not assume any liability arising out of the application or use of the Design; nor does Xilinx convey any license under its patents, copyrights, or any rights of others. You are responsible for obtaining any rights you may require for your use or implementation of the Design. Xilinx reserves the right to make changes, at any time, to the Design as deemed desirable in the sole discretion of Xilinx. Xilinx assumes no obligation to correct any errors contained herein or to advise you of any correction if such be made. Xilinx will not assume any liability for the accuracy or correctness of any engineering or technical support or assistance provided to you in connection with the Design.

THE DESIGN IS PROVIDED "AS IS" WITH ALL FAULTS, AND THE ENTIRE RISK AS TO ITS FUNCTION AND IMPLEMENTATION IS WITH YOU. YOU ACKNOWLEDGE AND AGREE THAT YOU HAVE NOT RELIED ON ANY ORAL OR WRITTEN INFORMATION OR ADVICE, WHETHER GIVEN BY XILINX, OR ITS AGENTS OR EMPLOYEES. XILINX MAKES NO OTHER WARRANTIES, WHETHER EXPRESS, IMPLIED, OR STATUTORY, REGARDING THE DESIGN, INCLUDING ANY WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, TITLE, AND NONINFRINGEMENT OF THIRD-PARTY RIGHTS.

IN NO EVENT WILL XILINX BE LIABLE FOR ANY CONSEQUENTIAL, INDIRECT, EXEMPLARY, SPECIAL, OR INCIDENTAL DAMAGES, INCLUDING ANY LOST DATA AND LOST PROFITS, ARISING FROM OR RELATING TO YOUR USE OF THE DESIGN, EVEN IF YOU HAVE BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. THE TOTAL CUMULATIVE LIABILITY OF XILINX IN CONNECTION WITH YOUR USE OF THE DESIGN, WHETHER IN CONTRACT OR TORT OR OTHERWISE, WILL IN NO EVENT EXCEED THE AMOUNT OF FEES PAID BY YOU TO XILINX HEREUNDER FOR USE OF THE DESIGN. YOU ACKNOWLEDGE THAT THE FEES, IF ANY, REFLECT THE ALLOCATION OF RISK SET FORTH IN THIS AGREEMENT AND THAT XILINX WOULD NOT MAKE AVAILABLE THE DESIGN TO YOU WITHOUT THESE LIMITATIONS OF LIABILITY.

The Design is not designed or intended for use in the development of on-line control equipment in hazardous environments requiring fail-safe controls, such as in the operation of nuclear facilities, aircraft navigation or communications systems, air traffic control, life support, or weapons systems ("High-Risk Applications"). Xilinx specifically disclaims any express or implied warranties of fitness for such High-Risk Applications. You represent that use of the Design in such High-Risk Applications is fully at your risk.

© 2007-2008 Xilinx, Inc. All rights reserved. XILINX, the Xilinx logo, and other designated brands included herein are trademarks of Xilinx, Inc. PCI Express is a registered trademark of PCI-SIG. All other trademarks are the property of their respective owners.

# **Revision History**

The following table shows the revision history for this document.

| Date     | Version | Revision                                                                                                                                                                                                                        |  |

|----------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 05/28/07 | 1.0     | Initial Xilinx release.                                                                                                                                                                                                         |  |

| 06/19/08 | 1.1     | Added note that PS/2 port I/Os should always be set to LVCMOS33 with the PULLUP attribute set true when used. Updated UCF examples to match reference designs. Added recommendation for 1 MHz BPI configuration. Updated links. |  |

# Table of Contents

| Preface: About This Guide                                                                                                                      |                      |

|------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| Acknowledgments                                                                                                                                | 10                   |

| Guide Contents                                                                                                                                 | 10                   |

| Additional Resources                                                                                                                           |                      |

| Chapter 1: Introduction and Overview                                                                                                           |                      |

| Getting Started                                                                                                                                | 13                   |

| Operating the Default Demonstration Design                                                                                                     |                      |

| VGA Display                                                                                                                                    |                      |

| Rotary Knob/Push-Button Menu System                                                                                                            |                      |

| Select MultiBoot Configuration Image                                                                                                           |                      |

| Scroll or Rotate Graphic                                                                                                                       |                      |

| Scroll or Scale Graphic                                                                                                                        |                      |

| LCD Screen Control Option                                                                                                                      |                      |

| Power-Saving Suspend Mode                                                                                                                      |                      |

| RS-232 Serial Port Control Option                                                                                                              |                      |

| Key Components and Features                                                                                                                    | 19                   |

| Design Trade-Offs                                                                                                                              | 21                   |

| Configuration Methods Galore!                                                                                                                  | 21                   |

| Voltages for all Applications                                                                                                                  |                      |

| Spartan-3A/3AN FPGA Starter Kit Design Examples                                                                                                | 21                   |

| Choose a Spartan-3 Generation Starter Kit Board for your Needs                                                                                 |                      |

| Spartan-3A/3AN FPGA Features and Embedded Processing Functions                                                                                 |                      |

| Other Spartan-3 Generation Development Boards                                                                                                  | 23                   |

| Spartan-3A and Spartan-3AN FPGAs                                                                                                               | 23                   |

| Related Resources                                                                                                                              | 24                   |

|                                                                                                                                                |                      |

| Chapter 2: Switches, Buttons, and Rotary Knob                                                                                                  |                      |

| Slide Switches                                                                                                                                 |                      |

| Locations and Labels                                                                                                                           |                      |

| Operation                                                                                                                                      |                      |

| UCF Location Constraints                                                                                                                       |                      |

| SUSPEND Switch                                                                                                                                 |                      |

| Push-Button Switches                                                                                                                           |                      |

| Locations and Labels                                                                                                                           |                      |

|                                                                                                                                                |                      |

|                                                                                                                                                |                      |

|                                                                                                                                                |                      |

| · · · · · · · · · · · · · · · · · · ·                                                                                                          |                      |

|                                                                                                                                                |                      |

|                                                                                                                                                |                      |

| Operation. PROG_B Push-Button Switch. UCF Location Constraints.  Rotary Push-Button Switch  Locations and Labels Operation. Push-Button Switch | 28<br>28<br>28<br>28 |

| 2              | y Shaft Encoder                           |    |

|----------------|-------------------------------------------|----|

| UCF Locat      | tion Constraints                          | 30 |

| Discrete LEDs  | S                                         | 30 |

| Locations a    | and Labels                                | 30 |

| <u> </u>       | l                                         |    |

|                | tion Constraints                          |    |

| ±              | crete LEDs                                |    |

|                | LED                                       |    |

| <del>_</del>   | ED                                        |    |

| UCF Locat      | tion Constraints                          | 32 |

| Chapter 3: Clo | ck Sources                                |    |

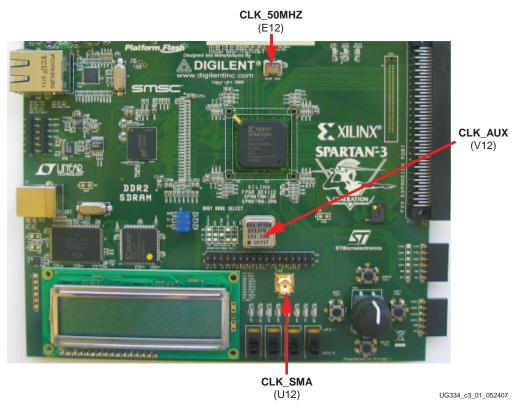

| Overview       |                                           | 33 |

| Clock Connec   | ctions                                    | 34 |

|                | Board Oscillator                          |    |

|                |                                           |    |

| •              | ock Oscillator Socket                     |    |

|                | nput or Output Connector                  |    |

|                | ints                                      |    |

|                |                                           |    |

|                | iod Constraints                           |    |

| Related Resou  | urces                                     | 35 |

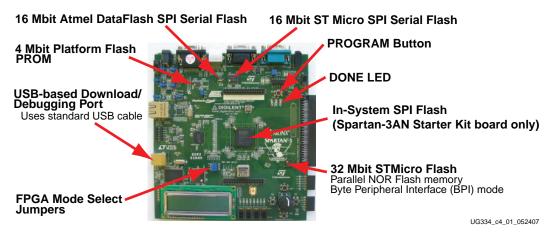

| Configuration  | GA Configuration Options  n Mode Jumpers  |    |

|                | m Flash Configuration PROM(s)             |    |

|                | Button Switch                             |    |

|                | ED                                        |    |

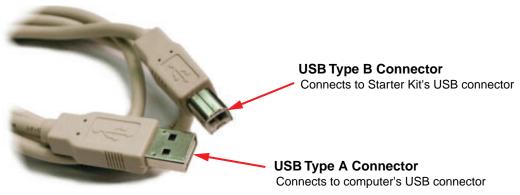

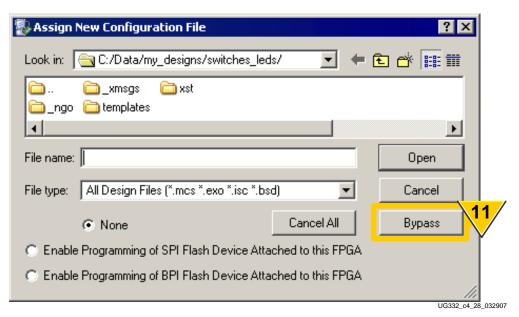

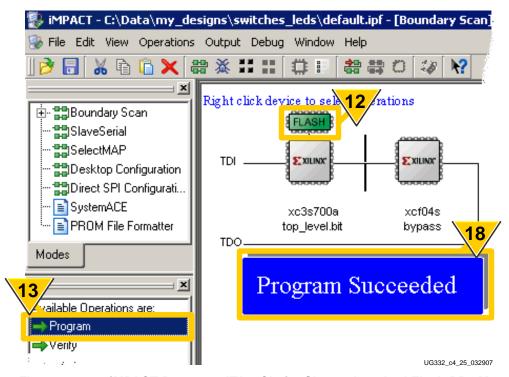

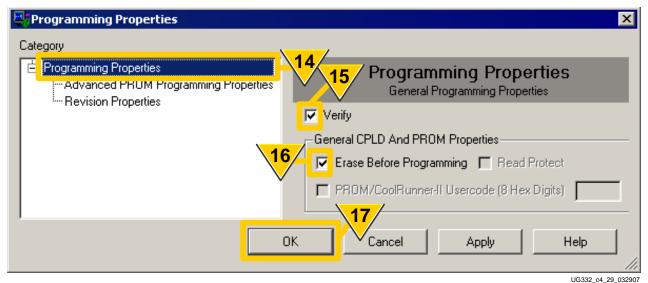

| Programming    | g the FPGA or Platform Flash PROM via USB | 41 |

|                | g the USB Cable                           |    |

| Platform F     | Flash Programming Example                 | 42 |

| -              | aracter LCD Screen                        | 40 |

|                |                                           |    |

|                | D Interface Signals                       |    |

| Voltage Comp   | patibility                                | 44 |

| UCF Location   | n Constraints                             | 44 |

| LCD Controll   | ler                                       | 45 |

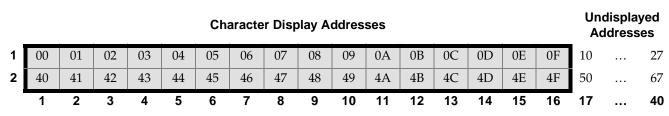

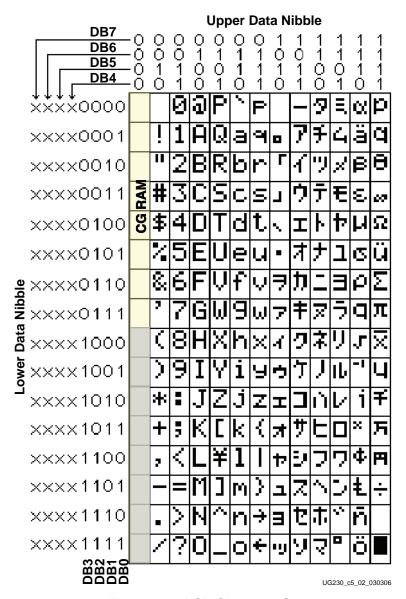

|                | Мар                                       |    |

|                | AM                                        |    |

|                | OM                                        |    |

|                | AM                                        |    |

|                | led                                       |    |

|                | Display                                   |    |

|                | n Cursor Home                             |    |

|                | Mode Set                                  |    |

|                | ay On/Off                                 |    |

|                |                                           |    |

|          | Cursor and Display Shift                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                            |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

|          | Function Set                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                            |

|          | Set CG RAM Address                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                            |

|          | Set DD RAM Address                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                            |

|          | Read Busy Flag and Address                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                            |

|          | Write Data to CG RAM or DD RAM                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                            |

|          | Read Data from CG RAM or DD RAM                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                            |

|          | Operation                                                                                                                                                                                                                                                                                                                                                                                                                                      | 52                                                                         |

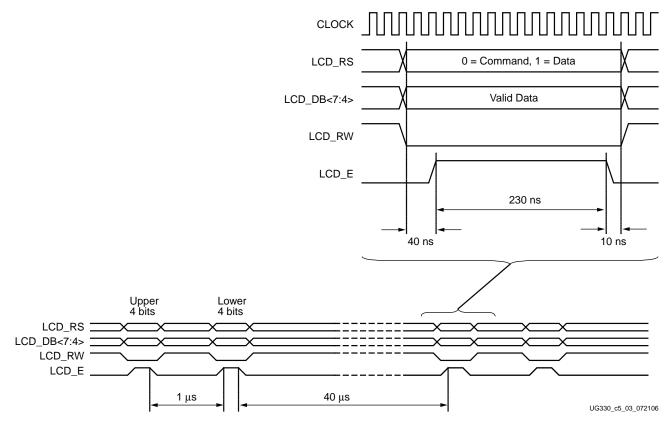

|          | Four-Bit Data Interface                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                            |

|          | Transferring Eight-Bit Data over the Four-Bit Interface                                                                                                                                                                                                                                                                                                                                                                                        |                                                                            |

|          | Initializing the Display                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                            |

|          | Power-On Initialization                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                            |

|          | Display Configuration                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                            |

|          | Writing Data to the Display                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                            |

|          | Disabling the Unused LCD.                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                            |

|          | Related Resources                                                                                                                                                                                                                                                                                                                                                                                                                              | 55                                                                         |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                            |

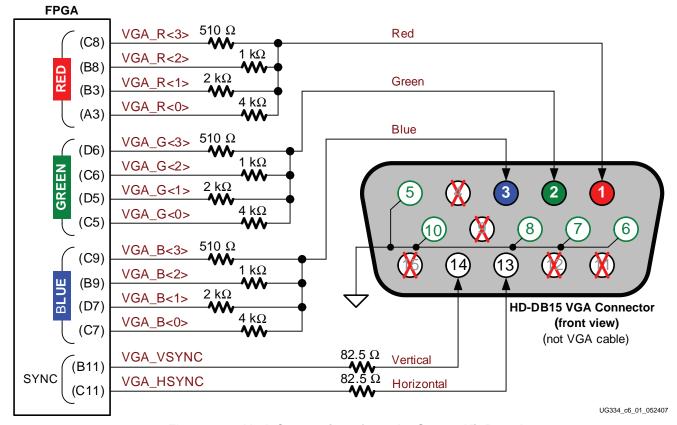

| Cha      | pter 6: VGA Display Port                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                            |

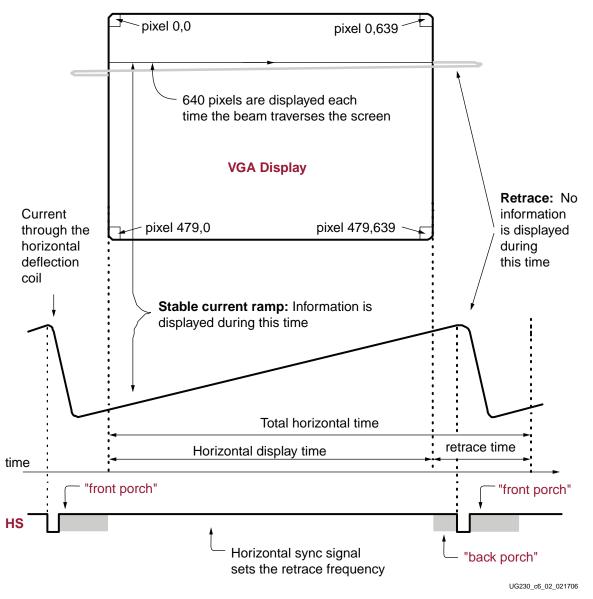

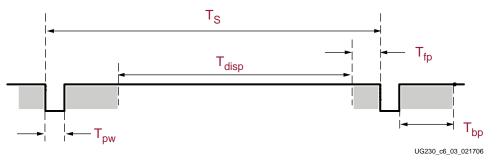

|          | Signal Timing for a 60 Hz, 640x480 VGA Display                                                                                                                                                                                                                                                                                                                                                                                                 | 50                                                                         |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                            |

|          | VGA Signal Timing                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                            |

|          | UCF Location Constraints                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                            |

|          | Related Resources                                                                                                                                                                                                                                                                                                                                                                                                                              | 61                                                                         |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                            |

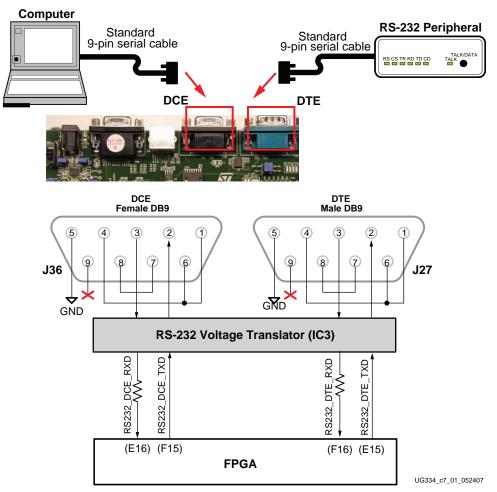

| Cha      | pter 7: RS-232 Serial Ports                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                            |

| •::•     | ptol 1: 1to Lot Collai i Olto                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                            |

| •        | •                                                                                                                                                                                                                                                                                                                                                                                                                                              | 62                                                                         |

| <b>.</b> | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                            |

|          | •                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                            |

|          | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                            |

|          | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                            |

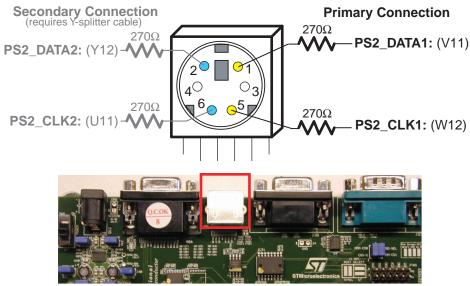

|          | Overview  UCF Location Constraints  pter 8: PS/2 Mouse/Keyboard Port                                                                                                                                                                                                                                                                                                                                                                           | 64                                                                         |

|          | Overview  UCF Location Constraints  pter 8: PS/2 Mouse/Keyboard Port  Keyboard                                                                                                                                                                                                                                                                                                                                                                 | 64                                                                         |

|          | Overview  UCF Location Constraints  pter 8: PS/2 Mouse/Keyboard Port  Keyboard  Mouse                                                                                                                                                                                                                                                                                                                                                          | 64<br>66<br>68                                                             |

|          | Overview UCF Location Constraints  pter 8: PS/2 Mouse/Keyboard Port  Keyboard  Mouse  Voltage Supply                                                                                                                                                                                                                                                                                                                                           | 64<br>66<br>68<br>69                                                       |

|          | Overview UCF Location Constraints  pter 8: PS/2 Mouse/Keyboard Port  Keyboard  Mouse  Voltage Supply  Adding a Second PS/2 Port Using a Y-Splitter Cable                                                                                                                                                                                                                                                                                       | 64<br>66<br>68<br>69                                                       |

|          | Overview UCF Location Constraints  pter 8: PS/2 Mouse/Keyboard Port  Keyboard  Mouse  Voltage Supply                                                                                                                                                                                                                                                                                                                                           | 64<br>66<br>68<br>69                                                       |

|          | Overview UCF Location Constraints  pter 8: PS/2 Mouse/Keyboard Port  Keyboard  Mouse  Voltage Supply  Adding a Second PS/2 Port Using a Y-Splitter Cable                                                                                                                                                                                                                                                                                       | 64<br>66<br>68<br>69<br>69<br>70                                           |

|          | Overview UCF Location Constraints  pter 8: PS/2 Mouse/Keyboard Port  Keyboard  Mouse  Voltage Supply  Adding a Second PS/2 Port Using a Y-Splitter Cable  UCF Location Constraints                                                                                                                                                                                                                                                             | 64<br>66<br>68<br>69<br>69<br>70                                           |

| Cha      | Overview UCF Location Constraints  pter 8: PS/2 Mouse/Keyboard Port  Keyboard  Mouse  Voltage Supply  Adding a Second PS/2 Port Using a Y-Splitter Cable  UCF Location Constraints  Related Resources                                                                                                                                                                                                                                          | 64<br>66<br>68<br>69<br>69<br>70                                           |

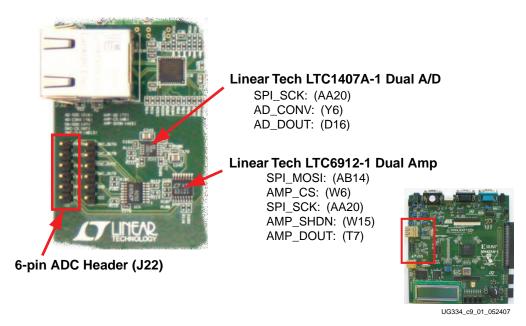

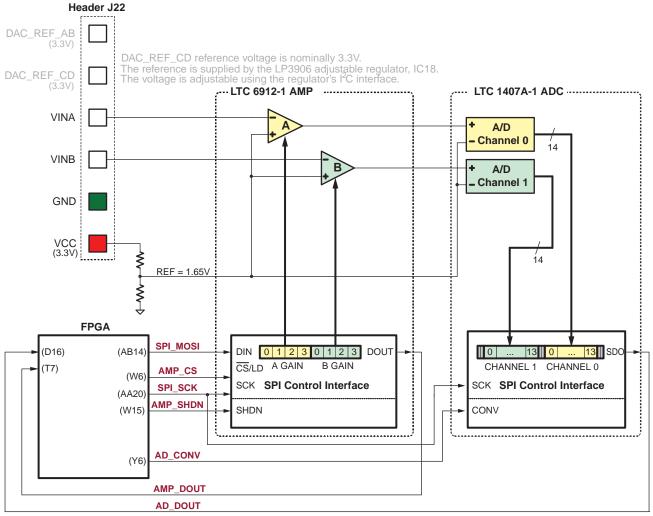

| Cha      | Overview UCF Location Constraints  pter 8: PS/2 Mouse/Keyboard Port Keyboard Mouse Voltage Supply Adding a Second PS/2 Port Using a Y-Splitter Cable UCF Location Constraints Related Resources  pter 9: Analog Capture Circuit                                                                                                                                                                                                                | 64<br>66<br>68<br>69<br>70<br>70                                           |

| Cha      | Overview UCF Location Constraints  pter 8: PS/2 Mouse/Keyboard Port  Keyboard  Mouse  Voltage Supply  Adding a Second PS/2 Port Using a Y-Splitter Cable  UCF Location Constraints  Related Resources                                                                                                                                                                                                                                          | 64<br>66<br>68<br>69<br>70<br>70                                           |

| Cha      | Overview UCF Location Constraints  pter 8: PS/2 Mouse/Keyboard Port Keyboard Mouse Voltage Supply Adding a Second PS/2 Port Using a Y-Splitter Cable UCF Location Constraints Related Resources  pter 9: Analog Capture Circuit                                                                                                                                                                                                                | 64<br>66<br>68<br>69<br>70<br>70                                           |

| Cha      | Overview UCF Location Constraints  pter 8: PS/2 Mouse/Keyboard Port Keyboard Mouse Voltage Supply Adding a Second PS/2 Port Using a Y-Splitter Cable UCF Location Constraints Related Resources  pter 9: Analog Capture Circuit Digital Outputs from Analog Inputs                                                                                                                                                                             | 64<br>66<br>68<br>69<br>70<br>70<br>72<br>73                               |

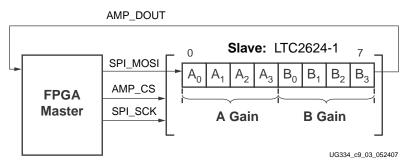

| Cha      | Overview UCF Location Constraints  pter 8: PS/2 Mouse/Keyboard Port  Keyboard Mouse  Voltage Supply Adding a Second PS/2 Port Using a Y-Splitter Cable UCF Location Constraints Related Resources  pter 9: Analog Capture Circuit  Digital Outputs from Analog Inputs  Programmable Pre-Amplifier Interface Programmable Gain                                                                                                                  | 64<br>66<br>68<br>69<br>70<br>70<br>72<br>73<br>73<br>73                   |

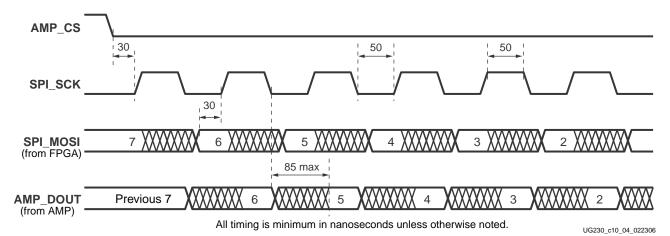

| Cha      | Overview UCF Location Constraints  pter 8: PS/2 Mouse/Keyboard Port  Keyboard Mouse Voltage Supply Adding a Second PS/2 Port Using a Y-Splitter Cable UCF Location Constraints Related Resources  pter 9: Analog Capture Circuit  Digital Outputs from Analog Inputs.  Programmable Pre-Amplifier Interface Programmable Gain SPI Control Interface                                                                                            | 64<br>68<br>69<br>70<br>70<br>72<br>73<br>73<br>74                         |

| Cha      | Overview UCF Location Constraints  pter 8: PS/2 Mouse/Keyboard Port  Keyboard Mouse  Voltage Supply Adding a Second PS/2 Port Using a Y-Splitter Cable UCF Location Constraints Related Resources  pter 9: Analog Capture Circuit  Digital Outputs from Analog Inputs  Programmable Pre-Amplifier Interface Programmable Gain                                                                                                                  | 64<br>68<br>69<br>70<br>70<br>72<br>73<br>73<br>74                         |

| Cha      | Overview UCF Location Constraints  pter 8: PS/2 Mouse/Keyboard Port  Keyboard Mouse Voltage Supply Adding a Second PS/2 Port Using a Y-Splitter Cable UCF Location Constraints Related Resources  pter 9: Analog Capture Circuit  Digital Outputs from Analog Inputs.  Programmable Pre-Amplifier Interface Programmable Gain SPI Control Interface                                                                                            | 64<br>68<br>69<br>70<br>70<br>72<br>73<br>73<br>74<br>75                   |

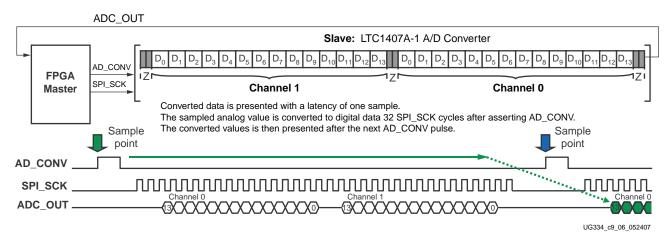

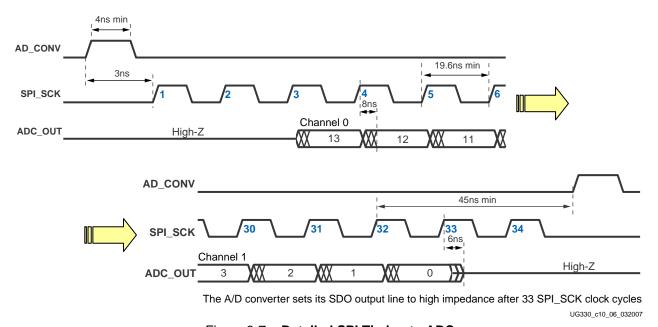

| Cha      | Overview UCF Location Constraints  pter 8: PS/2 Mouse/Keyboard Port  Keyboard Mouse Voltage Supply Adding a Second PS/2 Port Using a Y-Splitter Cable UCF Location Constraints Related Resources  pter 9: Analog Capture Circuit  Digital Outputs from Analog Inputs  Programmable Pre-Amplifier Interface Programmable Gain SPI Control Interface UCF Location Constraints  Analog-to-Digital Converter (ADC) Interface                       | 64<br>66<br>68<br>69<br>70<br>70<br>72<br>73<br>73<br>74<br>75<br>75<br>75 |

| Cha      | Overview UCF Location Constraints  pter 8: PS/2 Mouse/Keyboard Port  Keyboard Mouse Voltage Supply Adding a Second PS/2 Port Using a Y-Splitter Cable UCF Location Constraints Related Resources  pter 9: Analog Capture Circuit  Digital Outputs from Analog Inputs  Programmable Pre-Amplifier Interface Programmable Gain SPI Control Interface UCF Location Constraints  Analog-to-Digital Converter (ADC) Interface SPI Control Interface | 64<br>66<br>68<br>69<br>70<br>70<br>72<br>73<br>73<br>74<br>75<br>75<br>75 |

| Cha      | Overview UCF Location Constraints  pter 8: PS/2 Mouse/Keyboard Port  Keyboard Mouse Voltage Supply Adding a Second PS/2 Port Using a Y-Splitter Cable UCF Location Constraints Related Resources  pter 9: Analog Capture Circuit  Digital Outputs from Analog Inputs  Programmable Pre-Amplifier Interface Programmable Gain SPI Control Interface UCF Location Constraints  Analog-to-Digital Converter (ADC) Interface                       | 64<br>66<br>68<br>69<br>70<br>70<br>72<br>73<br>73<br>74<br>75<br>75<br>75 |

| Related Resources 7                                                  |

|----------------------------------------------------------------------|

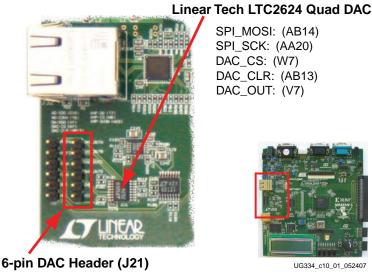

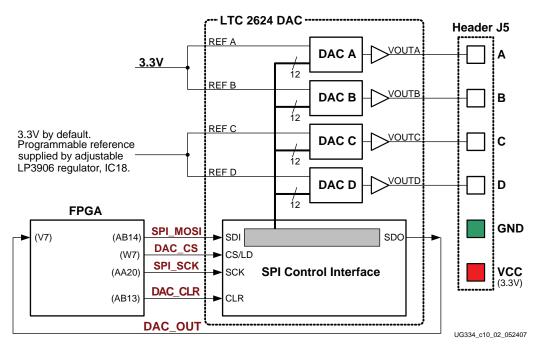

| Chapter 10: Digital-to-Analog Converter (DAC)                        |

| SPI Communication                                                    |

| Interface Signals                                                    |

| SPI Communication Details                                            |

| Communication Protocol                                               |

| Specifying the DAC Output Voltage                                    |

| UCF Location Constraints 8                                           |

| Related Resources 8                                                  |

| Chapter 11: Parallel NOR Flash PROM                                  |

| Flash Connections. 8 Shared SPI Flash and Platform Flash Data Line 8 |

| UCF Location Constraints                                             |

| Address                                                              |

| Data                                                                 |

| Control                                                              |

| Setting the FPGA Mode Select Pins 8                                  |

| Creating and Programming Configuration Images for Parallel Flash     |

| Related Resources 8                                                  |

| TREATURE TRESORICES                                                  |

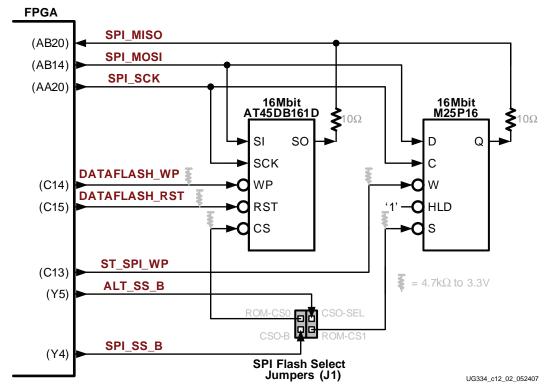

| Chapter 12: SPI Serial Flash                                         |

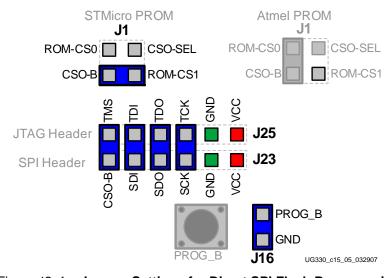

| SPI Flash PROM Select Jumpers (J1)                                   |

| UCF Location Constraints                                             |

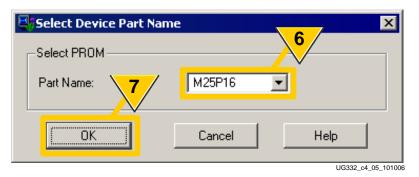

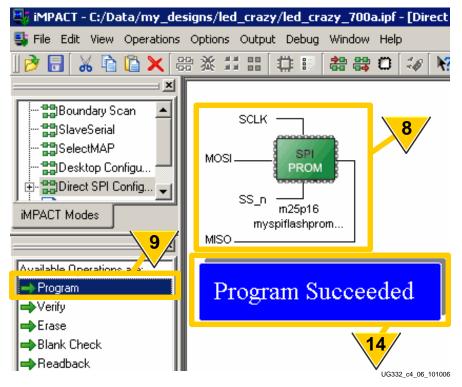

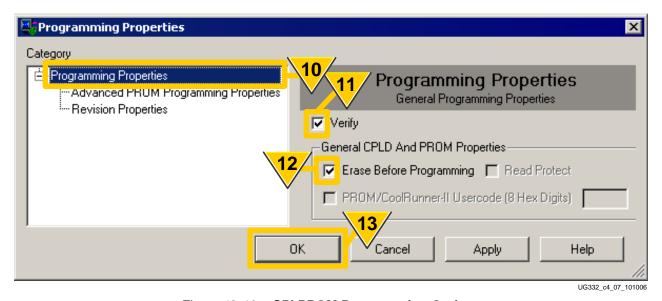

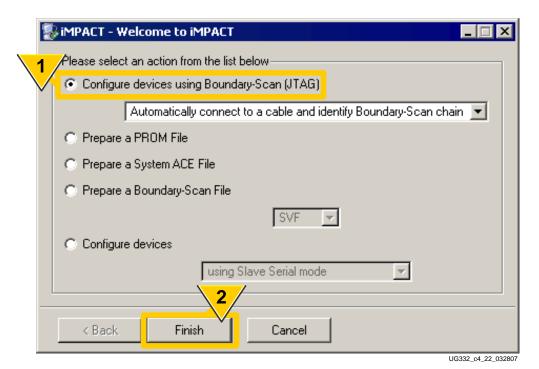

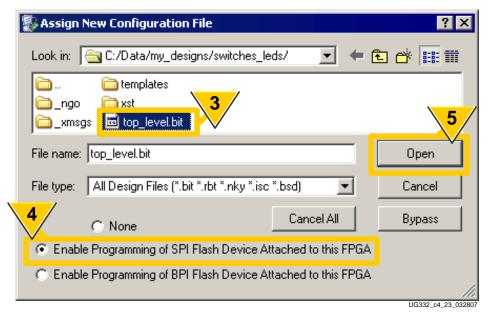

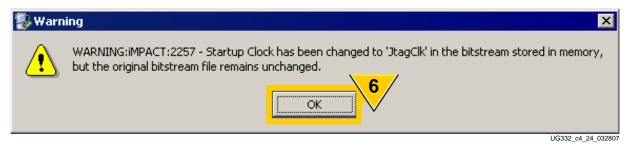

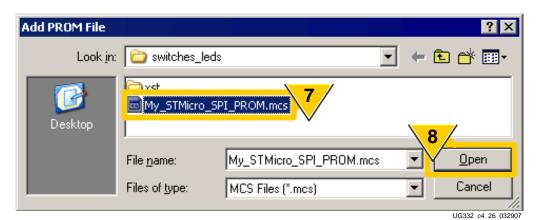

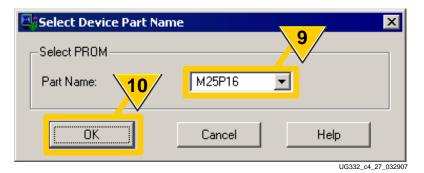

| Creating and Programming Configuration Images for SPI Serial Flash 9 |

| SPI Flash PROM Programming Options                                   |

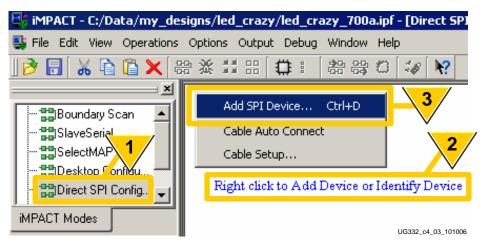

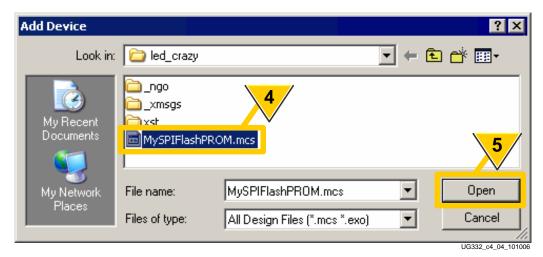

| Direct Programming Method                                            |

| Using Embedded USB JTAG Programmer                                   |

| Using a Separate JTAG Parallel Programming Cable (Optional)          |

| Direct SPI Flash Programming Using iMPACT                            |

| Indirect Programming Method                                          |

| Jumper Settings                                                      |

| Indirect SPI Flash Programming Using iMPACT                          |

| Related Resources 10                                                 |

| Chapter 13: DDR2 SDRAM                                               |

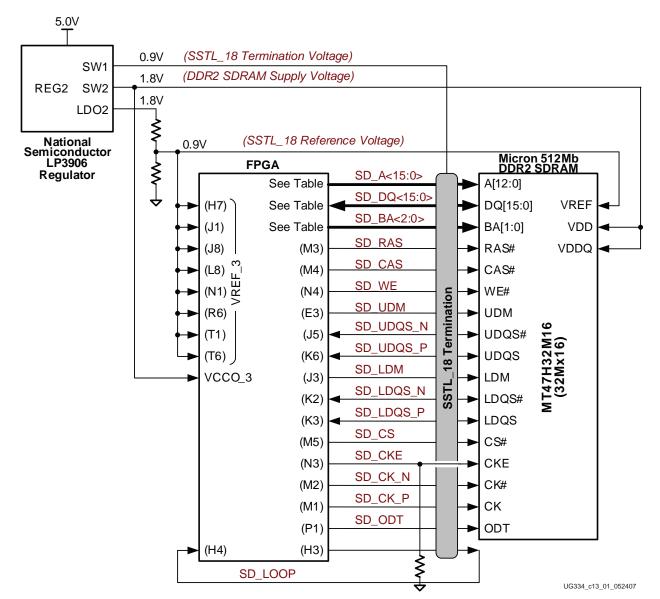

| DDR2 SDRAM Connections                                               |

| UCF Location Constraints                                             |

| Address                                                              |

| Data                                                                 |

| Control                                                              |

| Reserve FPGA V <sub>REF</sub> Pins                                   |

| Special Layout Recommendations                                       |

| Related Resources                                                    |

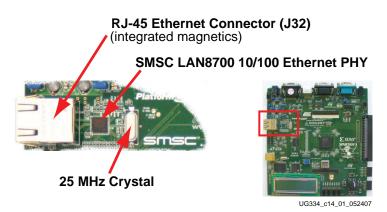

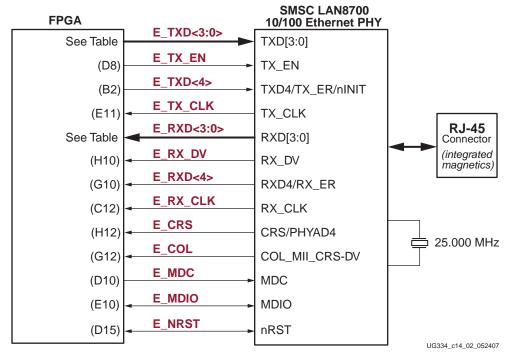

| Chapter 14: 10/100 Ethernet Physical Layer Interface |     |

|------------------------------------------------------|-----|

| Ethernet PHY Connections                             | 116 |

| MicroBlaze Ethernet IP Cores                         | 117 |

| UCF Location Constraints                             | 118 |

| Related Resources                                    |     |

|                                                      |     |

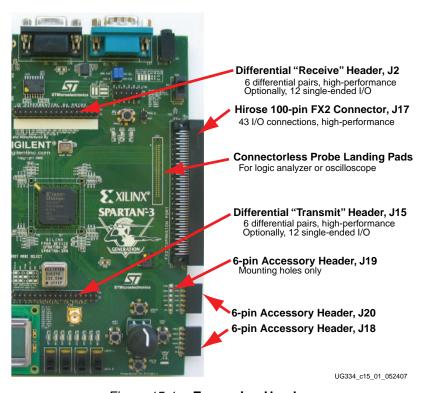

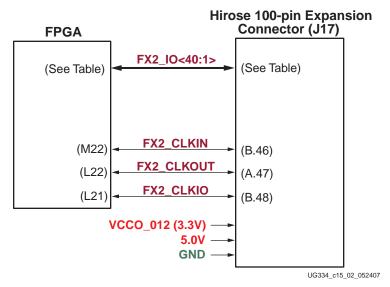

| Chapter 15: Expansion Connectors                     |     |

| Hirose 100-Pin FX2 Edge Connector (J17)              |     |

| Expansion Connector Compatibility                    |     |

| Voltage Supplies to the Connector                    |     |

| Connector Pinout and FPGA Connections                |     |

| Mating Receptacle Connectors                         |     |

| UCF Location Constraints.                            |     |

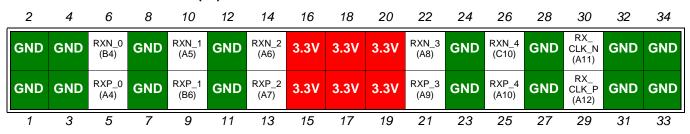

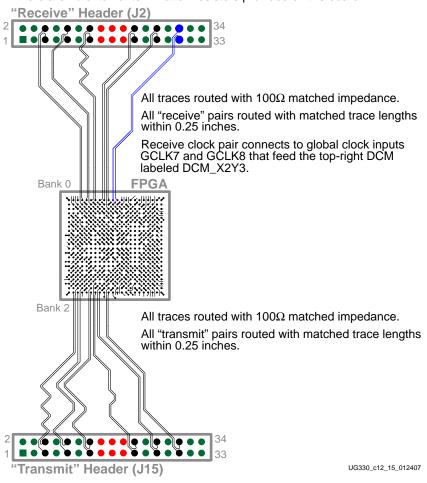

| Differential I/O Connectors                          |     |

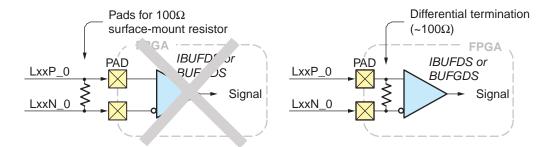

| Using Differential Inputs                            |     |

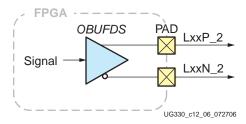

| Using Differential Outputs                           |     |

| Differential Trace Layout Considerations             |     |

| 34-Conductor Cable Assemblies (2x17)                 |     |

| UCF Location Constraints                             |     |

| Six-Pin Accessory Headers                            |     |

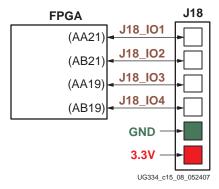

| J18 Header                                           |     |

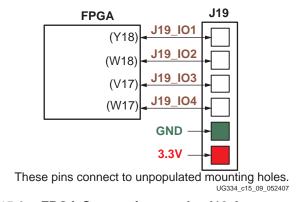

| J19 Header                                           |     |

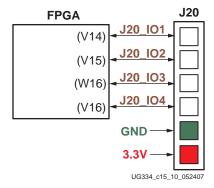

| J20 Header                                           |     |

| UCF Location Constraints                             |     |

|                                                      |     |

| Connectorless Debugging Port Landing Pads (J34)      | 131 |

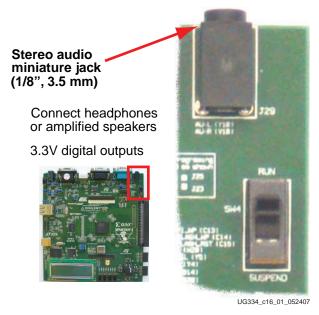

| Chapter 16: Miniature Stereo Audio Jack              |     |

| Supported Audio Devices                              | 133 |

| FPGA Connections                                     |     |

| UCF Location Constraints.                            | 134 |

| Related Resources                                    | 134 |

| Chapter 17: Voltage Supplies                         |     |

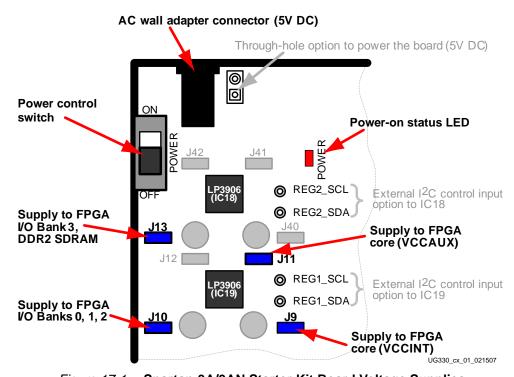

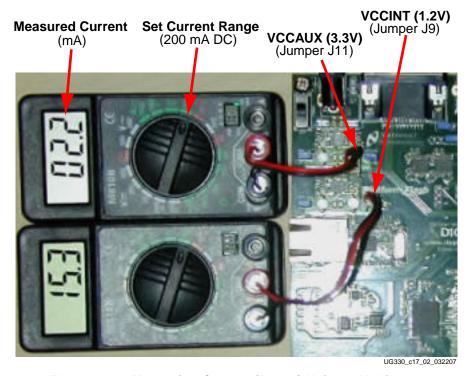

| Measuring Power Across Voltage Supply Jumpers        | 137 |

| I <sup>2</sup> C Voltage Adjustment Interface        |     |

| Possible Applications                                |     |

| Restoring Default Voltages                           | 139 |

| UCF Location Constraints                             | 139 |

| Related Resources                                    | 139 |

# About This Guide

This user guide provides basic information on the Spartan®-3A/3AN Starter Kit board capabilities, functions, and design. It includes general information on how to use the various peripheral functions included on the board. For detailed reference designs, including VHDL or Verilog source code, please visit the following web link.

• Spartan-3A/3AN FPGA Starter Kit Board Web Page http://www.xilinx.com/s3astarter and http://www.xilinx.com/s3anstarter

There are multiple versions of the Spartan-3A/3AN FPGA Starter Kit. This document describes the three kits that include the "Revision D" Spartan-3A/3AN FPGA Starter Kit Board, which is an updated version of the "Revision C" Spartan-3A FPGA Starter Kit Board. The following table describes the different kits.

| Feature           | Spartan-3AN<br>Starter Kit                                                         | Spartan-3A DDR2 SDRAM Interface Development Kit | Spartan-3A Starter<br>Kit, Revision D | Spartan-3A Starter Kit,<br>Revision C                      |

|-------------------|------------------------------------------------------------------------------------|-------------------------------------------------|---------------------------------------|------------------------------------------------------------|

| Part<br>Number    | HW-SPAR3AN-SK-UNI-G                                                                | HW-SPAR3ADDR2-DK-<br>UNI-G                      | HW-SPAR                               | 3A-SK-UNI-G                                                |

| Device            | XC3S700AN XC3S700A                                                                 |                                                 |                                       |                                                            |

| Board<br>Revision |                                                                                    | Revision C                                      |                                       |                                                            |

| DDR2<br>Memory    | Supported with 133 MHz crystal oscillator in auxiliary socket                      |                                                 |                                       | Requires board<br>modification for<br>improved performance |

| User<br>Guide     | UG334 (this document)                                                              |                                                 |                                       | <u>UG330</u>                                               |

| Web Page          | <u>www.xilinx.com/s3anstarter</u> <u>www.xilinx.com/s3addr2</u> <u>www.xilinx.</u> |                                                 |                                       | .com/s3astarter                                            |

Almost all functionality is identical between the Revision C and Revision D boards, although the silkscreen changes make the two boards look different. The pictures used in this document are from the Revision D board. If you are using the original Revision C version of the board, refer to <u>UG330</u> for pictures and documentation. The following figure highlights where to find the board revision code on a Revision C board.

# **Acknowledgments**

Xilinx wishes to thank the following companies for their support of the Spartan-3A/3AN Starter Kit board:

- STMicroelectronics for the 32 Mbit parallel NOR Flash and 16 Mbit SPI serial Flash memories

- Atmel for the 16 Mbit SPI serial DataFlash memory

- Linear Technology for the SPI-compatible A/D and D/A converters and the programmable pre-amplifier

- SMSC for the 10/100 Ethernet PHY

- National Semiconductor for the four-rail voltage regulators that power the FPGA and and all peripheral components

- Xilinx, Inc. Configuration Solutions for the XCF04S Platform Flash PROM and support for the embedded USB programmer

#### **Guide Contents**

This manual contains the following chapters:

- Chapter 1, "Introduction and Overview," provides an overview of the key features of the Spartan-3A/3AN Starter Kit board.

- Chapter 2, "Switches, Buttons, and Rotary Knob," defines the switches, buttons, and knobs present on the Spartan-3A/3AN Starter Kit board.

- Chapter 3, "Clock Sources," describes the various clock sources available on the Spartan-3A/3AN Starter Kit board.

- Chapter 4, "FPGA Configuration Options," describes the configuration options for the FPGA on the Spartan-3A/3AN Starter Kit board.

- Chapter 5, "Character LCD Screen," describes the functionality of the character LCD screen.

- Chapter 6, "VGA Display Port," describes the functionality of the VGA port.

- Chapter 7, "RS-232 Serial Ports," describes the functionality of the RS-232 serial ports.

- Chapter 8, "PS/2 Mouse/Keyboard Port," describes the functionality of the PS/2 mouse and keyboard port.

- Chapter 10, "Digital-to-Analog Converter (DAC)," describes the functionality of the D/A converter.

- Chapter 9, "Analog Capture Circuit," describes the functionality of the A/D converter with a programmable gain pre-amplifier.

- Chapter 11, "Parallel NOR Flash PROM," describes the functionality of the STMicroelectronics parallel NOR PROM.

- Chapter 12, "SPI Serial Flash," describes the functionality of the SPI Serial Flash memory interface.

- Chapter 13, "DDR2 SDRAM," describes the functionality of the DDR2 SDRAM memory interface.

- Chapter 14, "10/100 Ethernet Physical Layer Interface," describes the functionality of the 10/100Base-T Ethernet physical layer interface.

- Chapter 15, "Expansion Connectors," describes the various connectors available on the Spartan-3A/3AN Starter Kit board.

- Chapter 16, "Miniature Stereo Audio Jack," describes the audio interface.

- Chapter 17, "Voltage Supplies," describes the board's power distribution system.

# **Additional Resources**

To find additional documentation, see the Xilinx website at:

http://www.xilinx.com/support/documentation/index.htm

To search the Answer Database of silicon, software, and IP questions and answers, or to create a technical support WebCase, see the Xilinx website at:

http://www.xilinx.com/support.

# Introduction and Overview

Thank you for purchasing the Xilinx Spartan®-3A/3AN FPGA Starter Kit. The board is invaluable to develop a Spartan-3A or Spartan-3AN FPGA application.

# **Getting Started**

The Spartan-3A/3AN Starter Kit board is ready for use, right out of the box. The design stored in external Flash exercises the various I/O devices, such as the VGA display and serial ports. In addition it demonstrates new FPGA features, such as selectable MultiBoot and the power-saving Suspend mode.

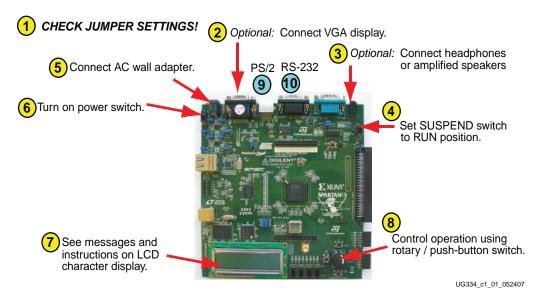

To start using the board, follow the simple steps outlined in Figure 1-1.

Figure 1-1: Powering Up the Starter Kit Board

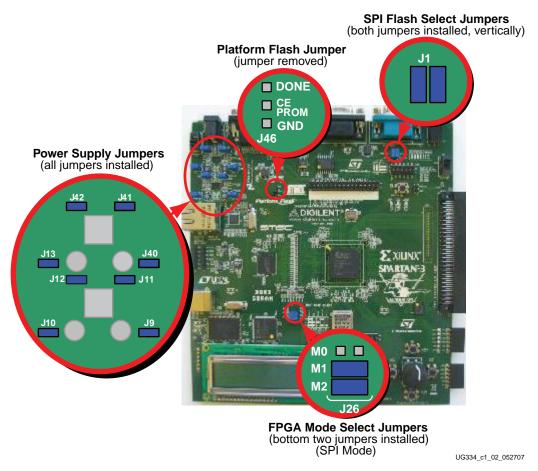

- 1. Double-check the position of the board jumpers, as shown in Figure 1-2, page 14. These settings are required for the demonstration design to configure correctly.

- 2. Optionally connect a VGA display device. The display device can be a CRT, a flat-panel, or even a projector.

- 3. Optionally connect headphones or amplified speakers to the audio jack.

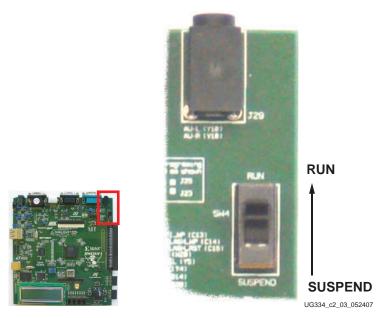

- 4. Set the SUSPEND switch to the "RUN" position.

- 5. Connect the included AC adapter to wall power and also to the board. The AC adapter also includes attachments to support worldwide locals.

- 6. Turn on the power switch.

- 7. The character LCD and VGA display, if connected, display various informational messages and instructions. If an audio device is connected, the board offers words of welcome in a variety of languages.

- 8. Use the rotary/push-button switch to control various board functions.

- 9. Optionally connect a PS/2-style keyboard to support one of the included demonstrating designs.

- 10. Optionally connect a PC directly to the board using a standard 9-pin serial cable.

Figure 1-2: Default Jumper Settings for Starter Kit Board

For more information on the demonstration design, visit the Design Examples web page:

- Spartan-3A/3AN FPGA Starter Kit Demo Design Overview www.xilinx.com/products/boards/s3astarter/reference\_designs.htm#demo

- Restoring the "Out of the Box" Flash Programming www.xilinx.com/products/boards/s3astarter/reference\_designs.htm#out

# **Operating the Default Demonstration Design**

The demonstration design programmed onto the Spartan-3A/3AN Starter Kit board provides various output information, depending on what I/O or display devices are connected. The VGA and audio ports provide the richest experience.

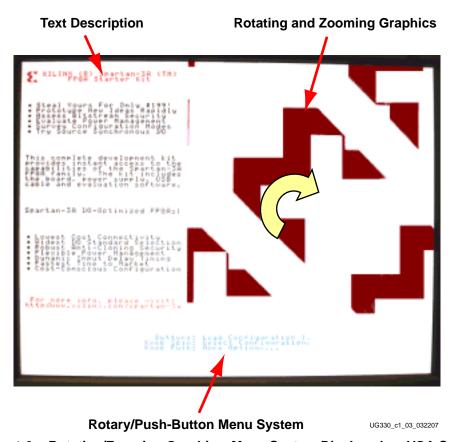

## VGA Display

If a VGA display is connected to the board, then the Starter Kit board displays graphics similar to that shown in Figure 1-3.

Until one of the four push buttons around the rotary knob (Figure 2-5, page 27) is pressed, the display automatically rotates a graphic image and zooms in and out around the image. This is called "AutoPilot" mode. A brief text overview describing the board appears along the left edge. Blue text at the bottom of the screen presents the menu system.

Figure 1-3: Rotating/Zooming Graphics, Menu System Displayed on VGA Screen

# Rotary Knob/Push-Button Menu System

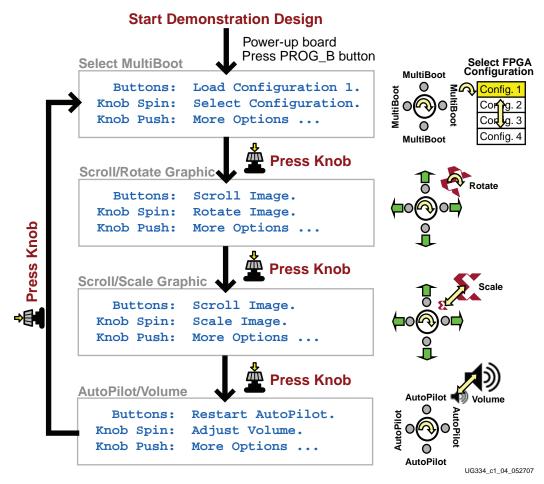

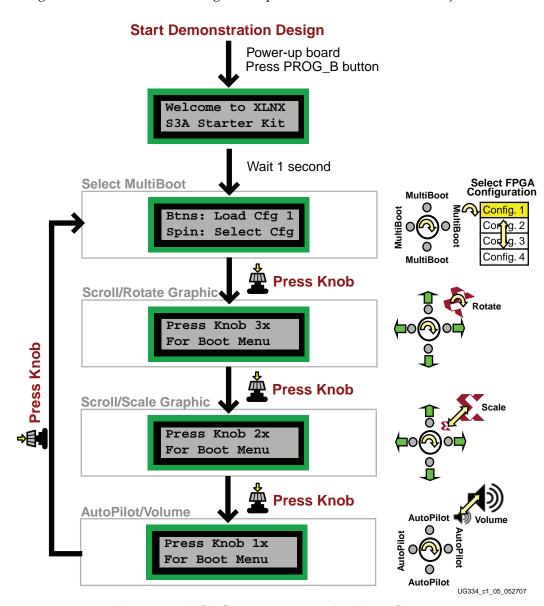

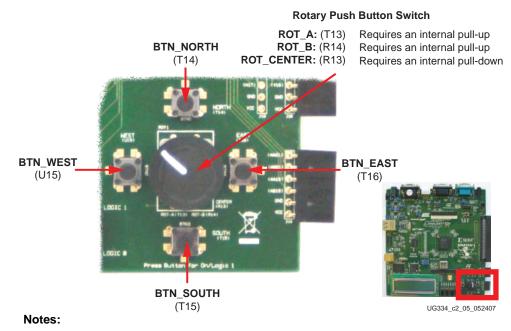

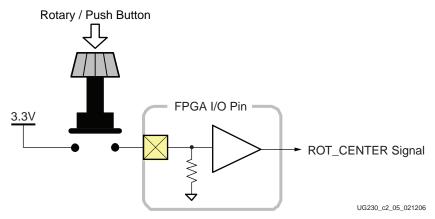

The Spartan-3A/3AN Starter Kit board demonstration design uses the rotary knob and surrounding push-button switches, shown in Figure 2-5, page 27, to implement a menu system. The menu display appears in blue text at the bottom of the VGA output. The menu functions are highlighted in Table 1-1 and Figure 1-4.

Table 1-1: Function of Each Menu Control

| Press Knob                              | Rotate Knob                                      | Press Push Button                                |  |

|-----------------------------------------|--------------------------------------------------|--------------------------------------------------|--|

| Move to next menu selection, next mode. | Depends on current mode, as shown in Figure 1-4. | Depends on current mode, as shown in Figure 1-4. |  |

Figure 1-4: Rotary Knob/Push-Button Menu System

# Select MultiBoot Configuration Image

Spartan-3A/3AN FPGAs support a selectable MultiBoot configuration interface. If the FPGA configures in one of its Master configuration modes, then the FPGA always loads the configuration image stored at address 0 in Flash at power-up, or whenever the PROG\_B button is pressed.

Spin the rotary knob to select a new FPGA configuration image. The blue text at the bottom of the display updates with each click of the rotary knob. For example, the application displays "Buttons: Load Configuration x" where 'x' corresponds to the bitstream image listed in Table 1-2. Table 1-2 describes the bitstreams preloaded on the board.

After selecting the desired image, press one of the four push-button switches that surround the rotary knob. This action causes the FPGA to load the selected image from external Flash memory.

To change to the "Scroll or Rotate Graphic" mode, press the rotary knob.

Table 1-2: FPGA Configuration Bitstreams Preprogrammed on the Starter Kit Board

| FPGA<br>Configuration<br>Bitstream | FPGA Application/Reference Design Example                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 0<br>(default)                     | Starter Kit board demonstration design. Loaded at power-up.  www.xilinx.com/products/boards/s3astarter/reference_designs.htm#demo                                                                                                                                                                                                                                                             |  |  |  |

| 1                                  | Device DNA Reader: Reads the FPGA's unique Device ID value and displays it on the character LG screen.  www.xilinx.com/products/boards/s3astarter/reference_designs.htm#dna_reader                                                                                                                                                                                                            |  |  |  |

| 2                                  | Fractal Generator: Computes fractal images in real time and displays on the VGA port. A user-contributed design by Matthias Alles. Rotate knob to zoom fractal image; press surrounding pus buttons to scroll the image.  www-user.rhrk.uni-kl.de/~alles/fpga/files.htm                                                                                                                       |  |  |  |

| 3                                  | <b>ASCII Terminal:</b> Implements a text terminal using an attached VGA display and PS/2 keyboard and will communicate with HyperTerminal on a PC via an RS-232 serial connection.  Source included in <a href="www.xilinx.com/products/boards/s3astarter/reference_designs.htm#out">www.xilinx.com/products/boards/s3astarter/reference_designs.htm#out</a> .                                |  |  |  |

| 4                                  | STMicro M29DW323DT Parallel Flash Programmer: Communicates to a PC using HyperTerminal via an RS-232 serial connection. Programs, erases, and reads the STMicro M29DW323DT parallel Flash PROM on the Starter Kit board.  www.xilinx.com/products/boards/s3astarter/reference_designs.htm#parallel_flash_programmer                                                                           |  |  |  |

| Spartan-3AN<br>FPGA                | Internal Flash Paint Application: Use a mouse to create drawings and read or write them to In-System Flash. Loaded from internal SPI Flash in Spartan-3AN FPGA Starter Kit Board. Requires setting Mode pins as described in Table 4-1, page 39 for Internal Master SPI mode. For Spartan-3AN Starter Kit Board only.  www.xilinx.com/products/boards/s3astarter/reference_designs.htm#paint. |  |  |  |

# Scroll or Rotate Graphic

In this mode, rotate the knob to rotate the graphic image clockwise or counterclockwise.

Use the four push-button switches to scroll the graphic image up, down, left, or right.

Press the rotary knob to change to the "Scroll or Scale Graphic" mode.

# Scroll or Scale Graphic

In this mode, rotate the knob to scale the size of the graphic image, zooming in and out.

Use the four push-button switches to scroll the resulting graphic image up, down, left, or right.

Press the rotary knob to change to the "Restart AutoPilot, Speaker Volume Control" mode.

# Restart AutoPilot, Speaker Volume Control

In this mode, rotate the knob to control the speaker output volume.

Press any of the four push-button switches to restart the AutoPilot function.

Press the rotary knob to change to the "Select MultiBoot Configuration Image" mode.

#### LCD Screen Control Option

While the demonstration design operates best with an attached VGA display, the on-board LCD screen tracks similar functionality, as shown in Figure 1-5. If no VGA display is attached, then the "Scroll or Rotate Graphic", "Scroll or Scale Graphic", and "Restart AutoPilot, Speaker Volume Control" modes offer little to no functionality, the exception being the volume control assuming that a speaker is attached to the audio jack.

Figure 1-5: LCD Screen Output using Menu System

# Power-Saving Suspend Mode

All of the preloaded FPGA configuration bitstreams have the power-saving Suspend mode enabled. Suspend mode reduces FPGA power consumption while preserving the present state of the FPGA application and the FPGA's configuration data. Set the SUSPEND switch to RUN or SUSPEND as described in "SUSPEND Switch," page 26.

Using one or two external multimeters, measure the corresponding difference in current consumption, as described in "Measuring Power Across Voltage Supply Jumpers," page 137.

**Caution!** Do not set the SUSPEND switch to "SUSPEND" while programming the parallel NOR Flash PROM using configuration bitstream #4, as described in Table 1-2.

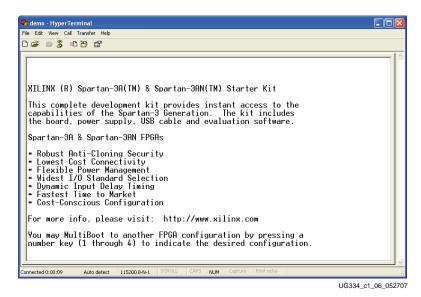

#### RS-232 Serial Port Control Option

Optionally, control the demonstration design using a serial port connection to a PC or workstation. On a PC, use the HyperTerminal program to communicate to the FPGA application, as shown in Figure 1-6. Using a standard, straight-through 9-pin serial cable, connect the PC's 9-pin RS-232 port to the board's DCE connector (see Figure 7-1, page 63).

Figure 1-6: Use HyperTerminal and a Standard Serial Cable to Connect to Board

When the demonstration design begins operating, it transmits a message using the serial port.

Press a number key on the PC to load the associated MultiBoot bitstream listed in Table 1-2.

# **Key Components and Features**

The key features of the Spartan-3A FPGA Starter Kit board or the Spartan-3AN FPGA Starter Kit board are:

- *Spartan-3A FPGA Starter Kit Board:* Xilinx 700K-gate XC3S700A <u>Spartan-3A FPGA</u> in the Pb-free 484-ball BGA package (FGG484)

- Spartan-3AN FPGA Starter Kit Board: Xilinx 700K-gate XC3S700AN Spartan-3AN nonvolatile FPGA in the Pb-free 484-ball BGA package (FGG484)

- Internal 8 Mbit In-System Flash memory

- Store FPGA configuration bitstream or nonvolatile data

- 4 Mbit Xilinx Platform Flash configuration PROM

- 64 MByte (512 Mbit) of DDR2 SDRAM, 32Mx16 data interface

- 4 MByte (32 Mbit) of parallel NOR Flash

- FPGA configuration storage

- ♦ MicroBlaze<sup>TM</sup> code storage/shadowing

- x8 or x16 data interface after configuration

- Two 16 Mbit SPI serial Flash

- STMicroelectronics and Atmel DataFlash serial architectures

- FPGA configuration storage

- Supports single configuration bitstream or multiple MultiBoot configuration bitstreams

- Nonvolatile data storage

- ♦ MicroBlaze code shadowing

- Two-line, 16-character LCD screen

- PS/2 port

- Supports PS/2-compatible mouse or keyboard

- Supports both mouse and keyboard using a Y-splitter cable (not included)

- VGA display port, 12-bit color

- 10/100 Ethernet PHY (requires Ethernet MAC in FPGA)

- Two nine-pin RS-232 ports (DTE- and DCE-style)

- On-board USB-based programming solution

- ♦ FPGA download/debug

- SPI serial Flash in-system direct programming

- 50 MHz clock oscillator

- 8-pin DIP socket for second oscillator

- SMA connector for clock inputs or outputs

- 100-pin Hirose FX2 expansion connector with up to 43 FPGA user I/Os

- Compatible with <u>Digilent FX2 add-on cards</u>

- High-speed differential I/O connectors

- Receiver: Six data channels or five data channels plus clock

- Transmitter: Six data channels or five data channels plus clock

- Supports multiple differential I/O standards, including LVDS, RSDS, mini-LVDS

- Also supports up to 24 single-ended I/O

- Uses widely available 34-conductor cables

- Two six-pin expansion connectors for <u>Digilent Peripheral Modules</u>

- Four-output, SPI-based Digital-to-Analog Converter (DAC)

- Two-input, SPI-based Analog-to-Digital Converter (ADC) with programmable-gain pre-amplifier

- Stereo audio jack using digital I/O pins

- ChipScope<sup>TM</sup> SoftTouch debugging port

- Rotary-encoder with push-button shaft

- Eight discrete LEDs

- Four slide switches

- Four push-button switches

# **Design Trade-Offs**

A few system-level design trade-offs were required in order to provide the Spartan-3A/3AN Starter Kit board with the most functionality.

## Configuration Methods Galore!

A typical FPGA application uses a single, nonvolatile memory to store configuration images. A typical Spartan-3AN nonvolatile FPGA application would not require any external memory. To demonstrate new Spartan-3A and Spartan-3AN FPGA capabilities, the starter kit board has four different configuration memory sources that all must function well together. The extra configuration functions make the starter kit board more complex than typical FPGA applications.

The starter kit board also includes an on-board USB-based JTAG programming interface. The on-chip circuitry simplifies the device programming experience. In typical applications, the JTAG programming hardware resides off-board or in a separate programming module, such as the Xilinx Platform USB cable.

## Voltages for all Applications

The Spartan-3A/3AN FPGA typically operates with two supply rails, 1.2V and 3.3V. The Spartan-3A/3AN Starter Kit board showcases a quadruple-output regulator developed by National Semiconductor specifically to power Spartan-3 generation FPGAs. This regulator is sufficient for most standalone FPGA applications.

# Spartan-3A/3AN FPGA Starter Kit Design Examples

provides demo technical details.

Visit the Spartan-3A/3AN FPGA Starter Kit Design Examples web page to download and use the latest applications that specifically target the starter kit board:

Spartan-3A/3AN Starter Kit Design Examples Web Page www.xilinx.com/products/boards/s3astarter/reference\_designs.htm

The list of designs is ever growing and the applications are often updated to the latest software releases. The following list provides a sample of design examples:

- Spartan-3A/3AN Starter Kit Demo Design Overview

<u>www.xilinx.com/products/boards/s3astarter/reference\_designs.htm#demo</u>

This describes the out-of-the box demo design shipped with the board. Includes how to set up and operate the demonstration, evaluate MultiBoot and Suspend, and

- Restoring the "Out of the Box" Flash Programming www.xilinx.com/products/boards/s3astarter/reference\_designs.htm#out

Provides a short overview of what the starter kit board does "out of the box" and includes instructions on how to restore the board to the original "out of the box" state. The ZIP file includes the "golden" MCS files that are pre-programmed into Flash memory before the board is shipped. The PDF file contains instructions for restoring the board to its original settings using these MCS files in case any of the configuration memories were overwritten during normal use.

• Spartan-3A/3AN Starter Kit Board Verification Design www.xilinx.com/products/boards/s3astarter/reference\_designs.htm#test

This example includes the board test specification and the board test design. This design was used during initial board verification and some functions are used during production test. It is provided to test out a board if something is not working as expected. The design files may also be of general interest. The ZIP file has the design source, a script to run them, and the resulting compiled files.

Programmer for the STMicroelectronics M29DW323DT Parallel NOR Flash www.xilinx.com/products/boards/s3astarter/reference\_designs.htm #parallel\_flash\_programmer

This design transforms the Spartan-3A or Spartan-3AN FPGA into a programmer for the 32Mbit STMicroelectronics M29DW323DT parallel NOR Flash memory. This memory optionally holds configuration images for the FPGA and provides general non-volatile storage for other applications implemented within the FPGA. Using a simple terminal program, this application provides the following capabilities:

- Erase the memory in part or in full

- Read the memory to verify contents

- Download complete configuration images using standard MCS files

- Manually program individual bytes

- Display the device identifier and 64-bit unique device numbers

- Spartan-3A/3AN "Device DNA" Reader <u>www.xilinx.com/products/boards/s3astarter/reference\_designs.htm#dna\_reader</u>

This design uses a PicoBlaze™ processor to read the unique "Device DNA" identifier embedded in each Spartan-3A/3AN FPGA and then display it on the LCD screen.

# **Choose a Spartan-3 Generation Starter Kit Board for your Needs**

The Spartan-3A and Spartan-3AN Starter Kit boards are best for prototyping Spartan-3A/3AN FPGA applications. Depending on specific requirements, however, Xilinx and third-party companies offer development boards that better suit other needs.

# Spartan-3A/3AN FPGA Features and Embedded Processing Functions

The Spartan-3A/3AN Starter Kit board highlights the unique features of the Spartan-3A and Spartan-3AN FPGA families and provides a convenient development board for embedded processing applications. The board highlights these features:

- Spartan-3AN specific features

- Nonvolatile configuration from internal SPI Flash

- Spartan-3A/3AN specific features

- Parallel NOR Flash configuration

- SPI serial Flash configuration using either the STMicroelectronics or Atmel DataFlash architectures

- MultiBoot FPGA configuration from both Parallel NOR and SPI serial Flash PROMs

- Embedded development

- MicroBlaze 32-bit embedded RISC processor

- PicoBlaze eight-bit embedded controller

- Power management using the Suspend mode feature

- DDR2 SDRAM memory interfaces

#### Other Spartan-3 Generation Development Boards

The Spartan-3A/3AN Starter Kit board demonstrates the full capabilities of the Spartan-3A and Spartan-3AN FPGA families and the Xilinx ISE® development software.

For a development board specific to the Spartan-3E FPGA family, consider the Spartan-3E Starter Kit board. There are multiple ordering codes, depending on the included power supply.

Spartan-3E Starter Kit Board (HS-SPAR3E-SK\_xx) www.xilinx.com/s3estarter

For MicroBlaze™ processor development, consider the Spartan-3A DSP Embedded Development board.

Spartan-3A DSP S3D1800A MicroBlaze Processor Edition (DO-SD1800A-EDK-DK-UNI-G)

www.xilinx.com/products/devkits/DO-SD1800A-EDK-DK-UNI-G.htm

For PCI Express<sup>®</sup> applications, consider the Spartan-3 PCI Express Starter Kit.

Spartan-3 PCI Express Starter Kit (HW-S3PCIE-DK) www.xilinx.com/s3pcie

For simple Spartan-3 FPGA applications, consider the fairly basic Spartan-3 Starter Kit board.

Spartan-3 Starter Kit (DO-SPAR3-DK) <u>www.xilinx.com/s3starter</u>

Also consider the capable boards offered by Xilinx partners:

Spartan-3 Generation Board Interactive Search www.xilinx.com/products/devboards/index.htm

# Spartan-3A and Spartan-3AN FPGAs

The Spartan-3AN FPGA platform offers nonvolatile pin-compatible versions of the Spartan-3A FPGA platform. The Spartan-3AN FPGAs support the same external programming sources as Spartan-3A FPGAs, but add an additional internal SPI Flash programming mode. The internal SPI Flash can also be used for user data. The Spartan-3A/3AN Starter Kit Board supports both external and Spartan-3AN internal configuration options.

Spartan-3AN FPGAs require  $V_{CCAUX}$  to be 3.3V while Spartan-3A FPGAs allow  $V_{CCAUX}$  to be either 2.5V or 3.3V. The Spartan-3A/3AN Starter Kit Board uses a default  $V_{CCAUX}$  of 3.3V.

Spartan-3A and Spartan-3AN FPGAs have different documentation and availability. Verify the latest version of the appropriate documentation on xilinx.com.

- Spartan-3A FPGAs

- Web page www.xilinx.com/spartan3a

- Data sheet <u>www.xilinx.com/support/documentation/data\_sheets/ds529.pdf</u>

- Errata www.xilinx.com/support/documentation/spartan-3a\_errata.htm

- Additional documentation www.xilinx.com/support/documentation/spartan-3a.htm

- Spartan-3AN FPGAs

- Web page www.xilinx.com/spartan3an

- Data sheet www.xilinx.com/support/documentation/data\_sheets/ds557.pdf

- Errata

www.xilinx.com/support/documentation/spartan-3an\_errata.htm

- Additional documentation

www.xilinx.com/support/documentation/spartan-3an.htm

#### **Related Resources**

Refer to the following links for additional information:

- Spartan-3A/3AN Starter Kit

- www.xilinx.com/s3astarter

- Spartan-3A/3AN Rev D Starter Kit user guide (this document)

- Spartan-3A Rev C Starter Kit user guide <u>www.xilinx.com/support/documentation/boards\_and\_kits/ug330.pdf</u>

- Example User Constraints File (UCF)

www.xilinx.com/products/boards/s3astarter/files/s3astarter.ucf

- Board schematics (annotated)

www.xilinx.com/products/boards/s3astarter\_schematic.pdf

- Bill of materials (BOM) list <u>www.xilinx.com/products/boards/s3astarter/s3astarter\_bom.xls</u>

- Link to design examples www.xilinx.com/products/boards/s3astarter/reference\_designs.htm

- Xilinx MicroBlaze<sup>TM</sup> Soft Processor www.xilinx.com/microblaze

- Xilinx PicoBlaze<sup>TM</sup> Soft Processor www.xilinx.com/picoblaze

- Xilinx Embedded Development Kit www.xilinx.com/ise/embedded\_design\_prod/platform\_studio.htm

- Xilinx Software Tutorials

www.xilinx.com/support/techsup/tutorials/

- Xilinx Technical Support www.xilinx.com/support

# Switches, Buttons, and Rotary Knob

#### Slide Switches

#### **Locations and Labels**

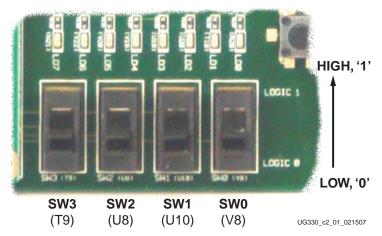

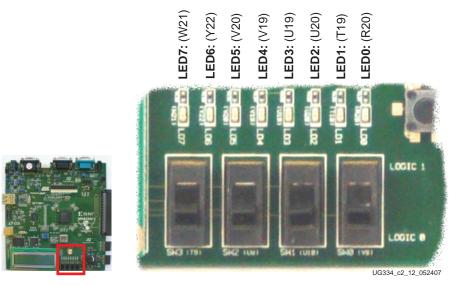

The Spartan®-3A/3AN FPGA Starter Kit board has four slide switches, as shown in Figure 2-1. The slide switches are located in the lower right corner of the board and are labeled SW3 through SW0. Switch SW3 is the left-most switch, and SW0 is the right-most switch.

Figure 2-1: Four Slide Switches

# Operation

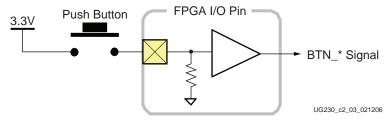

When in the UP or ON position, a switch connects the FPGA pin to 3.3V, a logic High. When DOWN or in the OFF position, the switch connects the FPGA pin to ground, a logic Low. The switches typically exhibit about 2 ms of mechanical bounce. There is no active debouncing circuitry, although such circuitry could easily be added to the FPGA design programmed on the board.

#### **UCF Location Constraints**

Figure 2-2 provides the UCF constraints for the four slide switches, including the I/O pin assignment and the I/O standard used. The PULLUP resistor is not required, but it defines the input value when the switch is in the middle of a transition.

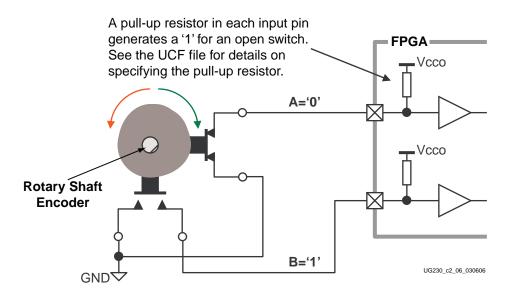

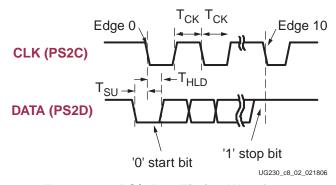

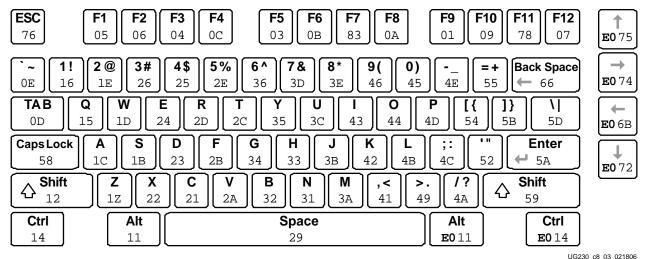

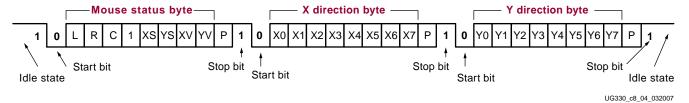

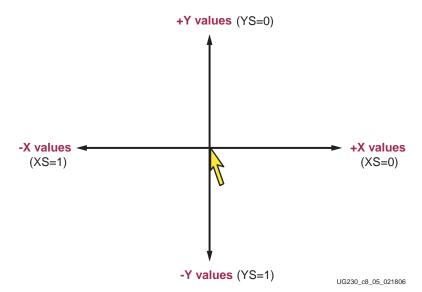

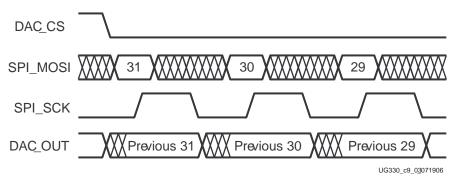

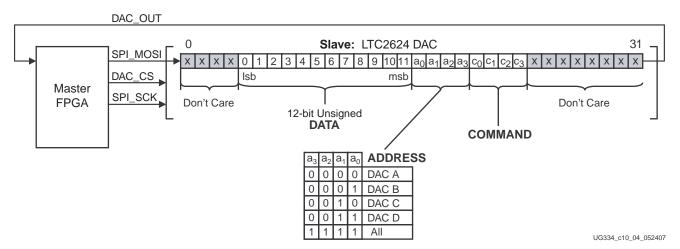

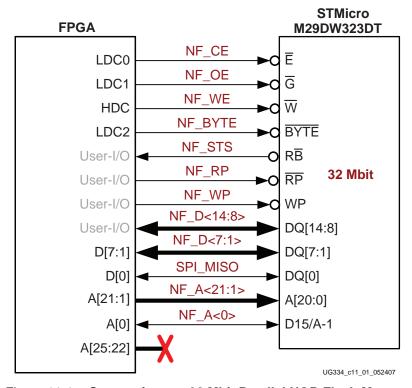

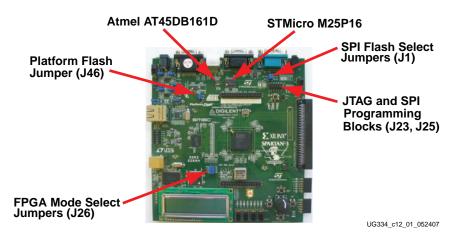

```