# TLE7183F

**Automotive Power**

#### **Table of Contents**

# **Table of Contents**

|                                                                                                                                        | Table of Contents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | . 2                                                                                    |

|----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| I                                                                                                                                      | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 3                                                                                    |

| 2                                                                                                                                      | Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | . 4                                                                                    |

| <b>3</b><br>3.1<br>3.2                                                                                                                 | Pin Configuration         Pin Assignment TLE7183F         Pin Definitions and Functions                                                                                                                                                                                                                                                                                                                                                                                                             | . 5                                                                                    |

| <b>1</b><br>1.1<br>1.2<br>1.3                                                                                                          | General Product Characteristics Absolute Maximum Ratings Functional Range Default State of Inputs                                                                                                                                                                                                                                                                                                                                                                                                   | . 8                                                                                    |

| 5.1<br>5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>5.2<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>5.2.6<br>5.2.7<br>5.2.8<br>5.3.1<br>5.4 | Description and Electrical Characteristics  MOSFET Driver Output Stages Operation at Vs<12V - Integrated Charge Pumps Sleep Mode Electrical Characteristics Protection and Diagnostic Functions Short Circuit Protection Overcurrent Warning Dead Time and Shoot Through Protection Undervoltage Shut Down Overvoltage Shut Down Overtemperature Warning ERR Pins Electrical Characteristics Shunt Signal Conditioning Electrical Characteristics Phase voltage feedback Electrical Characteristics | 11<br>12<br>12<br>13<br>16<br>16<br>16<br>17<br>17<br>17<br>17<br>17<br>20<br>21<br>23 |

| <b>5</b><br>6.1                                                                                                                        | Application Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 24<br>25                                                                               |

| 5.2                                                                                                                                    | Further Application Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                        |

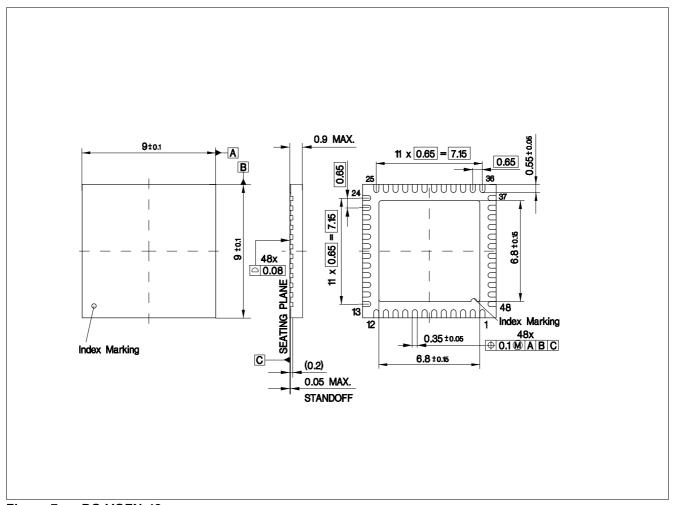

| 7                                                                                                                                      | Package Outlines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                        |

| 3                                                                                                                                      | Revision History                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 27                                                                                     |

#### **TLE7183F**

#### 1 Overview

#### **Features**

- · Compatible to very low ohmic normal level input N-Channel MOSFETs

- Separate input for each MOSFET

- PWM frequency up to 30kHz

- · Fulfils specification down to 5.5V supply voltage

- · Low EMC sensitivity and emission

- VQFN-48 package with exposed heat slug

- Control inputs with TTL characteristics

- Separate source connection for each MOSFET

- · Integrated minimum dead time

- Shoot through protection

- Short circuit protection with 5 fixed detection level available

- · Disable function and sleep mode

- · Detailed diagnosis

- · Thermal overload warning for driver IC

- integrated overcurrent warning

- Integrated current sense amplifier

- 0 to 100% duty cycle

- Green Product (RoHS compliant)

- AEC Qualified

### Description

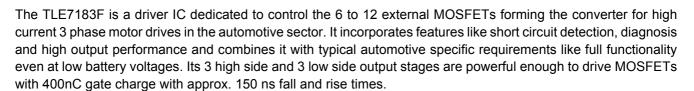

The TLE7183F can be ordered with 5 different options for a fixed short circuit detection level. Please see **Table 2** for detailed information.

Typical applications are cooling fan, water pump, electro-hydraulic and electric power steering. The TLE7183F is designed for 12 Vpower net.

PG-VQFN-48

**Block Diagram**

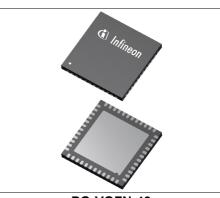

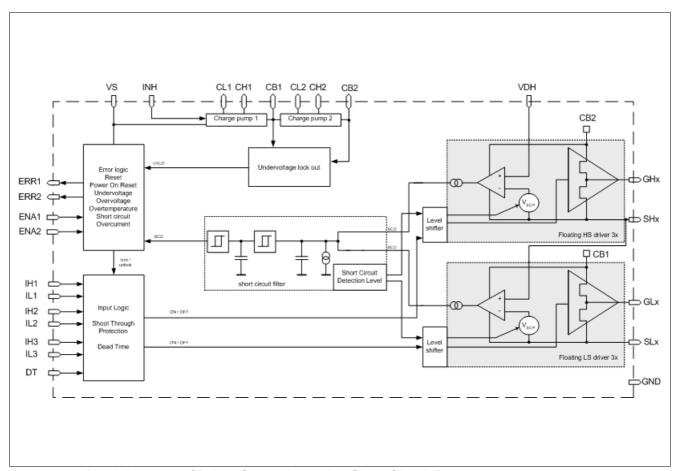

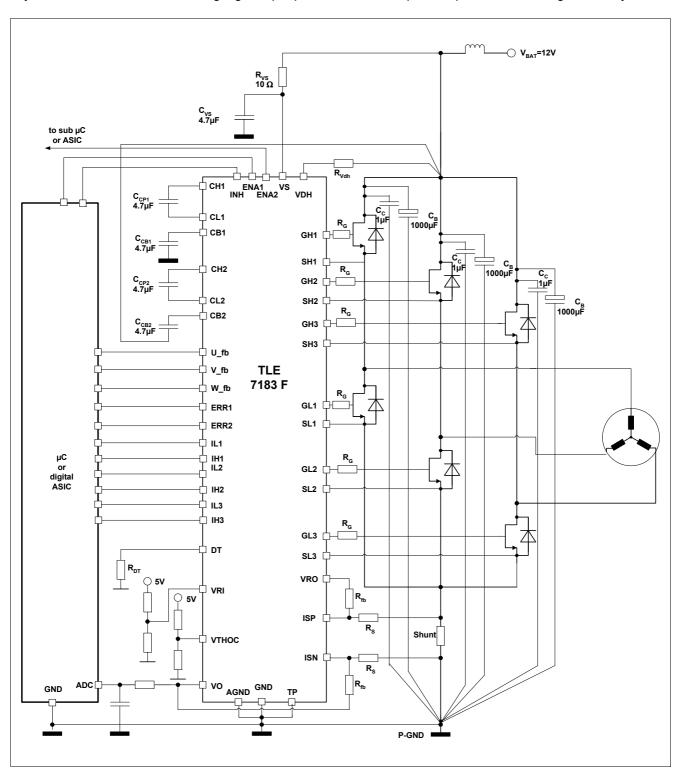

### 2 Block Diagram

Figure 1 Block Diagram

**Pin Configuration**

# 3 Pin Configuration

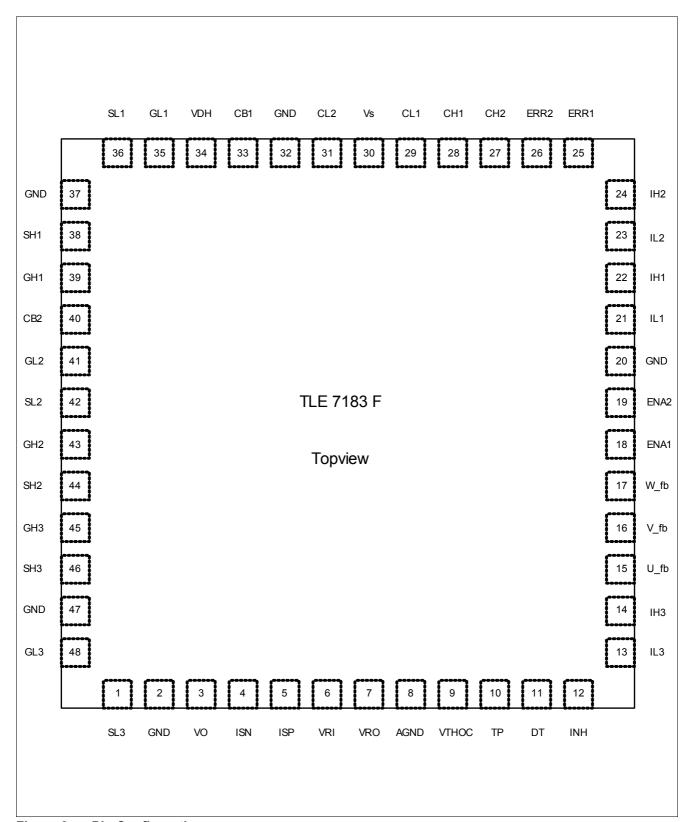

# 3.1 Pin Assignment TLE7183F

Figure 2 Pin Configuration

**Pin Configuration**

### 3.2 Pin Definitions and Functions

| Pin | Symbol | Function                                                              |

|-----|--------|-----------------------------------------------------------------------|

| 1   | SL3    | Connection to source low side switch 3                                |

| 2   | GND    | Logic and power ground                                                |

| 3   | VO     | Output of OpAmp for shunt signal amplification                        |

| 4   | ISN    | - Input of OpAmp for shunt signal amplification                       |

| 5   | ISP    | + Input of OpAmp for shunt signal amplification                       |

| 6   | VRI    | Input of bias reference amplifier                                     |

| 7   | VRO    | Output of bias reference amplifier                                    |

| 8   | AGND   | Analog ground especially for the current sense OpAmp                  |

| 9   | VTHOC  | Threshold voltage for overcurrent detection                           |

| 10  | TP     | test pin, connect to GND of driver IC                                 |

| 11  | DT     | Dead time program pin                                                 |

| 12  | INH    | Inhibit pin (active low)                                              |

| 13  | IL3    | Input for low side switch 3 (active high)                             |

| 14  | IH3    | Input for high side switch 3 (active low)                             |

| 15  | U_fb   | Digital logic representation of the voltage phase U; positive logic   |

| 16  | V_fb   | Digital logic representation of the voltage phase V; positive logic   |

| 17  | W_fb   | Digital logic representation of the voltage phase W; positive logic   |

| 18  | ENA1   | Enable pin (active high)                                              |

| 19  | ENA2   | Enable pin (active high)                                              |

| 20  | GND    | Logic and power ground                                                |

| 21  | IL1    | Input for low side switch 1 (active high)                             |

| 22  | IH1    | Input for high side switch 1 (active low)                             |

| 23  | IL2    | Input for low side switch 2 (active high)                             |

| 24  | IH2    | Input for high side switch 2 (active low)                             |

| 25  | ERR1   | Error signal 1                                                        |

| 26  | ERR2   | Error signal 2                                                        |

| 27  | CH2    | + terminal for pump capacitor of charge pump 2                        |

| 28  | CH1    | + terminal for pump capacitor of charge pump 1                        |

| 29  | CL1    | - terminal for pump capacitor of charge pump 1                        |

| 30  | VS     | Voltage supply                                                        |

| 31  | CL2    | - terminal for pump capacitor of charge pump 2                        |

| 32  | GND    | Logic and power ground                                                |

| 33  | CB1    | Buffer capacitor for charge pump 1                                    |

| 34  | VDH    | Connection to drain of high side switches for short circuit detection |

| 35  | GL1    | Output to gate low side switch 1                                      |

| 36  | SL1    | Connection to source low side switch 1                                |

| 37  | GND    | Logic and power ground                                                |

| 38  | SH1    | Connection to source high side switch 1                               |

| 39  | GH1    | Output to gate high side switch 1                                     |

| 40  | CB2    | Buffer capacitor for charge pump 2                                    |

### **Pin Configuration**

| Pin | Symbol                                     | Function                                |  |  |  |  |

|-----|--------------------------------------------|-----------------------------------------|--|--|--|--|

| 41  | GL2                                        | Output to gate low side switch 2        |  |  |  |  |

| 42  | SL2 Connection to source low side switch 2 |                                         |  |  |  |  |

| 43  | GH2                                        | Output to gate high side switch 2       |  |  |  |  |

| 44  | SH2                                        | Connection to source high side switch 2 |  |  |  |  |

| 45  | GH3                                        | Output to gate high side switch 3       |  |  |  |  |

| 46  | SH3                                        | Connection to source high side switch 3 |  |  |  |  |

| 47  | GND                                        | Logic and power ground                  |  |  |  |  |

| 48  | GL3                                        | Output to gate low side switch 3        |  |  |  |  |

#### **General Product Characteristics**

### 4 General Product Characteristics

### 4.1 Absolute Maximum Ratings

### Absolute Maximum Ratings 1)

40 °C  $\leq T_i \leq$  150 °C; all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Pos.    | Parameter                                                    | Symbol     | Lim  | nit Values | Unit | Conditions                                            |

|---------|--------------------------------------------------------------|------------|------|------------|------|-------------------------------------------------------|

|         |                                                              |            | Min. | Max.       |      |                                                       |

| Voltage | s                                                            |            |      |            | •    |                                                       |

| 4.1.1   | Supply voltage                                               | $V_{S}$    | -4.0 | 45         | V    | with 100hm and 1µF                                    |

| 4.1.2   | Supply voltage                                               | $V_{S}$    | -0.3 | 45         | V    | _                                                     |

| 4.1.3   | Supply voltage                                               | $V_{S}$    | -0.3 | 47         | V    | <i>t</i> <sub>p</sub> <200ms                          |

| 4.1.4   | Voltage range at IHx,ILx,ERRx, VO, DT, VTHOC, ENAx, VRI, VRO | $V_{DP}$   | -0.3 | 6.0        | V    | _                                                     |

| 4.1.5   | Voltage range at INH                                         | $V_{INH}$  | -0.3 | 18.0       | V    | _                                                     |

| 4.1.6   | Voltage range at TP                                          | $V_{TP}$   | -0.3 | 2          | V    |                                                       |

| 4.1.7   | Voltage range at SLx                                         | $V_{SL}$   | -7   | 7          | V    | _                                                     |

| 4.1.8   | Voltage range at SHx                                         | $V_{SH}$   | -7   | 45         | V    | _                                                     |

| 4.1.9   | Voltage range at GLx                                         | $V_{GL}$   | -7   | 18         | V    | _                                                     |

| 4.1.10  | Voltage range at GHx                                         | $V_{GH}$   | -7   | 55         | V    | _                                                     |

| 4.1.11  | Voltage difference Gxx-Sxx                                   | $V_{GS}$   | -0.3 | 15         | V    | _                                                     |

| 4.1.12  | Voltage range at VDH                                         | $V_{VDH}$  | -0.3 | 55         | V    | INH=high                                              |

| 4.1.13  | Voltage range at VDH                                         | $V_{VDH}$  | -4.0 | 55         | V    | INH=high;<br>with $R_{VDH} > 70\Omega$ ;<br>200ms, 5x |

| 4.1.14  | Voltage range at VDH                                         | $V_{VDH}$  | -0.3 | 28         | V    | INH=low                                               |

| 4.1.15  | Voltage range at VDH                                         | $V_{VDH}$  | -4.0 | 28         | V    | INH=low;<br>with $R_{VDH} > 70\Omega$ ;<br>200ms, 5x  |

| 4.1.16  | Voltage range at CL1                                         | $V_{CL1}$  | -0.3 | 25         | V    | _                                                     |

| 4.1.17  | Voltage range at CH1, CB1                                    | $V_{CH1}$  | -0.3 | 25         | V    | _                                                     |

| 4.1.18  | Voltage difference CH1-CL1                                   | $V_{DC1}$  | -0.3 | 25         | V    | _                                                     |

| 4.1.19  | Voltage range at CL2                                         | $V_{CL2}$  | -0.3 | 25         | V    | _                                                     |

| 4.1.20  | Voltage range at CH2, CB2                                    | $V_{CH2}$  | -0.3 | 45         | V    | _                                                     |

| 4.1.21  | Voltage difference CH2-CL2                                   | $V_{CP2}$  | -0.3 | 25         | V    | _                                                     |

| 4.1.22  | Voltage range at ISP, ISN                                    | $V_{ISI}$  | -5   | 5          | V    | _                                                     |

| 4.1.23  | Output current range at VO                                   | $I_{VO}$   | -20  | 20         | mA   | _                                                     |

| 4.1.24  | Gate resistor                                                | $R_{Gate}$ | 2    | _          | Ω    | _                                                     |

| Temper  | atures                                                       |            |      | *          | *    |                                                       |

| 4.1.25  | Junction temperature                                         | $T_{j}$    | -40  | 150        | °C   | _                                                     |

| 4.1.26  | Storage temperature                                          | $T_{stg}$  | -55  | 150        | °C   | _                                                     |

| 4.1.27  | Lead soldering temperature (1/16" from body)                 | $T_{sol}$  | _    | 260        | °C   | _                                                     |

#### **General Product Characteristics**

#### Absolute Maximum Ratings (cont'd)<sup>1)</sup>

40 °C  $\leq T_i \leq$  150 °C; all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Pos.    | Parameter                                       | Symbol     | Lin  | nit Values | Unit | Conditions |

|---------|-------------------------------------------------|------------|------|------------|------|------------|

|         |                                                 |            | Min. | Max.       |      |            |

| 4.1.28  | Peak reflow soldering temperature <sup>2)</sup> | $T_{ref}$  | _    | 260        | °C   | _          |

| Thermal | Resistance                                      |            |      |            |      |            |

| 4.1.29  | Junction to case                                | $R_{thjC}$ | _    | 5          | K/W  | _          |

| Power D | issipation                                      |            |      | <u>'</u>   |      | <u>'</u>   |

| 4.1.30  | Power Dissipation (DC) @ TCASE=125°C            | $P_{tot}$  | _    | 2          | W    | _          |

| ESD Sus | sceptibility                                    |            |      |            |      |            |

| 4.1.31  | ESD Resistivity <sup>3)</sup>                   | $V_{ESD}$  | _    | 2          | kV   |            |

| 4.1.32  | ESD Resistivity (charge device model)           | $V_{ESD}$  | _    | 750        | V    |            |

<sup>1)</sup> Not subject to production test, specified by design.

Attention: Stresses above the ones listed here may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Attention: Integrated protection functions are designed to prevent IC destruction under fault conditions described in the data sheet. Fault conditions are considered as "outside" normal operating range. Protection functions are not designed for continuous repetitive operation.

### 4.2 Functional Range

| Pos.  | Parameter                                    | meter Symbol Limit Values |      | mit Values | Unit | Conditions                            |  |

|-------|----------------------------------------------|---------------------------|------|------------|------|---------------------------------------|--|

|       |                                              |                           | Min. | Max.       |      |                                       |  |

| 4.2.1 | Supply voltage <sup>1)2)</sup>               | $V_{S}$                   | 5.5  | 20         | V    | DC                                    |  |

|       |                                              |                           | 5.5  | 28         |      | t<1s                                  |  |

| 4.2.2 | Duty cycle <sup>3)</sup>                     | D                         | 0    | 100        | %    | _                                     |  |

| 4.2.3 | PWM frequency                                | $F_{PWM}$                 | 0    | 25         | kHz  | Total gate charge<br>400nC            |  |

| 4.2.4 | Quiescent current <sup>4)</sup>              | $I_{Q}$                   | _    | 30         | μA   | V <sub>S</sub> ,V <sub>DH</sub> <20 V |  |

| 4.2.5 | Quiescent current into VDH                   | $I_{Q\_VDH}$              | _    | 30         | μA   | V <sub>DH</sub> <20V;                 |  |

|       |                                              |                           |      |            |      | V <sub>S</sub> pin open               |  |

| 4.2.6 | Supply current at Vs                         | $I_{Vs}$                  |      |            |      | F <sub>PWM</sub> =25kHz               |  |

|       |                                              |                           |      |            |      | Q <sub>G</sub> =250nC:                |  |

|       |                                              |                           | _    | 175        | mA   | $V_{S} = 5.5V$                        |  |

|       |                                              |                           | _    | 175        |      | $V_S = 14V$                           |  |

|       |                                              |                           |      | 110        |      | $V_S = 17V$                           |  |

|       |                                              |                           |      | 110        |      | $V_S = 20V$                           |  |

| 4.2.7 | Supply current at Vs(device                  | $I_{Vs(o)}$               | _    | 60         | mA   | Vs=5.5V17V                            |  |

|       | disabled by ENA)                             | 15(5)                     |      | 50         |      | Vs=17V20V                             |  |

| 4.2.8 | Currrent into VDH (device not in sleep mode) | $I_{VDH}$                 |      | 1.5        | mA   | V <sub>VDH</sub> =5.520V<br>INH=high  |  |

<sup>2)</sup> Reflow profile IPC/JEDEC J-STD-020C

<sup>3)</sup> ESD susceptibility HBM according to EIA/JESD 22-A 114B

<sup>4)</sup> ESD susceptibility CDM according to EIA/JESD 22-C 101

#### **General Product Characteristics**

| Pos.   | Parameter                  | Symbol    | Limit Values |      | Limit Values |                | Unit | Conditions |

|--------|----------------------------|-----------|--------------|------|--------------|----------------|------|------------|

|        |                            |           | Min.         | Max. |              |                |      |            |

| 4.2.9  | Voltage difference CB2-VDH | $V_{CB2}$ | -0.3         | 25   | V            | Operation mode |      |            |

| 4.2.10 | Junction temperature       | $T_{j}$   | -40          | 150  | °C           |                |      |            |

- 1) max ratings for Tj has to be considered as well

- 2) For proper start up minimum Vs=6.5V is required

- 3) Duty cycle is referred to the high side input command (IHx); The duty cycles can be driven continuously and fully operational

- 4) total current consumption from power net (Vs and VDH)

Note: Within the functional range the IC operates as described in the circuit description. The electrical characteristics are specified within the conditions given in the related electrical characteristics table.

### 4.3 Default State of Inputs

Table 1 Default State of Inputs

| Characteristic                                              | State                                | Remark                             |

|-------------------------------------------------------------|--------------------------------------|------------------------------------|

| Default state of ILx (if ILx left open)                     | Low                                  | Low side MOSFETs off               |

| Default state of IHx (if IHx left open)                     | High                                 | High side MOSFETs off              |

| Default state of ENA (if ENA1 left open)                    | Low                                  | Device outputs disabled            |

| Default state of ENA (if ENA2 left open)                    | Low                                  | Device outputs disabled            |

| Default state of INH (if INH left open)                     | Low                                  | Sleep mode, I <sub>Q</sub> < 30 μA |

| Default State of sense amplifier output $V_O$ (ISP=ISN=0V)  | Zero ampere equivalent               | -                                  |

| Status of the device and the outputs when ENA1=ENA2=INH='1' | Device active and outputs functional | Vs=5.528V                          |

| Pull up or pull down integrated resistors Ixx, ENA          | 30kΩ+/-40%                           | -                                  |

| Pull down integrated resistor INH                           | 45kΩ+/-40%                           | _                                  |

Note: The load condition "C=22nF;  $R_{Load}$ =1 $\Omega$ " in the paragraph "Electrical characteristics / Dynamic characteristic" means that  $R_{Load}$  is connected between the output Gxx and the positive terminal of the C. The negative terminal of the C is connected to GND and the corresponding Sxx. The voltage is measured at the positive terminal of the C.

### 5 Description and Electrical Characteristics

#### 5.1 MOSFET Driver

### 5.1.1 Output Stages

The 3 low side and 3 high side powerful push-pull output stages of the TLE7183F are all floating blocks, each with its own source pin. This allows the direct connection of the output stage to the source of each single MOSFET, allowing a perfect control of each gate-source voltage even when 200A are driven in the bridge with rise and fall times clearly below 1µs.

All 6 output stages have the same output power and thanks to the used charge pump principle they can be switched all up to 30kHz.

Its output stages are powerful enough to drive MOSFETs with 400nC gate charge with approx. 150ns fall and rise times or even to run 12 MOSFETs with 200nC each with fall and rise times of approx. 150ns.

Maximum allowed power dissipation, max. junction temperature and the limited current capabilities of the charge pump limit the use for higher frequencies.

Each output stage has its own short circuit detection block. For more details about short circuit detection see **Chapter 5.2.1**.

Figure 3 Block Diagram of Driver Stages including Short Circuit Detection

### 5.1.2 Operation at Vs<12V - Integrated Charge Pumps

The TLE7183F provides a feature tailored to the requirements in 12V automotive applications. Often the operation of an application has to be assured even at 9V supply voltage or lower. Normally bridge driver ICs provide in such conditions clearly less than 9V to the gate of the external MOSFETs, increasing their R<sub>DSon</sub> and the associated power dissipation.

The TLE7183F has two charge pump circuitries for external capacitors.

The operation of the charge pumps is independent upon the pulse pattern of the MOSFETs.

The output of the charge pumps are regulated. The first charge pump doubles the supply voltage as long as it is below 8V. At 8V supply voltage and above, charge pump 1 regulates its output to 15V typically. Above 15V supply voltage, the output voltage of charge pump 1 will increase linearly. Yet, the output will not exceed 25V.

Charge pump 2 is regulated as well but it is pumped to the voltage on Vs. Normally VDH and Vs are in the same voltage range. The driver is not designed to have significant higher voltages at VDH compared to Vs. This would lead to reduced supply voltages for the high side output stages.

Charge pump 1 supplies the low side MOSFETS and output stages for the low side MOSFETs with sufficient voltage to assure 10V at the MOSFETs' gate even if the supply voltage is below 10V. Charge pump 2 supplies the output stages for the high side MOSFETs with sufficient voltage to assure 10V at the MOSFETs' gate. In addition, the charge pump 1 supplies most of the internal circuits of the driver IC, including charge pump 2. Output of charge pump 1 is the buffer capacitor CB1 which is referenced to GND.

Charge pump 2 supplies the high side MOSFETs and the output stages for the high side MOSFETs with sufficient voltage to assure 10V at the high side MOSFET gate. Output of charge pump 2 is buffer capacitor CB2 which is referenced to VDH.

This concept allows to drive all external MOSFETs in the complete duty cycle range of 0 to 100% without taking care about recharging of any bootstrap capacitors.

This simplifies the use in all applications especially in motor drives with block wise commutation.

The charge pumps are only deactivated when the device is put into sleep mode via INH.

During Start Up of the device it is not allowed to have any PWM patterns at the ILx and IHx pins until the charge pumps have ramped up to their final values or it is recommended to keep one ENAx pin low. So for proper Wake Up at  $V_{VsWU}$  the output stages of the driver IC have to be switched off or one ENAx pin has to kept low.

The size of the charge pump capacitors (pump capacitors CPx as well as buffer capacitors CBx) can be varied between 1  $\mu$ F and 4.7  $\mu$ F. Yet, larger capacitor values result in higher charge pump voltages and less voltage ripple on the charge pump buffer capacistors CBx (which supply the internal circuits as well as the external MOSFETs, pls. see above). Besides the capacitance values the ESR of the buffer capacitors CBx determines the voltage ripple as well. It is recommended to use buffer capacitors CBx that have small ESR.

Pls. see also Chapter 5.1.3 for capacitor selection.

#### 5.1.3 Sleep Mode

When the INH pin is set to low, the driver will be set to sleep mode. The INH pin switches off the complete supply structure of the device and leads finally to an undervoltage shut down of the complete driver. Enabling the device with the INH pin means to switch on the supply structure. The device will run through power on reset during wake up. It is recommended to perform a Reset by ENA after Wake up to remove possible ERR signals; Reset is performed by keeping one or more ENA pins low until the charge pump voltages have ramped up.

Enabling and disabling with the INH pin is not very fast. For fast enable / disable the ENA pin is recommended.

When the TLE 7183 F is in INH mode (INH is low) or when the supply voltage is not available on the Vs pin, then the driver IC is not supplied, the charge pumps are inactive and the charge pump capacitors are discharged. Pin CB2 (+ terminal of buffer capacitor 2) will decay to GND. When the battery voltage is still applied to VDH (- terminal of buffer capacitor 2) the buffer capacitor 2 will slowly charged to battery voltage, yet with reversed polarity compared to the polarity during regular operation. Hence, it is important to use a buffer capacitor 2 (CB2) that can

withstand both, +25 V during operation mode and  $-V_{BAT}$  during INH mode, e.g. a ceramic capacitor. In case of load dump during INH mode, the negative voltage across CB2 will be clamped to -31 V (CB2 referenced to VDH).

#### 5.1.4 Electrical Characteristics

#### **Electrical Characteristics MOSFET drivers - DC Characteristics**

| Pos.   | Parameter                                                     | Symbol             | Limit Values |      |                   | Unit | Conditions                         |

|--------|---------------------------------------------------------------|--------------------|--------------|------|-------------------|------|------------------------------------|

|        |                                                               |                    | Min.         | Тур. | Max.              |      |                                    |

| 5.1.1  | Low level output voltage                                      | $V_{G\_LL}$        | -            | _    | 0.2               | V    | I=30mA                             |

| 5.1.2  | High level output voltage, Low Side                           |                    | 7.5          | _    | 13                | V    | I=-2mA; Vs=5.58V                   |

| 5.1.3  | High level output voltage, High Side                          | $V_{G\_HL}$        | 6.5          | _    | 13                | V    | I=-2mA; Vs=5.58V                   |

| 5.1.4  | High level output voltage                                     | $V_{G\_HL}$        | 9            | _    | 13                | V    | I=-2mA; Vs=820V                    |

| 5.1.5  | High level output voltage difference                          | $dV_{G\_H}$        | _            | _    | 1.0               | V    | I=-100mA; Vs=20V                   |

| 5.1.6  | Gate drive output voltage (device disabled via ENAx)          | $V_{G(DIS)}$       | -            | -    | 0.2               | V    | Disabled;<br>Vs=5.520V;<br>I=10mA  |

| 5.1.7  | Gate drive output voltage Tj=-40°C Tj=25°C Tj=150°C           | $V_{\mathrm{G_5}}$ | -            | _    | 1.4<br>1.2<br>1.0 | V    | UVLO; Vs<=5.5V                     |

| 5.1.8  | Gate drive output voltage high side Tj=-40°C Tj=25°C Tj=150°C | $V_{G\_HS}$        | -            | -    | 1.4<br>1.2<br>1.0 | V    | Overvoltage                        |

| 5.1.9  | Gate drive output voltage low side                            | $V_{G\_LS}$        | -            | _    | 0.2               | V    | Overvoltage                        |

| 5.1.10 | Low level input voltage of Ixx, ENAx                          | $V_{I\_LL}$        | _            | _    | 1.0               | V    | _                                  |

| 5.1.11 | High level input voltage of lxx, ENAx                         | $V_{I\_HL}$        | 2.0          | _    | _                 | V    | -                                  |

| 5.1.12 | Low level input voltage of INH                                | $V_{I\_LL}$        | _            | _    | 0.75              | V    | _                                  |

| 5.1.13 | High level input voltage of INH                               | $V_{I\_HL}$        | 2.1          | _    | _                 | V    | _                                  |

| 5.1.14 | Input hysteresis of IHx, ILx, ENAx                            | $dV_1$             | 50           | _    | _                 | mV   | Vs=5.58V                           |

| 5.1.15 | Input hysteresis of IHx, ILx, ENAx                            | $dV_1$             | 100          | 200  |                   | mV   | Vs=820V                            |

| 5.1.16 | Output bias current SHx                                       | $I_{SHx}$          | 0.3          | 1.0  | 1.6               | mA   | VSHx=0(Vs+1);<br>ILx=low; IHx=high |

| 5.1.17 | Output bias current SLx                                       | $I_{SLx}$          | 0.3          | 1.0  | 1.6               | mA   | VSLx=07V;<br>ILx=low; IHx=high     |

### **Electrical Characteristics MOSFET drivers - Dynamic Characteristics**

| Pos.   | Parameter                                                                                                                        | Symbol                |                              | Limit Val                    | ues                          | Unit | Conditions                                                                                                                      |

|--------|----------------------------------------------------------------------------------------------------------------------------------|-----------------------|------------------------------|------------------------------|------------------------------|------|---------------------------------------------------------------------------------------------------------------------------------|

|        |                                                                                                                                  |                       | Min.                         | Тур.                         | Max.                         |      |                                                                                                                                 |

| 5.1.18 | Min. internal dead time                                                                                                          | t <sub>DT_MIN</sub>   | 50                           | _                            | 200                          | ns   | DT pin to GND $(R_{DT}=0\Omega)$                                                                                                |

| 5.1.19 | Programmable internal dead time                                                                                                  | $t_{DT}$              | 0.26<br>0.64<br>1.07<br>2.02 | 0.41<br>1.05<br>1.85<br>3.82 | 0.56<br>1.45<br>2.63<br>5.62 | μs   | $R_{DT}$ =10 kΩ $R_{DT}$ =47 kΩ $R_{DT}$ =100 kΩ $R_{DT}$ =1000 kΩ                                                              |

| 5.1.20 | Max. internal dead time                                                                                                          | $t_{DT\_MAX}$         | 2.33                         | _                            | 6.35                         | μs   | DT pin open                                                                                                                     |

| 5.1.21 | Turn on current, peak                                                                                                            | $I_{G(on)}$           | _                            | 0.8                          | _                            | A    | $VGxx-VSxx=0V; \\ Vs=5.58V; \\ C=22nF; \\ R_{Load}=1\Omega$                                                                     |

| 5.1.22 | Turn on current, peak                                                                                                            | $I_{G(on)}$           | _                            | 1.5                          | _                            | A    | $VGxx-VSxx=0V; \\ Vs=820V \\ C=22nF; \\ R_{Load}=1\Omega$                                                                       |

| 5.1.23 | Turn off current, peak                                                                                                           | $I_{G(off)}$          | _                            | 1.5                          | _                            | A    | $ \begin{array}{l} \text{VGxx-VSxx=10V;} \\ \text{Vs=820V} \\ \text{C=22nF;} \\ \text{R}_{\text{Load}} = 1 \Omega \end{array} $ |

| 5.1.24 | Rise time (20-80%)<br>$T_{\rm j} = -40^{\circ}\text{C}$<br>$T_{\rm j} = 25^{\circ}\text{C}$<br>$T_{\rm i} = 150^{\circ}\text{C}$ | $t_{	extsf{G\_rise}}$ | _                            | 150                          | 400<br>400<br>700            | ns   | C=22nF; R <sub>Load</sub> =1Ω                                                                                                   |

| 5.1.25 | Fall time (20-80%) $T_{\rm j} = -40^{\circ}\text{C}$ $T_{\rm j} = 25^{\circ}\text{C}$ $T_{\rm j} = 150^{\circ}\text{C}$          | $t_{G\_fall}$         | -                            | 150                          | 230<br>230<br>500            | ns   | C=22nF; $R_{Load}$ =1 $\Omega$                                                                                                  |

| 5.1.26 | Input propagation time (low on)                                                                                                  | $t_{P(ILN)}$          | 90                           | 190                          | 290                          | ns   | C=22nF; $R_{Load}$ =1 $\Omega$                                                                                                  |

| 5.1.27 | Input propagation time (low off)                                                                                                 | $t_{P(ILF)}$          | 0                            | 100                          | 200                          | ns   | C=22nF; $R_{Load}$ =1 $\Omega$                                                                                                  |

| 5.1.28 | Input propagation time (high on)                                                                                                 | $t_{\mathrm{P(IHN)}}$ | 90                           | 190                          | 290                          | ns   | C=22nF; $R_{Load}$ =1 $\Omega$                                                                                                  |

| 5.1.29 | Input propagation time (high off)                                                                                                | $t_{\mathrm{P(IHF)}}$ | 0                            | 100                          | 200                          | ns   | C=22nF; $R_{Load}$ =1 $\Omega$                                                                                                  |

| 5.1.30 | Absolute input propagation time difference (all channels turn on)                                                                | $t_{P(an)}$           | _                            | _                            | 70                           | ns   | C=22nF; $R_{Load}$ =1 $\Omega$                                                                                                  |

| 5.1.31 | Absolute input propagation time difference (all channels turn off)                                                               | $t_{P(af)}$           | _                            | _                            | 50                           | ns   | C=22nF; $R_{Load}$ =1 $\Omega$                                                                                                  |

| 5.1.32 | Absolute input propagation time difference (1channel high off - low on)                                                          | t <sub>P(1hfln)</sub> | _                            | -                            | 150                          | ns   | C=22nF; $R_{Load}$ =1 $\Omega$                                                                                                  |

| 5.1.33 | Absolute input propagation time difference (1channel low off - high on)                                                          | t <sub>P(1lfhn)</sub> | _                            | -                            | 150                          | ns   | C=22nF; $R_{Load}$ =1 $\Omega$                                                                                                  |

#### **Electrical Characteristics MOSFET drivers - Dynamic Characteristics**

| Pos.   | Parameter                                                                  | Symbol                 | Limit Values |      |      | Unit | Conditions                                                               |

|--------|----------------------------------------------------------------------------|------------------------|--------------|------|------|------|--------------------------------------------------------------------------|

|        |                                                                            |                        | Min.         | Тур. | Max. |      |                                                                          |

| 5.1.34 | Absolute input propagation time difference (all channel high off - low on) | $t_{P(ahfln)}$         | _            | _    | 150  | ns   | C=22nF; $R_{Load}$ =1 $\Omega$                                           |

| 5.1.35 | Absolute input propagation time difference (all channel low off - high on) | $t_{P(alfhn)}$         | _            | -    | 150  | ns   | C=22nF; $R_{Load}$ =1 $\Omega$                                           |

| 5.1.36 | Wake up time; INH low to high                                              | t <sub>INH_Pen</sub>   | -            | -    | 20   | ms   | Driver fully functional;<br>Vs=6.58V;<br>ENAx=low;<br>CPx=CBx=4.7µF      |

| 5.1.37 | Wake up time; INH low to high                                              | t <sub>INH_Pen</sub>   | _            | _    | 10   | ms   | Driver fully functional; VS=820V; ENAx=low; CPx=CBx=4.7µF;               |

| 5.1.38 | Wake up time logic functions; INH low to high                              | $t_{INH\_log}$         | _            | _    | 10   | ms   | diagnostic, OpAmp<br>working;<br>Vs=6.58V;<br>ENAx=low;<br>CPx=CBx=4.7µF |

| 5.1.39 | Wake up time logic functions; INH low to high                              | $t_{INH\_log}$         | _            | -    | 5    | ms   | diagnostic, OpAmp<br>working;<br>VS=820V;<br>ENAx=low;<br>CPx=CBx=4.7µF  |

| 5.1.40 | INH propagation time to disable the output stages                          | t <sub>INH_P(O)</sub>  | _            | _    | 10   | μs   | Vs=5.58V                                                                 |

| 5.1.41 | INH propagation time to disable the output stages                          | t <sub>INH_P(O)</sub>  | -            | _    | 8    | μs   | Vs=820V                                                                  |

| 5.1.42 | INH propagation time to disable the entire driver IC                       | t <sub>INH_P(IC)</sub> | _            | _    | 300  | μs   | _                                                                        |

| 5.1.43 | Supply voltage V <sub>s</sub> for Wake up                                  | $V_{ m VsWU}$          | 6.5          | _    | -    | V    | diagnostic, OpAmp working;                                               |

| 5.1.44 | Charge pump frequency                                                      | $f_{\sf CP}$           | 38           | 55   | 72   | kHz  | _                                                                        |

### 5.2 Protection and Diagnostic Functions

#### 5.2.1 Short Circuit Protection

The TLE7183F provides a short circuit protection for the external MOSFETs. It is a monitoring of the drain-source voltage of the external MOSFETs. As soon as this voltage is higher than the short circuit detection limit, a timer will start to run.

The short circuit detection level is programmed fix in the chip. 5 different short circuit level options are available:

Table 2 Short circuit detection level options

| TLE7183 | typ. short ciruit detection level |

|---------|-----------------------------------|

| SCD1    | 0.5V                              |

| SCD2    | 0.75V                             |

| SCD3    | 1.0V                              |

| SCD4    | 1.5V                              |

| SCD5    | 2.0V                              |

After a delay of about 6 µs all external MOSFETs will be switched off until the driver is reset by the ENAx pin. The error flag is set.

The drain-source voltage monitoring of the short circuit detection for a certain external MOSFET is active as soon as the corresponding input is set to "on" and the dead time is expired.

### 5.2.2 Overcurrent Warning

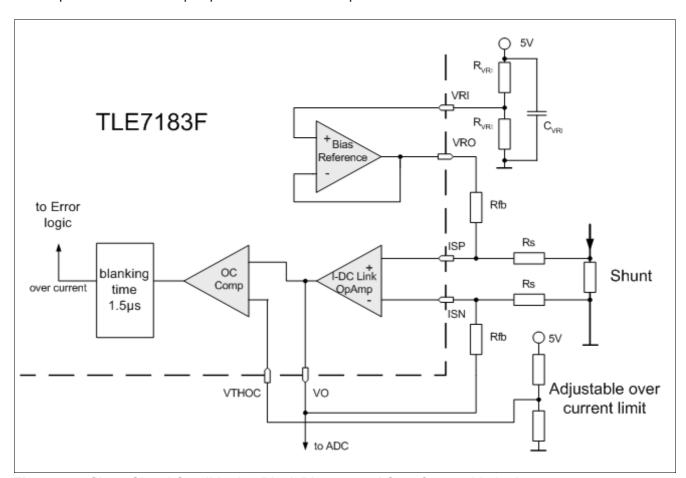

The TLE7183F offers the possibility to shut down the output stages if a current threshold is reached. (see **Figure 4** ). The output of the current sense OpAmp is connected to an integrated comparator, comparing the amplified current sense signal with an external adjustable threshold value. After the comparator a blanking time (1.5 µs typ.) is implemented to avoid false triggering caused by overswing of the current sense signal.

If the overcurrent situation is detected, only an error signal is given. During overcurrent the driver IC works normally. The error signal disappears as soon as the current decreases below the overcurrent limit set on the VTHOC pin. The error signal disappears as well when the current commutates from the low side MOSFET to the associated high side MOSFET (no current through the shunt resistor).

It is the decision of the user to react on the over current signal by modifying the Ixx patterns to lower the current.

### 5.2.3 Dead Time and Shoot Through Protection

In bridge applications it has to be assured that the external high side and low side Mosfet are not "on" at the same time, connecting directly the battery voltage to GND. The dead time generated in the TLE7183F is fixed to a minimum value of 50..200ns if the DT pin is connected to GND. This function assures a minimum dead time if the input signals coming from the  $\mu$ C are faulty.

The dead time can be increased beyond the internal fixed dead time by connecting the DT pin via a dead time resistor  $R_{DT}$  to GND - the larger the dead time resistor the larger the dead time (for details pls. see the "Dynamic Characteristic" table in the MOSFET driver section).

The exact dead time of the bridge is usually controlled by the PWM generation unit of the  $\mu C$ .

In addition to this dead time, the TLE7183F provides a locking mechanism, avoiding that both external MOSFETs of one half bridge can be switched on at the same time. This functionality is called shoot through protection.

If the command to switch on both high and low side switches in the same half bridge is given at the input pins, the command will be ignored.

### 5.2.4 Undervoltage Shut Down

The TLE7183F has an integrated undervoltage shut down, to assure that the behavior of the device is predictable in all supply voltage ranges.

If the voltage of a charge pump buffer capacitors CBx reaches the undervoltage shut down level for a minimum specified filter time, the gate-source voltage of all external MOSFETs will be actively pulled to low. In this situation the short circuit detection of this output stage is deactivated to avoid a latching shut down of the driver.

As soon as the charge pump buffer voltage recovers, the output stage condition will be aligned to the input patterns automatically. This allows to continue operation of the motor in case of undervoltage shut down without a reset by the  $\mu$ C.

Undervoltage shut down will not occur when  $V_S > 6$  V,  $Q_G < 250$  nC,  $F_{PWM} < 25$  kHz, and the charge pump capacitors  $Cxx = 4.7 \, \mu F$ .

#### 5.2.5 Overvoltage Shut Down

The TLE7183F has an integrated overvoltage shut down to avoid destruction of the IC at high supply voltages. The voltage is observed at the Vs and the VDH pin. When one of them or all of them exceed the overvoltage shut down level for more than the specified filter time then the external MOSFETs are switched off. In addition, overvoltage will shut down the charge pumps and will discharge the charge pump capacitors. This results in an undervoltage condition which will be indicated on the ERRx pins. During overvoltage shut down the external MOSFETs and the charge pumps remain off until a reset is performed.

### 5.2.6 Overtemperature Warning

If the junction temperature is exceeding typ. 170°C an error signal is given as warning. The driver IC will continue to operate in order not to disturb the application.

The warning is removed automatically when the junction temperature is cooling down.It is in the responsibility of the user to protect the device against overtemperature destruction.

#### **5.2.7 ERR Pins**

The TLE7183F has two status pins to provide diagnostic feedback to the  $\mu$ C. The outputs of these pins are 5V push pull stages, they are either high or low.

Table 3 Overview of error conditions

| ERR1 | ERR2 | Driver conditions                      |

|------|------|----------------------------------------|

| Low  | Low  | no errors                              |

| High | Low  | Overtemperature or overvoltage         |

| High | High | Undervoltage                           |

| Low  | High | Short circuit detection or overcurrent |

#### Table 4 Behaviour at different error conditions

| Error condition         | restart behavior                           | Shuts down                  |

|-------------------------|--------------------------------------------|-----------------------------|

| Short circuit detection | Latch, reset must be performed at ENAx pin | All external Power -MOSFETs |

| Overcurrent warning     | Self clearing                              | Nothing                     |

| Undervoltage            | Auto restart                               | All external Power -MOSFETs |

| Overvoltage             | Latch, reset must be performed at ENAx pin | All external Power -MOSFETs |

| Overtemperature warning | Self clearing                              | Nothing                     |

Note: All errors do NOT lead to sleep mode. Sleep mode is only initiated with the INH pin. The latch and restart behaviour allows to distinguish between the different error types combined at the ERR signals.

#### Table 5 Priorisation of Errors

| Priority | Error                          |

|----------|--------------------------------|

| 1        | Short circuit detection        |

| 2        | Undervoltage detection         |

| 3        | Overvoltage detection          |

| 4        | Overtemperature<br>Overcurrent |

#### Reset of ERROR registers and Disable

The TLE7183F can be reseted by the enable pins ENAx. If one or two ENAx pins is pulled to low for a specified minimum time, the error registers are cleared and the external MOSFETs are switched off actively.

During disable only the errors undervoltage shut down and overtemperature warning are shown. Other errors are not displayed.

#### 5.2.8 Electrical Characteristics

#### **Electrical Characteristics - Protection and diagnostic functions**

| Pos.    | Parameter                                                       | Symbol               | Limit Values |      |      | Unit | Conditions                                            |

|---------|-----------------------------------------------------------------|----------------------|--------------|------|------|------|-------------------------------------------------------|

|         |                                                                 |                      | Min.         | Тур. | Max. |      |                                                       |

| Overte  | mperature                                                       |                      |              |      | · ·  | "    | 1                                                     |

| 5.2.1   | Overtemperature warning                                         | $T_{\rm j(OW)}$      | 150          | 170  | 190  | °C   | _                                                     |

| 5.2.2   | Hysteresis for overtemperature warning                          | $dT_{\rm j(OW)}$     | _            | 20   | _    | °C   | -                                                     |

| Overcu  | irrent warning                                                  | 1                    |              |      |      |      | <u> </u>                                              |

| 5.2.3   | Overcurrent threshold                                           | $V_{THOC}$           | 2            | _    | 4.5  | V    | Vs=5.58V                                              |

| 5.2.4   | Overcurrent threshold                                           | $V_{THOC}$           | 2            | _    | 4.8  | V    | Vs=820V                                               |

| 5.2.5   | Input offset voltage of OC Comp                                 | $V_{OCOF}$           | -50          | _    | 50   | mV   | _                                                     |

| 5.2.6   | Input offset voltage temperature drift of OC Comp <sup>1)</sup> | $V_{IO}$             | -5           | _    | 5    | mV   | -                                                     |

| 5.2.7   | Over current protection threshold hysteresis                    | $dV_{\mathrm{THOC}}$ | 25           |      | _    | mV   | Vs=5.58V                                              |

| 5.2.8   | Over current protection threshold hysteresis                    | $dV_{\mathrm{THOC}}$ | 50           | 80   | _    | mV   | Vs=820V                                               |

| 5.2.9   | Filter time of over current protection                          | $t_{\rm OC}$         | 1.0          | 1.5  | 3.0  | μs   |                                                       |

| Short o | ircuit protection                                               |                      |              |      |      | "    | 1                                                     |

| 5.2.10  | Filter time of short circuit protection                         | $t_{SCP(off)}$       | 4.5          | 6.8  | 9    | μs   | default                                               |

| 5.2.11  | Maximum duty cycle for no SCD <sup>2)</sup>                     | $D_{ySCDmax}$        | -            | -    | 6    | %    | fPWM=20kHz a<br>IHx or ILx and a<br>static applied S0 |

| 5.2.12  | minimum duty cycle for periodic SCD <sup>2)</sup>               | $D_{ySCDmin}$        | 13           | _    | -    | %    | fPWM=20kHz a IHx or ILx and a static applied S0       |

#### Electrical Characteristics - Protection and diagnostic functions (cont'd)

| Pos.    | Parameter                                        | Symbol                   | Limit Values |      |      | Unit | Conditions               |

|---------|--------------------------------------------------|--------------------------|--------------|------|------|------|--------------------------|

|         |                                                  |                          | Min.         | Тур. | Max. |      |                          |

| 5.2.13  | Short circuit protection detection level SCD1    | $V_{\mathrm{SCP1(off)}}$ | 0.3          | 0.5  | 0.65 | V    |                          |

| 5.2.14  | Short circuit protection detection level SCD2    | $V_{\mathrm{SCP2(off)}}$ | 0.6          | 0.75 | 0.9  | V    |                          |

| 5.2.15  | Short circuit protection detection level SCD3    | $V_{\mathrm{SCP3(off)}}$ | 0.85         | 1.0  | 1.15 | V    |                          |

| 5.2.16  | Short circuit protection detection level SCD4    | $V_{\mathrm{SCP4(off)}}$ | 1.35         | 1.5  | 1.65 | V    |                          |

| 5.2.17  | Short circuit protection detection level SCD5    | $V_{\mathrm{SCP5(off)}}$ | 1.8          | 2.0  | 2.2  | V    |                          |

| ERR pir | ıs                                               | •                        | •            | •    |      | •    |                          |

| 5.2.18  | High level output voltage of ERRx                | $V_{OHERR}$              | 4.0          | _    | 5.2  | V    | I= -0.2mA                |

| 5.2.19  | Low level output voltage of ERRx                 | $V_{OLERR}$              | -0.1         | _    | 0.4  | V    | I= 0.2mA                 |

| 5.2.20  | Propagation time difference ERR1 to ERR2         | $t_{\rm PD(ERR)}$        |              | _    | 200  | ns   | _                        |

| 5.2.21  | Rise time ERRx (20 - 80 %)                       | $t_{r(ERR)}$             | 50           | _    | 600  | ns   | C <sub>LOAD</sub> =100pF |

| 5.2.22  | Fall time ERRx (80 - 20 %)                       | $t_{f(ERR)}$             | 50           | _    | 400  | ns   | C <sub>LOAD</sub> =100pF |

| Over- a | nd undervoltage                                  |                          |              |      | *    |      |                          |

| 5.2.23  | Overvoltage shut down                            | $V_{\mathrm{OV(off)}}$   | 28           | _    | 33   | V    | on Vs and/or VDH         |

| 5.2.24  | Overvoltage filter time                          | $t_{\sf OV}$             | 30           | _    | 65   | μs   | _                        |

| 5.2.25  | Undervoltage shut down CB1                       | $V_{UV1}$                | 6.75         | _    | 8.25 | V    | CB1 to GND               |

| 5.2.26  | Undervoltage shut down CB2                       | $V_{UV2}$                | 3.9          | _    | 5.7  | V    | CB2 to VDH               |

| 5.2.27  | Undervoltage shut down hysteresis of CB1 and CB2 | $V_{DUV}$                | _            | 1.0  | _    | V    | -                        |

| 5.2.28  | Undervoltage filter time                         | $t_{\sf UV}$             | 1            | _    | 3    | μs   | _                        |

| Reset a | nd Enable                                        | •                        |              | "    |      |      |                          |

| 5.2.29  | Reset time to clear ERR registers                | $t_{Res1}$               | 2.0          | _    | _    | μs   | _                        |

| 5.2.30  | Low time of ENAx signal without reset            | $t_{Res0}$               | _            | _    | 0.5  | μs   | -                        |

| 5.2.31  | ENAx propagation time (High> Low)                | t <sub>PENA_H-L</sub>    | _            | _    | 2.0  | μs   | -                        |

| 5.2.32  | ENAx propagation time (Low> High)                | $t_{PENA\_L-H}$          | _            | _    | 0.5  | μs   | _                        |

| 5.2.33  | Return time to normal operation at auto-restart  | $t_{AR}$                 | _            | -    | 1.0  | μs   | _                        |

<sup>1)</sup> Not subject to production test; specified by design

<sup>2)</sup> Parameters describe the behaviour of the internal SCD circuit. Therefore only internal delay times are considered. In application dead-/ delay times determined by application circuit (switching times of MOSFETs, adjusted dead time) have to be considered as well.

### 5.3 Shunt Signal Conditioning

The TLE7183F incorporates a fast and precise operational amplifier for conditioning and amplification of the current sense shunt signal. Additionally, one reference bias buffer is integrated to provide an adjustable bias reference for the three OpAmps. The voltage devider on the VRI pin should be less than 50 kOhm, the filtering capacitor less than 1.2  $\mu$ F - if needed at all. The gain of the OpAmp is adjustable by external resistors within a range of 5 to 15.

When V(ISP) = V(ISN), VO provides the reference voltage VRO. VRO is normally half of the regulated voltage provided from an external voltage regulator for the ADC used to read the current sense signal. The additional buffer allows bi-directional current sensing and permits the adaptation of the reference bias to different  $\mu$ C I/O voltages. The reference buffer assures a stable reference voltage even in the high frequency range.

The output of the I-DC link Opamp Vo is not short-circuit proof.

Figure 4 Shunt Signal Conditioning Block Diagram and Over Current Limitation

Over current warning see Chapter 5.2.2.

#### 5.3.1 Electrical Characteristics

#### **Electrical Characteristics - Current sense signal conditioning**

| Pos.   | Parameter                                                                         | Symbol                           | Limit Values |              |              | Unit | Conditions                                                            |

|--------|-----------------------------------------------------------------------------------|----------------------------------|--------------|--------------|--------------|------|-----------------------------------------------------------------------|

|        |                                                                                   |                                  | Min.         | Тур.         | Max.         |      |                                                                       |

| 5.3.1  | Series resistors                                                                  | $R_{S}$                          | 100          | 500          | 1000         | Ω    | _                                                                     |

| 5.3.2  | Feedback resistor Limited by the output voltage dynamic range                     | $R_{fb}$                         | 2000         | 7500         | _            | Ω    | -                                                                     |

| 5.3.3  | Resistor ratio (gain ratio)                                                       | $R_{\mathrm{fb}}/R_{\mathrm{S}}$ | 5            | _            | 15           | _    | _                                                                     |

| 5.3.4  | Steady state differential input voltage range across VIN <sup>1)</sup>            | $V_{IN(ss)}$                     | -400         | _            | 400          | mV   | -                                                                     |

| 5.3.5  | Transient differential input voltage range across VIN                             | V <sub>IN(tr)</sub>              | -800         | _            | 800          | mV   | _                                                                     |

| 5.3.6  | Input differential voltage (ISP - ISN)                                            | $V_{IDR}$                        | -800         | _            | 800          | mV   | _                                                                     |

| 5.3.7  | Input voltage (Both Inputs - GND) (ISP - GND) or (ISN -GND)                       | $V_{LL}$                         | -800         | -            | 1500         | mV   | Vs=5.58V                                                              |

| 5.3.8  | Input voltage (Both Inputs - GND) (ISP - GND) or (ISN -GND)                       | $V_{LL}$                         | -800         | -            | 2000         | mV   | Vs=820V                                                               |

| 5.3.9  | Input offset voltage of the I-DC link OpAmp                                       | V <sub>IO</sub>                  | _            | 1            | +/-5         | mV   | $R_S = 500\Omega; V_{CM} = 0V;$<br>$V_O = 1.65V;$<br>$V_{RI} = 1.65V$ |

| 5.3.10 | Input offset voltage temperature drift of the I-DC link OpAmp <sup>2)</sup>       | $V_{IO}$                         | _            | 1            | 2            | mV   | $R_S = 500\Omega; V_{CM} = 0V;$<br>$V_O = 1.65V;$<br>$V_{RI} = 1.65V$ |

| 5.3.11 | Input offset voltage of the reference buffer                                      | $V_{IO}$                         |              | 1            | +/-5         | mV   | -                                                                     |

| 5.3.12 | Input offset voltage temperature drift of the reference buffer <sup>2)</sup>      | $V_{IO}$                         |              | 1            | 2            | mV   | -                                                                     |

| 5.3.13 | Input range at VRI                                                                | $V_{IO}$                         | 1.2          | _            | 2.8          | V    | _                                                                     |

| 5.3.14 | Input bias current (ISx to GND)                                                   | $I_{IB}$                         | _            | _            | 300          | μΑ   | V <sub>CM</sub> =0V; V <sub>O</sub> =open                             |

| 5.3.15 | High level output voltage of VO                                                   | $V_{OH}$                         | 4.8          | _            | 5.2          | V    | V <sub>RI</sub> =1.65V/2.5V;<br>I <sub>OH</sub> =-3mA                 |

| 5.3.16 | Low level output voltage of VO                                                    | $V_{OL}$                         | -0.1         | _            | 0.2          | V    | V <sub>RI</sub> =1.65V/2.5V;<br>I <sub>OH</sub> =3mA                  |

| 5.3.17 | Output voltage of VO <sup>3)</sup> V <sub>RI</sub> = 2.5V, V <sub>RI</sub> =1.65V | $V_{OR}$                         | 2.42<br>1.58 | 2.50<br>1.65 | 2.58<br>1.73 | V    | V <sub>IN(SS)</sub> =0V;<br>Gain=15;                                  |

| 5.3.18 | Temperature drift of output voltage of VO <sup>3)</sup>                           | $V_{O}$                          | 0            | _            | 32           | mV   | V <sub>IN(SS)</sub> =0V;<br>Gain=15                                   |

| 5.3.19 | Output short circuit current                                                      | $I_{SC}$                         | 5            | _            | _            | mA   | _                                                                     |

| 5.3.20 | Differential input resistance <sup>2)</sup>                                       | $R_{I}$                          | 100          | _            | _            | kΩ   | _                                                                     |

| 5.3.21 | Common mode input capacitance <sup>2)</sup>                                       | $C_{CM}$                         | -            | _            | 10           | pF   | 10kHz                                                                 |

### Electrical Characteristics - Current sense signal conditioning (cont'd)

| Pos.   | Parameter                                                                                                                 | Symbol             |      | Limit Val      | ues  | Unit | Conditions                                                                                   |

|--------|---------------------------------------------------------------------------------------------------------------------------|--------------------|------|----------------|------|------|----------------------------------------------------------------------------------------------|

|        |                                                                                                                           |                    | Min. | Тур.           | Max. |      |                                                                                              |

| 5.3.22 | Common mode rejection ratio at DC CMRR = 20*Log((Vout_diff/Vin_diff) * (Vin_CM/Vout_CM))                                  | CMRR               | 80   | 100            | -    | db   | -                                                                                            |

| 5.3.23 | Common mode suppression <sup>4)</sup> with<br>CMS = 20*Log(Vout_CM/Vin_CM)<br>Freq =100kHz<br>Freq = 1MHz<br>Freq = 10MHz | CMS                | _    | 62<br>43<br>33 | _    | db   | VIN=360mV* sin( $2^*\pi^*$ freq*t); Rs=500 $\Omega$ ; Rfb=7500 $\Omega$ ; VRI=1.65/2.5V      |

| 5.3.24 | Slew rate                                                                                                                 | dV/dt              | 3    | 10             | -    | V/µs | Gain>= 5;<br>$R_L$ =1.0 $k\Omega$ ;<br>$C_L$ =500pF                                          |

| 5.3.25 | Large signal open loop voltage gain (DC)                                                                                  | $A_{OL}$           | 80   | 100            | _    | dB   | -                                                                                            |

| 5.3.26 | Unity gain bandwidth                                                                                                      | GBW                | 10   | 20             | _    | MHz  | $R_L=1k\Omega$ ; $C_L=100pF$                                                                 |

| 5.3.27 | Phase margin <sup>2)</sup>                                                                                                | $ \Phi_{M} $       | _    | 50             | _    | 0    | Gain>= 5;<br>$R_L=1k\Omega$ ; $C_L=100pF$                                                    |

| 5.3.28 | Gain margin <sup>2)</sup>                                                                                                 | $A_{M}$            | _    | 12             | _    | db   | $R_L=1k\Omega$ ; $C_L=100pF$                                                                 |

| 5.3.29 | Bandwidth                                                                                                                 | $BW_G$             | 1.6  | _              | _    | MHz  | Gain=15;<br>$R_L$ =1kΩ;<br>$C_L$ =500pF;<br>$R_s$ =500Ω                                      |

| 5.3.30 | Output settle time to 98% 1)                                                                                              | t <sub>set</sub>   | _    | 1              | 1.8  | μs   | Gain=15;<br>$R_L$ =1kΩ;<br>$C_L$ =500pF;<br>0.3 <vo< 4.8v;<br=""><math>R_s</math>=500Ω</vo<> |

| 5.3.31 | Output rise time 10% to 90% <sup>1)</sup>                                                                                 | t <sub>Irise</sub> | -    | _              | 1    | μs   | Gain=15;<br>$R_L$ =1kΩ; $C_L$ =500pF;<br>0.3 <vo< 4.8v;<br=""><math>R_s</math>=500Ω</vo<>    |

| 5.3.32 | Output fall time 90% to 10% <sup>1)</sup>                                                                                 | t <sub>Ifall</sub> | -    | _              | 1    | μs   | Gain=15;<br>$R_L$ =1kΩ; $C_L$ =500pF;<br>0.3 <vo< 4.8v;<br=""><math>R_s</math>=500Ω;</vo<>   |

<sup>1)</sup> Input current and output amplifier characteristics:

<sup>&</sup>quot;Output signal must be amplified and available at 2µs after input signal change (Gain 5...15)

<sup>2)</sup> Not subject to production test; specified by design

<sup>3)</sup> calculated out of **5.3.9**, **5.3.10**, **5.3.11** and **5.3.12**

<sup>4)</sup> Without considering any offsets such as input offset voltage, internal miss match and assuming no tolerance error in external resistors.

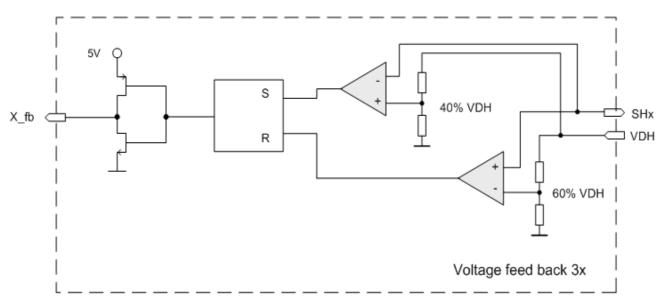

### 5.4 Phase voltage feedback

The TLE7183F incorporates an fast conversion of the phase voltages into logic signals. The threshold values are proportional to  $V_{DH}$ . The outputs are 5V push pull stages. When they are not used they can be left open.

Figure 5 Block diagram phase voltage feedback

#### 5.4.1 Electrical Characteristics

#### **Electrical Characteristics - Phase Voltage Feedback**

| Pos.  | Parameter                                      | Symbol      | Limit Values |      |      | Unit        | Conditions                              |

|-------|------------------------------------------------|-------------|--------------|------|------|-------------|-----------------------------------------|

|       |                                                |             | Min.         | Тур. | Max. |             |                                         |

| 5.4.1 | Low level threshold                            | $V_{ILfb}$  | 35           | 40   | 45   | % of<br>VDH | VDH>5.5V<br>V <sub>SHX</sub> decreasing |

| 5.4.2 | High level threshold                           | $V_{IHfb}$  | 55           | 60   | 65   | % of<br>VDH | VDH>5.5V<br>V <sub>SHX</sub> decreasing |