# Please note that Cypress is an Infineon Technologies Company.

The document following this cover page is marked as "Cypress" document as this is the company that originally developed the product. Please note that Infineon will continue to offer the product to new and existing customers as part of the Infineon product portfolio.

# **Continuity of document content**

The fact that Infineon offers the following product as part of the Infineon product portfolio does not lead to any changes to this document. Future revisions will occur when appropriate, and any changes will be set out on the document history page.

# **Continuity of ordering part numbers**

Infineon continues to support existing part numbers. Please continue to use the ordering part numbers listed in the datasheet for ordering.

www.infineon.com

# THIS SPEC IS OBSOLETE

Spec No: 001-53516

Spec Title: CY8C20111/CY8C20121, CAPSENSE(R)

EXPRESS(TM) - ONE BUTTON AND TWO BUTTON CAPACITIVE CONTROLLERS

Replaced by: NONE

# CapSense<sup>®</sup> Express™ – One Button and Two Button Capacitive Controllers

#### **Features**

- Capacitive button input tied to a configurable output

- □ Robust sensing algorithm

- ☐ High sensitivity, low noise

- Immunity to RF and AC noise

- □ Low radiated EMC noise

- □ Supports wide range of input capacitance, sensor shapes, and sizes

- Target Applications

- □ Printers

- Cellular handsets

- □ LCD monitors

- □ Portable DVD players

- Industry's best configurability

- Custom sensor tuning

- Output supports strong 20 mA sink current

- □ Output state can be controlled through I<sup>2</sup>C or directly from CapSense input state

- ☐ Run time reconfigurable over I<sup>2</sup>C

- Advanced features

- □ Plug-and-play with factory defaults tuned to support up to 1 mm overlay

- Nonvolatile storage of custom settings

- Easy integration into existing products configure output to match system

- □ No external components required

- □ World class free configuration tool

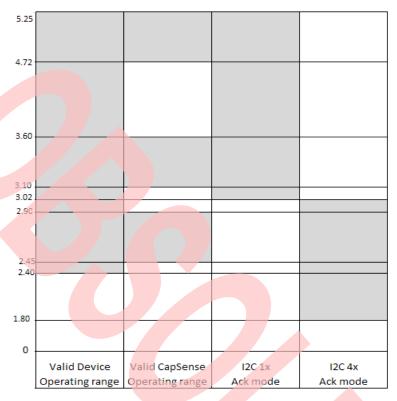

- Wide range of operating voltages

- □ 2.45 V to 2.9 V

- □ 3.10 V to 3.6 V

- □ 4.75 V to 5.25 V

- I<sup>2</sup>C communication

- □ Supported from 1.8 V

- □ Internal pull-up resistor support option

- □ Data rate up to 400 kbps.

- □ Configurable I<sup>2</sup>C addressing

- Industrial temperature range: -40 °C to +85 °C

- Available in 8-pin SOIC package

#### Overview

The CapSense<sup>®</sup> Express™ controllers support two capacitive sensing (CapSense) buttons and two general purpose outputs in CY8C20121 and one CapSense button and one general purpose output in CY8C20111. The device functionality is configured through the I<sup>2</sup>C port and can be stored in on-board nonvolatile memory for automatic loading at power on. The digital outputs are controlled from CapSense inputs in factory default settings, but are user configurable for direct control through I<sup>2</sup>C.

The four key blocks that make up the CY8C20111 and CY8C20121 controllers are: a robust capacitive sensing core with high immunity against radiated and conductive noise, control registers with nonvolatile storage, configurable outputs, and I<sup>2</sup>C communications. The user can configure registers with parameters needed to adjust the operation and sensitivity of the CapSense buttons and outputs and permanently store the settings. The standard I<sup>2</sup>C serial communication interface allows the host to configure the device and read sensor information in real time. I<sup>2</sup>C address is fully configurable without any external hardware strapping.

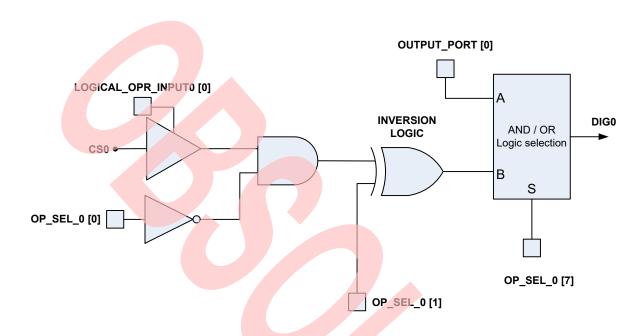

# CY8C20111 Digital Logic Diagram

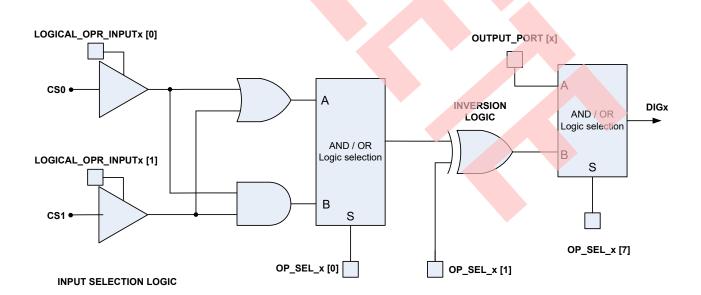

# CY8C20121 Digital Logic Diagram

#### **Contents**

| Pinouts                            |    |

|------------------------------------|----|

| Pin Definitions                    |    |

| Pinouts                            |    |

| Pin Definitions                    |    |

| Typical Circuits                   | 6  |

| Operating Modes                    |    |

| Normal Mode                        |    |

| Setup Mode                         |    |

| I2C Interface                      |    |

| I2C Device Addressing              |    |

| I2C Clock Stretching               | 9  |

| Format for Register Write and Read |    |

| Registers                          | 10 |

| Register Conventions               |    |

| Register Map                       |    |

| CapSense Express Commands          |    |

| OUTPUT_STATUS                      |    |

| OUTPUT_PORT                        |    |

| CS_ENABLE                          |    |

| DIG_ENABLE                         |    |

| SET_STRONG_DM                      |    |

| OP_SEL_x                           | 10 |

| LOGICAL_OPR_INPUTX                 |    |

| CS_NOISE_TH                        |    |

| CS_SETL_TIME                       |    |

| CS OTH SET                         |    |

| CS HYSTERISIS                      |    |

| CS DEBOUNCE                        |    |

| CS_NEG_NOISE_TH                    | 18 |

| CS_LOW_BL_RST                      | 18 |

| CS_FILTERING                       |    |

| CS SCAN POS x                      |    |

| CS_FINGER_TH_x                     | 20 |

| CS_IDAC_x                          |    |

| I2C ADDR LOCK                      | 20 |

| DEVICE ID                          |    |

| DEVICE STATUS                      |    |

| I2C ADDR DM                              | 22 |

|------------------------------------------|----|

| CS READ BUTTON                           | 22 |

| CS READ BLx                              | 23 |

| CS READ DIFFx                            |    |

| CS READ RAWx                             | 23 |

| CS_READ_STATUS                           | 24 |

| COMMAND_REG                              | 24 |

| Layout Guidelines and Best Practices     | 26 |

| Operating Voltages                       |    |

| CapSense Constraints                     |    |

| Absolute Maximum Ratings                 | 28 |

| Operating Temperature                    |    |

| Electrical Specifications                | 29 |

| DC Electrical Specifications             | 29 |

| CapSense Electrical Characteristics      | 31 |

| AC Electrical Specifications             | 31 |

| Appendix                                 |    |

| Examples of Frequently Used I2C Commands | 33 |

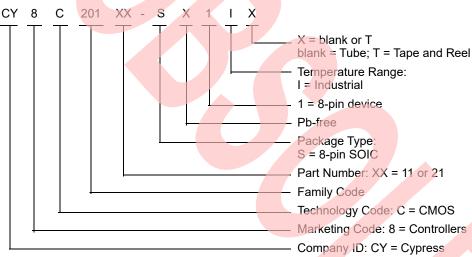

| Ordering Information                     |    |

| Ordering Code Definitions                |    |

| Thermal Impedances                       | 34 |

| Solder Reflow Specifications             | 34 |

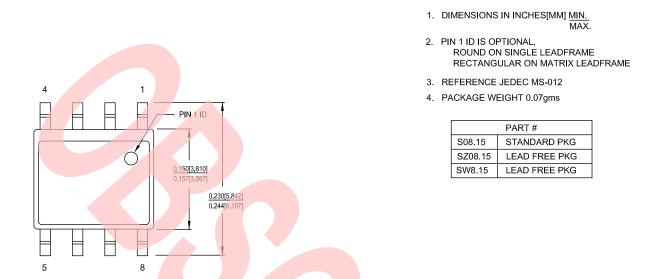

| Package Diagram                          |    |

| Acronyms                                 |    |

| Document Conventions                     |    |

| Units of Measure                         |    |

| Numeric Conventions                      |    |

| Glossary                                 |    |

| Errata                                   |    |

| CY8C20111/121                            |    |

| Document History Page                    |    |

| Sales, Solutions, and Legal Information  |    |

| Worldwide Sales and Design Support       |    |

| Products                                 |    |

| PSoC® Solutions                          |    |

| Cypress Developer Community              |    |

| Technical Support                        | 44 |

# **Pinouts**

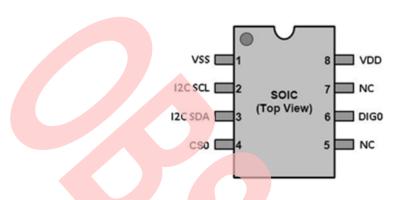

Figure 1. 8-pin SOIC (150 Mils) pinout CY8C20111 (1 Button)

# **Pin Definitions**

8-pin SOIC CY8C20111 (1 Button)

| Pin No | Name            | Description            |

|--------|-----------------|------------------------|

| 1      | V <sub>SS</sub> | Ground                 |

| 2      | I2C SCL         | I <sup>2</sup> C Clock |

| 3      | I2C SDA         | I <sup>2</sup> C Data  |

| 4      | CS0             | CapSense Input         |

| 5      | NC              | No Connect             |

| 6      | DIG0            | Digital Output         |

| 7      | NC              | No Connect             |

| 8      | $V_{DD}$        | Supply Voltage         |

# **Pinouts**

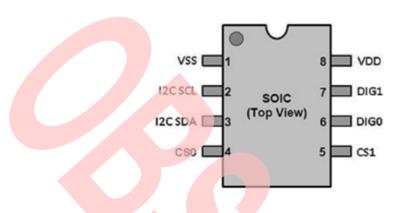

Figure 2. 8-pin SOIC (150 Mils) pinout CY8C20121 (2 Button)

# **Pin Definitions**

8-pin SOIC

CY8C20121 (2 Button)

| Pin No | Name     |                        | Description |

|--------|----------|------------------------|-------------|

| 1      | $V_{SS}$ | Ground                 |             |

| 2      | I2C SCL  | I <sup>2</sup> C Clock |             |

| 3      | I2C SDA  | I <sup>2</sup> C Data  |             |

| 4      | CS0      | CapSense Input         |             |

| 5      | CS1      | CapSense Input         |             |

| 6      | DIG0     | Digital Output         |             |

| 7      | DIG1     | Digital Output         |             |

| 8      | $V_{DD}$ | Supply Voltage         |             |

# **Typical Circuits**

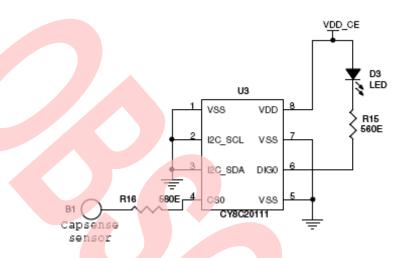

Figure 3. Circuit-1: One Button and One LED<sup>[1]</sup>

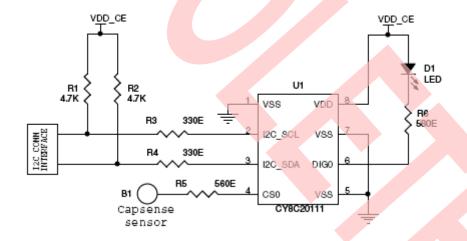

Figure 4. Circuit-2: One Button and One LED with I<sup>2</sup>C Interface

Note

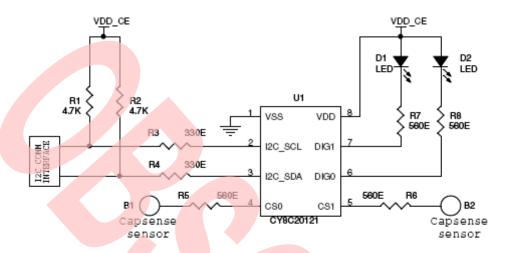

1. The sensors are factory tuned to work with 1 mm plastic or glass overlay.

# Typical Circuits (continued)

Figure 5. Circuit-3: Two Buttons and Two LEDs with I<sup>2</sup>C Interface

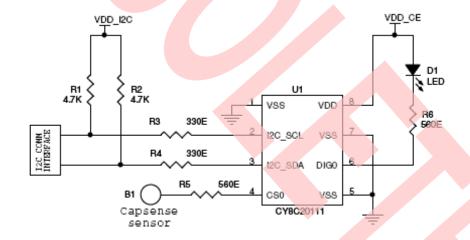

Figure 6. Circuit-4: Compatibility with 1.8 V I<sup>2</sup>C Signaling [2, 3]

<sup>2. 1.8</sup> V ≤ V<sub>DD</sub>\_I2C ≤ V<sub>DD</sub>\_CE and 2.4 V ≤ V<sub>DD</sub>\_CE ≤ 5.25 V.

3. The I2C drive mode of the CapSense device should be configured properly before using in an I2C environment with external pull-ups. Please refer to I2C\_ADDR\_DM register and its factory setting.

# Typical Circuits (continued)

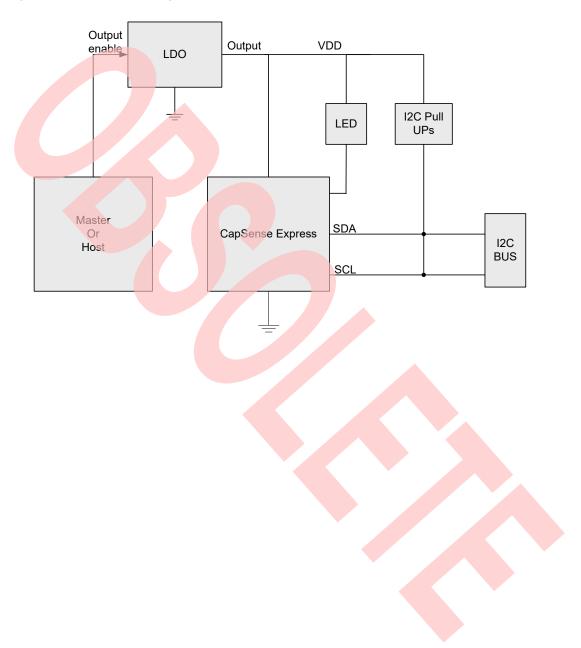

Figure 7. Circuit-5: Powering Down CapSense Express Device for Low Power Requirements [4]

#### Note

<sup>4.</sup> For low power requirements, if VDD is to be turned off, the above concept can be used. The VDDs of CapSense Express, I2C pull-ups, and LEDs must be from the same source. Turning off the VDD ensures that no signal is applied to the device while it is unpowered. The I2C signals should not be driven high by the master in this situation. If a port pin or group of port pins can cater to the power supply requirement of the circuit, the LDO can be avoided.

## **Operating Modes**

#### **Normal Mode**

In normal mode of operation, the acknowledgment time is optimized. The timings remain approximately the same for different configurations of the slave. To reduce the acknowledgment times in normal mode, the registers 0x07, 0x08, 0x11, 0x50, 0x51, 0x5C, 0x5D are given only read access. Writing to these registers can be done only in setup mode.

#### **Setup Mode**

All registers have read and write access (except those which are read only) in this mode. The acknowledgment times are longer compared to normal mode. When CapSense scanning is disabled (command code 0x0A in command register 0xA0), the acknowledgment times can be improved to values similar to the normal mode of operation.

Table 1. I<sup>2</sup>C Addresses

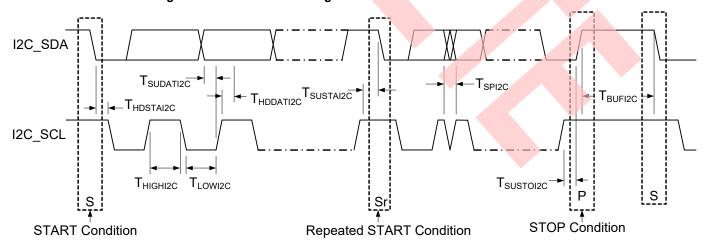

## I<sup>2</sup>C Interface

The CapSense Express devices support the industry standard I<sup>2</sup>C protocol, which can be used to:

- Configure the device

- Read the status and data registers of the device

- Control device operation

- Execute commands

The I<sup>2</sup>C address can be modified during configuration.

#### I<sup>2</sup>C Device Addressing

The device uses a seven bit addressing protocol. The I<sup>2</sup>C data transfer is always initiated by the master sending one byte address; first 7-bit contains address and LSb indicates the data transfer direction. Zero in the LSb indicates the write transaction form master and one indicates read transfer by the master. Table 1 shows example for different I<sup>2</sup>C addresses.

| 7-bit Slave Address (in Dec) | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0   | 8-bit Slave Address (in Hex) |

|------------------------------|----|----|----|----|----|----|----|------|------------------------------|

| 1                            | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 0(W) | 02                           |

| 1                            | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 1(R) | 03                           |

| 75                           | 1  | 0  | 0  | 1  | 0  | 1  | 1  | 0(W) | 96                           |

| 75                           | 1  | 0  | 0  | 1  | 0  | 1  | 1  | 1(W) | 97                           |

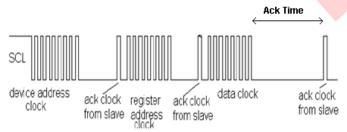

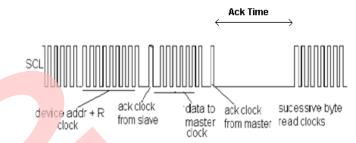

I<sup>2</sup>C Clock Stretching

"Clock stretching" or "bus stalling" in I<sup>2</sup>C communication protocol is a state in which the slave holds the SCL line low to indicate that it is busy. In this condition, the master is expected to wait until the SCL is released by the slave.

When an  $I^2C$  master communicates with the CapSense Express device, the CapSense Express stalls the  $I^2C$  bus after the reception of each byte (that is, just before the ACK/NAK bit) until processing of the byte is complete and critical internal functions are executed. Use a fully  $I^2C$  compliant master to communicate with the CapSense Express device.

An I<sup>2</sup>C master which does not support clock stretching (a bit banged software I<sup>2</sup>C Master) must wait for a specific amount of time specified (as shown in the section Format for Register Write and Read) for each register write and read operation before the

next bit is transmitted. It is mandatory to check the SCL status (it should be high) before 1<sup>2</sup>C master initiates any data transfer with CapSense Express. If the master fails to do so and continues to communicate, the communication is erroneous.

The following diagrams represent the ACK time delays shown in the Register Map on page 7.

Also note that, while using CapSense Express Devices on an I2C bus, I2C master should not generate a start or stop condition in the I2C bus before CapSense Express device generating acknowledgement (ACK/NCK) for the previous transaction. An acknowledgement state produced by the CapSense Express Device for the previous data transfer after start condition for new data transfer by the master may produce unexpected behavior from CapSense Express I2C slave interface.

Figure 8. Write ACK Time Representation

Document Number: 001-53516 Rev. \*N

Figure 9. Read ACK Time Representation

# Format for Register Write and Read

## Register write format

| Start   Slave Addr + vv   A   Reg Addr   A   Data   A   Data   A   Sto | Start | Slave Add | r + W | A | Reg Addr | A | Data | Α | Data | Α |  | Data | Α | Stop |

|------------------------------------------------------------------------|-------|-----------|-------|---|----------|---|------|---|------|---|--|------|---|------|

|------------------------------------------------------------------------|-------|-----------|-------|---|----------|---|------|---|------|---|--|------|---|------|

#### Register read format

| Start | Slave Addr + W | Α | Reg Addr | Α | Stop |   |          |   |      |   |

|-------|----------------|---|----------|---|------|---|----------|---|------|---|

| Start | Slave Addr + R | Α | Data     | Α | Data | Α | <br>Data | N | Stop | ì |

#### Legends

| Master | A – ACK |

|--------|---------|

| Slave  | N – NAK |

# Registers

## **Register Conventions**

| Convention | Description                              |

|------------|------------------------------------------|

| RW         | Register have both read and write access |

| R          | Register have only read access           |

| WPR        | Write register with pass code            |

| FD         | Factory defaults                         |

## **Register Map**

| Name                   | Register<br>Address<br>(in Hex) | Access | Writable<br>Only in<br>Setup | Values of | Default<br>Registers<br>Hex) | I <sup>2</sup> C Max ACK<br>Time in<br>Normal Mode | I <sup>2</sup> C Max ACK<br>Time in Setup<br>Mode (ms) <sup>[6]</sup> | Page No. |

|------------------------|---------------------------------|--------|------------------------------|-----------|------------------------------|----------------------------------------------------|-----------------------------------------------------------------------|----------|

|                        | (III TIEX)                      |        | Mode [5]                     | 1 Button  | 2 Button                     | (ms) <sup>[6]</sup>                                | Mode (ms)                                                             |          |

| OUTPUT_PORT            | 04                              | W      | _                            | 01        | 03                           | 0.10                                               | -                                                                     | 13       |

| CS_ENABLE              | 07                              | RW     | Yes                          | 01        | 03                           | _                                                  | 11                                                                    | 13       |

| DIG_ENABLE             | 08                              | RW     | Yes                          | 01        | 03                           | _                                                  | 11                                                                    | 14       |

| SET_STRONG_DM          | 11                              | RW     | Yes                          | 01        | 03                           | _                                                  | 11                                                                    | 14       |

| OP_SEL_0               | 1C                              | RW     | _                            | 82        | 82                           | 0.12                                               | 11                                                                    | 15       |

| LOGICAL_OPR_INPUT0     | 1E                              | RW     | _                            | 01        | 01                           | 0.12                                               | 11                                                                    | 15       |

| OP_SEL_1 [7]           | 21                              | RW     | _                            |           | 82                           | 0.12                                               | 11                                                                    | 15       |

| LOGICAL_OPR_INPUT1 [7] | 23                              | RW     | (-)                          |           | 02                           | 0.12                                               | 11                                                                    | 15       |

| CS_NOISE_TH            | 4E                              | RW     | -                            | 28        | 28                           | 0.11                                               | 11                                                                    | 16       |

| CS_BL_UPD_TH           | 4F                              | RW     | _                            | 64        | 64                           | 0.11                                               | 11                                                                    | 16       |

| CS_SETL_TIME           | 50                              | RW     | Yes                          | A0        | A0                           | _                                                  | 35                                                                    | 16       |

| CS_OTH_SET             | 51                              | RW     | Yes                          | 00        | 00                           | _                                                  | 35                                                                    | 17       |

| CS_HYSTERISIS          | 52                              | RW     | <b>/</b> -                   | 0A        | 0A                           | 0.11                                               | 11                                                                    | 17       |

| CS_DEBOUNCE            | 53                              | RW     | _                            | 03        | 03                           | 0.11                                               | 11                                                                    | 18       |

| CS_NEG_NOISE_TH        | 54                              | RW     |                              | 14        | 14                           | 0.11                                               | 11                                                                    | 18       |

| CS_LOW_BL_RST          | 55                              | RW     | -                            | 14        | 14                           | 0.11                                               | 11                                                                    | 18       |

| CS_FILTERING           | 56                              | RW     | -                            | 20        | 20                           | 0.11                                               | 11                                                                    | 19       |

| CS_SCAN_POS_0          | 5C                              | RW     | Yes                          | 00        | 00                           | -                                                  | 11                                                                    | 19       |

| CS_SCAN_POS_1 [7]      | 5D                              | RW     | Yes                          |           | 01                           | -                                                  | 11                                                                    | 19       |

| CS_FINGER_TH_0         | 66                              | RW     | _                            | 64        | 64                           | 0.14                                               | 11                                                                    | 20       |

| CS_FINGER_TH_1 [7]     | 67                              | RW     | _                            |           | 64                           | 0.14                                               | 11                                                                    | 20       |

| CS_IDAC_0              | 70                              | RW     | _                            | 0A        | 0A                           | 0.14                                               | 11                                                                    | 20       |

| CS_IDAC_1 [7]          | 71                              | RW     | _                            |           | 0A                           | 0.14                                               | 11                                                                    | 20       |

| I2C_ADDR_LOCK          | 79                              | RW     | _                            | 01        | 01                           | 0.11                                               | 11                                                                    | 20       |

| DEVICE_ID              | 7A                              | R      | _                            | 11        | 21                           | 0.11                                               | 11                                                                    | 21       |

| DEVICE_STATUS          | 7B                              | R      | _                            | 03        | 03                           | 0.11                                               | 11                                                                    | 21       |

| I2C_ADDR_DM            | 7C                              | RW     | _                            | 80        | 80                           | 0.11                                               | 11                                                                    | 22       |

| CS_READ_BUTTON         | 81                              | RW     | _                            | 81        | 81                           | 0.12                                               | 11                                                                    | 22       |

| CS_READ_BLM            | 82                              | R      | _                            | NA        | NA                           | 0.12                                               | 11                                                                    | 23       |

| CS_READ_BLL            | 83                              | R      | _                            | NA        | NA                           | 0.12                                               | 11                                                                    | 23       |

| CS_READ_DIFFM          | 84                              | R      | _                            | NA        | NA                           | 0.12                                               | 11                                                                    | 23       |

| CS_READ_DIFFL          | 85                              | R      | _                            | NA        | NA                           | 0.12                                               | 11                                                                    | 23       |

| CS_READ_RAWM           | 86                              | R      | _                            | NA        | NA                           | 0.12                                               | 11                                                                    | 23       |

| CS_READ_RAWL           | 87                              | R      | _                            | NA        | NA                           | 0.12                                               | 11                                                                    | 23       |

- These registers are writable only after entering into setup mode. All other registers are available for read and write in normal and setup mode.

The Ack times specified are 1x I2C Ack times.

These registers are available only in CY8C20121 device.

#### Register Map (continued)

| Name           | Register<br>Address<br>(in Hex) | Access | Only in Setup (in Hex) |          | Normai iyjoue | I <sup>2</sup> C Max ACK<br>Time in Setup<br>Mode (ms) <sup>[6]</sup> | Page No.    |    |

|----------------|---------------------------------|--------|------------------------|----------|---------------|-----------------------------------------------------------------------|-------------|----|

|                | (III TIEX)                      |        | Mode [5]               | 1 Button | 2 Button      | (ms) <sup>[6]</sup>                                                   | Wode (III3) |    |

| CS_READ_STATUS | 88                              | R      | _                      | NA       | NA            | 0.12                                                                  | 11          | 24 |

| COMMAND_REG    | A0                              | W      | _                      | 00       | 00            | 0.10                                                                  | 11          | 24 |

# **CapSense Express Commands**

| Command [8] | Description                        | Executable Mode | Duration the Device is NOT<br>Accessible after ACK (in ms) [9] |

|-------------|------------------------------------|-----------------|----------------------------------------------------------------|

| W 00 A0 00  | Get firmware revision              | Setup/Normal    | 0                                                              |

| W 00 A0 01  | Store current configuration to NVM | Setup/Normal    | 120                                                            |

| W 00 A0 02  | Restore factory configuration      | Setup/Normal    | 120                                                            |

| W 00 A0 03  | Write NVM POR defaults             | Setup/Normal    | 120                                                            |

| W 00 A0 04  | Read NVM POR defaults              | Setup/Normal    | 5                                                              |

| W 00 A0 05  | Read current configurations (RAM)  | Setup/Normal    | 5                                                              |

| W 00 A0 06  | Reconfigure device (POR)           | Setup           | 5                                                              |

| W 00 A0 07  | Set Normal mode of operation       | Setup/Normal    | 0                                                              |

| W 00 A0 08  | Set Setup mode of operation        | Setup/Normal    | 0                                                              |

| W 00 A0 09  | Start scan                         | Setup/Normal    | 10                                                             |

| W 00 A0 0A  | Stop scan                          | Setup/Normal    | 5                                                              |

| W 00 A0 0B  | Get CapSense scan status           | Setup/Normal    | 0                                                              |

Notes 8. 'W' indicates the write transfer. The next byte of data represents the 7-bit  $I^2C$  address. 9. The Ack times specified are 1x I2C Ack times.

#### OUTPUT\_STATUS

#### **Output Status Register**

OUTPUT\_STATUS: 00h

| 1 Button   | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0      |

|------------|---|---|---|---|---|---|---|--------|

| Access: FD |   |   |   |   |   |   |   | R:01   |

| Bit Name   |   |   |   |   |   |   |   | STS[0] |

| 2 Button   | 7 | 6 |  | 5 | 4 | 3 | 2 | 1   | 0     |

|------------|---|---|--|---|---|---|---|-----|-------|

| Access: FD |   |   |  |   |   |   |   | R:  | 03    |

| Bit Name   |   |   |  |   |   |   |   | STS | [1:0] |

The Output Status register represents the actual logical levels on the output pins.

| Bit | Name      | Description                         |

|-----|-----------|-------------------------------------|

| 1:0 | STS [1:0] | Used to represent the output status |

|     |           | 0 Output low                        |

|     |           | 1 Output high                       |

## OUTPUT\_PORT

#### **Output Port Register**

OUTPUT PORT: 04h

| 1 Button   | 7 | 6 | 5 | 4 |  | 3 | 2 | 1 | 0      |

|------------|---|---|---|---|--|---|---|---|--------|

| Access: FD |   |   |   |   |  |   |   |   | W:01   |

| Bit Name   |   |   |   |   |  |   | ^ |   | DIG[0] |

| 2 Button   | 7 | 6 | 5 | 4 | 3 |  | 2 | 1   | 0     |

|------------|---|---|---|---|---|--|---|-----|-------|

| Access: FD |   |   |   |   |   |  |   | W:  | :03   |

| Bit Name   |   |   |   |   |   |  |   | DIG | [1:0] |

This register is used to write data to DIG output port. Pins defined as output of combinational logic (in OP\_SEL\_x register) cannot be changed using this register.

| Bit | Name      | Description                                                    |

|-----|-----------|----------------------------------------------------------------|

| 1:0 | DIG [1:0] | A bit set in this register sets the logic level of the output. |

|     |           | 0 Logic '0'                                                    |

|     |           | 1 Logic '1'                                                    |

#### **CS\_ENABLE**

#### Select CapSense Input Register

CS\_ENABLE: 07h

(Writable only in Setup mode)

| 1 Button   | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0     |

|------------|---|---|---|---|---|---|---|-------|

| Access: FD |   |   |   |   |   |   |   | RW:01 |

| Bit Name   |   |   |   |   |   |   |   | CS[0] |

| 2 Button   | 7 | 6 | 5 | 4 | 3 | 2 | 1  | 0            |

|------------|---|---|---|---|---|---|----|--------------|

| Access: FD |   |   |   |   |   |   | RW | <i>l</i> :03 |

| Bit Name   |   |   |   |   |   |   | CS | [1:0]        |

This register is used to enable CapSense inputs. This register should be set before setting finger threshold (0x66, 0x67) and IDAC setting (0x70, 0x71) registers.

Bit Name Description

1:0 CS [1:0] These bits are used to enable CapSense inputs.

0 Disable CapSense input1 Enable CapSense input

#### DIG\_ENABLE

#### Select DIG Output Register

GPO\_ENABLE: 08h

(Writable only in Setup mode)

| (TTTTERETE CTTT) | iii ootaa maa |   |   |   |   |   |   |        |

|------------------|---------------|---|---|---|---|---|---|--------|

| 1 Button         | 7             | 6 | 5 | 4 | 3 | 2 | 1 | 0      |

| Access: FD       |               |   |   |   |   |   |   | RW:01  |

| Bit Name         |               |   |   |   |   |   |   | DIG[0] |

| 2 Button   | 7 | 6 |   | 5 | 4 | 4 | 3 | 2 | 1   | 0     |

|------------|---|---|---|---|---|---|---|---|-----|-------|

| Access: FD |   |   |   |   |   |   |   |   | RW  | /:03  |

| Bit Name   |   |   | / |   |   |   |   |   | DIG | [1:0] |

This register is used to enable DIG (Digital) outputs. If DIG output is enabled, the strong drive mode register (11h) should also be set. If DIG output is disabled the drive mode of these pins is High Z.

Bit Name Description

1:0 DIG [1:0] These bits are used to enable DIG outputs.

0 Disable DIG output

1 Enable DIG output

#### SET\_STRONG\_DM

#### **Sets Strong Drive Mode for DIG Outputs.**

SET\_STRONG\_DM: 11h

(Writable only in Setup mode)

| 1 Button   | 7 | 6 | 5 | 4 | 3 | 2 |  | 1 | 0      |

|------------|---|---|---|---|---|---|--|---|--------|

| Access: FD |   |   |   |   |   |   |  |   | RW:01  |

| Bit Name   |   |   |   |   |   |   |  |   | DM [0] |

| 2 Button   | 7 | 6 | 5 | 4 | 3 | 2 | 1 |    | 0     |

|------------|---|---|---|---|---|---|---|----|-------|

| Access: FD |   |   |   |   |   |   |   | RW | /:03  |

| Bit Name   |   |   |   |   |   |   |   | DM | [1:0] |

This register sets strong drive mode for DIG (Digital) outputs. To set strong drive mode the pin should be enabled as GP output.

| Bit | Name     | Description                                                      |

|-----|----------|------------------------------------------------------------------|

| 1:0 | DM [1:0] | These bits are used to set the strong drive mode to DIG outputs. |

|     |          | Strong drive mode not set                                        |

1 Strong drive mode set

#### OP\_SEL\_x

#### **Logic Operation Selection Registers**

OP\_SEL\_0: 1Ch OP\_SEL\_1: 21h (Not available for 1 Button)

| 1/2Button  | 7     | 6 | 5 | 4 | 3 | 2 | 1     | 0        |

|------------|-------|---|---|---|---|---|-------|----------|

| Access: FD | RW: 0 |   |   |   |   |   | RW: 0 | RW: 0    |

| Bit Name   | Op_En |   |   |   |   |   | InvOp | Operator |

This register is used to enable logic operation on GP outputs. OP\_SEL\_0 should be configured to get the logic operation output on DIG0 output and OP\_SEL\_1 for DIG1 output. Write to these registers during the disable state of respective DIG output pins does not have any effect.

The input to the logic operation can be selected in LOGIC\_OPRX registers. The selected inputs can be ORed or ANDed. The output of logic operation can also be inverted.

| Bit | Name     | Description                                                               |     |

|-----|----------|---------------------------------------------------------------------------|-----|

| 7   | Op_En    | This bit enables or disables logic operation.                             |     |

|     |          | 0 Disable logic operation                                                 |     |

|     |          | 1 Enable logic operation                                                  |     |

| 1   | InvOp    | This bit enables or disables logic operation output inversion.            |     |

|     |          | O Logic operation output not inverted                                     |     |

|     |          | 1 Logic operation output inverted                                         |     |

| 0   | Operator | This bit selects which operator should be used to compute logic operation | on. |

|     |          | 0 Logic operator OR is used on inputs                                     |     |

|     |          | 1 Logic operator AND is used on inputs                                    |     |

#### LOGICAL\_OPR\_INPUTx

#### **Selects Input for Logic Operation**

LOGICAL\_OPR\_INPUT0: 1Eh LOGICAL\_OPR\_INPUT1: 23h (Not available for 1 button)

LOGICAL OPR INPUT0

|            | _ |   |   |   |   |   |  |   |        |

|------------|---|---|---|---|---|---|--|---|--------|

| 1 Button   | 7 | 6 | 5 | 1 | 3 | 2 |  | 1 | 0      |

| Access: FD |   |   |   |   |   |   |  |   | RW:01  |

| Bit Name   |   |   |   |   |   |   |  |   | CSL[0] |

| 2 Button   | 7 | 6 | 5 | 4 | 3 | 2 |  | 1   | 0       |

|------------|---|---|---|---|---|---|--|-----|---------|

| Access: FD |   |   |   |   |   |   |  | RV  | V:01    |

| Bit Name   |   |   |   |   |   |   |  | CSI | _ [1:0] |

#### LOGICAL\_OPR\_INPUT1

| 2 Button   | 7 | 6 | 5 | 4 | 3 | 2 | 1 |     | 0     |

|------------|---|---|---|---|---|---|---|-----|-------|

| Access: FD |   |   |   |   |   |   |   | RW  | :02   |

| Bit Name   |   |   |   |   |   |   | • | CSL | [1:0] |

These registers are used to give the input to logic operation block. The inputs can be only CapSense input status.

| Bit | Name      | Description                                             |

|-----|-----------|---------------------------------------------------------|

| 1:0 | CSL [1:0] | These bits selects the input for logic operation block. |

#### CS\_NOISE\_TH

#### **Noise Threshold Register**

CS\_NOISE\_TH: 4Eh

| 1/2 Button | 7 | 6 | 5 | 4   | 3            | 2 | 1 | 0 |

|------------|---|---|---|-----|--------------|---|---|---|

| Access: FD |   |   |   | RW  | <b>/</b> :28 |   |   |   |

| Bit Name   |   |   |   | NT[ | 7:0]         |   |   |   |

This register sets the noise threshold value. For individual sensors, count values above this threshold do not update the baseline. This count is relative to baseline. This parameter is common for all sensors.

The range is 3 to 255 and it should satisfy the equation NT < Min (Finger Threshold – Hysteresis – 5). Recommended value is 40% of finger threshold.

| Bit | Name     | Description                                           |

|-----|----------|-------------------------------------------------------|

| 7:0 | NT [7:0] | These bits are used to set the noise threshold value. |

#### CS\_BL\_UPD\_TH

#### **Baseline Update Threshold Register**

CS BL UPD TH: 4Fh

| 1/2 Button | 7 | 6 | 5 | 4    |       | 3 | 2 | 1 | 0 |

|------------|---|---|---|------|-------|---|---|---|---|

| Access: FD |   |   |   | RW   | ':64  |   |   |   |   |

| Bit Name   |   |   |   | BLU' | [7:0] |   |   |   |   |

When the new raw count value is above the current baseline and the difference is below the noise threshold, the difference between the current baseline and the raw count is accumulated into a "bucket." When the bucket fills, the baseline increments and the bucket is emptied. This parameter sets the threshold that the bucket must reach for the baseline to increment. In other words, lower value provides faster baseline update rate and vice versa. This parameter is common for all sensors.

The range is 0 to 255.

| Bit | Name       | Description                                                             |

|-----|------------|-------------------------------------------------------------------------|

| 7:0 | BLUT [7:0] | These bits set the threshold that the bucket must reach for baseline to |

|     |            | increment.                                                              |

#### CS\_SETL\_TIME

#### **Settling Time Register**

CS SETL TIME: 50h

(Writable only in Setup mode)

| - 4 | 1 ,        |   | , |   |       |         | <br> | <br> |   |

|-----|------------|---|---|---|-------|---------|------|------|---|

|     | 1/2 Button | 7 | 6 | 5 | 4     | 3       | 2    | 1    | 0 |

|     | Access: FD |   |   |   | RW    | :A0     |      |      |   |

|     | Bit Name   |   |   |   | STLNG | TM[7:0] |      |      |   |

The settling time parameter controls the duration of the capacitance-to-voltage conversion phase. The parameter setting controls a software delay that allows the voltage on the integrating capacitor to stabilize. This parameter is common for all sensors.

This register should be set before setting finger threshold (0x66, 0x67) and IDAC setting (0x70, 0x71) registers.

The range is 2 to 255.

| Bit | Name           | Description                                         |

|-----|----------------|-----------------------------------------------------|

| 7:0 | STLNG_TM [7:0] | These bits are used to set the settling time value. |

#### CS\_OTH\_SET

#### CapSense Clock Select, Sensor Auto Reset Register

CS OTH SET: 51h

(Writable only in Setup mode)

| 1/2 Button | 7 | 6    | 5             | 4 | 3      | 2 | 1 | 0 |

|------------|---|------|---------------|---|--------|---|---|---|

| Access: FD |   | RW   | <b>/</b> : 00 |   | RW: 0  |   |   |   |

| Bit Name   |   | CS_C | LK[1:0]       |   | Sns_Ar |   |   |   |

The registers set the CapSense module frequency of operation and enables or disables the sensor auto reset.

CS\_CLK bits provides option to select variable clock input for the CapSense block. A sensor design having higher paratactic requires lower clock for better performance and vice versa.

Sensor Auto Reset determines whether the baseline is updated at all times or only when the signal difference is below the noise threshold. When set to '1' (enabled), the baseline is updated constantly. This setting limits the maximum time duration of the sensor, but it prevents the sensors from permanently turning on when the raw count suddenly rises without anything touching the sensor. This sudden rise can be caused by a large power supply voltage fluctuation, a high energy RF noise source, or a very quick temperature change. When the parameter is set to '0' (disabled), the baseline is updated only when raw count and baseline difference is below the noise threshold parameter. This parameter may be enabled unless there is a demand to keep the sensors in the on state for a long time. This parameter is common for all sensors.

| Bit | Name        | Description                                              |

|-----|-------------|----------------------------------------------------------|

|     |             | These bits selects the CapSense clock.                   |

|     |             | CS_CLK[1:0] Frequency of Operation                       |

| 3:5 | CS CLK[1:0] | 00 IMO                                                   |

|     |             | 01 IMO/2                                                 |

|     |             | 10 JMO/4                                                 |

|     |             | 11 IMO/8                                                 |

| 3   | Sns_Ar      | This bit is used to enable or disable sensor auto reset. |

|     |             | O Disable Sensor auto reset                              |

|     |             | 1 Enable Sensor auto reset                               |

#### **CS\_HYSTERISIS**

#### **Hysteresis Register**

CS HYSTERISIS: 52h

| 1/2 Button | 7 | 6 | 5 | 4   |       | 3 | 2 | 1 | 0 |

|------------|---|---|---|-----|-------|---|---|---|---|

| Access: FD |   |   |   | RW  | :0A   |   |   |   |   |

| Bit Name   |   |   |   | HYS | [7:0] |   |   |   |   |

The Hysteresis parameter adds to or subtracts from the finger threshold depending on whether the sensor is currently active or inactive. If the sensor is off, the difference count must overcome the 'finger threshold + hysteresis'. If the sensor is on, the difference count must go below the 'finger threshold – hysteresis'. It is used to add debouncing and "stickiness" to the finger detection algorithm. This parameter is common for all sensors.

Possible values are 0 to 255. However, the setting must be lower than the finger threshold parameter setting. Recommended value for hysteresis is 15 percent of finger threshold.

| Bit | Name      | Description                                      |

|-----|-----------|--------------------------------------------------|

| 7:0 | HYS [7:0] | These bits are used to set the hysteresis value. |

#### **CS\_DEBOUNCE**

#### Debounce Register.

CS DEBOUNCE: 53h

| 1/2 Button | 7 | 6     | 5       | 4 | 3 | 2 | 1 | 0 |  |  |  |

|------------|---|-------|---------|---|---|---|---|---|--|--|--|

| Access: FD |   | RW:0A |         |   |   |   |   |   |  |  |  |

| Bit Name   |   |       | DB[7:0] |   |   |   |   |   |  |  |  |

The Debounce parameter adds a debounce counter to the 'sensor active transition'. For the sensor to transition from inactive to active, the consecutive samples of difference count value must stay above the 'finger threshold + hysteresis' for the number specified. This parameter is common for all sensors.

Possible values are 1 to 255. A setting of '1' provides no debouncing.

| Bit | Name     |  | Description                                    |

|-----|----------|--|------------------------------------------------|

| 7:0 | DB [7:0] |  | These bits are used to set the debounce value. |

#### CS\_NEG\_NOISE\_TH

#### **Negative Noise Threshold Register**

CS NEG NOISE TH: 54h

| 1/2 Button | 7 | 6     |  |  | 5 |  | 4  | 3      | 2 | 1 | 0 |

|------------|---|-------|--|--|---|--|----|--------|---|---|---|

| Access: FD |   | RW:0A |  |  |   |  |    |        |   |   |   |

| Bit Name   |   |       |  |  |   |  | NN | Γ[7:0] |   |   |   |

This parameter adds a negative difference count threshold. If the current raw count is below the baseline and the difference between them is greater than this threshold, the baseline is not updated. However, if the current raw count stays in the low state (difference greater than the threshold) for the number of samples specified by the Low Baseline Reset parameter, the baseline is reset. This parameter is common for all sensors.

| Bit | Name      | Description                                          |

|-----|-----------|------------------------------------------------------|

| 7:0 | NNT [7:0] | These bits are used to set the negative noise value. |

#### CS\_LOW\_BL\_RST

#### Low Baseline Reset Register

CS\_LOW\_BL\_RST: 55h

| 1/2 Button | 7 | 6     | 5 | 4   |       | 3 | 2 | 2 | 1 |  | 0 |

|------------|---|-------|---|-----|-------|---|---|---|---|--|---|

| Access: FD |   | RW:0A |   |     |       |   |   |   |   |  |   |

| Bit Name   |   |       |   | LBR | [7:0] |   |   |   |   |  |   |

This parameter works together with the Negative Noise Threshold parameter. If the sample count values are below the baseline minus the negative noise threshold for the specified number of samples, the baseline is set to the new raw count value. It essentially counts the number of abnormally low samples required to reset the baseline. It is generally used to correct the finger-on-at-startup condition. This parameter is common for all sensors.

| Bit | Name      | Description                                              |

|-----|-----------|----------------------------------------------------------|

| 7:0 | LBR [7:0] | These bits are used to set the Low Baseline Reset value. |

#### **CS\_FILTERING**

#### **CapSense Filtering Register**

CS FILTERING: 56h

| 1/2 Button | 7     | 6 | 5      | 4      | 3 2 |  | 1              | 0 |  |

|------------|-------|---|--------|--------|-----|--|----------------|---|--|

| Access: FD | RW: 0 |   | RW: 1  | RW: 0  |     |  | RW: 00         |   |  |

| Bit Name   | RstBl |   | I2C_DS | Avg_En |     |  | Avg_Order[1:0] |   |  |

This register provides an option for forced baseline reset and to enable and configure two different types of software filters.

| Bit   | Name           | Description                                                                                                                   |

|-------|----------------|-------------------------------------------------------------------------------------------------------------------------------|

| 7     | RstBl          | This bit resets all the baselines and it is auto cleared to '0'.  O All Baselines are not reset                               |

|       |                | 0 All Baselines are not reset 1 All baselines are reset                                                                       |

| 5     | I2C_DS         | When this bit is set to '1' the CapSense scan sample is dropped if I <sup>2</sup> C communication was active during scanning. |

|       |                | <ul> <li>Disable the I<sup>2</sup>C drop sample filer</li> <li>Enable the I<sup>2</sup>C drop sample filter</li> </ul>        |

| 4     | Avg_En         | This bit enables average filter on raw counts.                                                                                |

|       |                | <ul> <li>Disable the average filter</li> <li>Enable the average filter</li> </ul>                                             |

|       |                | These bits are used to select the number of CapSense samples to average:                                                      |

|       |                | Avg_Order[1:0] in Hex Samples to Average                                                                                      |

| [1:0] | Avg_Order[1:0] | 00 2                                                                                                                          |

|       |                | 01 4                                                                                                                          |

|       |                | 10 8                                                                                                                          |

|       |                | 11 16                                                                                                                         |

# CS\_SCAN\_POS\_x

#### **Scan Position Registers**

CS SCAN POS 0:5Ch

(Writable only in Setup mode)

| 1/2 Button | 7 | 6 | 5 | 4 | 3 | 2 |  | 1 | 0         |

|------------|---|---|---|---|---|---|--|---|-----------|

| Access: FD |   |   |   |   |   |   |  |   | RW: 0     |

| Bit Name   |   |   |   |   |   |   |  |   | Scan_Pstn |

CS\_SCAN\_POS\_1: 5Dh (Not available for 1 Button)

(Writable only in Setup mode)

| 2 Button   | 7 | 6 | 5 | 4 | 3         | 1 | 2 | 1 | 0 |

|------------|---|---|---|---|-----------|---|---|---|---|

| Access: FD |   |   |   |   | RW: 1     |   |   |   |   |

| Bit Name   |   |   |   |   | Scan_Pstn |   |   |   |   |

This register is used to set the position of the sensors in the switch table for proper scanning sequence because the CapSense sensors are scanned in sequence.

This register should be set after setting 0x07, 0x50, and 0x51 registers.

| Bit | Name      | Description                      |

|-----|-----------|----------------------------------|

| 0   | Scan_Pstn | This bit sets the scan position. |

#### CS\_FINGER\_TH\_x

#### **Finger Threshold Registers**

| 1/2 Button | 7 | 6 | 5       | 4 | 3 | 2 | 1 | 0 |  |

|------------|---|---|---------|---|---|---|---|---|--|

| Access: FD |   |   | RW: 64  |   |   |   |   |   |  |

| Bit Name   |   |   | FT[7:0] |   |   |   |   |   |  |

This register sets the finger threshold value for CapSense inputs. Possible values are 3 to 255. This parameter should be configured individually for each CapSense inputs.

This register should be set after setting 0x07, 0x50, and 0x51 registers.

| Bit   | Name     |  | Description                                             |

|-------|----------|--|---------------------------------------------------------|

| [7:0] | FT [7:0] |  | These bit set the finger threshold for CapSense inputs. |

#### CS\_IDAC\_x

#### **IDAC Setting Registers**

CS IDAC 0: 70h CS IDAC 1: 71h (Not available in 1 Button)

| 1/2 Button | 7 | 6 | 5 |  | 4    |       | 3 | 2 | 1 | 0 |

|------------|---|---|---|--|------|-------|---|---|---|---|

| Access: FD |   |   |   |  | RW   | : 0A  |   |   |   |   |

| Bit Name   |   |   |   |  | IDAC | [7:0] |   |   |   |   |

The IDAC register controls the sensitivity of the CapSense algorithm. This register is used to tune the CapSense input for specific design or overlays. Decreasing the value of this register increases the sensitivity of the CapSense buttons and vice versa. Decreasing the value of IDAC increases noise and vice versa.

Possible values are 1 to 255. If the value is set to 0 then the value is reset to default value 10.

The recommended value is greater than 4. Setting value ≤ 4 creates excessive amount of noise.

This register should be set after setting 0x07, 0x50, and 0x51 registers.

| Bit   | Name       | Description                    |

|-------|------------|--------------------------------|

| [7:0] | IDAC [7:0] | These bit set the IDAC values. |

#### I2C\_ADDR\_LOCK

#### **I2C Address Lock Registers**

I2C\_ADDR\_LOCK: 79h

| 1/2 Button | 7 | 6 | 5 | 4 | 3 | 2 | 4 | 1 | 0      |

|------------|---|---|---|---|---|---|---|---|--------|

| Access: FD |   |   |   |   |   |   |   |   | WPR: 0 |

| Bit Name   |   |   |   |   |   |   |   |   | I2CAL  |

This register is used to unlock and lock the I<sup>2</sup>C address register (7Ch) access. The device I<sup>2</sup>C address should be modified by writing new address to register 7Ch after unlocking the access using this register. Write to the 7C register during the locked state does not have any effect and the new address take effect only after the access is locked.

To lock or unlock the I<sup>2</sup>C AL bit, the following three bytes must be written to register 79h:

■ unlock I2CAL: 3Ch A5h 69h■ lock I2CAL: 96h 5Ah C3h

Reading the I2CAL bit from register 79h indicates the current access state.

| Bit | Name  | Description                                                        |

|-----|-------|--------------------------------------------------------------------|

| 0   | I2CAL | This bit gives the lock/unlock status of I <sup>2</sup> C address. |

|     |       | 0 Unlocked                                                         |

|     |       | 1 Locked                                                           |

#### **DEVICE\_ID**

#### **Device ID Register**

DEVICE ID: 7Ah

| 1 Button   | 7 | 6     | 5           | 4 | 3 | 2 | 1 | 0 |  |  |  |  |

|------------|---|-------|-------------|---|---|---|---|---|--|--|--|--|

| Access: FD |   | R: 11 |             |   |   |   |   |   |  |  |  |  |

| Bit Name   |   |       | DEV_ID[7:0] |   |   |   |   |   |  |  |  |  |

| 2 Button   | 7 | 6 | 5     | 4           | 3 | 2 | 1 | 0 |  |  |

|------------|---|---|-------|-------------|---|---|---|---|--|--|

| Access: FD |   |   | R: 21 |             |   |   |   |   |  |  |

| Bit Name   |   |   |       | DEV_ID[7:0] |   |   |   |   |  |  |

This register contains the device and product ID. The device and product ID corresponds to "xx" in CY8C201xx.

#### Bit Name Description

7:0 DEV\_ID [7:0] These bits contain the device and product ID.

| Part No   | Device/Product ID |

|-----------|-------------------|

| CY8C20111 | 11                |

| CY8C20121 | 21                |

#### **DEVICE\_STATUS**

#### **Device Status Register**

DEVICE STATUS: 7Bh

| 1/2 Button | 7     | 6        | 5    | 4       | 3        | 2  | 1    | 0    |

|------------|-------|----------|------|---------|----------|----|------|------|

| Access: FD | R:    | : 00     | R: 0 | R:0     | R: 0     |    | R: 0 | R: 0 |

| Bit Name   | Ip_Vc | olt[1:0] | IRES | Load_FD | No_NVM_W | /r | CSE  | DIGE |

This register contains the device status.

#### Bit Name Description

Supply voltage is automatically detected and these bits are set accordingly.

|     |               | Ip_Volt[1:0] Supply Voltage                                                                                                                      |  |  |  |  |  |  |

|-----|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 7:6 | lp Volt [1:0] | 00 5                                                                                                                                             |  |  |  |  |  |  |

| 7.0 | .p_vent[1.0]  | 01 3.3                                                                                                                                           |  |  |  |  |  |  |

|     |               | 10 2.7                                                                                                                                           |  |  |  |  |  |  |

|     |               | 11 Reserved                                                                                                                                      |  |  |  |  |  |  |

| 5   | IRES          | When set to '1', this bit indicates that an internal reset occurred.                                                                             |  |  |  |  |  |  |

|     |               | 0 indicates the last system reset was not internal reset                                                                                         |  |  |  |  |  |  |

|     |               | 1 indicates the last system reset was internal reset                                                                                             |  |  |  |  |  |  |

| 4   | Load_FD       | This bit indicates whether factory defaults are loaded during power-up.                                                                          |  |  |  |  |  |  |

|     |               | 0 User default configuration is loaded during power-up                                                                                           |  |  |  |  |  |  |

|     |               | 1 Factory default configuration is loaded during power-up                                                                                        |  |  |  |  |  |  |

|     |               | When set to '1', this bit indicates that the supply voltage applied to the                                                                       |  |  |  |  |  |  |

| 3   | No_NVM_Wr     | device Is too low for a write to nonvolatile memory operation, and no write is performed. This bit must be checked before any Store or Write POR |  |  |  |  |  |  |

|     |               | command.                                                                                                                                         |  |  |  |  |  |  |

| 1   | CSE           | This bit indicates whether CapSense function is enabled or disabled.                                                                             |  |  |  |  |  |  |

|     |               | 0 Functionality of CapSense block is disabled                                                                                                    |  |  |  |  |  |  |

|     |               | 1 Functionality of CapSense block is enabled                                                                                                     |  |  |  |  |  |  |

| 0   | DIGE          | This bit indicates whether GP Output function is enabled or disabled.                                                                            |  |  |  |  |  |  |

|     |               | 0 Functionality of Digital output block is disabled                                                                                              |  |  |  |  |  |  |

|     |               | 1 Functionality of Digital output block is enabled                                                                                               |  |  |  |  |  |  |

#### I2C\_ADDR\_DM

#### Device I<sup>2</sup>C Address and I<sup>2</sup>C Pin Drive Mode Register

I2C ADDR DM: 7Ch

| 1 Button   | 7        | 6 | 5             | 4 | 3 | 2 | 1 | 0 |  |

|------------|----------|---|---------------|---|---|---|---|---|--|

| Access: FD | RW: 0    |   | RW: 00        |   |   |   |   |   |  |

| Bit Name   | I2CIP_EN |   | I2C_ADDR[6:0] |   |   |   |   |   |  |

This register sets the drive mode of I<sup>2</sup>C pins and I<sup>2</sup>C slave address. To write to this register, register 79h must first be unlocked. The value written to register 7Ch is applied only after locking register 79h again.

| Bit | Name           | Description                                                   |

|-----|----------------|---------------------------------------------------------------|

| 7   | I2CIP_EN       | This bit is used to set the I <sup>2</sup> C pins drive mode. |

|     |                | 0 Internal pull-up enabled                                    |

|     |                | 1 Internal pull-up disabled                                   |

| 6:0 | I2C_ADDR [6:0] | Used to set the device I <sup>2</sup> C address.              |

#### CS\_READ\_BUTTON

**Button Select Register**

CS\_READ\_BUTTON: 81h

| 1 Button   | 7     | 6 |   | <br>5 |  | 4 |   | 3 | 3 | 2 | 1 | 0       |

|------------|-------|---|---|-------|--|---|---|---|---|---|---|---------|

| Access: FD | RW: 0 |   | \ |       |  |   |   |   |   |   |   | RW: 0   |

| Bit Name   | RD_EN |   |   |       |  |   | 7 |   |   |   |   | CSBN[0] |

| 2 Button   | 7     | 6 | 5 | 5 | 4 |               | 3 | 2 | 1    | 0             |

|------------|-------|---|---|---|---|---------------|---|---|------|---------------|

| Access: FD | RW: 0 |   |   |   |   | $\overline{}$ |   |   | RW   | <b>'</b> : 00 |

| Bit Name   | RD_EN |   |   |   |   |               |   |   | CSBI | N[1:0]        |

The scan result of a CapSense input (raw count, difference count, and baseline) can be read only for one input at a time using 82h–87h registers. This register is used to select a CapSense input to read the raw count, difference count, and baseline. Only the pins defined as CapSense inputs in register 07h can be used with this register. Trying to select other pins not defined as CapSense does not have any change.

| Bit | Name       | Description                                                                                                                                                                     |

|-----|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | RD_EN      | This bit enables the CapSense raw data reading.                                                                                                                                 |

|     |            | Disable CapSense scan result reading                                                                                                                                            |

|     |            | 1 Enable CapSense scan result reading                                                                                                                                           |

|     |            | These bits decide which CapSense button scan result are read. When writing to this register, the bitmask must contain only one bit set to '1', otherwise the data is discarded. |

| 1:0 | CSBN [1:0] | CSBN [1:0] CapSense Button No                                                                                                                                                   |

|     |            | 01 1                                                                                                                                                                            |

|     |            | 10 2                                                                                                                                                                            |

#### CS\_READ\_BLx

#### **Baseline Value MSB/LSB Registers**

CS\_READ\_BLM: 82h

CS\_READ\_BLL: 83h

| 1/2 Button | 7 | 6 | 5     | 4    | 3    | 2 | 1 | 0 |  |

|------------|---|---|-------|------|------|---|---|---|--|

| Access: FD |   |   | R: 00 |      |      |   |   |   |  |

| Bit Name   |   |   |       | BL [ | 7:0] |   |   |   |  |

Reading from this register returns the 2-byte current baseline value for the selected CapSense input.

| Bit | Name     | Description                              |

|-----|----------|------------------------------------------|

| 7:0 | BL [7:0] | These bits represent the baseline value. |

#### CS\_READ\_DIFFX

#### Difference Count Value MSB/LSB Registers

CS\_READ\_DIFFM: 84h CS\_READ\_DIFFL: 85h

| 1/2 Button | 7 | 6 |  | 5 |  | 4   | 3     | 2 | 1 | 0 |

|------------|---|---|--|---|--|-----|-------|---|---|---|

| Access: FD |   |   |  |   |  | R:  | 00    |   |   |   |

| Bit Name   |   |   |  |   |  | DIF | [7:0] |   |   |   |

Reading from this register returns the 2-byte current difference count for the selected CapSense input.

| Bit | Name      | Description                                       |  |

|-----|-----------|---------------------------------------------------|--|

| 7:0 | DIF [7:0] | These bits represent the sensor difference count. |  |

#### CS\_READ\_RAWx

#### **Difference Count Value MSB/LSB Registers**

| 1/2 Button | 7 | 6 | 5 | 4 |      |      | 3 |  | 2 | $\Box$ | 1 | 0 |

|------------|---|---|---|---|------|------|---|--|---|--------|---|---|

| Access: FD |   |   |   |   | R: ( | 00   |   |  |   |        |   |   |

| Bit Name   |   |   |   | F | RC [ | 7:0] |   |  |   |        |   |   |

Reading from this register returns the 2-byte current raw count value for the selected CapSense input.

| Bit | Name     | Description                               |

|-----|----------|-------------------------------------------|

| 7:0 | RC [7:0] | These bits represent the raw count value. |

#### CS\_READ\_STATUS

## Sensor On Status Register

CS\_READ\_STATUS: 88h

| 1 Button   | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0        |

|------------|---|---|---|---|---|---|---|----------|

| Access: FD |   |   |   |   |   |   |   | R: 0     |

| Bit Name   |   |   |   |   |   |   |   | BT_ST[0] |

| 2 Button   | 7 | 6 | /1 | 5 | 4 | 3 | 2 | 1    | 0      |

|------------|---|---|----|---|---|---|---|------|--------|

| Access: FD | 7 |   |    |   |   |   |   | R:   | 00     |

| Bit Name   |   |   |    |   |   |   |   | BT_S | T[1:0] |

This register gives the sensor ON/OFF status. A bit '1' indicates sensor is ON and '0' indicates sensor is OFF.

Bit Name Description

1:0 BT\_ST [1:0] These bits used to represent sensor status.

0 Sensor OFF

1 Sensor ON

#### COMMAND\_REG

#### **Command Register**

COMMAND REG: A0h

| 1/2 Button | 7 | 6 | 5 | 4 |      |      | 3  | 2 | 1 | 0 |

|------------|---|---|---|---|------|------|----|---|---|---|

| Access: FD |   |   |   |   | W:   | 00   |    |   |   |   |

| Bit Name   |   |   |   |   | Cmnd | [7:0 | 0] |   |   |   |

Commands are executed by writing the command code to the command register.

| Bit | Name       | Description                                                |

|-----|------------|------------------------------------------------------------|

| 7:0 | Cmnd [7:0] | Refer to the following table for command register opcodes. |

#### **Table 2. Command Register Opcodes**

| Command<br>Code | Name                          | Description                                                                                                                                                                                                                                                                                |

|-----------------|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 00h             |                               | The I <sup>2</sup> C buffer is loaded with the one byte firmware revision value. Reading one byte after writing this command returns the firmware revision. The upper nibble of the firmware revision byte is the major revision number and the lower nibble is the minor revision number. |

| 01h             |                               | The current register settings are saved in nonvolatile memory (flash). This setting is automatically loaded after the next device reset/power-up or if the Reconfigure Device (06h) command is issued.                                                                                     |

| 02h             | Restore Factory Configuration | Replaces the saved user configuration with the factory default configuration. Current settings are unaffected by this command. New settings are loaded after the next device reset/power-up or if the 06h command is issued.                                                               |

**Table 2. Command Register Opcodes** (continued)

| Command<br>Code | Name                                | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

|-----------------|-------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 03h             | Write POR Defaults                  | Sends new power-up defaults to the CapSense controller without changing current settings unless the 06h command is issued afterwards. This command is followed by 123 data bytes according to the POR Default Data Structure table. The CRC is calculated as the XOR of the 122 data bytes (00h-79h). If the CRC check fails or an incomplete block is sent, the slave responds with an ACK and the data is NOT saved to flash. To define new POR defaults:  Write command 03h  Write 122 data bytes with new values of registers (use the _flash.iic file generated from s/w tool)  Write one CRC byte calculated as XOR of previous 122 data bytes |  |  |  |  |

|                 |                                     | Reads the POR settings stored in the nonvolatile memory. To read POR defaults:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| 04h             | Read POR Defaults                   | ■ Write command 04h ■ Read 122 data bytes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

|                 |                                     | Read one CRC byte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| 05h             | Read Device<br>Configuration (RAM)  | Reads the current device configuration. Gives the user "flat-address-space" access to all device settings. To read device configuration:  Write command 05h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

|                 | Cornigulation (TCAINI)              | ■ Read 122 data bytes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

|                 |                                     | ■ Read one CRC byte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| 06h             | Reconfigure Device (POR)            | Immediately reconfigures the device with actual POR defaults from flash. Has the sar effect on the registers as a POR. This command can only be executed in setup operation mode (command code 08).                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |