- Optimized for Texas Instrument's TI38054 •

- Supports both UTP Transmission •

- Complies with or exceeds IEEE 802.5 Requirements •

### Electrical Parameters @ 25° C

| Impedance<br>( $\Omega$ ) | Insertion Loss |          |           |           |           |           |           |           | Return Loss<br>(dB Min.) |             |              | Common Mode Rejection<br>(dB Min.) |          |          |           |           |            |            |

|---------------------------|----------------|----------|-----------|-----------|-----------|-----------|-----------|-----------|--------------------------|-------------|--------------|------------------------------------|----------|----------|-----------|-----------|------------|------------|

|                           | (dB Max.)      |          |           |           | (dB Min.) |           |           |           |                          |             |              |                                    |          |          |           |           |            |            |

| Chip Side<br>600          | 1-4<br>MHz     | 8<br>MHz | 16<br>MHz | 24<br>MHz | 32<br>MHz | 36<br>MHz | 44<br>MHz | 80<br>MHz | 1-6<br>MHz               | 6-17<br>MHz | 17-25<br>MHz | 100<br>KHz                         | 1<br>MHz | 5<br>MHz | 20<br>MHz | 70<br>MHz | 100<br>MHz | 200<br>MHz |

| Cable Side<br>100         | -.5            | -.8      | -1        | -1.9      | -7        | -25       | -30       | -25       | -14                      | -12         | -8           | -65                                | -45      | -30      | -30       | -15       | -15        | -20        |

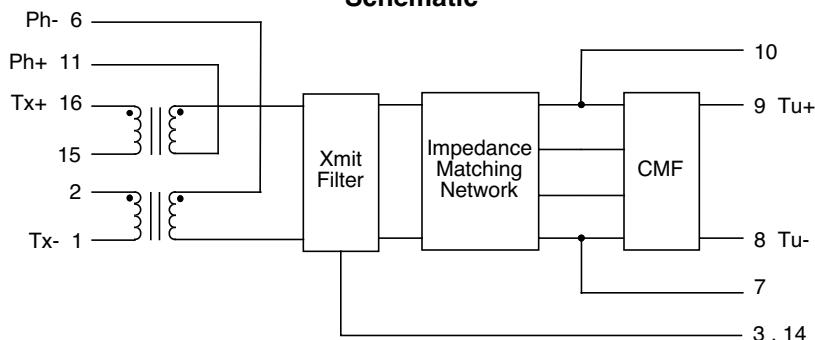

### Schematic

Pins 4, 5, 12, 13 are Not Connected

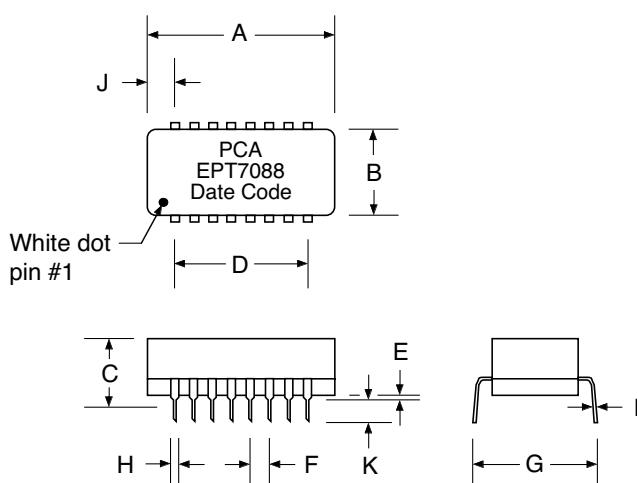

### Package

### Dimensions

| Dim. | (Inches) |       |      | (Millimeters) |       |       |

|------|----------|-------|------|---------------|-------|-------|

|      | Min.     | Max.  | Nom. | Min.          | Max.  | Nom.  |

| A    | .990     | 1.000 | .995 | 25.15         | 25.65 | 25.27 |

| B    | .442     | .462  | .452 | 11.23         | 11.73 | 11.48 |

| C    | .351     | .371  | .361 | 8.92          | 9.42  | 9.17  |

| D    | ---      | ---   | .700 | ---           | ---   | 17.78 |

| E    | .005     | .025  | .015 | .130          | .640  | .381  |

| F    | ---      | ---   | .100 | ---           | ---   | 2.54  |

| G    | .525     | .555  | .540 | 13.34         | 14.10 | 13.72 |

| H    | .016     | .022  | .020 | .406          | .559  | .508  |

| I    | ---      | ---   | .010 | ---           | ---   | 2.54  |

| J    | ---      | ---   | .147 | ---           | ---   | 3.75  |

| K    | .125     | .150  | .138 | 3.18          | 3.81  | 3.50  |

## Token Ring Transceiver Module

**EPT7088**

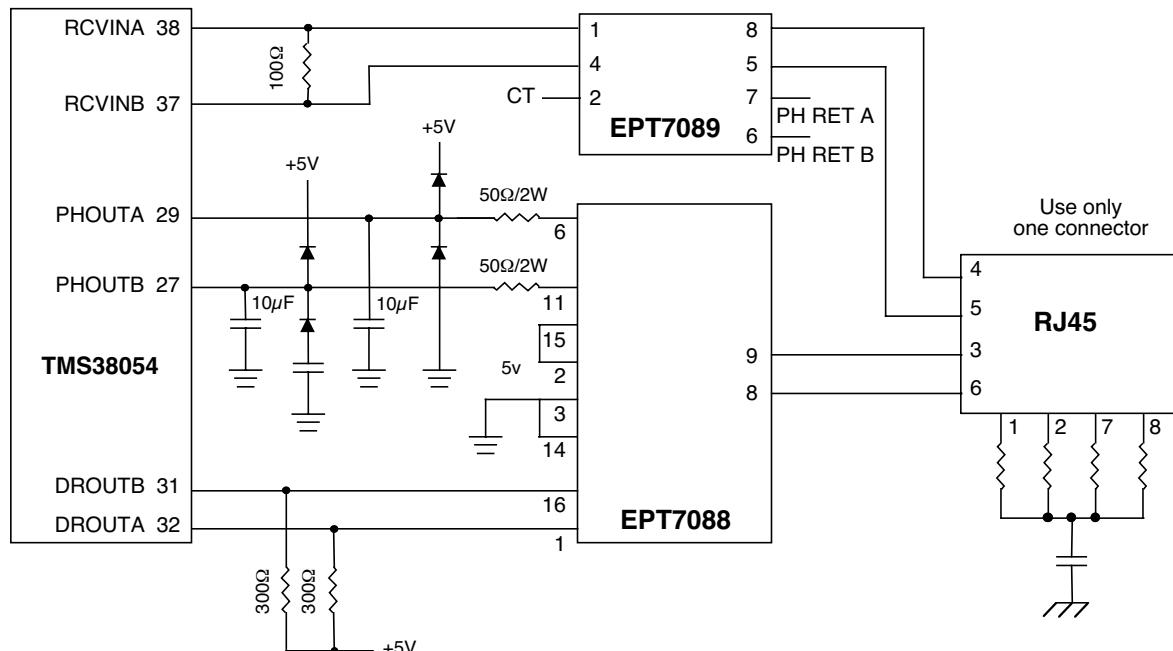

The circuit below is a guideline for interconnecting PCA's EPT7088 with a typical Token Ring PHY chip for 4 Mb/16Mb applications over UTP cable. Further details of system design should be obtained from the specific chip manufacturer. Note that this module is optimized for a "current source" driver such as TMS38054.

Typical insertion loss of the isolation transformer is 0.5dB up to 16 MHz. The Toek Ring filter design follows the I.E.E.E 802.5 last recommendations in the Standard regarding the differential phase delay and the return loss right up to the filter cut off frequency. This module requires either a receiver module with only isolation transformer/common mode choke combination(such as the EPT7089) or another module identical to the EPT7088 to complete the transceiver operation.

The pull down resistors to chassis via a cap shown around the RJ45 connector have been known to suppress unwanted radiation that unused wires pick up from the immediate environment. This is specially true if driving UTP cable. Their placement and use are to be considered carefully before a design is finalized.

No specific recommendation is made here for phantom circuitry, implementation varies. Please note that additional emission control has been observed if both nodes of the phantom bypass capacitor on the transmit channel are pulled to the chassis ground via suitable capacitors.

It is recommended that there be a neat separation of ground planes in the layout. It is generally accepted practice to limit the plane off at least 0.05 inches away from the chip side pins of EPT7088. There need not be any ground plane beyond this point.

For best results, PCB designer should design the outgoing traces preferably to be  $50\Omega$ , balanced and well coupled to achieve minimum radiation from these traces.

## Typical Application Circuit Connection to TMS38054 (or Equivalent)

Notes : Phantom returns are left unconnected. Applications vary. Your system may have a phantom drive return detection circuit needing pins 7 & 6 to be connected separately. Receiver CT can be grounded via a cap.