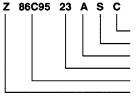

# Z86C95

CMOS Z8® DIGITAL SIGNAL PROCESSOR

#### **FEATURES**

- Complete Microcontroller, 16 I/O Lines, and up to 64 Kbytes of Addressable External Space Each for Program and Data Memory

- Embedded Reduced Instruction Set DSP (Digital Signal Processor) for Digital Servo Control, with 16 x 16-Bit Multiply and Accumulate in One Clock Cycle

- 8-Channel, 8-Bit A/D Converter with Track and Hold and Minimum Single Conversion Time of 2 μs

- 8-Bit D/A Converter with Programmable Gain Stage and a Maximum Settling Time of 3 μs

- Single Channel 40/80 kHz Pulse Width Modulator

- 256-Byte Register File, Including 236 General-Purpose Registers, Four I/O Port Registers and 16 Status and Control Registers

- 16 x 16-Bit Hardwired Multiply and 32-Bit by 16-Bit Divide, Exclusive of DSP

- Four External Vectored Priority Interrupts for I/O, Counter/Timers and UART

- On-Chip Oscillator that Accepts Crystal or External Clock Drive

- Full-Duplex UART

- 16-Bit Counter/Timers with Capture and Compare Registers

- Register Pointer for Short, Fast Instructions to Any One of the 16 Working Register Groups

- Serial Peripheral Interface

- Multiplexed and Demultiplexed Address/Data Bus

- Single +5V Power Supply, All I/O Pins TTL Compatible

- 1.2 Micron CMOS Technology

- Clock Speeds 24 and 33 MHz

- Three Low-Power Standby Modes; STOP, HALT, and PAUSE

- Flash EPROM Write Support

#### **GENERAL DESCRIPTION**

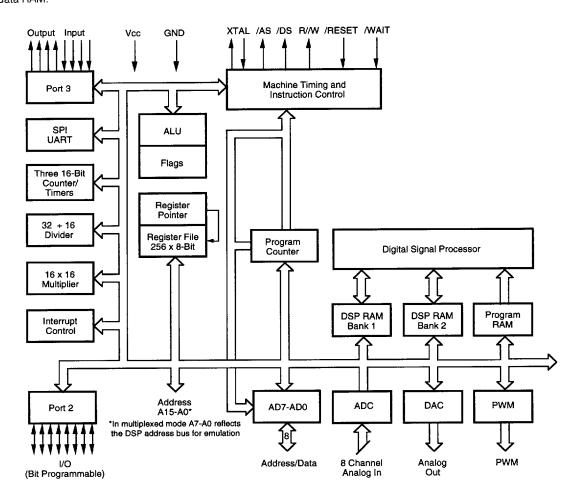

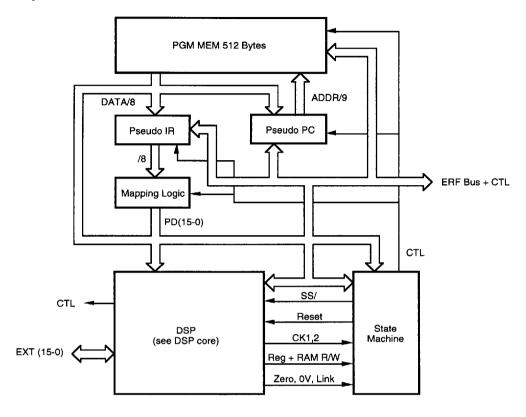

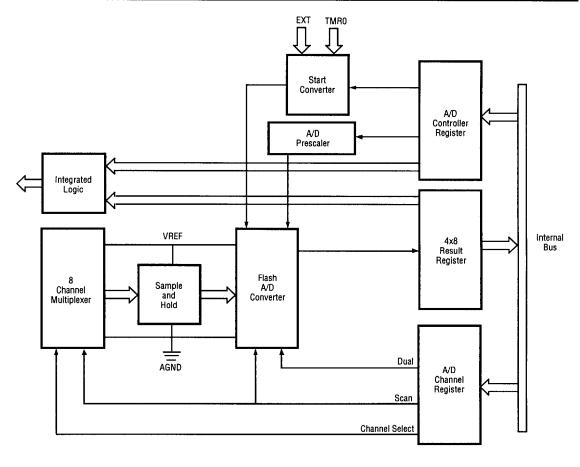

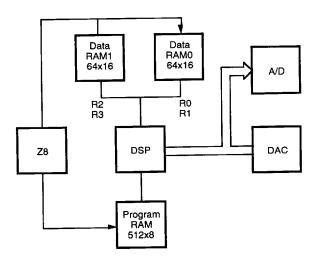

The Z86C95 MCU (Microcontroller Unit) is a member of the Z8\* single-chip microcontroller family incorporating a CMOS ROMless Z8 microcontroller with an embedded DSP processor for digital servo control. The DSP slave processor can perform 16 x 16-bit multiplicates and accumulates in one clock cycle. Additionally, the Z86C95 is further enhanced with a hardwired 16 x 16-bit multiplier and 32-bit/16-bit divider, three 16-bit counter timers with capture and compare registers, a half flash 8-bit A/D converter with a 2 µs conversion time, an 8-bit DAC with 1/4 programmable gain stage, UART, serial peripheral

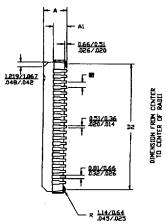

interface, and a PWM output channel (Figure 1). It is fabricated using 1.2 micron CMOS technology and offered in an 80-pin QFP, 84-pin PLCC package, or a 100-pin VQFP (Figures 2, 3, and 4).

The Z86C95 provides up to 16 output address lines. This permits an address space of up to 64 Kbytes of data and program memory each. Eight address outputs (AD7-AD0) are provided by a multiplexed, 8-bit, Address/Data bus. The remaining eight bits are provided through output address bits A15-A8.

5-2

### **GENERAL DESCRIPTION (Continued)**

There are 256 registers located on chip and organized as 236 general-purpose registers, 16 control and status registers, and four I/O port registers. The register file can be divided into 16 groups of 16 working registers each. Configuration of the registers in this manner allows the use of short format instructions; in addition, any of the individual registers can be accessed directly. The Z86C95 contains 256 words of DSP Program RAM configured from the Z8 side as 512 bytes of RAM and 128 words of DSP data RAM.

#### Notae:

All Signals with a preceding front slash, "/", are active Low, e.g., B//W (WORD is active Low); /B/W (BYTE is active Low, only).

Power connections follow conventional descriptions below:

| Connection | Circuit         | Device          |

|------------|-----------------|-----------------|

| Power      | V <sub>cc</sub> | V <sub>DD</sub> |

| Ground     | GND             | V <sub>SS</sub> |

Figure 1. Functional Block Diagram

: SS 9984043 0034823 924 MA

### **PIN DESCRIPTION**

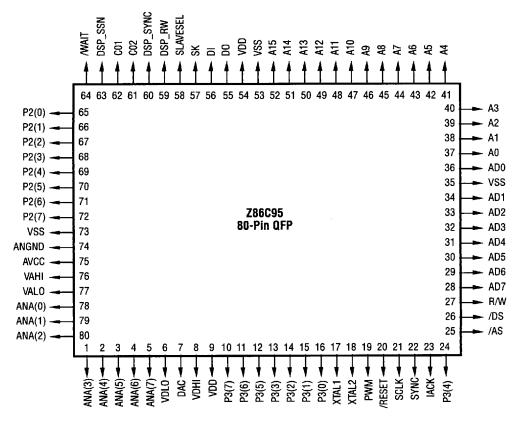

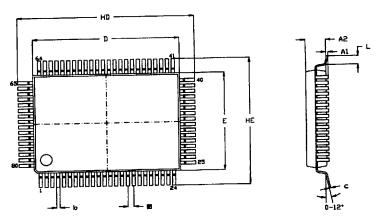

Figure 2. 80-Pin QFP Pin Assignments

### PIN DESCRIPTION (Continued)

Table 1. 80-Pin QFP Pin Identification

| No.         | Symbol                | Function                             | Direction                             |

|-------------|-----------------------|--------------------------------------|---------------------------------------|

| 1-5         | ANA(3)-ANA(7)         | Input to A/D                         | Input                                 |

| 6           | VD <sub>LO</sub>      | Low Ref Volt, DAC                    | Input                                 |

| 7           | DAC                   | D/A Converter Output                 | Output                                |

| 8           | VD <sub>H</sub>       | High Ref Volt, DAC                   | Input                                 |

| 9           | V <sub>DD</sub>       | Digital Power Supply                 | Input                                 |

| 10-12       | P3(7)-P3(5)           | Port 3, Pins 7,6,5                   | Output                                |

|             |                       | Port 3, Pins 3,2,1,0                 | Input                                 |

| 13-16<br>17 | P3(3)-P3(0)<br>XTAL1  | Crystal, OSC CLK                     | Input                                 |

|             |                       | Crystal, OSC CLK<br>Crystal, OSC CLK | Output                                |

| 18<br>19    | XTAL2<br>PWM          | Pulse Width Modulator                | Output                                |

|             |                       |                                      | · · · · · · · · · · · · · · · · · · · |

| 20          | /RESET                | Reset                                | Input                                 |

| 21          | SCLK                  | System Clock                         | Output                                |

| 22          | SYNC                  | Synchronize Pin                      | Output                                |

| 23          | IACK                  | Interrupt Acknowledge                | Output                                |

| 24          | P3(4)                 | Port 3, Pin 4                        | Output                                |

| 25          | /AS                   | Address Strobe                       | Output                                |

| 26          | /DS                   | Data Strobe                          | Output                                |

| 27          | R//W                  | Read/Write                           | Output                                |

| 28-34       | AD7-AD1               | MUX ADD/DATA, Pins 7-1               | Input/Output                          |

| 35          | V <sub>ss</sub>       | Digital Ground                       | Input                                 |

| 36          | AD0                   | MUX ADD/DATA, Pin 0                  | Input/Output                          |

| 37-52       | A0-A15                | External Address                     | Output                                |

| 53          | V <sub>ss</sub>       | Digital Ground                       | Input                                 |

| 54          | v ss<br>V             | Digital Power Supply                 | Input                                 |

| 55          | V <sub>DD</sub><br>DO | SPI Data Out                         | Output                                |

| 56          | DI                    | SPI Data In                          | Input                                 |

| 57          | SK                    | SPI Clock                            | Input/Output                          |

| 58          | SLAVESEL              | Slave Select                         | Input                                 |

| 59          | DSP_RW                | DSP Emulation R/W Pin                | Output                                |

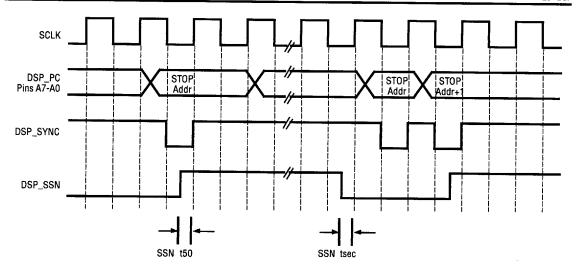

| 60          | DSP_SYNC              | DSP Emulation Sync Pin               | Output                                |

| 61-62       | CO2-CO1               | Compare Outputs for Timer 2          | Output                                |

| 63          | DSP_SSN               | DSP Emulation Single Step Pin        | Input                                 |

|             | MAIT                  | Wait                                 | Input                                 |

| 64          |                       | Port 2. Pins 0-7                     | •                                     |

| 65-72       | P2(0)-P2(7)           | ·                                    | Input, Output                         |

| 73          | V <sub>ss</sub>       | Digital Ground                       | Input                                 |

| 74          | AN <sub>GND</sub>     | Analog Ground                        | Input                                 |

| 75          | AV <sub>CC</sub>      | Analog Power Supply                  | Input                                 |

| 76          | VA                    | High Ref Volt, A/D                   | Input                                 |

| 77          | VA <sub>LO</sub>      | Low Ref Volt, A/D                    | Input                                 |

| 78-80       | ANĂ(0)-ANA(2)         | Input to A/D                         | Input                                 |

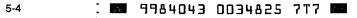

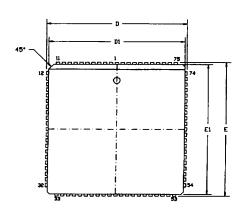

Figure 3. 84-Pin PLCC Pin Assignments

## PIN DESCRIPTION (Continued)

Table 2. 84-Pin PLCC Pin Identification

| No.   | Symbol                       | Function                      | Direction    |

|-------|------------------------------|-------------------------------|--------------|

| 1     | P27                          | Port 2 Pin 7                  | Input/Output |

| 2     | $V_{ss}$                     | Digital Ground                | Input        |

| 3     | AN                           | Analog Ground                 | Input        |

| 4     | AV <sub>CC</sub>             | Analog Power Supply           | Input        |

| 5     | VA <sub>HI</sub>             | High Ref Volt, A/D            | Input        |

| 6     | VA <sub>LO</sub>             | Low Ref Volt, A/D             | Input        |

| 7-10  | ANÃO-ANA3                    | Input to A/D, Pins 0-3        | Input        |

| 12-15 | ANA4-ANA7                    | Input to AD, Pins 5-7         | Input        |

| 16    | VD <sub>LO</sub>             | Low Ref Volt, DAC             | Input        |

| 17    | DAČ                          | D/A Converter Output          | Output       |

| 18    | VD <sub>HI</sub>             | High Ref Volt, DAC            | Input        |

| 19    | V <sub>DD</sub>              | Digital Power Supply          | Input        |

| 20-22 | V <sub>oo</sub> "<br>P37-P35 | Port 3, Pins 7-5              | Output       |

| 23-26 | P33-P30                      | Port 3, Pins 3-0              | Input        |

| 27    | XTAL1                        | Crystal, OSC CLK              | Input        |

| 28    | XTAL2                        | Crystal, OSC CLK              | Output       |

| 29    | PWM                          | Pulse Width Modulator         | Output       |

| 30    | /RESET                       | Reset                         | Input        |

| 31    | SCLK                         | System Clock                  | Output       |

| 32    | SYNC                         | Z8 Emulation Sync Pin         | Output       |

| 33    | N/C                          | No Connection                 |              |

| 34    | IACK                         | Interrupt Acknowledge         | Output       |

| 35    | P34                          | Port 3, Pin 4                 | Output       |

| 36    | /AS                          | Address Strobe                | Output       |

| 37    | /DS                          | Data Strobe                   | Output       |

| 38    | R//W                         | Read/Write                    | Output       |

| 39-45 | AD7-AD1                      | MUX ADD/DATA, Pins 7-1        | Input/Output |

| 46    | $V_{ss}$                     | Digital Ground                | Input        |

| 47    | ADO                          | MUX ADO/DATA Pin 0            | Input/Output |

| 48-51 | A0-A3                        | External Address              | Output       |

| 52    | DSP-A8                       | MSB of DSP PC                 | Output       |

| 53    | A4                           | External Address              | Output       |

| 54-64 | A5-A15                       | External Address              | Output       |

| 65    | $V_{ss}$                     | Digital Ground                | Input        |

| 66    | V <sub>DD</sub>              | Digital Power Supply          | Input        |

| 67    | DO                           | SPI Data Out                  | Output       |

| 68    | DI                           | SPI Data In                   | Input        |

| 69    | SK                           | SPI Clock                     | Input/Output |

| 70    | SLAVESEL                     | Slave Select                  | Input        |

| 71    | DSP_RW                       | DSP Emulation R/W Pin         | Output       |

| 72    | DSP_SYNC                     | DSP Emulation SYNC Pin        | Output       |

| 73-74 | C02-C01                      | Compare Outputs for Timer 2   | Output       |

| 75    | DSP_SSN                      | DSP Emulation Single Step Pin | Output       |

| 76    | N/C                          | No Connection                 |              |

| 77    | WAIT                         | Wait                          | Input        |

| 78-84 | P20-P26                      | Port 2, Pins 0-6              | Input/Output |

5-6 : 9984043 0034827 57T 💌

Powered by ICminer.com Electronic-Library Service CopyRight 2003

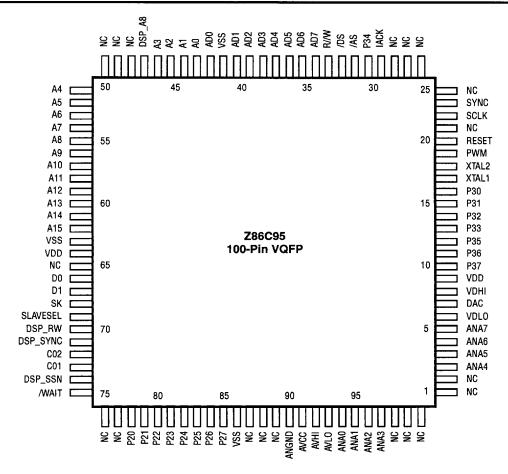

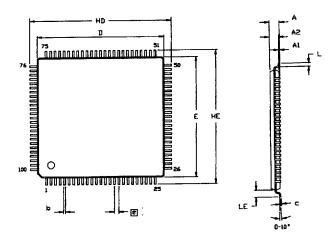

Figure 4. 100-Pin VQFP Pin Assignments

5-8

# PIN DESCRIPTION (Continued)

Table 3. 100-Pin VQFP Pin Identification

| No.    | Symbol           | Function                          | Direction    |

|--------|------------------|-----------------------------------|--------------|

| 1-2    | N/C              | No Connection                     |              |

| 3-6    | ANA4-ANA7        | Input to AD, Pins 5-7             | Input        |

| 7      | VDLO             | Low Ref Volt, DAC                 | Input        |

| 8      | DAC              | D/A Converter Output              | Output       |

| 9      | VDHI             | High Ref Volt, DAC                | Input        |

|        | VDD              | Digital Power Supply              | Input        |

| 10     |                  | , , ,                             | Output       |

| 11-13  | P37-P35          | Port 3, Pins 7-5                  | •            |

| 14-17  | P33-P30          | Port 3, Pins 3-0                  | Input        |

| 18     | XTAL1            | Crystal, OSC CLK                  | Input        |

| 19     | XTAL2            | Crystal, OSC CLK                  | Output       |

| 20     | PWM              | Pulse Width Modulator             | Output       |

| 21     | /RESET           | Reset                             | Input        |

| 22     | N/C              | No Connection                     |              |

| 23     | SCLK             | System Clock                      | Output       |

| 24     | SYNC             | Synchronize Pin                   | Output       |

| 25-28  | N/C              | No Connection                     |              |

| 29     | IACK             | Interrupt Acknowledge             | Output       |

| 30     | P34              | Port 3, Pin 4                     | Output       |

| 31     | /AS              | Address Strobe                    | Output       |

| 32     | /DS              | Data Strobe                       | Output       |

| 33     | R//W             | Read/Write                        | Output       |

| 34-40  | AD7-AD1          | MUX ADD/DATA, Pins 7-1            | Input/Output |

| 41     | VSS              | Digital Ground                    | Input        |

| 42     | AD0              | MUX AD0/DATA Pin 0                | Input/Output |

| 43-46  | A0-A3            | External Address                  | Output       |

| 43-46  | DSP-A8           | MSB of DSP PC                     | Output       |

|        | N/C              | No Connection                     | Output       |

| 48-50  | •                |                                   | Output       |

| 51-62  | A5-A15           | External Address                  | Output       |

| 63     | VSS              | Digital Ground                    | Input        |

| 64     | VDD <sub>.</sub> | Digital Power Supply              | Input        |

| 65     | N/C              | No Connection                     | Outro        |

| 66     | D0               | SPI Data Out                      | Output       |

| 67     | D1               | SPI Data In                       | Input        |

| 68     | SK               | SPI Clock                         | Input/Output |

| 69     | SLAVESEL         | Slave Select                      | Input        |

| 70     | DSP_RW           | DSP Emulation R/W Pin             | Output       |

| 71     | DSP_SYNC         | DSP Emulation SYNC Pin            | Output       |

| 72-73  | C02-C01          | Compare Outputs for Timer 2       | Output       |

| 74     | DSP_SSN          | DSP Emulation Single Step Pin     | Output       |

| 75     | /WAIT            | Wait                              | Input        |

| 76-77  | N/C              | No Connection                     |              |

| 78-85  | P20-P27          | Port 2, Pins 0-6                  | Input/Output |

| 86     | VSS              | Digital Ground                    | Input        |

| 87-89  | N/C              | No Connection                     | 1- 5-7       |

| 90     | ANGND            | Analog Ground                     | Input        |

| 91     | AVCC             | Analog Ground Analog Power Supply | Input        |

| 92     | VAHI             | High Ref Volt, A/D                | Input        |

|        |                  |                                   |              |

| 93     | VALO             | Low Ref Volt, A/D                 | Input        |

| 94-97  | ANAO-ANA3        | Input to A/D, Pins 0-3            | Input        |

| 98-100 | N/C              | No Connection                     |              |

9984043 0034829 342

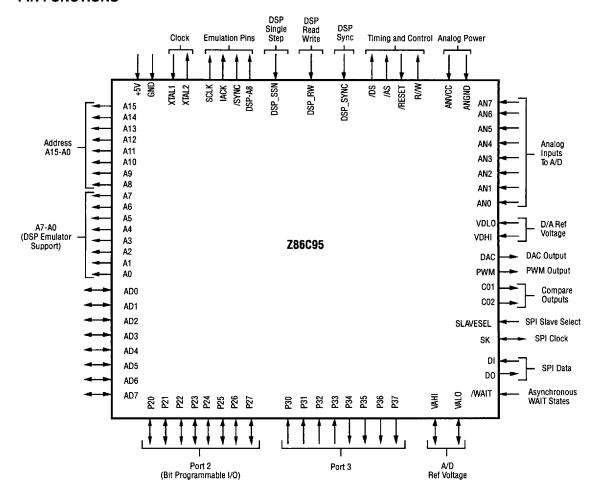

### **PIN FUNCTIONS**

Figure 5. Pin Functions

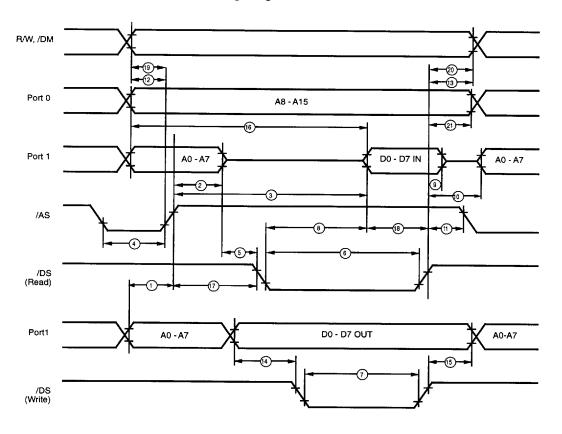

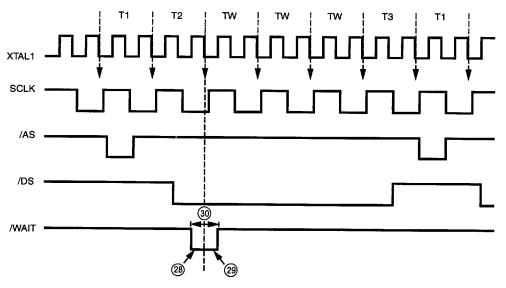

/DS (output, active Low). Data Strobe is activated once for each external memory transfer. For a READ operation, data must be available prior to the trailing edge of /DS. For WRITE operations, the falling edge of /DS indicates that output data is valid. Data Strobe will tri-state in reset.

/AS (output, active Low). Address Strobe is pulsed once at the beginning of each machine cycle. Memory address transfers are valid at the trailing edge of /AS. Under program control, /AS can be placed in the high-impedance state along with Port 1, Data Strobe, and Read/Write.

### PIN FUNCTIONS (Continued)

/RESET (input, active Low). To avoid asynchronous and noisy reset problems, the Z86C95 is equipped with a reset filter of four external clocks (4TpC). If the external /RESET signal is less than 4TpC in duration, no reset occurs.

On the fifth clock after the /RESET is detected, an internal RST signal is latched and held for an internal register count of 18 external clocks, or for the duration of the external /RESET, whichever is longer. During the reset cycle, /DS is held active Low while /AS cycles at a rate of TpC/2. When /RESET is deactivated, program execution begins at location 000CH. Reset time must be held Low for 50 ms or until  $V_{\rm DD}$  is stable, whichever is longer.

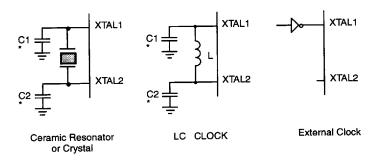

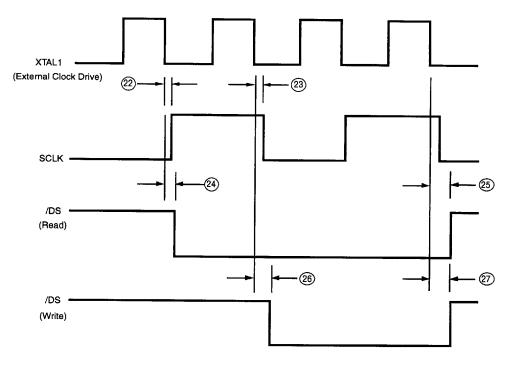

**XTAL1, XTAL2** Crystal 1, Crystal 2 (time-based input and output, respectively). These pins connect a parallel-resonant crystal, ceramic resonator, LC, or any external single-phase clock to the on-chip oscillator and buffer.

**R//W** (output, read High/write Low). The Read/Write signal is low when the MCU is writing to the external program or data memory. Will tri-state in reset.

A15-A8 (output). Demultiplexed high byte of Z8 external address bus, Auto Latch when in reset.

**A7-A0** (output). Demultiplexed low byte of Z8 external address bus or internal DSP address bus.

**AD7-AD0** (input, output). Multiplexed Z8 address/data bus. Auto Latch when in reset.

**AN7-AN0** (analog input). Analog inputs to the A/D converter.

DAC (output). Analog output of the D/A converter.

**PWM** (output). Pulse Width Modulator output. Open-Drain.

CO1 (output). Compare output1 for timer T2.

CO2 (output). Compare output2 for timer T2.

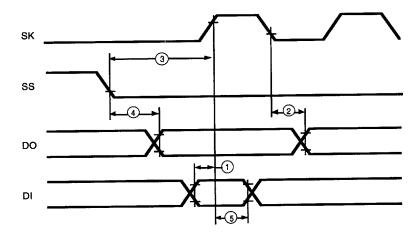

**SLAVESEL** (input, active Low). SPI Slave Select is used in Slave mode to mark the beginning and end of a transaction.

SK (input, output), SPI clock.

**DI** (input, active High). SPI serial data input in both master and slave mode.

DO (output, active High). SPI serial data output.

**WAIT** (input, active Low). Introduces asynchronous wait states into the external memory fetch cycle. When this input goes Low during an external memory access, the Z8 freezes the fetch cycle until this pin goes High. This pin is sampled after /DS goes Low; should be pulled up if not used.

$\mathbf{VA}_{\mathbf{H}}$  (input). Reference voltage (High) for the A/D converter.

$\mathbf{VA_{Lo}}$  (input). Reference voltage (Low) for the A/D converter.

**ANV**<sub>cc</sub> (input). Analog power supply for A/D and D/A.

AN<sub>GND</sub> (input). Analog ground for A/D and D/A.

**VD**<sub>41</sub> (input). Reference voltage (High) for D/A converter.

**VD**<sub>10</sub> (input). Reference voltage (Low) for D/A converter.

**SSTEP** (input, active High). DSP single-step control pin. The DSP processor will execute a NOP instruction and hold the program counter value when this pin is High. /SSTEP is synchronized with the system clock; should be pulled Low if not used.

**SCLK System Clock** (output). The internal system clock is available at this pin.

**IACK Interrupt Acknowledge** (output, active High). This output, when High, indicates that the Z86C95 is in an interrupt cycle.

/SYNC (output, active Low). This signal indicates the last clock cycle of the currently executing instruction.

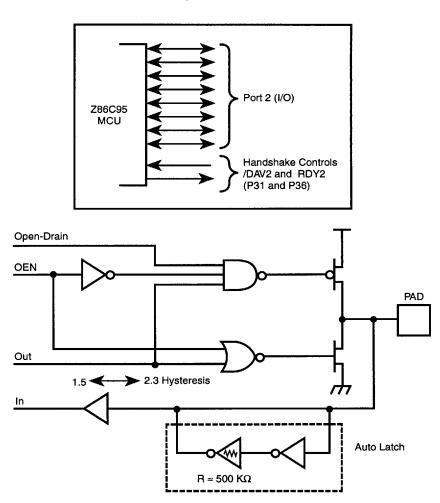

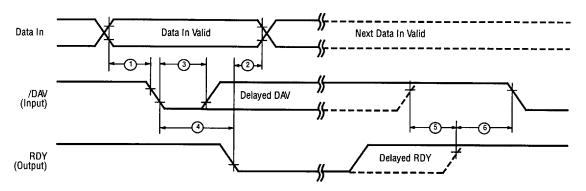

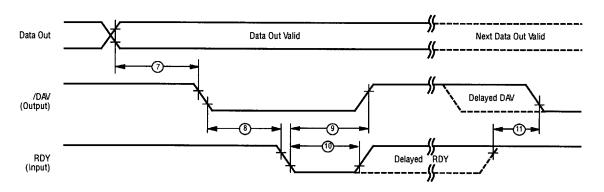

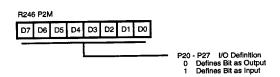

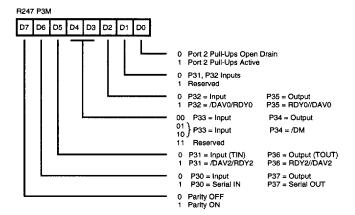

**Port 2** (P27-P20). Port 2 is an 8-bit, bit programmable, bidirectional, CMOS compatible port. Each of these eight I/O lines can be independently programmed as an input or output or globally as an open-drain output. Port 2 is always available for I/O operation. When used as an I/O port, Port 2 may be placed under handshake control. In this configu-

ration, Port 3 lines P31 (Port 3, bit 1) and P36 are used as the handshake controls lines /DAV2 and RDY2. The handshake signal assignment for Port 3 lines P31 and P36 is dictated by the direction (input or output) assigned to P27 (Figure 6).

Figure 6. Port 2 Configuration

### PIN FUNCTIONS (Continued)

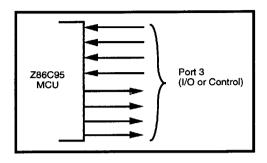

**Port 3** (P37-P30). Port 3 is an 8-bit, CMOS compatible four-fixed input and four-fixed output port. These 8 I/O lines have four-fixed (P33-P30) input and four-fixed (P37-P34)

output ports (Table 3). Port 3 P30 and P37, when used as serial I/O, are programmed as serial in and serial out, respectively (Figure 7).

Figure 7. Port 3 Configuration

Port 3 is configured under software control to provide the following control functions: Handshakes for Ports 2 (/DAV and RDY); four external interrupt request signals (IRQ3-IRQ0); timer input and output signals ( $T_{\text{IN}}$  and  $T_{\text{OUT}}$ ), and Data Memory Select (/DM).

Port 3 lines P37 and P30, can be programmed as serial I/O lines for full-duplex serial asynchronous receiver/transmitter operation. The bit rate is controlled by the Counter/Timer0.

Table 4. Port 3 Pin Assignments

| Pin# | 1/0 | CTC1               | Int. | P2HS | UART       | Ext. |

|------|-----|--------------------|------|------|------------|------|

| P30  | In  |                    | IRQ3 |      | Serial In  |      |

| P31  | In  | T <sub>IN</sub>    | IRQ2 | D/R  |            |      |

| P32  | In  | "4                 | IRQ0 |      |            |      |

| P33  | łn  |                    | IRQ1 |      |            |      |

| P34  | Out |                    |      |      |            | /DM  |

| P35  | Out |                    |      |      |            |      |

| P36  | Out | . T <sub>out</sub> |      | R/D  |            |      |

| P37  | Out | 001                |      |      | Serial Out |      |

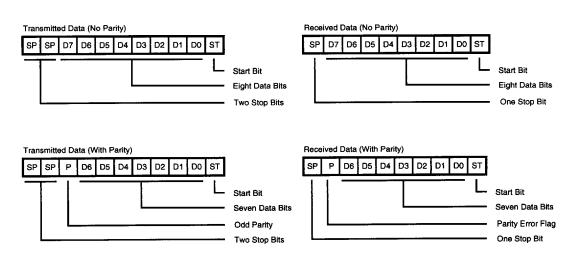

The Z86C95 automatically adds a start bit and two stop bits to transmitted data (Figure 8). Odd parity is also available as an option. Eight data bits are always transmitted, regardless of parity selection. If parity is enabled, the eighth bit is the odd parity bit. An interrupt request (IRQ4) is generated on all transmitted characters.

Received data must have a start bit, eight data bits and at least one stop bit. If parity is On, bit 7 of the received data

is replaced by a parity error flag. Received characters generate the IRQ3 interrupt request.

**Auto Latch.** The Auto Latch puts valid CMOS levels on all CMOS inputs that are not externally driven. Whether this level is 0 or 1, cannot be determined. A valid CMOS level rather, than a floating node, reduces excessive supply current flow in the input buffer.

Figure 8. Serial Data Formats

#### ADDRESS SPACE

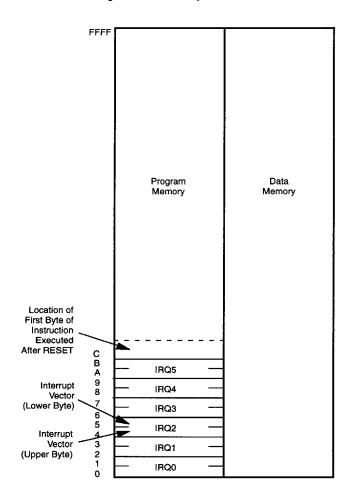

**Program Memory.** The Z86C95 can address up to 64 Kbytes of external program memory (Figure 9). Program execution begins at external location 000CH after a reset.

**Data Memory** (/DM). The Z86C95 can address up to 64 Kbytes of external data memory (Figure 9). External data memory may be included with, or separated from, the external program memory space. /DM, an optional I/O function, that can be programmed to appear on P34 (Port 3, bit 4), is used to distinguish between data and program memory space. The state of the /DM signal is controlled by

the type instruction being executed. An LDC opcode references program (/DM inactive) memory, and an LDE instruction references DATA (/DM active Low) memory. Data Memory will tri-state in reset.

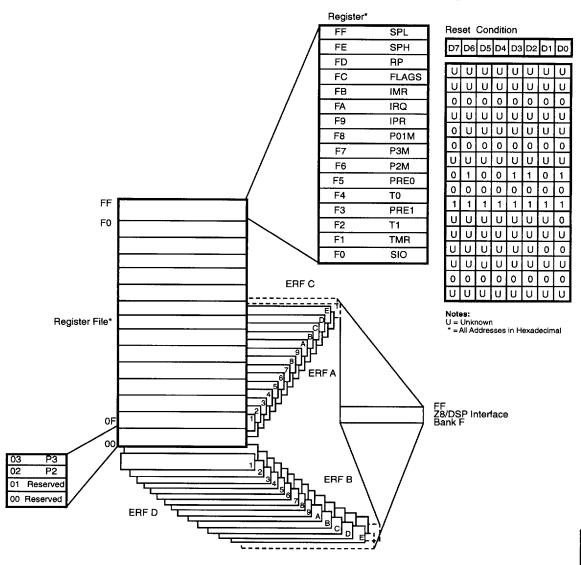

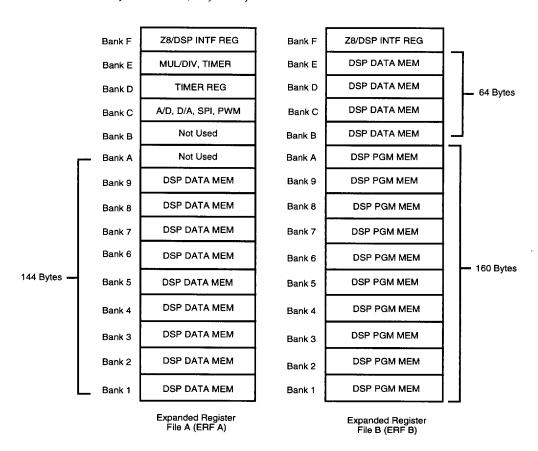

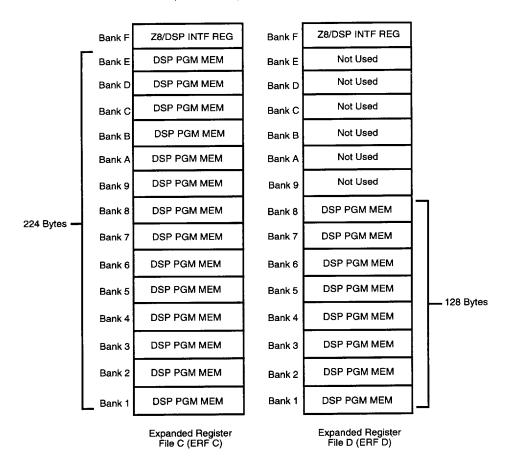

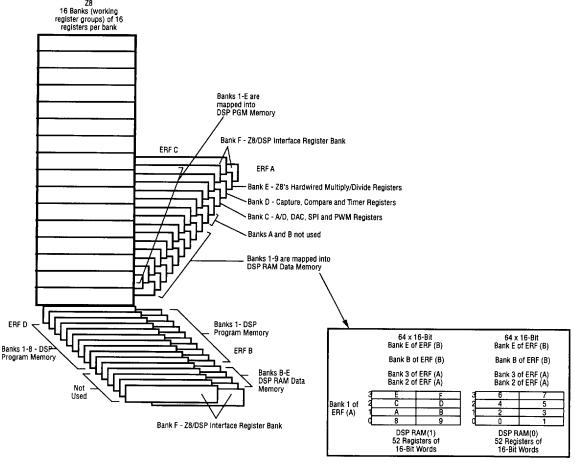

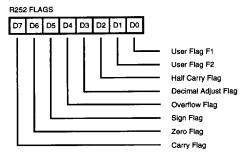

**Register Memory Map.** The Z86C95 register memory space is split into five register files; the original Z8 Register File, Expanded Register File A (ERF-A), Expanded Register File B (ERF-B), Expanded Register File C (ERF-C) and Expanded Register File D (ERF-D) (Figure 10).

Figure 9. Program and Data Memory Configuration

### **Z8 Standard Control Registers**

Figure 10. Register File

### **ADDRESS SPACE** (Continued)

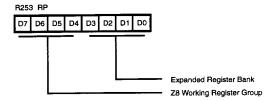

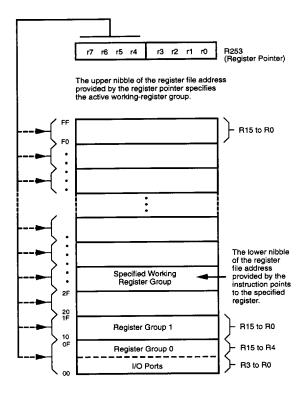

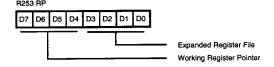

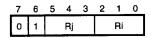

Register File. The Register File consists of four I/O port registers, 236 General-Purpose Registers and 16 control and status registers. The instructions can access registers directly or indirectly through an 8-bit address field. The Z86C95 also allows short 4-bit register addressing using the Register Pointer (Figures 11, 12). In the 4-bit mode, the Register File is divided into 16 working register groups, each occupying 16 contiguous locations. The Register Pointer addresses the starting location of the active working-register group.

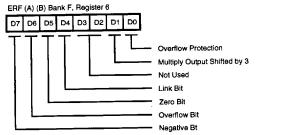

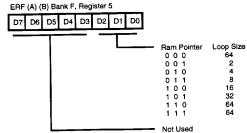

Expanded Register File. The register memory has been further expanded into four additional register files known as Expanded Register Files A thorough D. Each of these register files contain 15 banks of 16 registers per bank. ERF-A stores data for the DSP processor in nine banks of its register space as well as system control registers and peripheral device registers in the remaining six banks. ERF-B contains the remaining four banks of DSP data memory (total DSP data memory is 208 bytes [accessible by the Z8]) as well as ten banks of DSP program memory. ERF-C contains fourteen banks of DSP program memory, and ERF-D contains eight banks of DSP program memory making a total of 512 bytes. Bank F is common to all four Expanded Register Files. Register (8H) in bank F is the Z8/ DSP control register. This register allows a quick means of switching between register files while in the DSP. To do this, bits 5 and 6 of the Z8/DSP control register are used as follows: D6/5 - 00 for ERF-A, D6/5 - 01 for ERF-B, D6/5 - 10 for ERF-C,D6/5 - 11 for ERF-D. On power-up, bits 5 and 6 are reset to 0 thereby enabling access to ERF-A. Bits 7-4 of the register pointer, RP, select the working register bank of the register file while bits 3-0 of the register pointer, RP, selects the working register bank of the Expanded Register File. Once an expanded register bank is selected it is effectively overlaid onto Bank 0 of the Z8's working register file. When an expanded register bank is selected, access to the Z8's ports is turned off.

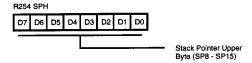

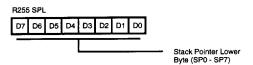

**Stack.** The Z86C95 has a 16-bit Stack Pointer (FEH-FFH) used for external stack that resides anywhere in the data memory. An 8-bit Stack Pointer (FFH) is used for the internal stack that resides within the 236 general-purpose registers (04H-EFH). The High byte of the Stack Pointer (SPI-Bits 15-8) can be used as a general-purpose register when using internal stack only.

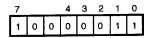

Figure 11. Register Pointer Register

Figure 12. Register Pointer

#### **Z8®/DSP MEMORY INTERFACE**

There are three types of memory spaces residing in the Z8/DSP interface:

- 1. DSP Program Memory. The size of this memory is 512 bytes. This memory space is mapped into ERF-B, C, and D of the Z8. It occupies bank 1 through bank A in ERF-B, bank 1 through bank E in ERF-C, and bank 1 through bank 8 in ERF-D. (Figures 13 and 14).

- DSP Data Memory. There are two data memory banks each 64 x 16 in size called DSP RAM0 and DSP RAM1. This translates to 256 bytes. However, only 208 bytes

- out of 256 are shared between the Z8 and the DSP. Out of this 208 bytes, 144 bytes are mapped to Bank 1 through Bank 9 of ERF-A. The remaining bytes are mapped into Bank B through Bank E of ERF-B.

- Z8/DSP Interface Registers. The register mapping of the various registers which are part of the Z8/DSP interface are shown in Figure 15.

Figure 13. DSP Program and Data Memory

### **Z8/DSP MEMORY INTERFACE** (Continued)

Figure 14. DSP Program and Data Memory

|            | ERF (A) ERF (B) Bank F        |  |  |

|------------|-------------------------------|--|--|

| 9H         | Register Pointer 0 (R0)       |  |  |

| <b>1</b> H | Register Pointer 1 (R1)       |  |  |

| 2H         | Register Pointer 2 (R2)       |  |  |

| 3H         | Register Pointer 3 (R3)       |  |  |

| 4H         | DSP Status Register High Byte |  |  |

| 5H         | DSP Status Register Low Byte  |  |  |

| 6H         | Psuedo Program Counter (LSB)  |  |  |

| 7H         | Psuedo Instruction Register   |  |  |

| 8H         | Z8/DSP Control Register       |  |  |

| АН         | Psuedo Program Counter (MSB)  |  |  |

| СН         | Shadow Latch (LSB)            |  |  |

| DH         | Shadow Latch (MSB)            |  |  |

Figure 15. Z8/DSP Interface Register Mapping

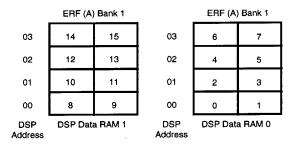

The details of the data memory mapping between the Z8 and the DSP are shown in Figures 16 and 17. For example, Bank 1 of ERF-A is split between DSP RAM1 and RAM0. Bytes 15 through 8 are mapped to DSP RAM1 and bytes 7 through 0 are mapped to DSP RAM0. Similarly, Banks 2, 3 and so on are all split between RAM0 for the first 8 bytes and RAM1 for the last 8 bytes. Also, notice that the higher order bits (15 through 8 of the DSP word) are mapped to an even number byte of the Z8 and the lower order bits of the DSP (7 through 0) are mapped to the odd numbered bytes of the Z8. The size of DSP RAM1 and RAM0 is 64 16-bit words each. These occupy hex addresses 00 through 3F. The following is the bank mapping of Z8 ERF-A and ERF-B to the DSP RAM1 and RAM0.

| DSP RAM1/RAM0 | Z8 Bank          |

|---------------|------------------|

| 00 - 03       | Bank 1 of ERF-A  |

| 04 - 07       | Bank 2 of ERF-A  |

| 08 - 0B       | Bank 3 of ERF-A  |

| 0C - 0F       | Bank 4 of ERF-A  |

| 10 - 13       | Bank 5 of ERF-A  |

| 14 - 17       | Bank 6 of ERF-A  |

| 18 - 1B       | Bank 7 of ERF-A  |

| 1C - 1F       | Bank 8 of ERF-A  |

| 20 - 23       | Bank 9 of ERF-A  |

| 24 - 27       | Bank B of ERF-B  |

| 28 - 2B       | Bank C of ERF-B  |

| 2C - 2F       | Bank D of ERF-B  |

| 30 - 33       | Bank E of ERF-B  |

| 34 - 3F       | Not mapped to Z8 |

#### **Z8/DSP MEMORY INTERFACE** (Continued)

Access to a working bank in ERF-A is achieved by selecting the appropriate lower four bits, 3-0 of the Register Pointer, RP located within the Z8's Standard Register Bank. Bits 5 and 6 of the Z8/DSP control register are used to access the remaining register files as follows: D6/5 - 00 for ERF-A, D6/5 - 01 for ERF-B,D6/5 - 10 for ERF-C,D6/5 - 11 for ERF-D. Notice that bank F in ERF-B or C or D is the same as that of ERF-A. This provides common access to the Z8/DSP control register which allows movement from

3F 3F Not Mapped to Z8 Not Mapped to Z8 34 34 33 33 ERF (B) Bank E ERF (B) Bank E ERF (B) Bank D ERF (B) Bank D ERF (B) Bank C ERF (B) Bank C ERF (B) Bank B ERF (B) Bank B 24 24 23 23 ERF (A) Bank 9 ERF (A) Bank 9 ERF (A) Bank 8 ERF (A) Bank 8 ERF (A) Bank 7 ERF (A) Bank 7 ERF (A) Bank 6 ERF (A) Bank 6 ERF (A) Bank 5 ERF (A) Bank 5 ERF (A) Bank 4 ERF (A) Bank 4 ERF (A) Bank 3 ERF (A) Bank 3 ERF (A) Bank 2 ERF (A) Bank 2 ERF (A) Bank 1 ERF (A) Bank 1 00 00 DSP Data RAM 1 DSP DSP Data RAM 0 DSP Address (64x16) Address (64x16)

Figure 16. Data Memory Mapping of Z8 and DSP

any register file to any other file. In other words, all the registers in bank F can be accessed from any of the four ERFs.

The interface registers (except the Z8/DSP control register) program memory and data memory of the DSP can not be accessed while the DSP is executing from the internal program memory.

Figure 17. Close-Up of ERF (A)

Bank 1 Byte Addressing

**Z8/DSP Interface.** The block diagram of the Z8/DSP interface logic and shared RAM between the Z8 and DSP is shown in Figures 18 and 19.

Figure 18. Block Diagram of Z8/DSP Interface

### **Z8/DSP MEMORY INTERFACE** (Continued)

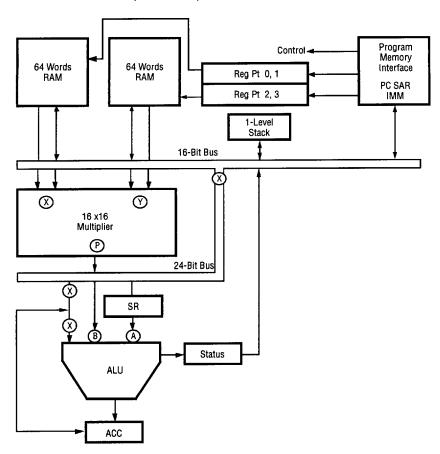

Figure 19. DSP Core

#### Access to DSP Processor

There are three ways to instruct the DSP to execute instructions.

1. Through the internal program memory (512 Bytes):

The program memory can be loaded by the Z8 (series of load immediate instructions). After loading the program memory, the Pseudo-PC can be loaded with the start address for program execution. Loading of the pseudo-PC will start the DSP. The DSP keeps executing until STOP DSP instruction which puts the DSP in the low power mode. As shown in the DSP instruction set, branching is allowed within the program memory space (512 bytes). The instruction execution time in this mode is one state time in the pipeline mode except for Branch and Load Immediate to the register pointers. This takes three and two state times, respectively, in the pipeline mode.

- 2. Another way to start the DSP execution from the internal program memory is to load the Shadow latch register with the start address and set bit 3 of the Z8/ DSP control register to 1. When the A/D converter finishes conversion, it generates an interrupt to the DSP which then loads the pseudo-PC from the shadow latch and start the execution from that location. Notice that this enables a very fast LOOP execution by avoiding a Z8 interrupt wait time delay.

- 3. Through loading the Psuedo-IR with the appropriate instruction:

The DSP instruction (8 bits) is loaded as a Load Immediate data value into the Pseudo-IR. The DSP then wakes up from the power-down mode, executes the instruction and goes back to the power down mode. Since a Load Immediate operation takes six clocks, the instruction execution time in this mode is six clocks. Notice, that branching in this mode can be done by examining the Status register of the DSP which is mapped to the Z8 space (Figure 20).

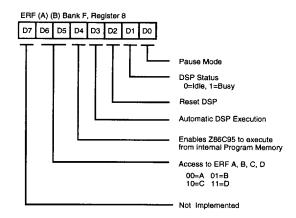

Figure 20. Z8/DSP Control Register

Bits 7 not implemented.

Bits 5, 6 Access to ERF A/B/C/D.

Bit 4 enables the Z8 to execute from internal memory (256 bytes) when set to 1, this bit is automatically reset to 0 on power-up.

Bit 3 enables automatic DSP execution when the A/D completes conversion (when set to 1).

Bit 2 allows reset of the DSP.

Bit 1 indicates the status of the DSP. When bit 1 is set to 1 it indicates the DSP is busy executing from internal program memory. Bit 1 is reset to 0 on power-up.

Bit 0 enables PAUSE mode when set to 1. Bit 0 is reset to 0 on power-up (see power-down mode).

#### **FUNCTIONAL DESCRIPTION**

### **Z8 Multiply/Divide Unit**

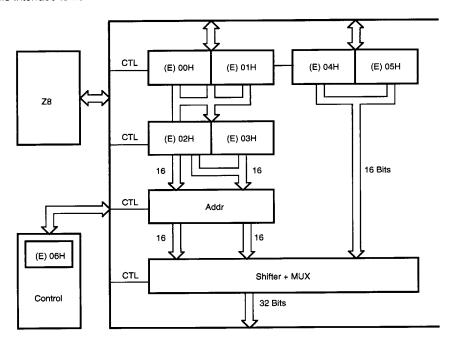

This section describes the basic features, implementation details and the interface between the Z8 and the multiply/ divide unit (Figure 21).

#### Basic features:

- 16 x 16-Bit Multiply with 32-Bit Product

- 32 x 16-Bit Divide with 16-Bit Quotient and 16-Bit Remainder

- Unsigned Integer Data Format

- Simple Interface to Z8

Interface to Z8. The following is a brief description of the register mapping in the multiply/divide unit and its interface to Z8.

The multiply/divide unit is interfaced like a peripheral. The only addressing mode available with the peripheral interface is register addressing. In other words, all the operands are in the respective registers before a multiplication/ division can start.

Figure 21. Z8 Multiply/Divide Unit Block Diagram

Register Mapping. The registers used in the multiply/ divide unit are mapped onto the expanded register file A in Bank E. The exact register locations used are as shown below.

|   | Register | Address |  |

|---|----------|---------|--|

|   | REG0     | (E) 00H |  |

|   | REG1     | (E) 01H |  |

|   | REG2     | (E) 02H |  |

|   | REG3     | (E) 03H |  |

| - | REG4     | (E) 04H |  |

|   | REG5     | (E) 05H |  |

|   | REG6     | (E) 06H |  |

|   | REG7     | (E) 14H |  |

|   | REG8     | (E) 15H |  |

|   |          |         |  |

Register Allocation. The following is the register allocation during multiplication.

| Allocation                                                                                                                                       | Register                             |

|--------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| Multiplier high byte<br>Multiplier low byte<br>Multiplicand high byte                                                                            | REG2<br>REG3<br>REG4                 |

| Multiplicand low byte                                                                                                                            | REG5                                 |

| Result high byte of high word<br>Result low byte of high word<br>Result high byte of low word<br>Result low byte of low word<br>Control register | REG0<br>REG1<br>REG2<br>REG3<br>REG6 |

The following is the register allocation during division.

| Allocation                                                                                                                                                               | Register                                     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| High byte of high word of dividend<br>Low byte of high word of dividend<br>High byte of low word of dividend<br>Low byte of low word of dividend<br>High byte of divisor | REG0<br>REG1<br>REG2<br>REG3<br>REG4         |

| Low byte of divisor High byte of remainder Low byte of remainder High byte of quotient Low byte of quotient Control register                                             | REG5<br>REG0<br>REG1<br>REG2<br>REG3<br>REG6 |

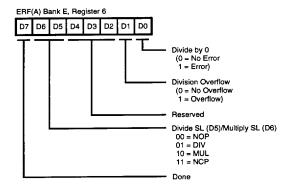

Control Register. The MDCON control register is used to interface with the multiply/divide unit (Figures 22 and 23). Specific functions of various bits in the control register are shown.

**DONE Bit** (D7). This bit is a handshake bit between the math unit and the external world. On power up, this bit is set to 1 to indicate that the math unit has completed the previous operation and is ready to perform the next operation.

Before starting a new multiply/divide operation this bit should be reset to 0 by the processor/programmer. This will indicate that all the data registers have been loaded and the math unit can now begin a multiply/divide operation. During the process of multiplication or division, this bit is write-protected. Once the math unit completes its operation it will set this bit to indicate the completion of operation. The processor/programmer can then read the result.

### **FUNCTIONAL DESCRIPTION** (Continued)

Figure 22. Multiply/Divide Control Register (MDCON)

| General-Purpose Register     |

|------------------------------|

| General-Purpose Register     |

| Compare Register 1 Low Byte  |

| Compare Register 1 High Byte |

| Not Used                     |

| MUL/DIV Control Register     |

| MUL/DIV Register 5           |

| MUL/DIV Register 4           |

| MUL/DIV Register 3           |

| MUL/DIV Register 2           |

| MUL/DIV Register 1           |

| MUL/DIV Register 0           |

Figure 23. ERF (A) Bank E

**MULSL** *Multiply Select* (D6). If this bit is set to 1, it will indicate a multiply operation directive. Like the DONE bit, this bit is also write-protected during math unit operation and is reset to zero by the math unit upon starting of multiply/divide operation.

**DIVSL** Division Select (D5). Similar to D6, D5 will start a division operation.

D4-D2 Reserved.

**DIVOVF** Division Overflow (D1). This bit indicated an overflow during the division process. Division overflow occurs when the high word of the dividend is greater than or equal to the divisor. This bit is read only. When set to 1, it indicates overflow error.

**DIVZR** Division by Zero (D0). When set to 1 this indicates an error of division by 0. This bit is read only.

#### Example:

Upon reset, the status of the MDCON register is 100uuu00b (D7 to D0).

u = Undefined

x = Irrelevant

b = Binary

If multiplication operation is desired, the MDCON register should be set to 010xxxxxb.

If the MDCON register is READ during multiplication, it would have a value of 000uuu00b.

On completion of multiplication, the result of the MDCON register will be 100uuu00b.

If division operation is desired, the MDCON register should be set to 001xxxxxb.

During division operation, the register would contain 000uu??b (? - value depends on the DIVIDEND, DIVISOR).

Upon completion of division operation, the MDCON register would contain 100uuu??b.

Note that once the multiplication/division operation starts, all data registers (REG5 thorough REG0) are write-protected and so are the writable bits of the MDCON register. The write protection is released once the math unit operation is complete. However, the registers can be read any time.

A multiplication sequence would look like:

- 1. Load multiplier and multiplicand.

- 2. Load MDCON register to start multiply operation.

- Wait for the DONE bit of the MDCON register to be set to 1 and then read results.

Note that while the multiply/divide operation is in progress, the programmer can use the Z8 to do other things. Also, since the multiplication/division takes fixed numbers of cycles, the results can be read before the DONE bit is set.

During a division operation, the error flag bits are set at the beginning of the division operation which means the flag bits can be checked by the Z8 while the division operation is being done.

REG7 and REG8 can be used as scratch pad registers or as external data memory address pointers during an LDE instruction. REG0 thorough REG5 and REG7 and REG8, if not used for multiplication or division, can be used as general-purpose registers.

**Performance of Multiplication.** The actual multiplication takes 17 clock cycles. It is expected that the chip would run at a 10 MHz internal clock frequency (external clock

**ABB**.

divided-by-two). This would result in an actual multiplication time (16  $\times$  16-bit) of 1.7  $\mu$ s. If we include the time taken to load and read the registers:

number of clock cycles to load 5 registers = 30 number of clock cycles to read 4 registers = 24

then, the total number of clock cycles is 71. This results in a net multiplication time of 7.1  $\mu$ s. Note that this would be the worst case. This assumes that all of the operands are loaded from the external world as opposed to some of the operands being already in place as a result of a previous operation whose destination register is one of the math unit registers.

**Performance of Division.** The actual division needs 20 clock cycles. This translates to 2.0 µs for the actual division at 10 MHz (internal clock speed). If the time to load operands and read results is included:

number of clock cycles to load operands = 42 number of clock cycles to read results = 24

The total clock cycles to perform a division is 86 cycles. This translates to  $8.6~\mu s$  at 10~MHz.

### **FUNCTIONAL DESCRIPTION (Continued)**

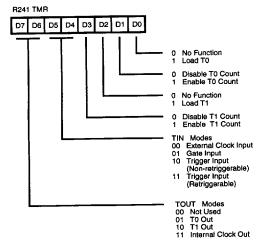

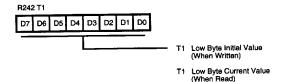

#### Counter/Timers

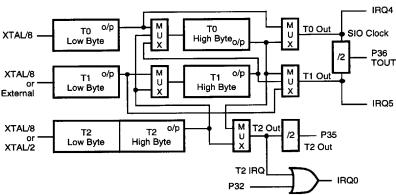

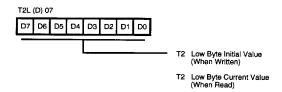

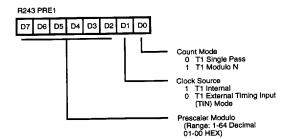

This section describes the enhanced features of the counter/timers (CTC) on the Z86C95 (Figure 24). It contains the register mapping of CTC registers and the bit functions of the newly added Timer2 control register.

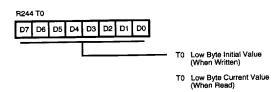

In a standard Z8, there are two 8-bit programmable counter/timers (T0 and T1), each driven by its own 6-bit programmable prescaler. The T1 prescaler can be driven by internal or external clock sources; however, the T0 prescaler is driven by the internal clock only.

The 6-bit prescalers can divide the input frequency of the clock source by any integer number from 1 to 64. Each prescaler drives its counter, which decrements the value (1 to 256) that has been loaded into the counter. When the counter reaches the end of the count, a timer interrupt request, IRQ4 (T0) or IRQ5 (T1), is generated.

The counters can be programmed to start, stop, restart to continue, or restart from the initial value. Also, the counters can be programmed to stop upon reaching zero (single pass mode) or to automatically reload the initial value and continue counting (modulo-n continuous mode).

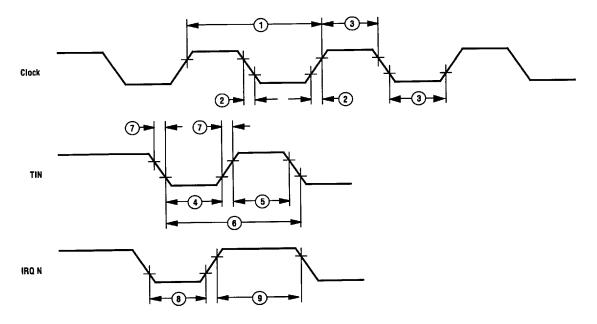

The counters, but not the prescalers, can be read at any time without disturbing their value or count mode. The clock source for T1 is user-definable and can be either the internal microprocessor clock divided by four, or an external signal input through Port 3. The Timer Mode register configures the external timer input (P31) as an external clock, a trigger input that can be retriggerable or non-retriggerable, or as a gate input for the internal clock. The counter/timers can be cascaded by connecting the T0 output to the input of T1. Either T0 or T1 can be outputted through P36.

The following are the enhancements made to the counter/ timer block on the Z86C95:

T0 counter length is extended to 16 bits. For example, T0 now has a 6-bit prescaler and 16-bit down counter.

T1 counter length is extended to 16 bits. For example, T1 now has a 6-bit prescaler and 16-bit down counter.

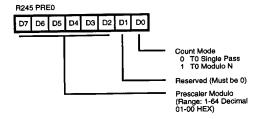

A new counter/timer T2 is added. T2 has a 4-bit prescaler and a 16-bit down counter with three capture registers and two compare registers.

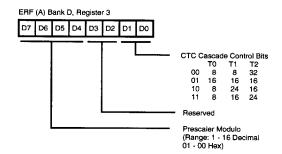

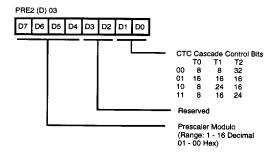

These three counters are cascadable as shown in Table 5. The result is that T2 may be extendable to 32 bits and T1 extendable to 24 bits. Bits 1 and 0 (CAS1 AND CAS0) of the T2 Prescaler Register (PRE2) determine the counter length.

Table 5. Z86C95 Counter Length Configurations

| CAS1 | CAS0 | TO | T1 | T2 |

|------|------|----|----|----|

| 0    | 0    | 8  | 8  | 32 |

| 0    | 1    | 16 | 16 | 16 |

| 1    | 0    | 8  | 24 | 16 |

| 1    | 1    | 8  | 16 | 24 |

|      |      |    |    |    |

The controlling clock input to T2 can be programmed to XTAL/2 or XTAL/8 which results in a resolution of 100 ns at external XTAL clock speed of 20 MHz.

Figure 24. Counter/Timer Block Diagram

### **Capture and Compare**

There are three capture registers associated with T2 HIGH BYTE and T2 LOW BYTE registers and two compare registers on timer T2 (Figure 25). At the falling edge of the appropriate Port 3 input, the current value of Timer 2 (T2) is "captured" into a read only register. For example, the negative going transition on P33 will enable the latching of the current T2 value (16-bits) into the Capture Register 1

(CAP1). The register mapping and the appropriate inputs are shown below (Table 6). Note that the negative transition on P33, P32, and P30 is capable of generating an interrupt. Also, the negative transition on Port 3 will always latch the current T2 value into the capture register. There in no need for a control bit to enable/disable the latching.

ERF (A), Bank D

| (D)0FH | Compare Register 2 Low Byte      |  |

|--------|----------------------------------|--|

| (D)0EH | Compare Register 2 High Byte     |  |

| (D)0DH | Capture Register 3 Low Byte      |  |

| (D)0CH | Capture Register 3 High Byte     |  |

| (D)0BH | Capture Register 2 Low Byte      |  |

| (D)0AH | Capture Register 2 High Byte     |  |

| (D)09H | Capture Register 1 Low Byte      |  |

| (D)08H | Capture Register 1 High Byte     |  |

| (D)07H | Timer2 Low Byte                  |  |

| (D)06H | Timer2 High Byte                 |  |

| (D)05H | Capture/Compare Control Register |  |

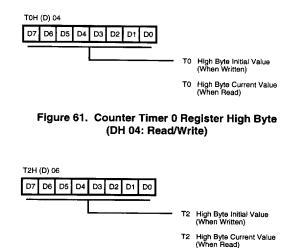

| (D)04H | Timer0 High Byte                 |  |

| (D)03H | Timer2 Prescaler                 |  |

| (D)02H | Timer1 High Byte                 |  |

| (D)01H | Timer2 Mode Register             |  |

|        |                                  |  |

Figure 25. Capture and Compare Registers

Table 6. Capture Register Mapping

| Capture Register | Port 3 | Input   | Addr. High | Addr. Low |

|------------------|--------|---------|------------|-----------|

| CAP1             | P33    | Falling | (D) 8      | (D) 9     |

| CAP2             | P32    | Falling | (D) A      | (D) B     |

| CAP3             | P30    | Falling | (D) C      | (D) D     |

### **FUNCTIONAL DESCRIPTION** (Continued)

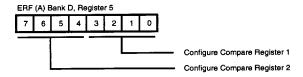

**Compare Registers.** Whenever the current value of T2 equals the contents of the compare register, some action is taken depending on the contents of the T2 Compare

**Control Register** (COMCON). Also, a successful comparison can generate an interrupt (if enabled) and also set a bit in the control register that can be polled at a later date (Figure 26).

**COM2** Compare 2 (D7). This bit is set to 1 when the contents of Compare Register 2 (COM2) match the current value of T2. This bit will have to be cleared by the interrupt polling routine.

**Interrupt Enable 2** (D6). This bit, when set to 1, will enable the interrupt for COM2.

**CO2 Output** (D5,D4). Controls the value outputted on CO2 according to Table 7.

**COM1** Compare 1 (D3). This bit is set to 1 when the contents of Compare Register 1 (COM1) match the current value of T2. This bit will have to be cleared by the interrupt polling routine (Table 8).

Interrupt Enable 1 (D2). This bit when set to 1 enables the interrupt for COM1. When either D6 or D2 is set and the corresponding compare register contents match the current value of T2, an interrupt is generated on IRQ5, which is configured as an OR of T1IRQ, COM1, or COM2 interrupts.

Figure 26. T2 Compare Control Register (COMCON)

**CO1 Output** (D1,D0). Controls the value outputted on CO1 according to the following table:

Table 7. Compare Output Status

|   | 5 Bit 4<br>1 Bit 0 | Output on Compare Output            |

|---|--------------------|-------------------------------------|

| 0 | 0                  | NOP (CO1/CO2 retain previous value) |

| 0 | 1                  | Reset to "0"                        |

| 1 | 0                  | Set to "1"                          |

| 1 | 1                  | Toggle status                       |

Table 8. Compare Register Mapping

|   | Compare Register | Addr. High | Addr. Low |

|---|------------------|------------|-----------|

| • | COM1             | (E) C      | (E) D     |

|   | COM2             | (D) E      | (D) F     |

#### Observations:

Except for the programmable down counter length and clock input, T2 is identical to T0.

TO and T1 retain all their features except that now they are extendable interims of the down counter length.

The output of T2, under program control, can go to an output pin (P35). Also, the interrupt generated by T2 can be ORed with the interrupt request generated by P32. Note that the service routine then has to poll the T2 flag bit and also clear it (bit 7 of T2 Timer Mode Register).

On power up, T0 and T1 are configured in the 8-bit down counter length mode (to be compatible with Z86C91) and T2 is in the 32-bit mode with its output disabled (no interrupt is generated and T2 output DOES NOT go to port P35).

The UART uses T0 for generating the bit clock. This means, while using UART T0 should be in 8-bit mode. So, while using the UART there are only two independent timer/counters.

The counters are configured in the following manner:

| T0 in 8-bit mode<br>T0 in 16-bit mode  | T0 Low byte<br>T0 High byte, T0 Low byte                               |

|----------------------------------------|------------------------------------------------------------------------|

| T1 in 8-bit mode<br>T1 in 16-bit mode  | T1 Low byte<br>T1 High byte, T1 Low byte                               |

| T1 in 24-bit mode                      | T0 High byte, T1 High byte<br>T1 Low byte                              |

| T2 in 16-bit mode<br>T2 in 24-bit mode | T2 High byte, T2 Low byte<br>T0 High byte, T2 High byte<br>T2 Low byte |

| T2 in 32-bit mode                      | T0 High byte, T1 High byte,<br>T2 High byte, T2 Low byte               |

Note that the T2 interrupt is logically 0Red with P32 to generate IRQ0.

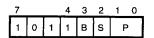

The T2 Timer Mode register is shown in Figure 27. Upon reaching end of count, bit 7 of this register is set to 1. This bit IS NOT reset in hardware and it has to be cleared by the interrupt service routine.

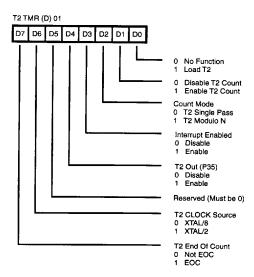

ERF (A) Bank D, Register 1 D6 D5 D4 D3 D2 D1 DO 0 No Function 1 Load T2 Disable T2 Count Enable T2 Count Count Mode T2 Single Pass 1 T2 Modulo N Interrupt Enabled Disable Enable T2 Out (P35) Disable Enable Reserved (Must be 0) T2 CLOCK Source XTAL/8 1 XTAL/2 T2 End Of Count 0 Not EOC EOC

Figure 27. T2 Timer Mode Register (T2)

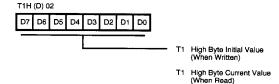

The register map of the new CTC registers is shown in Figure 12. TO High byte, T1 High byte are at the same relative locations as their respective Low bytes, but in a different register bank.

The T2 prescaler register is shown in Figure 28. Bit 1 and Bit 0 of this register controls the various cascade modes of the counters as shown in Table 1.

Figure 28. T2 Prescaler Register (PRE2)

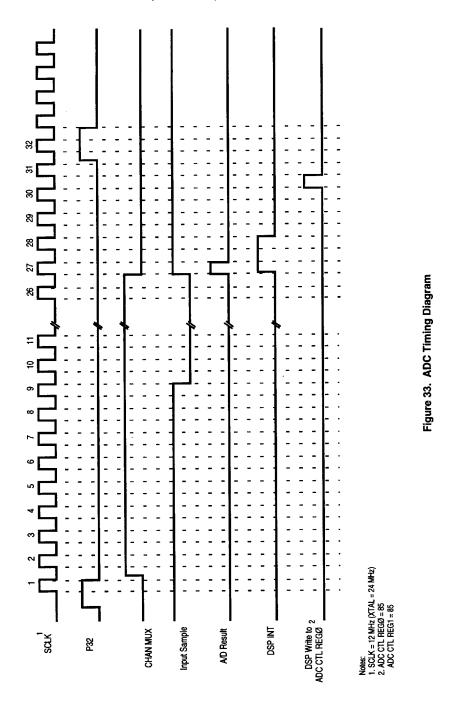

### Analog to Digital Converter (ADC)

The ADC is an 8-bit half flash converter which uses two reference resistor ladders for its upper 4 bits (MSBs) and lower 4 bits (LSBs) conversion. Two reference voltage pins,  $VA_{HI}$  (High) and  $VA_{LO}$  (Low), are provided for external reference voltage supplies. During the sampling period from one of the eight channel inputs, the converter is also being auto-zeroed before starting the conversion. The conversion time is dependent on the external clock frequency and the selection of the prescaler value for the internal ADC clock source. The minimum conversion time is 2.0  $\mu$ s. (See Figure 29, ADC Architecture.)

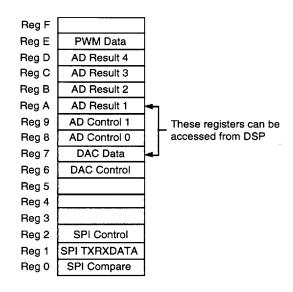

The ADC is controlled by the Z8 and its six registers (two Control and four Result) are mapped into the Extended Register File. The first Result register is also readable by the DSP. The DSP can access the ADC control register 0, and this allows the DSP to change Input Channel selections.

A conversion can be initiated in one of four ways: by writing to the Command register, from a rising or falling edge on Port 32 pin or Timer 0 equal 0. These four are programmable selectable. There are four modes of operation that can be selected: one channel converted four times with the results written to each Result register, one channel continuously converted and one Result channel updated for each conversion, four channels converted once each and the four results written to the Result registers, and four channels repeatedly converted and the Result registers kept updated. The channel to be converted is programmable and if one of the four-channel modes is selected then the programmed channel will be the first channel

converted and the other three will be in sequence following with wraparound from Channel 7 to Channel 0.

The start commands are implemented in such a way as to begin a conversion at any time, if a conversion is in progress and a new start command is received, then the conversion in progress will be aborted and a new conversion will be initiated. This allows the programmed values to be changed without affecting a conversion-in-progress. The new values will take effect only after a new start command is received.

The clock prescaler can be programmed to derive a minimum 2 µs conversion time for XTAL clock inputs from 4 MHz to 20 MHz. For example, with a 20 MHz XTAL clock the prescaler should be programmed for divide by 40 which then gives a 2 µs conversion rate.

The ADC can generate an Interrupt after either the first or fourth conversion is complete depending on the programmable selection.

The ADC can be disabled (for low power) or enabled by a Control Register bit.

Though the ADC will function for a smaller input voltage and voltage reference, the noise and offsets remain constant over the specified electrical range. The errors of the converter will increase and the conversion time may also take slightly longer due to smaller input signals.

Figure 29. ADC Architecture

### FUNCTIONAL DESCRIPTION (Continued)

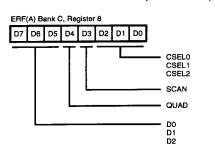

Figure 30. ADC Control Register 0

Prescaler Values (bits 7, 6, 5).

| D2 | D1 | D0 | Prescaler<br>(XTAL divided by) |

|----|----|----|--------------------------------|

| 0  | 0  | 0  | 8                              |

| 0  | 0  | 0  | 128*                           |

| 0  | 0  | 1  | 16                             |

| 0  | 1  | 0  | 24                             |

| 0  | 1  | 1  | 32                             |

| 1  | 0  | 0  | 40                             |

| 1  | 0  | 1  | 48                             |

| 1  | 1  | 0  | 56                             |

| 1  | 1  | 1  | 64                             |

The ADC is being characterized as of this date. The errors of the converter are estimated to increase to 2LSBs (Integral non-linearity), 1 LSB (Differential non-linearity) and 10mV (Zero error at 25°C) if the voltage swing on the reference ladder is decreased to -3V.

#### Modes (bits 4, 3).

| QUAD | SCAN |                                            |

|------|------|--------------------------------------------|

| 0    | 0    | Convert selected channel 4 times then stop |

| 0    | 1    | Convert selected channel then stop         |

| 1    | 0    | Convert 4 channels then stop               |

| 1    | 1    | Convert 4 channels continuously            |

Channel Select (bits 2, 1, 0).

| CSEL2 | CSEL1 | CSEL0 | Channel |

|-------|-------|-------|---------|

| 0     | 0     | 0     | 0       |

| 0     | 0     | 1     | 1       |

| 0     | 1     | 0     | 2       |

| 0     | 1     | 1     | 3       |

| 1     | 0     | 0     | 4       |

| 1     | 0     | 1     | 5       |

| 1     | 1     | 0     | 6       |

| 1     | 1     | 1     | 7       |

<sup>\* 33</sup> MHz Device only.

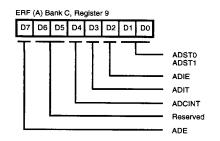

Figure 31. ADC Control Register 1

**ADE** (bit 7). A0 disables any A/D conversions or accessing any ADC registers except writing to ADE bit. A1 Enables all ADC accesses.

Reserved (bits 6, 5). Reserved for future use.

**ADCINT** (bit 4). This is the ADC Interrupt bit and is read only by the Z8, the ADCINT will be reset any time this register is written.

**ADIT** (bit 3). This bit selects when to set the ADC Interrupt if ADIE=1. A 0 sets the Interrupt after the first A/D conversion is complete. A 1 sets the Interrupt after the fourth A/D conversion is complete.

**ADIE** (bit 2). This is the ADC Interrupt Enable. A 0 disables setting the ADC Interrupt. A 1 enables setting the ADC Interrupt.

#### START (bits 1, 0).

| ADST1 | ADST0 | Mode                                             |

|-------|-------|--------------------------------------------------|

| 0     | 0     | Conversion starts when this register is written. |

| 0     | 1     | Conversion starts on a rising edge at Port 3-2.  |

| 1     | 0     | Conversion starts on a falling edge at Port 3-2. |

| 1     | 1     | Conversion starts when Timer0 times out.         |

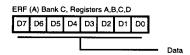

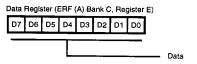

These are the four ADC result registers, Reg-A holds the first result and Reg-D the fourth result. These registers are R/W by the Z8 (Writable for test purposes) and Reg-A is Read Only by the DSP and is mapped to Reg 1 for the DSP. Figure 32 shows the timing diagram for the ADC.

Figure 32. Result Registers

## FUNCTIONAL DESCRIPTION (Continued)

5-36

· 9984043 003485? 20?

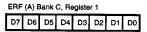

Figure 34. ERF(A) Bank C

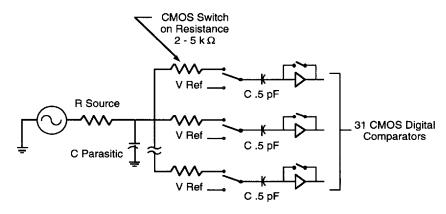

Figure 35 shows the input circuit of the ADC. When conversion starts the analog input voltage from one of the eight channel inputs is connected to the MSB and LSB flash converter inputs as shown in the Input Impedance CKT diagram. Effectively, shunting 31 parallel internal resistance of the analog switches and simultaneously charging 31 parallel 0.5 pF capacitors, which is equivalent to seeing a 400 Ohms input impedance in parallel with a

16 pF capacitor. Other input stray capacitance adds about 10 pF to the input load. For input source resistances up to 2 kOhms can be used under normal operating condition without any degradation of the input settling time. For larger input source resistance, longer conversion cycle time may be required to compensate the input settling time problem.

Figure 35. Input Impedance of ADC

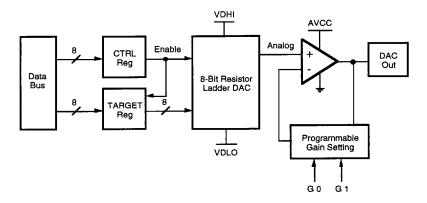

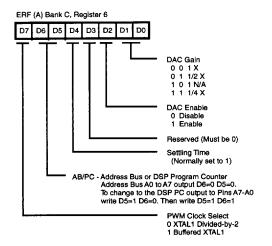

# Digital to Analog Converter (DAC)

The DAC (Digital to Analog Converter) is an 8-bit resistor string, with a programmable 0.25X and 0.5X gain output buffer. The DAC output voltage is settled after the internal digital data is latched. Two pins are provided externally for

the DAC reference voltage supplies,  $VD_{HI}$  and  $VD_{LO}$ , these should not exceed the supply voltages. The DAC output is latch-up protected and can drive output loads (Figure 36).

Figure 36. DAC Block Diagram

The DAC is controlled by the Z8. Its two registers (Control 1 and Data 1) are mapped into the ERF (Figures 37 and 38). The Data 1 register is writable by the DSP.

The DAC can be enabled or disabled by programming the Control 1 register or it can be programmed to output an analog voltage when the Data 1 register is loaded. The Control 1 register is used to program for the Gain factor of the DAC output.

The DAC Data Register is initialized to 80H on power-up (Figure 38). Also the DAC gain control pivots about a midpoint rather than ground. (Figure 38). When the gain control is at 1.0X or 0.5X or 0.25X the DAC output remains constant when the DAC data register equals 80H (Figure 39).

Figure 38. DAC Data Register

Figure 37. DAC Control Register

9984043 0034859 O8T 📨

Figure 39. Gain Control on DAC

# FUNCTIONAL DESCRIPTION (Continued)

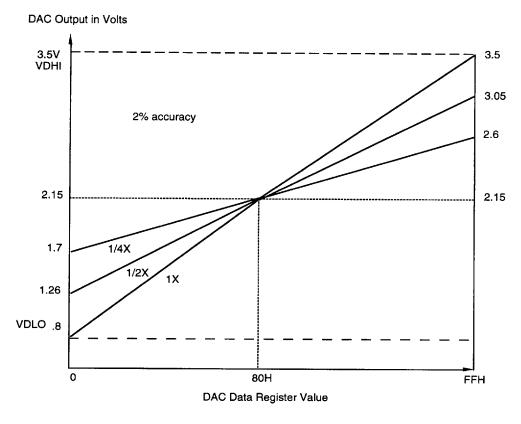

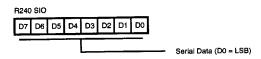

# Serial Peripheral Interface

Serial Peripheral Interface (SPI). The Z86C95 incorporates a serial peripheral interface for communication with other microcontrollers and peripherals. The SPI includes features such as Master/Slave selection and Compare mode. The SPI consists of four registers; SPI Control Register (SCON), SPI Compare Register (SCOMP), SPI Receive/Buffer Register (RxBUF), and SPI Shift Register (Figures 40, 41, and 42). SCON is located in bank C of the Expanded Register Group at Address 02. This register is a read/write register that controls; Master/Slave selection, interrupts, clock source and phase selection, and error flag. Bit 0 enables/disables the SPI with the default being SPI disabled. A 1 in this location enables the SPI, and a 0 disables the SPI.

Bits 1 and 2 of the SCON register in Master Mode selects the clock rate. The user may choose whether internal clock is divide by 2, 4, 8, or 16. In Slave Mode, Bit 1 of this register flags the user if an overrun of the RxBUF Register has occurred.

The RxCharOverrun flag can only be reset by writing a 0 to this bit. In slave mode, bit 2 of the Control Register can disable the data-out I/O function. If a 1 is written to this bit, the data-out pin is tri-stated. If a 0 is written to this bit, the SPI will shift out one bit for each bit received. Bit 3 of the SCON Register enables the interrupt of the SPI, with the default being disabled. Bit 4 signals that a receive character is available in the RxBUF Register. If the associated

IRQ0 is enabled, an interrupt is generated. Bit 5 controls the clock phase of the SPI. A 1 in Bit 5 allows for receiving data on the clock's falling edge and transmitting data on the clock's rising edge. A 0 allows receiving data on the clock's rising edge and transmitting on the clock's falling edge.

The SPI clock source is defined in bit 6 for Master mode. A 1 uses Timer0 output for the SPI clock, and a 0 uses TCLK for clocking the SPI. In Slave mode, bit 6 will enable or disable the address compare feature. Finally, bit 7 determines whether the SPI is used as a Master or a Slave. A 1 puts the SPI into Master mode and a 0 puts the SPI into Slave mode.

SPI Operation. The SPI can be used in one of two modes; either as system slave, or a system master. In the slave mode, data transfer starts when the slave select (SLAVESEL) pin goes active. Data is transferred into the slave's SPI Shift Register, through the DI pin, which has the same address as the RxBUF Register. After a byte of data has been received by the SPI Shift Register a Receive Character Available (RCA/IRQO) interrupt and flag is generated. The next byte of data may be received at this time, but the RxBUF Register must be cleared, or a Receive Character Overrun (RxCharOverrun) flag is set in the SCON Register and the data in the RxBUF Register is overwritten.

Figure 40. SPI Control Register (SCON)

Figure 41. SPI TXRXDATA Register

ERF (A) Bank C, Register 0

D7 D6 D5 D4 D3 D2 D1 D0

Figure 42. SPI Compare Register

# Serial Peripheral Interface (Continued)

When the communication between the master and slave is complete, the SS goes inactive. Unless disconnected, for every bit that is transferred into the slave through the DI pin, a bit is transferred out through the DO pin on the opposite clock edge. During slave operation, the SPI clock pin (SK) is an input (Figure 43). In master mode, the CPU must first activate a SS through one of it's I/O ports. Next, data is transferred through the master's DO pin one bit per master clock cycle. Loading data into the shift register initiates the transfer. In master mode, the master's clock drives the slave's clock. At the conclusion of a transfer, a Receive Character Available (RCA/IRQO) interrupt and flag is generated. Before data is transferred through the DO pin, the SPI Enable bit in the SCON Register must be enabled.

SPI Compare. When the SPI Compare Enable bit, D6 of the SCON Register is set to 1, the SPI Compare feature is enabled. The compare feature is only valid for slave mode. A compare transaction begins when the SS line goes active. Data is received as if it were a normal transaction, but there is no data transmitted to avoid bus contention with other slave devices. When the compare byte is received, IRQ0 is not generated. Instead, the data is compared with the contents of the SCOMP Register. If the data does not match, DO will remain inactive and the slave will ignore all data until the SS signal is reset.

**SPI Clock.** The SPI clock can be driven from three sources; with Timer0, a division of the internal system clock, or an external master when in slave mode. Bit D6 of the SCON Register controls what source drives the SPI clock. Divided-by-2, 4, 8, or 16 can be chosen as the scaler with bits D2. D1 in master mode.

Receive Character Available and Overrun. When a complete data stream is received an interrupt is generated and the RxCharAvail bit in the SCON Register is set. Bit 4 in the SCON Register is for enabling or disabling the RxCharAvail interrupt. The RxCharAvail bit is available for interrupt polling purposes and is reset when the RxBUF Register is read. RxCharAvail is generated in both master and slave modes. While in slave mode, if the RxBUF is not read before the next data stream is received and loaded into the RxBUF Register, Receive Character Overrun (RxCharOverrun) occurs. Since there is no need for clock control in slave mode, bit D1 in the SPI Control Register is used to log any RxCharOverrun.

Figure 43. SPI Timing

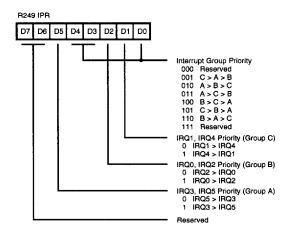

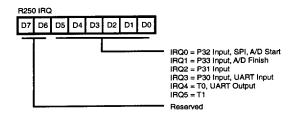

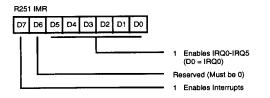

### Interrupts

The Z86C95 has six different interrupts from ten different sources (Table 9). The interrupts are maskable and prioritized. The eight sources are divided as follow: four sources are claimed by Port 3 lines P33-P30, one is Serial Out, one is Serial In, and two in the counter/timers. The Interrupt Mask Register globally or individually enables or disables the six interrupt requests. When more than one interrupt is pending, priorities are resolved by a programmable priority encoder that is controlled by the Interrupt Priority register. All Z86C95 interrupts are vectored through locations in the program memory. When an interrupt machine cycle is activated an interrupt request is granted. Thus, this disables all of the subsequent interrupts, save the Program Counter and Status Flags, and then branches to the program memory vector location reserved for that interrupt. This memory location and the next byte contain the 16-bit address of the interrupt service routine for that particular interrupt request.

To accommodate polled interrupt systems, interrupt inputs are masked and the Interrupt Request register is polled to determine which of the interrupt requests need service. Software initiated interrupts are supported by setting the appropriate bit in the Interrupt Request Register (IRQ).

Internal interrupt requests are sampled on the falling edge of the last cycle of every instruction, and the interrupt request must be valid 5TpC before the falling edge of the last clock cycle of the currently executing instruction.

When the device samples a valid interrupt request, the next 48 (external) clock cycles are used to prioritize the interrupt, and push the two PC bytes and the FLAG register on the stack. The following nine cycles are used to fetch the interrupt vector from external memory. The first byte of the interrupt service routine is fetched beginning on the 58th TpC cycle following the internal sample point, which corresponds to the 63rd TpC cycle following the external interrupts on the Z86C95.

Table 9. Z86C95 Interrupts

| Name | Source                | Vector | Comments               |

|------|-----------------------|--------|------------------------|

| IRQ0 | P3.2, SPI, A/D Start  | 0.1    | Falling Edge Triggered |

| IRQ1 | P3.3, A/D Finish      | 2,3    | Falling Edge Triggered |

| IRQ2 | P3.2, T <sub>IN</sub> | 4,5    | Falling Edge Triggered |

| IRQ3 | P3.0, Serial In       | 6,7    | Falling Edge Triggered |

| IRQ4 | T0, Serial Out        | 8,9    | Internal               |

| iRQ5 | T1                    | 10.11  | Internal               |

### FUNCTIONAL DESCRIPTION (Continued)

### Clock

The Z86C95 on-chip oscillator has a high-gain, parallelresonant amplifier for connection to a crystal, LC, ceramic resonator, or any suitable external clock source (XTAL1 = input, XTAL2 = Output). The crystal should be AT cut, 1 MHz to 24 MHz max, and series resistance (RS) is less than or equal to 100 Ohms. The crystal should be connected across XTAL1 and XTAL2 using the crystal vendor's recommended capacitors (10 pF < CL < 100 pF) from each pin  $V_{cs}$  pin (Figure 44).

<sup>\*</sup> VSS pin, not system ground

Figure 44. Oscillator Configuration

### **Power Down Modes**

HALT. Will turn off the internal CPU clock but not the XTAL oscillation. The counter/timers and the external interrupt IRQ0, IRQ1, IRQ2, and IRQ3 remains active. The devices may be recovered by interrupts, either externally or internally generated. An interrupt request must be executed (enabled) to exit HALT mode. After the interrupt service routine, the program continues from the instruction after the HALT.

**STOP.** This instruction turns off the internal clock and external crystal oscillation and reduces the standby current to 10 µA or less. The STOP mode is terminated by a /RESET, which causes the processor to restart the application program at address 000CH.

In order to enter STOP (or HALT) mode, it is necessary to first flush the instruction pipeline to avoid suspending execution in mid-instruction. To do this, the user must execute a NOP (opcode=OFFH) immediately before the appropriate sleep instruction. i.e.:

FF NOP ; clear the pipeline 6F STOP ; enter STOP mode

or

FF NOP ; clear the pipeline 7F HALT ; enter HALT mode

PAUSE. This is similar to the STOP mode, except in the recovery method, and the fact that the program counter simply continues from where it paused instead of resetting to 000CH. PAUSE mode is entered by setting bit 0 of DSP control register to 1 and executing a HALT instruction. All the internal clocks are stopped during the PAUSE mode thus resulting in very low power. To recover from the PAUSE mode, the Z86C95 needs to see a negative going transition on Port 32. This generates an interrupt and operation can resume by simply doing an IRET in the interrupt execution routine. The recovery time from PAUSE mode is equal to the XTAL oscillator stabilization time +1.3 ms (XTAL frequency of 20 MHz).

# Pulse Width Modulator (PWM)

This block provides a Pulse Width Modulated output at a constant period based on the input clock.

The PWM provides an output waveform whose period is either the internal system clock or the buffered XTAL input divided by 256. The duty cycle of this waveform is programmable by a register in the Extended Register File of the Z8 and can have values from 0 to 99.6% (Reg = 0 to 255). A programmed value of 0 will disable the counter and place the PWM in a low power mode. Any non-zero value programmed in this register will enable the PWM divider and generate the selected output waveform.

The clock source for the PWM is programmable providing the user access to a higher frequency clock versus using the internal clock. The clock source is selected using Bit 7 of the DAC control register (ERF(A) Bank C, Register 6). D7=1 selects a buffered XTAL1 clock, D7=0 selects XTAL divided-by-2 (Figure 37).

Figure 45. Pulse Width Modulation Register Assignment

The PWM register is used to program the duty cycle of the PWM. If the programmed value is 0, then the PWM is disabled and the PWM output is OFF. For any non-zero value the PWM output is a periodic waveform which is High for (value/256)X100% of the period.

# **DIGITAL SIGNAL PROCESSOR**

The DSP slave processor is a 16-bit fixed point, two's complement high-speed digital signal processor. The basic concept behind the DSP megacell is to simplify the architecture and instructions as much as possible, providing a user-friendly programming environment for various DSP algorithms (Figure 47). Additionally, a convenient mapping architecture was designed to allow the Z8 to map the DSP memory into the shared expanded register file architecture of the Z8.

The Z86C95's DSP has two sets of high-speed on-chip RAM for data storage. The RAM data specified by two different RAM address registers or instruction address field are read out in one machine cycle. Multiplication, addition and register loading can be accomplished in one clock cycle. The instructions are one cycle pipelined, which are transparent to the users.

# **Architectural Overview**

The Z86C95's DSP employs a 16-bit fixed point, two's complement number system (Figure 50). The binary point is assumed to be placed right next to the sign bit. DSP algorithms are accomplished by single-cycle multiply/ accumulate instructions, two on-chip RAM banks, dedicated arithmetic logic unit, user-definable I/O for signal processing and other functions. (See DSP Commands Section below.)

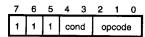

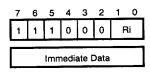

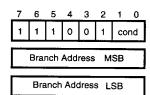

# **Cycles Per Instruction**

Most instructions are one machine cycle instructions which are executed in 1 cycle time. Load register pointer immediate and Branch instructions need two machine cycles to execute. Besides these execution machine cycles, one more cycle is required if the PC (program counter) is selected as the destination of a data transfer instruction. This happens when register indirect branch is executed. An a1 \*b1 +ACC→ACC calculation is done in one machine clock cycle modifying the RAM pointer contents. Both a1 and b1 can be RAM contents located in two independent addresses. Since each instruction is fetched into the instruction register one cycle earlier and the pre-fetched instruction is decoded at the next machine cycle, one