## DS0026 5 MHz Two Phase MOS Clock Driver

### General Description

DS0026 is a low cost monolithic high speed two phase MOS clock driver and interface circuit. Unique circuit design provides both very high speed operation and the ability to drive large capacitive loads. The device accepts standard TTL outputs and converts them to MOS logic levels. The device may be driven from standard 54/74 series and 54S/74S series gates and flip-flops or from drivers such as the DS8830 or DM7440. The DS0026 is intended for applications in which the output pulse width is logically controlled; i.e., the output pulse width is equal to the input pulse width. The DS0026 is designed to fulfill a wide variety of MOS interface requirements. As a MOS clock driver for long silicon-gate shift registers, a single device can drive over 10k bits at 5 MHz. Six devices provide input address and pre-charge drive for a 8k by 16-bit 1103 RAM memory system. Information on the correct usage of the DS0026 in these as well as other systems is included in the application note AN-76.

### Features

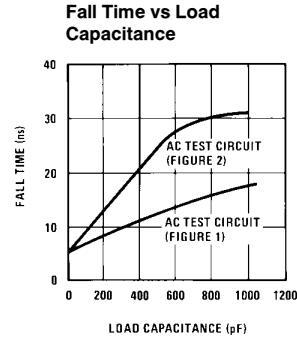

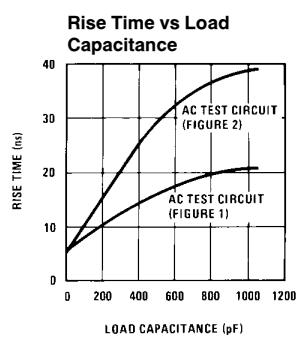

- Fast rise and fall times—20 ns 1000 pF load

- High output swing—20V

- High output current drive— $\pm 1.5$  amps

- TTL compatible inputs

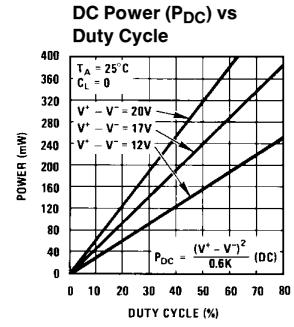

- High rep rate—5 to 10 MHz depending on power dissipation

- Low power consumption in MOS “0” state—2 mW

- Drives to 0.4V of GND for RAM address drive

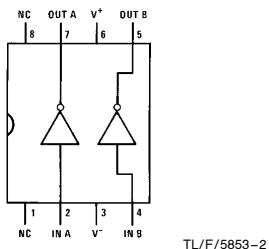

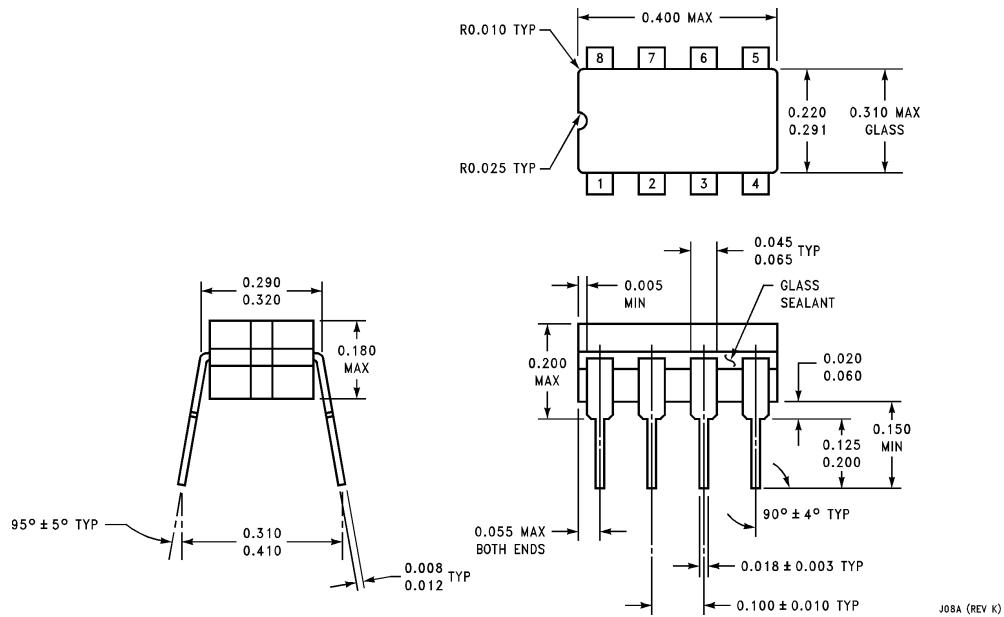

### Connection Diagrams (Top Views)

Dual-In-Line Package

TL/F/5853-2

Order Number DS0026CJ-8,

DS0026CL or DS0026CN

See NS Package Number

J08A or N08E

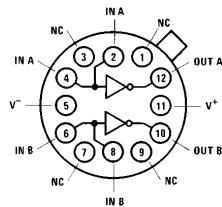

TO-8 Package

TL/F/5853-3

Order Number

DS0026G or DS0026CG

See NS Package

Number G12B

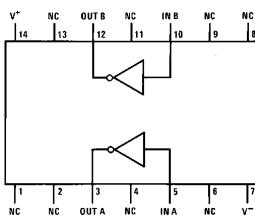

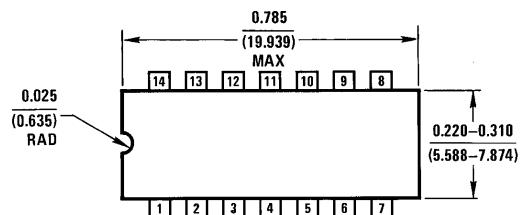

Dual-In-Line Package

TL/F/5853-4

Order Number

DS0026J or DS0026CJ

See NS Package

Number J14A

## Absolute Maximum Ratings (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

|                                                      |         |

|------------------------------------------------------|---------|

| V <sup>+</sup> – V <sup>-</sup> Differential Voltage | 22V     |

| Input Current                                        | 100 mA  |

| Input Voltage (V <sub>IN</sub> – V <sup>-</sup> )    | 5.5V    |

| Peak Output Current                                  | 1.5A    |

| Maximum Power Dissipation* at 25°C                   |         |

| Cavity Package (8-Pin)                               | 1150 mW |

| Cavity Package (14-Pin)                              | 1380 mW |

| Molded Package                                       | 1040 mW |

|                                       |                 |

|---------------------------------------|-----------------|

| EIAJ SO Package                       | 800 mW          |

| Operating Temperature Range           |                 |

| DS0026                                | –55°C to +125°C |

| DS0026C                               | 0°C to +70°C    |

| Storage Temperature Range             | –65°C to +150°C |

| Lead Temperature (Soldering, 10 sec.) | 300°C           |

\* Derate 8-pin cavity package 7.7 mW/°C above 25°C; derate 14-pin cavity package 9.3 mW/°C above 25°C; derate molded package 8.4 mW/°C above 25°C; derate metal can (TO-5) package 4.4 mW/°C above 25°C; derate EIAJ SO package 5.5 mW/°C above 25°C.

## Electrical Characteristics (Notes 2 and 3)

| Symbol               | Parameter                         | Conditions                                                                                                  | Min                  | Typ                  | Max                  | Units |

|----------------------|-----------------------------------|-------------------------------------------------------------------------------------------------------------|----------------------|----------------------|----------------------|-------|

| V <sub>IH</sub>      | Logic "1" Input Voltage           | V <sup>-</sup> = 0V                                                                                         | 2                    | 1.5                  |                      | V     |

| I <sub>IH</sub>      | Logic "1" Input Current           | V <sub>IN</sub> – V <sup>-</sup> = 2.4V                                                                     |                      | 10                   | 15                   | mA    |

| V <sub>IL</sub>      | Logic "0" Input Voltage           | V <sup>-</sup> = 0V                                                                                         |                      | 0.6                  | 0.4                  | V     |

| I <sub>IL</sub>      | Logic "0" Input Current           | V <sub>IN</sub> – V <sup>-</sup> = 0V                                                                       |                      | –3                   | –10                  | μA    |

| V <sub>OL</sub>      | Logic "1" Output Voltage          | V <sub>IN</sub> – V <sup>-</sup> = 2.4V, I <sub>OL</sub> = 1 mA                                             |                      | V <sup>-</sup> + 0.7 | V <sup>-</sup> + 1.0 | V     |

| V <sub>OH</sub>      | Logic "0" Output Voltage          | V <sub>IN</sub> – V <sup>-</sup> = 0.4V, V <sub>SS</sub> ≥ V <sup>+</sup> + 1.0V<br>I <sub>OH</sub> = –1 mA | V <sup>+</sup> – 1.0 | V <sup>+</sup> – 0.8 |                      | V     |

| I <sub>CC(ON)</sub>  | "ON" Supply Current (one side on) | V <sup>+</sup> – V <sup>-</sup> = 20V, V <sub>IN</sub> – V <sup>-</sup> = 2.4V                              |                      | 30                   | 40                   | mA    |

| I <sub>CC(OFF)</sub> | "OFF" Supply Current              | V <sup>+</sup> – V <sup>-</sup> = 20V,<br>V <sub>IN</sub> – V <sup>-</sup> = 0V                             | 70°C<br>125°C        | 10<br>10             | 100<br>500           | μA    |

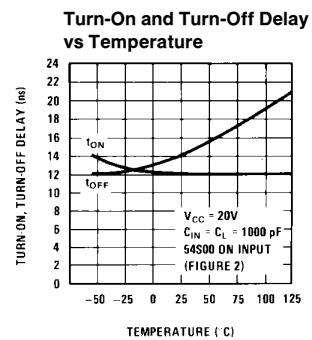

## Switching Characteristics (T<sub>A</sub> = 25°C) (Notes 5 and 6)

| Symbol           | Parameter      | Conditions              | Min                      | Typ | Max | Units |

|------------------|----------------|-------------------------|--------------------------|-----|-----|-------|

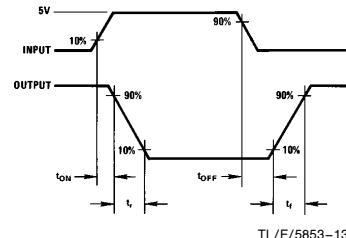

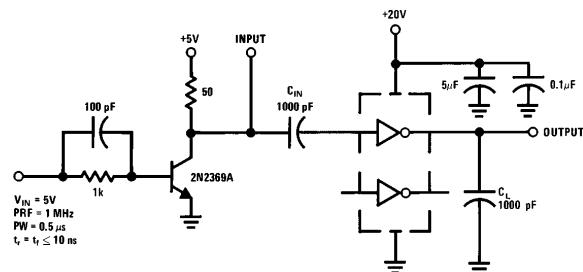

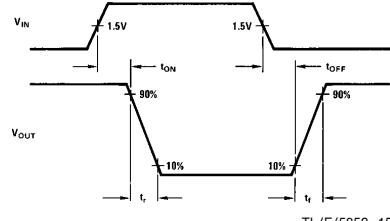

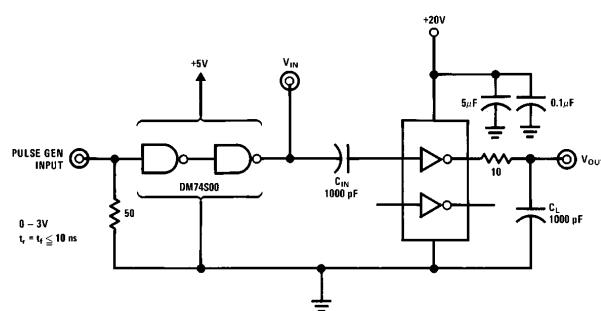

| t <sub>ON</sub>  | Turn-On Delay  | (Figure 1)              | 5                        | 7.5 | 12  | ns    |

|                  |                | (Figure 2)              |                          | 11  |     | ns    |

| t <sub>OFF</sub> | Turn-Off Delay | (Figure 1)              |                          | 12  | 15  | ns    |

|                  |                | (Figure 2)              |                          | 13  |     | ns    |

| t <sub>r</sub>   | Rise Time      | (Figure 1),<br>(Note 5) | C <sub>L</sub> = 500 pF  | 15  | 18  | ns    |

|                  |                |                         | C <sub>L</sub> = 1000 pF | 20  | 35  | ns    |

|                  |                | (Figure 2),<br>(Note 5) | C <sub>L</sub> = 500 pF  | 30  | 40  | ns    |

|                  |                |                         | C <sub>L</sub> = 1000 pF | 36  | 50  | ns    |

| t <sub>f</sub>   | Fall Time      | (Figure 1),<br>(Note 5) | C <sub>L</sub> = 500 pF  | 12  | 16  | ns    |

|                  |                |                         | C <sub>L</sub> = 1000 pF | 17  | 25  | ns    |

|                  |                | (Figure 2),<br>(Note 5) | C <sub>L</sub> = 500 pF  | 28  | 35  | ns    |

|                  |                |                         | C <sub>L</sub> = 1000 pF | 31  | 40  | ns    |

**Note 1:** "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. Except for "Operating Temperature Range" they are not meant to imply that the devices should be operated at these limits. The table of "Electrical Characteristics" provides conditions for actual device operation.

**Note 2:** These specifications apply for V<sup>+</sup> – V<sup>-</sup> = 10V to 20V, C<sub>L</sub> = 1000 pF, over the temperature range of –55°C to +125°C for the DS0026, and 0°C to +70°C for the DS0026C.

**Note 3:** All currents into device pins shown as positive, out of device pins as negative, all voltages referenced to ground unless otherwise noted. All values shown as max or min on absolute value basis.

**Note 4:** All typical values for T<sub>A</sub> = 25°C.

**Note 5:** Rise and fall time are given for MOS logic levels; i.e., rise time is transition from logic "0" to logic "1" which is voltage fall.

**Note 6:** The high current transient (as high as 1.5A) through the resistance of the internal interconnecting V<sup>-</sup> lead during the output transition from the high state to the low state can appear as negative feedback to the input. If the external interconnecting lead from the driving circuit to V<sup>-</sup> is electrically long, or has significant dc resistance, it can subtract from the switching response.

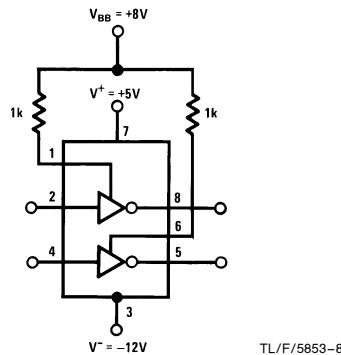

## Typical $V_{BB}$ Connection

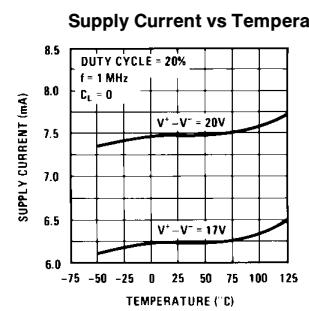

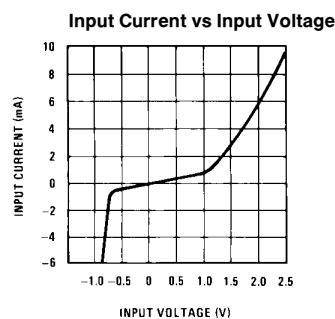

## Typical Performance Characteristics

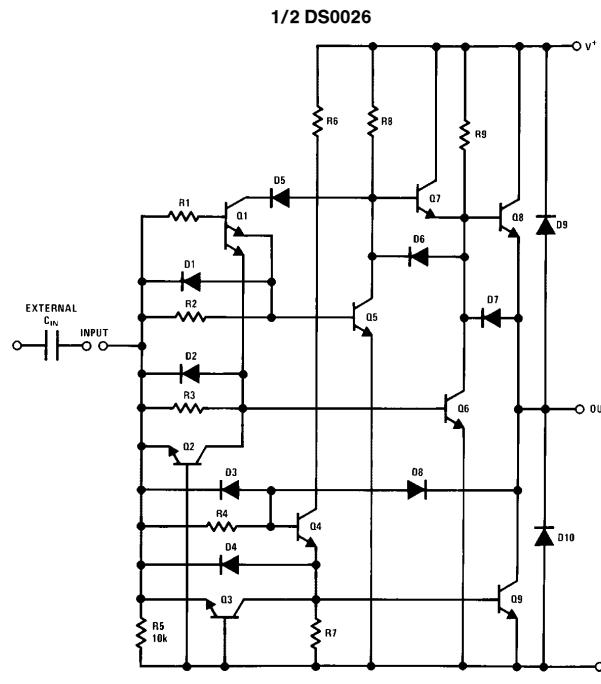

## Schematic Diagram

TL/F/5853-10

## AC Test Circuits and Switching Time Waveforms

FIGURE 1

FIGURE 2

## Typical Applications

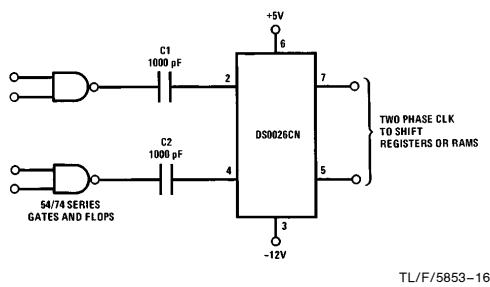

### AC Coupled MOS Clock Driver

### DC Coupled RAM Memory Address or Precharge Driver (Positive Supply Only)

## Application Hints

### DRIVING THE MM5262 WITH THE DS0026 CLOCK DRIVER

The clock signals for the MM5262 have three requirements which have the potential of generating problems for the user. These requirements, high speed, large voltage swing and large capacitive loads, combine to provide ample opportunity for inductive ringing on clock lines, coupling clock signals to other clocks and/or inputs and outputs and generating noise on the power supplies. All of these problems have the potential of causing the memory system to malfunction. Recognizing the source and potential of these problems early in the design of a memory system is the most critical step. The object here is to point out the source of these problems and give a quantitative feel for their magnitude.

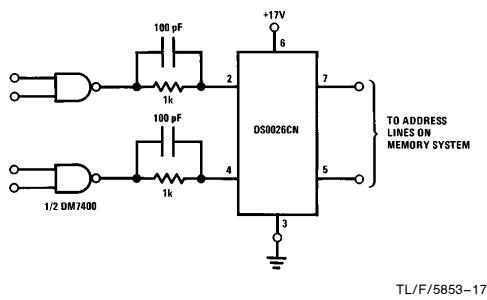

Line ringing comes from the fact that at a high enough frequency any line must be considered as a transmission line with distributed inductance and capacitance. To see how much ringing can be tolerated we must examine the clock voltage specification. Figure 3 shows the clock specification, in diagram form, with idealized ringing sketched in. The

ringing of the clock about the  $V_{SS}$  level is particularly critical. If the  $V_{SS} - 1 V_{OH}$  is not maintained, at all times, the information stored in the memory could be altered. Referring to Figure 1, if the threshold voltage of a transistor were  $-1.3V$ , the clock going to  $V_{SS} - 1$  would mean that all the devices, whose gates are tied to that clock, would be only 300 mV from turning on. The internal circuitry needs this noise margin and from the functional description of the RAM it is easy to see that turning a clock on at the wrong time can have disastrous results.

FIGURE 3. Clock Waveform

Controlling the clock ringing is particularly difficult because of the relative magnitude of the allowable ringing, compared to magnitude of the transition. In this case it is 1V out of 20V or only 5%. Ringing can be controlled by damping the clock driver and minimizing the line inductance.

Damping the clock driver by placing a resistance in series with its output is effective, but there is a limit since it also slows down the rise and fall time of the clock signal. Because the typical clock driver can be much faster than the worst case driver, the damping resistor serves the useful function of limiting the minimum rise and fall time. This is very important because the faster the rise and fall times, the worse the ringing problem becomes. The size of the damping resistor varies because it is dependent on the details of the actual application. It must be determined empirically. In practice a resistance of  $10\Omega$  to  $20\Omega$  is usually optimum.

Limiting the inductance of the clock lines can be accomplished by minimizing their length and by laying out the lines such that the return current is closely coupled to the clock lines. When minimizing the length of clock lines it is important to minimize the distance from the clock driver output to the furthest point being driven. Because of this, memory boards are usually designed with clock drivers in the center of the memory array, rather than on one side, reducing the maximum distance by a factor of 2.

Using multilayer printed circuit boards with clock lines sandwiched between the  $V_{DD}$  and  $V_{SS}$  power planes minimizes the inductance of the clock lines. It also serves the function of preventing the clocks from coupling noise into input and output lines. Unfortunately multilayer printed circuit boards are more expensive than two sided boards. The user must make the decision as to the necessity of multilayer boards. Suffice it to say here, that reliable memory boards can be designed using two sided printed circuit boards.

## Application Hints (Continued)

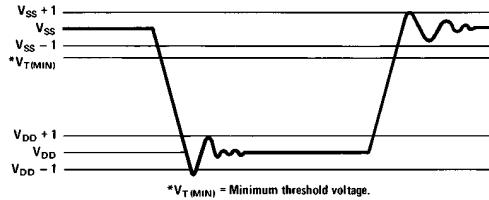

FIGURE 4. Clock Waveforms (Voltage and Current)

Because of the amount of current that the clock driver must supply to its capacitive load, the distribution of power to the clock driver must be considered. Figure 4 gives the idealized voltage and current waveforms for a clock driver driving a 1000 pF capacitor with 20 ns rise and fall time.

As can be seen the current is significant. This current flows in the  $V_{DD}$  and  $V_{SS}$  power lines. Any significant inductance in the lines will produce large voltage transients on the power supplies. A bypass capacitor, as close as possible to the clock driver, is helpful in minimizing this problem. This bypass is most effective when connected between the  $V_{SS}$  and  $V_{DD}$  supplies. The size of the bypass capacitor depends on the amount of capacitance being driven. Using a low inductance capacitor, such as a ceramic or silver mica, is most effective. Another helpful technique is to run the  $V_{DD}$  and  $V_{SS}$  lines, to the clock driver, adjacent to each other. This tends to reduce the lines inductance and therefore the magnitude of the voltage transients.

While discussing the clock driver, it should be pointed out that the DS0026 is a relatively low input impedance device. It is possible to couple current noise into the input without seeing a significant voltage. Since the noise is difficult to detect with an oscilloscope it is often overlooked.

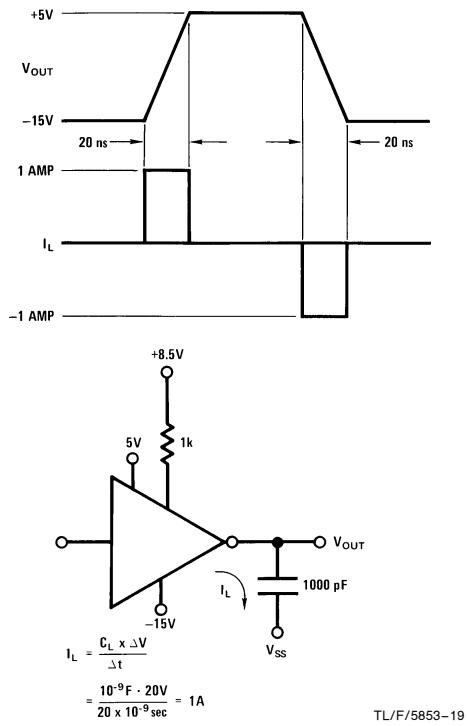

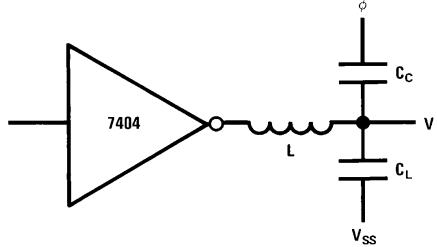

Lastly, the clock lines must be considered as noise generators. Figure 5 shows a clock coupled through a parasitic coupling capacitor,  $C_C$ , to eight data input lines being driven by a 7404. A parasitic lumped line inductance,  $L$ , is also shown. Let us assume, for the sake of argument, that  $C_C$  is 1 pF and that the rise time of the clock is high enough to completely isolate the clock transient from the 7404 because of the inductance,  $L$ .

FIGURE 5. Clock Coupling

With a clock transition of 20V the magnitude of the voltage generated across  $C_L$  is:

$$V = 20V \times \frac{C_C}{C_L + C_C} = 20V \times \left( \frac{1}{56 + 1} \right) = 0.35V$$

This has been a hypothetical example to emphasize that with 20V low rise/fall time transitions, parasitic elements can not be neglected. In this example, 1 pF of parasitic capacitance could cause system malfunction, because a 7404 without a pull up resistor has typically only 0.3V of noise margin in the "1" state at 25°C. Of course it is stretching things to assume that the inductance,  $L$ , completely isolates the clock transient from the 7404. However, it does point out the need to minimize inductance in input/output as well as clock lines.

The output is current, so it is more meaningful to examine the current that is coupled through a 1 pF parasitic capacitance. The current would be:

$$I = C_C \times \frac{\Delta V}{\Delta t} = \frac{1 \times 10^{-12} \times 20}{20 \times 10^{-9}} = 1 \text{ mA}$$

This exceeds the total output current swing so it is obviously significant.

Clock coupling to inputs and outputs can be minimized by using multilayer printed circuit boards, as mentioned previously, physically isolating clock lines and/or running clock lines at right angles to input/output lines. All of these techniques tend to minimize parasitic coupling capacitance from the clocks to the signals in question.

In considering clock coupling it is also important to have a detailed knowledge of the functional characteristics of the device being used. As an example, for the MM5262, coupling noise from the  $\phi_2$  clock to the address lines is of no particular consequence. On the other hand the address inputs will be sensitive to noise coupled from  $\phi_1$  clock.

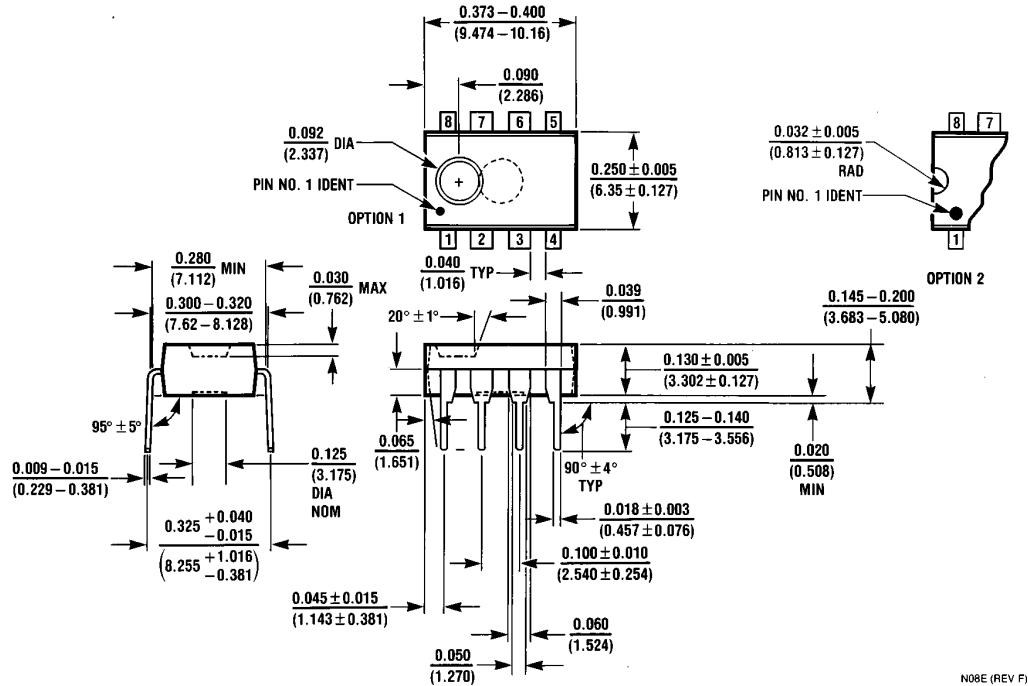

## Packaging Information

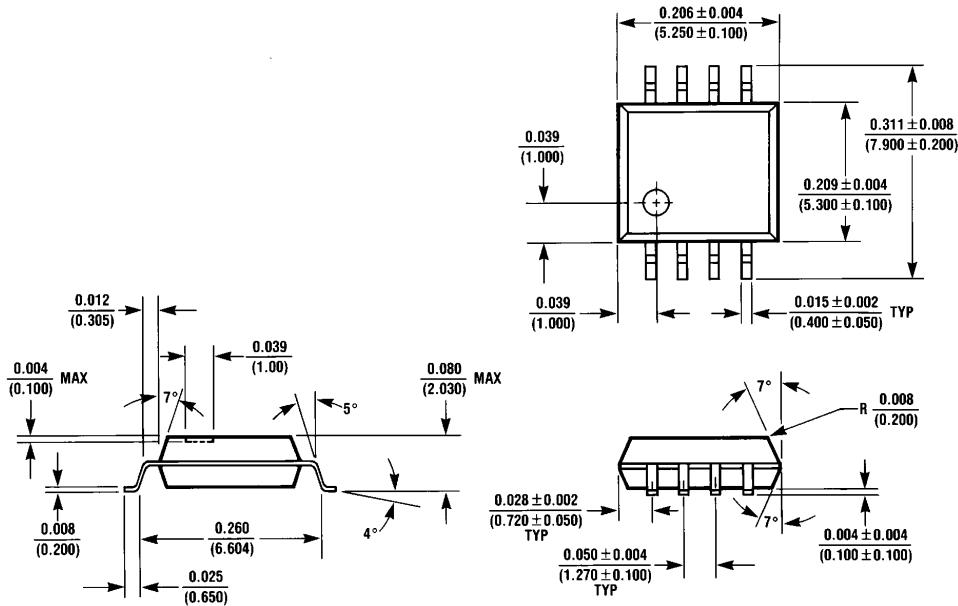

TL/F/5853-21

8-Lead Surface Mount Package

Order Number DS0026CL

**Physical Dimensions** inches (millimeters)

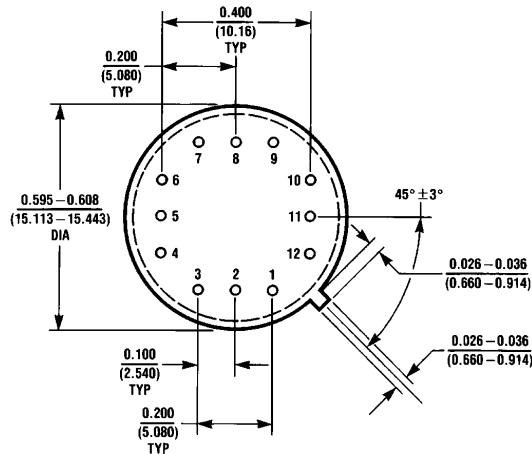

G12B (REV C)

Metal Can Package (G)

Order Number DS0026G or DS0026CG

NS Package Number G12B

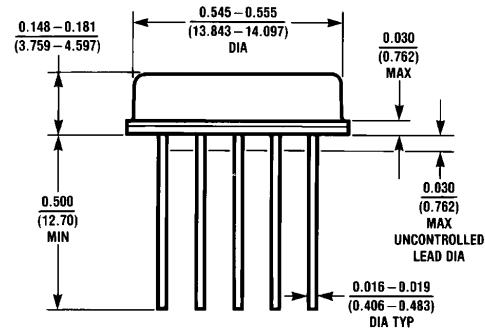

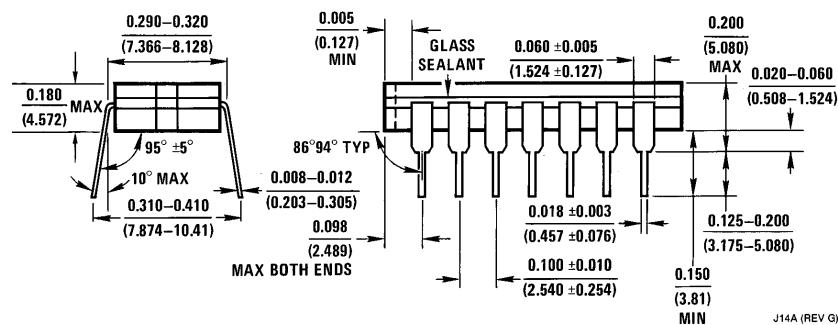

**Physical Dimensions** inches (millimeters) (Continued)

**Ceramic Dual-In-Line Package (J)**

Order Number DS0026CJ or DS0026J

NS Package Number J08A

**Ceramic Dual-In-Line Package (J)**

Order Number DS0026J or DS0026CJ

NS Package Number J14A

## **Physical Dimensions** inches (millimeters) (Continued)

**Molded Dual-In-Line Package (N)**

**Order Number DS0026CN**

**NS Package Number N08E**

## **LIFE SUPPORT POLICY**

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

|                                                                                                                                         |                                                                                                                                           |                                                                                                                                                                                                |                                                                                          |

|-----------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|

| <b>National Semiconductor Corporation</b><br>1111 West Bardin Road<br>Arlington, TX 76017<br>Tel: (800) 272-9959<br>Fax: (800) 737-7018 | <b>National Semiconductor Europe</b><br>Fax: (+49) 0-180-530 85 86<br>Email: <a href="mailto:cnjwe@tevm2.ssc.com">cnjwe@tevm2.ssc.com</a> | <b>National Semiconductor Hong Kong Ltd.</b><br>13th Floor, Straight Block,<br>Ocean Centre, 5 Canton Rd.<br>Tsimshatsui, Kowloon<br>Hong Kong<br>Tel: (852) 2737-1600<br>Fax: (852) 2736-9960 | <b>National Semiconductor Japan Ltd.</b><br>Tel: 81-043-299-2309<br>Fax: 81-043-299-2408 |

| Deutsch Tel: (+49) 0-180-530 85 85                                                                                                      | English Tel: (+49) 0-180-532 78 32                                                                                                        |                                                                                                                                                                                                |                                                                                          |

| Français Tel: (+49) 0-180-532 93 58                                                                                                     | Italiano Tel: (+49) 0-180-534 16 80                                                                                                       |                                                                                                                                                                                                |                                                                                          |