# DS3832C-311 with Clock

#### www.maxim-ic.com

#### **FEATURES**

- 3.0V to 3.6V operation

- Surface-mount nonvolatile (NV) RAM ball-grid array (BGA) module construction

- 1024k x 32 NV SRAM memory space and separate 64 x 8 real-time clock (RTC) memory space

- RTC maintains hundredths of seconds, seconds, minutes, hours, day, date, month, and year with leap-year compensation valid up to 2100

- Removable backup power source provides more than eight years of timekeeping and data retention

- Read and write access times as fast as 100ns for NV SRAM memory and 200ns for RTC

- Automatic data protection during power loss

- Unlimited write-cycle endurance

- Low-power CMOS operation

- Battery monitor checks remaining capacity daily

- Industrial temperature range of -40°C to +85°C

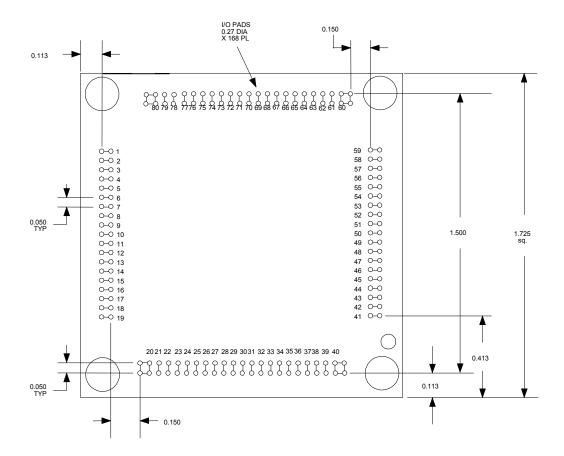

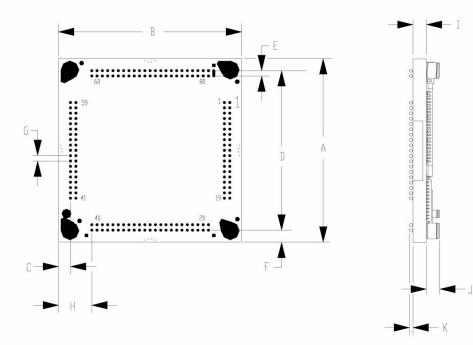

#### **PACKAGE OUTLINE**

Top View

#### DESCRIPTION

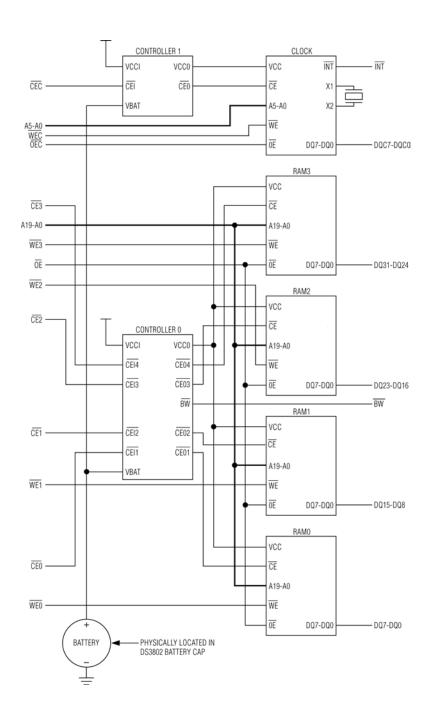

The DS3832C-311 is a 1,048,576 x 32 advanced NV SRAM module with a 168-bump BGA pinout. The highly integrated DS3832C-311 contains a 64-byte RTC, four 8Mb SRAMs, and control circuitry that constantly monitors V<sub>CC</sub> for an out-of-tolerance condition. When such a condition occurs, the DS3832C-311 makes use of an attached DS3802 battery cap to maintain clock information and preserve stored data while protecting that data by disallowing all memory accesses. Additionally, the DS3832C-311 has dedicated circuitry for monitoring the status of V<sub>CC</sub> and the status of an attached DS3802 battery cap.

> 1 of 18 081602

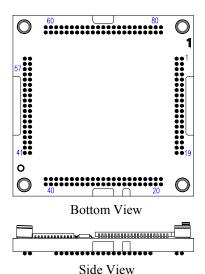

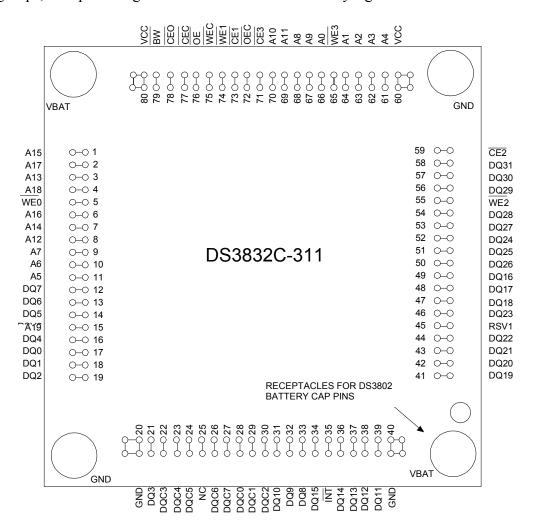

### PIN ASSIGNMENT (With Overlaid Package Outline) Figure 1

Because the DS3832C-311 has a total of 168 balls and only 76 active signals, balls are wired together into numbered groups, thus providing redundant connections for every signal.

#### PIN DESCRIPTION

| 5 = 5 - 1                                          | 11011                         |                          |                                 |

|----------------------------------------------------|-------------------------------|--------------------------|---------------------------------|

| A19 to A0                                          | - Address Inputs              | $\overline{\text{OEC}}$  | - Clock Output-Enable Input     |

| DQ31 to DQ0                                        | - NV SRAM Data In/Data Out    | $\overline{\mathrm{BW}}$ | - Battery Warning Output        |

| DQC7 to DQC0                                       | O - Clock Data In/Data Out    | $\overline{\text{INT}}$  | - Interrupt Output              |

| $\overline{\text{CE3}}$ to $\overline{\text{CE0}}$ | - NV SRAM Chip-Enable Inputs  | $V_{CC}$                 | - Power (3.3V)                  |

| $\overline{\text{CEC}}$                            | - Clock Chip-Enable Input     | GND                      | - Ground                        |

| $\overline{\text{WE3}}$ to $\overline{\text{WE0}}$ | - NV SRAM Write-Enable Inputs | RSV1                     | - No Connect                    |

| WEC                                                | - Clock Write-Enable Input    | VBAT                     | - DS3802 Battery Cap Connection |

| $\overline{\text{OE}}$                             | - NV SRAM Output-Enable Input |                          |                                 |

## **BLOCK DIAGRAM** Figure 2

#### **NV SRAM READ MODE**

The DS3832C-311 executes an NV SRAM read cycle whenever  $\overline{\text{WE0}}$  to  $\overline{\text{WE3}}$  (write enables) are inactive (high), any or all of  $\overline{\text{CE0}}$  to  $\overline{\text{CE3}}$  (chip enables) are active (low) and  $\overline{\text{OE}}$  (output enable) is active (low). The unique address specified by the 20 address inputs (A<sub>0</sub> to A<sub>19</sub>) defines which of the 1,048,576 words of data is accessed. The four chip-enable signals ( $\overline{\text{CE0}}$  to  $\overline{\text{CE3}}$ ) determine which bytes in the addressed word are output on data lines DQ31 to DQ0. Valid data will be output within t<sub>ACC</sub> (NV SRAM access time) after the last address input signal is stable, providing that  $\overline{\text{CE}}$  and  $\overline{\text{OE}}$  (output enable) access times are also satisfied. If  $\overline{\text{CE}}$  and  $\overline{\text{OE}}$  access times are not satisfied, then data access must be measured from the later occurring signal ( $\overline{\text{CE}}$  or  $\overline{\text{OE}}$ ) and the limiting parameter is either t<sub>CO</sub> for  $\overline{\text{CE}}$  or t<sub>OE</sub> for  $\overline{\text{OE}}$  rather than t<sub>ACC</sub>.

#### **NV SRAM WRITE MODE**

The DS3832C-311 executes an NV SRAM write cycle whenever any or all of the  $\overline{WE}$  signals ( $\overline{WE0}$  to  $\overline{WE3}$ ) are active (low) and any of the corresponding  $\overline{CE}\setminus \text{signals}$  ( $\overline{CE0}$  to  $\overline{CE3}$ ) are active (low) after all address inputs are stable. The later occurring falling edge of  $\overline{CE}$  or  $\overline{WE}$  determines the start of the write cycle. The write cycle is terminated by the earlier rising edge of  $\overline{CE}$  or  $\overline{WE}$ . All address inputs must be kept valid throughout the write cycle.  $\overline{WE0}$  to  $\overline{WE3}$  must return to the high state for a minimum recovery time ( $t_{WR}$ ) before another cycle can be initiated. The  $\overline{OE}$  control signal should be kept inactive (high) during write cycles to avoid bus contention. However, if output drivers are enabled ( $\overline{CE}$  and  $\overline{OE}$  active) then  $\overline{WE}$  disables the outputs in  $t_{ODW}$  from its falling edge.

#### **CLOCK READ MODE**

The DS3832C-311 executes a clock read cycle whenever  $\overline{\text{WEC}}$  (clock write enable) is inactive (high),  $\overline{\text{CEC}}$  (clock chip enable) is active (low), and  $\overline{\text{OEC}}$  (output enable) is active (low). The unique clock address specified by address inputs  $A_0$  to  $A_5$  defines which of the 64 bytes of data is accessed. Valid data is output within  $t_{ACC}$  (clock access time) after the last address input signal is stable, providing that  $\overline{\text{CEC}}$  and  $\overline{\text{OEC}}$  (output enable) access times are also satisfied. If  $\overline{\text{CEC}}$  and  $\overline{\text{OEC}}$  access times are not satisfied, then data access must be measured from the later occurring signal ( $\overline{\text{CEC}}$  or  $\overline{\text{OEC}}$ ) and the limiting parameter is either  $t_{CO}$  for  $\overline{\text{CEC}}$  or  $t_{OE}$  for  $\overline{\text{OEC}}$  rather than  $t_{ACC}$ . Only addresses 0 to 3Fh are implemented in the clock address space. Accesses to clock addresses higher than 3Fh are undefined.

#### CLOCK WRITE MODE

The DS3832C-311 executes a clock write cycle whenever  $\overline{\text{WEC}}$  is active (low) and  $\overline{\text{CEC}}$  is active (low) after all address inputs are stable. The later occurring falling edge of  $\overline{\text{CEC}}$  or  $\overline{\text{WEC}}$  determines the start of the write cycle. The write cycle is terminated by the earlier rising edge of  $\overline{\text{CEC}}$  or  $\overline{\text{WEC}}$ . All address inputs must be kept valid throughout the write cycle.  $\overline{\text{WEC}}$  must return to the high state for a minimum recovery time ( $t_{WR}$ ) before another cycle can be initiated. The  $\overline{\text{OEC}}$  control signal should be kept inactive (high) during write cycles to avoid bus contention. However, if output drivers are enabled ( $\overline{\text{CEC}}$  and  $\overline{\text{OEC}}$  active) then  $\overline{\text{WEC}}$  disables the outputs in  $t_{ODW}$  from its falling edge.

#### **DATA RETENTION MODE**

The DS3832C-311 provides full functional capability for  $V_{CC}$  greater than 3.0V and write protects by 2.8V. Data is maintained in the absence of  $V_{CC}$  without any additional support circuitry. The DS3832C-311 constantly monitors  $V_{CC}$ . Should the supply voltage decay to  $V_{TP}$ , the device automatically write protects itself, all inputs become "don't care," and all outputs become high impedance. As  $V_{CC}$  falls below approximately 2.8V, a power-switching circuit electrically connects an attached DS3802 battery cap to the SRAM to retain data. During power-up, when  $V_{CC}$  rises above approximately 2.8V, the power-switching circuit connects external  $V_{CC}$  to the SRAM and disconnects the DS3802 normal RAM operation can resume after  $V_{CC}$  reaches the minimum power-supply voltage.

#### **BATTERY MONITORING**

The DS3832C-311 automatically monitors the battery in an attached DS3802 battery cap on a 24-hour time interval. Such monitoring begins within  $t_{REC}$  after  $V_{CC}$  rises above  $V_{TP}$  and is suspended when power failure occurs.

After each 24-hour period has elapsed, the battery is connected to an internal  $1M\Omega$  test resistor for one second. During this one second, if battery voltage falls below the battery voltage trip point (2.6V), the battery warning output  $\overline{BW}$  is asserted. Once asserted,  $\overline{BW}$  remains active until the battery cap or DS3802 is replaced. The battery is still retested after each  $V_{CC}$  power-up even if  $\overline{BW}$  is active. If the battery voltage is found to be higher than 2.6V during such testing,  $\overline{BW}$  is de-asserted and regular 24-hour testing resumes.  $\overline{BW}$  has an open-drain output driver.

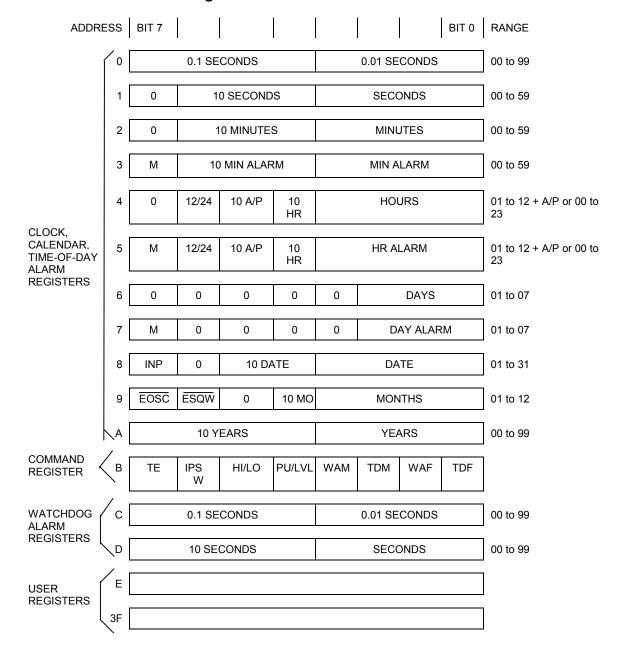

## **CLOCK REGISTERS** Figure 3

TIME-OF-DAY ALARM MASK BITS (Figure 4)

| REGISTER |       |      | ALARM                                     |

|----------|-------|------|-------------------------------------------|

| MINUTES  | HOURS | DAYS | ALAKN                                     |

| 1        | 1     | 1    | ALARM ONCE PER MINUTE                     |

| 0        | 1     | 1    | ALARM WHEN MINUTES MATCH                  |

| 0        | 0     | 1    | ALARM WHEN MINUTES AND HOURS MATCH        |

| 0        | 0     | 0    | ALARM WHEN MINUTES, HOURS, AND DAYS MATCH |

#### NOTE:

Any other bit combinations produce illogical operation.

#### **CLOCK REGISTERS**

The DS3832C-311 clock has 14 8-bit internal registers that contain all timekeeping, alarm, watchdog, and control information. The clock, calendar, alarm, and watchdog registers are memory locations that contain both external (user-accessible) and internal copies of the data. The external copies are independent of internal functions except that they are updated periodically by simultaneous transfer from the incremented internal copies. The command register bits are affected by both internal and external functions. In addition to the 14 registers, the clock also contains 50 bytes of user RAM. Clock registers 0, 1, 2, 4, 6, 8, 9, and A (hex) contain day, date, and time information stored in binary-code decimal (BCD) format. Registers 3, 5, and 7 contain time-of-day alarm information also stored in BCD format. Register B is the command register containing eight 1-bit binary fields. Registers C and D contain watchdog alarm information stored in BCD format. Addresses E through 3F are general-purpose user RAM.

#### DAY, DATE AND TIME REGISTERS

Registers 0, 1, 2, 4, 6, 8, 9, and A (hex) contain day, date, and time information in BCD format. Eleven bits within these eight registers are not used and will always read zero regardless of how they are written. Bits 6 and 7 in the month register (register 9) are binary control bits.

When set to logic 0, EOSC (register 9, bit 7) enables the clock oscillator. This bit is normally turned on by the user during device initialization. The oscillator can be turned on and off as needed by enabling or disabling this bit.

Register 8 bit 7, INP, controls the logic state of the INTP output pin of the clock device. Because this logic feature is not supported in the DS3832C-311, INP should be set to a logic zero.

Register 9 bit 6,  $\overline{\text{ESQW}}$ , enables and disables the output of a 1024Hz square wave. Because this feature is not supported in the DS3832C-311,  $\overline{\text{ESQW}}$  should be set to logic one.

Bit 6 of the hour register (register 4) is defined as the 12- or 24-hour select bit. When set to logic one, the 12-hour format is selected. In the 12-hour format, bit 5 is the AM/PM bit with logic 1 being PM. In the 24-hour mode, bit 5 is the upper-order 10-hour bit (set for hours 20 to 23).

The external day, date, and time registers are updated from their internal counterparts every 0.01 seconds except when the TE bit (bit 7 of register B) is set low or the clock oscillator is not running (EOSC high). Setting TE low freezes the external day, date, and time registers at their present values allowing all the registers to be read or written without any of them being updated from the internal registers. After the

registers have been read or written, setting TE high re-enables external register updates. While TE is set low and the external registers are frozen, the internal registers continue to be incremented.

#### TIME-OF-DAY ALARM REGISTERS

Registers 3, 5, and 7 contain the time-of-day alarm registers. Bits 3, 4, 5, and 6 of register 7 always read zero regardless of how they are written. Bit 7 of registers 3, 5, and 7 are mask bits (see Figure 4). When all of the mask bits are logic 0, a time-of-day alarm only occurs when registers 2, 4, and 6 match the values stored in registers 3, 5, and 7. An alarm is generated every day when bit 7 of register 7 is set to logic 1. Similarly, an alarm is generated every hour when registers 7 and 5 both have bit 7 set to logic 1. When registers 7, 5, and 3 all have bit 7 set to logic 1, an alarm occurs every minute at the point where register 1 (seconds) rolls over from 59 to 00. Whenever an alarm occurs, the time-of-day alarm flag TDF (register B, bit 0) and the internal time-of-day interrupt signal goes to the active state. If the interrupt-switch bit IPSW (register B, bit 6) is set to a logic 0 and the time-of-day alarm mask bit TDM (register B, bit 3) is logic 0, the interrupt-output pin INT also activates.

Time-of-day alarm registers are written and read in the same format as the day, date, and time registers. The time-of-day alarm flag, time-of-day interrupt, and  $\overline{\text{INT}}$  output are always cleared when the time-of-day alarm registers are read or written.

#### WATCHDOG ALARM REGISTERS

Registers C and D contain the timeout period for the watchdog alarm. The two registers contain a count from 0.01 to 99.99 seconds in BCD format. The two watchdog alarm registers can be written or read in any order. After a new value is entered or either of the watchdog alarm registers is read, an internal watchdog timer starts counting down from the entered watchdog alarm register value toward zero. When zero is reached, the watchdog alarm flag (register B, bit 1) and the internal watchdog interrupt signal go to the active state. If the interrupt switch bit IPSW (register B bit 6) is set to logic 1 and the watchdog alarm mask bit WAM (register B, bit 3) is logic 0, the interrupt output  $\overline{\text{INT}}$  also activates. The watchdog timer countdown is interrupted and the timer is re-initialized to the value in the watchdog alarm registers every time either watchdog alarm register is accessed. Controlled, periodic accesses to the watchdog alarm registers can prevent the activation of the watchdog alarm flag, the internal watchdog interrupt signal and the  $\overline{\text{INT}}$  output. The watchdog alarm registers always read the value entered. The actual watchdog timer is internal and is not accessible. Writing 00h to registers C and D disables the watchdog alarm feature.

#### **COMMAND REGISTER**

Register B, the command register, contains control bits and flag bits. The operation of each bit is described below.

**TE—Transfer Enable (Bit 7).** When set to logic 0, this bit disables the transfer of data between internal and external clock registers. The contents of the external registers are frozen and reads and writes of day, date, and time information are not affected by updates. This bit must be set to logic 1 to enable updates.

**IPSW—Interrupt Switch (Bit 6).** This bit should be initialized to logic 1 to connect the internal watchdog interrupt signal to the  $\overline{\text{INT}}$  output pin. Setting this bit to logic 0 connects the internal time-of-day interrupt signal to the  $\overline{\text{INT}}$  output pin.

HI/LO— $\overline{\text{INT}}$  Sink or Source Current (Bit 5). When this bit is set to logic 1 and  $V_{CC}$  is applied, the  $\overline{\text{INT}}$  output pin will source current when activated (see  $I_{OH}$  spec). When this bit is set to logic 0,  $\overline{\text{INT}}$  sinks current (see  $I_{OL}$  spec).

**PU/LVL**—INT **Pulse or Level (Bit 4).** When this bit is set to logic 0, INT is in the level mode, going to the logic level defined by the HI/LO bit and staying there until the interrupt is cleared. When this bit is set to logic 1, INT is in pulse mode, sourcing or sinking current as defined by the HI/LO bit for a minimum of 3ms and then releasing.

**WAM**—Watchdog Alarm Mask (Bit 3). When this bit is set to logic 0, the internal watchdog interrupt signal is enabled. If IPSW is also set to logic 1, any watchdog alarm activates the  $\overline{\text{INT}}$  output. When this bit is set to logic 1, watchdog alarms have no effect on the internal watchdog interrupt signal or on the  $\overline{\text{INT}}$  pin.

**TDM**—**Time-of-Day Alarm Mask (Bit 2).** When this bit is set to logic 0, the internal time-of-day interrupt signal is enabled. If IPSW is set to logic 0, any time-of-day alarm activates the  $\overline{\text{INT}}$  output. When this bit is set to logic 1, time-of-day alarms have no effect on the internal time-of-day interrupt signal or on the  $\overline{\text{INT}}$  pin.

WAF—Watchdog Alarm Flag (Bit 1). This bit is set to logic 1 when a watchdog alarm occurs (regardless of the state of the watchdog alarm mask bit WAM). WAF is read-only. This bit is reset when either of the watchdog alarm registers is accessed. When the PU/LVL bit is in the pulse mode, this flag is only set to logic 1 for the 3ms duration of the INT output pulse.

**TDF—Time-of-Day Alarm Flag (Bit 0).** This bit is set to logic 1 when a time-of-day alarm occurs (regardless of the state of the time-of-day alarm mask bit TDM). TDF is read-only. The time the alarm occurred can be determined by reading the time-of-day alarm registers. This bit is reset to logic 0 when any of the time-of-day alarm registers is accessed. When the PU/LVL bit is in the pulse mode, this flag is only set to logic 1 for the 3ms duration of the  $\overline{\text{INT}}$  output pulse.

#### **ABSOLUTE MAXIMUM RATINGS\***

Voltage on Any Pin Relative to Ground

Operating Temperature Range

-0.3 to +4.6 V

-40°C to +85°C

Storage Temperature Range

-40°C to +85°C

Soldering Temperature See IPC/JEDEC J-STD-020A Specification

### RECOMMENDED DC OPERATING CONDITIONS

$(T_A = -40^{\circ}C \text{ to } +85^{\circ}C)$

| PARAMETER             | SYMBOL      | MIN | TYP | MAX      | UNITS | NOTES |

|-----------------------|-------------|-----|-----|----------|-------|-------|

| Power Supply Voltage  | $V_{CC}$    | 3.0 | 3.3 | 3.6      | V     | 1     |

| Logic 1 Input Voltage | $V_{ m IH}$ | 2.2 |     | $V_{CC}$ | V     | 1     |

| Logic 0 Input Voltage | $ m V_{IL}$ | 0   |     | 0.6      | V     | 1     |

DC ELECTRICAL CHARACTERISTICS ( $T_A = -40$ °C to +85°C;  $V_{CC} = 3.3V \pm 0.3V$ )

| DO LLLO I MOAL O                       |                   |     | ( I A I O V |     | , v <sub>C</sub> 0.0 | v = 0.0 v |

|----------------------------------------|-------------------|-----|-------------|-----|----------------------|-----------|

| PARAMETER                              | SYMBOL            | MIN | TYP         | MAX | UNITS                | NOTES     |

| Input Leakage Current                  | $I_{\mathrm{IL}}$ | -5  |             | 5   | μΑ                   |           |

| I/O Leakage Current                    | $I_{IO}$          | -1  |             | 1   | μΑ                   |           |

| Output Current at 2.4V                 | $I_{OH}$          | -1  |             |     | mA                   |           |

| Output Current at 0.4V                 | $I_{OL}$          | 2   |             |     | mA                   |           |

| Standby Current                        | I <sub>CCS1</sub> |     | 5           | 7   | mA                   |           |

| (All $\overline{CE} = V_{IH}$ )        |                   |     |             |     |                      |           |

| Standby Current                        | $I_{CCS2}$        |     | 2           | 5   | mA                   |           |

| (All $\overline{CE} = V_{CC} - 0.3V$ ) |                   |     |             |     |                      |           |

| Operating Current                      | $I_{CCO1}$        |     |             | 50  | mA                   | 4         |

| (One $\overline{CE} = V_{IL}$ )        |                   |     |             |     |                      |           |

| Operating Current                      | $I_{CCO2}$        |     |             | 200 | mA                   | 4         |

| (All $\overline{CE} = V_{IL}$ )        |                   |     |             |     |                      |           |

| Write Protection                       | $V_{TP}$          | 2.8 | 2.9         | 3.0 | V                    |           |

| Voltage                                |                   |     |             |     |                      |           |

**CAPACITANCE**  $(T_A = +25^{\circ}C)$

| PARAMETER                                                                                               | SYMBOL    | MIN | TYP | MAX | UNITS | NOTES |

|---------------------------------------------------------------------------------------------------------|-----------|-----|-----|-----|-------|-------|

| Input Capacitance:                                                                                      | $C_{IN}$  |     | 25  | 50  | pF    |       |

| A19 to A0, $\overline{\text{OE}}$                                                                       |           |     |     |     |       |       |

| Input Capacitance: <del>CE3</del> -                                                                     | $C_{IN}$  |     | 5   | 10  | pF    |       |

| $\overline{\text{CE0}}$ , $\overline{\text{WE3}}$ – $\overline{\text{WE0}}$ , $\overline{\text{CEC}}$ , |           |     |     |     |       |       |

| $\overline{\text{WEC}}$ , $\overline{\text{OEC}}$                                                       |           |     |     |     |       |       |

| I/O Capacitance:                                                                                        | $C_{I/O}$ |     | 5   | 10  | pF    |       |

| DQ31–DQ0,                                                                                               |           |     |     |     |       |       |

| DQC7–DQC0                                                                                               |           |     |     |     |       |       |

| Output Capacitance: BW,                                                                                 | $C_{OUT}$ |     | 5   | 10  | pF    |       |

| INT                                                                                                     |           |     |     |     |       |       |

<sup>\*</sup> This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operation sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods of time may affect reliability.

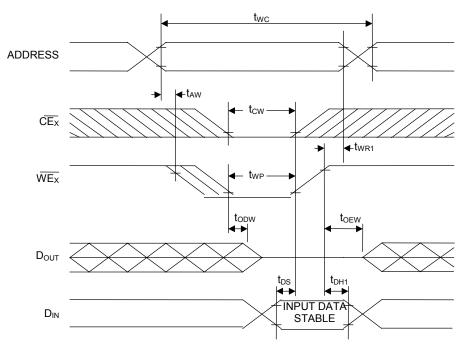

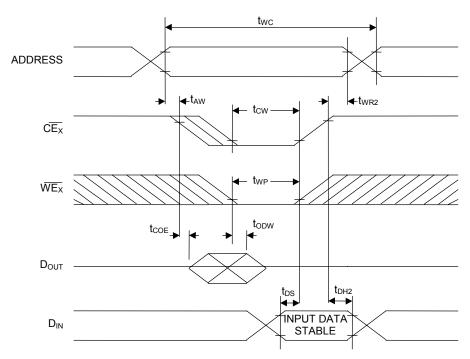

# AC ELECTRICAL CHARACTERISTICS ( $T_A = -40^{\circ}\text{C}$ to $+85^{\circ}\text{C}$ ; $V_{CC} = 3.3\text{V} \pm 0.3\text{V}$ )

|                     |                    | NV S | RAM | CLO | OCK |       |       |

|---------------------|--------------------|------|-----|-----|-----|-------|-------|

| PARAMETER           | SYMBOL             | MIN  | MAX | MIN | MAX | UNITS | NOTES |

| Read Cycle Time     | $t_{ m RC}$        | 100  |     | 200 |     | ns    |       |

| Access Time         | $t_{ACC}$          |      | 100 |     | 200 | ns    |       |

| OE to Output Valid  | $t_{ m OE}$        |      | 50  |     | 70  | ns    |       |

| CE to Output Valid  | $t_{CO}$           |      | 100 |     | 200 | ns    |       |

| OE or CE to Output  | $t_{\rm COE}$      | 5    |     | 5   |     | ns    | 6     |

| Active              |                    |      |     |     |     |       |       |

| Output High-Z from  | $t_{\mathrm{OD}}$  |      | 35  |     | 50  | ns    | 6     |

| Deselection         |                    |      |     |     |     |       |       |

| Output Hold from    | $t_{\mathrm{OH}}$  | 5    |     | 5   |     | ns    |       |

| Address Change      |                    |      |     |     |     |       |       |

| Write Cycle Time    | $t_{ m WC}$        | 100  |     | 200 |     | ns    |       |

| CE Pulse Width      | $t_{\rm CW}$       | 100  |     | 200 |     |       |       |

| Write Pulse Width   | $t_{\mathrm{WP}}$  | 75   |     | 150 |     | ns    |       |

| Address Setup Time  | $t_{AW}$           | 0    |     | 0   |     | ns    |       |

| Write Recovery Time | $t_{\mathrm{WR}1}$ | 5    |     | 15  |     | ns    | 12    |

|                     | $t_{ m WR2}$       | 20   |     | 20  |     | ns    | 13    |

| Output High-Z from  | $t_{\mathrm{ODW}}$ |      | 35  |     | 50  | ns    | 6     |

| WE                  |                    |      |     |     |     |       |       |

| Output Active from  | $t_{OEW}$          | 5    |     | 5   |     | ns    | 6     |

| WE                  |                    |      |     |     |     |       |       |

| Data Setup Time     | $t_{ m DS}$        | 40   |     | 100 |     | ns    | 5     |

| Data Hold Time      | $t_{ m DH1}$       | 0    |     | 0   |     | ns    | 12    |

|                     | $t_{ m DH2}$       | 20   |     | 20  |     | ns    | 13    |

## **TIMING DIAGRAM: READ CYCLE**

See Note 2.

# TIMING DIAGRAM: WRITE CYCLE 1 (WE)

See Notes 3, 5, 7, 8, 9, and 12.

## TIMING DIAGRAM: WRITE CYCLE 2 (CE)

See Notes 3, 5, 7, 8, 9, and 13.

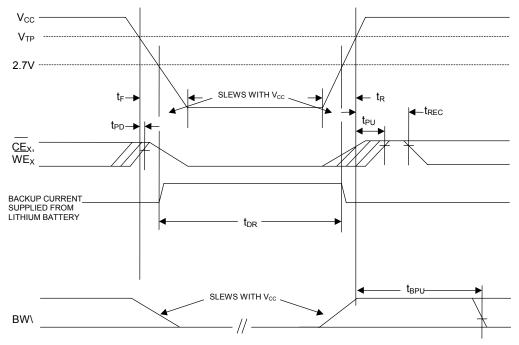

## POWER-DOWN/POWER-UP CONDITION

See Note 11.

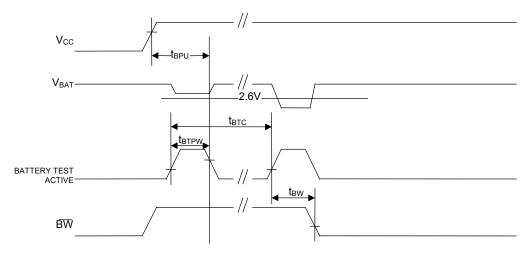

## **TIMING DIAGRAM: BATTERY WARNING DETECTION**

See Note 14.

## POWER-DOWN/POWER-UP TIMING

$(T_A = -40^{\circ}C \text{ to } +85^{\circ}C)$

| PARAMETER                                             | SYMBOL            | MIN | TYP | MAX | UNITS | NOTES |

|-------------------------------------------------------|-------------------|-----|-----|-----|-------|-------|

| V <sub>CC</sub> Fail Detect to $\overline{\text{CE}}$ | $t_{\mathrm{PD}}$ |     |     | 0   | μs    | 11    |

| and WE\ Inactive                                      |                   |     |     |     |       |       |

| $V_{CC}$ Slew from $V_{TP}$ to $0V$                   | $t_{ m F}$        | 300 |     |     | μs    |       |

| V <sub>CC</sub> Slew from 0V to V <sub>TP</sub>       | $t_R$             | 300 |     |     | μs    |       |

| V <sub>CC</sub> Valid to $\overline{\text{CE}}$ and   | $t_{\mathrm{PU}}$ |     |     | 2   | ms    |       |

| WE Inactive                                           |                   |     |     |     |       |       |

| V <sub>CC</sub> Valid to End of                       | $t_{ m REC}$      |     |     | 125 | ms    |       |

| Write Protection                                      |                   |     |     |     |       |       |

| V <sub>CC</sub> Valid to BW Valid                     | $t_{ m BPU}$      |     |     | 1   | S     | 14    |

| INT Pulse Width                                       | $t_{ m IPW}$      | 3   |     |     | ms    | 15    |

| (PU/LVL Bit High)                                     |                   |     |     |     |       |       |

## **BATTERY WARNING TIMING**

|  | (T <sub>△</sub> | $= -40^{\circ}$ | C to | +85°C: | $V_{CC} =$ | = 3.3V ± | 0.3V |

|--|-----------------|-----------------|------|--------|------------|----------|------|

|--|-----------------|-----------------|------|--------|------------|----------|------|

| PARAMETER                | SYMBOL             | MIN | TYP | MAX | UNITS | NOTES |

|--------------------------|--------------------|-----|-----|-----|-------|-------|

| Battery Test Cycle       | $t_{\mathrm{BTC}}$ |     | 24  |     | hr    |       |

| Battery Test Pulse Width | $t_{ m BTPW}$      |     |     | 1   | S     |       |

| Battery Test to BW       | $t_{ m BW}$        |     |     | 1   | S     |       |

| Active                   |                    |     |     |     |       |       |

$(T_A = +25^{\circ}C)$

|                         |                   |     |     |     | \ /\  | /     |

|-------------------------|-------------------|-----|-----|-----|-------|-------|

| PARAMETER               | SYMBOL            | MIN | TYP | MAX | UNITS | NOTES |

| Expected Data Retention | $t_{\mathrm{DR}}$ | 8   |     |     | years | 10    |

| Time                    |                   |     |     |     |       |       |

### **WARNING:**

Under no circumstances are negative undershoots, of any amplitude, allowed when this device is in battery backup mode.

#### NOTES:

- 1) All voltages referenced to ground.

- 2) WE is high throughout read cycle.

- 3)  $\overline{OE} = V_{IH}$  or  $V_{IL}$ . If  $\overline{OE} = V_{IH}$  during write cycle, the output buffers remain in a high-impedance state.

- 4) All outputs open-circuited.

- 5)  $t_{DS}$  is measured from the earlier of  $\overline{CE}$  or  $\overline{WE}$  going high.

- 6) These parameters are sampled with a 5pF load and are not 100% tested.

- 7) If the  $\overline{\text{CE}}$  low transition occurs simultaneously with, or later than, the  $\overline{\text{WE}}$  low transition, the output buffers remain in a high-impedance state during this period.

- 8) If the  $\overline{\text{CE}}$  high transition occurs prior to, or simultaneously with, the  $\overline{\text{WE}}$  high transition, the output buffers remain in a high-impedance state during this period.

- 9) If  $\overline{\text{WE}}$  is low or the  $\overline{\text{WE}}$  low transition occurs prior to, or simultaneously with, the  $\overline{\text{CE}}$  low transition, the output buffers remain in a high-impedance state during this period.

- 10) Expected data retention time can be extended indefinitely if the DS3802 battery cap is periodically replaced.

- 11) In a power-down condition, the voltage on any pin may not exceed the voltage on  $V_{CC}$ .

- 12)  $t_{WR1}$ ,  $t_{DH1}$  are measured from  $\overline{WE}$  going high.

- 13)  $t_{WR2}$ ,  $t_{DH2}$  are measured from  $\overline{CE}$  going high.

- 14)  $\overline{\text{BW}}$  is an open-drain output and cannot source current. An external pullup resistor should be connected to this pin for proper operation. This pin sinks 10mA.

- 15) INT activates within 100ns after the alarm condition arises.

#### DC TEST CONDITIONS

Outputs Open All voltages are referenced to ground

#### **AC TEST CONDITIONS**

Output load: 100pF + 1 TTL gate Input pulse levels: 0V to 2.7V Timing measurement reference levels

Input: 1.5V Output: 1.5V

Input pulse rise and fall times: 5ns

## **DS3832C-311 PACKAGE DIMENSIONS**

| DI | M  | MIN   | MAX   |

|----|----|-------|-------|

| A  | in | 1.720 | 1.730 |

|    | mm | 43.69 | 43.94 |

| В  | in | 1.720 | 1.730 |

|    | mm | 43.69 | 43.94 |

| C  | in | 0.108 | 0.118 |

|    | mm | 2.74  | 3.00  |

| D  | in | 1.497 | 1.503 |

|    | mm | 38.02 | 38.18 |

| E  | in | 0.047 | 0.053 |

|    | mm | 1.19  | 1.35  |

| F  | in | 0.108 | 0.118 |

|    | mm | 2.74  | 3.00  |

| G  | in | 0.047 | 0.053 |

|    | mm | 1.19  | 1.35  |

| H  | in | 0.305 | 0.320 |

|    | mm | 7.74  | 8.13  |

| I  | in | 0.125 | 0.135 |

|    | mm | 3.10  | 3.43  |

| J  | in | -     | .135  |

|    | mm | -     | 3.43  |

| K  | in | 0.025 | 0.032 |

|    | mm | 0.64  | 0.76  |

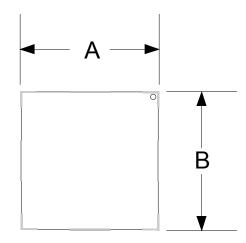

# DS3832C-311 PACKAGE DIMENSIONS (With Attached DS3802 Battery Cap)

| DIM |    | MIN | MAX    |

|-----|----|-----|--------|

| A   | in | -   | 1.830  |

|     | mm | -   | 45.046 |

| В   | in | -   | 1.830  |

|     | mm | -   | 45.046 |

| C   | in | -   | 0.435  |

|     | mm | -   | 10.708 |

| D   | in | -   | 0.0390 |

|     | mm | -   | 0.9600 |

### **DS3832C-311 RECOMMENDED LAND PATTERN**

(With Overlaid Package Outline)

The DS3832C-311 ball grid array is a subset of the industry-standard 40mm BGA format, with all balls on a 50mil grid. Corner balls have been removed to provide space for the electrical and mechanical interface features that facilitate attachment of the DS3802 battery cap