# 5 V and 3.3 V Supply Monitor, Watchdog Timer, Manual Reset, with Active High & Low Resets

#### **FEATURES**

- Selectable reset voltage tolerance

- CAT1232LP for 5 V supply

- CAT1832 for 3.3 V supply

- Selectable watchdog period: 150 ms, 600 ms or 1.2 s

- Two reset outputs

- Active high, push-pull reset output

- Active low, open-drain reset output (CAT1232LP)

- Active low, push-pull reset output (CAT1832)

- Debounced manual push-button reset

- Compact SOIC and MSOP packages

For Ordering Information details, see page 11.

#### **APPLICATIONS**

- Microprocessor Systems

- Portable Equipment

- Controllers

- Single Board Computers

- Instrumentations

- Telecommunications

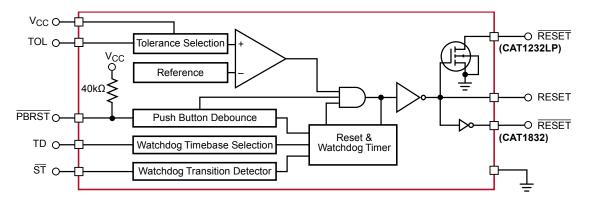

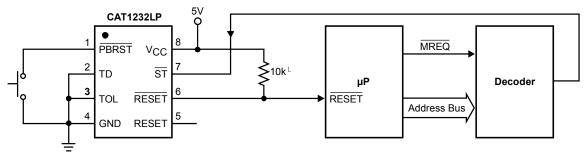

# **FUNCTIONAL DIAGRAM**

#### DESCRIPTION

The CAT1232LP and CAT1832 microprocessor supervisors can halt and restart a "hung-up" or "stalled" microprocessor, restart a microprocessor after a power failure, and debounce a manual/pushbutton microprocessor reset switch. The devices are drop in replacements for the Maxim/Dallas Semiconductor DS1232LP and DS1832 supervisors

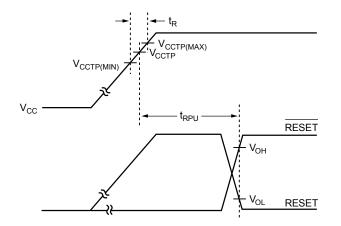

Precision reference and comparator circuits monitor the 5 V or  $3.3 \, \text{V}$  system power supply voltage,  $V_{\text{CC}}$ . During power-up or when the power supply falls outside selectable tolerance limits, both the RESET and  $\overline{\text{RESET}}$  become active. After the power supply voltage rises above the RESET threshold voltage, the reset signals remain active for a minimum of 250ms, allowing the power supply and system processor to stabilize. The trip-point tolerance input, TOL, selects the trip level tolerance to be either 5% or 10% for the CAT1232LP 5 V supply and 10% or 20% for the CAT1832 3.3 V supply.

Each device has a push-pull, active HIGH reset output. The CAT1232LP also has an open drain, active LOW reset output while the CAT1832 also has a push-pull, active LOW reset output.

A debounced manual reset input activates the reset outputs and holds them active for a minimum period of 250 ms after being released.

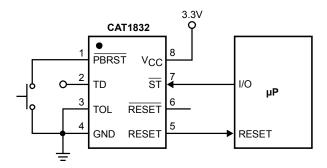

Also included is a watchdog timer to reset a microprocessor that has stopped due to a software or hardware failure. Three watchdog time-out periods are selectable: 150 ms, 600 ms and 1.2 s. If the  $\overline{ST}$  input is not strobed low before the watchdog time out period expires, the reset signals become active for a minimum of 250 ms.

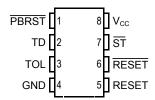

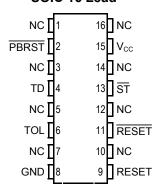

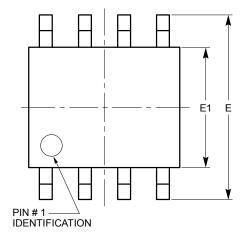

#### **PIN CONFIGURATION**

SOIC 8 Lead MSOP 8 Lead PDIP 8 Lead

#### **SOIC 16 Lead**

#### **PIN DESCRIPTION**

| Pin Number<br>8-Lead<br>Package | Pin Number<br>16-Lead<br>Package | Name            | Function                                                                                                                                                                                                                     |

|---------------------------------|----------------------------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                               | 2                                | PBRST           | Debounced manual pushbutton reset input                                                                                                                                                                                      |

| 2                               | 4                                | TD              | Watchdog typical time delay selection:<br>a) $t_{TD}$ = 150 ms for TD = GND<br>b) $t_{TD}$ = 600 ms for TD = Open<br>c) $t_{TD}$ = 1200 ms for TD = $V_{CC}$                                                                 |

| 3                               | 6                                | TOL             | CAT1232LP TOL selects 5% (TOL = GND) or 10% (TOL = $V_{CC}$ ) trip point tolerance. CAT1832 TOL selects 10% (TOL = GND) or 20% TOL = $V_{CC}$ ) trip point tolerance.                                                        |

| 4                               | 8                                | GND             | Ground                                                                                                                                                                                                                       |

| 5                               | 9                                | RESET           | Active HIGH reset output. RESET is active  1. If V <sub>CC</sub> falls below the reset voltage trip point  2. If PBRST is low  3. If ST is not strobed low before the timeout period set by TD expires.  4. During power-up. |

| 6                               | 11                               | RESET           | Active LOW reset output. (See RESET)                                                                                                                                                                                         |

| 7                               | 13                               | ST              | Strobe Input                                                                                                                                                                                                                 |

| 8                               | 15                               | V <sub>CC</sub> | Power Supply                                                                                                                                                                                                                 |

|                                 | 1, 3. 5, 7, 10,<br>12, 14, 16    | NC              | No internal connection                                                                                                                                                                                                       |

# **ABSOLUTE MAXIMUM RATINGS** (\*)

| Parameters                          | Ratings                       | Units |

|-------------------------------------|-------------------------------|-------|

| Voltage on V <sub>CC</sub>          | -0.5 to 7.0                   | V     |

| Voltage on ST and TD                | -0.5 to V <sub>CC</sub> + 0.5 | V     |

| Voltage on PBRST,<br>RESETand RESET | -0.5 to V <sub>CC</sub> + 0.5 | V     |

| Parameters                       | Ratings     | Units |

|----------------------------------|-------------|-------|

| Maximum Junction Temperature     | 125         | °C    |

| Storage Temperature Range        | -65 to +150 | °C    |

| Lead Soldering Temperature (10s) | 300         | လ     |

| Operating Temperature Range      | -40 to +85  | °C    |

<sup>\*</sup> Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions outside of those listed in the operational sections of this specification is not implied. Exposure to any absolute maximum rating for extended periods may affect device performance and reliability.

#### **ELECTRICAL CHARACTERISTICS**

Unless otherwise stated, 1.0 V -  $V_{CC}$  - 5.5 V and over the operating temperature range of -40°C to +85°C. All voltages are referenced to ground.

| Symbol            | Parameter                                           | Conditions                         | Min                     | Тур                    | Max                     | Units |

|-------------------|-----------------------------------------------------|------------------------------------|-------------------------|------------------------|-------------------------|-------|

| V <sub>CC</sub>   | Supply Voltage                                      |                                    | 1.0                     |                        | 5.5                     | V     |

| ı                 | Cumply Current                                      | V <sub>CC</sub> = 5.5 V, CAT1232LP |                         | 35                     | 50                      |       |

| I <sub>CC1</sub>  | Supply Current                                      | V <sub>CC</sub> = 3.6 V, CAT1832   |                         | 20                     | 35                      | μA    |

| \/                | ST and PBRST Input High                             | (5)                                | 2                       |                        | V <sub>CC</sub> + 0.3 V | V     |

| $V_{IH}$          | Level                                               | (6)                                | V <sub>CC</sub> - 0.4 V |                        | V <sub>CC</sub> + 0.3 V | V     |

| \/                | ST and PBRST Input Low                              | V <sub>CC</sub> = 5.5 V, CAT1232LP | -0.3                    |                        | 0.8                     | V     |

| $V_{IL}$          | Level                                               | V <sub>CC</sub> = 3.6 V, CAT1832   |                         |                        | 0.5                     | V     |

| $V_{\text{CCTP}}$ | V <sub>CC</sub> Trip Point (TOL = GND)              | CAT1232LP                          | 4.50                    | 4.62                   | 4.74                    | V     |

| V <sub>CCTP</sub> | V <sub>CC</sub> Trip Point (TOL = V <sub>CC</sub> ) | CAT1232LP                          | 4.25                    | 4.37                   | 4.49                    | V     |

| V <sub>CCTP</sub> | V <sub>CC</sub> Trip Point (TOL = GND)              | CAT1832                            | 2.80                    | 2.88                   | 2.97                    | V     |

| V <sub>CCTP</sub> | V <sub>CC</sub> Trip Point (TOL = V <sub>CC</sub> ) | CAT1832                            | 2.47                    | 2.55                   | 2.64                    | V     |

| t <sub>TD</sub>   | Watchdog Time-Out Period                            | TD = GND                           | 62.5                    | 150                    | 250                     | ms    |

| t <sub>TD</sub>   | Watchdog Time-Out Period                            | $TD = V_{CC}$                      | 500                     | 1200                   | 2000                    | ms    |

| t <sub>TD</sub>   | Watchdog Time-Out Period                            | TD floating                        | 250                     | 600                    | 1000                    | ms    |

| V <sub>OH</sub>   | Output Voltage                                      | I = -500 μA <sup>(3)</sup>         | V <sub>CC</sub> -0.5 V  | V <sub>CC</sub> -0.1 V |                         | V     |

| I <sub>OH</sub>   | Output Current                                      | Output = 2.4 V (2)                 |                         | -350                   |                         | μΑ    |

| I <sub>OL</sub>   | Output Current                                      | Output = 0.4 V                     | 10                      |                        |                         | mA    |

| I <sub>IL</sub>   | Input Leakage                                       | (1)                                | -1.0                    |                        | 1.0                     | μΑ    |

| R <sub>PU</sub>   | Internal Pull-Up Resistor                           | (1)                                | 32                      | 40                     | 55                      | kΩ    |

| C <sub>IN</sub>   | Input Capacitance                                   |                                    |                         |                        | 5                       | pF    |

| C <sub>OUT</sub>  | Output Capacitance                                  |                                    |                         |                        | 7                       | pF    |

| t <sub>PB</sub>   | PBRST Manual Reset<br>Minimum Low Time              | PBRST = V <sub>IL</sub>            | 20                      |                        |                         | ms    |

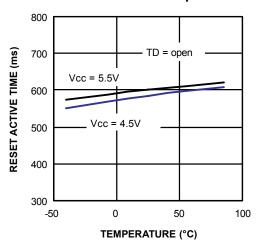

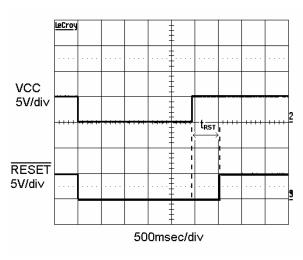

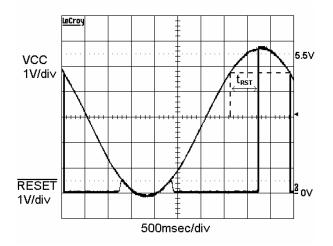

| $t_{RST}$         | Reset Active Time                                   |                                    | 250                     | 600                    | 1000                    | ms    |

| t <sub>ST</sub>   | ST Pulse Width                                      | (4)                                | 20                      |                        |                         | ns    |

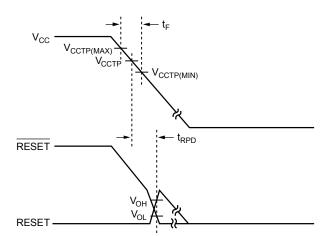

| t <sub>RPD</sub>  | V <sub>CC</sub> Fail Detect to RESET or RESET       |                                    |                         | 5                      | 8                       | μs    |

| t <sub>F</sub>    | V <sub>CC</sub> Slew Rate                           |                                    | 20                      |                        |                         | μs    |

| t <sub>PDLY</sub> | PBRST Stable LOW to RESET and RESET Active          |                                    |                         |                        | 20                      | ms    |

| t <sub>RPU</sub>  | V <sub>CC</sub> Detect to RESET or RESET Inactive   | t <sub>RISE</sub> = 5 μs           | 250                     | 600                    | 1000                    | ms    |

| $t_{R}$           | V <sub>CC</sub> Slew Rate                           | 4.25 V to 4.75 V                   | 0                       |                        |                         | ns    |

- (1)  $\overline{PBRST}$  is internally pulled HIGH to  $V_{CC}$  through a nominal 40 k $\Omega$  resistor (RPU).

- (2) RESET is an open drain output on the CAT1232LP.

- (3) RESET remains within 0.5 V of  $V_{CC}$  on power-down until  $V_{CC}$  falls below 2 V. RESET remains within 0.5 V of ground on power-down until  $V_{CC}$  falls below 2.0 V.

- (4) Must not exceed the minimum watchdog time-out period ( $t_{TD}$ ). The watchdog circuit cannot be disabled. To avoid a reset,  $\overline{ST}$  must be strobed.

- (5) Measured with  $V_{CC} \ge 2.7 \text{ V}$ .

- (6) Measured with  $V_{CC}$  < 2.7 V.

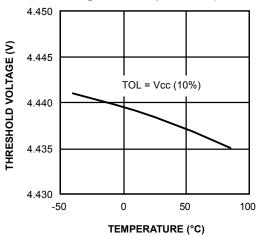

#### TYPICAL CHARACTERISTICS

For the CAT1232LP,  $V_{CC}$  = 5 V and  $T_{AMB}$  = 25°C unless otherwise stated.

#### Threshold Voltage vs. Temperature (10% TOL)

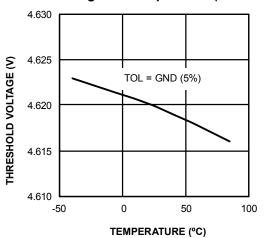

#### Threshold Voltage vs. Temperature (5% TOL)

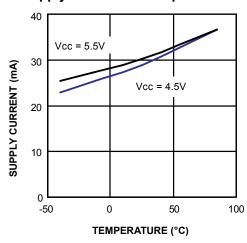

#### **Supply Current vs. Temperature**

**Reset Active Time vs. Temperature**

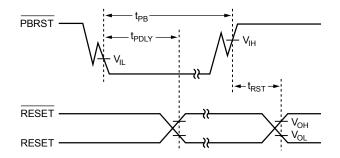

#### **Reset Active Time Waveform**

#### **Transient Response**

#### APPLICATION INFORMATION

#### **SUPPLY VOLTAGE MONITOR**

#### **Reset Signal Polarity and Output Stage Structure**

RESET is an active LOW signal. It is developed with an open drain driver in the CAT1232LP. A pull-up resistor is required, typical values are 10 kΩ to 50 kΩ. The CAT1832 uses a CMOS push-pull output stage for the  $\overline{\text{RESET}}$ .

RESET is an active High signal developed by a CMOS push-pull output stage and is the logical opposite to RESET.

#### **Trip Point Tolerance Selection**

The TOL input is used to select the  $V_{CC}$  trip point threshold. This selection is made connecting the TOL input to ground or  $V_{CC}$ . Connecting TOL to Ground makes the  $V_{CC}$  trip threshold 4.62 V for the CAT1232LP and 2.88 V for the CAT1832.

Connecting TOL to  $V_{\text{CC}}$  makes the  $V_{\text{CC}}$  trip threshold 4.37 V for the CAT1232LP and 2.55 V for the CAT1832.

After  $V_{CC}$  has risen above the trip point set by TOL, RESET and RESETremain active for a minimum time period of 250 ms.

On power-down, once  $V_{\text{CC}}$  falls below the reset threshold the RESET outputs will remain active and are guaranteed valid down to a  $V_{\text{CC}}$  level of 1.0 V.

Figure 1. Timing Diagram: Power Up

| Tolerance<br>Select                | Trip Point | Trip Point Voltage (V) |         |      |

|------------------------------------|------------|------------------------|---------|------|

| Voltage                            | Tolerance  | Min                    | Nominal | Max  |

| CAT1232LP<br>TOL = V <sub>CC</sub> | 10 %       | 4.25                   | 4.37    | 4.49 |

| CAT1232LP<br>TOL = GND             | 5 %        | 4.50                   | 4.62    | 4.74 |

| CAT1832<br>TOL = V <sub>CC</sub>   | 20 %       | 2.47                   | 2.55    | 2.64 |

| CAT1832<br>TOL = GND               | 10 %       | 2.80                   | 2.88    | 2.97 |

#### **Manual Reset Operation**

Push-button input,  $\overline{PBRST}$ , allows the user to issue reset signals. The pushbutton input is debounced and is pulled high through an internal 40 k $\Omega$  resistor.

When PBRST is held low for the minimum time of 20 ms, both resets become active and remain active for a minimum time period of 250 ms after PBRST returns high.

No external pull-up resistor is required, since  $\overline{\mathsf{PBRST}}$  is pulled high by an internal 40 k $\Omega$  resistor.

PBRST can be driven from a TTL or CMOS logic line or short-ed to ground with a mechanical switch.

Figure 2. Timing Diagram: Power Down

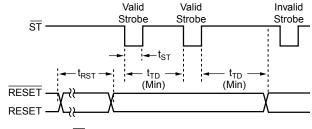

#### WATCHDOG TIMER AND ST INPUT

A watchdog timer stops and restarts a microprocessor that has stopped proper operation or become "hung". The watchdog performs this function by monitoring the  $\overline{ST}$  input. After the reset outputs go inactive the  $\overline{ST}$  input must be strobed with a high-to-low signal transition prior to the minimum watchdog timeout period. However if the  $\overline{ST}$  input is not strobed with a high-to-low signal transition prior to a watchdog timeout the reset outputs will become active for TRST reseting and restarting the microprocessor. Once the resets return to the inactive state the watchdog timer restarts the process.

The TD input allows the user to select from three predetermined watchdog timeout periods. Always use the minimum timeout period to determine the required frequency of  $\overline{ST}$  high-to-low transitions and the maximum to determine the time prior to the reset outputs becoming active.  $\overline{ST}$  pulse widths must be 20 ns or greater.

The watchdog timer cannot be disabled. It must be strobed with a high-to-low signal transition to avoid a watchdog timeout and subsequent reset.

| TD Voltage      | Watchdog Time-out Period (ms) |         |      |  |

|-----------------|-------------------------------|---------|------|--|

| Level           | Min                           | Nominal | Max  |  |

| GND             | 62.5                          | 150     | 250  |  |

| Floating        | 250                           | 600     | 1000 |  |

| V <sub>CC</sub> | 500                           | 1200    | 2000 |  |

Figure 4. CAT1832 Application Circuit:

Pushbutton Reset

Figure 5. CAT1232LP Application Circuit: Watchdog Timer

Figure 6. Timing Diagram: Pushbutton Reset

Note:  $\overline{\text{ST}}$  is ignored whenever a reset is active

Figure 7. Timing Diagram: Strobe Input

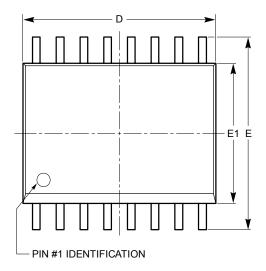

# **PACKAGE OUTLINE DRAWINGS**

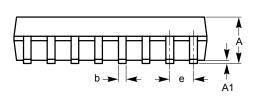

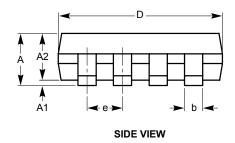

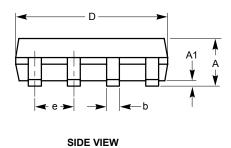

# SOIC 16-Lead 300 mils (W)<sup>(1)(2)</sup>

| SYMBOL | MIN      | NOM   | MAX   |

|--------|----------|-------|-------|

| Α      | 2.36     | 2.49  | 2.64  |

| A1     | 0.10     |       | 0.30  |

| b      | 0.33     | 0.41  | 0.51  |

| С      | 0.18     | 0.23  | 0.28  |

| D      | 10.08    | 10.31 | 10.49 |

| E      | 10.01    | 10.31 | 10.64 |

| E1     | 7.39     | 7.49  | 7.59  |

| е      | 1.27 BSC |       |       |

| h      | 0.25     |       | 0.75  |

| L      | 0.38     | 0.81  | 1.27  |

| θ      | 0°       |       | 8°    |

SIDE VIEW

**TOP VIEW**

**END VIEW**

- (1) All dimensions are in millimeters.

- (2) Complies with JEDEC MS-013.

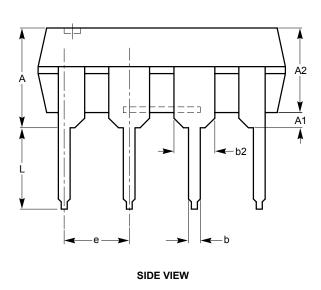

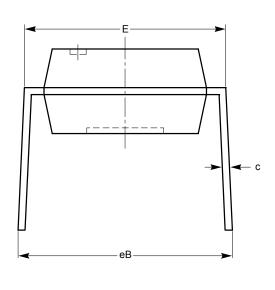

PDIP 8-Lead 300mils  $(L)^{(1)(2)}$

| SYMBOL | MIN  | NOM      | MAX   |

|--------|------|----------|-------|

| Α      |      |          | 5.33  |

| A1     | 0.38 |          |       |

| A2     | 2.92 | 3.30     | 4.95  |

| b      | 0.36 | 0.46     | 0.56  |

| b2     | 1.14 | 1.52     | 1.78  |

| С      | 0.20 | 0.25     | 0.36  |

| D      | 9.02 | 9.27     | 10.16 |

| Е      | 7.62 | 7.87     | 8.25  |

| е      |      | 2.54 BSC |       |

| E1     | 6.10 | 6.35     | 7.11  |

| eB     | 7.87 |          | 10.92 |

| Ĺ      | 2.92 | 3.30     | 3.80  |

**TOP VIEW**

**END VIEW**

- (1) All dimensions are in millimeters.

- (2) Complies with JEDEC MS-001.

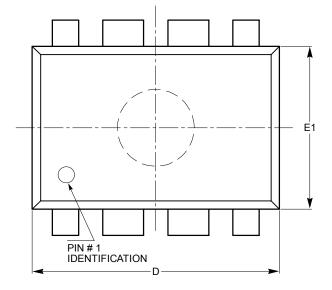

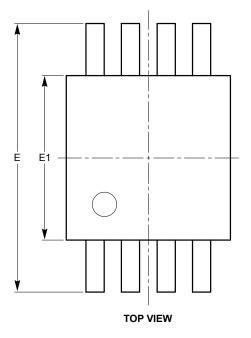

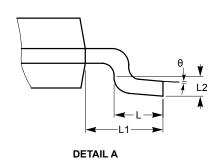

MSOP 8-Lead (Z) (1)(2)

| SYMBOL | MIN      | NOM      | МАХ  |

|--------|----------|----------|------|

| Α      |          |          | 1.10 |

| A1     | 0.05     | 0.10     | 0.15 |

| A2     | 0.75     | 0.85     | 0.95 |

| b      | 0.22     |          | 0.38 |

| С      | 0.13     |          | 0.23 |

| D      | 2.90     | 3.00     | 3.10 |

| Е      | 4.80     | 4.90     | 5.00 |

| E1     | 2.90     | 3.00     | 3.10 |

| е      |          | 0.65 BSC |      |

| L      | 0.40     | 0.60     | 0.80 |

| L1     | 0.95 REF |          |      |

| L2     | 0.25 BSC |          |      |

| θ      | 0°       |          | 6°   |

- (1) All dimensions are in millimeters. Angles in degrees.

- (2) Complies with JEDEC MO-187.

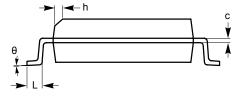

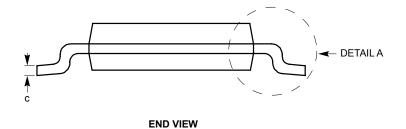

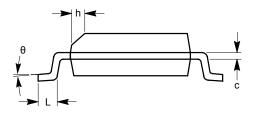

# SOIC 8-Lead 150mils (V) $^{(1)(2)}$

| SYMBOL | MIN  | NOM      | MAX  |  |

|--------|------|----------|------|--|

| А      | 1.35 |          | 1.75 |  |

| A1     | 0.10 |          | 0.25 |  |

| b      | 0.33 |          | 0.51 |  |

| С      | 0.19 |          | 0.25 |  |

| D      | 4.80 |          | 5.00 |  |

| Е      | 5.80 |          | 6.20 |  |

| E1     | 3.80 |          | 4.00 |  |

| е      |      | 1.27 BSC |      |  |

| h      | 0.25 |          | 0.50 |  |

| L      | 0.40 |          | 1.27 |  |

| θ      | 0°   |          | 8°   |  |

**TOP VIEW**

**END VIEW**

- (1) All dimensions are in millimeters. Angles in degrees.

- (2) Complies with JEDEC MS-012.

#### ORDERING INFORMATION

| ORDERING PART NUMBER | Package      | Parts per Tube | Parts Per Reel | Reel Size (inch) |

|----------------------|--------------|----------------|----------------|------------------|

| CAT1232LPV-GT3*      | 8-lead, SOIC |                | 3,000          | 13               |

| CAT1232LPZ-GT3*      | 8-lead, MSOP | _              | 3,000          | 13               |

|                      |              |                |                |                  |

| CAT1832L-G           | 8-lead, PDIP | 50             | <del>-</del>   | _                |

| CAT1832V-GT3         | 8-lead, SOIC | _              | 3,000          | 13               |

| CAT1832Z-GT3         | 8-lead, MSOP | _              | 3,000          | 13               |

<sup>\*</sup> Consult sales.

#### Notes:

- (1) All packages are RoHS-compliant (Lead-free, Halogen-free).

- (2) The standard lead finish is NiPdAu.

- (3) The device used in the above example is a CAT1232LPV-GT3 (SOIC 8-Lead, NiPdAu, Tape & Reel).

- (4) For additional package and temperature options, please contact your nearest ON Semiconductor Sales office.

- (5) The SOIC 16-Lead package is only available in Matte-Tin finish.

ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC) or its subsidiaries in the United States and/or other countries. SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of SCILLC's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such application and specifications and in the product of t

#### **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor

P.O. Box 61312, Phoenix, Arizona 85082–1312 USA

Phone: 480–829–7710 or 800–344–3860 Toll Free USA/Canada

Fax: 480–829–7709 or 800–344–3867 Toll Free USA/Canada

Email: orderlit@onsemi.com

N. American Technical Support: 800-282-9855 Toll Free USA/Canada

Japan: ON Semiconductor, Japan Customer Focus Center 2–9–1 Kamimeguro, Meguro–ku, Tokyo, Japan 153–0051 **Phone**: 81–3–5773–3850

ON Semiconductor Website: http://onsemi.com

Order Literature: http://www.onsemi.com/litorder

For additional information, please contact your local Sales Representative.