# LMP8100 Programmable Gain Amplifier

Check for Samples: LMP8100

### **FEATURES**

- Typical Values, T<sub>A</sub> = 25°C

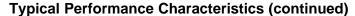

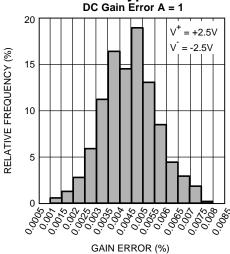

- Gain Error (Over Temperature Range)

- LMP8100A 0.03%

- LMP8100 0.075%

- Gain Range 1 to 16 V/V in 1 V/V Steps

- Programmable Frequency Compensation

- Input Zero Calibration Switch

- Input Offset Voltage (Max, LMP8100A) 250 μV

- Input Bias Current 0.1 pA

- Input Noise Voltage 12 nV/√Hz

- · Unity Gain Bandwidth 33 MHz

- Slew Rate 12 V/µs

- Output Current 20 mA

- Supply Voltage Range 2.7V to 5.5V

- Supply Current 5.3 mA

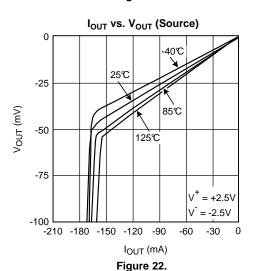

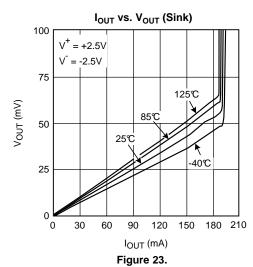

- Rail-to-Rail Output Swing V<sup>+</sup> −50 mV to V<sup>-</sup> +50 mV

#### **APPLICATIONS**

- Industrial Instrumentation

- Data Acquisition Systems

- Test Equipment

- Scaling Amplifier

- Gain Control

- Sensor Interface

### DESCRIPTION

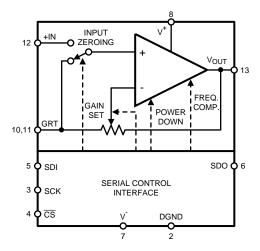

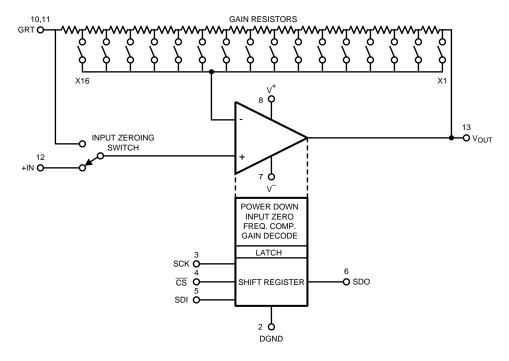

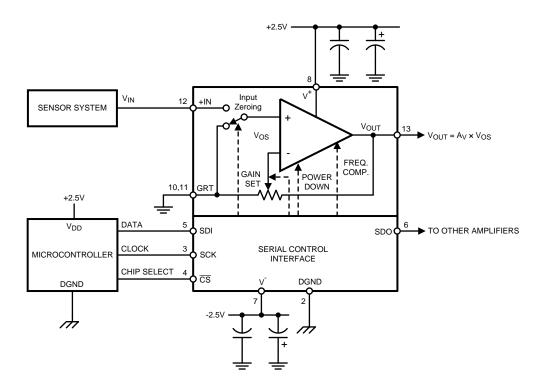

The LMP8100 programmable gain amplifier features an adjustable gain from 1 to 16 V/V in 1 V/V increments. At the core of the LMP8100 is a precision, 33 MHz, CMOS input, rail-to-rail input/output operational amplifier with a typical openloop gain of 110 dB. Amplifier closed-loop gain is set by an array of precision thin-film resistors. Amplifier control modes are programmed via a serial port that allows devices to be cascaded so that an array of LMP8100 amplifiers can be programmed by a single serial data stream. The control mode registers are double buffered to insure glitch-free transitions between programmed settings. The LMP8100 is part of the LMPTM precision amplifier family and is ideal for a variety of applications.

The amplifier features several programmable controls including: gain; a power-conserving shutdown mode which can reduce current consumption to only 20  $\mu$ A; an input zeroing switch which allows the output offset voltage to be measured to facilitate system calibration; and four levels of internal frequency compensation which can be set to maximize bandwidth at the different gain settings.

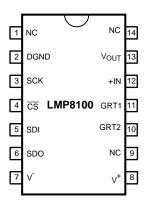

The LMP8100 comes in a 14-Pin SOIC package.

M

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

LMP is a trademark of Texas Instruments.

All other trademarks are the property of their respective owners.

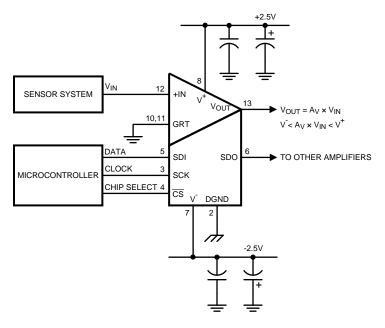

# **Simplified Block Diagram**

# **Block Diagram**

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

Absolute Maximum Ratings (1)(2)

| Human Body Model                                         | 2 kV                                                                    |

|----------------------------------------------------------|-------------------------------------------------------------------------|

| Machine Model                                            | 200V                                                                    |

|                                                          | 2.5V                                                                    |

|                                                          |                                                                         |

|                                                          | 6V                                                                      |

|                                                          | V <sup>+</sup> +0.3V, V <sup>−</sup> −0.3V                              |

|                                                          | ±10 mA                                                                  |

|                                                          | −65°C to +150°C                                                         |

|                                                          | +150°C                                                                  |

| Lead Temperature, Infrared or Convection Reflow (20 sec) | 235°C                                                                   |

| Lead Temperature, Wave Solder (10 sec)                   | 260°C                                                                   |

|                                                          | Machine Model  Lead Temperature, Infrared or Convection Reflow (20 sec) |

- (1) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is intended to be functional, but for which specific performance is not ensured. For ensured specifications and the test conditions, see Electrical Characteristics.

- (2) If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office/ Distributors for availability and specifications.

- (3) Human Body Model, applicable std. MIL-STD-883, Method 3015.7. Machine Model, applicable std. JESD22–A115–A (ESD MM std. of JEDEC). Field-Induced Charge-Device Model, applicable std. JESD22–C101–C (ESD FICDM std. of JEDEC).

- (4) The short circuit test is a momentary test which applies to both single-supply and split-supply operation. Continuous short circuit operation at elevated ambient temperature can exceed the maximum allowable junction temperature of 150°C.

- (5) The maximum power dissipation is a function of  $T_{J(MAX)}$ ,  $\theta_{JA}$ . The maximum allowable power dissipation at any ambient temperature is  $P_D = (T_{J(MAX)} T_A)/\theta_{JA}$ . All numbers apply for packages soldered directly onto a PC Board.

## Operating Ratings(1)

| Supply Voltage $(V_S = V^+ - V^-)$                           |             | 2.7V to 5.5V    |

|--------------------------------------------------------------|-------------|-----------------|

| Junction Temperature Range <sup>(2)</sup>                    | LMP8100A    | -40°C to +125°C |

|                                                              | LMP8100     | -40°C to +85°C  |

| Package Thermal Resistance (θ <sub>JA</sub> <sup>(2)</sup> ) | 14-Pin SOIC | 145°C/W         |

- (1) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is intended to be functional, but for which specific performance is not ensured. For ensured specifications and the test conditions, see Electrical Characteristics.

- (2) The maximum power dissipation is a function of  $T_{J(MAX)}$ ,  $\theta_{JA}$ . The maximum allowable power dissipation at any ambient temperature is  $P_D = (T_{J(MAX)} T_A) / \theta_{JA}$ . All numbers apply for packages soldered directly onto a PC Board.

## **5V Electrical Characteristics**

Unless otherwise specified, all limits are ensured for  $T_A = 25^{\circ}\text{C}$ .  $V^+ = 5\text{V}$ ,  $V^- = 0\text{V}$ , DGND = 0V, +IN = GRT =  $V^+/2$ ,  $R_L = 10$  k $\Omega$  to  $V^+/2$ ; Gain = 1 V/V. **Boldface** limits apply at the temperature extremes.

| Symbol | Parame                                      | ter           | Conditions                                                              | Min <sup>(1)</sup> | Typ <sup>(2)</sup> | Max <sup>(1)</sup>    | Units    |

|--------|---------------------------------------------|---------------|-------------------------------------------------------------------------|--------------------|--------------------|-----------------------|----------|

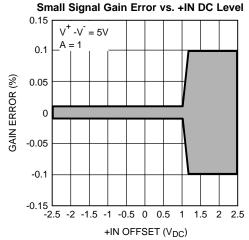

|        | Gain Error                                  | LMP8100A      | 0V < +IN (DC) < 3.5V,<br>1 V/V ≤ Gain ≤ 16 V/V, 0.5V < V <sub>OUT</sub> |                    | 0.015              | 0.03<br><b>0.03</b>   | 0/       |

|        | Gain Error                                  | LMP8100       | < 4.5V                                                                  |                    | 0.015              | 0.075<br><b>0.075</b> | %        |

|        | LMP8100 Gain Error (0<br>Extended +IN Range | Gain = 1 V/V) | +IN > 3.5V,<br>0.3V < V <sub>OUT</sub> < 4.7V                           |                    |                    | 0.1<br><b>0.2</b>     | %        |

| TCGE   | Gain Drift                                  | LMP8100A      | Gain = 16                                                               |                    | 0.5                | 2.2                   | 22 mm/0C |

|        |                                             | LMP8100       | Gain = 16                                                               |                    | 0.8                | 4.8                   | ppm/°C   |

<sup>(1)</sup> All limits are specified by testing or statistical analysis.

<sup>(2)</sup> Typical Values indicate the most likely parametric norm as determined at the time of characterization. Actual typical values may vary over time and will also depend on the application and configuration. The typical values are not tested and are not specified on shipped production material.

## 5V Electrical Characteristics (continued)

Unless otherwise specified, all limits are ensured for  $T_A = 25^{\circ}\text{C}$ .  $V^+ = 5V$ ,  $V^- = 0V$ , DGND = 0V, +IN = GRT =  $V^+/2$ ,  $R_L = 10$  k $\Omega$  to  $V^+/2$ ; Gain = 1 V/V. **Boldface** limits apply at the temperature extremes.

| Symbol            | Param                 | eter      | Conditions                                 | Min <sup>(1)</sup> | Typ <sup>(2)</sup> | Max <sup>(1)</sup>   | Units            |

|-------------------|-----------------------|-----------|--------------------------------------------|--------------------|--------------------|----------------------|------------------|

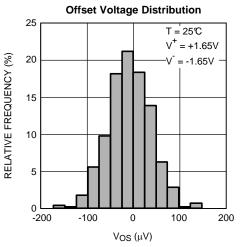

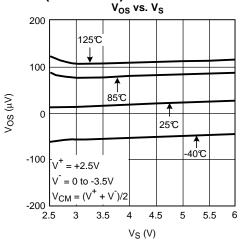

| V <sub>OS</sub>   | Input Offset Voltage  | LMP8100A  |                                            |                    | ±50                | ±250<br>± <b>450</b> | .,               |

|                   |                       | LMP8100   |                                            |                    | ±50                | ±400<br>± <b>600</b> | μV               |

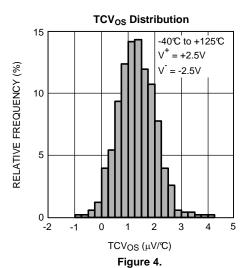

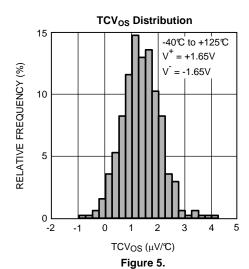

| TCV <sub>OS</sub> | Input Offset Temp Co  | efficient | See <sup>(3)</sup>                         |                    | 1.5                | 5                    | μV/°C            |

| I <sub>B</sub>    | Input Bias Current    |           |                                            |                    | 0.1                | 5<br><b>100</b>      | pA               |

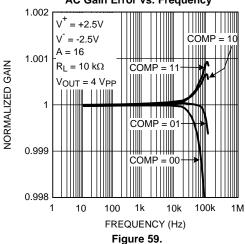

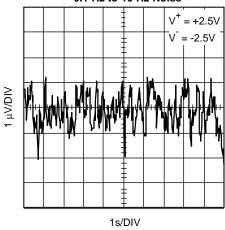

| e <sub>n</sub>    | Input-Referred Noise  | Voltage   | f = 10 kHz, 1 V/V ≤ Gain ≤ 16 V/V          |                    | 12                 |                      | nV/√Hz           |

|                   |                       |           | f = 0.1 Hz to 10 Hz, 1 V/V ≤ Gain ≤ 16 V/V |                    | 3.8                |                      | μV <sub>PP</sub> |

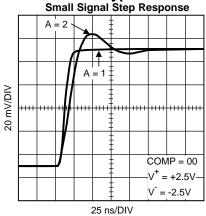

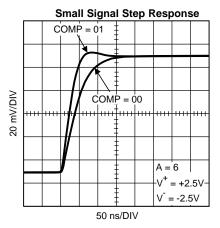

| BW                | Bandwidth             |           | C1 = C0 = 0, Gain = 1 V/V                  |                    | 33                 |                      |                  |

|                   |                       |           | C1 = C0 = 0, Gain = 2 V/V                  |                    | 15.5               |                      | MHz              |

|                   |                       |           | C1 = C0 = 1, Gain = 16 V/V                 |                    | 9.5                |                      |                  |

| SR                | Slew Rate             |           | See <sup>(4)</sup>                         |                    | 12                 |                      | V/µs             |

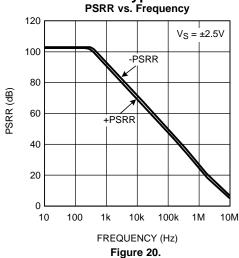

| PSRR              | Power Supply Rejecti  | on Ratio  | 2.7V < V <sup>+</sup> < 5.5V               | 90<br><b>85</b>    | 100                |                      | dB               |

| Vo                | Output Swing<br>High  |           | +IN = 5V                                   | 4.9<br><b>4.85</b> | 4.95               |                      | V                |

|                   | Output Swing<br>Low   |           | +IN = 0V                                   |                    | 50                 | 100<br><b>150</b>    | mV               |

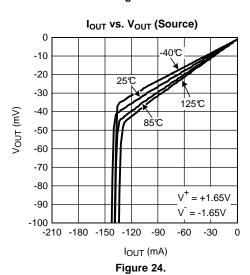

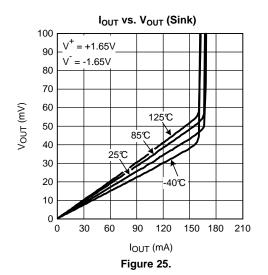

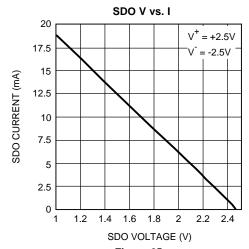

| $I_{O}$           | Output Current        |           | Sourcing and Sinking                       | 15                 | 20                 |                      | mA               |

| V <sub>IN</sub>   | Input Voltage Range   |           |                                            | −0.2<br><b>0</b>   |                    | 5.2<br><b>5.0</b>    | V                |

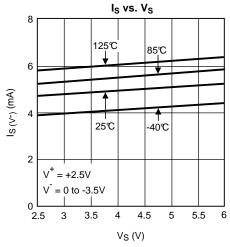

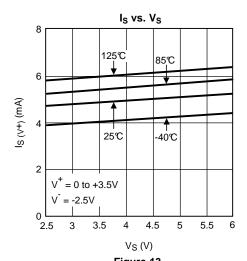

| I <sub>S</sub>    | Supply Current        |           |                                            |                    | 5.3                | 6.0<br><b>7.2</b>    | mA               |

| I <sub>PD</sub>   | Supply Current, Power | er Down   |                                            |                    | 3.5                | 20<br><b>40</b>      | μA               |

|                   | Feedback Resistance   | ,         |                                            |                    | 5.6                |                      | kΩ               |

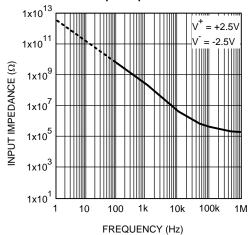

| R <sub>IN</sub>   | Input Impedance       |           | f = 10 Hz                                  |                    | >10                |                      | GΩ               |

<sup>3)</sup> The offset voltage average drift is determined by dividing the value of VOS at the temperature extremes by the total temperature change.

#### 3.3V Electrical Characteristics

Unless otherwise specified, all limits are ensured for  $T_A = 25^{\circ}C$ .  $V^+ = 3.3V$ ,  $V^- = 0V$ , DGND = 0V, +IN = GRT =  $V^+/2$ ,  $R_L = 10$  k $\Omega$  to  $V^+/2$ ; Gain = 1 V/V. **Boldface** limits apply at the temperature extremes.

| Symbol | Param                                      | eter          | Conditions                                                         | Min <sup>(1)</sup> | Typ <sup>(2)</sup> | Max <sup>(1)</sup>    | Units  |

|--------|--------------------------------------------|---------------|--------------------------------------------------------------------|--------------------|--------------------|-----------------------|--------|

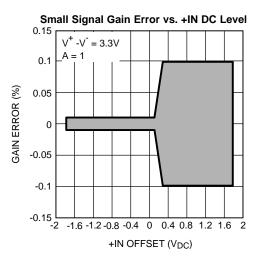

|        |                                            |               | 0V < +IN < 1.8V,<br>1 V/V ≤ Gain ≤ 16 V/V, 0.3V < V <sub>OUT</sub> |                    | 0.015              | 0.03<br><b>0.03</b>   | 0/     |

|        | Gain Error                                 | LMP8100       | < 3.0V                                                             |                    | 0.015              | 0.075<br><b>0.075</b> | %      |

|        | LMP8100 Gain Error (<br>Extended +IN Range | Gain = 1 V/V) | +IN > 1.8V,<br>0.3V < V <sub>OUT</sub> < 3.0V                      |                    |                    | 0.1<br><b>0.2</b>     | %      |

| TCGE   | Gain Drift                                 | LMP8100A      | Gain = 16                                                          |                    | 0.5                | 2.2                   | /00    |

|        |                                            | LMP8100       | Gain = 16                                                          |                    | 0.8                | 4.8                   | ppm/°C |

| Vos    | Input Offset Voltage                       | LMP8100A      |                                                                    |                    | ±50                | ±250<br><b>±450</b>   | \/     |

|        |                                            | LMP8100       |                                                                    |                    | ±50                | ±400<br><b>±600</b>   | μV     |

<sup>1)</sup> All limits are specified by testing or statistical analysis.

<sup>(4)</sup> Slew rate is the average of the rising and falling slew rates.

<sup>(2)</sup> Typical Values indicate the most likely parametric norm as determined at the time of characterization. Actual typical values may vary over time and will also depend on the application and configuration. The typical values are not tested and are not specified on shipped production material.

## 3.3V Electrical Characteristics (continued)

Unless otherwise specified, all limits are ensured for  $T_A = 25^{\circ}\text{C}$ .  $V^+ = 3.3\text{V}$ ,  $V^- = 0\text{V}$ , DGND = 0V, +IN = GRT = V<sup>+</sup>/2,  $R_L = 10$  k $\Omega$  to V<sup>+</sup>/2; Gain = 1 V/V. **Boldface** limits apply at the temperature extremes.

| Symbol            | Parameter                     | Conditions                                 | Min <sup>(1)</sup> | Typ <sup>(2)</sup> | Max <sup>(1)</sup> | Units              |

|-------------------|-------------------------------|--------------------------------------------|--------------------|--------------------|--------------------|--------------------|

| TCV <sub>OS</sub> | Input Offset Temp Coefficient | See <sup>(3)</sup>                         |                    | 1.5                | 5                  | μV/°C              |

| I <sub>B</sub>    | Input Bias Current            |                                            |                    | 0.1                | 5<br><b>100</b>    | pA                 |

| e <sub>n</sub>    | Input-referred Noise Voltage  | f = 10 kHz, 1 V/V ≤ Gain ≤ 16 V/V          |                    | 12                 |                    | nV/√ <del>Hz</del> |

|                   |                               | f = 0.1 Hz to 10 Hz, 1 V/V ≤ Gain ≤ 16 V/V |                    | 3.8                |                    | $\mu V_{PP}$       |

| BW                | Bandwidth                     | C1 = C0 = 0, Gain = 1 V/V                  |                    | 33                 |                    |                    |

|                   |                               | C1 = C0 = 0, Gain = 2 V/V                  |                    | 15.5               |                    | MHz                |

|                   |                               | C1 = C0 = 1, Gain = 16 V/V                 |                    | 9.5                |                    |                    |

| SR                | Slew Rate                     | See <sup>(4)</sup>                         |                    | 12                 |                    | V/µs               |

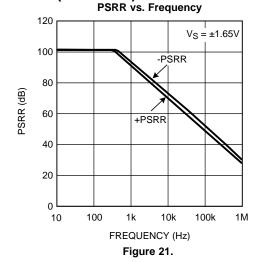

| PSRR              | Power Supply Rejection Ratio  | 2.7V < V <sup>+</sup> < 3.6V               | 90<br><b>80</b>    | 100                |                    | dB                 |

| Vo                | Output Swing<br>High          | +IN = 3.3V                                 | 3.2<br><b>3.15</b> | 3.25               |                    | V                  |

|                   | Output Swing<br>Low           | +IN = 0V                                   |                    | 50                 | 100<br><b>150</b>  | mV                 |

| Io                | Output Current                | Sourcing and Sinking                       | 15                 | 20                 |                    | mA                 |

| $V_{IN}$          | Input Voltage Range           |                                            | -0.2<br><b>0</b>   |                    | 3.5<br><b>3.3</b>  | V                  |

| I <sub>S</sub>    | Supply Current                |                                            |                    | 5.1                | 5.8<br><b>7.0</b>  | mA                 |

| I <sub>PD</sub>   | Supply Current, Power Down    |                                            |                    | 1.8                | 20<br><b>40</b>    | μΑ                 |

|                   | Feedback Resistance           |                                            |                    | 5.6                |                    | kΩ                 |

| R <sub>IN</sub>   | Input Impedance               |                                            |                    | >10                |                    | GΩ                 |

<sup>(3)</sup> The offset voltage average drift is determined by dividing the value of V<sub>OS</sub> at the temperature extremes by the total temperature change.

## **Electrical Characteristics (Serial Interface)**

Unless otherwise specified, all limits ensured for  $T_A = 25^{\circ}C$ ,  $V^+ - V^- \ge 2.7V$ ,  $V_D = V^+ - DGND \ge 2.5V$ .

| Symbol           | Parameter                             | Conditions                                                                                | Min <sup>(1)</sup>   | Typ <sup>(2)</sup> | Max <sup>(1)</sup>   | Units     |

|------------------|---------------------------------------|-------------------------------------------------------------------------------------------|----------------------|--------------------|----------------------|-----------|

| V <sub>IL</sub>  | Logic Low Threshold                   |                                                                                           |                      |                    | 0.3 × V <sub>D</sub> | V         |

| V <sub>IH</sub>  | Logic High Threshold                  |                                                                                           | 0.7 × V <sub>D</sub> |                    |                      | V         |

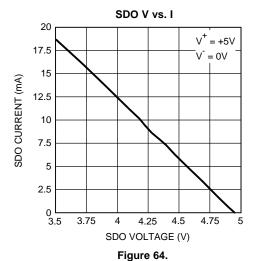

| I <sub>SDO</sub> | Output Source Current, SDO            | $\frac{V_D}{CS} = 3.3V \text{ or } 5.0V,$<br>$\frac{V_D}{CS} = 0V, V_{OH} = V^+ - 0.7V$   | -7                   |                    |                      | <b></b> ∧ |

|                  | Output Sink Current, SDO              | $\frac{V_D}{CS} = 3.3V \text{ or } 5.0V,$<br>$\frac{V_D}{CS} = 0V, V_{OL} = 1.0V$         | 10                   |                    |                      | mA        |

| l <sub>OZ</sub>  | Output Tri-state Leakage Current, SDO | $\frac{V_D}{CS} = 3.3V \text{ or } 5.0V,$<br>$\frac{V_D}{CS} = V_D = 3.3V \text{ or } 5V$ |                      |                    | ±1                   | μΑ        |

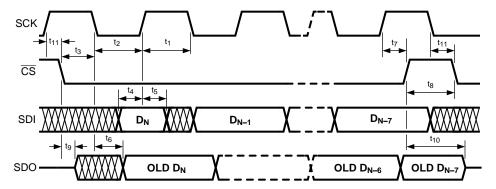

| t <sub>1</sub>   | High Period, SCK                      | See <sup>(3)</sup>                                                                        | 100                  |                    |                      | ns        |

| t <sub>2</sub>   | Low Period, SCK                       | See <sup>(3)</sup>                                                                        | 100                  |                    |                      | ns        |

| t <sub>3</sub>   | Set Up Time, CS to SCK                | See <sup>(3)</sup>                                                                        | 50                   |                    |                      | ns        |

| t <sub>4</sub>   | Set Up Time, SDI to SCK               | See <sup>(3)</sup>                                                                        | 30                   |                    |                      | ns        |

| t <sub>5</sub>   | Hold Time, SCK to SDI                 | See <sup>(3)</sup>                                                                        | 10                   |                    |                      | ns        |

| t <sub>6</sub>   | Prop. Delay, SCK to SDO               | See <sup>(3)</sup>                                                                        |                      |                    | 60                   | ns        |

<sup>(1)</sup> All limits are specified by testing or statistical analysis.

<sup>(4)</sup> Slew rate is the average of the rising and falling slew rates.

<sup>(2)</sup> Typical Values indicate the most likely parametric norm as determined at the time of characterization. Actual typical values may vary over time and will also depend on the application and configuration. The typical values are not tested and are not ensured on shipped production material.

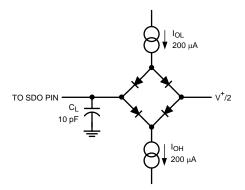

<sup>(3)</sup> Load for these tests is shown in the Timing Diagram Test Circuit.

# **Electrical Characteristics (Serial Interface) (continued)**

Unless otherwise specified, all limits ensured for  $T_A = 25^{\circ}C$ ,  $V^+ - V^- \ge 2.7V$ ,  $V_D = V^+ - DGND \ge 2.5V$ .

| Symbol                         | Parameter                                                        | Conditions         | Min <sup>(1)</sup> | Typ <sup>(2)</sup> | Max <sup>(1)</sup> | Units |

|--------------------------------|------------------------------------------------------------------|--------------------|--------------------|--------------------|--------------------|-------|

| t <sub>7</sub>                 | Hold Time, SCK Transition to $\overline{\text{CS}}$ Rising Edge  | See <sup>(3)</sup> | 50                 |                    |                    | ns    |

| t <sub>8</sub>                 | CS Inactive                                                      | See <sup>(3)</sup> | 50                 |                    |                    | ns    |

| t <sub>9</sub>                 | Prop. Delay, CS to SDO Active                                    | See <sup>(3)</sup> |                    |                    | 50                 | ns    |

| t <sub>10</sub>                | Prop. Delay, CS to SDO Inactive                                  | See <sup>(3)</sup> |                    |                    | 50                 | ns    |

| t <sub>11</sub>                | Hold Time, SCK Transition to $\overline{\text{CS}}$ Falling Edge | See <sup>(3)</sup> | 10                 |                    |                    | ns    |

| t <sub>R</sub> /t <sub>F</sub> | Signal Rise and Fall Times                                       | See <sup>(3)</sup> | 1.5                |                    | 5                  | ns    |

## **Connection Diagram**

Figure 1. 14-Pin SOIC (Top View)

# **Timing Diagram Test Circuit**

Submit Documentation Feedback

## **Timing Diagram**

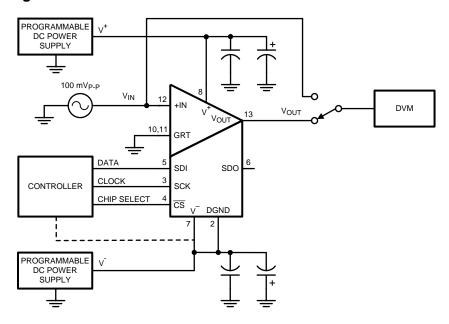

## **Test Circuit Diagram**

#### **GAIN ERROR TEST**

#### SMALL SIGNAL GAIN ERROR TEST

**Test Circuit**

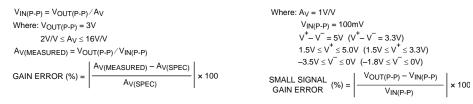

## **Typical Performance Characteristics**

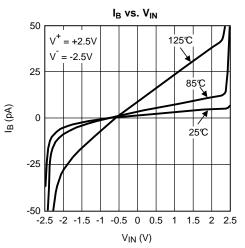

Figure 2.

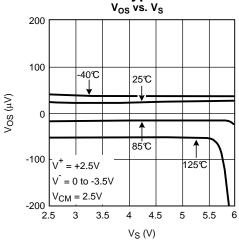

V<sub>OS</sub> vs. V<sub>IN</sub>

V<sub>IN</sub> (V) Figure 6.

Figure 3.

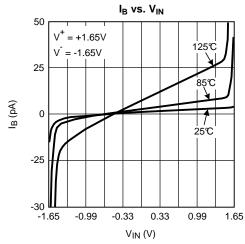

100 125°C 85°C 85°C -40°C V<sup>+</sup> = +1.65V

= -1.65V

-0.99

$V_{OS}$  vs.  $V_{IN}$

200

-200

-1.65

V<sub>IN</sub> (V) Figure 7.

0.66

0.99

1.65

-0.33

Submit Documentation Feedback

200

Figure 10.

Figure 12.

Figure 9.

Figure 11.

Figure 13.

Figure 14.

\_ . \_ ...\_.

Figure 18.

Figure 15.

Figure 17.

Figure 19.

Copyright © 2007–2013, Texas Instruments Incorporated

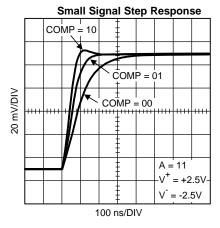

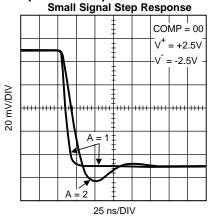

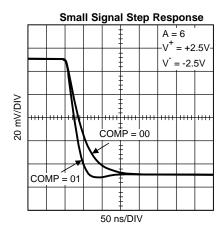

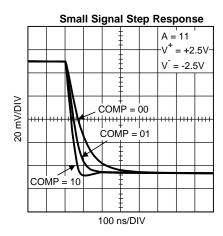

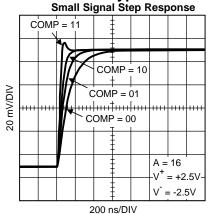

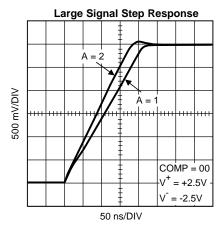

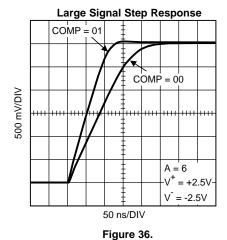

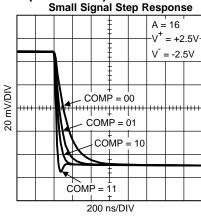

# Typical Performance Characteristics (continued) Small Signal Step Response Small Signal Step Response

Figure 26.

Figure 28.

Figure 30.

Figure 27.

Figure 29.

Figure 31.

# Typical Performance Characteristics (continued) Small Signal Step Response Small Signal Step Response

Figure 32.

Figure 34.

Figure 33.

Figure 35.

Figure 37.

Figure 38.

Figure 40.

Figure 39.

Figure 41.

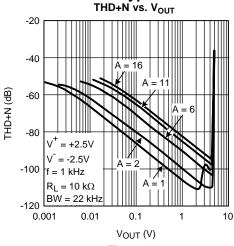

Figure 44.

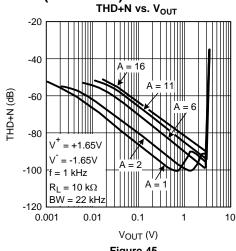

Figure 45.

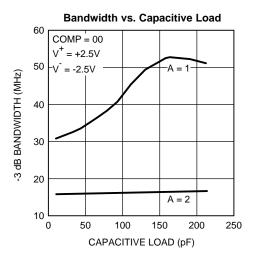

Figure 46.

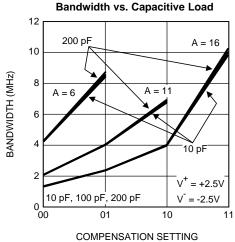

Figure 47.

Figure 49.

Figure 51.

Figure 52.

Figure 55.

Figure 54.

Submit Documentation Feedback

100k

FREQUENCY (Hz)

Figure 57.

## Noise vs. Frequency

Figure 61.

Figure 62.

Input Impedance

Figure 63.

Figure 65.

Submit Documentation Feedback

Copyright © 2007–2013, Texas Instruments Incorporated

#### APPLICATIONS INFORMATION

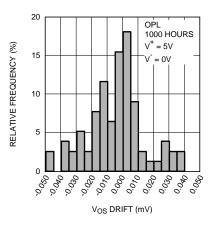

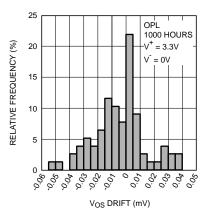

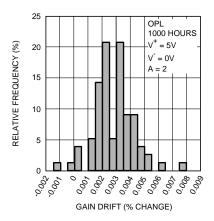

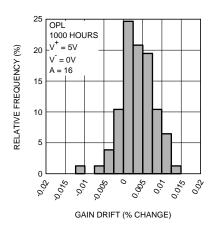

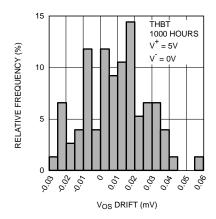

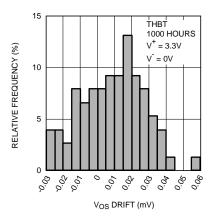

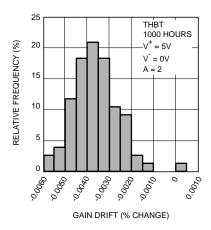

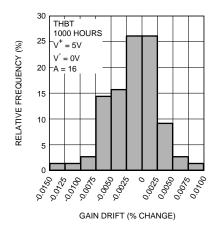

#### LIFETIME DRIFT

Offset voltage  $(V_{OS})$  and gain are electrical parameters which may drift over time. This drift, known as lifetime drift, is very common in operational amplifiers; however, its effect is more evident in precision amplifiers. This is due to the very low offset voltage specification and very precise gain specification of the LMP8100. The LMP8100 has an option to zero out the offset voltage. When the zero bit of the register is set high, +IN is connected to GRT. Output offset voltage can be measured and adjusted out of the signal path. See the "Input Zeroing" section, for more information. Numerous reliability tests have been performed to characterize this drift for the LMP8100. Prior to each long term reliability test the input offset voltage and gain at 2X and 16X of each LMP8100 was measured at room temperature.

The long term reliability tests include Operating Life Time (OPL) performed at 150°C for an extended period of time and Temperature Humidity Bias Testing (THBT) at 85°C and 85% humidity for an extended period of time. The offset voltage and gain of 2X and 16X were measured again at room temperature after each reliability test.

The offset voltage drift is the difference between the initial measurement and the later measurement, after the reliability test.

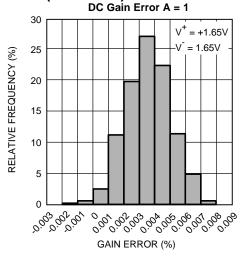

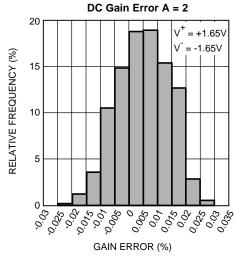

The gain drift is the percentage difference between the initial measurement and the later measurement, after the reliability test. Figure 66 – Figure 69 show the offset voltage drift and gain drift after 1000 hours of OPL.

Figure 70 - Figure 73 show the offset voltage drift and gain drift after 1000 hours of THBT.

Figure 66. OPL Vos Drift

Figure 67. OPL Vos Drift

Figure 68. OPL Gain Drift, A = 2

Figure 69. OPL Gain Drift, A = 16

Figure 70. THBT Vos Drift

Product Folder Links: LMP8100

20

Figure 71. THBT Vos Drift

Figure 72. THBT Gain Drift, A = 2

Figure 73. THBT Gain Drift, A = 16

#### **POWER-ON RESET**

Copyright © 2007-2013, Texas Instruments Incorporated

The LMP8100 has a power-up reset feature that sets all the register bits to 0 when the part is powered up. To implement this feature the  $\overline{\text{CS}}$  and SCK pins must be held at or above  $V_{\text{IH}}$  when the LMP8100 is powered-up. Failure to power up in this method can lead to an unpredictable state of the register bits after power-up.

Brodust Folder Links: //

#### **CONTROL REGISTER**

The control register retains the information which controls the amplifier gain, bandwidth compensation, input zeroing, and power down. The register is loaded by way of the serial control interface. The register is double buffered so that changes can be made with minimum effect on amplifier performance. Table 1 shows the organization of the control register. Table 2 gives the codes for gain setting, input zeroing and power down control. Table 3 shows the codes for the four gain-bandwidth compensation levels.

Table 1. Control Register Format<sup>(1)</sup>

| C1  | C0 | Zero | PD | G3 | G2 | G1 | G0  |

|-----|----|------|----|----|----|----|-----|

| MSB |    |      |    |    |    |    | LSB |

(1) C0, C1: Compensation setting

Zero: Zero Input PD: Power Down G0 to G3: Gain setting

Table 2. Input Zero, Power-Down and Gain Setting Codes

| Zero | PD | G3 | G2 | G1 | G0 | Non-Inverting Gain |

|------|----|----|----|----|----|--------------------|

|      | 0  | 0  | 0  | 0  | 0  | 1                  |

|      | 0  | 0  | 0  | 0  | 1  | 2                  |

|      | 0  | 0  | 0  | 1  | 0  | 3                  |

|      | 0  | 0  | 0  | 1  | 1  | 4                  |

|      | 0  | 0  | 1  | 0  | 0  | 5                  |

|      | 0  | 0  | 1  | 0  | 1  | 6                  |

|      | 0  | 0  | 1  | 1  | 0  | 7                  |

|      | 0  | 0  | 1  | 1  | 1  | 8                  |

|      | 0  | 1  | 0  | 0  | 0  | 9                  |

|      | 0  | 1  | 0  | 0  | 1  | 10                 |

|      | 0  | 1  | 0  | 1  | 0  | 11                 |

|      | 0  | 1  | 0  | 1  | 1  | 12                 |

|      | 0  | 1  | 1  | 0  | 0  | 13                 |

|      | 0  | 1  | 1  | 0  | 1  | 14                 |

|      | 0  | 1  | 1  | 1  | 0  | 15                 |

|      | 0  | 1  | 1  | 1  | 1  | 16                 |

| Х    | 1  | Х  | Х  | Х  | Х  | Power Down         |

| 1    | 0  | Х  | Х  | Х  | Х  | Zero Input         |

**Table 3. Amplifier Gain Compensation Codes**

| C1 | C0 | Compensation Level | Condition            |

|----|----|--------------------|----------------------|

| 0  | 0  | 0                  | Maximum Compensation |

| 0  | 1  | 1                  |                      |

| 1  | 0  | 2                  |                      |

| 1  | 1  | 3                  | Minimum Compensation |

## AMPLIFIER GAIN SETTING AND BANDWIDTH COMPENSATION CONTROL

The gain of the LMP8100 is set to one of 16 levels under program control by setting the appropriate bits G[3:0] of the control register with a number from 00h to 15h. This sets the gain to a level from 1 V/V to 16 V/V respectively.

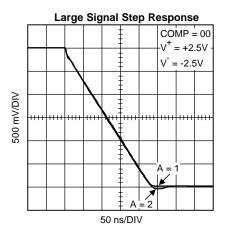

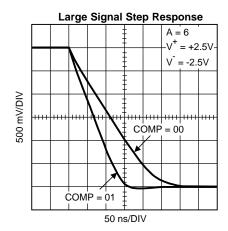

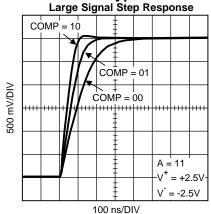

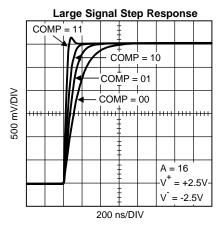

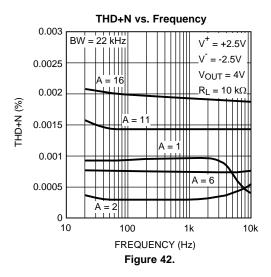

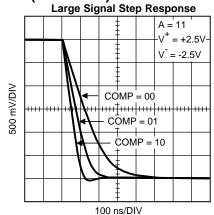

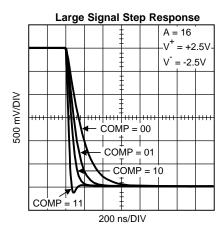

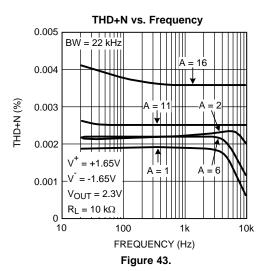

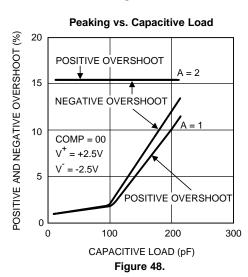

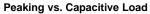

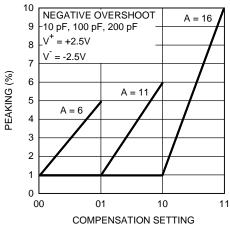

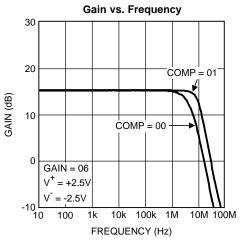

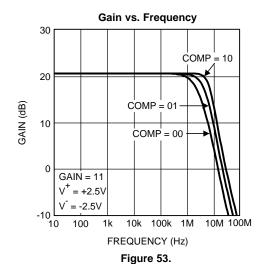

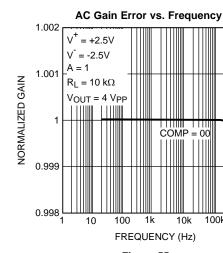

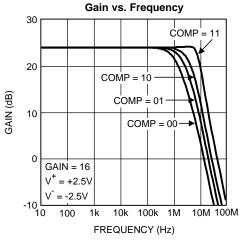

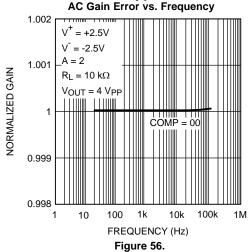

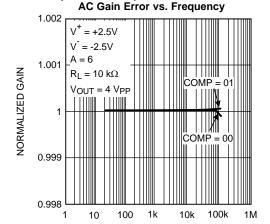

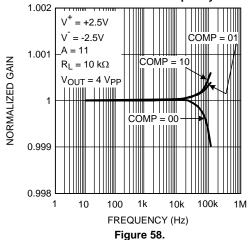

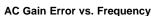

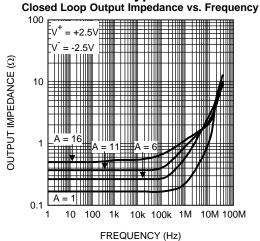

The gain-bandwidth compensation is also selectable to one of four levels under program control. The amount of compensation can be decreased to maximize the available bandwidth as the gain of the amplifier is increased. The compensation level is selected by setting bits C[1:0] of the control register with a number from 00b to 11b with 00b being maximum compensation and 11b being minimum compensation. Table 4 shows the bandwidths achieved at several gain and compensation settings. It will be noted that for gains between X1 and X5, the recommended compensation setting is 00b. For gain settings between X6 and X10, compensation settings may be 00b and 01b. Gain settings between X11 and X15 may use the three bandwidth compensation settings between 00b and 10b. At a gain of X16, all bandwidth compensation ranges may be used. Note that, for lower gains, it is possible to under-compensate the amplifier into instability.

|     | Table 4. Ampliner Cam and Compensation vs. Bandwidth |        |             |                      |  |  |  |  |  |  |  |

|-----|------------------------------------------------------|--------|-------------|----------------------|--|--|--|--|--|--|--|

|     | Gain                                                 | Compen | sation Bits | 3 dB Bandwidth (MHz) |  |  |  |  |  |  |  |

| V/V | dB                                                   | C1     | C0          |                      |  |  |  |  |  |  |  |

| 1   | 0                                                    | 0      | 0           | 33.0                 |  |  |  |  |  |  |  |

| 2   | 6.02                                                 | 0      | 0           | 15.5                 |  |  |  |  |  |  |  |

| 6   | 15.6                                                 | 0      | 0           | 4.2                  |  |  |  |  |  |  |  |

| 6   | 15.6                                                 | 0      | 1           | 8.3                  |  |  |  |  |  |  |  |

| 11  | 20.8                                                 | 0      | 0           | 2.0                  |  |  |  |  |  |  |  |

| 11  | 20.8                                                 | 0      | 1           | 3.9                  |  |  |  |  |  |  |  |

| 11  | 20.8                                                 | 1      | 0           | 6.6                  |  |  |  |  |  |  |  |

| 16  | 24.1                                                 | 0      | 0           | 1.3                  |  |  |  |  |  |  |  |

| 16  | 24.1                                                 | 0      | 1           | 2.3                  |  |  |  |  |  |  |  |

| 16  | 24.1                                                 | 1      | 0           | 3.8                  |  |  |  |  |  |  |  |

| 16  | 24.1                                                 | 1      | 1           | 9.5                  |  |  |  |  |  |  |  |

Table 4. Amplifier Gain and Compensation vs. Bandwidth

#### NON-INVERTING AMPLIFIER OPERATION

The principal application of the LMP8100 is as a non-inverting amplifier as shown in the simplified schematic, Figure 74. The amplifier supply voltage ( $V^+$  to  $V^-$ ) is specified as 5.5V maximum. The  $V^-$  supply pin is connected to the system ground for single supply operation.  $V^-$  can be returned to a negative voltage when required by the application. The digital supply voltage for the serial interface is applied between the  $V^+$  supply pin and DGND.

Figure 74. Basic Non-Inverting Amplifier

#### **GRT PINS**

The GRT pins must have a low impedance connection to either ground or a reference voltage. Any parasitical impedance on these pins will affect the gain accuracy of the LMP8100. Figure 75 shows a simplified schematic of the LMP8100 showing the internal gain resistors and an external parasitical resistance RP. The gain of the LMP8100 is determined by  $R_F$  and  $R_G$ , the values of which are set by the internal register. The gain of the amplifier is given by the equation

$$GAIN = 1 + \frac{R_F}{R_G}$$

(1)

Any resistance between the GRT pins and either ground or a reference voltage will change the gain to

$$GAIN = 1 + \frac{R_F}{R_G + R_P}$$

(2)

Figure 75. LMP8100 with External Parasitical Resistance

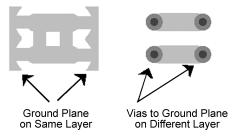

The connection between the GRT pins and ground or a reference voltage should be as short as possible using wide traces to minimize the parasitical resistance. Figure 76 shows two suggested methods of connecting the GRT pins to a ground plane on the same layer or to a ground plane on a different layer of the PCB.

Figure 76. GRT Connection Methods

The GRT pin can be connected to a reference voltage source to provide an offset adjustment to the gain function. Any DC resistance that may be present between the voltage source and the GRT pin must be kept to an absolute minimum to avoid introducing gain errors into the circuit.

#### **INPUT ZEROING**

Measurements made with the LMP8100 in the signal path may be adjusted for the output offset voltage of the amplifier. For example: The measurement of  $V_{OUT}$  for offset correction might be made using an ADC under microprocessor control. Output offset is measured under program control by setting the ZERO bit in the programming register. In this mode, +IN is disconnected from the input pin and internally connected to the GRT input. Figure 77 shows the LMP8100 in the input zeroing mode.

Figure 77. Non-Inverting Input Zeroing Function

### SERIAL CONTROL INTERFACE OPERATION

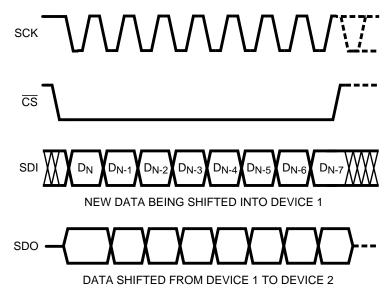

The LMP8100 gain, bandwidth compensation, power down, and input zeroing are controlled by data stored in a programming register. Data to be written into the control register is first loaded into the LMP8100 via the serial interface. The serial interface employs an 8-bit shift register. Data is loaded through the serial data input, SDI. Data passing through the shift register is output through the serial data output, SDO. The serial clock, SCK controls the serial loading process. All eight data bits are required to correctly program the amplifier. The falling edge of  $\overline{CS}$  enables the shift register to receive data. The SCK signal must be high during the falling and rising edge of  $\overline{CS}$ . Each data bit is clocked into the shift register on the rising edge of SCK. Data is transferred from the shift register to the holding register on the rising edge of  $\overline{CS}$ . Operation is shown in the timing diagram, Figure 78.

Figure 78. Serial Control Interface Timing

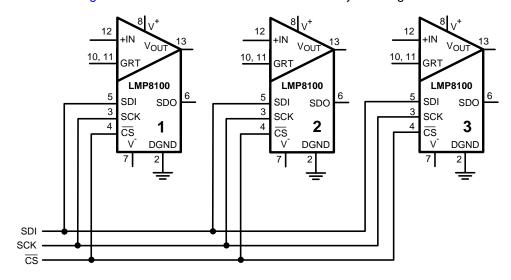

The serial control pins can be connected in one of two ways when two or more LMP8100s are used in an application.

## **Star Configuration**

This configuration can be used if each LMP8100 will always have the same value in each register. The connections are shown in Figure 79. After the microcontroller writes a byte all registers will have the same value.

Figure 79. Star Configuration

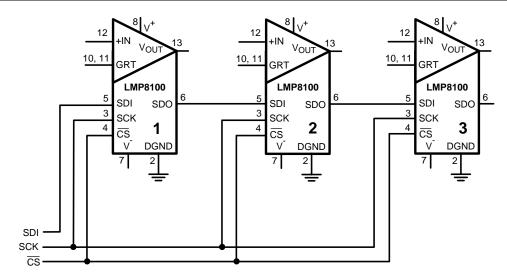

## **Daisy Chain Configuration**

This configuration can be used to program the same or different values in the register of each LMP8100. The connections are shown in Figure 80. In this configuration the SDO pin of each LMP8100 is connected to the SDI pin of the following LMP8100. The following two examples show how the registers are written.

If all three LMP8100s need a gain of 11 with a compensation level of 10. (10001010)

www.ti.com

|                 | Register of LMP8100 #1 | Register of LMP8100 #2 | Register of LMP8100 #3 | Notes                                                                                                               |

|-----------------|------------------------|------------------------|------------------------|---------------------------------------------------------------------------------------------------------------------|

| Power on        | 00000000               | 00000000               | 00000000               | Default power on state (see above)                                                                                  |

| Byte one sent   | 10001010               | 00000000               | 00000000               | The data in the register of LMP8100 #1 is shifted                                                                   |

| Byte two sent   | 10001010               | 10001010               | 00000000               | into the register of LMP8100 #2, the data in the register of LMP8100 #2 is shifted into the register of LMP8100 #3. |

| Byte three sent | 10001010               | 10001010               | 10001010               |                                                                                                                     |

If LMP8100 #1 needs a gain of 11 with a compensation level of 10 (10001010), LMP8100 #2 needs a gain of 6 with a compensation of 00 (00000101), and LMP8100 #3 needs a gain of 2 with a compensation of 00 (00000001).

|                 | Register of LMP8100 #1 | Register of LMP8100 #2 | Register of LMP8100 #3 | Notes                                                                                                                                                                 |

|-----------------|------------------------|------------------------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power on        | 00000000               | 00000000               | 00000000               | Default power on state (see above)                                                                                                                                    |

| Byte one sent   | 0000001                | 00000000               | 00000000               | The data in the register of LMP8100 #1 is shifted into the register of LMP8100 #2, the data in the register of LMP8100 #2 is shifted into the register of LMP8100 #3. |

| Byte two sent   | 00000101               | 0000001                | 00000000               |                                                                                                                                                                       |

| Byte three sent | 10001010               | 00000101               | 0000001                |                                                                                                                                                                       |

Figure 80. Daisy Chain Configuration

### POWER SUPPLY PURITY AND BYPASSING

Particular attention to power supply purity is needed in order to preserve the LMP8100's gain accuracy and low noise. The LMP8100 worst-case PSRR is 85 dB or 56.2  $\mu$ V/V. Nevertheless, the usable dynamic range, gain accuracy and inherent low noise of the amplifier can be compromised through the introduction and amplification of power supply noise.

To decouple the LMP8100 from supply line AC noise, a 0.1  $\mu$ F capacitor should be located on each supply line, close to the LMP8100. Adding a 10  $\mu$ F capacitor in parallel with the 0.1  $\mu$ F capacitor will reduce the noise introduced to the LMP8100 even more by providing an AC path to ground for most frequency ranges.

A power supply dropout ( $V^+$  - $V^-$  < 2.7V) can cause an unintended reset of the register. If a dropout occurs, the register will need to be reprogrammed with the correct values.

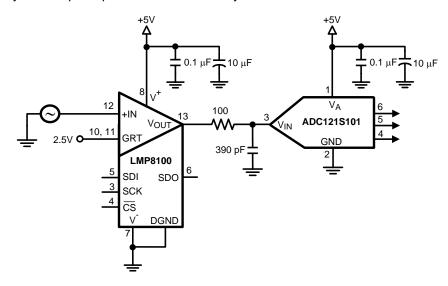

#### SCALING AMPLIFIER

The LMP8100 is ideally suited for use as an amplifier between a sensor that has a wide output range and an ADC. As the signal from the sensor changes the gain of the LMP8100 can be changed so that the entire input range of the ADC is being used at all times. Figure 81 shows a data acquisition system using the LMP8100 and the ADC121S101. The 100 $\Omega$  resistor and 390 pF capacitor form an antialiasing filter for the ADC121S101. The capacitor also stores and delivers charge to the switched capacitor input of the ADC. The capacitive load on the LMP8100 created by the 390pF capacitor is decreased by the 100 $\Omega$  resistor.

Figure 81. Data Acquisition System Using the LMP8100

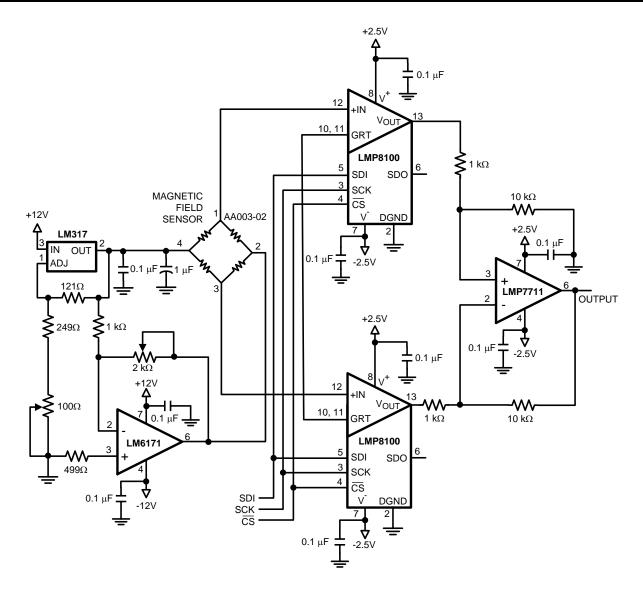

#### **BRIDGE AMPLIFIER**

In Figure 82 two LMP8100s are used with a LMP7711 to build an amplifier for the signal from a GMR Magnetic Field Sensor. The advantage of using the LMP8100 is that as the signal strength from the Magnetic Field Sensor decreases, the gain of the LMP8100 can be increased. An example is if the signal from this composite amplifier is used to drive an ADC. When the maximum magnetic field to be measured is applied, the gain of the LMP7711 can be set to supply a full range signal to the ADC input with the gain of the LMP8100 set to one. As the magnetic field decreases, the gain of the LMP8100 can be increased, so that the signal supplied to the ADC uses a maximum amount of the ADC input range.

The following can be done to maximize performance:

- Connect the GRT pins directly together and to GND with a low impedance trace.

- Make the traces between the Magnetic Field Sensor and the LMP8100s short to minimize noise pickup.

- Place 0.1 µF capacitors close to each of the LMP8100 supply pins.

The following can be done to simplify the design:

- Connect the SCL, SCK, and CS lines in parallel and one microcontroller can be used to drive both LMP8100s.

- The SDO pin can be left floating.

The LM317 and LM6171 are used for the supply of the Magnetic Sensor. The  $100\Omega$  potentiometer is used to adjust the supply voltage to the Magnetic Field Sensor. The  $2~k\Omega$  potentiometer is used to fine tune the negative supply to set the Magnetic Field Sensor output to zero.

Figure 82. Bridge Amplifier

## SNOSAO1C -JULY 2007-REVISED MARCH 2013

## **REVISION HISTORY**

| Cł | Changes from Revision B (March 2013) to Revision C |  |    |  |  |

|----|----------------------------------------------------|--|----|--|--|

| •  | Changed layout of National Data Sheet to TI format |  | 29 |  |  |

#### IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

Products Applications

Audio www.ti.com/audio Automotive and Transportation www.ti.com/automotive Communications and Telecom **Amplifiers** amplifier.ti.com www.ti.com/communications **Data Converters** dataconverter.ti.com Computers and Peripherals www.ti.com/computers **DLP® Products** www.dlp.com Consumer Electronics www.ti.com/consumer-apps

DSP **Energy and Lighting** dsp.ti.com www.ti.com/energy Clocks and Timers www.ti.com/clocks Industrial www.ti.com/industrial Interface interface.ti.com Medical www.ti.com/medical logic.ti.com Logic Security www.ti.com/security

Power Mgmt power.ti.com Space, Avionics and Defense www.ti.com/space-avionics-defense

Microcontrollers <u>microcontroller.ti.com</u> Video and Imaging <u>www.ti.com/video</u>

RFID <u>www.ti-rfid.com</u>

OMAP Applications Processors <a href="www.ti.com/omap">www.ti.com/omap</a> TI E2E Community <a href="e2e.ti.com">e2e.ti.com</a>

Wireless Connectivity <u>www.ti.com/wirelessconnectivity</u>