# **Ultra-Fast Voltage Comparators**

#### DISTINCTIVE CHARACTERISTICS

- 2.7 ns typical propagation delay

- Complementary ECL outputs

- 50-Ω driving capability

- **Built-in latch**

#### **GENERAL DESCRIPTION**

The Am6687 is an ultra-fast dual voltage comparator constructed on a single silicon chip with the advanced IMOX\* process. It is pin-for-pin compatible with the Am687, and has improved speed performance. The circuit features very short propagation delays as well as excellent matching characteristics. Each comparator has differential analog inputs and complementary logic outputs compatible with most forms of ECL. The output drive current is capable of driving terminated 50-ohm transmission lines. The low-input offsets and short delays make these comparators especially suitable for high-speed precision analog-to-digital processing.

Separate latch functions are provided to allow each comparator to be independently used in a sample-hold mode. The Latch Enable inputs are intended to be driven from the complementary outputs of a standard ECL gate. If LE is HIGH and LE is LOW, the comparator functions normally. When LE is driven LOW and LE is driven HIGH, the comparator outputs are locked in their existing logical states. If the latch function is not used, the LE must be connected to ground.

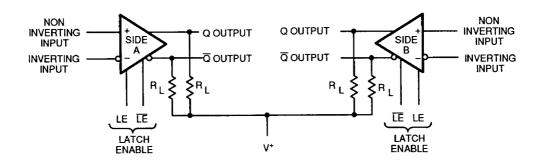

#### **BLOCK DIAGRAM**

The outputs are open emitters, therefore external pull-down resistors are required. These resistors may be in the range of 50–200  $\Omega$  connected to –2.0 V, or 200–2000  $\Omega$ connected to -5.2 V.

05679-001B

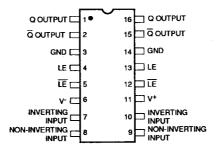

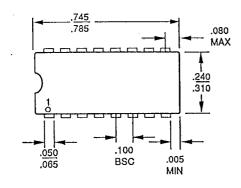

# CONNECTION DIAGRAM Top View

DIP

05679-002

Note: Pin 1 is marked for orientation.

Am6687

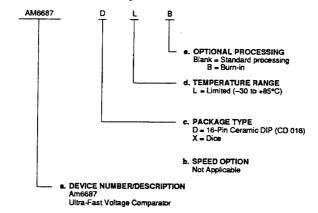

#### ORDERING INFORMATION

#### Standard Products

AMD standard products are available in several packages and operating ranges. The order number (Valid Combination) is formed by a combination of: a. Device Number

- b. Speed Option (if applicable)

- c. Package Type

- d. Temperature Range

- e. Optional Processing

#### Valid Combinations

| Valid Con  | nbinations         |  |

|------------|--------------------|--|

| <br>AM6687 | DL, DLB,<br>XL, XM |  |

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations, to check on newly released combinations, and to obtain additional data on AMD's standard military grade products.

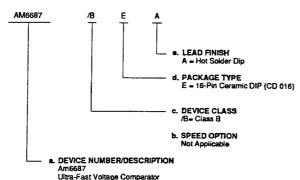

#### MILITARY ORDERING INFORMATION

#### **APL Products**

AMD products for Aerospace and Defense applications are available in several packages and operating ranges. APL (Approved Products List) products are fully compliant with MIL-STD-883C requirements. The order number (Valid Combination) for APL

- products is formed by a combination of: a. Device Number

- b. Speed Option (if applicable)

- c. Device Class d. Package Type

- a. Package Type.

b. Lead Finish

#### Valid Combinations

| Valid Con | Valid Combinations |  |  |  |

|-----------|--------------------|--|--|--|

| AM6687    | /BEA               |  |  |  |

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations or to check on newly released valid combinations.

#### Group A Tests

Group A tests consist of subgroups 1, 2, 3,

## **ABSOLUTE MAXIMUM RATINGS**

| Storage Temperature                  | 65 to +150°C |

|--------------------------------------|--------------|

| Positive Supply Voltage              |              |

| Negative Supply Voltage              |              |

| Input Voltage                        |              |

| Differential Input Voltage           | ±6 V         |

| Output Current                       | 30 mA        |

| Power Dissipation (Note 1)           | 500 mW       |

| Lead Temperature (soldering, 60 s)   | 300°C        |

| Minimum Operating Voltage (V+ to V-) | 9.7 V        |

Stresses above those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to absolute maximum ratings for extended periods may affect device reliability.

#### **OPERATING RANGES**

| Limited (L) Devices Ambient Temperature (T <sub>A</sub> )  | 30 to +85°C  |

|------------------------------------------------------------|--------------|

| Military (M) Devices Ambient Temperature (T <sub>a</sub> ) | 55 to +125°C |

Operating ranges define those limits between which the functionality of the device is guaranteed.

**DC CHARACTERISTICS** over operating range unless otherwise specified (for APL Products, Group A, Subgroups 1, 2, 3, 4, 5, 6 are tested unless otherwise noted)

| D                    | Parameter<br>Description                   | Test Conditions (Note 2)                        | LIMITED |        |        |       |        |        |       |

|----------------------|--------------------------------------------|-------------------------------------------------|---------|--------|--------|-------|--------|--------|-------|

| Parameter<br>Symbol  |                                            |                                                 | Min.    | Тур.   | Max.   | Min.  | Тур.   | Max.   | Unit  |

| V <sub>os</sub>      | Input Offset Voltage                       | RS ≤ 100 Ω, T <sub>A</sub> = 25°C               | -2      | 0.3    | +2     | -2    | 0.3    | +2     | mV    |

|                      |                                            | RS ≤ 100 Ω                                      | -2.5    |        | +2.5   | -3    |        | +3     | mv    |

| ΔV <sub>os</sub> /ΔT | Average Tempco of V <sub>os</sub> (Note 3) | RS ≤ 100 Ω                                      | -15     | +3     | +15    | -15   | +3     | +15    | μV/°C |

| los                  | Input Offset Current                       | 25°C ≤ T <sub>A</sub> ≤ T <sub>A</sub> (Max.)   | -1.5    | 0.2    | +1.5   | -1.5  | 0.2    | +1.5   | μА    |

|                      |                                            | T <sub>A</sub> = T <sub>A</sub> (Min.)          | -2.5    | 0.3    | +2.5   | -3.0  | 0.3    | +3.0   |       |

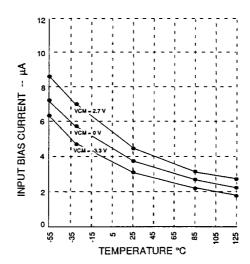

| I <sub>B</sub>       | Input Bias Current                         | 25°C ≤ T <sub>A</sub> ≤ T <sub>A</sub> (Max.)   |         | 4      | 15     |       | 4      | 15     | μА    |

|                      |                                            | T <sub>A</sub> = T <sub>A</sub> (Min.)          |         | 7      | 25     |       | 8      | 30     |       |

| V <sub>IN</sub>      | Input Voltage Range                        |                                                 | -3.3    |        | +2.7   | -3.3  |        | +2.7   | ٧     |

| CMRR                 | Common Mode Rejection<br>Ratio             | RS ≤ 100 Ω,<br>-3.3 V ≤ V <sub>cM</sub> ≤ 2.7 V | 80      |        |        | 80    |        |        | dB    |

| SVRR                 | Supply Voltage Rejection<br>Ratio          | RS $\leq$ 100 $\Omega$ , $V_s = \pm 5\%$        | 60      |        |        | 60    |        |        | dB    |

| V <sub>oH</sub>      | Output HIGH Voltage                        | T <sub>A</sub> = 25°C                           | -0.96   | -0.885 | -0.81  | -0.96 | -0.885 | -0.81  |       |

|                      |                                            | T_ = T_ (Min.)                                  | -1.06   | -0.975 | -0.89  | -1.1  | -1.010 | -0.92  | v     |

|                      |                                            | $T_A = T_A (Max.)$                              | -0.89   | -0.795 | -0.70  | -0.85 | -0.735 | 0.62   |       |

| V <sub>oL</sub>      | Output LOW Voltage                         | T <sub>A</sub> = 25°C                           | -1.85   | -1.750 | -1.65  | -1.85 | -1.750 | -1.65  |       |

|                      |                                            | T <sub>A</sub> = T <sub>A</sub> (Min.)          | -1.89   | -1.783 | -1.675 | -1.91 | -1.800 | -1.69  | v     |

|                      |                                            | $T_A = T_A (Max.)$                              | -1.825  | -1.725 | -1:625 | -1.81 | -1.693 | -1.575 |       |

Table continued on next page

#### DC CHARACTERISTICS (Cont'd.)

| Devenue             | Parameter<br>Description | Test<br>Conditions (Note 2) | LIMITED |      |      | MIL  |      |      |      |

|---------------------|--------------------------|-----------------------------|---------|------|------|------|------|------|------|

| Parameter<br>Symbol |                          |                             | Min.    | Тур. | Max. | Min. | Тур. | Max. | Unit |

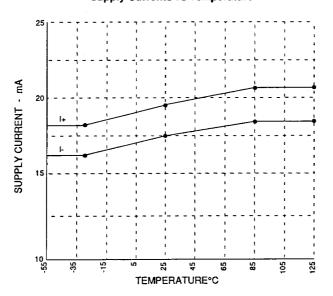

| l+                  | Positive Supply Current  |                             |         | 20   | 32   |      | 20   | 32   | mA   |

| <b> -</b>           | Negative Supply Current  |                             |         | 18   | 30   |      | 18   | 30   | mA   |

| P <sub>DISS</sub>   | Power Dissipation        |                             |         | 250  | 373  |      | 250  | 373  | mW   |

Notes: See notes following Switching Characteristics.

#### **DEFINITION OF TERMS**

V<sub>os</sub> Input Offset Voltage

That voltage which must be applied between the two input terminals through two equal resistances to obtain zero voltage between the two outputs.

#### ∆V<sub>os</sub>/∆T Average Temperature Coefficient of Input Offset Voltage

The ratio of the change in input offset voltage over the operating temperature range to the temperature range.

## I<sub>os</sub> Input Offset Current

The difference between the currents into the two input terminals when there is zero voltage between the two outputs.

#### I, input Bias Current

The average of the two input currents.

## R<sub>IN</sub> Input Resistance

The resistance looking into either input terminal with the other grounded.

## C<sub>IN</sub> Input Capacitance

The capacitance looking into either input terminal with the other grounded.

V<sub>cm</sub> Input Voltage Range

The range of voltages on the input terminals for which the offset and propagation delay specifications apply.

#### CMRR Common Mode Rejection Ratio

The ratio of the input voltage range to the peak-to-peak change in input offset voltage over this range.

#### SVRR Supply Voltage Rejection Ratio

The ratio of the change in input offset voltage to the change in power supply voltages producing it.

# V<sub>on</sub> Output HIGH Voltage

The logic-HIGH output voltage with an external pull-down resistor returned to a negative supply.

# V<sub>oL</sub> Output LOW Voltage

The logic-LOW output voltage with an external pull-down resistor returned to a negative supply.

#### I+ Positive Supply Current

The current required from the positive supply to operate the comparator.

#### I- Negative Supply Current

The current required from the negative supply to operate the comparator.

P<sub>biss</sub> Power Dissipation

The power dissipated by the comparator with both outputs terminated in 50  $\Omega$  to -2.0 V.

2-7 Am6687

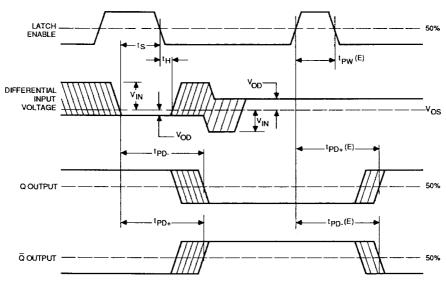

**SWITCHING CHARACTERISTICS** over operating range unless otherwise specified (for APL Products, Group A, Subgroup 9 is tested unless otherwise noted)  $(V_{IN} = 100 \text{ mV}, V_{OVERDRIVE} = 10 \text{ mV})$

| Parameter<br>Symbol                           | Parameter<br>Description                | Test<br>Conditions (Note 2)    | LIMITED |      |      |      |      |      |      |

|-----------------------------------------------|-----------------------------------------|--------------------------------|---------|------|------|------|------|------|------|

|                                               |                                         |                                | Min.    | Тур. | Max. | Min. | Тур. | Max. | Unit |

| t <sub>PD+</sub> , t <sub>PD-</sub>           | Propagation Delay                       | T <sub>A</sub> = 25°C (Note 3) | 2.0     | 2.7  | 4.0  | 2.0  | 2.7  | 4.0  | ns   |

| t <sub>PD+</sub> (E),<br>t <sub>PD-</sub> (E) | Latch Enable to Output<br>(HIGH or LOW) | T <sub>A</sub> = 25°C (Note 4) |         | 2.3  |      |      | 2.3  |      | ns   |

| t <sub>s</sub>                                | Min. Latch Setup Time                   | T <sub>A</sub> = 25°C (Note 4) |         | 1.0  |      |      | 1.0  |      | ns   |

| t <sub>H</sub>                                | Min. Latch Hold Time                    | T <sub>A</sub> = 25°C (Note 4) |         | -0.5 |      |      | -0.5 |      | ns   |

Notes: 1. Derate at 9 mW/°C for operation at ambient temperature above +115°C.

- 2. Unless otherwise specified V<sub>+</sub> = 5.0 V, V<sub>-</sub> = -5.2 V, V<sub>τ</sub> = 2.0 V, and R<sub>t</sub> = 50 Ω, all switching characteristics are for a 100-mV input step with 10 mV overdrive. The specification given for V<sub>os</sub>, I<sub>os</sub>, I<sub>os</sub>, SVRR, I<sub>po</sub>, and I<sub>po</sub>, apply for ±5% supply voltages. The Am6687 is designed to meet the specifications given in the table after thermal equilibrium has been established with a transverse air flow of 500 linear feet per minute or greater.

- 3. Not 100% tested. Group A sample only.

- 4. Not tested in production. These tests are supported by device characterization data.

#### **DEFINITION OF TERMS**

(refer to Switching Waveforms)

#### t<sub>pp</sub> Input to Output HIGH Delay

The propagation delay measured from the time the input signal crosses the input offset voltage to the 50% point of an output LOW-to-HIGH transition.

#### tpn\_ input to Output LOW Delay

The propagation delay measured from the time the input signal crosses the input offset voltage to the 50% point of an output HIGH-to-LOW transition.

#### t<sub>pn</sub>(E) Latch Enable to Output HIGH Delay

The propagation delay measured from the 50% point of the Latch Enable signal LOW-to-HIGH transition to the 50% point of an output LOW-to-HIGH transition.

#### t<sub>pp</sub>(E) Latch Enable to Output LOW Delay

The propagation delay measured from the 50% point of the Latch Enable signal LOW-to-HIGH transition to the 50% point of an output HIGH-to-LOW transition.

#### t, Minimum Setup Time

The minimum time before the negative transition of the Latch Enable signal that an input signal change must be present in order to be acquired and held at the outputs.

#### t., Minimum Hold Time

The minimum time after the negative transition of the Latch Enable signal that the input signal must remain unchanged in order to be acquired and held at the outputs.

#### Other Symbols

T<sub>A</sub> = Ambient temperature

R<sub>s</sub> = Input source resistance

V<sub>s</sub> = Supply voltages

V+ = Positive supply voltage

V- = Negative supply voltage

V<sub>r</sub> = Output load terminating voltage

R = Output load resistance

V<sub>IN</sub> = Input pulse amplitude

V<sub>op</sub> = Input overdrive

f = Frequency

2-8 Am6687

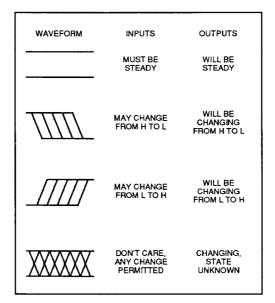

# SWITCHING WAVEFORMS KEY TO SWITCHING WAVEFORMS

KS000010

05679-003

The setup and hold times are a measure of the time required for an input signal to propagate through the first stage of the comparator to reach the latching circuitry. Input signal changes occurring before  $t_s$  will be detected and held; those occurring after  $t_\mu$  will not be detected. Changes between  $t_s$  and  $t_\mu$  may or may not be detected.

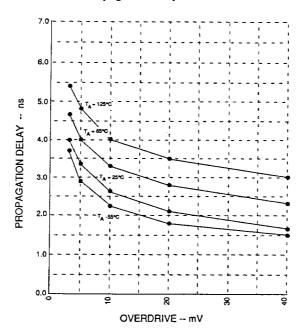

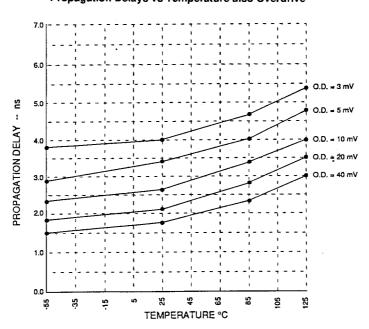

## **TYPICAL PERFORMANCE CURVES**

## **Propagation Delay vs Overdrive**

05975-005

## Propagation Delays vs Temperature also Overdrive

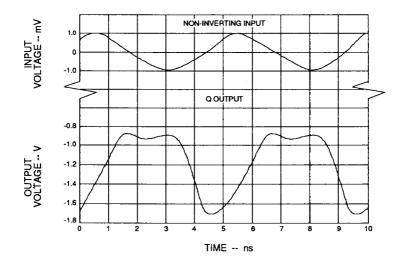

## Response to 200-MHz Sine Wave

05975-009

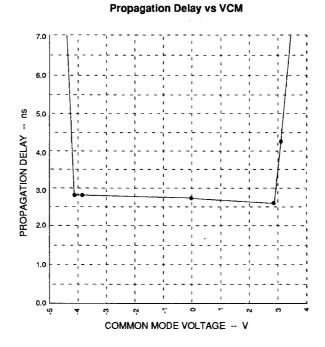

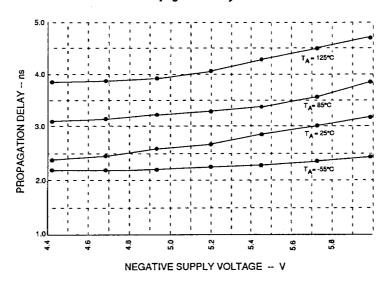

# Propagation Delay vs V-

05975-010

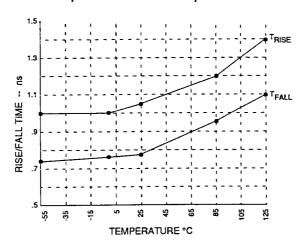

# **Output Rise and Fall vs Temperature**

05975-011

2-12 Am6687

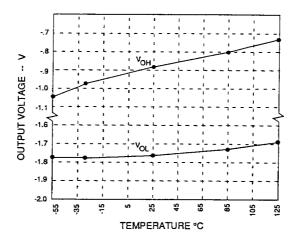

## **Output Voltage vs Temperature**

05975-012

# Input Bias Current vs Temperature

## **Supply Currents vs Temperature**

05679-004

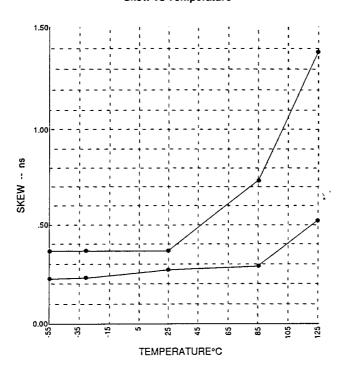

## **Skew vs Temperature**

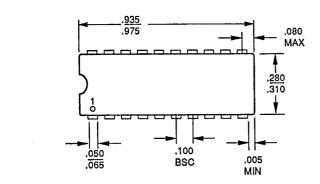

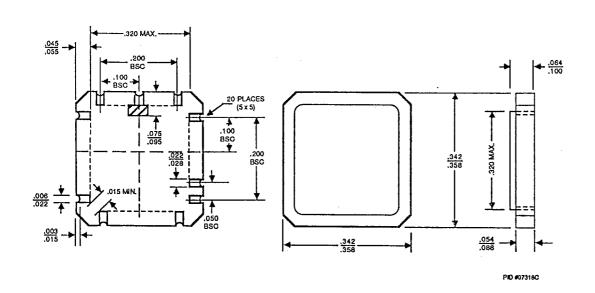

# PHYSICAL DIMENSIONS CD 016

07319B

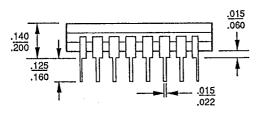

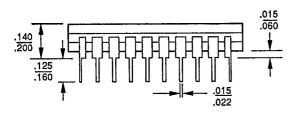

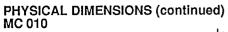

# CD 020

03941-004C

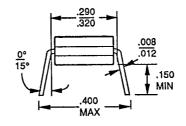

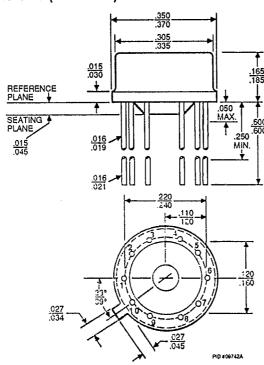

# PHYSICAL DIMENSIONS (continued) CD 024

03067-008A

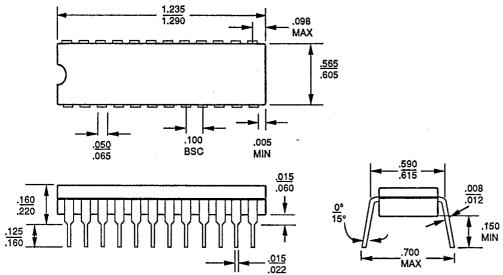

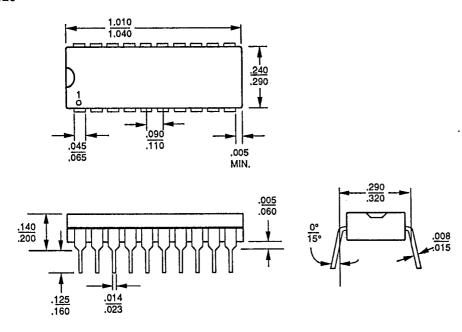

**CL 020**

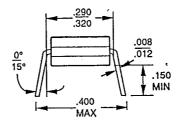

# PD 020

03941-005C