# Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: <a href="http://www.renesas.com">http://www.renesas.com</a>

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (<a href="http://www.renesas.com">http://www.renesas.com</a>)

Send any inquiries to http://www.renesas.com/inquiry.

#### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights

of third parties by or arising from the use of Renesas Electronics products or technical information described in this document.

No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights

of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics product for any application for which it is not intended without the prior written consent of Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anti-crime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majority-owned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

# Regarding the change of names mentioned in the document, such as Mitsubishi Electric and Mitsubishi XX, to Renesas Technology Corp.

The semiconductor operations of Hitachi and Mitsubishi Electric were transferred to Renesas Technology Corporation on April 1st 2003. These operations include microcomputer, logic, analog and discrete devices, and memory chips other than DRAMs (flash memory, SRAMs etc.) Accordingly, although Mitsubishi Electric, Mitsubishi Electric Corporation, Mitsubishi Semiconductors, and other Mitsubishi brand names are mentioned in the document, these names have in fact all been changed to Renesas Technology Corp. Thank you for your understanding. Except for our corporate trademark, logo and corporate statement, no changes whatsoever have been made to the contents of the document, and these changes do not constitute any alteration to the contents of the document itself.

Note: Mitsubishi Electric will continue the business operations of high frequency & optical devices and power devices.

Renesas Technology Corp. Customer Support Dept. April 1, 2003

# MITSUBISHI MICROCOMPUTERS M35072-XXXFP

SCREEN CHARACTER and PATTERN DISPLAY CONTROLLERS

#### **DESCRIPTION**

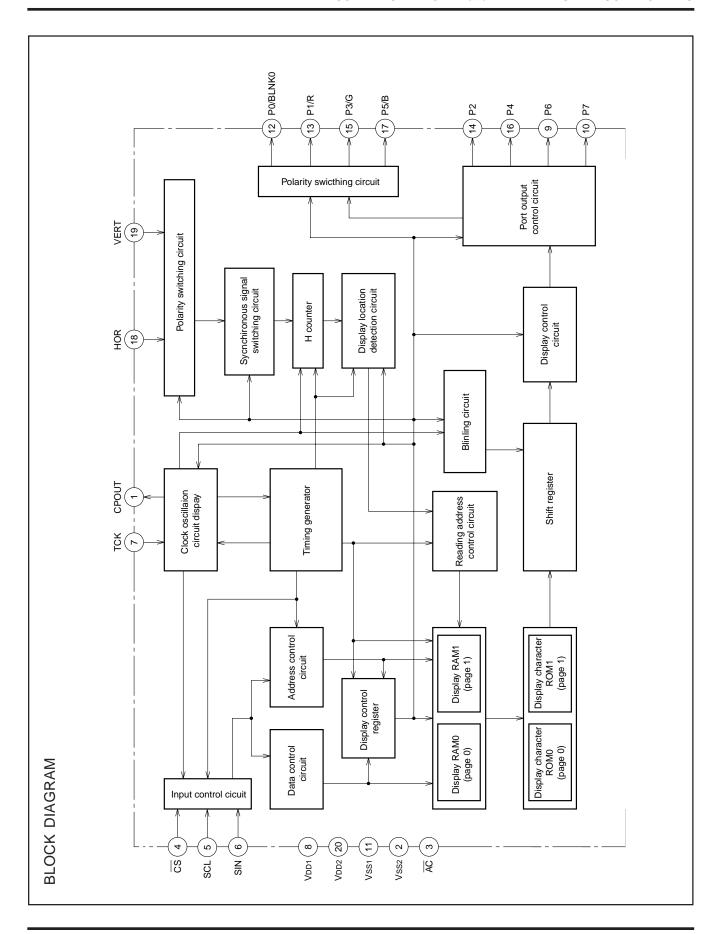

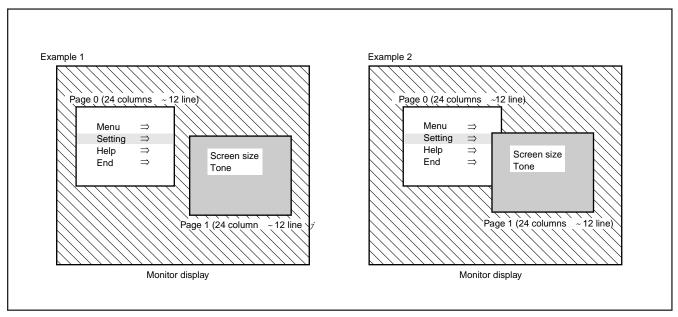

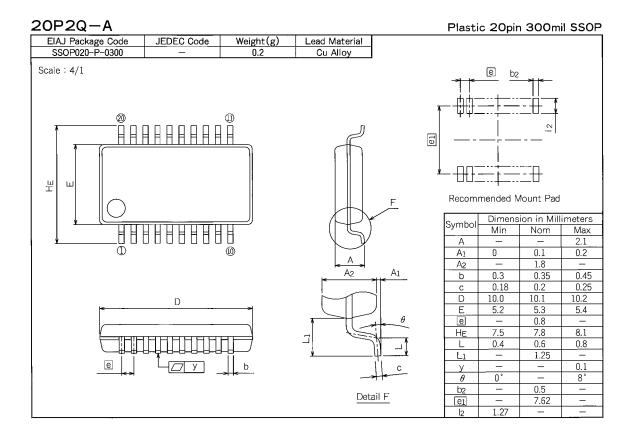

The M35072-XXXFP is a character pattern display control IC can display on the display monitor. It can display 2 pages (24 characters  $\times$  12 lines per 1 page) at the same time. It uses a silicon gate CMOS process and it housed in a 20-pin shrink SOP package .

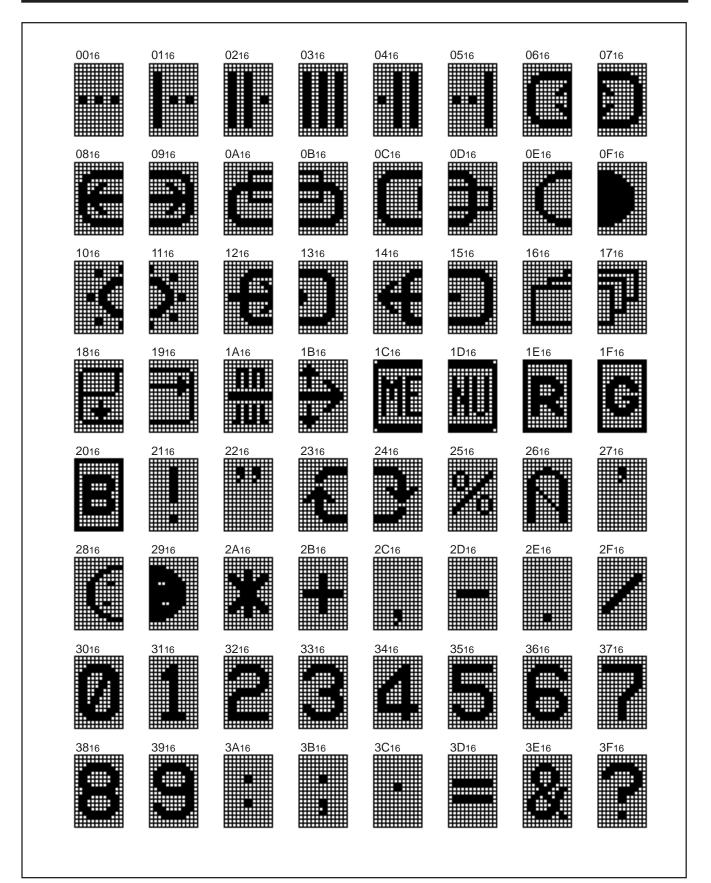

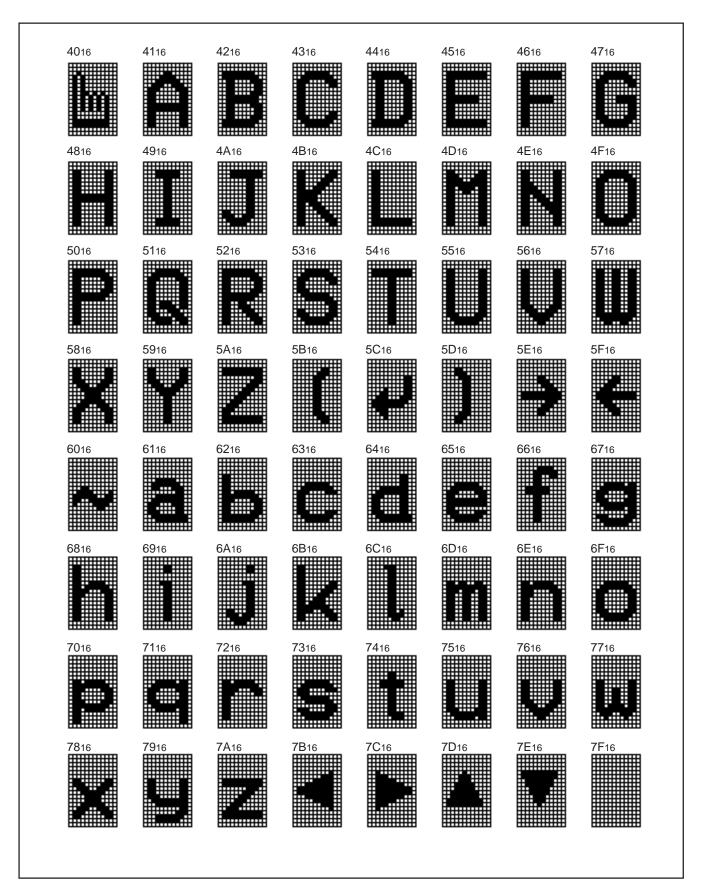

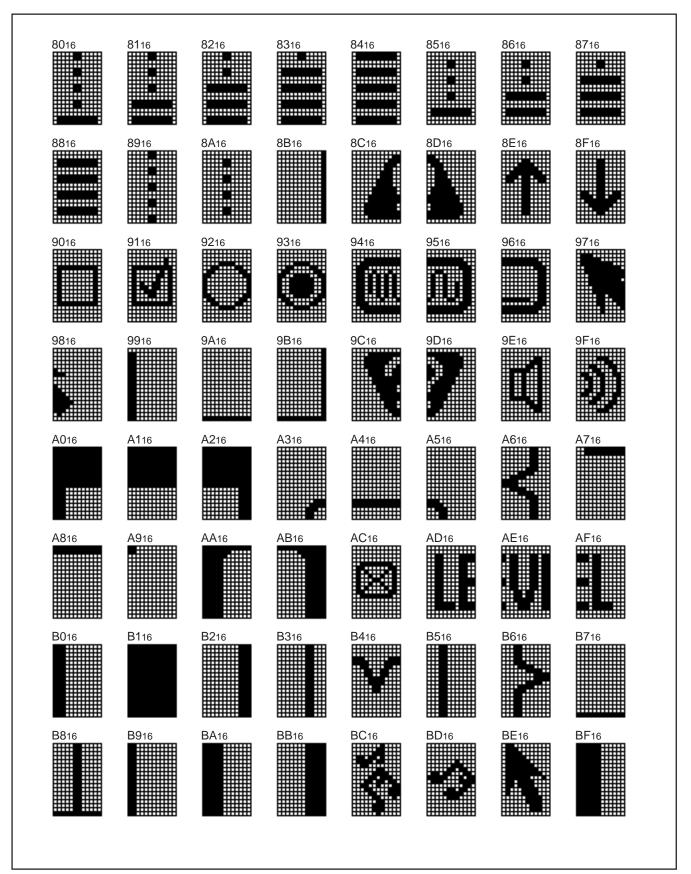

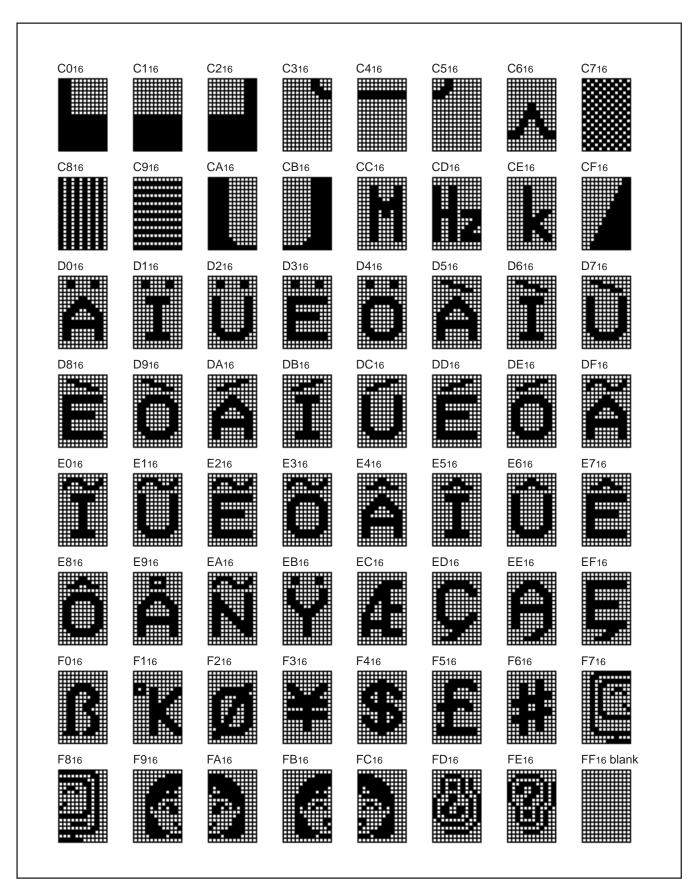

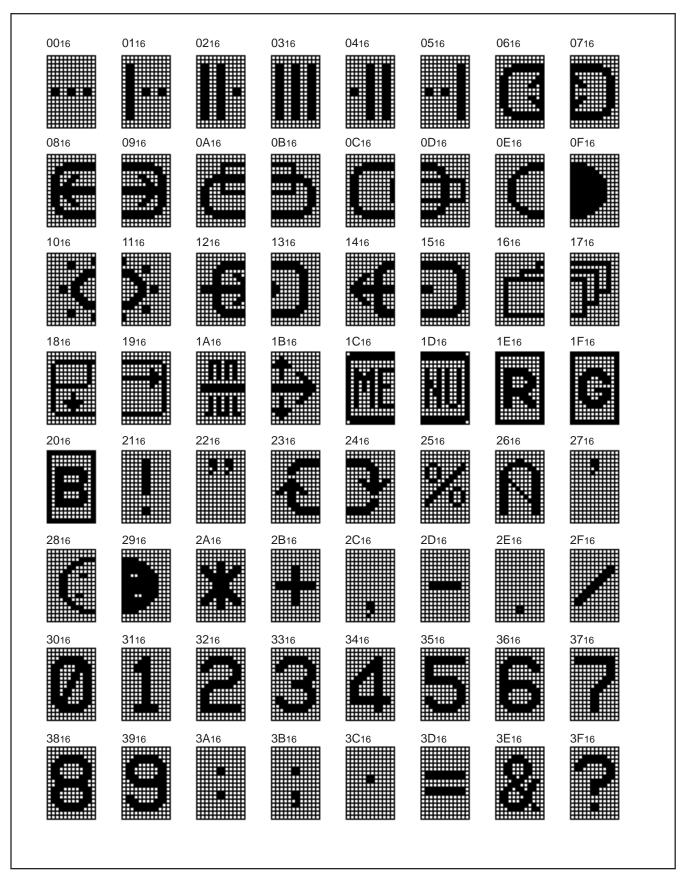

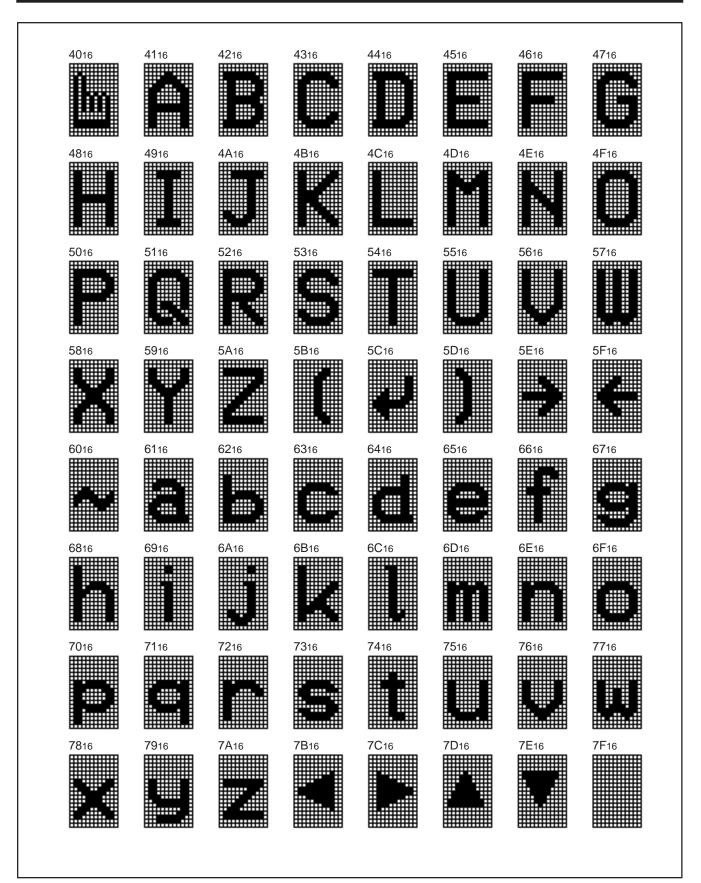

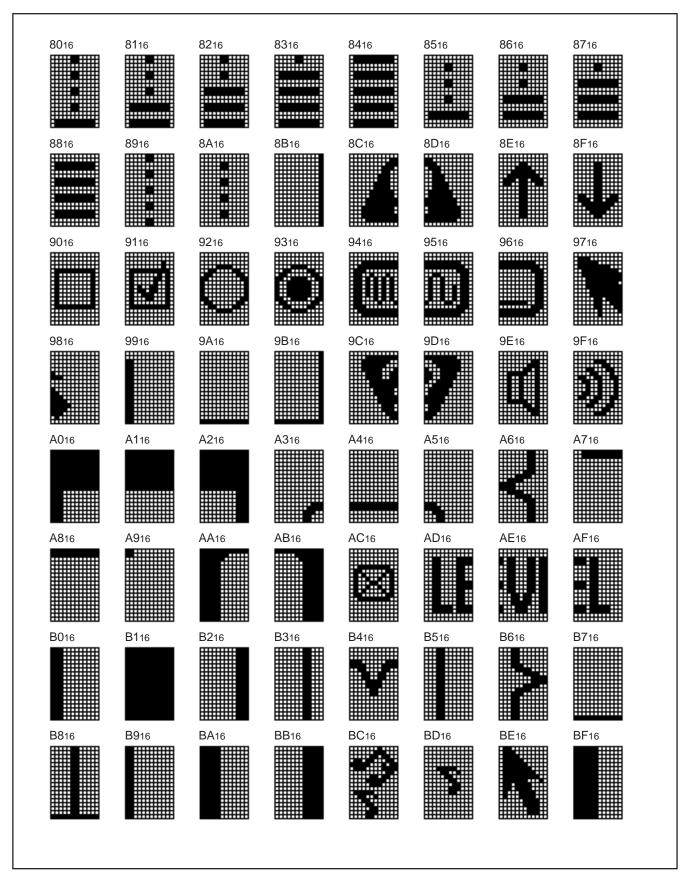

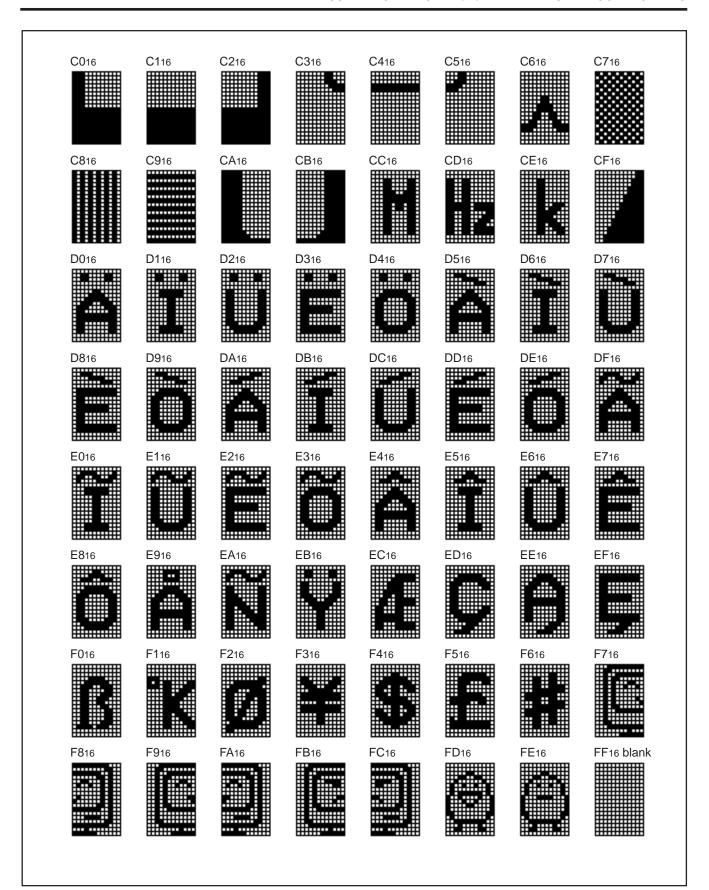

For M35072-002FP that is a standard ROM version of M35072-XXXFP respectively, the character pattern is also mentioned.

#### **FEATURES**

| • Screen composition 24 characters 12 lines X 2 pages             |

|-------------------------------------------------------------------|

| ● Number of characters displayed 288 (Max.) X 2 pages             |

| Character composition                                             |

| • Characters available page 0 : 256 characters                    |

| page 1 : 256 characters                                           |

| ● Character sizes available 4 (vertical) X 2 (horizontal)         |

| Display locations available                                       |

| Horizontal direction                                              |

| Vertical direction 1023 locations                                 |

| Blinking Character units                                          |

| Cycle : division of vertical synchronization signal into 32 or 64 |

| Duty : 25%, 50%, or 75%                                           |

| • Data input By the 16-bit serial input function                  |

| <ul><li>Coloring</li></ul>                                        |

| Character color Character unit                                    |

| Background coloring Character unit                                |

| Border (shadow) coloring 8 colors (RGB output)                    |

| Specified by register                                             |

| Raster coloring 8 colors (RGB output)                             |

| Specified by register                                             |

| • Blanking Character size blanking                                |

| Border size blanking                                              |

| Matrix-outline blanking                                           |

| All blanking (all raster area)                                    |

- Output ports

- 4 shared output ports (toggled between RGB output)

- 4 dedicated output ports

- Display RAM erase function

- Display input frequency range ...... Fosc = 20MHz to 80MHz

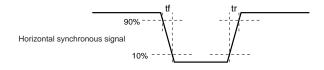

- Horizontal synchronous input frequency

- ......H.sync = 15 kHz to 130 kHz

- Display oscillation stop function

#### **APPLICATION**

Liquid crystal display, Plasma display

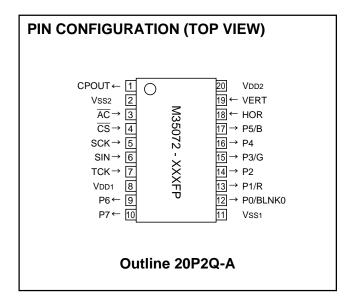

## **PIN DESCRIPTION**

| Pin<br>Number | Symbol   | Pin name                                 | Input/<br>Output | Function                                                                                                                                                          |

|---------------|----------|------------------------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

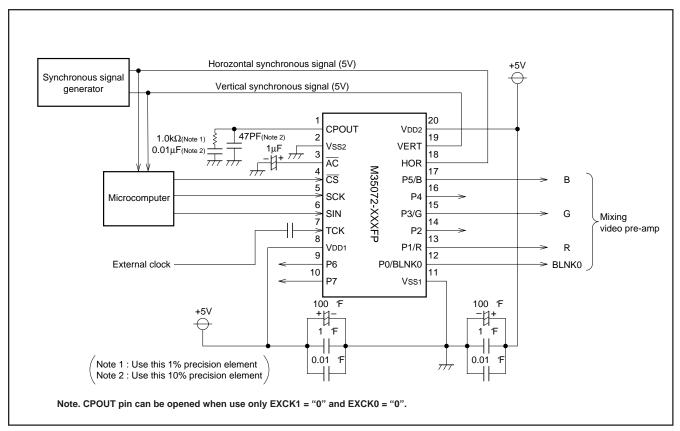

| 1             | CPOUT    | Filter output                            | Output           | Filter output. Connect loop filter to this pin.                                                                                                                   |

| 2             | VSS2     | Earthing pin                             | -                | Connect to GND.                                                                                                                                                   |

| 3             | ĀC       | Auto-clear input                         | Input            | When "L", this pin resets the internal IC circuit. Hysteresis input. Built-in pull-up resistor.                                                                   |

| 4             | CS       | Chip select input                        | Input            | This is the chip select input pin, and when serial data transmission is being carried out, it goes to "L." Hysteresis input. Built-in pull-up resistor.           |

| 5             | SCK      | Serial clock input                       | Input            | When $\overline{\text{CS}}$ pin is "L," SIN serial data is taken in when SCK rises. Hysteresis input. Built-in pull-up resistor.                                  |

| 6             | SIN      | Serial data input                        | Input            | This is the pin for serial input of data and addresses for the display control register and the display data memory. Hysteresis input. Built-in pull-up resistor. |

| 7             | TCK      | External clock                           | Input            | This is the pin for external clock input.                                                                                                                         |

| 8             | VDD1     | Power pin                                | _                | Please connect to +5V with the power pin.                                                                                                                         |

| 9             | P6       | Port P6 output                           | Output           | This is the output port.                                                                                                                                          |

| 10            | P7       | Port P7 output                           | Output           | This is the output port.                                                                                                                                          |

| 11            | Vss1     | Earthing pin                             | _                | Please connect to GND using circuit earthing pin.                                                                                                                 |

| 12            | P0/BLNK0 | Port P0 output                           | Output           | This pin can be toggled between port pin output and BLNK0 signal output.                                                                                          |

| 13            | P1/R     | Port P1 output                           | Output           | This pin can be toggled between port pin output and R signal output.                                                                                              |

| 14            | P2       | Port P2 output                           | Output           | This is the output port.                                                                                                                                          |

| 15            | P3/G     | Port P3 output                           | Output           | This pin can be toggled between port pin output and G signal output.                                                                                              |

| 16            | P4       | Port P4 output                           | Output           | This is the output port.                                                                                                                                          |

| 17            | P5/B     | Port P5 output                           | Output           | This pin can be toggled between port pin output and B signal output.                                                                                              |

| 18            | HOR      | Horizontal synchro-<br>nous signal input | Input            | This pin inputs the horizontal synchronous signal. Hysteresis input.                                                                                              |

| 19            | VERT     | Vertical synchro-<br>nous signal input   | Input            | This pin inputs the vertical synchronous signal. Hysteresis input.                                                                                                |

| 20            | VDD2     | Power pin                                | _                | Please connect to +5V with the power pin.                                                                                                                         |

#### **MEMORY CONSTITUTION**

Address 00016 to 11F16 are assigned to the display RAM, address 12016 to 12816 are assigned to the display control registers. The internal circuit is reset and all display control registers (address 12016 to 12816) are set to "0" when the  $\overline{AC}$  pin level is "L". And then, RAM is not erased and be undefinited. This memory is consisted of 2

pages: page 0 memory and page 1 memory (their addresses are common), page controlled by DAF bit of each address when writing data. For detail, see "Data input". Memory constitution is shown in Figure 1 and 2.

| Addresses         | DAF | DAE    | DAD                  | DAC    | DAB           | DAA    | DA9       | DA8    | DA7   | DA6   | DA5   | DA4      | DA3    | DA2   | DA1   | DA0   |

|-------------------|-----|--------|----------------------|--------|---------------|--------|-----------|--------|-------|-------|-------|----------|--------|-------|-------|-------|

| 00016             | 0   | BB     | BG                   | BR     | BLINK         | В      | G         | R      | C7    | C6    | C5    | C4       | С3     | C2    | C1    | C0    |

| 00116             | 0   | BB     | BG                   | BR     | BLINK         | В      | G         | R      | C7    | C6    | C5    | C4       | С3     | C2    | C1    | C0    |

|                   | :   |        | ackgroui<br>coloring |        | Blink-<br>ing | Char   | racter co | olor   |       |       | C     | Characte | r code |       |       |       |

| 11E <sub>16</sub> | 0   | BB     | BG                   | BR     | BLINK         | В      | G         | R      | C7    | C6    | C5    | C4       | С3     | C2    | C1    | C0    |

| 11F16             | 0   | BB     | BG                   | BR     | BLINK         | В      | G         | R      | C7    | C6    | C5    | C4       | С3     | C2    | C1    | C0    |

| 12016             | 0   | EXCK0  | VJT                  | DIVS1  | DIVS0         | DIV10  | DIV9      | DIV8   | DIV7  | DIV6  | DIV5  | DIV4     | DIV3   | DIV2  | DIV1  | DIV0  |

| 12116             | 0   | RSEL0  | PTD7                 | PTD6   | PTD5          | PTD4   | PTD3      | PTD2   | PTD1  | PTD0  | PTC5  | PTC4     | PTC3   | PTC2  | PTC1  | PTC0  |

| 12216             | 0   | RSEL1  | SPACE2               | SPACE1 | SPACE0        | HP10   | HP9       | HP8    | HP7   | HP6   | HP5   | HP4      | HP3    | HP2   | HP1   | HP0   |

| 12316             | 0   | EXCK1  | TEST3                | TEST2  | TEST1         | TEST0  | VP9       | VP8    | VP7   | VP6   | VP5   | VP4      | VP3    | VP2   | VP1   | VP0   |

| 12416             | 0   | TEST9  | TEST5                | TEST4  | DSP11         | DSP10  | DSP9      | DSP8   | DSP7  | DSP6  | DSP5  | DSP4     | DSP3   | DSP2  | DSP1  | DSP0  |

| 12516             | 0   | TEST10 | VSZ1H1               | VSZ1H0 | VSZ1L1        | VSZ1L0 | V1SZ1     | V1SZ0  | LIN9  | LIN8  | LIN7  | LIN6     | LIN5   | LIN4  | LIN3  | LIN2  |

| 12616             | 0   | TEST13 | VSZ2H1               | VSZ2H0 | VSZ2L1        | VSZ2L0 | V18SZ1    | V18SZ0 | LIN17 | LIN16 | LIN15 | LIN14    | LIN13  | LIN12 | LIN11 | LIN10 |

| 12716             | 0   | MODE0  | TEST12               | HSZ20  | TEST11        | HSZ10  | BETA14    | TEST8  | TEST7 | TEST6 | FB    | FG       | FR     | RB    | RG    | RR    |

| 12816             | 0   | MODE1  | BLINK2               | BLINK1 | BLINK0        | DSPON  | STOP      | RAMERS | SYAD  | BLK1  | BLK0  | POLH     | POLV   | VMASK | B/F   | BCOL  |

Fig. 1 Memory constitution (page 0 memory)

## M35072-XXXFP

#### SCREEN CHARACTER and PATTERN DISPLAY CONTROLLERS

| Addresses | DAF | DAE | DAD                 | DAC    | DAB           | DAA    | DA9       | DA8    | DA7   | DA6   | DA5   | DA4     | DA3     | DA2   | DA1   | DA0   |

|-----------|-----|-----|---------------------|--------|---------------|--------|-----------|--------|-------|-------|-------|---------|---------|-------|-------|-------|

| 00016     | 1   | BB  | BG                  | BR     | BLINK         | В      | G         | R      | C7    | C6    | C5    | C4      | C3      | C2    | C1    | C0    |

| 00116     | 1   | BB  | BG                  | BR     | BLINK         | В      | G         | R      | C7    | C6    | C5    | C4      | C3      | C2    | C1    | C0    |

|           |     | В   | ackgrou<br>coloring | I .    | Blink-<br>ing | Chai   | racter co | olor   |       |       |       | Charact | er code |       |       |       |

| 11E16     | 1   | ВВ  | BG                  | BR     | BLINK         | В      | G         | R      | C7    | C6    | C5    | C4      | C3      | C2    | C1    | C0    |

| 11F16     | 1   | BB  | BG                  | BR     | BLINK         | В      | G         | R      | C7    | C6    | C5    | C4      | C3      | C2    | C1    | C0    |

| 12016     | 1   | -   | _                   | _      | _             | _      | -         | _      | -     | _     | _     | _       | _       | _     | _     | _     |

| 12116     | 1   | -   | _                   | _      | -             | -      | _         | _      | -     | -     | -     | -       | -       | -     | -     | -     |

| 12216     | 1   | -   | SPACE2              | SPACE1 | SPACE0        | HP10   | HP9       | HP8    | HP7   | HP6   | HP5   | HP4     | HP3     | HP2   | HP1   | HP0   |

| 12316     | 1   | _   | TEST3               | TEST2  | TEST1         | TEST0  | VP9       | VP8    | VP7   | VP6   | VP5   | VP4     | VP3     | VP2   | VP1   | VP0   |

| 12416     | 1   | -   | _                   | TEST4  | DSP11         | DSP10  | DSP9      | DSP8   | DSP7  | DSP6  | DSP5  | DSP4    | DSP3    | DSP2  | DSP1  | DSP0  |

| 12516     | 1   | -   | VSZ1H1              | VSZ1H0 | VSZ1L1        | VSZ1L0 | V1SZ1     | V1SZ0  | LIN9  | LIN8  | LIN7  | LIN6    | LIN5    | LIN4  | LIN3  | LIN2  |

| 12616     | 1   | -   | VSZ2H1              | VSZ2H0 | VSZ2L1        | VSZ2L0 | V18SZ1    | V18SZ0 | LIN17 | LIN16 | LIN15 | LIN14   | LIN13   | LIN12 | LIN11 | LIN10 |

| 12716     | 1   | -   | TEST12              | HSZ20  | TEST11        | HSZ10  | BETA14    | TEST8  | TEST7 | TEST6 | FB    | FG      | FR      | RB    | RG    | RR    |

| 12816     | 1   | -   | BLINK2              | BLINK1 | BLINK0        | DSPON  | TEST13    | RAMERS | SYAD  | BLK1  | BLK0  | -       | -       | -     | -     | BCOL  |

Fig. 2 Memory constitution (page 1 memory)

Note: Page 0 and page 1 registers are found in their respective pages. For example, HP10 to HP0 of the page 0 memory sets the horizontal display start position of page 0, whereas HP10 to HP0 (same register name) of the page 1 memory sets the horizontal display start position of page 1. Also, registers common to both page 0 and page 1 are found only in the page 0 memory. For example, PTC0 is the control register of the P0 pin and is found only in the page 0 memory.

#### **SCREEN CONSTITUTION**

The screen lines and rows are determined from each address of the display RAM (page 0 and page 1 are common). The screen constitution is shown in Figure 3.

| _   | _     |       |       |       |                   |       |                   |       |       |       |       |       |       |       |       |       |       |       |       |                   |                   |       |                   |       |

|-----|-------|-------|-------|-------|-------------------|-------|-------------------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------------------|-------------------|-------|-------------------|-------|

| Row | 1     | 2     | 3     | 4     | 5                 | 6     | 7                 | 8     | 9     | 10    | 11    | 12    | 13    | 14    | 15    | 16    | 17    | 18    | 19    | 20                | 21                | 22    | 23                | 24    |

| 1   | 00016 | 00116 | 00216 | 00316 | 00416             | 00516 | 00616             | 00716 | 00816 | 00916 | 00A16 | 00B16 | 00C16 | 00D16 | 00E16 | 00F16 | 01016 | 01116 | 01216 | 01316             | 01416             | 01516 | 01616             | 01716 |

| 2   | 01816 | 01916 | 01A16 | 01B16 | 01C <sub>16</sub> | 01D16 | 01E <sub>16</sub> | 01F16 | 02016 | 02116 | 02216 | 02316 | 02416 | 02516 | 02616 | 02716 | 02816 | 02916 | 02A16 | 02B16             | 02C16             | 02D16 | 02E16             | 02F16 |

| 3   | 03016 | 03116 | 03216 | 03316 | 03416             | 03516 | 03616             | 03716 | 03816 | 03916 | 03A16 | 03B16 | 03C16 | 03D16 | 03E16 | 03F16 | 04016 | 04116 | 04216 | 04316             | 04416             | 04516 | 04616             | 04716 |

| 4   | 04816 | 04916 | 04A16 | 04B16 | 04C16             | 04D16 | 04E16             | 04F16 | 05016 | 05116 | 05216 | 05316 | 05416 | 05516 | 05616 | 05716 | 05816 | 05916 | 05A16 | 05B16             | 05C16             | 05D16 | 05E16             | 05F16 |

| 5   | 06016 | 06116 | 06216 | 06316 | 06416             | 06516 | 06616             | 06716 | 06816 | 06916 | 06A16 | 06B16 | 06C16 | 06D16 | 06E16 | 06F16 | 07016 | 07116 | 07216 | 07316             | 07416             | 07516 | 07616             | 07716 |

| 6   | 07816 | 07916 | 07A16 | 07B16 | 07C16             | 07D16 | 07E16             | 07F16 | 08016 | 08116 | 08216 | 08316 | 08416 | 08516 | 08616 | 08716 | 08816 | 08916 | 08A16 | 08B16             | 08C16             | 08D16 | 08E16             | 08F16 |

| 7   | 09016 | 09116 | 09216 | 09316 | 09416             | 09516 | 09616             | 09716 | 09816 | 09916 | 09A16 | 09B16 | 09C16 | 09D16 | 09E16 | 09F16 | 0A016 | 0A116 | 0A216 | 0A316             | 0A416             | 0A516 | 0A616             | 0A716 |

| 8   | 0A816 | 0A916 | 0AA16 | 0AB16 | 0AC16             | 0AD16 | 0AE16             | 0AF16 | 0B016 | 0B116 | 0B216 | 0B316 | 0B416 | 0B516 | 0B616 | 0B716 | 0B816 | 0B916 | 0BA16 | 0BB16             | 0BC16             | 0BD16 | 0BE16             | 0BF16 |

| 9   | 0C016 | 0C116 | 0C216 | 0C316 | 0C416             | 0C516 | 0C616             | 0C716 | 0C816 | 0C916 | 0CA16 | 0CB16 | 0CC16 | 0CD16 | 0CE16 | 0CF16 | 0D016 | 0D116 | 0D216 | 0D316             | 0D416             | 0D516 | 0D616             | 0D716 |

| 10  | 0D816 | 0D916 | 0DA16 | 0DB16 | 0DC16             | 0DD16 | 0DE16             | 0DF16 | 0E016 | 0E116 | 0E216 | 0E316 | 0E416 | 0E516 | 0E616 | 0E716 | 0E816 | 0E916 | 0EA16 | 0EB16             | 0EC16             | 0ED16 | 0EE16             | 0EF16 |

| 11  | 0F016 | 0F116 | 0F216 | 0F316 | 0F416             | 0F516 | 0F616             | 0F716 | 0F816 | 0F916 | 0FA16 | 0FB16 | 0FC16 | 0FD16 | 0FE16 | 0FF16 | 10016 | 10116 | 10216 | 10316             | 10416             | 10516 | 10616             | 10716 |

| 12  | 10816 | 10916 | 10A16 | 10B16 | 10C16             | 10D16 | 10E <sub>16</sub> | 10F16 | 11016 | 11116 | 11216 | 11316 | 11416 | 11516 | 11616 | 11716 | 11816 | 11916 | 11A16 | 11B <sub>16</sub> | 11C <sub>16</sub> | 11D16 | 11E <sub>16</sub> | 11F16 |

\* The hexadecimal numbers in the boxes show the display RAM address.

Fig. 3 Screen constitution

## **DISPLAY RAM**

Address 00016 to 11F16

| DA | Register  |        | Contents                                                                             | Remarks                                   |

|----|-----------|--------|--------------------------------------------------------------------------------------|-------------------------------------------|

|    | rtogistor | Status | Function                                                                             | Nomano                                    |

| 0  | 00        | 0      | Set the displayed ROM character and                                                  | Set display character                     |

| 0  | C0        | 1      | Set the displayed ROM character code.                                                | Set display character                     |

|    |           | 0      | To write data into page 0 (Note 2), select the data from the ROM                     |                                           |

| 1  | C1        | 1      | characters (256 types) for page 0 and set the character code. To                     |                                           |

|    |           | 0      | write data into page 1, do the same from the ROM characters (256 types) for page 1.  |                                           |

| 2  | C2        | 1      |                                                                                      |                                           |

|    |           | 0      |                                                                                      |                                           |

| 3  | C3        | 1      |                                                                                      |                                           |

|    |           | 0      |                                                                                      |                                           |

| 4  | C4        | 1      |                                                                                      |                                           |

|    |           |        |                                                                                      |                                           |

| 5  | C5        | 0      |                                                                                      |                                           |

|    |           |        |                                                                                      |                                           |

| 6  | C6        | 0      |                                                                                      |                                           |

|    |           | 1      |                                                                                      |                                           |

| 7  | C7        | 0      |                                                                                      |                                           |

|    |           | 1      |                                                                                      |                                           |

| 8  | R         | 0      | B G R Color                                                                          | Set character color (character unit)      |

|    |           | 1      | 0 0 0 Black<br>0 0 1 Red                                                             |                                           |

|    |           | 0      | 0 1 0 Green                                                                          |                                           |

| 9  | G         | 1      | 0 1 1 Yellow<br>1 0 0 Blue                                                           |                                           |

|    |           | 0      | 1 0 1 Magenta                                                                        |                                           |

| Α  | В         | 1      | 1 1 0 Cyan<br>1 1 1 White                                                            |                                           |

|    |           | 0      | Do not blink.                                                                        | Set blinking                              |

| В  | BLINK     | 1      |                                                                                      | See register BLINK2 to BLINK0 (ad-        |

|    |           |        | Blinking                                                                             | dress128 <sub>16</sub> )                  |

| С  | BR        | 0      | BB         BG         BR         Color           0         0         0         Black | Set character background (character unit) |

|    |           | 1      | 0 0 1 Red                                                                            | (Grianaciei uriii)                        |

| D  | BG        | 0      | 0 1 0 Green<br>0 1 1 Yellow                                                          |                                           |

|    | 100       | 1      | 1 0 0 Blue                                                                           |                                           |

|    |           | 0      | 1 0 1 Magenta                                                                        |                                           |

| E  | BB        | 1      | 1 1 0 Cyan<br>1 1 1 White                                                            |                                           |

Notes 1. The display RAM is undefined state at the  $\overline{AC}$  pin.

2. The display RAM consists of 2 pages, page 0 and page 1 (common address). The page in which data is written is controlled by the DAF bit. When set to "0", data is written into page 0, whereas when set to "1", data is written into page 1.

#### **REGISTERS DESCRIPTION**

(1) Address 120<sub>16</sub>

|    | 5                 |        | Contents                                                                                                                                              |                                                                                                                                                      |

|----|-------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| DA | Register          | Status | Function                                                                                                                                              | Remarks                                                                                                                                              |

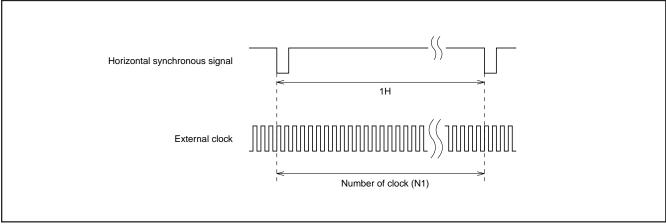

| 0  | DIV0<br>(Note 3)  | 1      | Set external clock frequency division value of horizontal oscillation frequency.                                                                      | Set display frequency by division value setting. For details, see REGISTER                                                                           |

| 1  | DIV1<br>(Note 3)  | 1      | $N1 = \sum_{n=0}^{10} (DIVn \times 2^n)$                                                                                                              | SUPPLYMENTARY DESCRIPTION (1).                                                                                                                       |

| 2  | DIV2<br>(Note 3)  | 1      | N1 : division value                                                                                                                                   | Also, set the display frequency range by<br>registers DIVS0, DIVS1(address<br>12016), RSEL0(address 12116) and<br>RSEL1(address 12216) in accordance |

| 3  | DIV3<br>(Note 3)  | 1      |                                                                                                                                                       | with the display frequency.  Any of this settings above is required                                                                                  |

| 4  | DIV4<br>(Note 3)  | 1      |                                                                                                                                                       | only when EXCK1 = 1, EXCK0 = 1.                                                                                                                      |

| 5  | DIV5<br>(Note 3)  | 1      |                                                                                                                                                       |                                                                                                                                                      |

| 6  | DIV6<br>(Note 3)  | 1      |                                                                                                                                                       |                                                                                                                                                      |

| 7  | DIV7<br>(Note 3)  | 1      |                                                                                                                                                       |                                                                                                                                                      |

| 8  | DIV8<br>(Note 3)  | 1      |                                                                                                                                                       |                                                                                                                                                      |

| 9  | DIV9<br>(Note 3)  | 1      |                                                                                                                                                       |                                                                                                                                                      |

| А  | DIV10<br>(Note 3) | 1      |                                                                                                                                                       |                                                                                                                                                      |

| В  | DIVS0<br>(Note 3) | 1      | For setting, see REGISTER SUPPLYMENTARY DESCRIPTION (2).                                                                                              | Set display frequency range.                                                                                                                         |

| С  | DIVS1<br>(Note 3) | 1      |                                                                                                                                                       |                                                                                                                                                      |

| D  | VJT<br>(Note 3)   | 1      | It is used to "0", normally.  Alleviates continuous vertical jitters.                                                                                 |                                                                                                                                                      |

| E  | EXCK0<br>(Note 3) | 1      | EXCK1 EXCK0 Display clock input  0 0 External synchronous (external clock)  0 1 Do not set  1 0 Do not set  1 1 External synchronous (internal clock) | Display clock setting See REGISTER SUPPLYMENTARY DESCRIPTION (1) EXCK1 : address12316                                                                |

- 2. The page in which data is written is controlled by the DAF bit. When set to "0", data is written into page 0, whereas when set to "1", data is written into page 1.

- 3. Registers marked with (Note 3) are found only in page 0, therefore the register value does not change when the DAF bit is set to "1".

#### (2) Address 121<sub>16</sub>

| DA | Register |        | Contents                                                  | Remarks                      |  |  |  |

|----|----------|--------|-----------------------------------------------------------|------------------------------|--|--|--|

| DA | Register | Status | Function                                                  | Remarks                      |  |  |  |

| 0  | PTC0     | 0      | P0 output (port P0).                                      | P0 pin output control.       |  |  |  |

|    | (Note 3) | 1      | BLNK0 output.                                             |                              |  |  |  |

| 1  | PTC1     | 0      | P1 output (port P1).                                      | P1 pin output control.       |  |  |  |

|    | (Note 3) | 1      | R signal output.                                          |                              |  |  |  |

| 2  | PTC2     | 0      | P2 output (port P2).                                      | P2 pin output control.       |  |  |  |

|    | (Note 3) | 1      | Can not be used.                                          |                              |  |  |  |

| 3  | PTC3     | 0      | P3 output (port P3).                                      | P3 pin output control.       |  |  |  |

|    | (Note 3) | 1      | G signal output.                                          |                              |  |  |  |

| 4  | PTC4     | 0      | P4 output (port P4).                                      | P4 pin output control.       |  |  |  |

|    | (Note 3) | 1      | Can not be used.                                          |                              |  |  |  |

| 5  | PTC5     | 0      | P5 output (port P5).                                      | P5 pin output control.       |  |  |  |

|    | (Note 3) | 1      | B signal output.                                          |                              |  |  |  |

| 6  | PTD0     | 0      | "L" output or negative polarity output (BLNK0 output).    | P0 pin data control.         |  |  |  |

| Ü  | (Note 3) | 1      | "H" output or positive polarity output (BLNK0 output).    |                              |  |  |  |

| 7  | PTD1     | 0      | "L" output or negative polarity output (R signal output). | P1 pin data control.         |  |  |  |

|    | (Note 3) | 1      | "H" output or positive polarity output (R signal output). |                              |  |  |  |

| 8  | PTD2     | 0      | "L" output.                                               | P2 pin data control.         |  |  |  |

|    | (Note 3) | 1      | "H" output.                                               |                              |  |  |  |

| 9  | PTD3     | 0      | "L" output or negative polarity output (G signal output). | P3 pin data control.         |  |  |  |

|    | (Note 3) | 1      | "H" output or positive polarity output (G signal output). |                              |  |  |  |

| Α  | PTD4     | 0      | "L" output.                                               | P4 pin data control.         |  |  |  |

| ^  | (Note 3) | 1      | "H" output.                                               |                              |  |  |  |

| В  | PTD5     | 0      | "L" output or negative polarity output (B signal output). | P5 pin data control.         |  |  |  |

| В  | (Note 3) | 1      | "H" output or positive polarity output (B signal output). |                              |  |  |  |

|    | PTD6     | 0      | "L" output.                                               | P6 pin data control.         |  |  |  |

| С  | (Note 3) | 1      | "H" output.                                               |                              |  |  |  |

|    | PTD7     | 0      | "L" output.                                               | P7 pin data control.         |  |  |  |

| D  | D   PID/ | 1      | "H" output.                                               |                              |  |  |  |

| _  | RSEL0    | 0      | For setting, see REGISTER SUPPLYMENTARY DESCRIPTION       | Set display frequency range. |  |  |  |

| Е  | (Note 3) | 1      | (2).                                                      |                              |  |  |  |

- 2. The page in which data is written is controlled by the DAF bit. When set to "0", data is written into page 0, whereas when set to "1", data is written into page 1.

- 3. Registers marked with (Note 3) are found only in page 0, therefore the register value does not change when the DAF bit is set to "1".

| (3) Addres |          |        | Contents                                                 |                                                                                  |

|------------|----------|--------|----------------------------------------------------------|----------------------------------------------------------------------------------|

| DA         | Register | Status | Function                                                 | Remarks                                                                          |

| 0          | HP0      | 0      | If HS is the horizontal display start location,          | Horizontal display start location is                                             |

| 0          | пРО      | 1      | $HS = T \times (\sum_{n=0}^{10} 2^n HP_n + 6)$           | specified using the 11 bits from HP10 to HP0.                                    |

| 1          | HP1      | 0      | T : Period of display frequency                          | HP10 to HP0 = (000000000002) and (000001001112) setting is forbidden.            |

|            |          | 1      | 2007 settings are possible.                              |                                                                                  |

| 2          | HP2      | 1      | HOR                                                      |                                                                                  |

|            |          |        |                                                          |                                                                                  |

| 3          | HP3      | 1      |                                                          |                                                                                  |

| 4          | LIDA     | 0      | vs ↓ vs                                                  |                                                                                  |

| 4          | HP4      | 1      | <->-                                                     |                                                                                  |

| 5          | HP5      | 0      | HS <sup>*</sup> Display area                             |                                                                                  |

|            | 1110     | 1      |                                                          | HS* (shown left) shows horizontal display start location that is register B/F    |

| 6          | HP6      | 0      |                                                          | (address 128 <sub>16</sub> ) = 0 is set.                                         |

|            |          | 1      |                                                          |                                                                                  |

| 7          | HP7      | 0      |                                                          |                                                                                  |

|            |          | 1      |                                                          |                                                                                  |

| 8          | HP8      | 0      |                                                          |                                                                                  |

|            |          | 1      |                                                          |                                                                                  |

| 9          | HP9      | 1      |                                                          |                                                                                  |

|            |          | (0)    |                                                          |                                                                                  |

| Α          | HP10     | 1      |                                                          |                                                                                  |

| В          | SPACE0   | 0      | SPACE Number of Lines and Space <(S) represents space>   | Leave one line worth of space in the vertical direction.                         |

|            | 0171020  | 1      | 0 0 0 12<br>0 0 1 1 (S) 10 (S) 1                         | For example, 6 (S) 6 indicates two sets of 6 lines with a line of spaces between |

| С          | SPACE1   | 0      | 0 1 0 2 (S) 8 (S) 2<br>0 1 1 3 (S) 6 (S) 3               | lines 6 and 7. A line is 18 × N horizontal scan lines.                           |

|            |          | 1      | 1 0 0 4 (S) 4 (S) 4<br>1 0 1 5 (S) 2 (S) 5               | N is determined by the character size in the vertical direction                  |

| D          | SPACE2   | 0      | 1 1 0 6 (S) 6<br>1 1 1 6 (S)(S) 6                        |                                                                                  |

|            |          | 1      | (S) represents one line worth of spac                    |                                                                                  |

| E          | RSEL1    | 0      | For setting, see REGISTER SUPPLYMENTARY DESCRIPTION (2). | Set display frequency range.                                                     |

|            | (Note 3) | 1      | (4).                                                     |                                                                                  |

- 2. The page in which data is written is controlled by the DAF bit. When set to "0", data is written into page 0, whereas when set to "1", data is written into page 1.

- 3. Registers marked with (Note 3) are found only in page 0, therefore the register value does not change when the DAF bit is set to "1".

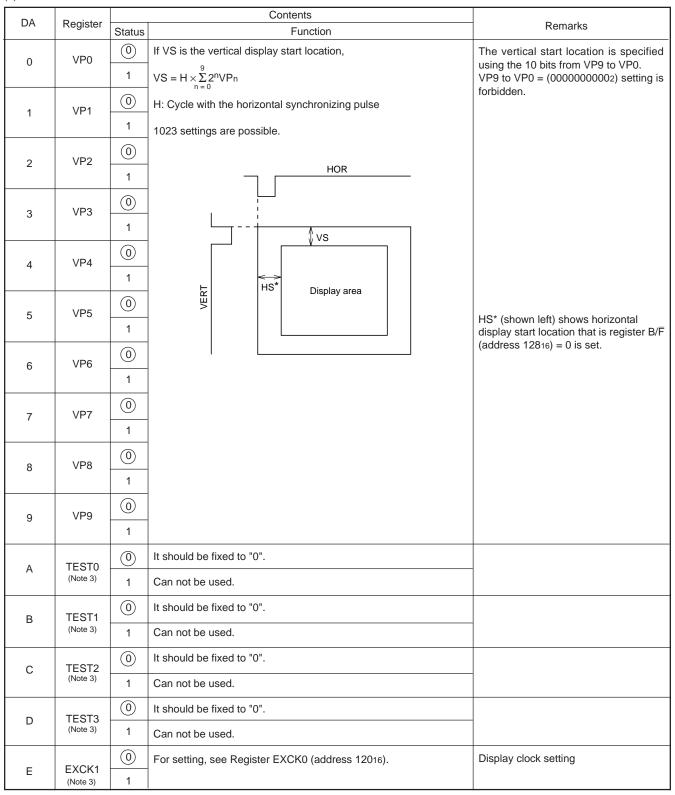

#### (4) Address 123<sub>16</sub>

- 2. The page in which data is written is controlled by the DAF bit. When set to "0", data is written into page 0, whereas when set to "1", data is written into page 1.

- 3. Registers marked with (Note 3) are found only in page 0, therefore the register value does not change when the DAF bit is set to "1"

#### (5) Address 124<sub>16</sub>

| DA | Register |        |                              |                          | Contents                               |                                           |       | Daniele                            |

|----|----------|--------|------------------------------|--------------------------|----------------------------------------|-------------------------------------------|-------|------------------------------------|

|    | Register | Status |                              |                          | Function                               |                                           |       | Remarks                            |

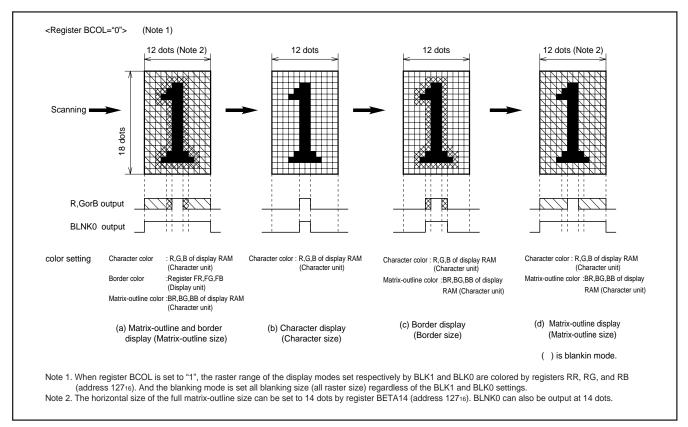

| 0  | DSP0     | 0      | The display r                | node (blar               | nking mode) for lin                    | e n on the display                        |       | Sets the display mode of line 1.   |

|    |          | 1      |                              |                          | e, using DŚPn (n                       |                                           |       |                                    |

| 1  | DSP1     | 0      | The display r<br>BLK1 and BL | node is de<br>.K0 (addre | etermined by the coess 12816). Setting | ombination of regis<br>s are given below. | sters | Sets the display mode of line 2.   |

| '  | DOI 1    | 1      |                              |                          |                                        |                                           |       |                                    |

|    | DODO     | 0      | BLK1                         | BLK0                     | DSPn= "0"                              | DSPn= "1"                                 |       | Coto the diapley made of line 2    |

| 2  | DSP2     | 1      | 0                            | 0<br>1                   | Matrix-outline border Character        | Matrix-outline<br>Border                  |       | Sets the display mode of line 3.   |

|    |          | 0      | 1 1                          | 1                        | Border<br>Matrix-outline               | Matrix-outline<br>Character               |       |                                    |

| 3  | DSP3     | 1      |                              |                          | (At r                                  | egister BCOL = "0")                       |       | Sets the display mode of line 4.   |

|    |          | 0      |                              |                          |                                        |                                           |       |                                    |

| 4  | DSP4     |        | For detail, se               | e DISPLA                 | Y FORM1(1).                            |                                           |       | Sets the display mode of line 5.   |

|    |          | 1      |                              |                          |                                        |                                           |       |                                    |

| 5  | DSP5     | 0      |                              |                          |                                        |                                           |       | Sets the display mode of line 6.   |

|    |          | 1      |                              |                          |                                        |                                           |       |                                    |

| 6  | DSP6     | 0      |                              |                          |                                        |                                           |       | Sets the display mode of line 7.   |

|    |          | 1      |                              |                          |                                        |                                           |       |                                    |

| 7  | DSP7     | 0      |                              |                          |                                        |                                           |       | Sets the display mode of line 8.   |

|    |          | 1      |                              |                          |                                        |                                           |       |                                    |

| 8  | DSP8     | 0      |                              |                          |                                        |                                           |       | Sets the display mode of line 9.   |

| O  | D31 0    | 1      |                              |                          |                                        |                                           |       | Solo the diopidy mode of line of   |

|    | 2020     | 0      |                              |                          |                                        |                                           |       | Cata the display was do of line 40 |

| 9  | DSP9     | 1      |                              |                          |                                        |                                           |       | Sets the display mode of line 10.  |

|    |          | 0      |                              |                          |                                        |                                           |       |                                    |

| Α  | DSP10    | 1      |                              |                          |                                        |                                           |       | Sets the display mode of line 11.  |

|    |          | 0      |                              |                          |                                        |                                           |       |                                    |

| В  | DSP11    | 1      |                              |                          |                                        |                                           |       | Sets the display mode of line 12.  |

|    |          |        | It should be f               | ived to "O"              |                                        |                                           |       |                                    |

| С  | TEST4    | 0      |                              |                          | •                                      |                                           |       | _                                  |

|    |          | 1      | Can not be us                |                          |                                        |                                           |       |                                    |

| D  | TEST5    | 0      | It should be f               |                          |                                        |                                           |       | _                                  |

|    | (Note 3) | 1      | Can not be u                 |                          |                                        |                                           |       |                                    |

| Е  | TEST9    | 0      | Can not be u                 | sed.                     |                                        |                                           |       |                                    |

|    | (Note 3) | 1      | It should be f               | ixed to "1"              |                                        |                                           |       |                                    |

- 2. The page in which data is written is controlled by the DAF bit. When set to "0", data is written into page 0, whereas when set to "1", data is written into page 1.

- 3. Registers marked with (Note 3) are found only in page 0, therefore the register value does not change when the DAF bit is set to "1".

#### (6) Address 125<sub>16</sub>

| DA  | Register           |        | Contents                                                                                               | Domesto                                                                   |

|-----|--------------------|--------|--------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

|     | Register           | Status | Function                                                                                               | Remarks                                                                   |

| 0   | LIN2               | 0      | The vertical dot size for line n in the character dot lines (18 vertical                               | Character size setting in the vertical                                    |

|     |                    | 1      | lines) is set using LINn (n = 2 to 17).                                                                | direction for the 2nd line.                                               |

| 1   | LIN3               | 0      | Dot size can be selected between 2 types for each dot line.                                            | Character size setting in the vertical                                    |

|     | Liivo              | 1      | For det size, see the helpy registers. Line 1 and lines 2 to 12 can                                    | direction for the 3rd line.                                               |

| 2   | LIN4               | 0      | For dot size, see the below registers. Line 1 and lines 2 to 12 can be set independent of one another. | Character size setting in the vertical                                    |

|     | LINA               | 1      | LINn = "0" LINn = "1"                                                                                  | direction for the 4th line.                                               |

| 3   | LIN5               | 0      | 1st line Refer to VSZ1L0 Refer to VSZ1H0                                                               | Character size setting in the vertical                                    |

| 3   | LINO               | 1      | and VSZ1L1   and VSZ1H1                                                                                | direction for the 5th line.                                               |

| 4   |                    | 0      | line   and VSZ2L1   and VSZ2H1                                                                         | Character size setting in the vertical                                    |

| 4   | LIN6               | 1      |                                                                                                        | direction for the 6th line.                                               |

| _   |                    | 0      |                                                                                                        | Character size setting in the vertical                                    |

| 5   | LIN7               | 1      |                                                                                                        | direction for the 7th line.                                               |

|     | LINIO              | 0      |                                                                                                        | Character size setting in the vertical                                    |

| 6   | LIN8               | 1      |                                                                                                        | direction for the 8th line.                                               |

| 7   | LIN9               | 0      |                                                                                                        | Character size setting in the vertical                                    |

| ,   | Liivo              | 1      |                                                                                                        | direction for the 9th line.                                               |

| 8   | V1SZ0              | 0      | H: Cycle with the horizontal synchronizing pulse                                                       | Character size setting in the vertical                                    |

|     | V 1320             | 1      | V1SZ1         V1SZ0         Vertical direction size           0         0         1H/dot               | direction for the 1st line.<br>(display monitor 1 to 12 line)             |

| 9   | V4.074             | 0      | 0 1 2H/dot<br>1 0 3H/dot                                                                               |                                                                           |

| 9   | V1SZ1              | 1      | 1 1 4H/dot                                                                                             |                                                                           |

| A   | VSZ1L0             | 0      | H: Cycle with the horizontal synchronizing pulse                                                       | Character size setting in the vertical                                    |

| _ ^ | VSZTLU             | 1      | VSZ1L1 VSZ1L0 Vertical direction size 0 0 1H/dot                                                       | direction (display monitor 1 line) at "0" state in register LIN2 to LIN17 |

| _   |                    | 0      | 0 1 2H/dot                                                                                             | (address 12516, 12616).                                                   |

| В   | VSZ1L1             | 1      | 1 0 3H/dot<br>1 1 4H/dot                                                                               |                                                                           |

|     | \/C=:::            | 0      | H: Cycle with the horizontal synchronizing pulse                                                       | Character size setting in the vertical                                    |

| С   | VSZ1H0             | 1      | VSZ1H1 VSZ1H0 Vertical direction size 0 0 1H/dot                                                       | direction (display monitor 1 line) at "1" state in register LIN2 to LIN17 |

|     |                    | 0      | 0 1 2H/dot                                                                                             | (address 12516, 12616).                                                   |

| D   | VSZ1H1             | 1      | 1 0 3H/dot<br>1 1 4H/dot                                                                               |                                                                           |

| _   | TECT               | 0      | It should be fixed to "0".                                                                             |                                                                           |

| E   | TEST10<br>(Note 3) | 1      | Can not be used.                                                                                       |                                                                           |

- 2. The page in which data is written is controlled by the DAF bit. When set to "0", data is written into page 0, whereas when set to "1", data is written into page 1.

- 3. Registers marked with (Note 3) are found only in page 0, therefore the register value does not change when the DAF bit is set to "1".

#### (7) Address 126<sub>16</sub>

| DA | Pogistor |        | Contents                                                                                                       | Barrada                                                                                                              |

|----|----------|--------|----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|

| DA | Register | Status | Function                                                                                                       | Remarks                                                                                                              |

| 0  | LIN10    | 0      | The vertical dot size for line n in the character dot lines (18 vertical                                       | Character size setting in the vertical direction for the 10th line.                                                  |

| 1  | LIN11    | 0      | lines) is set using LINn (n = 2 to 17).  Dot size can be selected between 2 types for each dot line.           | Character size setting in the vertical direction for the 11th line.                                                  |

| 2  | LIN12    | 0 1    | For dot size, see the below registers. Line 1 and lines 2 to 12 can be set independent of one another.         | Character size setting in the vertical direction for the 12th line.                                                  |

| 3  | LIN13    | 0 1    | LINn = "0" LINn = "1"                                                                                          | Character size setting in the vertical direction for the 13th line.                                                  |

| 4  | LIN14    | 1      | line and VSZ2L1 and VSZ2H1                                                                                     | Character size setting in the vertical direction for the 14th line.                                                  |

| 5  | LIN15    | 1      |                                                                                                                | Character size setting in the vertical direction for the 15th line.                                                  |

| 6  | LIN16    | 1      |                                                                                                                | Character size setting in the vertical direction for the 16th line.                                                  |

| 7  | LIN17    | 1      |                                                                                                                | Character size setting in the vertical direction for the 17th line.                                                  |

| 8  | V18SZ0   | 1      | H: Cycle with the horizontal synchronizing pulse    V18SZ1   V18SZ0   Vertical direction size   0              | Character size setting in the vertical direction for the 18th line. (display monitor 1 to 12 line)                   |

| 9  | V18SZ1   | 1      | 0 1 2H/dot<br>1 0 3H/dot<br>1 1 4H/dot                                                                         |                                                                                                                      |

| Α  | VSZ2L0   | 0 1    | H: Cycle with the horizontal synchronizing pulse    VSZ2L1   VSZ2L0   Vertical direction size   0   0   1H/dot | Character size setting in the vertical direction (display monitor for 2 to 12 line) at "0" state in register LIN2 to |

| В  | VSZ2L1   | 1      | 0 1 2H/dot<br>1 0 3H/dot<br>1 1 4H/dot                                                                         | LIN17 (address 12516, 12616).                                                                                        |

| С  | VSZ2H0   | 1      | H: Cycle with the horizontal synchronizing pulse    VSZ2H1   VSZ2H0   Vertical direction size   0   0   1H/dot | Character size setting in the vertical direction (display monitor for 2 to 12                                        |

| D  | VSZ2H1   | 1      | 0         1         2H/dot           1         0         3H/dot           1         1         4H/dot           | line) at "0" state in register LIN2 to LIN17 (address 12516, 12616).                                                 |

| E  | TEST13   | 1      | It should be fixed to "0".  Can not be used.                                                                   |                                                                                                                      |

- 2. The page in which data is written is controlled by the DAF bit. When set to "0", data is written into page 0, whereas when set to "1", data is written into page 1.

- 3. Registers marked with (Note 3) are found only in page 0, therefore the register value does not change when the DAF bit is set to "1".

## M35072-XXXFP

#### SCREEN CHARACTER and PATTERN DISPLAY CONTROLLERS

#### (8) Address 127<sub>16</sub>

| (8) Addres | 55 12716          |        |                          | Conter                        | nts             |                                                                            |

|------------|-------------------|--------|--------------------------|-------------------------------|-----------------|----------------------------------------------------------------------------|

| DA         | Register          | Status |                          |                               | nction          | Remarks                                                                    |

|            |                   | 0      |                          |                               |                 |                                                                            |

| 0          | RR                |        | RB RG 0                  | RR<br>0                       | Color<br>Black  | Sets the raster color of all blankings.                                    |

|            |                   | 1      | 0 0                      | 1                             | Red             |                                                                            |

| 1          | DC                | 0      | 0 1 0                    | 0                             | Green<br>Yellow |                                                                            |

| '          | RG                | 1      | 1 0                      | 0                             | Blue            |                                                                            |

|            |                   | 0      | 1 0                      | 0                             | Magenta<br>Cyan |                                                                            |

| 2          | RB                |        | 1 1                      | 1                             | White           |                                                                            |

|            |                   | 1      |                          |                               |                 |                                                                            |

|            |                   | 0      | FB FG                    | FR                            | Color           | Sets the blanking color of the Border                                      |

| 3          | FR                | 1      | 0 0                      | 0                             | Black           | size, or the shadow size.                                                  |

|            |                   | -      | 0 0 0                    | 0                             | Red<br>Green    |                                                                            |

| 4          | FG                | 0      | 0 1                      | 1                             | Yellow          |                                                                            |

|            |                   | 1      | 1 0                      | 0                             | Blue<br>Magenta |                                                                            |

|            |                   | 0      | 1 1                      | 0                             | Cyan            |                                                                            |

| 5          | FB                |        | 1 1                      | 1                             | White           |                                                                            |

|            |                   | 1      |                          |                               |                 |                                                                            |

| 6          | TEST6             | 0      | It should be fixed to "C | O".                           |                 |                                                                            |

|            | 15510             | 1      | Can not be used.         |                               |                 |                                                                            |

| 7          | TEST7             | 0      | It should be fixed to "( | 0".                           |                 |                                                                            |

|            |                   | 1      | Can not be used.         |                               |                 |                                                                            |

| 8          | TEST8             | 0      | It should be fixed to "C | 0".                           |                 |                                                                            |

|            |                   | 1      | Can not be used.         |                               |                 |                                                                            |

| 9          | BETA14            | 0      | Matrix-outline display   | (12×18                        | dot)            |                                                                            |

|            | DETAIT            | 1      | Matrix-outline display   | (14 × 18                      | dot)            |                                                                            |

| _          |                   | 0      |                          | l direction s                 | size            | Character size setting in the horizontal direction for the first line.     |

| A          | HSZ10             | 1      |                          | T/dot<br>?T/dot               |                 | T : Display frequency cycle                                                |